SLUSAH9-MARCH 2011

3.3-V/5-V Input, 6-A, D-CAP+<sup>™</sup> Mode Synchronous Step-Down Integrated FETs Converter

Check for Samples: TPS51317

# FEATURES

www.ti.com

- Integrated FETs Converter w/TI Proprietary D-CAP+<sup>™</sup> Mode Architecture

- Minimum External Components Count

- Support all MLCC Output Capacitor and SP/POSCAP

- Auto-Skip Mode and Ripple Reduction Mode

- · Optimized Efficiency at Light and Heavy Loads

- Selectable 800-kHz, 1-MHz, 1.2-MHz and 1.5-MHz Frequency

- Up to 6.0-V Conversion Voltage Range

- Adjustable Output Voltage Range From 0.6 V to 2 V

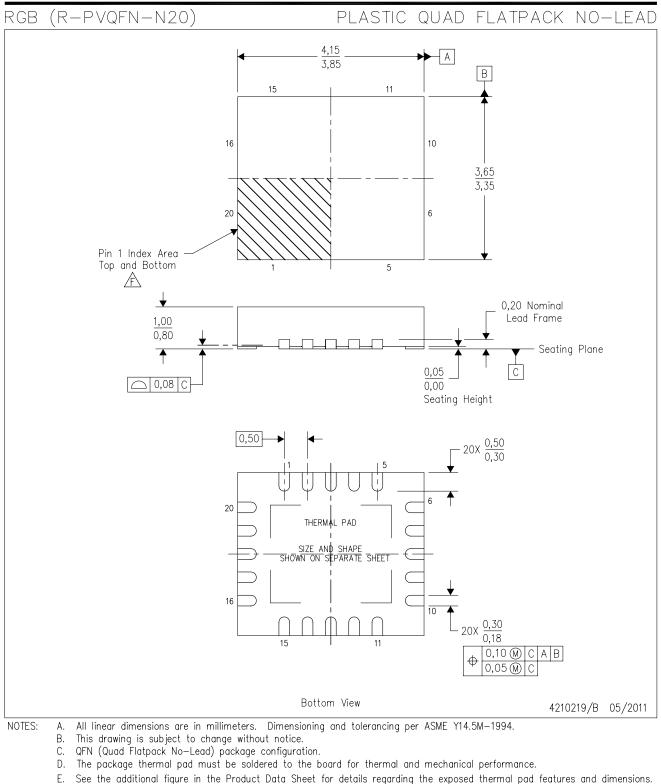

- Small 3.5 mm × 4 mm, 20-Pin QFN Package

# **APPLICATIONS**

Low-Voltage Applications Stepping Down from 5-V or 3.3-V Rail

# DESCRIPTION

The TPS51317 is a fully integrated synchronous buck regulator employing D-CAP+™ mode architechture. It is used for 3.3-V and 5-V step-down systems where space is a consideration, high-performance and optimized component count are required. The TPS51317 features four switching frequency settings (up to 1.5 MHz), synchronous operation in SKIP, droop support, external tracking support, pre-bias startup, output soft discharge, integrated bootstrap switch, power good function, enable function and complete protection functions, and both output ceramic and SP/POS capacitor support. It supports supply and conversion voltages up to 6.0 V, and output voltages adjustable from 0.6 V to 2.0V. The TPS51317 is available in the 3.5 mm × 4 mm 20-pin QFN package (Green RoHs compliant and Pb free) and is specified from -40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. D-CAP+ is a trademark of Texas Instruments.

SLUSAH9-MARCH 2011

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### Table 1. ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERING NUMBER | PINS | OUTPUT SUPPLY | MINIMUM<br>QUANTITY | ECO PLAN        |

|----------------|------------------------|-----------------|------|---------------|---------------------|-----------------|

| -40°C to 85°C  | Plastic QFN            | TPS51317RGBR    | 20   | Tape and reel | 3000                | Green (RoHS and |

| -40 C 10 65 C  | (RGB)                  | TPS51317RGBT    | 20   | Mini reel     | 250                 | no Pb/Br)       |

(1) For the most current package and ordering information, see the *Package Option Addendum* at the end of this document, or visit the TI website at www.ti.com.

(2) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

### THERMAL INFORMATION

|                         |                                                             | TPS51317 |       |

|-------------------------|-------------------------------------------------------------|----------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                               | RGB      | UNITS |

|                         |                                                             | 20 PINS  |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 35.5     |       |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 39.6     |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance <sup>(4)</sup>         | 12.4     | °C/W  |

| ΨJT                     | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.5      | C/W   |

| ΨJB                     | Junction-to-board characterization parameter <sup>(6)</sup> | 12.5     |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 3.7      |       |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

### **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

over operating free-air temperature range (unless otherwise noted)

|                        |                                         | VALUE |      | UNIT |

|------------------------|-----------------------------------------|-------|------|------|

|                        |                                         | MIN   | MAX  |      |

|                        | VIN, V5IN, BST (with respect to SW)     | -0.3  | 7.0  |      |

| Input voltage range    | BST                                     | -0.3  | 14.0 |      |

|                        | SW                                      | -2    | 7    |      |

|                        | EN                                      | -0.3  | 7    | V    |

|                        | MODE, REFIN                             | -0.3  | 3.6  |      |

|                        | VOUT                                    | -1    | 3.6  |      |

|                        | COMP, VREF                              | -0.3  | 3.6  |      |

| Output voltage range   | PGOOD                                   | -0.3  | 7.0  | V    |

|                        | PGND                                    | -0.3  | 0.3  |      |

| Junction temperature   | TJ                                      | -40   | 150  |      |

| Storage temperature    | T <sub>stg</sub>                        | -55   | 150  | °C   |

| Lead temperature 1,6 n | nm (1/16 inch) from case for 10 seconds |       | 300  | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**

|                             |                   |      | ALUE    | UNIT |  |

|-----------------------------|-------------------|------|---------|------|--|

|                             |                   | MIN  | ΤΥΡ ΜΑΧ | UNIT |  |

|                             | VIN               | -0.1 | 6.5     |      |  |

| Input voltage range         | V5IN              | 4.5  | 6.5     |      |  |

|                             | BST               | -0.1 | 13.5    | v    |  |

|                             | SW                | -1.0 | 6.5     |      |  |

|                             | EN                | -0.7 | 6.5     |      |  |

|                             | VOUT, MODE, REFIN | -0.1 | 3.5     |      |  |

|                             | COMP, VREF        | -0.1 | 3.5     |      |  |

| Output voltage range        | PGOOD             | -0.1 | 5.5     | V    |  |

|                             | PGND              | -0.1 | 0.1     |      |  |

| Operating temperature range | , T <sub>A</sub>  | -40  | -40 85  |      |  |

# SLUSAH9-MARCH 2011

### **ELECTRICAL CHARACTERISTICS**

over recommended free-air temperature range,  $V_{V5IN}$  = 5.0 V, PGND = GND (unless otherwise noted)

|                        | PARAMETER                                           | CONDITIONS                                                                              | MIN   | TYP   | MAX   | UNIT |

|------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY: VO             | LTAGE, CURRENTS AND 5 V UVLO                        |                                                                                         |       |       |       |      |

| I <sub>VINSD</sub>     | VIN shutdown current                                | EN = 'LO'                                                                               |       | 0.02  | 5     | μA   |

| V <sub>5VIN</sub>      | 5VIN supply voltage                                 | V5IN voltage range                                                                      | 4.5   | 5.0   | 6.5   | V    |

| I <sub>5VIN</sub>      | 5VIN supply current                                 | EN ='HI', V5IN supply current                                                           |       | 1.1   | 2     | mA   |

| I <sub>5VINSD</sub>    | 5VIN shutdown current                               | EN = 'LO', V5IN shutdown current                                                        |       | 0.2   | 7.0   | μA   |

| V <sub>V5UVLO</sub>    | V5IN UVLO                                           | Ramp up; EN = 'HI'                                                                      | 4.20  | 4.37  | 4.50  | V    |

| V <sub>V5UVHYS</sub>   | V5IN UVLO hysteresis                                | Falling hysteresis                                                                      |       | 440   |       | mV   |

| V <sub>VREFUVLO</sub>  | REF UVLO <sup>(1)</sup>                             | Rising edge of VREF, EN = 'HI'                                                          |       | 1.8   |       | V    |

| V <sub>VREFUVHYS</sub> | REF UVLO hysteresis <sup>(1)</sup>                  |                                                                                         |       | 100   |       | mV   |

| V <sub>POR5VFILT</sub> | Reset                                               | OVP latch is reset by V5IN falling below the reset threshold                            | 1.5   | 2.3   | 3.1   | V    |

|                        | EDBACK LOOP: VREF, VOUT, AND V                      |                                                                                         |       |       | _     |      |

| V <sub>OUTTOL</sub>    | VOUT accuracy                                       | V <sub>REFIN</sub> = 1 V, No droop                                                      | -1%   | 0%    | 1%    |      |

|                        |                                                     | I <sub>VREF</sub> = 0 µA                                                                | 1.98  | 2.00  | 2.02  |      |

| V <sub>VREF</sub>      | VREF                                                | I <sub>VREF</sub> = 50 µA                                                               | 1.975 | 2.000 | 2.025 | V    |

| IREFSNK                | VREF sink current                                   | V <sub>VREF</sub> = 2.05 V                                                              |       | 2.5   |       | mA   |

| G <sub>M</sub>         | Transconductance                                    | VRF                                                                                     |       | 1.00  |       | mS   |

| V <sub>CM</sub>        | Common mode input voltage range <sup>(1)</sup>      |                                                                                         | 0     |       | 2     | V    |

| V <sub>DM</sub>        | Differential mode input voltage                     |                                                                                         | 0     |       | 80    | mV   |

|                        | COMP pin maximum sinking current                    | V <sub>COMP</sub> = 2 V, (V <sub>REFIN</sub> - V <sub>OUT</sub> ) = 80 mV               | -     | 80    |       | μA   |

|                        | COMP pin maximum sourcing current                   | $V_{\text{COMP}} = 2 \text{ V}$                                                         |       | -80   |       | μA   |

| V <sub>OFFSET</sub>    | Input offset voltage                                | $T_A = 25^{\circ}C$                                                                     |       | 0     |       | mV   |

| R <sub>DSCH</sub>      | Output voltage discharge resistance                 |                                                                                         |       | 42    |       | Ω    |

| f_3dbVL                | -3dB Frequency <sup>(1)</sup>                       |                                                                                         | 4.5   | 6.0   | 7.5   | MHz  |

|                        |                                                     |                                                                                         |       |       |       |      |

| A <sub>CSINT</sub>     | Internal current sense gain                         | Gain from the current of the low-side FET to PWM comparator when PWM = "OFF"            | 43    | 53    | 57    | mV/A |

| I <sub>OCL</sub>       | Positive overcurrent limit (valley)                 |                                                                                         |       | 7.6   |       | А    |

| I <sub>OCL(neg)</sub>  | Negative overcurrent limit (valley)                 |                                                                                         |       | -9.3  |       | А    |

| V <sub>ZXOFF</sub>     | Zero crossing comp internal offset                  |                                                                                         |       | 0     |       | mV   |

|                        | DOT STRAP SWITCH                                    |                                                                                         |       |       |       |      |

| R <sub>DSONBST</sub>   | Internal BST switch on-resistance                   | $I_{BST} = 10 \text{ mA}, T_A = 25^{\circ}\text{C}$                                     |       |       | 10    | Ω    |

| IBSTLK                 | Internal BST switch leakage current                 | V <sub>BST</sub> = 14 V, V <sub>SW</sub> = 7 V                                          |       |       | 1     | μA   |

|                        | N: OVP, UVP, PGOOD, and THERMAL S                   | SHUTDOWN                                                                                |       |       |       |      |

| V <sub>PGDLL</sub>     | PGOOD deassert to lower (PGOOD $\rightarrow$ Low)   | Measured at the VOUT pin wrt/ V <sub>REFIN</sub>                                        |       | 84%   |       |      |

| V <sub>PGHYSHL</sub>   | PGOOD high hysteresis                               |                                                                                         |       | 8%    |       |      |

| V <sub>PGDLH</sub>     | PGOOD de-assert to higher (PGOOD $\rightarrow$ Low) | Measured at the VOUT pin wrt/ V <sub>REFIN</sub>                                        |       | 116%  |       |      |

| V <sub>PGHYSHH</sub>   | PGOOD high hysteresis                               |                                                                                         |       | -8%   |       |      |

| VINMINPG               | Minimum VIN voltage for valid<br>PGOOD              | Measured at the VIN pin with a 2-mA sink current on PGOOD pin                           | 0.9   | 1.3   | 1.5   | V    |

| V <sub>OVP</sub>       | OVP threshold                                       | Measured at the VOUT pin wrt/ V <sub>REFIN</sub>                                        | 117%  | 120%  | 123%  |      |

| V <sub>UVP</sub>       | UVP threshold                                       | Measured at the VOUT pin wrt/ V <sub>REFIN</sub> , device latches OFF, begins soft-stop | 65%   | 68%   | 71%   |      |

| TH <sub>SD</sub>       | Thermal shutdown <sup>(1)</sup>                     | Latch off controller, attempt soft-stop.                                                |       | 145   |       | °C   |

| TH <sub>SD(hys)</sub>  | Thermal Shutdown hysteresis <sup>(1)</sup>          | Controller re-starts after temperature has dropped                                      |       | 10    |       | °C   |

(1) Ensured by design, not production tested.

SLUSAH9-MARCH 2011

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

over recommended free-air temperature range,  $V_{V5IN}$  = 5.0 V, PGND = GND (unless otherwise noted)

|                         | PARAMETER                             | CONDITIONS                                                                                           | MIN  | TYP  | MAX  | UNIT |  |

|-------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| TIMERS: ON              | I-TIME, MINIMUM OFF-TIME, SS, AND I/  | O TIMINGS                                                                                            |      |      | 1    |      |  |

|                         |                                       | V <sub>VIN</sub> = 5 V, V <sub>VOUT</sub> = 1.05 V, f <sub>SW</sub> = 860 KHz                        |      | 240  |      |      |  |

|                         |                                       | V <sub>VIN</sub> = 5 V, V <sub>VOUT</sub> = 1.05 V, f <sub>SW</sub> = 1 MHz                          |      | 210  |      |      |  |

| t <sub>ONESHOTC</sub>   | PWM one-shot <sup>(2)</sup>           | V <sub>VIN</sub> = 5 V, V <sub>VOUT</sub> = 1.05 V, f <sub>SW</sub> = 1.2 MHz                        |      | 175  |      | ns   |  |

|                         |                                       | V <sub>VIN</sub> = 5 V, V <sub>VOUT</sub> = 1.05 V, f <sub>SW</sub> = 1.5 MHz                        |      |      |      |      |  |

| t <sub>MIN(off)</sub>   | Minimum OFF time                      | $V_{VIN}$ = 5 V, $V_{VOUT}$ = 1.05 V, $f_{SW}$ = 1 MHz, DRVL on, SW = PGND, $V_{VOUT}$ < $V_{REFIN}$ |      | 360  |      | ns   |  |

| t <sub>INT(SS)</sub>    | Soft-start time                       | From EN = HI to VOUT =95%, default setting                                                           |      | 1.6  |      | ms   |  |

| t <sub>INT(SSDLY)</sub> | Internal soft-start delay time        | From EN = HI to VOUT ramp starts                                                                     |      | 260  |      | μs   |  |

| t <sub>PGDDLY</sub>     | PGOOD startup delay time              | External tracking                                                                                    |      | 8    |      | ms   |  |

| t <sub>PGDPDLYH</sub>   | PGOOD high propagation delay time     | 50 mV over drive, rising edge                                                                        | 0.8  | 1    | 1.2  | ms   |  |

| t <sub>PGDPDLYL</sub>   | PGOOD low propagation delay time      | 50 mV over drive, falling edge                                                                       |      | 10   |      | μs   |  |

| tOVPDLY                 | OVP delay time                        | Time from the VOUT pin out of +20% of REFIN to OVP fault                                             |      | 10   |      | μs   |  |

|                         | Lindomialtara fault anable delay      | Time from EN_INT going high to undervoltage fault is ready                                           |      |      |      |      |  |

| t <sub>UVDLYEN</sub>    | Undervoltage fault enable delay       | External tracking from VOUT ramp starts                                                              |      | 8    |      | ms   |  |

| t <sub>UVPDLY</sub>     | UVP delay time                        | Time from the VOUT pin out of -30% of REFIN to UVP fault                                             |      | 256  |      | μs   |  |

| LOGIC PINS              | : I/O VOLTAGE AND CURRENT             |                                                                                                      |      |      |      |      |  |

| V <sub>PGDPD</sub>      | PGOOD pull-down voltage               | PGOOD low impedance, $I_{SINK} = 4$ mA, $V_{VSIN} = 4.5$ V                                           |      |      | 0.3  | V    |  |

| IPGDLKG                 | PGOOD leakage current                 | PGOOD high impedance, forced to 5.5 V                                                                | -1   | 0    | 1    | μA   |  |

| V <sub>ENH</sub>        | EN logic high                         | EN, VCCP logic                                                                                       | 2    |      |      | V    |  |

| V <sub>ENL</sub>        | EN logic low                          | EN, VCCP logic                                                                                       |      |      | 0.5  | V    |  |

| I <sub>EN</sub>         | EN input current                      |                                                                                                      |      |      | 1    | μA   |  |

|                         |                                       | Threshold 1                                                                                          | 80   | 130  | 180  |      |  |

|                         |                                       | Threshold 2                                                                                          | 200  | 250  | 300  |      |  |

| V <sub>MODETH</sub>     | MODE threshold voltage <sup>(3)</sup> | Threshold 3                                                                                          | 370  | 420  | 470  |      |  |

|                         |                                       | Threshold 4                                                                                          | 1.77 | 1.80 | 1.85 | V    |  |

| IMODE                   | MODE current                          |                                                                                                      |      | 15   |      | μA   |  |

(2)

Ensured by design, not production tested. See Table 4 for descriptions of MODE parameters. (3)

SLUSAH9-MARCH 2011

www.ti.com

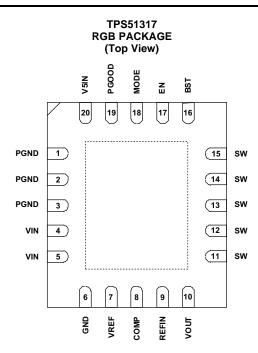

### Table 2. PIN FUNCTIONS

| I   | PIN      |     |                                                                                                                                 |  |  |  |  |  |  |

|-----|----------|-----|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NO. | NAME     | I/O | DESCRIPTION                                                                                                                     |  |  |  |  |  |  |

| 16  | BST      | I   | Power supply for internal high-side gate driver. Connect a $0.1$ - $\mu$ F bootstrap capacitor between this pin and the SW pin. |  |  |  |  |  |  |

| 8   | COMP     | 0   | Connect series R-C filter between this pin and VREF for loop compensation.                                                      |  |  |  |  |  |  |

| 17  | EN       | I   | Enable of the SMPS (3.3-V logic compatible).                                                                                    |  |  |  |  |  |  |

| 6   | GND      | _   | Signal ground.                                                                                                                  |  |  |  |  |  |  |

| 18  | MODE     | I   | Allows selection of switching frequencies light-load modes. (See Table 4)                                                       |  |  |  |  |  |  |

| 1   |          |     |                                                                                                                                 |  |  |  |  |  |  |

| 2   | 2 PGND I | I   | Power ground. Source terminal of the rectifying low-side power FET. Positive input for current sensing.                         |  |  |  |  |  |  |

| 3   |          |     |                                                                                                                                 |  |  |  |  |  |  |

| 19  | PGOOD    | 0   | Power good output. Connect pull-up resistor.                                                                                    |  |  |  |  |  |  |

| 9   | REFIN    |     | Target output voltageinput pin. Apply voltage between 0.6 V to 2.0 V.                                                           |  |  |  |  |  |  |

| 11  |          |     |                                                                                                                                 |  |  |  |  |  |  |

| 12  |          |     |                                                                                                                                 |  |  |  |  |  |  |

| 13  | SW       | I/O | Switching node output. Connect to the external inductor. Also serve as current-sensing negative input.                          |  |  |  |  |  |  |

| 14  |          |     |                                                                                                                                 |  |  |  |  |  |  |

| 15  |          |     |                                                                                                                                 |  |  |  |  |  |  |

| 20  | V5IN     | I   | 5-V power supply for analog circuits and gate drive.                                                                            |  |  |  |  |  |  |

| 4   | VIN      |     | Power supply input pin. Drain terminal of the switching high-side power FET.                                                    |  |  |  |  |  |  |

| 5   | VIIN     | I   | Fower suppry input pin. Drain terminal of the switching high-side power FET.                                                    |  |  |  |  |  |  |

| 10  | VOUT     | I   | Output voltage monitor input pin.                                                                                               |  |  |  |  |  |  |

| 7   | VREF     | 0   | 2.0-V reference output. Connect a 0.22-µF ceramic capacitor to GND.                                                             |  |  |  |  |  |  |

www.ti.com

SLUSAH9-MARCH 2011

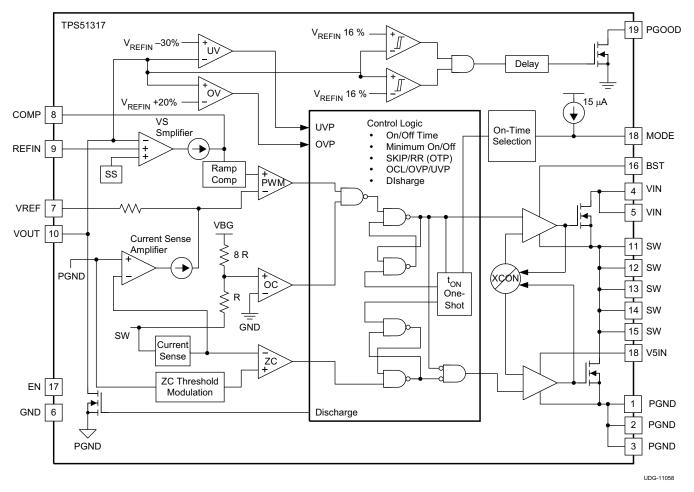

### **BLOCK DIAGRAM**

SLUSAH9-MARCH 2011

TEXAS INSTRUMENTS

www.ti.com

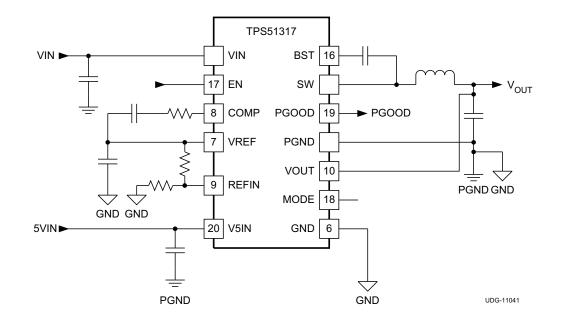

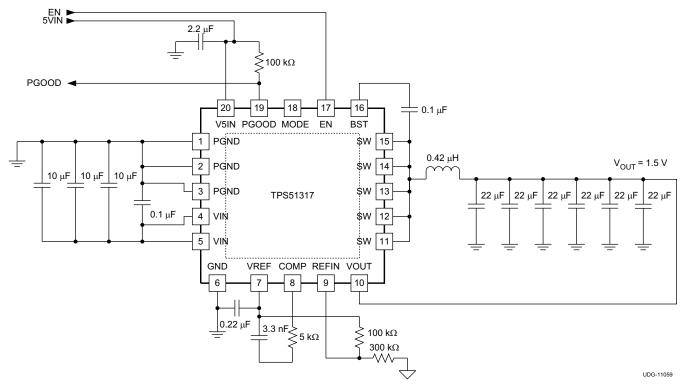

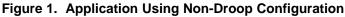

### **APPLICATION SCHEMATIC WITH TPS51317**

UDG-11060

### **Application Circuit List of Materials**

Recommended parts for key external components for the circuits in Figure 1 and Figure 2 are listed in Table 3.

# Table 3. Key External Component Recommendations (Figure 1 and Figure 2)

| FUNCTION                   | MANUFACTURER | PART NUMBER        |  |  |

|----------------------------|--------------|--------------------|--|--|

| Output Inductor            | Nec-Tokin    | MPCG0740LR42C      |  |  |

| Coromia Output Consolitors | Panasonic    | ECJ2FB0J226M       |  |  |

| Ceramic Output Capacitors  | Murata       | GRM21BR60J226ME39L |  |  |

SLUSAH9-MARCH 2011

www.ti.com

### **APPLICATION INFORMATION**

### **Functional Overview**

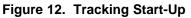

The TPS51317 is a D-CAP+<sup>™</sup> mode adaptive on-time converter. Integrated high-side and low-side FET supports output current to a maximum of 6-ADC. The converter automatically runs in discontinuous conduction mode (DCM) to optimize light-load efficiency. Multiple switching frequencies are provided to enable optimization of the power chain for the cost, size and efficiency requirements of the design (see Table 4).

In adaptive on-time converters, the controller varies the on-time as a function of input and output voltage to maintain a nearly constant frequency during steady-state conditions. In conventional constant on-time converters, each cycle begins when the output voltage crosses to a fixed reference level. However, in the TPS51317, the cycle begins when the current feedback reaches an error voltage level which is the amplified difference between the reference voltage and the feedback voltage.

### **PWM Operation**

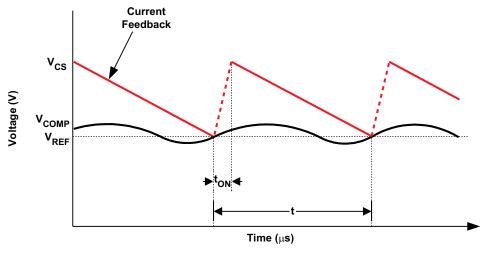

Referring to Figure 3, in steady state, continuous conduction mode, the converter operates in the following way.

Starting with the condition that the top FET is off and the bottom FET is on, the current feedback ( $V_{CS}$ ) is higher than the error amplifier output ( $V_{COMP}$ ).  $V_{CS}$  falls until it hits  $V_{COMP}$ , which contains a component of the output ripple voltage.  $V_{CS}$  is not directly accessible by measuring signals on pins of TPS51317. The PWM comparator senses where the two waveforms cross and triggers the on-time generator.

UDG-10187

Figure 3. D-CAP+<sup>™</sup> Mode Basic Waveforms

The current feedback is an amplified and filtered version of the voltage between PGND and SW during low-side FET on-time. The TPS51317 also provides a single-ended differential voltage ( $V_{OUT}$ ) feedback to increase the system accuracy and reduce the dependence of circuit performance on layout.

### **PWM Frequency and Adaptive on Time Control**

In general, the on-time (at the SW node) can be estimated by Equation 1.

$$t_{ON} = \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}}$$

where

f<sub>sw</sub> is the frequency selected by the connection of the MODE pin

(1)

The on-time pulse is sent to the top FET. The inductor current and the current feedback rises to peak value. Each ON pulse is latched to prevent double pulsing. Switching frequency settings are shown in .

### **Non-Droop Configuration**

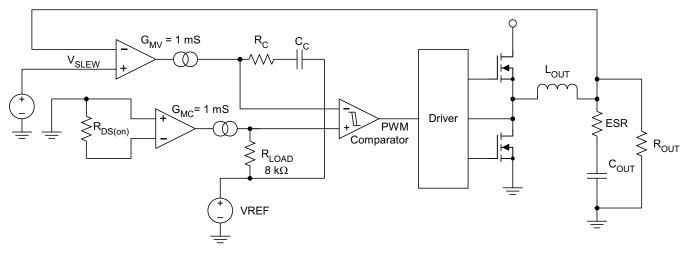

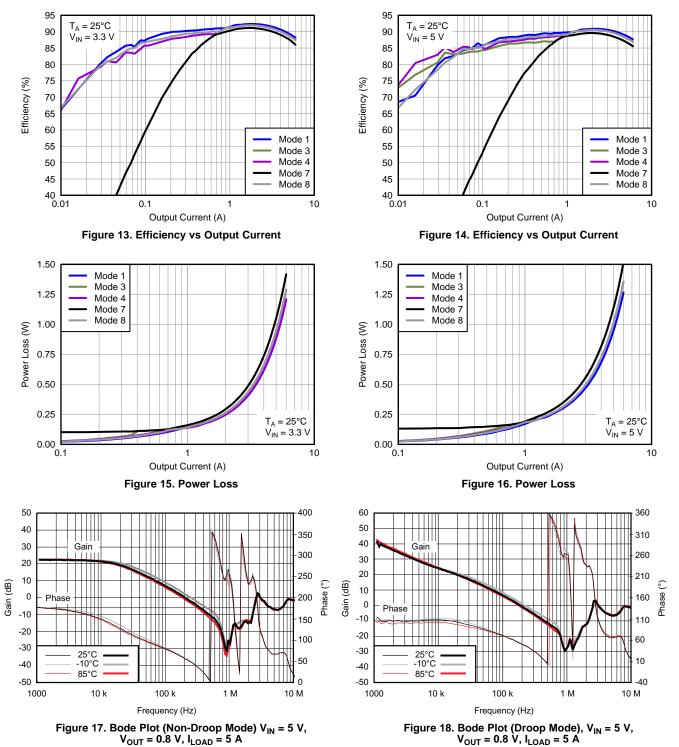

The TPS51317 can be configured as a non-droop solution. The benefit of a non-droop approach is that load regulation is flat, therefore, in a system where tight DC tolerance is desired, the non-droop approach is recommended. For the Intel system agent application, non-droop is recommended as the standard configuration.

The non-droop approach can be implemented by connecting a resistor and a capacitor between the COMP and the VREF pins. The purpose of the type II compensation is to obtain high DC feedback gain while minimizing the phase delay at unity gain cross over frequency of the converter.

The value of the resistor ( $R_c$ ) can be calculated using the desired unity gain bandwidth of the converter, and the value of the capacitor ( $C_c$ ) can be calculated by knowing where the zero location is desired. An application tool that calculates these values is available from your local TI Field Application Engineer.

Figure 4 shows the basic implementation of the non-droop mode using the TPS51317.

UDG-10190

Figure 4. Non-Droop Mode Basic Implementation

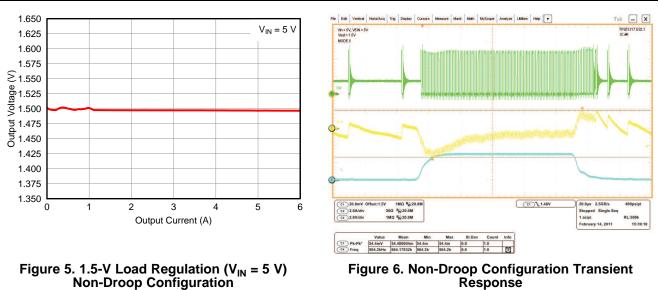

Figure 5 shows shows the load regulation using non-droop configuration.

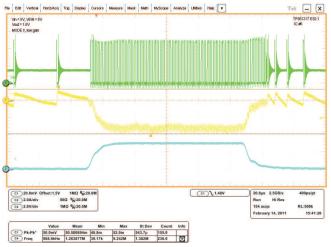

Figure 6 shows the transient response of TPS51317 using non-droop configuration, where  $C_{OUT} = 6 \times 22 \mu$ F. The applied step load is from 0 A to 3 A.

Texas Instruments

www.ti.com

(2)

### SLUSAH9-MARCH 2011

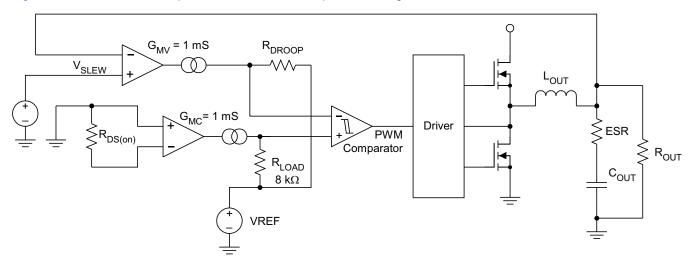

The terminology for droop is the same as *load line* or *voltage positioning* as defined in the Intel CPU  $V_{CORE}$  specification. Based on the actual tolerance requirement of the application, load-line set points can be defined to maximize either cost savings (by reducing output capacitors) or power reduction benefits.

Accurate droop voltage response is provided by the finite gain of the droop amplifier. The equation for droop voltage is shown in Equation 2.

$$V_{DROOP} = \frac{A_{CSINT} \times I(L)}{R_{DROOP} \times G_{M}}$$

where

- low-side on-resistence is used as the current sensing element

- $A_{CSINT}$  is a constant, which nominally is 53 mV/A.

- I(L) is the DC current of the inductor, or the load current

- R<sub>DROOP</sub> is the value of resistor from the COMP pin to the VREF pin

- G<sub>M</sub> is the transconductance of the droop amplifier with nominal value of 1 mS

Equation 3 can be used to easily derive R<sub>DROOP</sub> for any load line slope/droop design target.

$$R_{LOAD\_LINE} = \frac{V_{DROOP}}{I(L)} = \frac{A_{CSINT}}{R_{DROOP} \times G_{M}} \therefore R_{DROOP} = \frac{A_{CSINT}}{R_{LOAD\_LINE} \times G_{M}}$$

(3)

SLUSAH9-MARCH 2011

Figure 7 shows the basic implementation of the droop mode using the TPS51317.

UDG-10188

Figure 7. DROOP Mode Basic Implementation

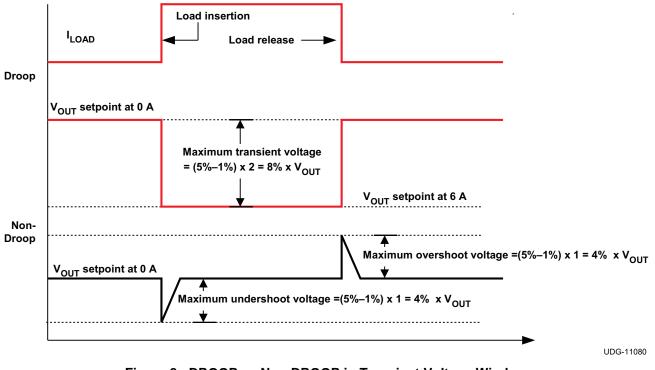

The droop (voltage positioning) method was originally recommended to reduce the number of external output capacitors required. The effective transient voltage range is increased because of the active voltage positioning (see Figure 8).

Figure 8. DROOP vs Non-DROOP in Transient Voltage Window

In applications where the DC and the AC tolerances are not separated, which means there is not a strict DC tolerance requirement, the droop method can be used.

### SLUSAH9-MARCH 2011

| MODE | MODE RESISTANCE<br>(kΩ) | LIGHT-LOAD POWER<br>SAVING MODE | SWITCHING<br>FREQUENCY<br>(f <sub>SW</sub> ) (MHz) |  |  |

|------|-------------------------|---------------------------------|----------------------------------------------------|--|--|

| 1    | 0                       | SKIP                            | 0.86                                               |  |  |

| 2    | 12                      | SKIP                            | 1.2                                                |  |  |

| 3    | 22                      | SKIP                            | 1.5                                                |  |  |

| 4    | 33                      | RR <sup>(1)</sup>               | 1.0                                                |  |  |

| 5    | 47                      | RR <sup>(1)</sup>               | 0.86                                               |  |  |

| 6    | 68                      | PWM                             | 1.2                                                |  |  |

| 7    | 100                     | PWM                             | 1.5                                                |  |  |

| 8    | OPEN                    | SKIP                            | 1.0                                                |  |  |

### **Table 4. Mode Definitions**

(1) Ripple reduction is a special light-load power saving feature. See (Light-Load Power Saving Features)

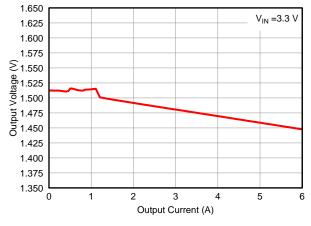

Figure 9 shows the load regulation of the 1.5-V rail using an  $R_{DROOP}$  value of 5 k $\Omega$ .

Figure 10 shows the transient response of the TPS51317 using droop configuration and  $C_{OUT} = 6 \times 22 \ \mu\text{F}$ . The applied step load is from 0 A to 3 A.

Figure 9. 1.5-V Load Regulation ( $V_{IN} = 5 V$ )

Figure 10. Droop Configuration Transient Response,  $C_{OUT} = 6 \times 22 \ \mu$ F and 0 A to 3 A

The TPS51317 has an automatic pulse-skipping mode to provide excellent efficiency over a wide load range. The converter senses inductor current and prevents negative flow by shutting off the low-side gate driver. This saves power by eliminating re-circulation of the inductor current. Further, when the bottom FET shuts off, the converter enters discontinuous mode, and the switching frequency decreases, thus reducing switching losses as well.

TPS51317 also provides a special light-load power saving feature, called ripple reduction. Essentially, it reduces the on-time in SKIP mode to effectively reduce the output voltage ripple associated with using an all MLCC capacitor output power stage design.

### **Power Sequences**

### Non-Tracking Startup

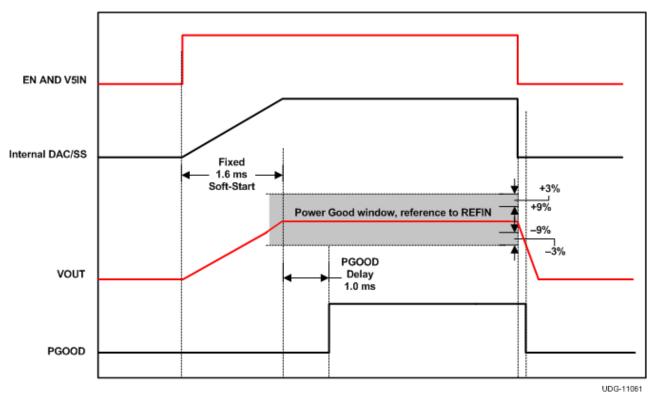

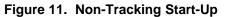

The TPS51317 can be configured for non-tracking application. When non-tracking is configured, output voltage is regulated to the REFIN voltage which taps off the voltage dividers from the 2VREF. Either the EN pin or the V5IN pin can be used to start up the device. The TPS51317 uses internal voltage servo DAC to provide a precise 1.6-ms soft-start time during soft-start initialization. (See Figure 11)

### Tracking Startup

TPS51317 can also be configured for tracking application. When tracking configuration is desired, output voltage is also regulated to the REFIN voltage which comes from external power source. In order for TPS51317 to differentiate between a non-tracking configuration or a tracking configuration, there is a minimum delay time of 260  $\mu$ s required between the time when the EN pin or the 5VIN pin is validated to the time when the REFIN pin voltage can be applied, in order for the TPS51317 to track properly (see Figure 12). The valid REFIN voltage range is between 0.6 V to 2 V.

### **Protection Features**

The TPS51317 offers many features to protect the converter power chain as well as the system electronics.

### 5-V Undervoltage Protection (UVLO)

The TPS51317 continuously monitors the voltage on the V5IN pin to ensure that the voltage level is high enough to bias the device properly and to provide sufficient gate drive potential to maintain high efficiency. The converter starts with approximately 4.3 V and has a nominal of 440 mV of hysteresis. If the 5-V UVLO limit is reached, the converter transitions the phase node into a off function. And the converter remains in the off state until the device is reset by cycling 5 V until the 5-V POR is reached (2.3-V nominal). The power input does not have an UVLO function

### Power Good Signals

The TPS51317 has one open-drain *power good* (PGOOD) pin. During startup, there is a 1-ms power good high propagation delay. The PGOOD pin de-asserts as soon as the EN pin is pulled low or an undervoltage condition on V5IN or any other faults that require latch off action is detected.

### Output Overvoltage Protection (OVP)

In addition to the power good function described above, the TPS51317 has additional OVP and UVP thresholds and protection circuits.

An OVP condition is detected when the output voltage is approximately 120% ×  $V_{REFIN}$ . In this case, the converter de-asserts the PGOOD signals and performs the overvoltage protection function. The converter remains in this state until the device is reset by cycling 5 V until the 5-V POR threshold (2.3 V nominal) is reached.

### Output Undervoltage Protection (UVP)

Output undervoltage protection works in conjunction with the current protection described in the Overcurrent Protection and Overcurrent Limit sections. If the output voltage drops below 70% of V<sub>REFIN</sub>, after an 8-µs delay, the device latches OFF. Undervoltage protection can be reset only by EN or a 5-V POR.

### SLUSAH9-MARCH 2011

### **Overcurrent Protection**

Both positive and negative overcurrent protection are provided in the TPS51317:

- Overcurrent Limit (OCL)

- Negative OCL (level same as positive OCL)

# **Overcurrent Limit**

If the sensed current value is above the OCL setting, the converter delays the next ON pulse until the current drops below the OCL limit. Current limiting occurs on a pulse-by-pulse basis. The TPS51317 uses a valley current limiting scheme where the DC OCL trip point is the OCL limit plus half of the inductor ripple current. The minimum valley OCL is 6 A over process and temperature.

During the overcurrent protection event, the output voltage likely droops until the UVP limit is reached. Then, the converter de-asserts the PGOOD pin, and then latches OFF after an 8-µs delay. The converter remains in this state until the device is reset.

$$I_{OCL(dc)} = I_{OCL(valley)} + \frac{1}{2} \times I_{P-P}$$

### Negative OCL

The negative OCL circuit acts when the converter is sinking current from the output capacitor(s). The converter continues to act in a *valley* mode, the absolute value of the negative OCL set point is typically -6.5 A.

### **Thermal Protection**

### Thermal Shutdown

The TPS51317 has an internal temperature sensor. When the temperature reaches a nominal 145°C, the device shuts down until the temperature cools by approximately 10°C. Then the converter restarts.

(4)

SLUSAH9-MARCH 2011

### **Startup Timing Diagrams**

### SLUSAH9-MARCH 2011

**TYPICAL CHARACTERISTICS**

www.ti.com

- 1. V<sub>OUT</sub> = 1.5 V

- 2.  $I_{CC(max)} = 6 A$

- 3.  $I_{DYN(max)} = 3 A$

- 4.  $I_{CC(tdc)} = 3 A$

## Step Two

Determine system parameters.

The input voltage range and operating frequency are of primary interest. For example:

- 1.  $V_{IN} = 5 V$

- 2.  $f_{SW} = 1 \text{ MHz}$

### Step Three

Determine inductor value and choose inductor.

Smaller values of inductor have better transient performance but higher ripple and lower efficiency. Higher values have the opposite characteristics. It is common practice to limit the ripple current to 25% to 50% of the maximum current. In this case, use 40%:

DESIGN PROCEDURE

The simplified design procedure is done for a non-droop application using the TPS51317 converter.

$$I_{P-P} = 6A \times 0.4 = 2.4A \tag{5}$$

At  $f_{SW} = 1$  MHz, with a 5-V input and a 1.5-V output:

$$L = \frac{V \times dT}{I_{P-P}} = \frac{(V_{IN} - V_{OUT}) \times \left(\frac{V_{OUT}}{(f_{SW} \times V_{IN})}\right)}{I_{P-P}} = \frac{(5 - 1.5) \times \left(\frac{1.5}{(1 \times 5)}\right)}{1.5 A} = 0.43 \,\mu \text{H}$$

(6)

For this application, a 0.42- $\mu$ H, 1.55-m $\Omega$  inductor from NEC-TOKIN with part number MPCG0740LR42C is chosen.

### **Step Four**

Set the output voltage.

$$V_{OUT} = \frac{V_{VREF}}{R_{UPPER} + R_{LOWER}} \times R_{LOWER}$$

The output voltage is determined by the 2-V reference (VREF) and the resistor dividers ( $R_{UPPER}$  and  $R_{LOWER}$ ). The output voltage is regulated to the REFIN pin. Because the 2-V reference current capability is limited to less than 50  $\mu$ A, care should be taken when selecting the resistor dividers. For the current reference design of 1.5 V (see application schematics shown in Figure 1 and Figure 2,  $R_{UPPER} = 100 \text{ k}\Omega$ ,  $R_{LOWER} = 300 \text{ k}\Omega$ .

### **Step Five**

Calculate OCL.

The DC OCL level of TPS51317 design is determined by Equation 8,

$$I_{OCL(dc)} = I_{OCL(valley)} + \frac{1}{2} \times I_{P-P} = 6A + \frac{1}{2} \times 1.5A = 6.75A$$

Copyright © 2011, Texas Instruments Incorporated

TPS51317

19

Submit Documentation Feedback

www.ti.com

Step One

Step Six

#### SLUSAH9-MARCH 2011

calculated to be 6.75A.

Determine the output capacitance.

capacitance for a given transient.

(10)

(11)

To determine COUT based on transient and stability requirement, first calculate the the minimum output

Equation 10 and Equation 9 can be used to estimate the amount of capacitance needed for a given dynamic load step/release. Please note that there are other factors that may impact the amount of output capacitance for a specific design, such as ripple and stability. Equation 10 and Equation 9 are used only to estimate the transient requirement, the result should be used in conjunction with other factors of the design to determine the necessary output capacitance for the application.

The minimum valley OCL is 6 A over process and temperature, and  $I_{P-P} = 1.5$  A, the minimum DC OCL is

$$C_{OUT(min\_under)} = \frac{L \times \Delta I_{LOAD(max)}^{2} \times \left(\frac{V_{VOUT} \times t_{SW}}{V_{IN(min)}} + t_{MIN(off)}\right)}{2 \times \Delta V_{LOAD(insert)} \times \left(\left(\frac{V_{IN(min)} - V_{VOUT}}{V_{IN(min)}}\right) \times t_{SW} - t_{MIN(off)}\right) \times V_{VOUT}}$$

$$C_{OUT(min\_over)} = \frac{L_{OUT} \times \left(\Delta I_{LOAD(max)}\right)^{2}}{2 \times \Delta V_{LOAD(release)} \times V_{VOUT}}$$

(10)

Equation 9 and Equation 10 calculate the minimum

$$C_{OUT}$$

for meeting the transient requirement, which is 84  $\mu$ F assuming the following:

- ±3% voltage allowance for load step and release

- MLCC capacitance derating of 60% due to DC and AC bias effect

In this reference design, 6, 22-µF capacitors are used in order to provide this amount of capacitance.

### Step Seven

Determine the stability based on the output capacitance C<sub>OUT</sub>.

In order to achieve stable operation. The 0-dB frequency, f<sub>0</sub> should be kept less than 1/5 of the switching frequency (1 MHz). (See Figure 4)

$$f_0 = \frac{1}{2\pi} \times \frac{G_M}{C_{OUT}} \times \frac{R_C}{R_S} = 190 \, \text{kHz}$$

where

•

$$R_S = R_{DS(on)} \times G_{MC} \times R_{LOAD}$$

$$R_{C} = \frac{f_{0} \times R_{S} \times 2\pi \times C_{OUT}}{G_{M}} = \frac{190 \,\text{kHz} \times 53 \text{m}\Omega \times 2\pi \times 80 \,\mu\text{F}}{1\text{mS}} \approx 5 \,\text{k}\Omega \tag{12}$$

Using 6, 22- $\mu$ F capacitors, the compensation resistance, R<sub>c</sub> can be calculated to be approximately 5 k $\Omega$ .

The purpose of the comparator capacitor ( $C_C$ ) is to reduce the DC component to obtain high DC feedback gain. However, as it causes phase delay, another zero to cancel this effect at fo is needed. This zero can be determined by values of  $C_C$  and the compensation resistor,  $R_C$ .

$$f_Z = \frac{1}{2\pi \times R_C \times C_C} = \frac{f_0}{10}$$

(13)

And since R<sub>c</sub> has previously been derived, the value of C<sub>c</sub> is calculated to be 2.2 nF. In order to further boost phase margin, a value of 3.3-nF is chosen for this reference design.

www.ti.com

### Step Eight

Select decoupling and peripheral components.

For TPS51317 peripheral capacitors use the following minimum values of ceramic capacitance. X5R or better temperature coefficient is recommended. Tighter tolerances and higher voltage ratings are always appropriate.

- V5IN decoupling  $\geq$  22 µF,  $\geq$  10 V

- VREF decoupling 0.22  $\mu$ F to 1  $\mu$ F,  $\geq$  4 V

- Bootstrap capacitors ≥ 0.1 µF, ≥ 10 V

- Pull-up resistors on PGOOD, 100 kΩ

### **Layout Considerations**

Good layout is essential for stable power supply operation. Follow these guidelines for an efficient PCB layout.

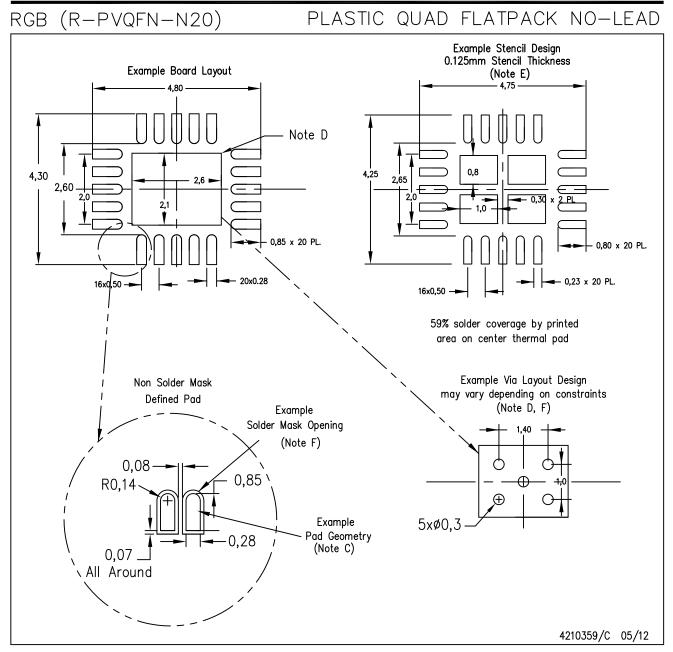

- Connect PGND pins (or at least one of the pins) to the thermal PAD underneath the device. Also connect GND pin to the thermal PAD underneath the device. Use four vias to connect the thermal pad to internal ground planes.

- Place VIN, V5IN and 2VREF decoupling capacitors as close to the device as possible.

- Use wide traces for the VIN, VOUT, PGND and SW pins. These nodes carry high current and also serve as heat sinks.

- Place feedback and compensation components as close to the device as possible.

- Keep COMP analog signal away from noisy signals (SW, BST).

11-Apr-2013

### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        |                  | (3)                 |              | (4)               |         |

| TPS51317RGBR     | ACTIVE | VQFN         | RGB     | 20   | 3000    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 51317             | Samples |

| TPS51317RGBT     | ACTIVE | VQFN         | RGB     | 20   | 250     | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 51317             | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

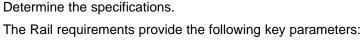

### TAPE AND REEL INFORMATION

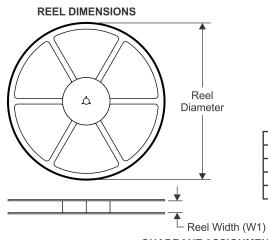

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal<br>Device | 1    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------------------------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS51317RGBR                          | VQFN | RGB                | 20 | 3000 | 330.0                    | 12.4                     | 3.8        | 4.3        | 1.5        | 8.0        | 12.0      | Q1               |

| TPS51317RGBR                          | VQFN | RGB                | 20 | 3000 | 330.0                    | 12.4                     | 3.8        | 4.3        | 1.5        | 8.0        | 12.0      | Q1               |

| TPS51317RGBT                          | VQFN | RGB                | 20 | 250  | 180.0                    | 12.4                     | 3.8        | 4.3        | 1.5        | 8.0        | 12.0      | Q1               |

| TPS51317RGBT                          | VQFN | RGB                | 20 | 250  | 180.0                    | 12.4                     | 3.8        | 4.3        | 1.5        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

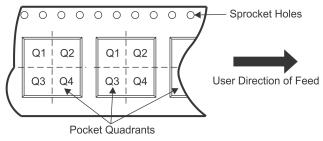

# PACKAGE MATERIALS INFORMATION

26-Jan-2013

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS51317RGBR | VQFN         | RGB             | 20   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS51317RGBR | VQFN         | RGB             | 20   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS51317RGBT | VQFN         | RGB             | 20   | 250  | 210.0       | 185.0      | 35.0        |

| TPS51317RGBT | VQFN         | RGB             | 20   | 250  | 210.0       | 185.0      | 35.0        |

# **MECHANICAL DATA**

$\stackrel{\text{l. See the deditional light in the robust but sheet of details regularing the exposed thermal put robust and an <math display="inline">\stackrel{\text{l. See the deditional light in the robust but of the package and within the zone indicated.}$

The Pin 1 identifiers are either a molded, marked, or metal feature.

# RGB (R-PVQFN-N20)

## PLASTIC QUAD FLATPACK NO-LEAD

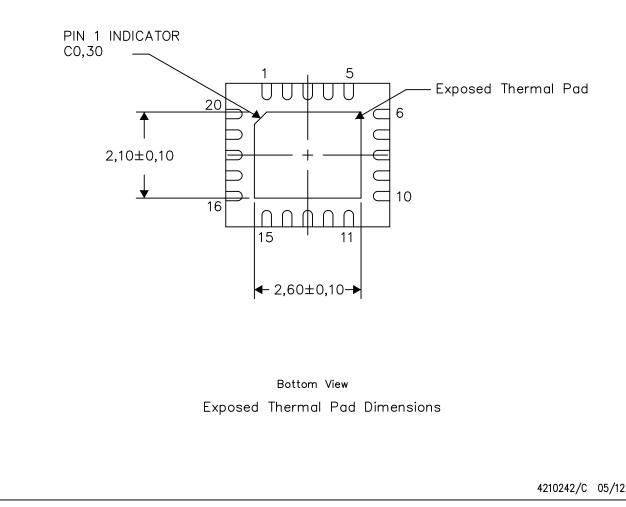

### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

#### NOTE: All linear dimensions are in millimeters

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat-Pack QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated