SLUS772E - MARCH 2008 - REVISED OCTOBER 2011

# 4.5-V TO 52-V INPUT CURRENT MODE BOOST CONTROLLER

Check for Samples: TPS40210, TPS40211

# **FEATURES**

- For Boost, Flyback, SEPIC, LED Drive Apps

- Wide Input Operating Voltage: 4.5 V to 52 V

- Adjustable Oscillator Frequency

- Fixed Frequency Current Mode Control

- Internal Slope Compensation

- Integrated Low-Side Driver

- Programmable Closed Loop Soft Start

- Overcurrent Protection

- External Synchronization Capable

- Reference700-mV (TPS40210), 260-mV (TPS40211)

- Low Current Disable Function

# **APPLICATIONS**

- LED Lighting

- Industrial Control Systems

- Battery Powered Systems

# CONTENTS

| Device Ratings             | 2  |

|----------------------------|----|

| Electrical Characteristics | 3  |

| Typical Characteristics    | 5  |

| Terminal Information       | 10 |

| Application Information    | 12 |

| Additional References      | 25 |

| Design Examples            | 26 |

|                            |    |

# DESCRIPTION

The TPS40210 and TPS40211 are wide-input voltage (4.5 V to 52 V), non-synchronous boost controllers. They are suitable for topologies which require a grounded source N-channel FET including boost, flyback, SEPIC and various LED Driver applications. The device features include programmable soft start, overcurrent protection with automatic retry and programmable oscillator frequency. Current mode control provides improved transient response and simplified loop compensation. The main difference between the two parts is the reference voltage to which the error amplifier regulates the FB pin.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

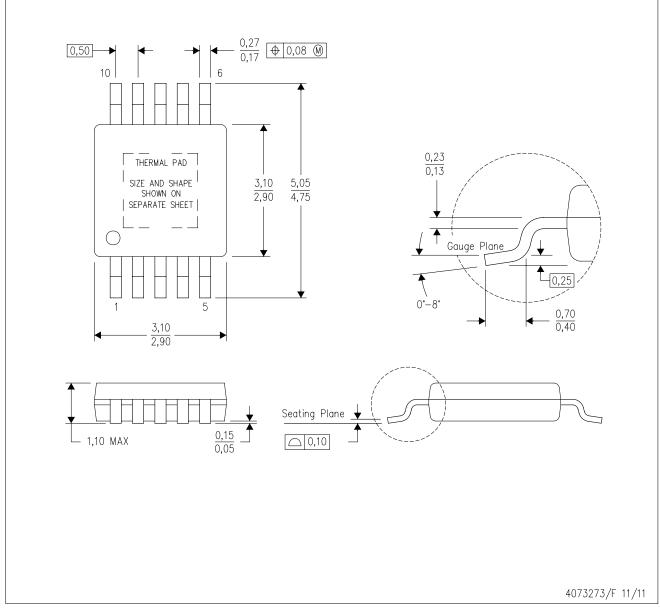

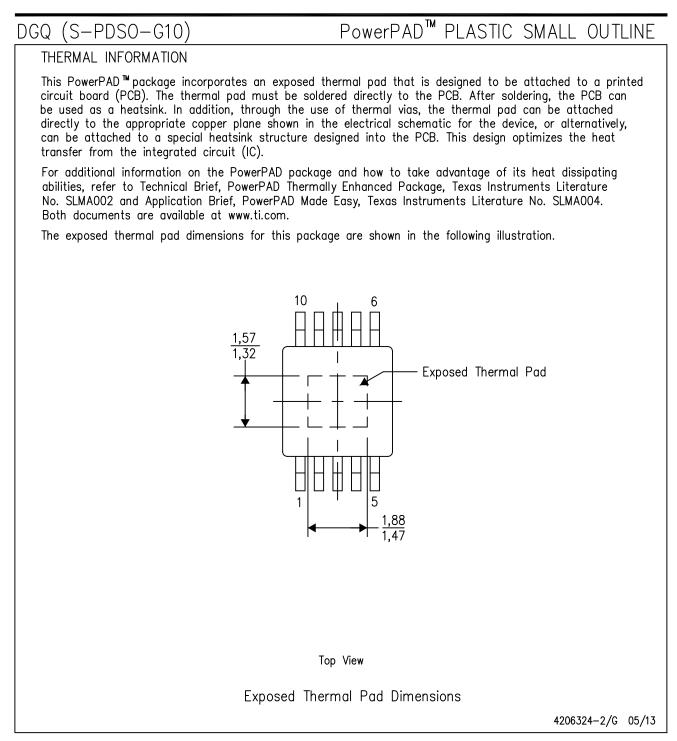

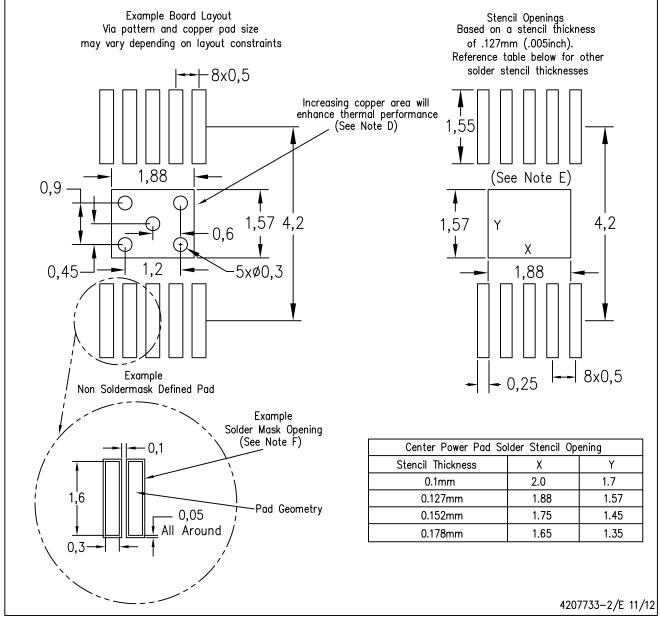

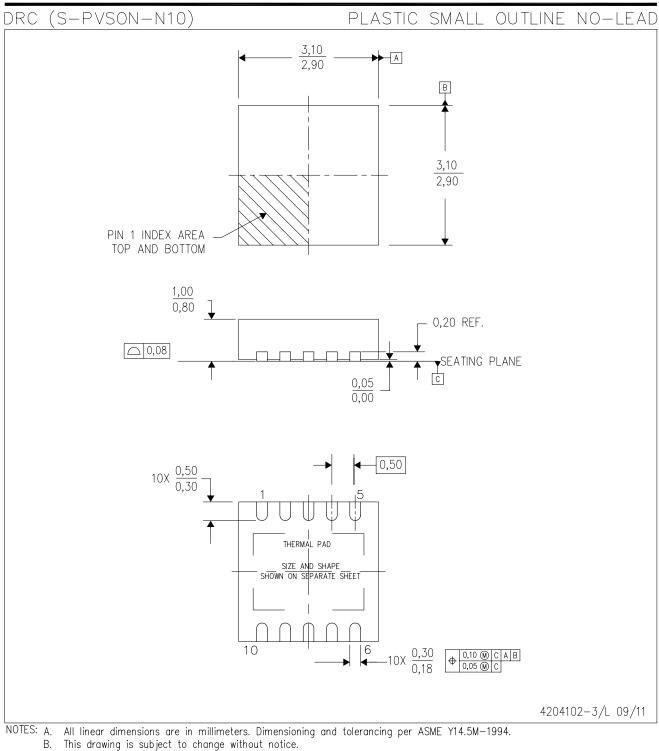

| ORDERING INFORMATION |             |                 |                           |              |  |  |

|----------------------|-------------|-----------------|---------------------------|--------------|--|--|

| Tj                   | PACKAGE     | PACKAGE<br>LEAD | TAPE AND REEL<br>QUANTITY | PART NUMBER  |  |  |

|                      | 10-Pin MSOP | DGQ             | 2500                      | TPS40210DGQR |  |  |

| -40°C to 125°C       | PowerPAD    | DGQ             | 80                        | TPS40210DGQ  |  |  |

| -40 C to 125 C       | 10-Pin SON  | DRC             | 3000                      | TPS40210DRCR |  |  |

|                      |             |                 | 250                       | TPS40210DRCT |  |  |

|                      | 10-Pin MSOP | DGQ             | 2500                      | TPS40211DGQR |  |  |

| 40°C to 125°C        | PowerPAD    | DGQ             | 80                        | TPS40211DGQ  |  |  |

| -40°C to 125°C       | 10-Pin SON  | DBC             | 3000                      | TPS40211DRCR |  |  |

|                      | IU-PIN SON  | DRC             | 250                       | TPS40211DRCT |  |  |

## **DEVICE RATINGS**

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                  |                          |                    | TPS40210<br>TPS40211 | UNIT |

|------------------|--------------------------|--------------------|----------------------|------|

|                  |                          | VDD                | -0.3 to 52           |      |

|                  | Input voltage range      | RC, SS, FB, DIS/EN | –0.3 to 10           | V    |

|                  |                          | ISNS               | -0.3 to 8            | v    |

|                  | Output voltage range     | COMP, BP, GDRV     | –0.3 to 9            |      |

| TJ               | Operating junction tempe | erature range      | -40 to 150           | °C   |

| T <sub>stg</sub> | Storage temperature      |                    | –55 to 150           |      |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

|           |                                | MIN | NOM MAX | UNIT |

|-----------|--------------------------------|-----|---------|------|

| $V_{VDD}$ | Input voltage                  | 4.5 | 52      | V    |

| TJ        | Operating Junction temperature | -40 | 125     | °C   |

## PACKAGE DISSIPATION RATINGS

| PACKAGE                       | AIRFLOW (LFM)          | R <sub>θJA</sub> High-K Board <sup>(1)</sup><br>(°C/W) | Power Rating (W)<br>T <sub>A</sub> = 25°C | Power Rating (W)<br>T <sub>A</sub> = 85°C |

|-------------------------------|------------------------|--------------------------------------------------------|-------------------------------------------|-------------------------------------------|

| 10-Pin MSOP PowerPAD<br>(DGQ) | 0 (Natural Convection) | 57.7                                                   | 1.73                                      | 0.693                                     |

| 10-Pin SON (DRC)              | 0 (Natural Convection) | 47.9                                                   | 2.08                                      | 0.835                                     |

Ratings based on JEDEC High Thermal Conductivity (High K) Board. For more information on the test method, see TI Technical Brief SZZA017.

## **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                            | MIN | TYP  | MAX | UNIT |

|----------------------------|-----|------|-----|------|

| Human Body Model (HBM)     |     | 1500 |     | V    |

| Charged Device Model (CDM) |     | 1500 |     | v    |

www.ti.com

## **ELECTRICAL CHARACTERISTICS**

$T_{J} = -40^{\circ}$ C to 125°C,  $V_{VDD} = 12 V_{dc}$ , all parameters at zero power dissipation (unless otherwise noted)

|                         | PARAMETER                                     |            | TEST CONDITIONS                                                                                                                                                                             | MIN  | TYP  | MAX  | UNIT |

|-------------------------|-----------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VOLTAGE                 | REFERENCE                                     |            |                                                                                                                                                                                             |      |      |      |      |

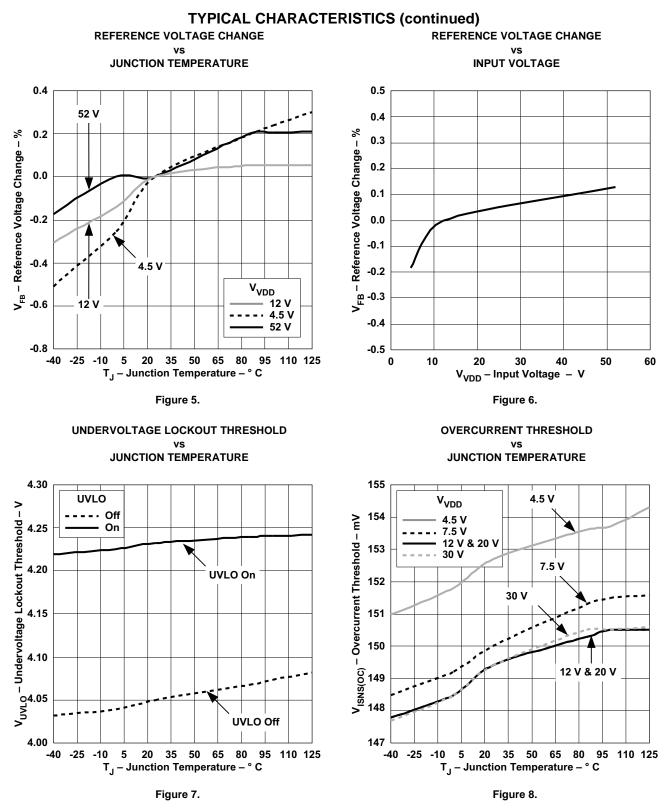

|                         | For the sharehow as a set                     | TPS40210   | $COMP = FB, 4.5 \le V_{VDD} \le 52 \text{ V}, \text{ T}_{\text{J}} = 25^{\circ}\text{C}$                                                                                                    | 693  | 700  | 707  |      |

|                         | Feedback voltage range                        | TPS40211   | COMP=FB, $4.5 \le V_{VDD} \le 52 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}$                                                                                                             | 254  | 260  | 266  |      |

| V <sub>FB</sub>         |                                               | TPS40210   | $\begin{array}{l} \text{COMP} = \text{FB},  4.5 \leq \text{V}_{\text{VDD}} \leq 52  \text{V},  \text{-}40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq \\ 125^{\circ}\text{C} \end{array}$ | 686  | 700  | 714  | mV   |

|                         |                                               | TPS40211   | COMP = FB, $4.5 \le V_{VDD} \le 52 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$                                                                          | 250  | 260  | 270  |      |

| INPUT SUF               | PPLY                                          |            |                                                                                                                                                                                             |      |      |      |      |

| V <sub>VDD</sub>        | Input voltage range                           |            |                                                                                                                                                                                             | 4.5  |      | 52   | V    |

|                         |                                               |            | $4.5 \le V_{VDD} \le 52$ V, no switching, $V_{DIS} < 0.8$                                                                                                                                   |      | 1.5  | 2.5  | mA   |

| I <sub>VDD</sub>        | Operating current                             |            | $2.5 \le V_{\text{DIS}} \le 7 \text{ V}$                                                                                                                                                    |      | 10   | 20   | μA   |

|                         |                                               |            | $V_{VDD} < V_{UVLO(on)}, V_{DIS} < 0.8$                                                                                                                                                     |      |      | 530  | μA   |

| UNDERVO                 | LTAGE LOCKOUT                                 |            |                                                                                                                                                                                             |      |      |      |      |

| V <sub>UVLO(on)</sub>   | Turn on threshold voltage                     |            |                                                                                                                                                                                             | 4.00 | 4.25 | 4.50 | V    |

| V <sub>UVLO(hyst)</sub> | UVLO hysteresis                               |            |                                                                                                                                                                                             | 140  | 195  | 240  | mV   |

| OSCILLAT                | OR                                            |            | <u> </u>                                                                                                                                                                                    |      |      |      |      |

|                         | Oscillator frequency range <sup>(1)</sup>     |            |                                                                                                                                                                                             | 35   |      | 1000 |      |

| fosc                    | Oscillator frequency                          |            | R <sub>RC</sub> = 182 kΩ, C <sub>RC</sub> = 330 pF                                                                                                                                          | 260  | 300  | 340  | kHz  |

|                         | Frequency line regulation                     |            | $4.5 \le V_{DD} \le 52 V$                                                                                                                                                                   | -20% |      | 7%   |      |

| V <sub>SLP</sub>        | Slope compensation ramp                       |            |                                                                                                                                                                                             | 520  | 620  | 720  | mV   |

| PWM                     |                                               |            |                                                                                                                                                                                             |      |      |      |      |

|                         |                                               |            | $V_{VDD} = 12V^{(1)}$                                                                                                                                                                       |      | 275  | 400  |      |

| t <sub>ON(min)</sub>    | Minimum pulse width                           |            | $V_{VDD} = 30V$                                                                                                                                                                             |      | 90   | 200  | ns   |

| t <sub>OFF(min)</sub>   | Minimum off time                              |            |                                                                                                                                                                                             |      | 170  | 200  |      |

| V <sub>VLY</sub>        | Valley voltage                                |            |                                                                                                                                                                                             |      | 1.2  |      | V    |

| SOFT-STA                | RT                                            |            | l l                                                                                                                                                                                         |      |      | 1    |      |

| V <sub>SS(ofst)</sub>   | Offset voltage from SS pin to amplifier input | error      |                                                                                                                                                                                             |      | 700  |      | mV   |

| R <sub>SS(chg)</sub>    | Soft-start charge resistance                  |            |                                                                                                                                                                                             | 320  | 430  | 600  |      |

| R <sub>SS(dchg)</sub>   | Soft-start discharge resistance               | e          |                                                                                                                                                                                             | 840  | 1200 | 1600 | kΩ   |

| ERROR AN                | <b>MPLIFIER</b>                               |            |                                                                                                                                                                                             |      |      | L    |      |

| GBWP                    | Unity gain bandwidth product                  | (1)        |                                                                                                                                                                                             | 1.5  | 3.0  |      | MHz  |

| A <sub>OL</sub>         | Open loop gain <sup>(1)</sup>                 |            |                                                                                                                                                                                             | 60   | 80   |      | dB   |

| I <sub>IB(FB)</sub>     | Input bias current (current out pin)          | of FB      |                                                                                                                                                                                             |      | 100  | 300  | nA   |

| I <sub>COMP(src)</sub>  | Output source current                         |            | V <sub>FB</sub> = 0.6 V, V <sub>COMP</sub> = 1 V                                                                                                                                            | 100  | 250  |      | μA   |

| I <sub>COMP(snk)</sub>  | Output sink current                           |            | V <sub>FB</sub> = 1.2 V, V <sub>COMP</sub> = 1 V                                                                                                                                            | 1.2  | 2.5  |      | mA   |

| · · /                   | RENT PROTECTION                               |            | L L                                                                                                                                                                                         |      |      |      |      |

| V <sub>ISNS(oc)</sub>   | Overcurrent detection threshour ISNS pin)     | old (at    | $4.5 \le V_{DD} < 52 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$                                                                                        | 120  | 150  | 180  | mV   |

| D <sub>OC</sub>         | Overcurrent duty cycle <sup>(1)</sup>         |            |                                                                                                                                                                                             |      |      | 2%   |      |

| V <sub>SS(rst)</sub>    | Overcurrent reset threshold vercurrent        | oltage (at |                                                                                                                                                                                             | 100  | 150  | 350  | mV   |

| T <sub>BLNK</sub>       | Leading edge blanking <sup>(1)</sup>          |            |                                                                                                                                                                                             |      | 75   |      | ns   |

(1) Ensured by design. Not production tested.

NSTRUMENTS

ÈXAS

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

$T_J = -40^{\circ}$ C to 125°C,  $V_{VDD} = 12 V_{dc}$ , all parameters at zero power dissipation (unless otherwise noted)

|                        | PARAMETER                    | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT |  |

|------------------------|------------------------------|-------------------------------------|-----|-----|-----|------|--|

| CURRENT                | SENSE AMPLIFIER              | · · · · ·                           |     |     |     |      |  |

| A <sub>CS</sub>        | Current sense amplifier gain |                                     | 42  | 5.6 | 7.2 | V/V  |  |

| I <sub>B(ISNS)</sub>   | Input bias current           |                                     |     | 1   | 3   | μA   |  |

| DRIVER                 |                              |                                     |     |     |     |      |  |

| I <sub>GDRV(src)</sub> | Gate driver source current   | $V_{GDRV} = 4 V, T_J = 25^{\circ}C$ | 375 | 400 |     | ~ ^  |  |

| I <sub>GDRV(snk)</sub> | Gate driver sink current     | $V_{GDRV} = 4 V, T_J = 25^{\circ}C$ | 330 | 400 |     | mA   |  |

| LINEAR RI              | EGULATOR                     |                                     |     |     | ,   |      |  |

| V <sub>BP</sub>        | Bypass voltage output        | 0 mA < I <sub>BP</sub> < 15 mA      | 7   | 8   | 9   | V    |  |

| DISABLE/               | ENABLE                       |                                     |     |     |     |      |  |

| V <sub>DIS(en)</sub>   | Turn on voltage              |                                     | 0.7 |     | 1.3 | V    |  |

| V <sub>DIS(hys)</sub>  | Hysteresis voltage           |                                     | 25  | 130 | 220 | mV   |  |

| R <sub>DIS</sub>       | DIS pin pulldown resistance  |                                     | 0.7 | 1.1 | 1.5 | MΩ   |  |

Copyright © 2008–2011, Texas Instruments Incorporated

## SLUS772E - MARCH 2008-REVISED OCTOBER 2011

Copyright © 2008–2011, Texas Instruments Incorporated

6

#### SLUS772E - MARCH 2008 - REVISED OCTOBER 2011

8

www.ti.com

NSTRUMENTS

ÈXAS

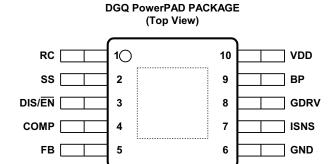

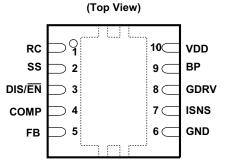

## **DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

| TERM   | TERMINAL |     | MINAL I/O                                                                                                                                                                                                                                                                                                                                                          |  | DESCRIPTION |  |  |  |

|--------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|--|

| NAME   | NO.      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                        |  |             |  |  |  |

| COMP   | 4        | 0   | Error amplifier output. Connect control loop compensation network between COMP pin and FB pin.                                                                                                                                                                                                                                                                     |  |             |  |  |  |

| DIS/EN | 3        | Η   | Disable pin. Pulling this pin high, places the part into a shutdown mode. Shutdown mode is characterized by a very low quiescent current. While in shutdown mode, the functionality of all blocks is disabled and the BP regulator is shut down. This pin has an internal 1-M $\Omega$ pull-down resistor to GND. Leaving this pin unconnected enables the device. |  |             |  |  |  |

| FB     | 5        | Ι   | Error amplifier inverting input. Connect a voltage divider from the output to this pin to set output voltage. Compensation network is connected between this pin and COMP.                                                                                                                                                                                         |  |             |  |  |  |

| GDRV   | 8        | 0   | Connect the gate of the power N channel MOSFET to this pin.                                                                                                                                                                                                                                                                                                        |  |             |  |  |  |

| GND    | 6        | -   | Device ground.                                                                                                                                                                                                                                                                                                                                                     |  |             |  |  |  |

| ISNS   | 7        | Ι   | Current sense pin. Connect an external current sensing resistor between this pin and GND. The voltage on this pin is used to provide current feedback in the control loop and detect an overcurrent condition. An overcurrent condition is declared when ISNS pin voltage exceeds the overcurrent threshold voltage, 150 mV typical.                               |  |             |  |  |  |

| RC     | 1        | Ι   | Switching frequency setting pin. Connect a resistor from RC pin to VDD of the IC power supply and a capacitor from RC to GND.                                                                                                                                                                                                                                      |  |             |  |  |  |

| SS     | 2        | I   | Soft-start time programming pin. Connect capacitor from SS pin to GND to program converter soft-start time. This pin also functions as a timeout timer when the power supply is in an overcurrent condition.                                                                                                                                                       |  |             |  |  |  |

| BP     | 9        | 0   | Regulator output pin. Connect a 1.0-µF bypass capacitor from this pin to GND.                                                                                                                                                                                                                                                                                      |  |             |  |  |  |

| VDD    | 10       | Ι   | System input voltage. Connect a local bypass capacitor from this pin to GND. Depending on the amount of required slope compensation, this pin can be connected to the converter output. See Application Information section for additional details.                                                                                                                |  |             |  |  |  |

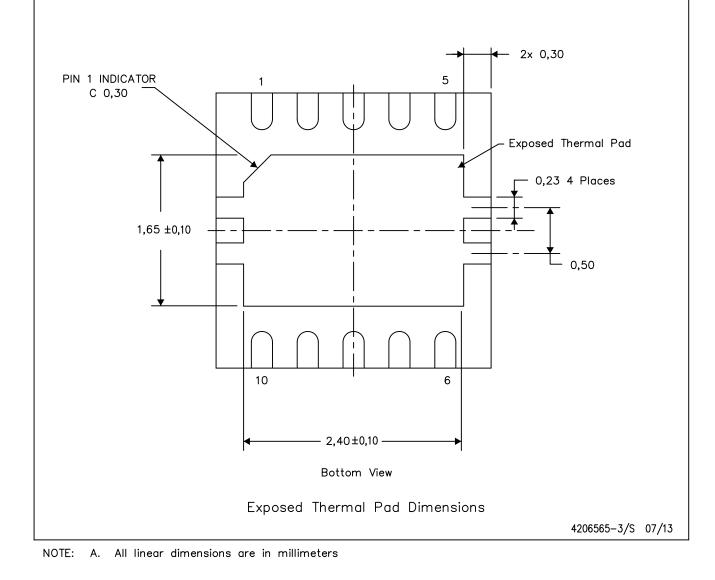

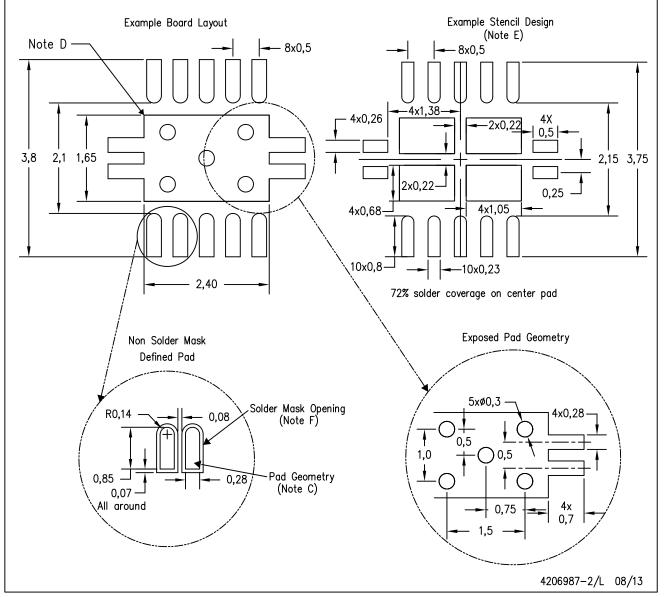

DRC SURFACE MOUNT PACKAGE

Copyright © 2008–2011, Texas Instruments Incorporated

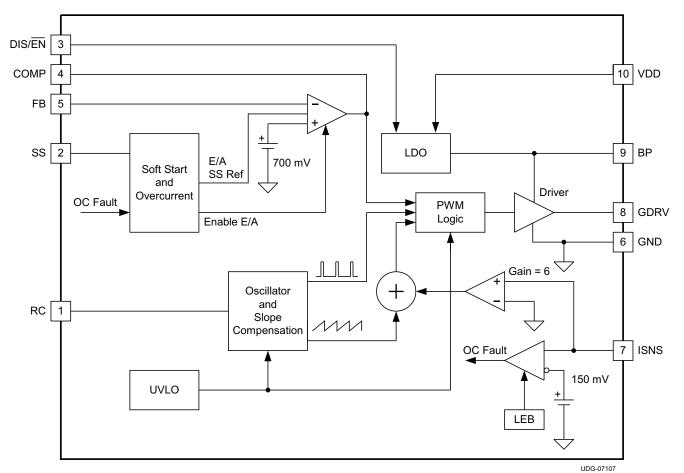

#### FUNCTIONAL BLOCK DIAGRAM

Copyright © 2008–2011, Texas Instruments Incorporated

www.ti.com

. .

SLUS772E - MARCH 2008-REVISED OCTOBER 2011

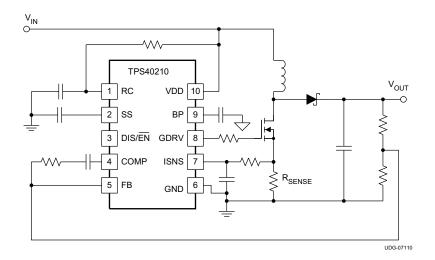

## APPLICATION INFORMATION

## Minimum On-Time and Off Time Considerations

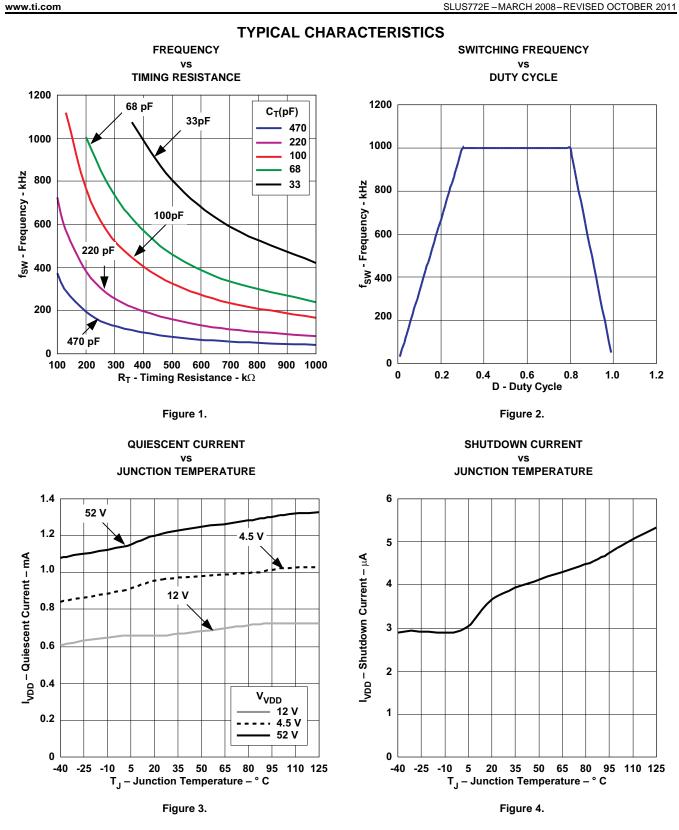

The TPS40210 has a minimum off time of approximately 200 ns and a minimum on time of 300 ns. These two constraints place limitations on the operating frequency that can be used for a given input to output conversion ratio. See Figure 2 for the maximum frequency that can be used for a given duty cycle.

The duty cycle at which the converter operates is dependent on the mode in which the converter is running. If the converter is running in discontinuous conduction mode, the duty cycle varies with changes to the load much more than it does when running in continuous conduction mode.

In continuous conduction mode, the duty cycle is related primarily to the input and output voltages.

$$\frac{V_{OUT} + V_D}{V_{IN}} = \frac{1}{1 - D}$$

$$D = \left(1 - \left(\frac{V_{IN}}{V_{OUT} + V_D}\right)\right)$$

(2)

In discontinuous mode the duty cycle is a function of the load, input and output voltages, inductance and switching frequency.

$$D = \frac{2 \times (V_{OUT} + V_D) \times I_{OUT} \times L \times f_{SW}}{(V_{IN})^2}$$

(3)

All converters using a diode as the freewheeling or catch component have a load current level at which they transition from discontinuous conduction to continuous conduction. This is the point where the inductor current just falls to zero. At higher load currents, the inductor current does not fall to zero but remains flowing in a positive direction and assumes a trapezoidal wave shape as opposed to a triangular wave shape. This load boundary between discontinuous conduction and continuous conduction can be found for a set of converter parameters as follows.

$$I_{OUT(crit)} = \frac{\left(V_{OUT} + V_D - V_{IN}\right) \times \left(V_{IN}\right)^2}{2 \times \left(V_{OUT} + V_D\right)^2 \times f_{SW} \times L}$$

(4)

For loads higher than the result of Equation 4, the duty cycle is given by Equation 2 and for loads less that the results of Equation 4, the duty cycle is given Equation 3. For Equations 1 through 4, the variable definitions are as follows.

- V<sub>OUT</sub> is the output voltage of the converter in V

- $V_{D}$  is the forward conduction voltage drop across the rectifier or catch diode in V

- V<sub>IN</sub> is the input voltage to the converter in V

- I<sub>OUT</sub> is the output current of the converter in A

- L is the inductor value in H

- $f_{SW}$  is the switching frequency in Hz

(3)

#### www.ti.com

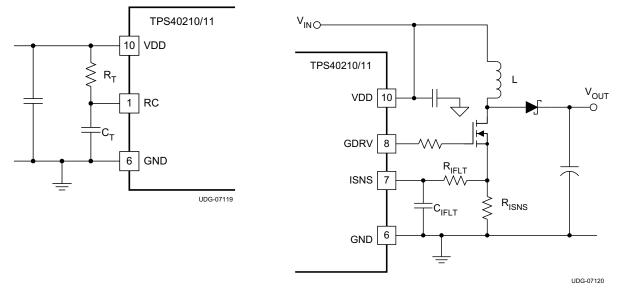

#### Setting the Oscillator Frequency

The oscillator frequency is determined by a resistor and capacitor connected to the RC pin of the TPS40210. The capacitor is charged to a level of approximately  $V_{VDD}/20$  by current flowing through the resistor and is then discharged by a transistor internal to the TPS40210. The required resistor for a given oscillator frequency is found from either Figure 1 or Equation 5.

$$R_{T} = \frac{1}{5.8 \times 10^{-8} \times f_{SW} \times C_{T} + 8 \times 10^{-10} \times f_{SW}^{2} + 1.4 \times 10^{-7} \times f_{SW} - 1.5 \times 10^{-4} + 1.7 \times 10^{-6} \times C_{T} - 4 \times 10^{-9} \times C_{T}^{2}}$$

(5)

Where:

- $R_T$  is the timing resistance in k $\Omega$

- f<sub>SW</sub> is the switching frequency in kHz

- C<sub>T</sub> is the timing capacitance in pF

For most applications a capacitor in the range of 68 pF to 120 pF gives the best results. Resistor values should be limited to between 100 k $\Omega$  and 1 M $\Omega$  as well. If the resistor value falls below 100 k $\Omega$ , decrease the capacitor size and recalculate the resistor value for the desired frequency. As the capacitor size decreases below 47 pF, the accuracy of Equation 5 degrades and empirical means may be needed to fine tune the timing component values to achieve the desired switching frequency.

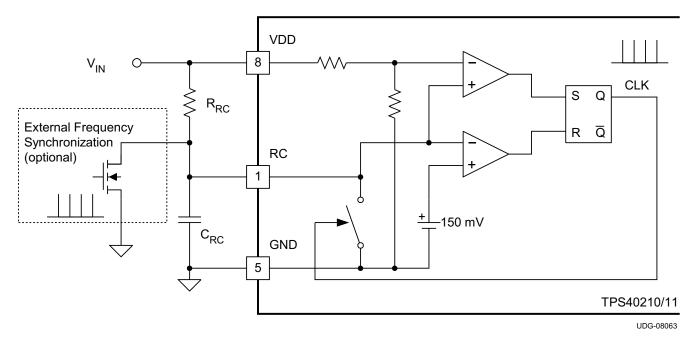

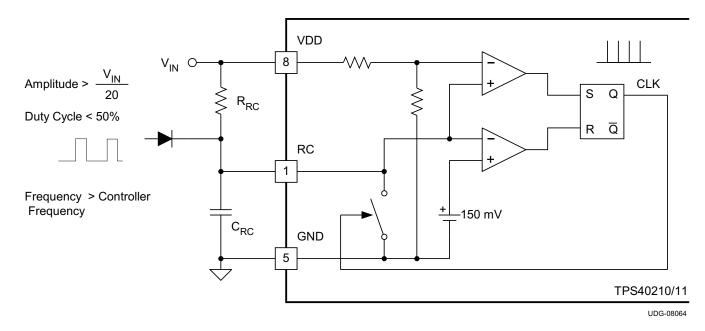

## Synchronizing the Oscillator

The TPS40210 and TPS40211 can be synchronized to an external clock source. Figure 20 shows the functional diagram of the oscillator. When synchronizing the oscillator to an external clock, the RC pin must be pulled below 150 mV for 20 ns or more. The external clock frequency must be higher than the free running frequency of the converter as well. When synchronizing the controller, if the RC pin is held low for an excessive amount of time, erratic operation may occur. The maximum amount of time that the RC pin should be held low is 50% of a nominal output pulse, or 10% of the period of the synchronization frequency.

Under circumstances where the duty cycle is less than 50%, a Schottky diode connected from the RC pin to an external clock may be used to synchronize the oscillator. The cathode of the diode is connected to the RC pin. The trip point of the oscillator is set by an internal voltage divider to be 1/20 of the input voltage. The clock signal must have an amplitude higher than this trip point. When the clock goes low, it allows the reset current to restart the RC ramp, synchronizing the oscillator to the external clock. This provides a simple, single-component method for clock synchronization.

#### Figure 20. Oscillator Functional Diagram

**ISTRUMENTS**

EXAS

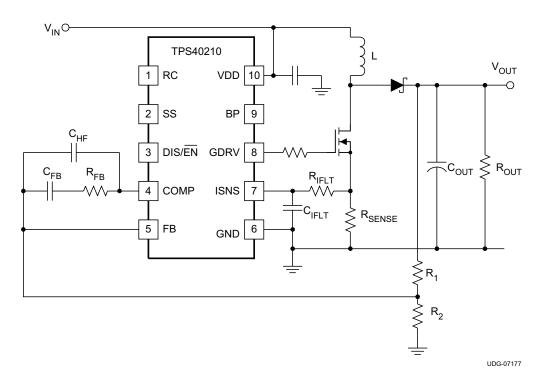

## **Current Sense and Overcurrent**

The tps40210 and TPS40211 are current mode controllers and use a resistor in series with the source terminal power FET to sense current for both the current mode control and overcurrent protection. The device enters a current limit state if the voltage on the ISNS pin exceeds the current limit threshold voltage  $V_{ISNS(oc)}$  from the electrical specifications table. When this happens the controller discharges the SS capacitor through a relatively high impedance and then attempt to restart. The amount of output current that causes this to happen is dependent on several variables in the converter.

#### Figure 22. Oscillator Components

Figure 23. Current Sense Components

The load current overcurrent threshold is set by proper choice of  $R_{ISNS}$ . If the converter is operating in discontinuous mode the current sense resistor is found in Equation 6.

www.ti.com

NSTRUMENTS

$$\mathsf{R}_{\mathsf{ISNS}} = \frac{f_{\mathsf{SW}} \times \mathsf{L} \times V_{\mathsf{ISNS(oc)}}}{\sqrt{2 \times \mathsf{L} \times f_{\mathsf{SW}} \times \mathsf{I}_{\mathsf{OUT(oc)}} \times (\mathsf{V}_{\mathsf{OUT}} + \mathsf{V}_{\mathsf{D}} - \mathsf{V}_{\mathsf{IN}})}}$$

(6)

If the converter is operating in continuous conduction mode R<sub>ISNS</sub> can be found in Equation 7.

$$R_{ISNS} = \frac{V_{ISNS}}{\left(\frac{I_{OUT}}{1-D}\right) + \left(\frac{I_{RIPPLE}}{2}\right)} = \frac{V_{ISNS}}{\left(\frac{I_{OUT}}{(1-D)}\right) + \left(\frac{D \times V_{IN}}{2 \times f_{SW} \times L}\right)}$$

(7)

Where:

- R<sub>ISNS</sub> is the value of the current sense resistor in Ω.

- V<sub>ISNS(oc)</sub> is the overcurrent threshold voltage at the ISNS pin (from electrical specifications)

- D is the duty cycle (from Equation 2)

- f<sub>SW</sub> is the switching frequency in Hz

- V<sub>IN</sub> is the input voltage to the power stage in V (see text)

- · L is the value of the inductor in H

- I<sub>OUT</sub>(oc) is the desired overcurrent trip point in A

- V<sub>D</sub> is the drop across the diode in Figure 23

The TPS40210/11 has a fixed undervoltage lockout (UVLO) that allows the controller to start at a typical input voltage of 4.25 V. If the input voltage is slowly rising, the converter might have less than its designed nominal input voltage available when it has reached regulation. As a result, this may decreases the apparent current limit load current value and must be taken into consideration when selecting  $R_{ISNS}$ . The value of  $V_{IN}$  used to calculate  $R_{ISNS}$  must be the value at which the converter finishes startup. The total converter output current at startup is the sum of the external load current and the current required to charge the output capacitor(s). See the *Soft Start* section of this datasheet for information on calculating the required output capacitor charging current.

The topology of the standard boost converter has no method to limit current from the input to the output in the event of a short circuit fault on the output of the converter. If protection from this type of event is desired, it is necessary to use some secondary protection scheme, such as a fuse, or rely on the current limit of the upstream power source.

#### **Current Sense and Sub-Harmonic Instability**

A characteristic of peak current mode control results in a condition where the current control loop can exhibit instability. This results in alternating long and short pulses from the pulse width modulator. The voltage loop maintains regulation and does not oscillate, but the output ripple voltage increases. The condition occurs only when the converter is operating in continuous conduction mode and the duty cycle is 50% or greater. The cause of this condition is described in Texas Instruments literature number SLUA101, available at www.ti.com. The remedy for this condition is to apply a compensating ramp from the oscillator to the signal going to the pulse width modulator. In the TPS40210/11 the oscillator ramp is applied in a fixed amount to the pulse width modulator. The slope of the ramp is given in Equation 8.

$$s_e = f_{SW} \times \left(\frac{V_{VDD}}{20}\right)$$

(8)

To ensure that the converter does not enter into sub-harmonic instability, the slope of the compensating ramp signal must be at least half of the down slope of the current ramp signal. Since the compensating ramp is fixed in the TPS40210/11, this places a constraint on the selection of the current sense resistor.

The down slope of the current sense wave form at the pulse width modulator is described in Equation 9.

$$m2 = \frac{A_{CS} \times R_{ISNS} \times (V_{OUT} + V_D - V_{IN})}{L}$$

(9)

# TPS40210, TPS40211

Since the slope compensation ramp must be at least half, and preferably equal to the down slope of the current sense waveform seen at the pulse width modulator, a maximum value is placed on the current sense resistor when operating in continuous mode at 50% duty cycle or greater. For design purposes, some margin should be applied to the actual value of the current sense resistor. As a starting point, the actual resistor chosen should be 80% or less that the value calculated in Equation 10. This equation calculates the resistor value that makes the slope compensation ramp equal to one half of the current ramp downslope. Values no more than 80% of this result would be acceptable.

$$\mathsf{R}_{\mathsf{ISNS}(\mathsf{max})} = \frac{\mathsf{V}_{\mathsf{VDD}} \times \mathsf{L} \times f_{\mathsf{SW}}}{60 \times (\mathsf{V}_{\mathsf{OUT}} + \mathsf{V}_{\mathsf{D}} - \mathsf{V}_{\mathsf{IN}})}$$

Where:

- S<sub>e</sub> is the slope of the voltage compensating ramp applied to the pulse width modulator in V/s

- *f*<sub>SW</sub> is the switching frequency in Hz

SLUS772E - MARCH 2008 - REVISED OCTOBER 2011

- V<sub>VDD</sub> is the voltage at the VDD pin in V

- m2 is the down slope of the current sense waveform seen at the pulse width modulator in V/s

- R<sub>ISNS</sub> is the value of the current sense resistor in Ω

- $V_{OUT}$  is the converter output voltage  $V_{IN}$  is the converter power stage input voltage

- V<sub>D</sub> is the drop across the diode in Figure 23

It is possible to increase the voltage compensation ramp slope by connecting the VDD pin to the output voltage of the converter instead of the input voltage as shown in Figure 23. This can help in situations where the converter design calls for a large ripple current value in relation to the desired output current limit setting.

#### NOTE

Connecting the VDD pin to the output voltage of the converter affects the startup voltage of the converter since the controller undervoltage lockout (UVLO) circuit monitors the VDD pin and senses the input voltage less the diode drop before startup. The effect is to increase the startup voltage by the value of the diode voltage drop.

If an acceptable  $R_{ISNS}$  value is not available, the next higher value can be used and the signal from the resistor divided down to an acceptable level by placing another resistor in parallel with  $C_{IFLT}$

## **Current Sense Filtering**

$t_{ON} = \frac{D}{f_{SW}}$

In most cases, a small filter placed on the ISNS pin improves performance of the converter. These are the components  $R_{IFLT}$  and  $C_{IFLT}$  in Figure 23. The time constant of this filter should be approximately 10% of the nominal pulse width of the converter. The pulse width can be found using Equation 11.

$$R_{IFLT} \times C_{IFLT} = 0.1 \times t_{ON}$$

The range of  $R_{IFLT}$  should be from about 1 k $\Omega$  to 5 k $\Omega$  for best results. Higher values can be used but this raises the impedance of the ISNS pin connection more than necessary and can lead to noise pickup issues in some layouts.  $C_{IFLT}$  should be located as close as possible to the ISNS pin as well to provide noise immunity.

## Soft Start

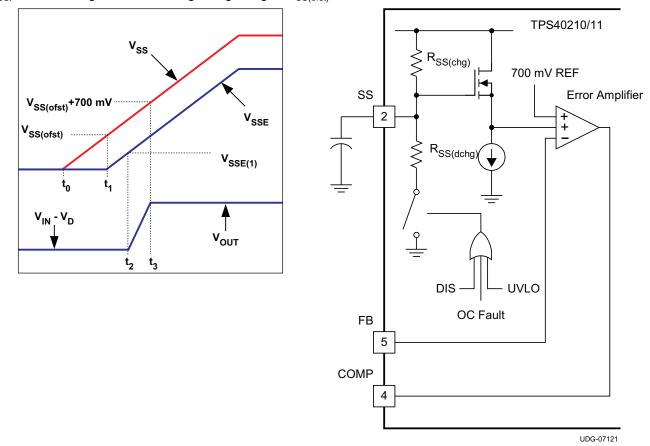

The soft-start feature of the TPS40210/11 is a closed loop soft start, meaning that the output voltage follows a linear ramp that is proportional to the ramp generated at the SS pin. This ramp is generated by an internal resistor connected from the BP pin to the SS pin and an external capacitor connected from the SS pin to GND. The SS pin voltage ( $V_{SS}$ ) is level shifted down by approximately  $V_{SS(ofst)}$  (approximately 700 mV) and sent to one of the "+" (the "+" input with the lowest voltage dominates) inputs of the error amplifier. When this level shifted voltage ( $V_{SSE}$ ) starts to rise at time t<sub>1</sub> (see Figure 24), the output voltage the controller expects, rises as well. Since  $V_{SSE}$  starts at near 0 V, the controller attempts to regulate the output voltage from a starting point of zero

(12)

(10)

<sup>16</sup> Submit Documentation Feedback

Copyright © 2008–2011, Texas Instruments Incorporated

volts. It cannot do this due to the converter architecture. The output voltage starts from the input voltage less the drop across the diode ( $V_{IN} - V_D$ ) and rises from there. The point at which the output voltage starts to rise ( $t_2$ ) is the point where the  $V_{SSE}$  ramp passes the point where it is commanding more output voltage than ( $V_{IN} - V_D$ ). This voltage level is labeled  $V_{SSE(1)}$ . The time required for the output voltage to ramp from a theoretical zero to the final regulated value (from  $t_1$  to  $t_3$ ) is determined by the time it takes for the capacitor connected to the SS pin ( $C_{SS}$ ) to rise through a 700 mV range, beginning at  $V_{SS(ofst)}$  above GND.

Figure 24. SS Pin Voltage and Output Voltage

## Figure 25. SS Pin Functional Circuit

The required capacitance for a given soft start time  $t_3 - t_1$  in Figure 24 is calculated in Equation 13.

$$C_{SS} = \frac{t_{SS}}{R_{SS} \times In \left( \frac{V_{BP} - V_{SS(ofst)}}{V_{BP} - \left( V_{SS(ofst)} + V_{FB} \right)} \right)}$$

Where:

- t<sub>SS</sub> is the soft-start time, in seconds

- $R_{SS(chq)}$  is the SS charging resistance in  $\Omega$ , typically 500 k $\Omega$

- C<sub>SS</sub> is the value of the capacitor on the SS pin, in F

- V<sub>BP</sub> is the value of the voltage on the BP pin, in V

- V<sub>SS(ofst)</sub> is the approximate level shift from the SS pin to the error amplifier (~700 mV)

- V<sub>FB</sub> is the error amplifier reference voltage, 700mV typical

Note that  $t_{SS}$  is the time it takes for the output voltage to rise from 0 V to the final output voltage. Also note the tolerance on  $R_{SS(chg)}$  given in the electrical specifications table. This contributes to some variability in the output voltage rise time and margin must be applied to account for it in design.

#### Copyright © 2008–2011, Texas Instruments Incorporated

(13)

# TPS40210, TPS40211

#### SLUS772E - MARCH 2008 - REVISED OCTOBER 2011

Also take note of V<sub>BP</sub>. Its value varies depending on input conditions. For example, a converter operating from a slowly rising input initializes V<sub>BP</sub> at a fairly low value and increases during the entire startup sequence. If the controller has a voltage above 8 V at the input and the DIS pin is used to stop and then restart the converter, V<sub>BP</sub> is approximately 8 V for the entire startup sequence. The higher the voltage on BP, the shorter the startup time is and conversely, the lower the voltage on BP, the longer the startup time is.

The soft-start time (t<sub>SS</sub>) must be chosen long enough so that the converter can start up without going into an overcurrent state. Since the over current state is triggered by sensing the peak voltage on the ISNS pin, that voltage must be kept below the overcurrent threshold voltage V<sub>ISNS(oc)</sub>. The voltage on the ISNS pin is a function of the load current of the converter, the rate of rise of the output voltage and the output capacitance, and the current sensing resistor. The total output current that must be supported by the converter is the sum of the charging current required by the output capacitor and any external load that must be supplied during startup. This current must be less than the IOUT(oc) value used in Equation 6 or Equation 7 (depending on the operating mode of the converter) to determine the current sense resistor value. In these equations, the actual input voltage at the time that the controller reaches the final output voltage is the important input voltage to use in the calculations. If the input voltage is slowly rising and is at less than the nominal input voltage when the startup time ends, the output current limit is less than I<sub>OUT(oc)</sub> at the nominal input voltage. The output capacitor charging current must be reduced (decrease C<sub>OUT</sub> or increase the t<sub>SS</sub>) or I<sub>OUT(oc)</sub> must be increased and a new value for R<sub>ISNS</sub> calculated.

$$I_{C(chg)} = \left[ \frac{C_{OUT} \times V_{OUT}}{t_{SS}} \right]$$

$$t_{SS} > \left[ \frac{C_{OUT} \times V_{OUT}}{(I_{OUT(oc)} - I_{EXT})} \right]$$

(15)

Where:

- I<sub>C(chg)</sub> is the output capacitor charging current in A

- C<sub>OUT</sub> is the total output capacitance in F

- V<sub>OUT</sub> is the output voltage in V

- t<sub>SS</sub> is the soft start time from Equation 13

- I<sub>OUT(oc)</sub> is the desired over current trip point in A

- I<sub>FXT</sub> is any external load current in A

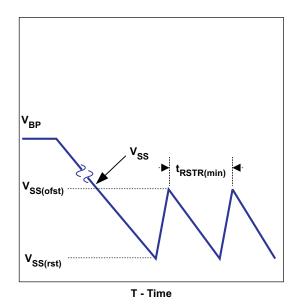

The capacitor on the SS pin (C<sub>SS</sub>) also plays a role in overcurrent functionality. It is used as the timer between restart attempts. The SS pin is connected to GND through a resistor, R<sub>SS(dchg)</sub>, whenever the controller senses an overcurrent condition. Switching stops and nothing else happens until the SS pin discharges to the soft-start reset threshold, V<sub>SS(rst)</sub>. At this point, the SS pin capacitor is allowed to charge again through the charging resistor R<sub>SS(chg)</sub>, and the controller restarts from that point. The shortest time between restart attempts occurs when the SS  $\check{p}$ in discharges from V<sub>SS(ofst)</sub> (approximately 700 mV) to V<sub>SS(rst)</sub> (150 mV) and then back to V<sub>SS(ofst)</sub> and switching resumes. In actuality, this is a conservative estimate since switching does not resume until the V<sub>SSE</sub> ramp rises to a point where it is commanding more output voltage than exists at the output of the controller. This occurs at some SS pin voltage greater than V<sub>SS(ofst)</sub> and depends on the voltage that remains on the output overvoltage the converter while switching has been halted. The fastest restart time can be calculated by using Equation 16, Equation 17 and Equation 18.

$$t_{\text{DCHG}} = R_{\text{SS(dchg)}} \times C_{\text{SS}} \times \ln\left(\frac{V_{\text{SS(ofst)}}}{V_{\text{SS(rst)}}}\right)$$

(16)

$$\left(\left(V_{\text{BP}} - V_{\text{SS(rst)}}\right)\right)$$

$$t_{CHG} = R_{SS(chg)} \times C_{SS} \times In \left( \frac{(V_{BP} - V_{SS(ofst)})}{(V_{BP} - V_{SS(ofst)})} \right)$$

(17)

$$t_{RSTRT(min)} = t_{CHG} + t_{DCHG}$$

(15)

(18)

SLUS772E - MARCH 2008-REVISED OCTOBER 2011

Figure 26. Soft Start During Overcurrent

Copyright © 2008–2011, Texas Instruments Incorporated

(21)

# **BP Regulator**

The TPS40210/11 has an on board linear regulator the supplies power for the internal circuitry of the controller, including the gate driver. This regulator has a nominal output voltage of 8 V and must be bypassed with a  $1-\mu$ F capacitor. If the voltage at the VDD pin is less than 8 V, the voltage on the BP pin will also be less and the gate drive voltage to the external FET is reduced from the nominal 8 V. This should be considered when choosing a FET for the converter.

Connecting external loads to this regulator can be done, but care must be taken to ensure that the thermal rating of the device is observed since there is no thermal shutdown feature in this controller. Exceeding the thermal ratings cause out of specification behavior and can lead to reduced reliability. The controller dissipates more power when there is an external load on the BP pin and is tested for dropout voltage for up to 5-mA load. When the controller is in the disabled state, the BP pin regulator also shuts off so loads connected there power down as well. When the controller is disabled with the DIS/EN pin, this regulator is turned off.

The total power dissipation in the controller can be calculated as follows. The total power is the sum of  $P_Q$ ,  $P_G$  and  $P_E$ .

| $P_{Q} = V_{VDD} \times I_{VDD(en)}$                  | (19) |

|-------------------------------------------------------|------|

| $P_{G} = V_{VDD} \times Q_{g} \times \mathit{f}_{SW}$ | (20) |

$$P_{E} = V_{VDD} \times I_{EXT}$$

Where:

- P<sub>Q</sub> is the quiescent power of the device in W

- V<sub>VDD</sub> is the VDD pin voltage in V

- I<sub>VDD(en)</sub> is the quiescent current of the controller when enabled but not switching in A

- P<sub>G</sub> is the power dissipated by driving the gate of the FET in W

- $Q_{\alpha}$  is the total gate charge of the FET at the voltage on the BP pin in C

- f <sub>SW</sub> is the switching frequency in Hz

- P<sub>E</sub> is the dissipation caused be external loading of the BP pin in W

- I<sub>EXT</sub> is the external load current in A

## Shutdown (DIS/EN Pin)

The DIS/EN pin is an active high shutdown command for the controller. Pulling this pin above 1.2 V causes the controller to completely shut down and enter a low current consumption state. In this state, the regulator connected to the BP pin is turned off. There is an internal  $1.1-M\Omega$  pull-down resistor connected to this pin that keeps the pin at GND level when left floating. If this function is not used in an application, it is best to connect this pin to GND.

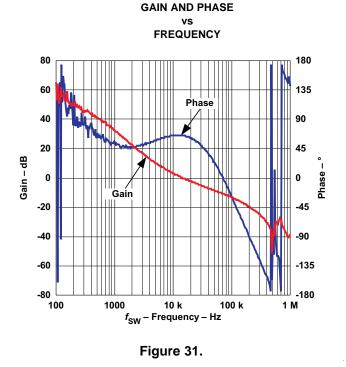

#### **Control Loop Considerations**

There are two methods to design a suitable control loop for the TPS4021x. The first and preferred if equipment is available is to use a frequency response analyzer to measure the open loop modulator and power stage gain and to then design compensation to fit that. The usage of these tools for this purpose is well documented with the literature that accompanies the tool and is not be discussed here.

The second option is to make an initial guess at compensation, and then evaluate the transient response of the system to see if the compensation is acceptable to the application or not. For most systems, an adequate response can be obtained by simply placing a series resistor and capacitor ( $R_{FB}$  and  $C_{FB}$ ) from the COMP pin to the FB pin as shown in Figure 27.

Figure 27. Basic Compensation Network

The natural phase characteristics of most capacitors used for boost outputs combined with the current mode control provide adequate phase margin when using this type of compensation. To determine an initial starting point for the compensation, the desired crossover frequency must be considered when estimating the control to output gain. The model used is a current source into the output capacitor and load.

When using these equations, the loop bandwidth should be no more than 20% of the switching frequency, f  $_{SW}$ . A more reasonable loop bandwidth would be 10% of the switching frequency. Be sure to evaluate the transient response of the converter over the expected load range to ensure acceptable operation.

$$\begin{aligned} \left| \mathsf{K}_{CO} \right| &= \mathsf{g}_{\mathsf{M}} \times \left| \mathsf{Z}_{\mathsf{OUT}} \left( f_{\mathsf{CO}} \right) \right| \end{aligned} \tag{22} \\ \mathsf{g}_{\mathsf{M}} &= \frac{0.13 \times \sqrt{\mathsf{L} \times \frac{f_{\mathsf{SW}}}{\mathsf{R}_{\mathsf{OUT}}}}}{\left( \mathsf{R}_{\mathsf{ISNS}} \right)^2 \times \left( 120 \times \mathsf{R}_{\mathsf{ISNS}} + \mathsf{L} \times f_{\mathsf{SW}} \right)} \end{aligned} \tag{23} \\ \left| \mathsf{Z}_{\mathsf{OUT}} \right| &= \mathsf{R}_{\mathsf{OUT}} \times \sqrt{\frac{\left( 1 + \left( 2\pi \times \mathsf{f}_{\mathsf{L}} \times \mathsf{R}_{\mathsf{ESR}} \times \mathsf{C}_{\mathsf{OUT}} \right)^2 \right)}{1 + \left( \left( \mathsf{R}_{\mathsf{OUT}} \right)^2 + 2 \times \mathsf{R}_{\mathsf{OUT}} \times \mathsf{R}_{\mathsf{ESR}} + \left( \mathsf{R}_{\mathsf{ESR}} \right)^2 \right) \times \left( 2\pi \times \mathsf{f}_{\mathsf{L}} \times \mathsf{C}_{\mathsf{OUT}} \right)^2} \end{aligned} \tag{24}$$

Copyright © 2008–2011, Texas Instruments Incorporated

www.ti.com

## Where:

- K<sub>CO</sub> is the control to output gain of the converter, in V/V

- $g_M$  is the transconductance of the power stage and modulator, in S

- R<sub>OUT</sub> is the output load equivalent resistance, in Ω

- $Z_{OUT}$  is the output impedance, including the output capacitor, in  $\Omega$

- $R_{ISNS}$  is the value of the current sense resistor, in  $\Omega$

- L is the value of the inductor, in H

- COUT is the value of the output capacitance, in F

- $R_{ESR}$  is the equivalent series resistance of  $C_{OUT}$ , in  $\Omega$

- f <sub>SW</sub> is the switching frequency, in Hz

- f<sub>L</sub> is the desired crossover frequency for the control loop, in Hz

These equations assume that the operation is discontinuous and that the load is purely resistive. The gain in continuous conduction can be found by evaluating Equation 23 at the resistance that gives the critical conduction current for the converter. Loads that are more like current sources give slightly higher gains than predicted here. To find the gain of the compensation network required for a control loop of bandwidth  $f_L$ , take the reciprocal of Equation 22.

$$K_{\text{COMP}} = \frac{1}{|K_{\text{CO}}|}$$

(25)

The GBWP of the error amplifier is only guaranteed to be at least 1.5 MHz. If  $K_{COMP}$  multiplied by  $f_L$  is greater than 750 kHz, reduce the desired loop crossover frequency until this condition is satisfied. This ensures that the high-frequency pole from the error amplifier response with the compensation network in place does not cause excessive phase lag at f  $_L$  and decreased phase margin in the loop.

The R-C network connected from COMP to FB places a zero in the compensation response. That zero should be approximately 1/10th of the desired crossover frequency, f<sub>L</sub>. With that being the case, R<sub>FB</sub> and C<sub>FB</sub> can be found from Equation 26 and Equation 27

$$R_{FB} = \frac{R1}{|K_{CO}|} = R1 \times K_{COMP}$$

$$C_{FB} = \frac{10}{2\pi \times f_L \times R_{FB}}$$

(26)

(27)

Where:

- R1 is the high side feedback resistor in Figure 27, in Ω

- fL is the desired loop crossover frequency, in Hz

1

Thought not strictly necessary, it is recommended that a capacitor be added between COMP and FB to provide high-frequency noise attenuation in the control loop circuit. This capacitor introduces another pole in the compensation response. The allowable location of that pole frequency determines the capacitor value. As a starting point, the pole frequency should be  $10 \times f_L$ . The value of  $C_{HF}$  can be found from Equation 28.

$$C_{HF} = \frac{I}{20\pi \times f_{L} \times R_{FB}}$$

(28)

SLUS772E - MARCH 2008 - REVISED OCTOBER 2011

While the error amplifier GBWP will usually be higher, it can be as low as 1.5 MHz. If  $10 \times K_{Comp} \times f_L > 1.5$  MHz, the error amplifier gain-bandwidth product may limit the high-frequency response below that of the high-frequency capacitor. To maintain a consistent high-frequency gain roll-off,  $C_{HF}$  can be calculated by Equation 29.

$$C_{HF} = \frac{1}{2\pi \times 1.5 \times (10)^6 \times R_{FB}}$$

Where:

- C<sub>HF</sub> is the high-frequency roll-off capacitor value in F

- R<sub>FB</sub> is the mid band gain setting resistor value in Ω

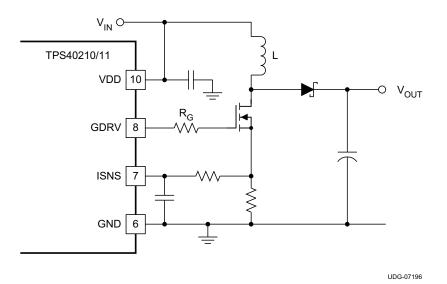

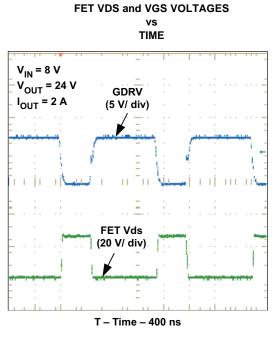

## GATE DRIVE CIRCUIT

Some applications benefit from the addition of a resistor connected between the GDRV pin and the gate of the switching MOSFET. In applications that have particularly stringent load regulation (under 0.75%) requirements and operate from input voltages above 5 V, or are sensitive to pulse jitter in the discontinuous conduction region, this resistor is recommended. The recommended starting point for the value of this resistor can be calculated from Equation 30.

$$R_G = \frac{105}{Q_G}$$

Where:

- Q<sub>G</sub> is the MOSFET total gate charge at 8-V V<sub>GS</sub> in nC

- R<sub>G</sub> is the suggested starting point gate resistance in Ω

Figure 28. Gate Drive Resistor

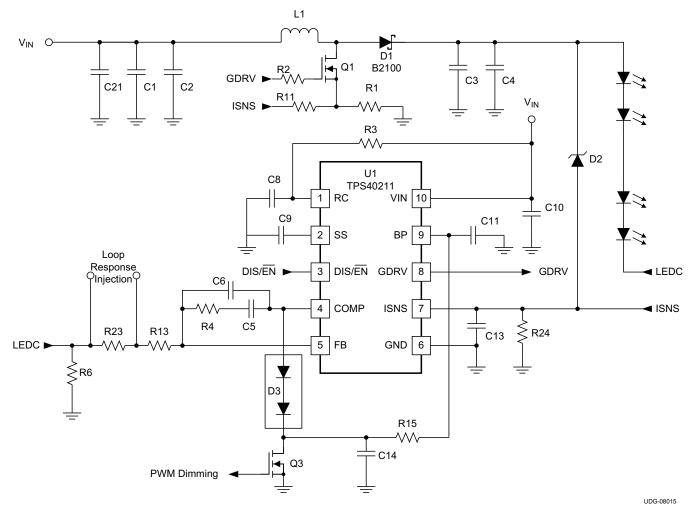

## TPS40211

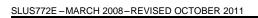

The only difference between the TPS40210 and the TPS40211 is the reference voltage that the error amplifier uses to regulate the output voltage. The TPS40211 uses a 260-mV reference and is intended for applications where the output is actually a current instead of a regulated voltage. A typical example of an application of this type is an LED driver. An example schematic is shown in Figure 29.

Copyright © 2008–2011, Texas Instruments Incorporated

(29)

(30)

(31)

## Figure 29. Typical LED Drive Schematic

The current in the LED string is set by the choice of the resistor  $R_{ISNS}$  as shown in Equation 31.

$$R_{IFB} = \frac{V_{FB}}{I_{OUT}}$$

Where:

- $R_{\text{IFB}}$  is the value of the current sense resistor for the LED string in  $\Omega$

- V<sub>FB</sub> is the reference voltage for the TPS40211 in V (0.260 V typ)

- I<sub>OUT</sub> is the desired DC current in the LED string in A

Copyright © 2008–2011, Texas Instruments Incorporated

#### SLUS772E - MARCH 2008-REVISED OCTOBER 2011

## ADDITIONAL REFERENCES

## **Related Devices**

The following devices have characteristics similar to the TPS40210 and may be of interest.

| DEVICE   | DESCRIPTION                                                             |

|----------|-------------------------------------------------------------------------|

| TPS6100X | Single- and Dual-Cell Boost Converter with Start-up into Full Load      |

| TPS6101X | High Efficiency 1-Cell and 2-Cell Boost Converters                      |

| TPS6300X | High Efficiency Single Inductor Buck-Boost Converter with 1.8A Switches |

#### Table 1. Related Parts

## References

These references may be found on the web at www.power.ti.com under Technical Documents. Many design tools and links to additional references, may also be found at www.power.ti.com

- 1. Design and Application Guide for High Speed MOSFET Gate Drive Circuits, SEM 1400, 2001 Seminar Series

- 2. Designing Stable Control Loops, SEM 1400, 2001 Seminar Series

- 3. Additional PowerPAD<sup>TM</sup> information may be found in Applications Briefs SLMA002 and SLMA004

- 4. QFN/SON PCB Attachment, Texas Instruments Literature Number SLUA271, June 2002

www.ti.com

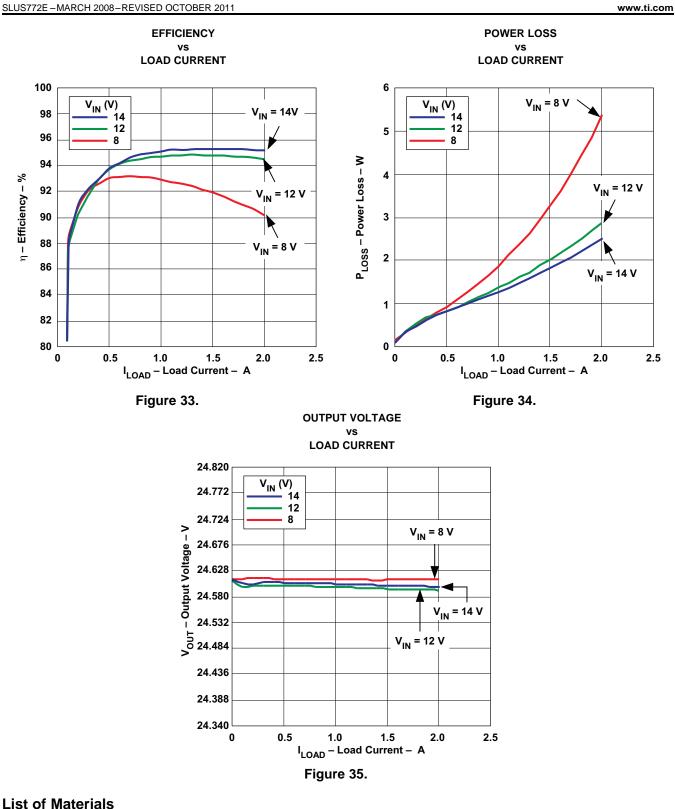

## **DESIGN EXAMPLE 1**

## 12-V to 24-V Non-Synchronous Boost Regulator

The following example illustrates the design process and component selection for a 12-V to 24-V non-synchronous boost regulator using the TPS40210 controller.

|                          | PARAMETER                          | CONDITIONS                                                | MIN  | NOM  | MAX  | UNIT      |

|--------------------------|------------------------------------|-----------------------------------------------------------|------|------|------|-----------|

| INPUT CH                 | ARACTERISTICS                      |                                                           | ·    |      |      |           |

| V <sub>IN</sub>          | Input voltage                      |                                                           | 8    | 12   | 14   | V         |

| I <sub>IN</sub>          | Input current                      |                                                           |      | 4.4  |      | •         |

|                          | No load input current              |                                                           |      |      | 0.05 | A         |

| V <sub>IN(UVLO)</sub>    | Input undervoltage lockout         |                                                           |      | 4.5  |      | V         |

| OUTPUT C                 | HARACTERISTICS                     |                                                           |      |      |      |           |

| V <sub>OUT</sub>         | Output voltage                     |                                                           | 23.5 | 24.0 | 24.5 | V         |

|                          | Line regulation                    |                                                           |      |      | 1%   |           |

|                          | Load regulation                    |                                                           |      |      | 1%   |           |

| V <sub>OUT(ripple)</sub> | Output voltage ripple              |                                                           |      |      | 500  | $mV_{PP}$ |

| I <sub>OUT</sub>         | Output current                     | $8 \text{ V} \leq \text{V}_{\text{IN}} \leq 14 \text{ V}$ | 0.1  | 1    | 2.0  | •         |

| I <sub>OCP</sub>         | Output overcurrent inception point |                                                           | 3.5  |      |      | A         |

|                          | Transient response                 |                                                           |      |      |      |           |

| ΔI                       | Load step                          |                                                           |      | 1    |      | А         |

|                          | Load slew rate                     |                                                           |      | 1    |      | A/µs      |

|                          | Overshoot threshold voltage        |                                                           |      | 500  |      | mV        |

|                          | Settling time                      |                                                           |      | 5    |      | ms        |

SLUS772E - MARCH 2008 - REVISED OCTOBER 2011

| Table 2. TPS40210 Design Example Specifications (continued) | inued) |

|-------------------------------------------------------------|--------|

|-------------------------------------------------------------|--------|

|                 | PARAMETER                   | CONDITIONS                                                          | MIN NOM MAX | UNIT |

|-----------------|-----------------------------|---------------------------------------------------------------------|-------------|------|

| SYSTEM          | M CHARACTERISTICS           |                                                                     |             |      |

| f <sub>SW</sub> | Switching frequency         |                                                                     | 600         | kHz  |

| η <sub>PK</sub> | Peak efficiency             | V <sub>IN</sub> = 12 V                                              | 95%         |      |

| η               | Full load efficiency        | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 2 A                      | 94%         |      |

| T <sub>OP</sub> | Operating temperature range | 8 V $\leq$ V <sub>IN</sub> $\leq$ 14 V, I <sub>OUT</sub> $\leq$ 2 A | 25          | °C   |

| MECHA           | NICAL DIMENSIONS            |                                                                     |             |      |

| W               | Width                       |                                                                     | 1.5         |      |

| L               | Length                      |                                                                     | 1.5         | in   |

| h               | Height                      |                                                                     | 0.5         |      |

## Step-By-Step Design Procedure

#### **Duty Cycle Estimation**

The duty cycle of the main switching MOSFET is estimated using Equation 32 and Equation 33.

$$D_{MIN} \approx \frac{V_{OUT} - V_{IN(max)} + V_{FD}}{V_{OUT} + V_{FD}} = \frac{24 V - 14 V + 0.5 V}{24 V + 0.5 V} = 42.9\%$$

$$D_{MAX} \approx \frac{V_{OUT} - V_{IN(min)} + V_{FD}}{V_{OUT} + V_{FD}} = \frac{24 V - 8 V + 0.5 V}{24 V + 0.5 V} = 67.3\%$$

(32)

Using an estimated forward drop ( $V_{FD}$ ) of 0.5 V for a schottky rectifier diode, the approximate duty cycle is 42.9% (minimum) to 67.3% (maximum).

#### **Inductor Selection**

The peak-to-peak ripple is chosen to be 30% of the maximum input current.

$$I_{\text{RIPPLE}(\text{max})} = 0.3 \times \frac{I_{\text{OUT}(\text{max})}}{1 - D_{\text{MIN}}} = 0.3 \times \frac{2}{1 - 0.429} = 1.05 \text{ A}$$

(34)

The minimum inductor size can be estimated using Equation 35.

$$L_{\text{MIN}} \approx \frac{V_{\text{IN}(\text{max})}}{I_{\text{RIPPLE}(\text{max})}} \times D_{\text{MIN}} \times \frac{1}{f_{\text{SW}}} = \frac{14 \text{ V}}{1.05 \text{ A}} \times 0.429 \times \frac{1}{600 \text{ kHz}} = 9.5 \,\mu\text{H}$$

(35)

The next higher standard inductor value of 10  $\mu$ H is selected. The ripple current for nominal and minimum V<sub>IN</sub> is estimated by Equation 36 and Equation 37.

$$I_{\text{RIPPLE}(V_{\text{in}}\text{typ})} \approx \frac{V_{\text{IN}}}{L} \times D \times \frac{1}{f_{\text{SW}}} = \frac{12V}{10\,\mu\text{H}} \times 0.50 \times \frac{1}{600\,\text{kHz}} = 1.02\,\text{A}$$

(36)

$$I_{\text{RIPPLE}(\text{Vinmin})} \approx \frac{V_{\text{IN}}}{L} \times D \times \frac{1}{f_{\text{SW}}} = \frac{8V}{10\,\mu\text{H}} \times 0.673 \times \frac{1}{600\,\text{kHz}} = 0.90\,\text{A}$$

(37)

The worst case peak-to-peak ripple current occurs at 50% duty cycle ( $V_{IN}$  = 12.25 V) and is estimated as 1.02 A. Worst case RMS current through the inductor is approximated by Equation 38.

$$I_{Lrms} = \sqrt{\left(I_{L(avg)}\right)^{2} + \left(\frac{1}{12}I_{RIPPLE}\right)^{2}} \approx \sqrt{\left(\frac{I_{OUT(max)}}{1 - D_{MAX}}\right)^{2} + \left(\frac{1}{12}I_{RIPPLE(VINmin)}\right)^{2}} = \sqrt{\left(\frac{2}{1 - 0.673}\right)^{2} + \left(\left(\frac{1}{12}\right) \times 0.90A\right)^{2}} = 6.13 \text{ Arms}$$

(38)

The worst case RMS inductor current is 6.13 Arms. The peak inductor current is estimated by Equation 39.

$$I_{\text{Lpeak}} \approx \frac{I_{\text{OUT(max)}}}{1 - D_{\text{MAX}}} + \binom{1}{2} I_{\text{RIPPLE(Vinmin)}} = \frac{2}{1 - 0.673} + \binom{1}{2} 0.90 = 6.57 \text{ A}$$

(39)

Copyright © 2008–2011, Texas Instruments Incorporated

A 10-µH inductor with a minimum RMS current rating of 6.13 A and minimum saturation current rating of 6.57 A must be selected. A TDK RLF12560T-100M-7R5 7.5-A 10-µH inductor is selected.

This inductor power dissipation is estimated by Equation 40.

$$P_{L} \approx \left(I_{Lrms}\right)^{2} \times DCR \tag{40}$$

The TDK RLF12560T-100M-7R5 12.4-mΩ DCR dissipates 466 mW of power.

#### **Rectifier Diode Selection**

A low forward voltage drop schottky diode is used as a rectifier diode to reduce its power dissipation and improve efficiency. Using 80% derating on  $V_{OUT}$  for ringing on the switch node, the rectifier diode minimum reverse break-down voltage is given by Equation 41.

$$V_{(BR)R(min)} \ge \frac{V_{OUT}}{0.8} = 1.25 \times V_{OUT} = 1.25 \times 24 \text{ V} = 30 \text{ V}$$

(41)

The diode must have reverse breakdown voltage greater than 30 V. The rectifier diode peak and average currents are estimated by Equation 42 and Equation 43.

$$I_{D(avg)} \approx I_{OUT(max)} = 2A$$

(42)

$$I_{D(peak)} = I_{L(peak)} = 6.57 A$$

(43)

The power dissipation in the diode is estimated by Equation 44.

$$P_{D(max)} \approx V_{FD} \times I_{D(avg)} = 0.5 V \times 2A = 1W$$

(44)

For this design, the maximum power dissipation is estimated as 1 W. Reviewing 30-V and 40-V schottky diodes, the MBRS340T3, 40-V, 3-A diode in an SMC package is selected. This diode has a forward voltage drop of 0.48-V at 6-A, so the conduction power dissipation is approximately 960 mW, less than half its rated power dissipation.

#### **Output Capacitor Selection**

Output capacitors must be selected to meet the required output ripple and transient specifications.

$$C_{OUT} = 8 \frac{I_{OUT} \times D}{V_{OUT(ripple)}} \times \frac{1}{f_{SW}} = 8 \left( \frac{2A \times 0.673}{500 \,\text{mV}} \right) \times \frac{1}{600 \,\text{kHz}} = 36 \,\mu\text{F}$$

$$ESR = \frac{7}{8} \times \frac{V_{OUT(ripple)}}{I_{L(peak)} - I_{OUT}} = \frac{7}{8} \times \frac{500 \,\text{mV}}{6.57 \,\text{A} - 2 \,\text{A}} = 96 \,\text{m}\Omega$$

$$(45)$$

A Panasonic EEEFC1V330P 35V 33- $\mu$ F, 120-m $\Omega$  bulk capacitor and a 6.8- $\mu$ F ceramic capacitor are selected to provide the required capacitance and ESR at the switching frequency. The combined capacitance of 39.8  $\mu$ F and ESR of 60 m $\Omega$  are used in compensation calculations.

#### **Input Capacitor Selection**

Since a boost converter has continuous input current, the input capacitor senses only the inductor ripple current. The input capacitor value can be calculated by Equation 47 and Equation 48.

$$C_{IN} > \frac{I_{RIPPLE}}{4 \times V_{IN(ripple)} \times f_{SW}} = \frac{1.02 \text{ A}}{4 \times 60 \text{ mV} \times 600 \text{ kHz}} = 7.1 \mu \text{F}$$

$$(47)$$

$$\mathsf{ESR} < \frac{\mathsf{v}_{\mathsf{IN}(\mathsf{ripple})}}{2 \times \mathsf{I}_{\mathsf{RIPPLE}}} = \frac{60 \, \mathsf{mV}}{2 \times 1.02 \, \mathsf{A}} = 29 \, \mathsf{m}\Omega \tag{48}$$

For this design to meet a maximum input ripple of 60 mV (1/2% of V<sub>IN</sub> nominal), a minimum 7.1- $\mu$ F input capacitor with ESR less than 29 m $\Omega$  is needed. A 10- $\mu$ F X7R ceramic capacitor is selected.

28 Submit Documentation Feedback

**EXAS**

www.ti.com

#### **Current Sense and Current Limit**

The maximum allowable current sense resistor value is limited by both the current limit and sub-harmonic stability. These two limitations are given by Equation 49 and Equation 50.

$$R_{ISNS} < \frac{V_{ISNS(OC)MIN}}{1.1 \times (l_{L(peak)} + l_{Drive})} = \frac{120 \text{ mV}}{1.1 \times (6.57 \text{ A} + 0.50 \text{ A})} = 15.4 \text{ m}\Omega$$

$$R_{ISNS} < \frac{V_{IN(MAX)} \times L \times f_{SW}}{60 \times (V_{OUT} + V_{FD} - V_{IN})} = \frac{14 \text{ V} \times 10 \,\mu\text{H} \times 600 \text{ kHz}}{60 \times (24 \text{ V} + 0.48 \text{ V} - 14 \text{ V})} = 134 \text{ m}\Omega$$

(49)

(50)

With 10% margin on the current limit trip point (the 1.1 factor) and assuming a maximum gate drive current of 500 mA, the current limit requires a resistor less than 15.4 m $\Omega$  and stability requires a sense resistor less than 134 m $\Omega$ . A 10-m $\Omega$  resistor is selected. Approximately 2-m $\Omega$  of routing resistance is added in compensation calculations.

The power dissipation in R<sub>ISNS</sub> is calculated by Equation 51.

$$P_{R_{ISNS}} = (I_{LRMS})^2 \cdot R_{ISNS} \cdot D$$

(51)

At maximum duty cycle, this is 0.253 W.

#### **Current Sense Filter**

To remove switching noise from the current sense, an R-C filter is placed between the current sense resistor and the ISNS pin. A resistor with a value between 1 k $\Omega$  and 5 k $\Omega$  is selected and a capacitor value is calculated by Equation 52.

$$C_{IFLT} = \frac{0.1 \times D_{MIN}}{f_{SW} \times R_{IFLT}} = \frac{0.1 \times 0.429}{600 \,\text{kHz} \times 1 \text{k}\Omega} = 71\text{pF}$$

(52)

For a 1-k $\Omega$  filter resistor, 71 pF is calculated and a 100-pF capacitor is selected.

#### Switching MOSFET Selection

The TPS40210 drives a ground referenced N-channel FET. The R<sub>DS(on)</sub> and gate charge are estimated based on the desired efficiency target.

$$\mathsf{P}_{\mathsf{DISS}(\mathsf{total})} \approx \mathsf{P}_{\mathsf{OUT}} \times \left(\frac{1}{\eta} - 1\right) = \mathsf{V}_{\mathsf{OUT}} \times \mathsf{I}_{\mathsf{OUT}} \times \left(\frac{1}{\eta} - 1\right) = 24 \,\mathsf{V} \times 2 \,\mathsf{A} \times \left(\frac{1}{0.95} - 1\right) = 2.526 \,\mathsf{W} \tag{53}$$

For a target of 95% efficiency with a 24 V Input voltage at 2 A, maximum power dissipation is limited to 2.526 W. The main power dissipating devices are the MOSFET, inductor, diode, current sense resistor and the integrated circuit, the TPS40210.

$$P_{\text{FET}} < P_{\text{DISS}(\text{total})} - P_{\text{L}} - P_{\text{D}} - P_{\text{Risns}} - V_{\text{IN}(\text{max})} \times I_{\text{VDD}(\text{max})}$$

(54)

This leaves 812 mW of power dissipation for the MOSFET. This can likely cause an SO-8 MOSFET to get too hot, so power dissipation is limited to 500 mW. Allowing half for conduction and half for switching losses, we can determine a target  $R_{DS(on)}$  and  $Q_{GS}$  for the MOSFET by Equation 55 and Equation 56.

$$Q_{GS} < \frac{3 \times P_{FET} \times I_{DRIVE}}{2 \times V_{OUT} \times I_{OUT} \times f_{SW}} = \frac{3 \times 0.50 \text{ W} \times 0.50 \text{ A}}{2 \times 24 \text{ V} \times 2A \times 600 \text{ kHz}} = 13.0 \text{ nC}$$

(55)

A target MOSFET gate-to-source charge of less than 13.0 nC is calculated to limit the switching losses to less than 250 mW.

$$R_{DS(on)} < \frac{P_{FET}}{2 \times (l_{RMS})^2 \times D} = \frac{0.50 \,\text{W}}{2 \times 6.13^2 \times 0.673} = 9.9 \,\text{m}\Omega$$

(56)

A target MOSFET  $R_{DS(on)}$  of 9.9 m $\Omega$  is calculated to limit the conduction losses to less than 250 mW. Reviewing 30-V and 40-V MOSFETs, an Si4386DY 9-m $\Omega$  MOSFET is selected. A gate resistor was added per Equation 30. The maximum gate charge at V<sub>as</sub>=8 V for the Si4386DY is 33.2 nC, this implies  $R_G = 3.3 \Omega$ .

Copyright © 2008–2011, Texas Instruments Incorporated

#### Feedback Divider Resistors

The primary feedback divider resistor (R<sub>FB</sub>) from V<sub>OUT</sub> to FB should be selected between 10-k $\Omega$  and 100-k $\Omega$  to maintain a balance between power dissipation and noise sensitivity. For a 24-V output a high feedback resistance is desirable to limit power dissipation so R<sub>FB</sub> = 51.1 k $\Omega$  is selected.

$$R_{BIAS} = \frac{V_{FB} \times R_{FB}}{V_{OUT} - V_{FB}} = \frac{0.700 \text{ V} \times 51.1 \text{k}\Omega}{24 \text{ V} - 0.700 \text{ V}} = 1.53 \text{k}\Omega$$

$R_{BIAS} = 1.50 \text{ k}\Omega$  is selected.

#### **Error Amplifier Compensation**

While current mode control typically only requires Type II compensation, it is desirable to layout for Type III compensation to increase flexibility during design and development.

Current mode control boost converters have higher gain with higher output impedance, so it is necessary to calculate the control loop gain at the maximum output impedance, estimated by Equation 58.

$$R_{OUT(max)} = \frac{V_{OUT}}{I_{OUT(min)}} = \frac{24 V}{0.1 A} = 240 \Omega$$

(58)

The transconductance of the TPS40210 current mode control can be estimated by Equation 59.

$$g_{M} = \frac{0.13 \times \sqrt{L \times \frac{f_{SW}}{R_{OUT}}}}{\left(R_{ISNS}\right)^{2} \times \left(120 \times R_{ISNS} + L \times f_{SW}\right)} = \frac{0.13 \times \sqrt{10 \,\mu H \times \frac{600 \,kHz}{240 \,\Omega}}}{\left(12 \,m \Omega\right)^{2} \times \left(120 \times 12 \,m \Omega + 10 \,\mu H \times 600 \,kHz\right)} = 19.2 \,\frac{A}{\sqrt{10}}$$

(59)

The maximum output impedance  $Z_{OUT}$ , can be estimated by Equation 60.

$$|Z_{OUT}(f)| = R_{OUT} \times \sqrt{\frac{\left(1 + \left(2\pi \times f \times R_{ESR} \times C_{OUT}\right)^{2}\right)}{1 + \left(\left(R_{OUT}\right)^{2} + 2 \times R_{OUT} \times R_{ESR} + \left(R_{ESR}\right)^{2}\right) \times \left(2\pi \times f \times C_{OUT}\right)^{2}}}$$

$$|Z_{OUT}(f_{L})| = 240\Omega \times \sqrt{\frac{\left(1 + \left(2\pi \times 30 \text{ kHz} \times 60 \text{ m}\Omega \times 39.8 \, \mu\text{F}\right)^{2}\right)}{1 + \left(\left(240\Omega\right)^{2} + 2 \times 240\Omega \times 60 \text{ m}\Omega + \left(60\text{ m}\Omega\right)^{2}\right) \times \left(2\pi \times 30 \text{ kHz} \times 39.8 \, \mu\text{F}\right)^{2}}} = 0.146\Omega$$

(60)

(61)

At the desired crossover frequency ( $f_L$ ) of 30 kHz,  $Z_{OUT}$  becomes 0.146 $\Omega$ .

The modulator gain at the desired cross-over can be estimated by Equation 62.

$$|K_{CO}| = g_M \times |Z_{OUT}(f_{CO})| = 19.2 \frac{A}{V} \times 0.146 \Omega = 2.80$$

(62)

The feedback compensation network needs to be designed to provide an inverse gain at the cross-over frequency for unity loop gain. This sets the compensation mid-band gain at a value calculated in Equation 63.

$$K_{\text{COMP}} = \frac{1}{|K_{\text{CO}}|} = \frac{1}{2.80} = 0.357$$

(63)

To set the mid-band gain of the error amplifier to K<sub>COMP</sub> use Equation 64.

$$R4 = R7 \times K_{COMP} = \frac{R7}{|K_{CO}|} = \frac{51.1 k\Omega}{2.80} = 18.2 k\Omega$$

(64)

$R4 = 18.7 \text{ k}\Omega$  selected.

Place the zero at 1/10th of the desired cross-over frequency.

www.ti.com

$$C2 = \frac{10}{2\pi \times f_{L} \times R4} = \frac{10}{2\pi \times 30 \,\text{kHz} \times 18.7 \,\text{k}\Omega} = 2837 \,\text{pF}$$

(65)

C2 = 2200 pF selected.

Place a high-frequency pole at about 5 times the desired cross-over frequency and less than one-half the unity gain bandwidth of the error amplifier:

$$C4 \approx \frac{1}{10\pi \times f_{L} \times R4} = \frac{1}{10\pi \times 30 \text{ kHz} \times 18.7 \text{ k}\Omega} = 56.74 \text{ pF}$$

$$C4 > \frac{1}{\pi \times \text{GBW} \times R4} = \frac{1}{\pi \times 1.5 \text{ MHz} \times 18.7 \text{ k}\Omega} = 11.35 \text{ pF}$$

(66)

(67)

C4 = 47 pF selected.

#### **R-C Oscillator**