# SX1701B – Datasheet

## **Highly linear wideband LNA**

# Multi-channel, single-ended to differential conversion

#### **GENERAL DESCRIPTION**

The SX1701B is an integrated LNA operating over a wide frequency range from 40 MHz to 2.5 GHz. It is optimized for high OIP2 and OIP3 with minimum current consumption. It also performs a single-ended to differential conversion.

Two independent output channels are available and the gain of each may be adjusted independently.

#### **APPLICATIONS**

- Digital Set Top Boxes (Satellite and Terrestrial)

- CATV Distribution Systems

- Active Splitter

- Data Communications Systems

- Active Balun

#### **KEY PRODUCT FEATURES**

- Single-ended input / Dual differential outputs

- Independent programmable gain for each channel: 6, 12 and 18 dB

- High Linearity: OIP2 of 57 dBm and OIP3 of 22 dBm

- Noise Figure of 7 dB

- 75 Ω Input impedance

- $100 \Omega$  differential output impedance

- Current consumption of 130 mA with one channel enabled

- ESD protection (Normal ESD handling procedures should be observed)

- Very small package: MLPQ-16, 4 mm x 4 mm (equivalent to QFN-16, 4 mm x 4 mm)

#### ORDERING INFORMATION

| Part number   | Temp  | erature range | Package              |

|---------------|-------|---------------|----------------------|

| SX1701BI085TR | T -40 | °C to +85 °C  | Lead Free<br>MLPQ-16 |

Note: This device is WEEE and RoHS compliant.

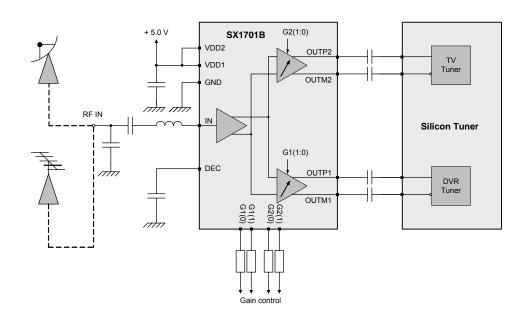

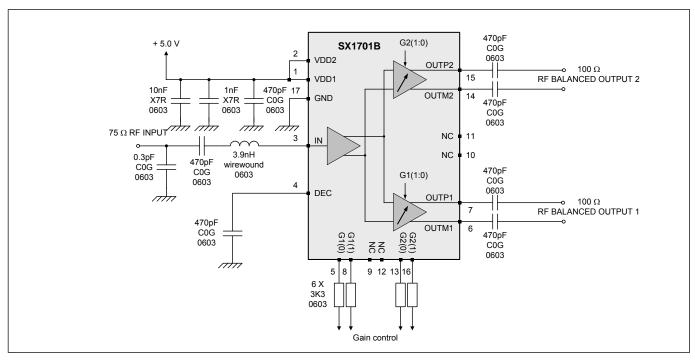

#### TYPICAL APPLICATION

### **TABLE OF CONTENTS**

| 1     | Simplified Block Diagram                                                                               |    |

|-------|--------------------------------------------------------------------------------------------------------|----|

| 2     | Simplified Block DiagramPin Description                                                                |    |

| 2.1.1 | Pin Connections                                                                                        | _  |

| 2.1.2 | Gain Control Pins                                                                                      |    |

| 3     | Electrical Characteristics                                                                             | 5  |

| 3.1   | Absolute Maximum Ratings                                                                               |    |

| 3.2   | Specifications                                                                                         | 5  |

| 3.2.1 | Operating Range                                                                                        | 5  |

| 3.2.2 | Operating Range  Electrical Specifications  Typical Operating Characteristics  Application Information | 6  |

| 3.3   | Typical Operating Characteristics                                                                      |    |

| 4     | Application Information                                                                                | ç  |

| 5     | Application Example                                                                                    | 10 |

| 5.1   | Single-Ended Input to 1 Differential Outputs with Loop-through Single-Ended OUTPUT                     |    |

| 6     | Package Outline Drawing                                                                                |    |

| 7     | Marking Information                                                                                    |    |

| 8     | Land Pattern Drawing                                                                                   |    |

|       |                                                                                                        |    |

#### 1 SIMPLIFIED BLOCK DIAGRAM

The simplified block diagram of the SX1701B is illustrated below in Figure 1.

The amplifier comprises two main stages. The first stage is common to both channels and performs the single-ended to differential conversion. The second stage, duplicated for both channels, is implemented as two cascaded stages and performs independently the gain control for each channel.

Figure 1. Simplified block diagram of the SX1701B.

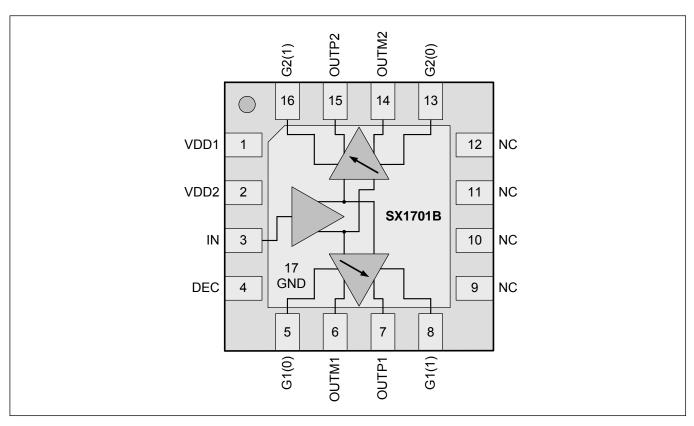

#### **2 PIN DESCRIPTION**

#### 2.1.1 Pin Connections

The pin description of the SX1701B is given in Table 1.

| Number | Name  | Туре   | Description                     |

|--------|-------|--------|---------------------------------|

| 1      | VDD1  | Input  | Supply voltage                  |

| 2      | VDD2  | Input  | Supply voltage                  |

| 3      | IN    | Input  | LNA input                       |

| 4      | DEC   | Input  | Decoupling capacitor            |

| 5      | G1(0) | Input  | Control of the 1st channel      |

| 6      | OUTM1 | Output | Differential output 1st Channel |

| 7      | OUTP1 | Output | Differential output 1st Channel |

| 8      | G1(1) | Input  | Control of the 1st channel      |

| 9      | NC    | None   | No Connect                      |

| 10     | NC    | None   | No Connect                      |

| 11     | NC    | None   | No Connect                      |

| 12     | NC    | None   | No Connect                      |

| 13     | G2(0) | Input  | Control of the 3rd channel      |

| 14     | OUTM2 | Output | Differential output 3rd Channel |

| 15     | OUTP2 | Output | Differential output 3rd Channel |

| 16     | G2(1) | Input  | Control of the 3rd channel      |

| 17     | GND   | Input  | Ground pad                      |

Table 1. Pin description.

#### 2.1.2 Gain Control Pins

The gain setting for each channel is given in Table 2.

| Gi(1:0) | Description                                          |

|---------|------------------------------------------------------|

| 0 0     | Channel OFF (default value set by pull-down devices) |

| 0 1     | Channel ON, G = 6 dB                                 |

| 10      | Channel ON, G = 12 dB                                |

| 11      | Channel ON, G = 18 dB                                |

Table 2. Channel gain setting.

<u>Note:</u> For applications that require less than 3 outputs, the unused differential outputs and the corresponding channel gain setting pins can be left floating. The default channel gain setting is "channel OFF [0:0]" (set by internal pull down resistors).

#### 3 ELECTRICAL CHARACTERISTICS

#### 3.1 ABSOLUTE MAXIMUM RATINGS

Stresses above the values listed below may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Symbol | Description          | Min. | Max. | Unit |

|--------|----------------------|------|------|------|

| VDDmr  | Supply voltage       | -0.5 | 5.5  | V    |

| Tmr    | Storage temperature  | -55  | +125 | °C   |

| Tjmr   | Junction Temperature | -    | +125 | °C   |

| Pmr    | Input level          | -    | 0    | dBm  |

Table 3. Absolute Maximum ratings.

#### 3.2 SPECIFICATIONS

#### 3.2.1 Operating Range

| Symbol | Description    | Min. | Max. | Unit |

|--------|----------------|------|------|------|

| VDDop  | Supply voltage | 4.5  | 5.3  | V    |

| Trop   | Temperature    | -40  | +85  | °C   |

Table 4. Operating Range.

#### 3.2.2 Electrical Specifications

The table below gives the electrical specifications of the LNA under the following conditions: VDD = 5.0 V, Temperature = 25 °C, Input frequency = 1 GHz, Gain = 18 dB, Pin = -20dBm, unless otherwise specified.

| Symbol   | Description                                                 | Condition                               |                                   | Min  | Тур | Max | Unit  |

|----------|-------------------------------------------------------------|-----------------------------------------|-----------------------------------|------|-----|-----|-------|

| RIN      | Input impedance                                             | Single-ended                            | Single-ended                      |      | 75  | -   | Ω     |

| ROUT     | Output impedance                                            | Differential                            |                                   | -    | 100 | -   | Ω     |

| FR       | Frequency range                                             |                                         |                                   | 0.04 | -   | 2.5 | GHz   |

| G        | Gain                                                        | S <sub>21</sub>                         |                                   | -    | 6   | -   |       |

|          |                                                             | Programmable                            |                                   | -    | 12  | -   | dB    |

|          |                                                             |                                         |                                   | -    | 18  | -   |       |

| GFLAT    | Gain Flatness                                               | Rs = 75 Ω, max                          | imum gain                         | -    | ±1  | -   | dB    |

| NF       | Noise figure                                                | Rs = 75 Ω                               | G = 18 dB                         | -    | 7   | -   |       |

|          |                                                             |                                         | G = 12 dB                         | -    | 9   | -   | dB    |

|          |                                                             |                                         | G = 6 dB                          | -    | 13  | -   |       |

| P1dB     | Output P1dB compression point                               |                                         |                                   | -    | 13  | -   | dBm   |

| OIP3     | Output 3 <sup>rd</sup> order intermodulation (differential) | f <sub>1</sub> = 1.0 GHz                | G = 18 dB                         | -    | 22  | -   |       |

|          |                                                             | f <sub>2</sub> = 1.1 GHz                | G = 12 dB                         | -    | 21  | -   | dBm   |

|          |                                                             |                                         | G = 6 dB                          | -    | 19  | -   |       |

| OIP2     | Output 2 <sup>nd</sup> order intermodulation (differential) | f <sub>1</sub> = 1.0 GHz                | @ f <sub>1</sub> + f <sub>2</sub> | -    | 53  | -   | dBm   |

|          |                                                             | f <sub>2</sub> = 1.1 GHz                | @ f <sub>2</sub> - f <sub>1</sub> | -    | 57  | -   | UDIII |

| IDD      | Current consumption                                         | 1 channel enabled<br>2 channels enabled |                                   | -    | 130 | -   |       |

|          |                                                             |                                         |                                   | -    | 200 | -   | mA    |

|          |                                                             | 3 channels enabled                      |                                   | -    | 270 | -   |       |

| IRL      | Input Return loss                                           | -20.log(ls <sub>11</sub> l)             |                                   | -    | 15  |     | dB    |

| ORL      | Output Return loss                                          | -20.log(ls iil)                         |                                   | -    | 20  |     | dB    |

| ISOUTIN  | RF out to RF in Isolation                                   | -20.log(ls <sub>1 i</sub> l)            |                                   | 50   | -   | -   | dB    |

| ISOUTOUT | RF out i to RF out j isolation                              | -20.log(ls <sub>i j</sub> l)            | G = 18 dB                         | -    | 25  | -   |       |

|          |                                                             |                                         | G = 12 dB                         | -    | 30  | -   | dB    |

|          |                                                             |                                         | G = 6 dB                          | -    | 35  | 1   |       |

| ISOUTDWN | RF in to RF out isolation in shut down mode                 | -20.log(ls <sub>i1</sub> l)             |                                   | -    | 50  | 1   | dB    |

| CMRR     | Common mode rejection at the output                         |                                         |                                   | -    | 20  | -   | dB    |

| VESD     | ESD robustness on all pins                                  | НВМ                                     |                                   | 3    | -   | -   | kV    |

Table 5. Electrical Specifications.

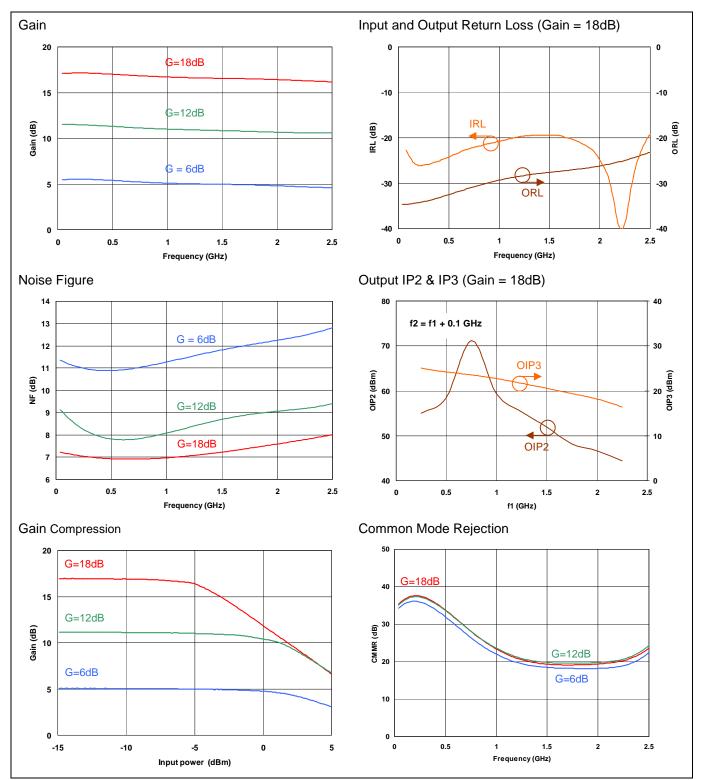

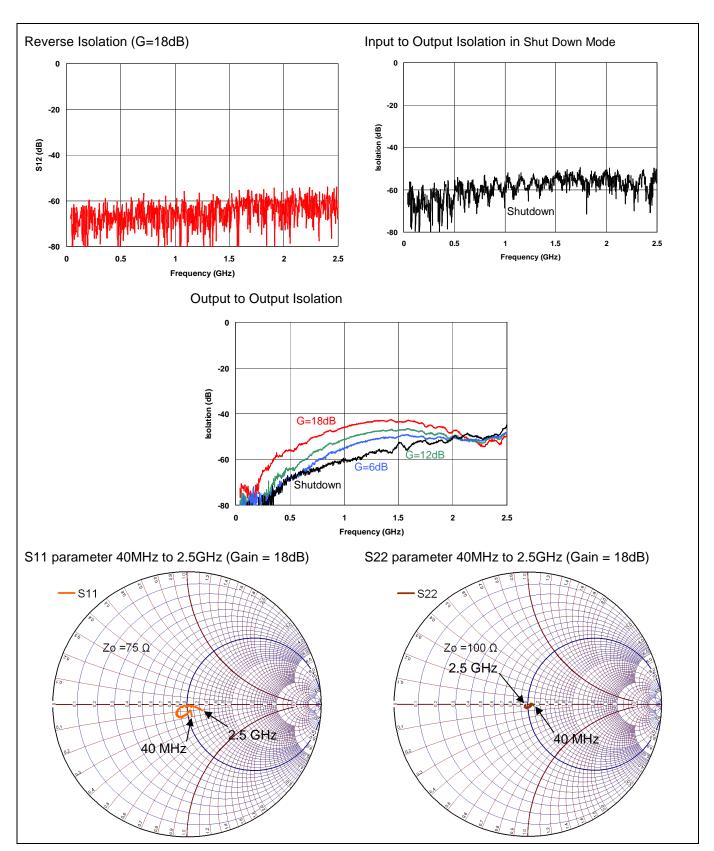

#### 3.3 TYPICAL OPERATING CHARACTERISTICS

The curves below give the typical RF performances of the LNA under the following conditions: VDD = 5.0 V, Temperature = 25  $^{\circ}$ C, Z  $^{\circ}$ Source = 75 $^{\circ}$ C, Z  $^{\circ}$ Load = 100 $^{\circ}$ C differential, Frequency range = 40 MHz to 2.5 GHz, input matching network according to application schematics of figure 4.

Figure 2. Typical Operating Characteristics Curves.

Figure 3. Typical Operating Characteristics Curves.

#### 4 APPLICATION INFORMATION

Figure 4, below, shows the recommended board schematic. Typical component values are shown and are subject to change depending on the PCB layout and material used. Please refer to the Semtech SX1701B reference design at <a href="https://www.semtech.com">www.semtech.com</a>.

Figure 4. Application board schematic.

#### 5 APPLICATION EXAMPLE

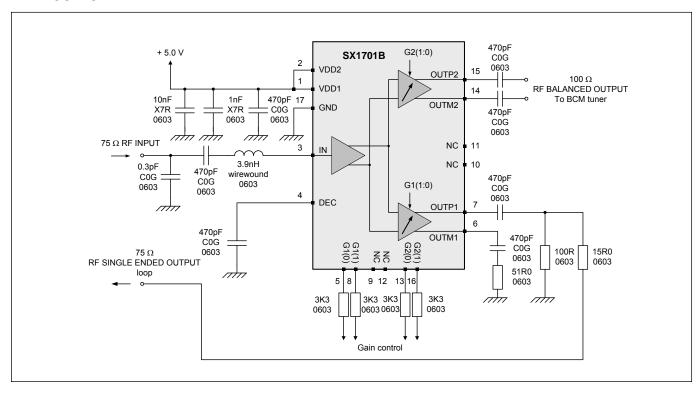

Although intended for differential output operation, the SX1701B may be used for the single-ended output configuration as shown in Figure 5. Note that some degradation in device performance may be experienced, including a 3 dB reduction in gain.

# 5.1 SINGLE-ENDED INPUT TO 1 DIFFERENTIAL OUTPUTS WITH LOOP-THROUGH SINGLE-ENDED OUTPUT

Figure 5. Differential output with loop-through.

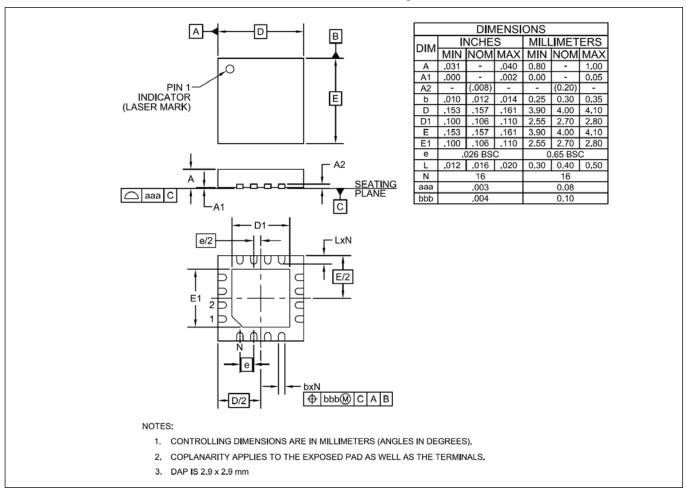

#### 6 PACKAGE OUTLINE DRAWING

SX1701B is assembled in a MLPQ-16, 4 mm x 4 mm as shown in Figure 6.

Figure 6. Package outline drawing.

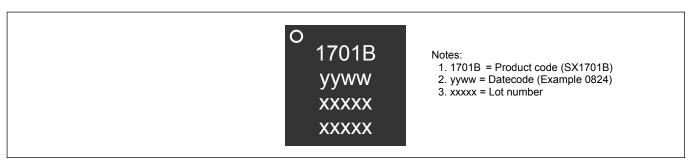

#### 7 MARKING INFORMATION

Figure 7. Marking information.

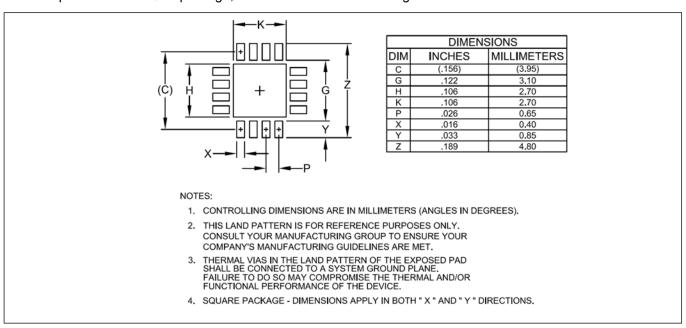

#### 8 LAND PATTERN DRAWING

The land pattern of MLPQ-16 package, 4 mm x 4 mm is shown in Figure 8.

Figure 8. Land pattern drawing.

#### © Semtech 2008

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights. Semtech assumes no responsibility or liability whatsoever for any failure or unexpected operation resulting from misuse, neglect improper installation, repair or improper handling or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified range.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

#### **Contact Information**

Semtech Corporation

Advanced Communications and Sensing Products Division

200 Flynn Road, Camarillo, CA 93012

Phone (805) 498-2111 Fax: (805) 498-3804