# **OMAP3530/25/15/03 Applications Processor Silicon Revisions 3.1.2, 3.1, 3.0, 2.1, and 2.0**

### Silicon Errata

Literature Number: SPRZ278F February 2008–Revised October 2010

### **Contents**

| 1 | Introdu | ction     |                                                                                                                       | 5  |

|---|---------|-----------|-----------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1     | OMAP3     | 5x Device and Development Support Tool Nomenclature                                                                   | 5  |

|   | 1.2     | Revision  | n Identification                                                                                                      | 6  |

| 2 | Silicon | Revisio   | n 3.1.2 Usage Notes and Known Design Exceptions to Functional                                                         |    |

|   | Specifi | cations   |                                                                                                                       | 7  |

|   | 2.1     | Usage N   | Notes for Silicon Revision 3.1.2                                                                                      | 7  |

|   |         | 2.1.1     | Cortex-A8 Errata List                                                                                                 | 7  |

|   |         | 2.1.2     | Performance Limitation On LCD Read/Write Access Through RFBI L4 Port                                                  | 7  |

|   |         | 2.1.3     | IVA2: IDLE Instruction Must be Executed From L1P or L2 SRAM Under Hardware Emulation (OMAP3530/25 only)               | 8  |

|   |         | 2.1.4     | Domain Woken Up by Wake-up Dependency Cannot Transition to Inactive State                                             | 9  |

|   |         | 2.1.5     | VENC: Last Data Line Missing in PAL                                                                                   | 9  |

|   |         | 2.1.6     | Observability Signals Not Functional in OFF Mode                                                                      |    |

|   |         | 2.1.7     | Constraints on Module Clocks When Using DVFS                                                                          | 9  |

|   |         | 2.1.8     | Retention Voltage Not Supported                                                                                       | 9  |

|   |         | 2.1.9     | UART: Cannot Acknowledge Idle Requests in Smartidle Mode When Configured for DMA Operations                           | 10 |

|   |         | 2.1.10    | Unexpected RFBI Latency for High Frame Rate                                                                           | 10 |

|   |         | 2.1.11    | GPIO Drives Random Values When Device Comes Back from OFF Mode                                                        | 10 |

|   |         | 2.1.12    | Access to IVA Boot ROM at OPP1 Is no Longer Supported                                                                 | 11 |

|   |         | 2.1.13    | Maximum 12 bits Output (1 bit sign + 11 bits of value) Is Supported on CAVLD of iVLCD                                 | 11 |

|   |         | 2.1.14    | Maximum Pixel Rate on Resizer With A-Law Decompression and Horizontal Zoom Greater than                               |    |

|   |         | 2.1.15    | Extra Power Consumption at vdds_mmc1/vdds_sim in Device Off Mode                                                      |    |

|   |         | 2.1.16    | Extra Power Consumed When Repeated Start Operation Mode Is Enabled on I2C Interface Dedicated for Smart Reflex (I2C4) | 12 |

|   |         | 2.1.17    | OMAP HS Devices Are Not Recovering From Warm Reset While in OFF Mode                                                  | 12 |

|   |         | 2.1.18    | DPLL3 Recall and Long Relock Time                                                                                     | 12 |

|   |         | 2.1.19    | Transfer of Multiple Command Packets Coming from L4 Interconnect During a Blanking Period i Interleaving Mode         |    |

|   |         | 2.1.20    | Downscaling limitations                                                                                               | 13 |

|   | 2.2     | Silicon F | Revision 3.1.2 Known Design Exceptions to Functional Specifications                                                   | 15 |

| 3 |         |           | n 3.1 Usage Notes and Known Design Exceptions to Functional                                                           | 20 |

|   | 3.1     | Usage N   | Notes for Silicon Revision 3.1                                                                                        | 20 |

|   | 3.2     |           | Revision 3.1 Known Design Exceptions to Functional Specifications                                                     |    |

| 4 |         |           | n 3.0 Usage Notes and Known Design Exceptions to Functional                                                           | 22 |

|   | 4.1     | Usage N   | Notes for Silicon Revision 3.0                                                                                        | 22 |

|   |         | 4.1.1     | Display Controller Subsystem (DSS): Limitations Exist When Generating Horizontal and Vertical                         |    |

|   |         | 4.1.2     | Camera ISP: IIR Filters in Auto Focus (AF) Engine Should Only Be Used for Auto-Focus 1                                |    |

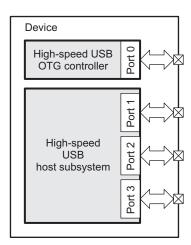

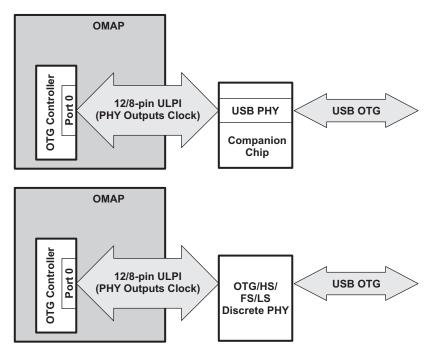

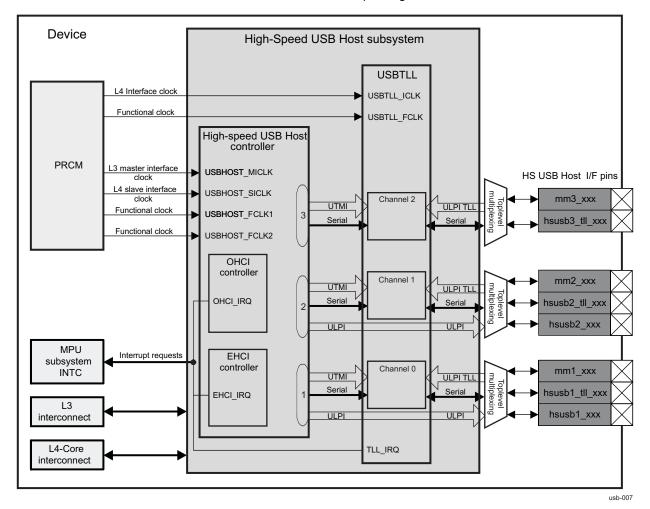

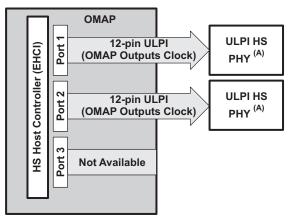

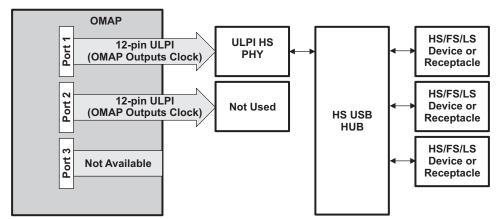

|   |         | 4.1.3     | High-Speed USB Host Subsystem: Some Limitations Exist When Connecting to External Device                              | s  |

|   | 4.2     | Silicon F | Revision 3.0 Known Design Exceptions to Functional Specifications                                                     | 26 |

| 5     | Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications |                                                                           |     |

|-------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|

|       | <b>5</b> .1                                                                               | Usage Notes for Silicon Revision 2.1                                      |     |

|       | 5.2                                                                                       | Silicon Revision 2.1 Known Design Exceptions to Functional Specifications | 132 |

| 6     | Silicon Revision 2.0 Usage Notes and Known Design Exceptions to Functional Specifications |                                                                           |     |

|       | 6.1                                                                                       | Usage Notes for Silicon Revision 2.0                                      | 140 |

|       | 6.2                                                                                       | Silicon Revision 2.0 Known Design Exceptions to Functional Specifications | 140 |

| Apper | ndix A                                                                                    | Revision History                                                          | 153 |

## OMAP3530/25/15/03 Applications Processor Silicon Revision 3.1.2

#### 1 Introduction

This document describes the known exceptions to the functional specifications for the OMAP3530, OMAP3525, OMAP3515, and OMAP3503 applications processors. [See the *OMAP3530/25 Applications Processor Data Manual* (literature number <a href="SPRS507">SPRS507</a>) and the *OMAP3515/03 Applications Processor Data Manual* (literature number <a href="SPRS505">SPRS505</a>)].

For additional information, see the latest version of the *OMAP35x Technical Reference Manual* (literature number SPRUF98).

The advisory numbers in the document are not sequential. Some advisory numbers have been moved to the next revision. When items are moved, the remaining advisory numbers are not resequenced.

This document also contains "Usage Notes." Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### 1.1 OMAP35x Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all OMAP processors and support tools. Each commercial OMAP platform member has one of three prefixes: X, P, or null (no prefix). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMDX) through fully qualified production devices/tools (TMDS).

Device development evolutionary flow:

X Experimental device that is not necessarily representative of the final device's electrical

specifications

P Final silicon die that conforms to the device's electrical specifications but has not

completed quality and reliability verification

**NULL** Fully-qualified production device

Support tool development evolutionary flow:

**TMDX** Development-support product that has not yet completed Texas Instruments internal

qualification testing

**TMDS** Fully-qualified development-support product

X and P devices and TMDX development-support tools are shipped against the following disclaimer: "Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

Introduction www.ti.com

#### 1.2 Revision Identification

The device revision can be determined by the symbols marked on the top of the package. Figure 1 provides an example of the OMAP35x Applications Processor device markings.

Figure 1. Example, Device Revision Codes for OMAP35x Applications Processor

#### NOTES:

- (A) Non-qualified devices are marked with the letters "X" or "P" at the beginning of the device name, while qualified devices have a "blank" at the beginning of the device name.

- (B) "#" denotes an alphanumeric character.

- (C) On some "TMX" devices, the device speed may not be shown.

Silicon revision is identified by a code marked on the package. The code is of the format X3530xCBB, where "x" denotes the silicon revision. On TMX devices, if x is"C", then the silicon is revision 3.0. Table 1 and Table 2 list the information associated with each silicon revision on TMX devices.

| DEVICE REVISION CODE | SILICON REVISION | COMMENTS                                             |

|----------------------|------------------|------------------------------------------------------|

| E                    | 3.1.2            | Silicon revision 3.1.2 (also referred to as ES3.1.2) |

| D                    | 3.1              | Silicon revision 3.1 (also referred to as ES3.1)     |

| С                    | 3.0              | Silicon revision 3.0 (also referred to as ES3.0)     |

| В                    | 2.1              | Silicon revision 2.1 (also referred to as ES2.1)     |

Table 1. OMAP35x Applications Processor Revision Codes

Each silicon revision uses a specific revision of the C64x+ CPU, the C64x+ Megamodule, as well as the ARM Cortex-A8 processor. Table 2 lists the C64x+ CPU and C64x+ Megamodule revision associated with each silicon revision. The C64x+ CPU revision can be read from the REVISION\_ID field of the CPU Control Status Register (CSR). The C64x+ Megamodule revision can be read from the REVISION field of the Megamodule Revision ID register (MM\_REVID) located at address IVA2.2 subsystem memory address 0181 2000h. The ARM Cortex-A8 variant and revision can be read from the Main ID Register.

The ROM code revision can be read from base address 4001 BFFCh. The ROM code version consists of two decimal numbers: major and minor. The major number is always 14, minor number counts ROM code version. The ROM code version is coded as hexadecimal readable values, e.g. ROM version 14.04 will be coded as 0000 1404h. Table 2 shows the ROM code revision for each silicon revision of the device.

#### Table 2. Silicon Revision Variables

| SILICON<br>REVISION | C64X+ CPU<br>REVISION             | C64X+ MEGAMODULE<br>REVISION | ARM CORTEX-A8<br>VARIANT/REVISION | ROM<br>REVISION |

|---------------------|-----------------------------------|------------------------------|-----------------------------------|-----------------|

| 3.1.2               | CPU_ID = 10h<br>REVISION_ID = 02h | MM_REVID[REVISION] = 0h      | r1p7                              | 14.04           |

| 3.1                 | CPU_ID = 10h<br>REVISION_ID = 02h | MM_REVID[REVISION] = 0h      | r1p3                              | 14.04           |

| 3.0                 | CPU_ID = 10h<br>REVISION_ID = 02h | MM_REVID[REVISION] = 0h      | r1p3                              | 14.04           |

| 2.1                 | CPU_ID = 10h<br>REVISION_ID = 02h | MM_REVID[REVISION] = 0h      | r1p2                              | 14.04           |

| 2.0                 | CPU_ID = 10h<br>REVISION_ID = 02h | MM_REVID[REVISION] = 0h      | r1p1                              | 14.04           |

### 2 Silicon Revision 3.1.2 Usage Notes and Known Design Exceptions to Functional Specifications

#### 2.1 Usage Notes for Silicon Revision 3.1.2

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data manual), and the behaviors they describe will not be altered in future silicon revisions.

**Note:** The peripherals supported on the various OMAP35x Application Processors are different. The user should only refer to usage notes and advisories pertaining to features supported on the specific device. For a complete list of the supported features of the OMAP35x Application Processors, see the device-specific data manuals.

#### 2.1.1 Cortex-A8 Errata List

The OMAP3530/25/15/03 Applications Processor Silicon Revisions 3.1.2, 3.1, 3.0, 2.1, and 2.0 Silicon Errata does not cover the advisories associated with the Cortex-A8 processor. For a list of the advisories associated with each version of the Cortex-A8 processor, contact your TI representative for a copy of the ARM Core Cortex-A8 (AT400/AT401) Errata Notice. See Table 2 to determine which version of the Cortex-A8 processor is included in each OMAP35x silicon revision.

#### 2.1.2 Performance Limitation On LCD Read/Write Access Through RFBI L4 Port

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, back-to-back accesses for both *Read* and *Write* to the LCD through the L4 interconnect interface of the RFBI module are not supported. A penalty of 1 L4 clock cycle between two consecutive accesses exists.

Read access to the LCD through the RFBI L4 port: The data of a *Read* access is sent back to the initiator of the access only at RECycleTime. RECycleTime is used as a reference event for CS release as well (CS is used as an on-going access notification signal depending on the type of LCD panel connected). This means that any *Read* access to the LCD through the L4 interface of the RFBI will be ended by a CS release (CS going inactive at the end of the access). Therefore, the OMAP35x Applications Processor does not support two consecutive *Read* accesses to the LCD (there is always 1 L4 clock cycle between 2 accesses).

Write access to the LCD through the RFBI L4 port: For a *Write* access, the back-to-back data of a single access that has been split is supported and guaranteed (e.g., one 32-bit write split in two consecutive, back-to-back, 16-bit accesses). In this case, the internal bus CS signal will be kept active until split access completion. However, when there are two different write accesses from the initiator, they will not be seen as back-to-back by the LCD. At the end of the transaction corresponding to one write

access from the initiator, the internal bus CS will be released at WECycleTime, and the next command from the initiator will be accepted. Consequently, any *Write* access to the LCD through the L4 interface of the RFBI will be ended by a CS release (CS going inactive at the end of the access). Therefore, the OMAP35x Applications Processor does not support two consecutive data transmits to the LCD (corresponding to two different and consecutive *Write* accesses from the initiator).

(Internal reference number: 2.1)

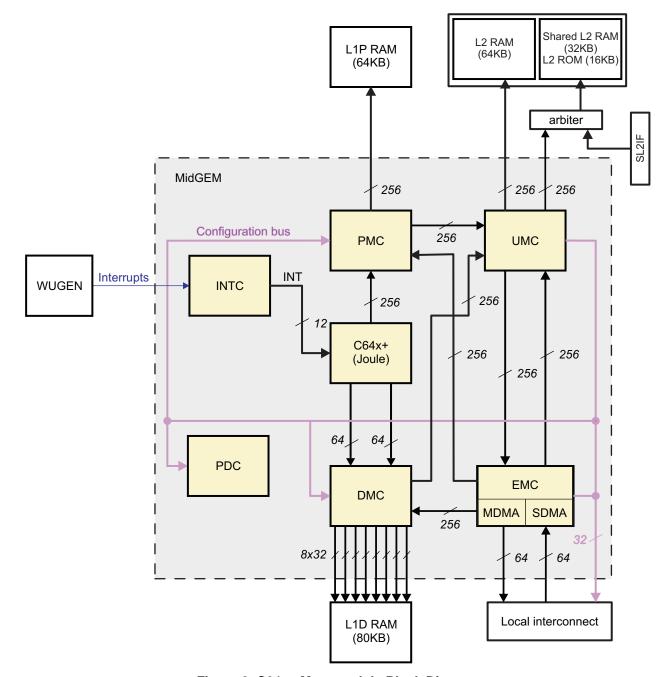

### 2.1.3 IVA2: IDLE Instruction Must be Executed From L1P or L2 SRAM Under Hardware Emulation (OMAP3530/25 only)

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, when the C64x core executes an IDLE instruction, and an emulator access to a register or memory happens simultaneously, the CPU may hang, depending on the relative speed of TCK, GEM clock, and the external memory where the IDLE instruction is fetched. This limitation is *only* applicable in *emulation* mode when an external emulator, such as TI XDS560, is connected to the device.

To ensure this race condition does not occur, the IDLE instruction should be executed from L1P SRAM or L2SRAM. This will allow the IDLE instruction to execute safely under hardware emulation.

(Internal reference number: 2.4)

#### 2.1.4 Domain Woken Up by Wake-up Dependency Cannot Transition to Inactive State

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, when a domain is activated up by a wake-up dependency, it cannot transition to an inactive (RET/OFF) state until one of the following conditions are satisfied:

- 1. If the domain has a sleep dependency with another domain, this domain and the sleep dependency must be also activated (hard-wired or enabled by the software).

- 2. If the domain is an initiator, it must be taken out of Standby mode.

**Note**: The user should ensure that when a wake-up dependency is enabled for a domain, it is expected to be fully active after the wake-up occurs. This issue happens in a case where a domain has been woken-up, but not activated and used.

(Internal reference number: 2.7)

#### 2.1.5 VENC: Last Data Line Missing in PAL

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, the VENC cannot show the image data at the end of the even frames on line 623. This is a minor violation of the ITU-R BT.470-6. Since lines 23 and 336 are reserved for WSS, the VENC can only show 574 lines of data instead of the 576 lines defined in the standard. One half line is missing for lines 23 (reserved for WSS) and 623, and one full line is missing for line 336 (reserved for WSS).

(Internal reference number: 2.8)

#### 2.1.6 Observability Signals Not Functional in OFF Mode

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, signals are routed to observability pins through a buffer powered by VDD2. Consequently, observability is not functional when VDD2 is powered off. This impacts the observability debug feature, but has no functional drawback.

**Note**: Maintaining the VDD2 supply on the board has no effect since isolation cells are activated regardless of the supplied voltage.

(Internal reference number: 2.10)

#### 2.1.7 Constraints on Module Clocks When Using DVFS

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, module interface timings can depend on the operating point (OPP). The timing closure is done for one instance of a module at a particular voltage. Operating conditions which work on one OPP are not automatically guaranteed on another module's OPP. For more details on the module interface switching characteristics, see the OMAP35x Applications Processor device-specific data manual.

When Dynamic Voltage and Frequency Scaling (DVFS) is performed, the software should ensure that no timing violations will occur by the two following methods:

- Using software, reconfigure the module accordingly when DVFS is performed to avoid timing violations.

- Use a conservative frequency on the module interface clock corresponding to the performance of the lower OPP used to ensure that DVFS can be performed without additional software management.

(Internal reference number: 2.11)

#### 2.1.8 Retention Voltage Not Supported

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, the retention voltage *is not* supported. The TI 65nm process defines a retention voltage which is lower than the lowest OPP voltage. This retention voltage is defined assuming that there is no logic activity at all in the device, which does not apply to the OMAP35x Applications Processor where asynchronous signals (wake-up) can be triggered during the device RET state. Because of this system requirement, the retention voltage does not apply to the OMAP35x Applications Processor, and the lowest OPP voltage should be used instead of a specific retention voltage.

The lowest operating point voltage should be used when the OMAP35x Applications Processor is in *retention* mode.

**Note**: This voltage can be optimized using SmartReflex before the device goes into *retention* mode. (Internal reference number: 2.14)

### 2.1.9 UART: Cannot Acknowledge Idle Requests in Smartidle Mode When Configured for DMA Operations

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, when configured for DMA operations using *smartidle* mode (SYSC[4:3].IDLEMODE = 0x2), the UART module will not acknowledge incoming idle requests. As a consequence, it can prevent L4 from going to idle.

When there are additional expected transfers, the UART should be placed in force-idle mode.

(Internal reference number: 2.15)

#### 2.1.10 Unexpected RFBI Latency for High Frame Rate

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, the Remote Frame Buffer (RFBI) state machine architecture can create non-optimized pipelining of the RFBI output data stream. As a result, some idle cycles may be inserted between RFBI accesses to the external panels. The number of idle cycles added depends on the OMAP clock configuration and RFBI configuration. Table 3 shows the minimum additional number of cycles depending on the RFBI configurations.

RFBI CONFIG. MIN CYCLETIME (Number of **RFBI PERFORMANCE** RFBI\_CONFIG. OCPFORMAT OCP cycles) **CYCLEFORMAT OCP Slave** 1 pixel/ cycle 1 pixel 5 1 pixel/ 2 cycles 1 pixel 4 4 1 pixel/ 3 cycles 1 pixel 2 pixels/ 3 cycles 1 pixel 6 4 1 pixel/ cycle 2 pixels 1 pixel/ 2 cycles 2 pixels 4 1 pixel/ 3 cycles 2 pixels 4 2 pixels/ 3 cycles 2 pixels 6 N/A 4 Display Controller 1 pixel/ cycle 1 pixel/ 2 cycles N/A 3 1 pixel/ 3 cycles N/A 3 1 pixel/ 3 cycles N/A 6

Table 3. Additional Minimum Cycletime (CS/WE Always Asserted)

(Internal reference number: 2.20)

#### 2.1.11 GPIO Drives Random Values When Device Comes Back from OFF Mode

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, the GPIO modules in the PER (Peripheral) domain drives random values when the device comes back from OFF mode with VDD2 voltage shut down.

Regardless of the active configuration of a GPIO (input or output), when coming back from OFF mode, GPIO can randomly drive the line high or low.

Root cause: The isolation at the boundary of the peripheral domain is done through isolation latches which are supplied by VDD2. When VDD2 is shut down, the content of the latches is lost. When the device is waking-up from the OFF mode, the padconf is automatically restored by the Hardware and then the isolation latches drives the pin until isolation is released (PER is woken-up). There is no reset value for the isolation latches thus leading to random value driven by the GPIO.

This does not impact GPIO from the WU domain.

Only GPIO implements this type of isolation latches and hence other functions are not impacted by this limitation.

Workaround 1 allows the software to work in SW supervised mode while Workaround 2 takes the benefit of HW dependency. For both the workarounds, SW is in charge to configure the internal pull in the padconf register to the desired value.

Workaround 1: Change padconf mode to safe mode before initiating the transition to OFF. This would avoid line being driven by isolation latch and the desired level is maintained by the pull.

Workaround 2: Create a WU dependency between WU domain and PER domain (PM\_WKDEP\_PER[4]: EN\_WKUP=1). This will WU the PER domain then release the isolation latch before the isolation cell is released at pad boundary. The reset value of the GPIO module configures the GPIO in input and then the pull ensures the that line is driven to the right value until GPIO module is restored by the applicative SW.

(Internal reference number: 2.23)

#### 2.1.12 Access to IVA Boot ROM at OPP1 Is no Longer Supported

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, accesses to IVA ROM code at low temperature and low voltage (VDD1; OPP1) cannot be guaranteed across the process. In case a failing access happens, the system behavior is unpredictable. Consequently, no access to IVA internal boot ROM at OPP1 is allowed.

Do not access IVA ROM or boot the IVA at any OPP except OPP1.

(Internal reference number: 2.24)

#### 2.1.13 Maximum 12 bits Output (1 bit sign + 11 bits of value) Is Supported on CAVLD of iVLCD

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, while decoding DC coeffs of an Intra16x16 MB, the iVLCD is not able to handle coeff with range greater than 11 bits. It is observed that the value returned by the iVLCD will be the equivalent of (actual\_value & 0x07FF). For e.g., value of 0x08A7 will be decoded as 0x00A7. However, the bits consumed by the iVLCD is correct and the decoding continues.

As per the standard, normal imagery can generate DC coeffs with range greater than 11 bits (especially at low QP) and some of the test cases are failing due to this issue. Since the error is in DC it will not only affect the MB in question, but propagate to neighboring MBs in the slice. The impact is visually noticeable.

This issue occurs very rarely and only if QP=1.

This special case must be handled with C64x+ software which increases code size and add extra MHz.

(Internal reference number: 2.25)

#### 2.1.14 Maximum Pixel Rate on Resizer With A-Law Decompression and Horizontal Zoom Greater than 2

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, failure conditions: SDRAM->PRV->RSZ->SDRAM path used with A-Law decompression cannot be used with Horizontal zoom greater than 2. RSZ can only accept pixel rate at up to OCP freq/(2\*hzoom). The Maximum horizontal zoom hzoom=4. However, the PRV read rate can only be slowed down to OCP freq/4.

Perform memory -> RSZ -> memory upscaling when Horizontal zoom greater than 2. Don't use PRV-> RSZ path when A-Law decompression is used in PRV.

(Internal reference number: 2.28)

#### 2.1.15 Extra Power Consumption at vdds mmc1/vdds sim in Device Off Mode

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, IO cells which are supplied by vdds\_mmc1 and vdds\_sim are dual voltage buffer. CONTROL\_PBIAS\_LITE.PBIASLITEPWRDNx bit controls enable/disable of these PBIAS cell. When PBIASLITEPWRDNx=1 (PBIAS is enabled), additional ~30uA at 1.8V or ~300uA at 3.0V power is consumed by the cell. This additional power consumption is negligible while the device is active, but it can be significant during device off mode.

To reduce the power consumption, the SW should do the following configuration before the OFF mode entry.

- Disable PBIAS cell (PBIASLITEPWRDNZx bit = 0).

- + If there is no external pulls or the line is not driven by the external IC, enable the pull down and

ensure that the PAD is in input mode by setting the muxmode in safe\_mode or in gpio(input).

This workaround cannot be applied for the cases the PAD needs to maintain high level during device off mode. Neither an internal pull-up nor high level driving works while PBIAS is disabled.

(Internal reference number: 2.29)

### 2.1.16 Extra Power Consumed When Repeated Start Operation Mode Is Enabled on I2C Interface Dedicated for Smart Reflex (I2C4)

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, on the I2C interface dedicated for Smart Reflex communication with the Power Management IC (I2C4), when Repeated Start operation mode is enabled (PRM\_VC\_I2C\_CFG[SREN]='1'), the I2C lines (SCL and SDA) are always driving a low state between two I2C commands (i.e. when there is no I2C traffic).

Knowing that there are external Pull-Up attached on these lines, this will impact the power consumption.

Setting PRM\_VC\_I2C\_CFG[SREN] register bit to '0' will allow the I2C4 lines driving a high state between two I2C commands.

(Internal reference number: 2.30)

#### 2.1.17 OMAP HS Devices Are Not Recovering From Warm Reset While in OFF Mode

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, a deadlock situation occurs if warm reset occurs during OFF mode or after WU from OFF but before ROM code execution is completed on HS device.

Root cause: It was not captured as a ROM code requirement to support a Warm reset during OFF mode.

#### Failure mechanisms:

- 1. If warm reset occurs before SSM restoration, then SSM generates secure violation (resulting in warm reset assertion) as soon as ARM is accessing other location than secure ROM. (This always occurs if warm reset happens during OFF mode).

- 2. If warm reset is asserted after SSM restoration but before ROM code completion then some part of the restoration normally performed by ROM code is missing which can result in unpredictable behavior (lockup or crash happening later on).

Condition of occurrence: The only source of warm reset during OFF mode are: MPU WD, Secure WD and external warm reset: sys\_nreswarm pin. With accurate sw configuration, and no security attack, MPU and secure watchdog are not expected to expire during OFF mode (either WDs are disabled before system transitioning to OFF mode or a timer will WU system before to reload WD before expiration). The only remaining relevant warm reset source during OFF mode is sys\_nreswarm.

No workaround needs to be implemented if sys\_nreswarm is used as OMAP output only; this issue should never happen.

If sys\_nreswarm is used as an OMAP input and is potentially asserted while OMAP is in OFF mode then the only way to recover is to generate a power on reset. This can be programmed in the warm\_reset sequence if TWL4030/5030 PMIC is used.

(Internal reference number: 2.31)

#### 2.1.18 DPLL3 Recall and Long Relock Time

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, temperature drift is impacting DPLL3 relock time. High temperature drift (positive or negative delta t > 20C) can extend relock time from 40 up to 150 clock cycles. This could cause issues in low power scenarios when the DPLL3 is idle most of the time and needs a fast wakeup to meet application timing.

The issue is fixed by disabling DPLL3 automatic control (bypass or stop mode). Automatic control should be enabled again before doing a transition to retention or off modes.

(Internal reference number: 2.32)

### 2.1.19 Transfer of Multiple Command Packets Coming from L4 Interconnect During a Blanking Period in Interleaving Mode

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, in video mode, the command mode packets, provided through the DSI protocol engine OCP port, can be interleaving during the vertical and/or horizontal blanking periods of the video stream sequence.

When TxFifo on the OCP slave port is empty, and if the 1st packet written to TxFifo is less than 13 words when 1 data lane is active or 17 words when 2 data lanes are active, only this packet will be sent out on the HS link during the next blanking period enabled for command packet transfer. This is the only sent packet, because this packet is the only completely written packet at the time of FSM read the last location of this packet from TxFifo. Even if more packets are written in TxFifo before the interleaving starts these packets will not be sent during that blanking period.

No workaround is available. The impact is minor because:

- When interleaving is done on a vertical blanking period (VSA, VFP, VBP), since this blanking are expressed in a number of lines, the remaining packet(s) in TxFifo will be sent on the HS link during the next line blanking interval within the same blanking period or during the next one.

- When the interleaving is done on a horizontal blanking period (HSA, HFP, HBP), the remaining data in TxFifo will be sent on the next blanking period.

(Internal reference number: 2.33)

#### 2.1.20 Downscaling limitations

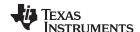

On OMAP35x Applications Processor silicon revisions 3.1.2 and earlier, Synclost interrupts are observed when performing downscaling and shifting resulting windows on the right of the LCD panel. This interrupt occurs because there is not sufficient time to load the necessary lines buffer before performing downscaling operation. DISPC video pipeline is expected to be ready with the pixels at the end of HSW+HBP period. This limitation is applicable on 3 and 5 taps configurations.

Figure 2. Synclost Interrupt

To ensure proper downscaling operation, these conditions should be met:

- ((PPL-SizeX-PosX) + (HBP+HSW+HFP)) \* PCD >= Max(0,Ceil(DS)-2)\*(OrgSizeX+1)

- ((PPL-SizeX) + (HBP+HSW+HFP)) \* PCD >= Max(0,Ceil(DS)-1)\*(OrgSizeX+1)

In case VRFB 90/270 rotation with YUV or RGB16 format, these conditions should be met:

((PPL-SizeX-PosX) + (HBP+HSW+HFP)) \* PCD >= Max(0,Ceil(DS)-1)\*(OrgSizeX+1)

• ((PPL-SizeX) + (HBP+HSW+HFP)) \* PCD >= (Max(0,Ceil(DS)-1)\*(OrgSizeX+1))\* 2

Where:

DS = (OrgSizeY+1)/(SizeY+1)

Ceil(x) is a round-up of x

(Internal reference number: 2.34)

### 2.2 Silicon Revision 3.1.2 Known Design Exceptions to Functional Specifications Table 4. Silicon Revision 3.1.2 Advisory List

| Title                                                                                                                           | Page |

|---------------------------------------------------------------------------------------------------------------------------------|------|

| Advisory 3.1.1.2 — I2C Module Does Not Allow 0-Byte Data Requests                                                               | 18   |

| Advisory 3.1.1.4 — Delay Required to Read Some GP, WD, and Sync Timer Registers After Wake-Up                                   | 19   |

| Advisory 3.1.1.9 — L1D Cache : C64x+ L1D Cache May Lose Data or Hang DMA Operations Under Certain Conditions (OMAP3530/25 only) | 20   |

| Advisory 3.1.1.11 — Race Condition May Cause I2C Slave to NACK a Transfer                                                       |      |

| Advisory 3.1.1.12 — MDR1 Access Can Freeze UART Module When in IrDa Mode                                                        |      |

| Advisory 3.1.1.13 — IVA2: Block Cache Operations Word Count (*WC) Must Be Less Than or Equal to 0xFF80 (OMAP3530/25 only)       | )    |

| Advisory 3.1.1.15 — I2C: RDR Flag May Be Incorrectly Set                                                                        |      |

| Advisory 3.1.1.16 — IVA2: EDMA Channel Priority Is Not Correctly Enforced (OMAP3530/25 only)                                    |      |

| Advisory 3.1.1.29 — Inactive State Management: Impossible to Transition to OFF or RETENTION States                              |      |

| Advisory 3.1.1.36 — Inappropriate Warm Reset Generation on Smart Reflex I2C Error                                               | 28   |

| Advisory 3.1.1.41 — CPU: Back-to-Back SPLOOPS With Interrupts Can Cause Incorrect Operation on C64x+ (OMAP3530/25 only)         |      |

| Advisory 3.1.1.42 — IVA2: DSP Generates False Internal Exception for Multiple Writes (OMAP3530/25 only)                         | 30   |

| Advisory 3.1.1.53 — GPMC May Stall After 256 Write Accesses in NAND_DATA, NAND_COMMAND, or NAND_ADDRESS Registers               | 32   |

| Advisory 3.1.1.57 — SPI Dummy DMA RX Request Generation                                                                         |      |

| Advisory 3.1.1.62 — 90 and 270-Degree Rotation DMA Optimization Does Not Function Properly                                      |      |

| Advisory 3.1.1.66 — SDMA: DMA4_IRQSTATUS_Lx and DMA4_IRQENABLE_Lx Registers Are Not Secure                                      |      |

| Advisory 3.1.1.74 — PRM_VOLTCTRL and PRM_CLKSRC_CTRL Registers Reset on Warm Reset                                              | 37   |

| Advisory 3.1.1.75 — IVA2: CAM/SGX Dependencies (OMAP3530/25 only)                                                               | 38   |

| Advisory 3.1.1.76 — Erroneous SResp Generation Issued to AES Immediately After Soft Reset                                       | 39   |

| Advisory 3.1.1.77 — MPU L2 Cache Size Status Register Value Inverted                                                            | 40   |

| Advisory 3.1.1.83 — L3 Interconnect Clock Divisor Default Value Must Be Modified Before Configuration of SD Controller          |      |

| Advisory 3.1.1.114 — DMA: Drain_IE Reset Value                                                                                  | 44   |

| Advisory 3.1.1.115 — sDMA: Channel Is Not Disabled After a Transaction Error                                                    | 45   |

| Advisory 3.1.1.121 — USB DEVICE Aborts Remote Wake-Up Sequence When OMAP35x Device Wakes From OFF/RET to ON in USB TLL Mode     |      |

| Advisory 3.1.1.127 — CONTROL_SWRV_i and CONTROL_MSV Registers Accessible Only in Secure Mode on Devices                         |      |

| Advisory 3.1.1.128 — Pending Interrupt to Video Sequencer Prevent IVA2 from Going Into Idle Mode                                | 48   |

| Advisory 3.1.1.129 — McSPI Can Generate a Wrong Underflow Interrupt                                                             | 49   |

| Advisory 3.1.1.131 — TV Detect AC Coupling Mode Not Supported                                                                   | 50   |

| Advisory 3.1.1.132 — USB DMA Cannot Handle Concurrent Channels                                                                  | 51   |

| Advisory 3.1.1.133 — VC1 En/De-coded Bit Stream Corrupted When iLF Is Used                                                      | 52   |

| Advisory 3.1.1.134 — Unexpected Stalling May Occur During SDMA/IDMA Accesses to DSP L2 Memory                                   | 53   |

| Advisory 3.1.1.138 — ISP: LSC Issue When Used Concurrently With Resizer                                                         | 57   |

| Advisory 3.1.1.141 — ISP CCDC DRAM Read-Port Issue                                                                              |      |

| Advisory 3.1.1.142 — ISP Lens Shading Correction Issue                                                                          |      |

| Advisory 3.1.1.144 — SDRC Does Not Send Auto-refresh When OMAP Wakes-up From OFF Mode                                           |      |

| Advisory 3.1.1.145 — CONTROL_REVISION Register Not Aligned With Silicon Revision                                                |      |

| Advisory 3.1.1.146 — HS USB OTG Software Reset Is Not Fully Functional                                                          |      |

| Advisory 3.1.1.148 — CKE PAD Is Not Set When Initializing External RAM                                                          |      |

| Advisory 3.1.1.149 — ROM Code: SDRC_POWER Register Is Initialized With Hardcoded Value                                          |      |

| Advisory 3.1.1.150 — I2C : I2C_STAT:XUDF Is Not Functional in Slave Transmitter Mode                                            |      |

| Advisory 3.1.1.152 — SDRC Timings Are Not Aligned With JEDEC Standard                                                           |      |

| Advisory 3.1.1.155 — I2C: Data Lost on Transmission From Memory to I2C Interface                                                | 67   |

#### Table 4. Silicon Revision 3.1.2 Advisory List (continued)

| Advisory 3.1.1.157 — EHCI Controller- Issue in Suspend Resume Protocol                                      | . 68 |

|-------------------------------------------------------------------------------------------------------------|------|

| Advisory 3.1.1.159 — Pull-up Not Maintained On GPIO_28/29 Pin During Padconf Restore                        | . 71 |

| Advisory 3.1.1.160 — GPIO Pad Glitch/Spike Upon Wake-Up From System OFF Mode                                | . 72 |

| Advisory 3.1.1.161 — I2C: Wrong RDR Interrupt After Disabling the Module With I2C_EN                        | . 74 |

| Advisory 3.1.1.162 — Voltage Processor TRANXDONE Interrupt Occurs Too Early                                 | . 75 |

| Advisory 3.1.1.164 — SMS ReadEx Deadlock                                                                    | . 76 |

| Advisory 3.1.1.166 — HS USB OTG: Idle_req / idle_ack Mechanism Potentially Broken When Autoidle Is Enabled  | . 77 |

| Advisory 3.1.1.167 — HS USB OTG: OTG_SYSCONFIG: AUTOIDLE Bit Not Correctly Reset                            | . 78 |

| Advisory 3.1.1.168 — IVA iVLCD Cannot Detect Errors                                                         | . 79 |

| Advisory 3.1.1.169 — UART Not Asserting Its TX DMA Request When RX FIFO Is Not Empty                        | . 80 |

| Advisory 3.1.1.170 — IVA2 Does Not Wake-Up After It Goes to IDLE While DMA Request Is Still Asserted        | . 81 |

| Advisory 3.1.1.173 — ISP: A-LAW Decompression Cannot be Performed in the PREVIEW Module                     | . 82 |

| Advisory 3.1.1.174 — SW Reset Done While ISP Processing Is Ongoing Can Cause OCP Protocol Violations        | . 83 |

| Advisory 3.1.1.175 — SBL_PCR [24]CCDCPRV_2_RSZ_OVF Goes High as Soon as RSZ_CNT[28]INPSRC Is Set to         | 0    |

| 1                                                                                                           |      |

| Advisory 3.1.1.176 — PRV Pixel Data Read from Memory When CCDC Video Port Is Active                         | . 85 |

| Advisory 3.1.1.177 — H3A Buffer Overrun                                                                     |      |

| Advisory 3.1.1.178 — Accesses to DDR Stall in SDRC After a Warm-reset                                       | . 87 |

| Advisory 3.1.1.180 — High-Speed USBOTG Short Packet Issue                                                   | . 88 |

| Advisory 3.1.1.181 — Standard OTG Compliance Electrical Tests for HOST Mode Will Fail                       | . 89 |

| Advisory 3.1.1.183 — GPMC Has Incorrect ECC Computation for 4-Bit BCH Mode                                  | . 90 |

| Advisory 3.1.1.185 — HS USB: ECHI and OHCI Controllers Cannot Work Concurrently                             | . 91 |

| Advisory 3.1.1.186 — MMC OCP Clock Not Gated When Thermal Sensor Is Used                                    | . 92 |

| Advisory 3.1.1.187 — Context Save Operation Randomly Failing for CONTROL_PAD_CONF_ETK14                     | . 93 |

| Advisory 3.1.1.188 — I2C4 Does Not Meet I2C Standard AC Timing in FS Mode                                   | . 94 |

| Advisory 3.1.1.189 — I2C1 to 3 SCL Low Period Is Shorter in FS Mode                                         | . 95 |

| Advisory 3.1.1.190 — Unexpected Warm Reset Assertion on HS Devices                                          | . 96 |

| Advisory 3.1.1.191 — Warm Reset Assertion Time When Warm Reset Happen During OFF Mode                       | . 97 |

| Advisory 3.1.1.192 — Missed Dependency With McBSP External Clock Avoid Transition to OSWR                   | . 98 |

| Advisory 3.1.1.193 — MPU Cannot Exit From Standby                                                           | . 99 |

| Advisory 3.1.1.194 — sDMA FIFO Draining Does Not Finish                                                     | 100  |

| Advisory 3.1.1.195 — HSUSB Interoperability Issue With SMSC USB3320 PHY                                     | 101  |

| Advisory 3.1.1.196 — IVA2 Does Not Wake-up After It Goes to IDLE While an Interrupt Line Is Not Cleared     | 102  |

| Advisory 3.1.1.197 — POWERVR SGX™: MMU Lockup on Multiple Page Miss                                         | 103  |

| Advisory 3.1.1.198 — HS USB OTG: ULPI LINK Possibly Sticks After DPLL3 SW Reset if USB Cable Stays          |      |

| Connected                                                                                                   |      |

| Advisory 3.1.1.199 — USB Host EHCI May Stall When Exiting Smart-standby Mode                                |      |

| Advisory 3.1.1.200 — USB Host EHCI May Stall When Running High Peak-Bandwidth Demanding Use Cases           |      |

| Advisory 3.1.1.201 — USB OTG DMA May Stall When Entering Standby Mode                                       | 107  |

| Advisory 3.1.1.202 — DPLL3 in Manual Lock Mode Cannot be Used When CORE Goes to OSWR or OFF State           | 108  |

| Advisory 3.1.1.203 — PRCM DPLL Control FSM Removes SDRC_IDLEREQ Before DPLL3 Locks                          | 109  |

| Advisory 3.1.1.204 — PER Domain Reset Issue After Domain-OFF/OSWR Wakeup                                    | 110  |

| Advisory 3.1.1.205 — McBSP Used in Slave Mode Can Create a Dead Lock Situation When Doing Power Management  | 111  |

| Advisory 3.1.1.206 — DPLL3 Bypass Condition Does Not Consider State of SGX FCLK                             |      |

| Advisory 3.1.1.207 — I2C: In SCCB Mode, Under Specific Conditions, the Module Might Hold the Bus by Keeping |      |

| SCL Low                                                                                                     | 113  |

| Advisory 3.1.1.208 — I2C: Spurious Wakeup Event When sysclk Period is Higher Than ocpclk Period             | 114  |

| Advisory 3.1.1.209 — I2C: Wrong Behavior When a Data With MSB 0 is Put in the FIFO Before a Ttansfer with   |      |

| SBLOCK is Started                                                                                           | 115  |

#### Table 4. Silicon Revision 3.1.2 Advisory List (continued)

| Advisory 3.1.1.210 — I2C: After an Arbitration Lost the Module Starts Incorrectly the Next Transfer         | 116 |

|-------------------------------------------------------------------------------------------------------------|-----|

| Advisory 3.1.1.211 —4-cycle Saturating .M Unit Instructions May Mask 2-cycle Saturating. M Unit Instruction |     |

| Saturation Bit Update                                                                                       | 117 |

| Advisory 3.1.1.212 — SPLOOP CPU Cross-Path Stall                                                            | 118 |

| Advisory 3.1.1.2 | I2C Module Does Not Allow 0-Byte Data Requests |

|------------------|------------------------------------------------|

|------------------|------------------------------------------------|

**Revision(s) Affected** 3.1.2 and earlier

**Details** When configured as the master, the I2C module does not allow 0-byte data transfers.

**Note**: Programming I2Ci.I2C\_CNT[15:0]: DCOUNT = 0 will cause undefined behavior.

Workaround(s) No workaround. *Do not* use 0-byte data requests.

#### Advisory 3.1.1.4

#### Delay Required to Read Some GP, WD, and Sync Timer Registers After Wake-Up

#### Revision(s) Affected

3.1.2 and earlier

#### **Details**

If a General Purpose Timer (GPTimer) is in *posted* mode (TSIRC.POSTED = 1), due to internal resynchronizations, any values read in TCRR, TCAR1, and TCAR2 registers immediately after the timer interface clock (L4) goes from a stopped state to an active state may not return the expected values. This situation is most likely when the OMAP35x Applications Processor wakes up from an idle state.

#### Notes:

- GPTimer non-posted synchronization mode is not impacted by this advisory.

- This advisory also impacts reads from Watchdog timers WCRR registers.

- All of the watchdog timers support only posted internal synchronization mode. There

is no capability to change the internal synchronization scheme to non-posted mode

via software.

- The 32K sync timer CR and 32SYNCNT\_REV registers are also impacted by this advisory, since the 32K sync timer is always in posted synchronization mode.

#### Workaround(s)

The software must wait at least 2 timer interface clock cycles + 1 timer functional clock cycle after L4 clock-wakeup before reading TCRR, TCAR1, or TCAR2 registers for GP Timers in *posted* internal synchronization mode, and before reading the WCRR register of the Watchdog timers. The same workaround must be applied before reading CR and 32KSYNCNT\_REV registers of the synctimer module.

**Advisory 3.1.1.9** — L1D Cache: C64x+ L1D Cache May Lose Data or Hang DMA Operations Under Certain Conditions (OMAP3530/25 only) www.ti.com

#### Advisory 3.1.1.9

### L1D Cache: C64x+ L1D Cache May Lose Data or Hang DMA Operations Under Certain Conditions (OMAP3530/25 only)

#### Revision(s) Affected

3.1.2 and earlier

#### **Details**

Under certain conditions, parallel loads with predication to the same cache line may cause victims to be dropped and/or DMA to hang.

All of the following conditions *must* be true in order for this problem to occur:

- 1. Two LD instructions in parallel.

- 2. Both are LDs to the same cache line (upper 26 address bits are the same).

- 3. The LD using T1 is predicated and the predicate is false.

- 4. The LD using T2 is either not predicated, or is predicated and the predicate is true.

- 5. The cache line is absent from the cache.

- 6. The two other lines in the same L1D set are valid.

- 7. The LRU cache line in the set is dirty.

#### Results:

- L1D informs L2 to expect a victim for the affected set.

- L2 stalls DMAs with addresses that correspond to that set (DMA includes accesses from IDMA and EDMA).

**Note:** DMA includes accesses from IDMA, EDMA, and any external masters, such as PCI or other CPUs.

- L1D processes the true-predicated request correctly.

- · L1D does not send the indicated victim.

#### Impact:

- · If the load instruction reads a cacheable location:

- The updated data in the LRU line gets dropped.

- DMA accesses whose addresses match the affected set hang.

- If the load instruction reads a non-cacheable location:

- L1D retains the updated data from the LRU line.

- DMA reads may see stale data if the LRU line's address is in L2 memory.

#### Workaround(s)

Use Code Gen patch 6.0.3 (available on update advisor) to recompile your source code and avoid this issue. Libraries supplied by TI will be re-released using the 6.0.3 compiler patch. Customer-generated libraries from TI's third-party supplier may also need to be recompiled.

For existing object code and libraries, an available Perl script can determine locations of parallel predicated loads that may fail. The script is available at the same update advisor location as the Code Gen patch.

#### Advisory 3.1.1.11 Race Condition May Cause I2C Slave to NACK a Transfer

Revision(s) Affected

3.1.2 and earlier

**Details**

If the I2C module is configured as a slave, in *autoidle* mode (I2C\_SYSC.AUTOIDLE = 1) and the ARDY (I2C.12C\_STAT[2]) condition and the START condition are detected in the module at the same time, internal clock gating will be incorrectly applied. This will cause the I2C to NACK (I2C.12C\_STAT[1]) the transfer for which the START (I2C.I2C\_STA[6]) condition was received. Subsequent transfers will be ACKed as expected.

Workaround(s)

**Workaround 1**: Software *must* set SYSC\_AUTOIDLE to 0. In this case, the failure condition never occurs.

**Workaround 2**: Ensure that the external I2C master always resends a NACKed transfer via software. If a transfer was NACKed because of this race condition, the next transfer will always be ACKed.

#### Advisory 3.1.1.12 MDR1 Access Can Freeze UART Module When in IrDa Mode

#### Revision(s) Affected

3.1.2 and earlier

#### **Details**

Because of a glitchy structure inside the UART module, accessing the MDR1 register may create a dummy underrun condition and freeze the UART IrDa transmission. Only IrDa modes *Slow Infrared* (SIR), *Medium Infrared* (MIR), and *Fast Infrared* (FIR) are impacted. Even if the bug condition occurs in *UART* mode or *IrDa CIR* mode, it will have no effect. Therefore, UART1 and UART2 are immune to this problem, and only UART3 may exhibit this issue when used in one of the IrDa modes— SIR, MIR, or FIR.

#### Workaround(s)

To ensure this problem does not occur, the following software initialization sequence must be used each time MDR1 must be changed to one of the three failing *IrDa* modes:

- 1. If needed, setup the UART by writing the required registers, except MDR1.

- 2. Set appropriately the MDR1.MODE\_SELECT bit field.

- 3. Wait for 5 L4 clock cycles + 5 UART functional clock cycles.

- 4. Clear TX and RX FIFO in FCR register to reset its counter logic.

- 5. Read RESUME register to resume the halted operation.

www.ti.com Advisory 3.1.1.13 — IVA2: Block Cache Operations Word Count (\*WC) Must Be Less Than or Equal to 0xFF80 (OMAP3530/25 only)

Advisory 3.1.1.13 IVA2: Block Cache Operations Word Count (\*WC) Must Be Less Than or Equal to

0xFF80 (OMAP3530/25 only)

**Revision(s) Affected** 3.1.2 and earlier

**Details** When performing any block cache operation, such as "Writeback", "Writeback with

Invalidate", or "Invalidate", for any memory controller or memory range (e.g., L1P, L2, L1D) the word count programmed *must be* less than or equal to 0xFF80. If a value greater than 0xFF80 is desired, then this must be broken into multiple operations. The following registers are affected: L2WWC, L2WWC, L2IWC, L1PIWC, L1DWIWC,

L1DWWC, and L1DIWC.

Workaround(s) No workaround.

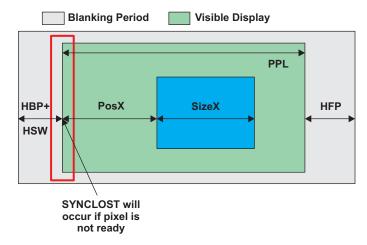

Advisory 3.1.1.15 I2C: RDR Flag May Be Incorrectly Set

Revision(s) Affected 3.1.2 and earlier

**Details** Under certain rare conditions, the I2C\_STAT[13].RDR bit may be set as well as the

corresponding interrupt fire, even when there is no data in the receive FIFO, or the I2C data transfer is still ongoing. These spurious RDR events must be ignored by the

software.

Workaround(s) Software must filter out unexpected RDR pulses, using the flowchart illustrated in

Figure 3 when receiving an I2C RDR interrupt.

Figure 3. I2C Flowchart

#### Advisory 3.1.1.16 IVA2: EDMA Channel Priority Is Not Correctly Enforced (OMAP3530/25 only)

#### Revision(s) Affected

3.1.2 and earlier

**Details**

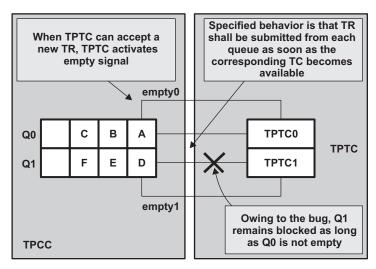

The EDMA channel controller (TPCC) has 2 event queues: Q0 and Q1. Each queue can be mapped to one of the two Transfer Controllers (TPTC): TPTC0 or TPTC1. As explained in the *OMAP35x Technical Reference Manual* (literature number <u>SPRUF98</u>), the events in each event queue will be extracted as soon as the corresponding TPTC is available for a new Transfer Request (TR) to be programmed into the TPTC. However, due to an issue in the IVA2.2 subsystem, the requests queued in Q1 cannot be submitted to their TPTC as long as Q0 is not empty.

Figure 4. TR Submission Scheme

#### Workaround(s)

Infrequent short transfers (e.g., latency critical synchronized transfers to/from peripheral) must be placed in Q0, and longer transfers (e.g., block copy) in Q1. For example, when a latency critical transfer is placed in EDMA and a longer transfer in QDMA, the following programming model will minimize the impact of this limitation:

- EDMA Event is gueued to Q0 (using IVA\_TPCC.DMAQNUMn register, n from 0 to 7)

- QDMA Event is queued to Q1 (using IVA\_TPCC.QDMAQNUM register)

- Queue to TC Mapping is Q0:TPTC1 Q1:TPTC0 (using IVA\_TPCC.QUETCMAP register)

- Queue Priority is Q0 = 0x0, Q1 = 0x7 (using IVA\_TPCC.QUEPRI register)

www.ti.com Advisory 3.1.1.29 — Inactive State Management: Impossible to Transition to OFF or RETENTION States

#### Advisory 3.1.1.29 Inactive State Management: Impossible to Transition to OFF or RETENTION States

Revision(s) Affected

3.1.2 and earlier

**Details**

If a power domain meets the conditions to go to an INACTIVE state (i.e., POWERSTATE is programmed to 0x3 (ON) and clock can be shut off), then the domain will transition to INACTIVE state. However, the domain cannot go to RET or OFF state automatically from INACTIVE state, even if software updates the POWERSTATE bit to 0x1 (RET) or 0x0 (OFF). The domain must be transitioned to the ON state before it can transition to the RET or OFF states.

Workaround(s)

The following two conditions must be met:

- 1. Do not use autostate with PM\_PWSTCTRL\_XXX.POWERSTATE=0x3 (ON) to put power state in INACTIVE. Using autostate from ON to RET (or OFF) transition is not impacted.

- 2. Perform wake-up event (software must force wakeup) to transition to an active state before transitioning to the RET or OFF states.

#### Advisory 3.1.1.36 Inappropriate Warm Reset Generation on Smart Reflex I2C Error

#### Revision(s) Affected

3.1.2 and earlier

#### **Details**

The Voltage Controller generates an I2C access error when an I2C command is sent to PowerIC during a voltage domain sleep transition. When the access error is generated, an interrupt is generated for software error handling. PRCM generates a warm\_reset when an access error is generated by the Voltage Controller during voltage domain wake-up transition. This is to recover the full system (OMAP35x Applications Processor + OMAP Peripherals + Power IC) and avoid a deadlock (OMAP35x Applications Processor wakeup transition stalling due to I2C access error and VDD1/ VDD2 not supplied). Since both VDD1 and VDD2 Voltage Controllers share the same interrupt line, an access error for VDD2 Voltage controller is also propagated to VDD1 Voltage controller.

This bug occurs only with the I2C module used by the Smart Reflex module. Other instances of the I2C module are not impacted by this issue.

In the following scenario,

- 1. VDD1 is performing a wake-up transition while VDD2 is performing a sleep transition.

- An I2C access error is generated on VDD2 sleep request and VDD1 and VDD2 share the same error line, so this access error on VDD2 is broadcasted to both VDD1 and VDD2.

The condition for a warm\_reset generation is met on VDD1, and Warm\_reset is asserted inappropriately.

This issue was detected in simulation, but it is a corner case that is not expected to occur in production, since the I2C access error should never occur if the PCB is safe. This bug is reported in the silicon errata to help developpers in case this kind of behavior is detected, but so far it has not been seen in real silicon.

#### Workaround(s)

By construction, the issue cannot happen if no I2C command is sent during a VDD2 sleep transition (use SYS\_OFF\_MODE and Smart Reflex disabled). It will never happen if an I2C access error does not occur (this is the expected behavior).

www.ti.com Advisory 3.1.1.41 — CPU: Back-to-Back SPLOOPS With Interrupts Can Cause Incorrect Operation on C64x+ CPU (OMAP3530/25 only)

Advisory 3.1.1.41 CPU: Back-to-Back SPLOOPS With Interrupts Can Cause Incorrect Operation on C64x+ CPU (OMAP3530/25 only)

Revision(s) Affected 3.1.2 and earlier

**Details** An issue can occur during C64x+ execution when:

- 1. The DSP code contains 2 contiguous SPLOOP/D/W

- 2. DSP is interrupted when executing the first SPLOOP/D/W

- There are less than 2 execute packets between the SPKERNEL of the first SPLOOP/D/W and the SPLOOP/D/W instruction of the second

When this issue occurs, the first SPLOOP/D/W terminates abruptly (i.e. without completing the loop), even though the termination condition is false. The failure mechanism can be seen as a hang or by the first SPLOOP/D/W draining for the interrupt and starting the second SPLOOP/D/W without taking the interrupt or returning to complete the first SPLOOP/D/W.

Ensure there are at least two execute packets between the SPKERNEL of the first SPLOOP/D/W and the SPLOOP/D/W instruction of the second.

A fix is implemented in the compiler included in version CGT6.0.6 of the Code Generation Tool (CGT). From this revision of CGT, the compiler now ensures there are two cycles between SPKERNEL and SPLOOP/D/W instructions by adding the appropriate number of NOP instructions following the SPKERNEL instruction.

#### **Advisory 3.1.1.42**

### IVA2: DSP Generates False Internal Exception for Multiple Writes (OMAP3530/25 only)

#### Revision(s) Affected

3.1.2 and earlier

#### **Details**

A false internal exception can be generated by C64x+ if an interrupt happens during DSP code flow and the instructions that will be annulled during pipeline flush are dependant. This issue occurs in the exception detection logic. It examines the DSP instructions during the pipeline flush, even though they have been annulled. The hardware does not detect this and incorrectly assumes that multiple write instructions to the same register with 2 different conditional registers will be executed.

The DSP generates an incorrect internal exception in the following scenario: the CPU is draining the pipeline as part of an interrupt context switch. During this time, it annuls instructions in the pipeline. The first annulled execute packet changes the value of one or more predicate registers. The second annulled execute packet has two or more predicated instructions that use the predicates written in the previous cycle. The values held in the predicate registers appear to cause the instructions in the second annulled execute packet to write to the same register. The conflicting writes would not happen if the first execute packet was not annulled.

#### Example:

```

ZERO A0

ZERO A1

-----> (interrupt occurs here)

MVK 1, A0; (annulled)

[!A0] MVK 2, A1; (annulled)

|| [!B0] MVK 3, A1; (annulled)

```

Invalid exception triggers as it appears that the last two MVK will both write A1.

Even if this issue appears in a DSP code, it does not affect the code flow and does not produce an unexpected exit routine value.

#### Workaround(s)

The CPU only recognizes the incorrect exception while it drains the pipeline for an interrupt. As a result, the CPU begins exception processing upon reaching the interrupt handler. The NRP (NMI Return Pointer Register) and NTSR (NMI Task State Register) will reflect the state of the machine upon arriving at the interrupt handler.

Therefore, to identify the incorrect resource conflict exception in software, verify the following conditions at the beginning of the exception handler prior to normal exception processing:

- 1. Exception occurred during an interrupt context switch.

- In NTSR, verify that INT=1, SPLX=0, IB=0, CXM=00.

- Verify that NRP points to an interrupt service fetch packet. That is, (NRP & 0xFFFFE1F) == (ISTP & 0xFFFFE1F).

- 2. The exception is a resource conflict exception. In IERR, verify that RCX == 1 and all other IERR bits == 0.

- 3. The exception is an internal exception. In EFR, verify that IXF == 1 and all other EFR bits == 0.

Upon matching the above conditions, suppress the exception as follows:

- Clear EFR.IXF by writing 2 to ECR.

- Resume the interrupt handler by branching to NRP.

The above workaround identifies and suppresses all cases of the incorrect resource conflict exception. It resumes normal program execution when the incorrect exception occurs, and has minimal impact on the execution time of program code. The interrupted code sequence runs as expected when the interrupt handler returns.

The workaround also suppresses a particular valid exception case that is

www.ti.com Advisory 3.1.1.42 — IVA2: DSP Generates False Internal Exception for Multiple Writes (OMAP3530/25 only)

indistinguishable from the incorrect case. Specifically, the code will suppress the exception generated by two instructions with different delay slots (e.g., LDW and DOTP2) writing to the same register in the same cycle, where the conflicting writes occur during the interrupt context switch.

Example of sequence with incorrectly suppressed exception:

The workaround will not suppress these valid resource conflict exceptions if the multiple writes occur outside an interrupt context switch. That is, the workaround will not suppress the exception generated by the code above when it executes without an interfering interrupt.

**Advisory 3.1.1.53** — GPMC May Stall After 256 Write Accesses in NAND\_DATA, NAND\_COMMAND, or NAND\_ADDRESS Registers www.ti.com

### Advisory 3.1.1.53 GPMC May Stall After 256 Write Accesses in NAND\_DATA, NAND\_COMMAND, or NAND\_ADDRESS Registers

#### Revision(s) Affected

3.1.2 and earlier

#### **Details**

The GPMC may stall if the following conditions are met:

- 1. GPMC CONFIG[0].NANDFORCEPOSTEDWRITE=1.

- Software performs more than 256 continuous write accesses in NAND\_COMMAND\_x, NAND\_ADDRESS\_x or NAND\_DATA\_x registers.

- GPMC\_STATUS[0].EMPTYWRITEBUFFERSTATUS is always 0 (buffer not empty)

during write accesses. This means the software has to write fast enough in GPMC

registers in order to never have the write buffer empty.

This mechanism is CS independent. If the software performs 128 write accesses in NAND\_DATA\_0 followed by 128 write accesses in NAND\_DATA\_1 then the bug will occur.

#### Workaround(s)

Accesses performed through the "prefetch and write posting engine" of the GPMC are not impacted by this limitation, and software should use this mechanism for the best performance.

If the prefetch and write posting engine is not used, when GPMC\_CONFIG[0].NANDFORCEPOSTEDWRITE=1 and after 255 write accesses in NAND\_COMMAND\_x, NAND\_DATA\_x or NAND\_ADDRESS\_x registers, the software has to wait until GPMC\_STATUS[0].EMPTYWRITEBUFFERSTATUS=1 before sending the next 255 write accesses.

#### **Advisory 3.1.1.57**

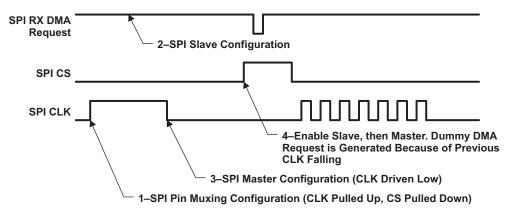

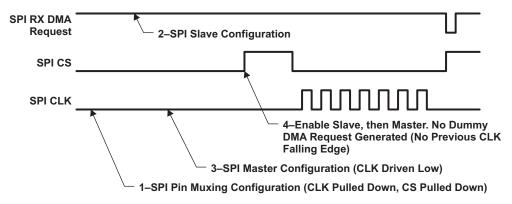

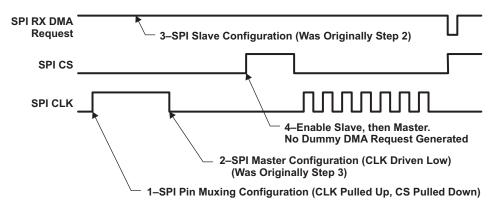

#### SPI Dummy DMA RX Request Generation

#### Revision(s) Affected

3.1.2 and earlier

#### **Details**

A dummy DMA RX request is generated as soon as the SPI is configured in *slave* mode and a SPI clock edge is detected. The dummy DMA RX request is generated during module configuration, when the module is not performing an SPI transfer. The dummy DMA RX request occurs as soon as the SPI interface signal sensitivity is changed compared to the default value.

The dummy DMA RX request is generated because the mechanism to avoid dummy data capture on a CS glitch is done regardless of channel activation.

Figure 5. SPI Dummy DMA RX Generation

#### Workaround(s)

Avoid conditions where the SPI is in *slave* mode and the SPI clock toggles (see examples below).

Figure 6. Dummy DMA RX Generation (No Clock Edge)

Figure 7. Dummy DMA RX Generation (Slave Mode After Clock Line Driven to Default Value)

www.ti.com Advisory 3.1.1.62 — 90 and 270-Degree Rotation DMA Optimization Does Not Function Properly

Advisory 3.1.1.62 90 and 270-Degree Rotation DMA Optimization Does Not Function Properly

**Revision(s) Affected** 3.1.2 and earlier

**Details** The DMA optimization functionality has been implemented in the display controller to

reduce bandwidth.

The access to the memory in 90- and 270- degree-rotation can be programmed to fetch two pixels per access. When this feature is used, the re-sampling (even if the ratio is 1) must be enabled to store the pixel in the lines buffer. This feature can be used with RGB16 and YUV422 pixels formats. Due to the address generation and the horizontal scaling issue, the DMA optimization does not work properly with RGB16 and YUV422 format for 90-degree and 270-degree rotations. The image is not correctly displayed on

the panel.

Workaround(s) No workaround. The bit VIDDMAOPTIMIZATION (bit 20 of DISPC VID1 ATTRIBUTES

or DISPC\_VID2\_ATTRIBUTES register) must be left to its default value: 0x0.

Advisory 3.1.1.66 — SDMA: DMA4\_IRQSTATUS\_Lx and DMA4\_IRQENABLE\_Lx Registers Are Not Secure www.ti.com

Advisory 3.1.1.66 SDMA: DMA4\_IRQSTATUS\_Lx and DMA4\_IRQENABLE\_Lx Registers Are Not

Secure

Revision(s) Affected 3.1.2 and earlier

**Details** The DMA4\_IRQSTATUS\_Lx and DMA4\_IRQENABLE\_Lx registers, where x is 0, 1, 2 or

3 are not protected in secure and supervisor modes. Therefore, the channel interrupt line of a secure / supervisor channel can be asserted. However, it is not possible to set or

reset an interrupt event.

Workaround(s) No workaround.

www.ti.com Advisory 3.1.1.74 — PRM\_VOLTCTRL and PRM\_CLKSRC\_CTRL Registers Reset on Warm Reset

Advisory 3.1.1.74 PRM\_VOLTCTRL and PRM\_CLKSRC\_CTRL Registers Reset on Warm Reset

Revision(s) Affected 3.1.2 and earlier

**Details** The PRM\_VOLTCTRL and PRM\_CLKSRC\_CTRL registers are reset on a Warm Reset;

however, they should be reset on Cold Reset only. These parameters depend on the

device environment only, but the registers must be re-programmed.

Workaround(s) No consequence. If default values are used, the registers must be re-programmed at

Warm Reset release.

# Advisory 3.1.1.75 IVA2: CAM/SGX Dependencies (OMAP3530/25 only)

### Revision(s) Affected

3.1.2 and earlier

### **Details**

### Scenario:

- IVA2 is idled.

- Interrupt is propagated to the IVA2.

- IVA2 INTC (WUGEN) generates a Wake-Up event to the PRCM for IVA2 Wake-Up.

- A Wake-Up dependency is defined between IVA and CAM, or IVA and SGX.

- PRCM wakes-up IVA2, which initiates wake-up for CAM/SGX.

- Interrupt is propagated to IVA2 Core.

- At this point IVA2 Core could initiate a transfer to CAM/SGX even though the CAM/SGX module may not have finished its wake-up sequence, thus resulting in OCP transfer fail.

# Workaround(s)

The IVA2 software should look at the CAM/SGX clock activity status bit to verify that the CAM/SGX domain is ON before performing any accesses. Next, 10 NOPs should be inserted for additional margin.

www.ti.com Advisory 3.1.1.76 — Erroneous SResp Generation Issued to AES Immediately After Soft Reset

Advisory 3.1.1.76 Erroneous SResp Generation Issued to AES Immediately After Soft Reset

Revision(s) Affected 3.1.2 and earlier

Details An OCP bus error (SRESP) occurs when an access to the module is performed while

the module is coming out of Soft Reset.

Workaround(s) Insert 2 NOPs after Soft Reset assertion.

# Advisory 3.1.1.77 MPU L2 Cache Size Status Register Value Inverted

## Revision(s) Affected

3.1.2 and earlier

### **Details**

The MPU L2 Cache Size Status register value is inverted compared to the value given in the spec. The MPU L2 cache size status

(CONTROL\_FEATURE\_OMAP\_STATUS[11:10].MPU\_L2\_CACHESIZE) is inverted:

# Expected:

- 00 = 0KB

- 01 = 64KB

- 10 = 128KB

- 11 = 256KB

### Current implementation:

- 00 = 256KB

- 01 = 128KB

- 10 = 64KB

- 11 = 0KB

# Workaround(s)

The software should appropriately handle the inversion.

www.ti.com Advisory 3.1.1.80 — Acting as a Host; For Bulk Split IN Transactions, the MUSBMHDRC Can Transmit Tokens too Close to the SOF Packet, Causing an IPG Error

# **Advisory 3.1.1.80**

Acting as a Host; For Bulk Split IN Transactions, the MUSBMHDRC Can Transmit Tokens too Close to the SOF Packet, Causing an IPG Error

### Revision(s) Affected

3.1.2 and earlier

#### **Details**

This defect will only occur for the following conditions:

- The USBMOTGHS is acting as a host

- BULK IN Split transactions in which the RX polling interval (RXINTERVAL) is large and the peripheral is not responding

This may cause tokens and packets to be transmitted near the SOF causing inter-packet gap violations and data corruption of the packet.

When the USBOTGHS is acting as a host and a Bulk Split IN transaction is in progress, the USBOTGHS transmits an in token and the device responds by sending data. If data is received, the USBOTGHS requests another packet at its scheduled time (send an IN token). However, if the device responds with a NAK by default, then the USBOTGHS will continue to request a packet until stopped by software. However the RXINTERVAL (0x1D) register can be used to limit the number of NAKs received. By default, the USBOTGHS will not limit the number of requests. The error identified by this defect occurs if the USBOTGHS has been transmitting IN tokens for the entire micro frame In this case, the MUSBMHDRC can transmit an IN token that is so close to the SOF that if the device responds by sending a packet, the packet would be corrupted by the transmission of the SOF. The result would be a corrupted packet (which can be identified by the CRC). For all other transactions, this corruption is avoided by use of the HS\_EOF1 (0x1C), FS\_EOF1 (0x1D) or LS\_EOF1 (0x1E) registers. These registers define a blackout that prevents transmission of IN tokens too close to the SOF.

### Workaround(s)

Limit the number of times the USBOTGHS will transmit an IN token if no packet is available. Limiting the number of attempts to 2 or 3 attempts will ensure that this corruption will never occur.

# Advisory 3.1.1.81 OCP Error Does Not Get Communicated to USBOTG

Revision(s) Affected

3.1.2 and earlier

**Details**

The OCP master interface of the sub-chip has a design limitation. This interface connects to an OCP slave on one side and to the AHB master interface of Mentor Graphics® USB On-The-Go (OTG) controller, MUSBMHDRC on the other side. It's a wrapper that converts AHB master read/write requests to equivalent OCP read/write requests and the OCP response/data from OCP slave is expected to be converted to equivalent AHB response/data. In the design, the AHB hresp is always set to OKAY. As a result, an OCP response is never translated to an equivalent AHB response. If an OCP error response is received on the master interface, it will be sent as an AHB OKAY response and not as an AHB Error response.

The DMA controller will continue with the DMA read/write transfer since it is unaware of the OCP error response that occurred for the given read/write transfer. The bus error bit in DMA\_CNTL register will never be set.

Workaround(s)

In an OCP error scenario, halt the DMA and terminate the DMA transfer.

www.ti.com Advisory 3.1.1.83 — L3 Interconnect Clock Divisor Default Value Must Be Modified Before Configuration of SDRAM Controller

Advisory 3.1.1.83 L3 Interconnect Clock Divisor Default Value Must Be Modified Before

Configuration of SDRAM Controller

**Revision(s) Affected** 3.1.2 and earlier

Details The SDRAM output clock is gated when an incorrect L3 CLK\_SEL ratio is set. This

operation is generally transparent and handled at boot time by the ROM code. The

workaround should be implemented for the following scenarios:

· GP device External Fast boot is used.

· EMU device External boot is used.

Workaround(s) For External Boot or External Fast Boot which are both impacted by the issue,

CLKSEL\_L3 (bit 1:0) = 10b must be set before performing SDRC configuration. In all other cases, this programing is handled by the ROM code and no workaround is

necessary.

# Advisory 3.1.1.114 DMA: Drain\_IE Reset Value

**Revision(s) Affected** 3.1.2 and earlier

Details The Drain\_IE bit in the DMA4\_CICRi[12] register is not initialized after POR, and its

default value can be either '0' or '1' while the documentation specifies '0'.

Workaround(s) Prior to the DMA setup, the software must write 0x0 to this bit to disable the Drain\_IE

interrupt in the CICR register.

# Advisory 3.1.1.115 sDMA: Channel Is Not Disabled After a Transaction Error

Revision(s) Affected 3.1.2 and earlier

**Details** During a destination synchronized transfer on the write port (or source sync with

SDMA.DMA4\_CCRi[25] BUFFERING\_DISABLE = 1), if a transaction error is reported at the last element of the transaction, the channel is not automatically disabled by DMA.

Workaround(s) Whenever a transaction error is detected on the write side of the channel, the software

must disable the channel by writing a '0' to DMA4\_CCRi[7]: ENABLE bit.

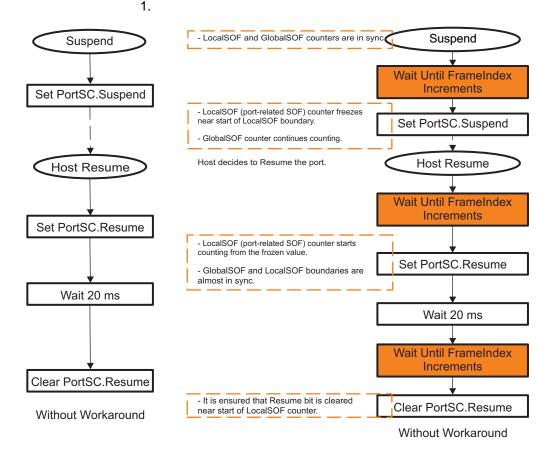

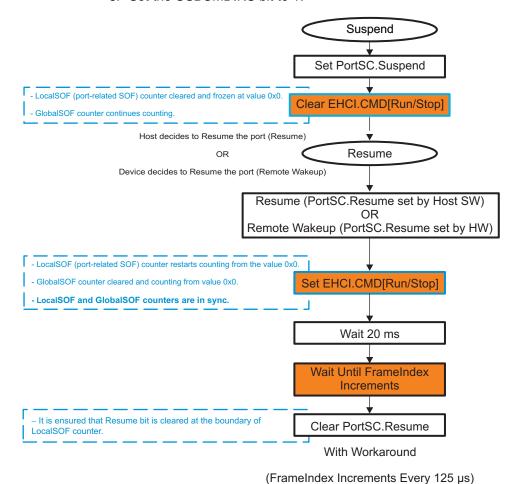

**Advisory 3.1.1.121** — USB DEVICE Aborts Remote Wake-Up Sequence When OMAP35x Device Wakes From OFF/RET to ON in USB TLL Mode www.ti.com