## TMS320C5535/34/33/32 Ultra-Low Power DSP

# **Technical Reference Manual**

Literature Number: SPRUH87C August 2011 – Revised March 2012

## **Contents**

| Pref | ace  |         |                                                           | . 33 |

|------|------|---------|-----------------------------------------------------------|------|

| 1    | Syst | em Cor  | ntrol                                                     | . 34 |

|      | 1.1  | Introdu | uction                                                    | . 35 |

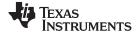

|      |      | 1.1.1   | Block Diagram                                             | . 36 |

|      |      | 1.1.2   | Device Differences                                        | . 37 |

|      |      | 1.1.3   | CPU Core                                                  | . 37 |

|      |      | 1.1.4   | FFT Hardware Accelerator (TMS320C5535 Only)               | . 37 |

|      |      | 1.1.5   | Power Management                                          |      |

|      |      | 1.1.6   | Peripherals                                               | . 39 |

|      | 1.2  | Syster  | n Memory                                                  | . 39 |

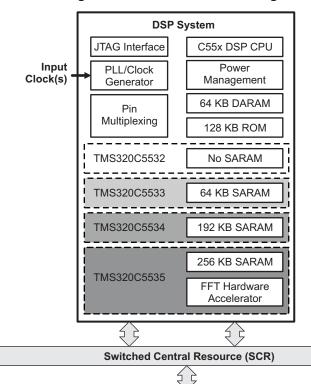

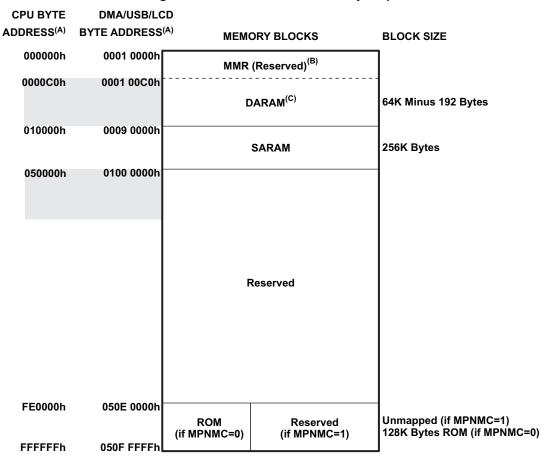

|      |      | 1.2.1   | Program/Data Memory Map                                   | . 39 |

|      |      | 1.2.2   | I/O Memory Map                                            | . 45 |

|      | 1.3  | Device  | e Clocking                                                | . 46 |

|      |      | 1.3.1   | Overview                                                  | . 46 |

|      |      | 1.3.2   | Clock Domains                                             | . 47 |

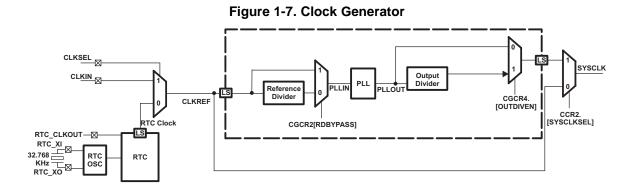

|      | 1.4  | Syster  | n Clock Generator                                         | . 48 |

|      |      | 1.4.1   | Overview                                                  | . 48 |

|      |      | 1.4.2   | Functional Description                                    | . 49 |

|      |      | 1.4.3   | Configuration                                             | . 51 |

|      |      | 1.4.4   | Clock Generator Registers                                 | . 55 |

|      | 1.5  | Power   | Management                                                | . 59 |

|      |      | 1.5.1   | Overview                                                  | . 59 |

|      |      | 1.5.2   | Power Domains                                             | . 59 |

|      |      | 1.5.3   | Clock Management                                          | . 60 |

|      |      | 1.5.4   | Static Power Management                                   | . 72 |

|      |      | 1.5.5   | Power Considerations                                      | . 76 |

|      |      | 1.5.6   | Power Configurations                                      | . 82 |

|      | 1.6  | Interru | pts                                                       | . 86 |

|      |      | 1.6.1   | IFR and IER Registers                                     | . 86 |

|      |      | 1.6.2   | Interrupt Timing                                          | . 88 |

|      |      | 1.6.3   | Timer Interrupt Aggregation Flag Register (TIAFR) [1C14h] | . 89 |

|      |      | 1.6.4   | GPIO Interrupt Enable and Aggregation Flag Registers      | . 89 |

|      |      | 1.6.5   | DMA Interrupt Enable and Aggregation Flag Registers       | . 89 |

|      | 1.7  | Syster  | n Configuration and Control                               | . 90 |

|      |      | 1.7.1   | Overview                                                  | . 90 |

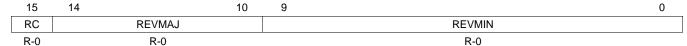

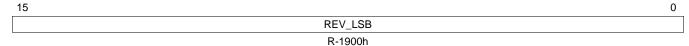

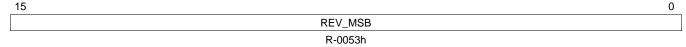

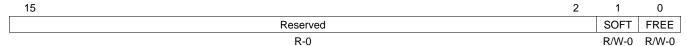

|      |      | 1.7.2   | Device Identification                                     | . 90 |

|      |      | 1.7.3   | Device Configuration                                      |      |

|      |      | 1.7.4   | DMA Controller Configuration                              | 104  |

|      |      | 1.7.5   | Peripheral Reset                                          |      |

|      |      | 1.7.6   | USB Byte Access (Not Available for TMS320C5532)           | 109  |

| 2    | FFT  | Implem  | entation on the TMS320C5535 DSP                           | 111  |

|      | 2.1  | -       | uction                                                    |      |

|      | 2.2  |         | of DFT and FFT                                            |      |

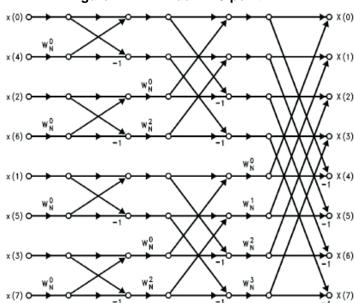

|      |      | 2.2.1   | Radix-2 Decimation in Time Equations                      |      |

|      |      | 2.2.2   | Radix-2 DIT Butterfly                                     |      |

|      |      |         |                                                           |      |

2

|   |       | 2.2.3 Computational Complexity                                                                        |                   |

|---|-------|-------------------------------------------------------------------------------------------------------|-------------------|

|   |       | 2.2.4 FFT Graphs                                                                                      |                   |

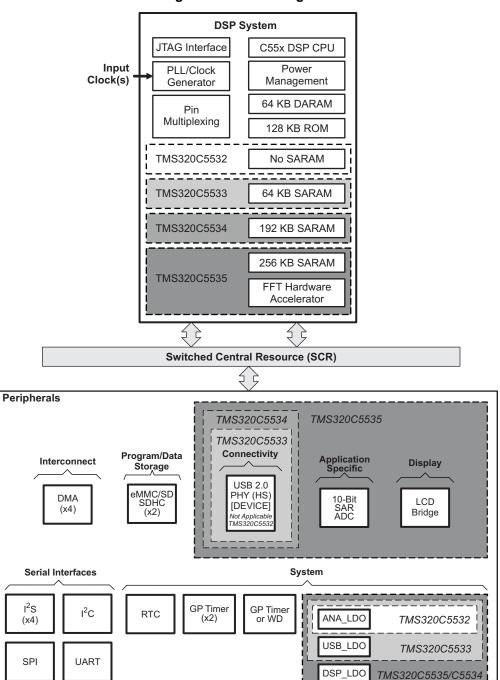

|   | 2.3   | DSP Overview Including the FFT Accelerator                                                            |                   |

|   | 2.4   | FFT Hardware Accelerator Description                                                                  |                   |

|   |       | 2.4.1 Tightly-Coupled Hardware Accelerator                                                            |                   |

|   |       | 2.4.2 Hardware Butterfly, Double-Stage and Single-Stage Mode                                          |                   |

|   |       | 2.4.3 Pipeline and Latency                                                                            |                   |

|   |       | 2.4.4 Software Control                                                                                |                   |

|   |       | 2.4.5 Twiddle Factors                                                                                 |                   |

|   |       | 2.4.6 Scaling                                                                                         |                   |

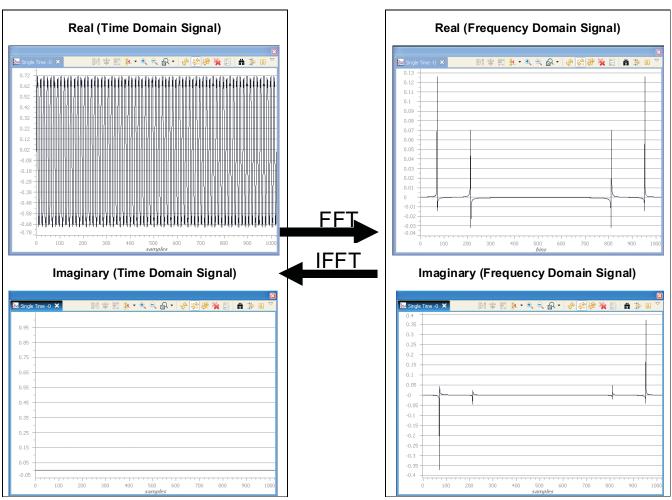

|   | 2.5   | HWAFFT Software Interface                                                                             | 120               |

|   |       | 2.5.1 Data Types                                                                                      |                   |

|   |       | 2.5.2 HWAFFT Functions                                                                                |                   |

|   |       | 2.5.3 Bit Reverse Function                                                                            |                   |

|   |       | 2.5.4 Function Descriptions and ROM Locations                                                         |                   |

|   |       | 2.5.5 Project Configuration for Calling Functions from ROM                                            |                   |

|   | 2.6   | Simple Example to Illustrate the Use of the FFT Accelerator                                           | 126               |

|   |       | 2.6.1 1024-Point FFT, Scaling Disabled                                                                | 126               |

|   |       | 2.6.2 1024-Point IFFT, Scaling Disabled                                                               | 126               |

|   |       | 2.6.3 Graphing FFT Results in CCS4                                                                    |                   |

|   | 2.7   | FFT Benchmarks                                                                                        |                   |

|   | 2.8   | Description of Open Source FFT Example Software                                                       | 130               |

|   | 2.9   | Computation of Large (Greater Than 1024-Point) FFTs                                                   | 131               |

|   |       | 2.9.1 Procedure for Computing Large FFTs                                                              | 131               |

|   |       | 2.9.2 Twiddle Factor Computation                                                                      |                   |

|   |       | 2.9.3 Bit-Reverse Separates Even and Odd Indexes                                                      | 131               |

|   |       | 2.9.4 2048-point FFT Source Code                                                                      | 131               |

|   | 2.10  | Appendix A Methods for Aligning the Bit-Reverse Destination Vector                                    | 133               |

|   |       | 2.10.1 Statically Allocate Buffer at Beginning of Suitable RAM Block                                  | 133               |

|   |       | 2.10.2 Use the ALIGN Descriptor to Force log <sub>2</sub> (4 * N) Zeros in the Least Significant Bits | 134               |

|   |       | 2.10.3 Use the DATA_ALIGN Pragma                                                                      | 134               |

| 3 | Direc | et Memory Access (DMA) Controller                                                                     | 135               |

|   | 3.1   | Introduction                                                                                          | 136               |

|   |       | 3.1.1 Purpose of the DMA Controller                                                                   | 136               |

|   |       | 3.1.2 Key Features of the DMA Controller                                                              | 136               |

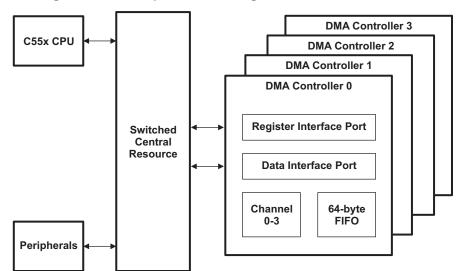

|   |       | 3.1.3 Block Diagram of the DMA Controller                                                             | 137               |

|   | 3.2   | DMA Controller Architecture                                                                           | 138               |

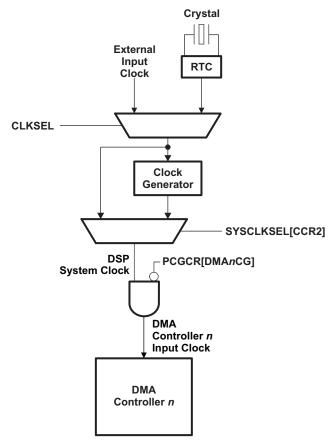

|   |       | 3.2.1 Clock Control                                                                                   | 138               |

|   |       | 3.2.2 Memory Map                                                                                      | 139               |

|   |       | 3.2.3 DMA Channels                                                                                    | 139               |

|   |       | 3.2.4 Channel Source and Destination Start Addresses                                                  | 140               |

|   |       | 3.2.5 Updating Addresses in a Channel                                                                 | 141               |

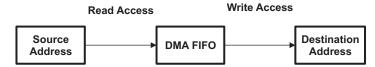

|   |       | 3.2.6 Data Burst Capability                                                                           |                   |

|   |       | 3.2.7 Synchronizing Channel Activity to DSP Peripheral Events                                         |                   |

|   |       | 3.2.8 Channel Auto-Initialization Capability                                                          |                   |

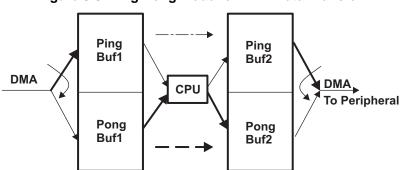

|   |       | 3.2.9 Ping-Pong DMA Mode                                                                              |                   |

|   |       | 3.2.10 Monitoring Channel Activity                                                                    |                   |

|   |       | 3.2.11 Latency in DMA Transfers                                                                       |                   |

|   |       | 0.2.11 Latonoy III Divirt Handrold IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                               | _                 |

|   |       | 3.2.12 Reset Considerations                                                                           | 145               |

|   |       | •                                                                                                     |                   |

|   |       | 3.2.12 Reset Considerations                                                                           | 146               |

|   |       | 3.2.12 Reset Considerations         3.2.13 Initialization         3.2.14 Interrupt Support            | 146<br>147        |

|   |       | 3.2.12 Reset Considerations 3.2.13 Initialization 3.2.14 Interrupt Support                            | 146<br>147<br>147 |

|   | 3.3   | DMA T   | ransfer Examples                                                | 147 |

|---|-------|---------|-----------------------------------------------------------------|-----|

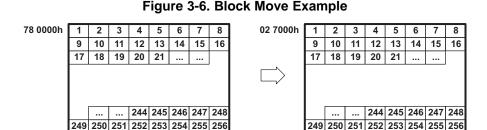

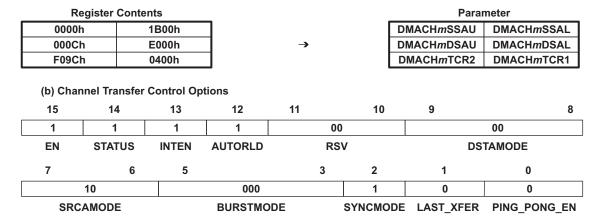

|   |       | 3.3.1   | Block Move Example                                              | 147 |

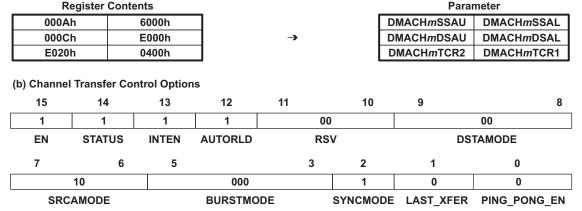

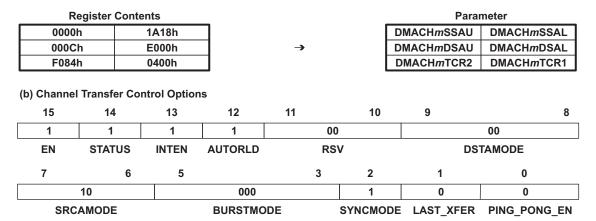

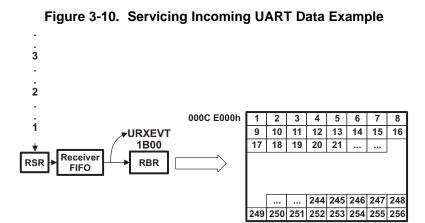

|   |       | 3.3.2   | Peripheral Servicing Example                                    | 148 |

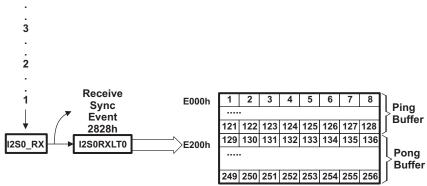

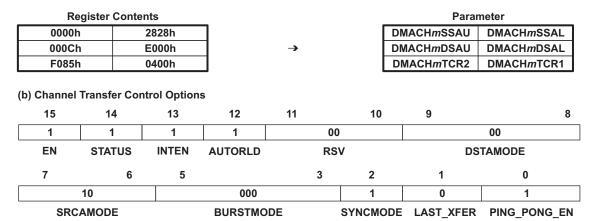

|   |       | 3.3.3   | Ping-Pong DMA Example                                           | 150 |

|   | 3.4   | Registe | ers                                                             | 152 |

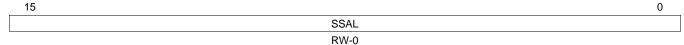

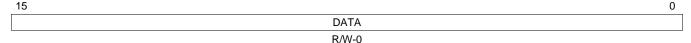

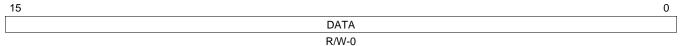

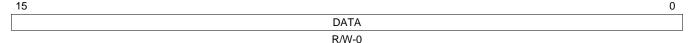

|   |       | 3.4.1   | Source Start Address Registers (DMACHmSSAL and DMACHmSSAU)      | 155 |

|   |       | 3.4.2   | Destination Start Address Registers (DMACHmDSAL and DMACHmDSAU) | 156 |

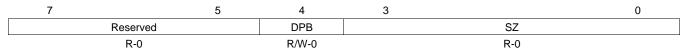

|   |       | 3.4.3   | Transfer Control Registers (DMACHmTCR1 and DMACHmTCR2)          |     |

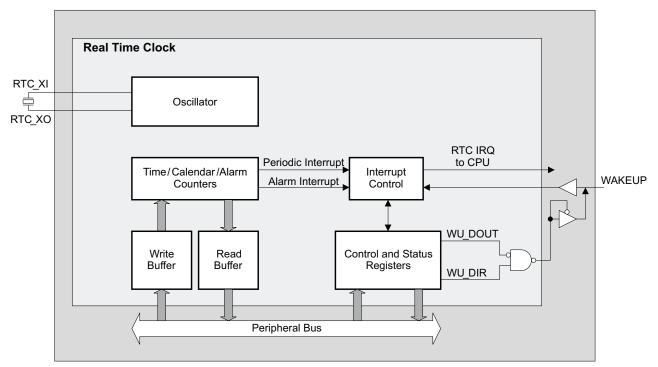

| 4 | Real. |         | Slock (RTC)                                                     |     |

| 7 | 4.1   |         | iction                                                          |     |

|   | 7.1   | 4.1.1   | Purpose of the Peripheral                                       |     |

|   |       |         | Features                                                        |     |

|   |       |         | Functional Block Diagram                                        |     |

|   | 4.2   |         | eral Architecture                                               |     |

|   | 4.2   | 4.2.1   | Clock Control                                                   |     |

|   |       | 4.2.1   | Signal Descriptions                                             |     |

|   |       | 4.2.3   | RTC-Only Mode                                                   |     |

|   |       | 4.2.3   | Using the Real-Time Clock Time and Calendar Registers           |     |

|   |       |         | · · ·                                                           |     |

|   |       | 4.2.5   | Using the Real-Time Clock Time and Calendar Alarms              |     |

|   |       | 4.2.6   | Real-Time Clock Interrupt Requests                              |     |

|   | 4.0   | 4.2.7   | Reset Considerations                                            |     |

|   | 4.3   | •       | ers                                                             |     |

|   |       | 4.3.1   | Overview                                                        |     |

|   |       |         | 3 13                                                            |     |

| 5 | 32-Bi |         | /Watchdog Timer                                                 |     |

|   | 5.1   | Introdu | ıction                                                          |     |

|   |       | 5.1.1   | Purpose of the Timers                                           |     |

|   |       | 5.1.2   | Features                                                        |     |

|   |       |         | Functional Timer Block Diagram                                  |     |

|   | 5.2   | Genera  | al-Purpose Timer                                                |     |

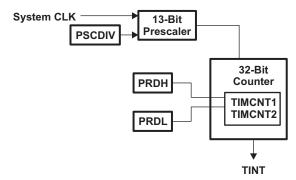

|   |       | 5.2.1   | General-Purpose Timer Clock Control                             |     |

|   |       | 5.2.2   | Using the 32-bit General Purpose Timer                          |     |

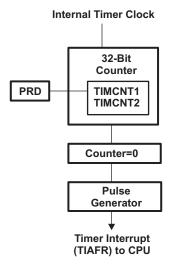

|   | 5.3   |         | dog Timer                                                       |     |

|   |       |         | Watchdog Timer Function                                         |     |

|   |       | 5.3.2   | Watchdog Timer Operation                                        | 189 |

|   | 5.4   | Reset   | Considerations                                                  | 190 |

|   |       | 5.4.1   | Hardware Reset Considerations                                   | 190 |

|   | 5.5   |         | pt Support                                                      |     |

|   | 5.6   | Registe | ers                                                             |     |

|   |       | 5.6.1   | Watchdog Kick Lock Register (WDKCKLK)                           | 192 |

|   |       | 5.6.2   | Watchdog Kick Register (WDKICK)                                 | 192 |

|   |       | 5.6.3   | Watchdog Start Value Lock Register (WDSVLR)                     | 193 |

|   |       | 5.6.4   | Watchdog Start Value Register (WDSVR)                           | 193 |

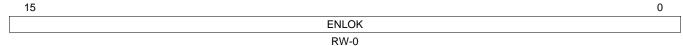

|   |       | 5.6.5   | Watchdog Enable Lock Register (WDENLOK)                         | 194 |

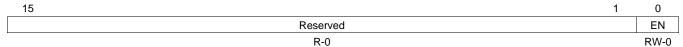

|   |       | 5.6.6   | Watchdog Enable Register (WDEN)                                 | 194 |

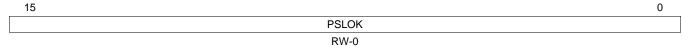

|   |       | 5.6.7   | Watchdog Prescaler Lock Register (WDPSLR)                       | 195 |

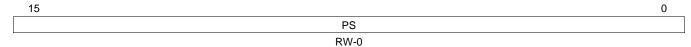

|   |       | 5.6.8   | Watchdog Prescaler Register (WDPS)                              | 195 |

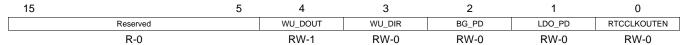

|   |       | 5.6.9   | Timer n Control Register (TCR)                                  | 196 |

|   |       | 5.6.10  | Timer n Period Register 1 (TIMPRD1)                             |     |

|   |       | 5.6.11  | Timer n Period Register 2 (TIMPRD2)                             | 197 |

|   |       | 5.6.12  | Timer n Counter Register 1 (TIMCNT1)                            |     |

|   |       | 5.6.13  | Timer n Counter Register 2 (TIMCNT2)                            |     |

|   |       | 5.6.14  | Timer Interrupt Aggregation Flag Register (TIAFR)               | 199 |

|   |       |         |                                                                 |     |

|   |      | 5.6.15  | Clock Gating                                               | 199 |

|---|------|---------|------------------------------------------------------------|-----|

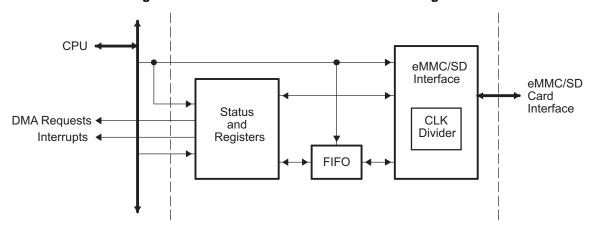

| 6 | Embe | edded I | Multimedia Card (eMMC)/Secure Digital (SD) Card Controller | 200 |

|   | 6.1  |         | ction                                                      |     |

|   |      | 6.1.1   | Purpose of the Peripheral                                  | 201 |

|   |      | 6.1.2   | Features                                                   | 201 |

|   |      | 6.1.3   | Functional Block Diagram                                   | 201 |

|   |      | 6.1.4   | Supported Use Case Statement                               | 201 |

|   |      | 6.1.5   | Industry Standard(s) Compliance Statement                  | 202 |

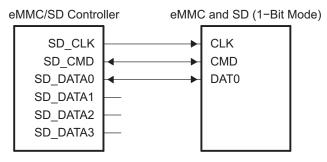

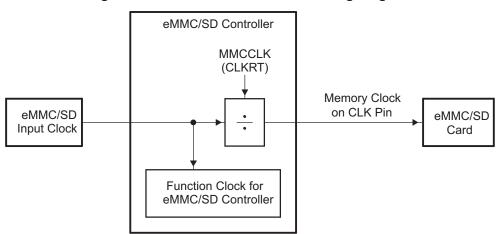

|   | 6.2  | Periph  | eral Architecture                                          | 202 |

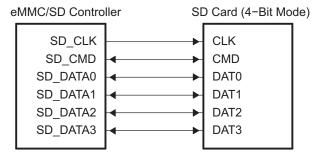

|   |      | 6.2.1   | Clock Control                                              | 204 |

|   |      | 6.2.2   | Signal Descriptions                                        | 204 |

|   |      | 6.2.3   | Pin Multiplexing                                           | 205 |

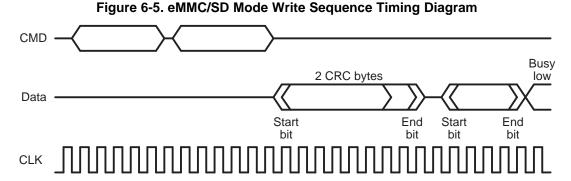

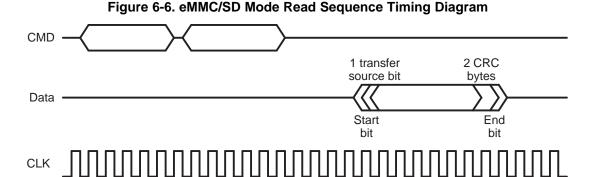

|   |      | 6.2.4   | Protocol Descriptions                                      | 205 |

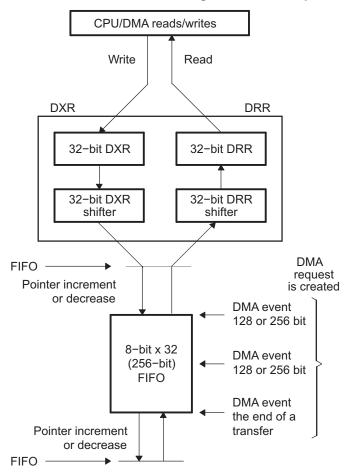

|   |      | 6.2.5   | Data Flow in the Input/Output FIFO                         | 206 |

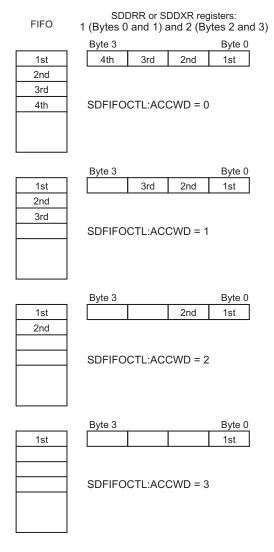

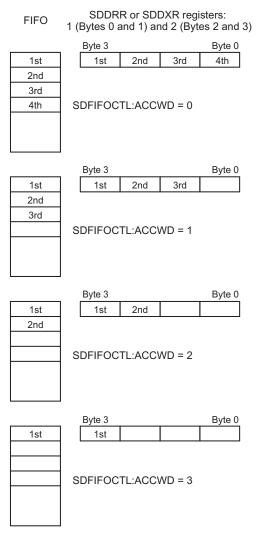

|   |      | 6.2.6   | Data Flow in the Data Registers (SDDRR and SDDXR)          | 208 |

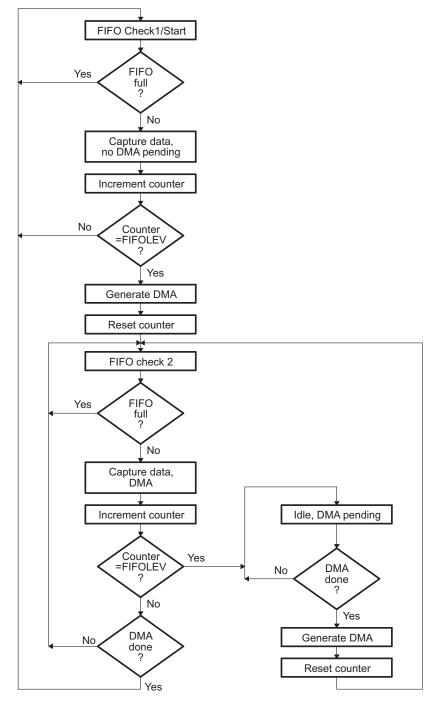

|   |      | 6.2.7   | FIFO Operation During Card Read Operation                  | 209 |

|   |      | 6.2.8   | FIFO Operation During Card Write Operation                 | 210 |

|   |      | 6.2.9   | Reset Considerations                                       | 212 |

|   |      | 6.2.10  | Programming and Using the SD Controller                    | 213 |

|   |      | 6.2.11  | Interrupt Support                                          | 217 |

|   |      | 6.2.12  | DMA Event Support                                          | 217 |

|   |      | 6.2.13  | Emulation Considerations                                   | 217 |

|   | 6.3  | Proced  | lures for Common Operations                                | 218 |

|   |      | 6.3.1   | Card Identification Operation                              | 218 |

|   |      | 6.3.2   | eMMC/SD Mode Single-Block Write Operation Using CPU        | 219 |

|   |      | 6.3.3   | eMMC/SD Mode Single-Block Write Operation Using DMA        | 220 |

|   |      | 6.3.4   | eMMC/SD Mode Single-Block Read Operation Using CPU         | 221 |

|   |      | 6.3.5   | eMMC/SD Mode Single-Block Read Operation Using DMA         | 222 |

|   |      | 6.3.6   | eMMC/SD Mode Multiple-Block Write Operation Using CPU      | 223 |

|   |      | 6.3.7   | eMMC/SD Mode Multiple-Block Write Operation Using DMA      | 224 |

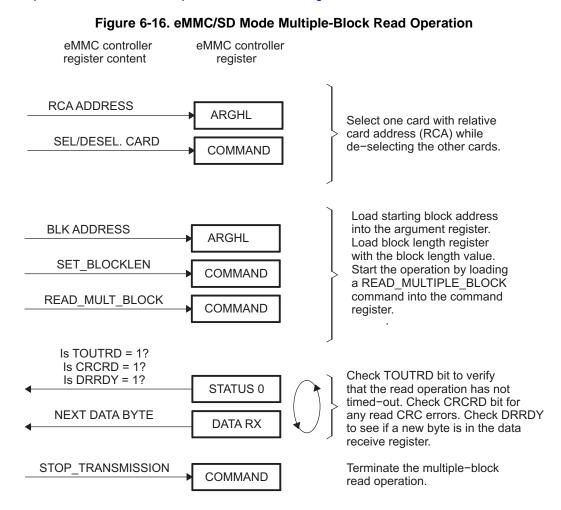

|   |      | 6.3.8   | eMMC/SD Mode Multiple-Block Read Operation Using CPU       | 225 |

|   |      | 6.3.9   | eMMC/SD Mode Multiple-Block Read Operation Using DMA       | 226 |

|   |      | 6.3.10  | SD High Speed Mode                                         | 227 |

|   |      | 6.3.11  | SDIO Card Function                                         | 227 |

|   | 6.4  | Registe | ers                                                        | 228 |

|   |      | 6.4.1   | SD Control Register (SDCTL)                                | 230 |

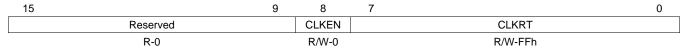

|   |      | 6.4.2   | SD Memory Clock Control Register (SDCLK)                   | 231 |

|   |      | 6.4.3   | SD Status Register 0 (SDST0)                               |     |

|   |      | 6.4.4   | SD Status Register 1 (SDST1)                               |     |

|   |      | 6.4.5   | SD Interrupt Mask Register (SDIM)                          |     |

|   |      | 6.4.6   | SD Response Time-Out Register (SDTOR)                      |     |

|   |      | 6.4.7   | SD Data Read Time-Out Register (SDTOD)                     |     |

|   |      | 6.4.8   | SD Block Length Register (SDBLEN)                          | 237 |

|   |      | 6.4.9   | SD Number of Blocks Register (SDNBLK)                      |     |

|   |      | 6.4.10  |                                                            |     |

|   |      | 6.4.11  | SD Data Receive Register (SDDRR1) and (SDDRR2)             |     |

|   |      | 6.4.12  |                                                            |     |

|   |      | 6.4.13  |                                                            |     |

|   |      | 6.4.14  |                                                            |     |

|   |      | 6.4.15  |                                                            |     |

|   |      | 6.4.16  |                                                            |     |

|   |      | 6.4.17  |                                                            |     |

|   |      |         | SDIO Control Register (SDIOCTL)                            |     |

|   |      | _       | ,                                                          |     |

|   |       | 6.4.19   | SDIO Status Register 0 (SDIOST0)                      | 247 |

|---|-------|----------|-------------------------------------------------------|-----|

|   |       | 6.4.20   | SDIO Interrupt Enable Register (SDIOIEN)              | 248 |

|   |       | 6.4.21   | SDIO Interrupt Status Register (SDIOIST)              |     |

|   |       | 6.4.22   | SD FIFO Control Register (SDFIFOCTL)                  |     |

| 7 | Unive |          | synchronous Receiver/Transmitter (UART)               |     |

| • | 7.1   |          | action                                                |     |

|   | 7.1   | 7.1.1    | Purpose of the Peripheral                             |     |

|   |       |          | Features                                              |     |

|   |       |          |                                                       |     |

|   |       |          | Functional Block Diagram                              |     |

|   | 7.2   | 7.1.4    | Industry Standard(s) Compliance Statement             |     |

|   | 1.2   |          | eral Architecture                                     |     |

|   |       | 7.2.1    |                                                       |     |

|   |       | 7.2.2    | Signal Descriptions                                   |     |

|   |       | 7.2.3    | Pin Multiplexing                                      |     |

|   |       | 7.2.4    | Protocol Description                                  |     |

|   |       | 7.2.5    | Operation                                             |     |

|   |       | 7.2.6    | Exception Processing                                  |     |

|   |       | 7.2.7    | Reset Considerations                                  |     |

|   |       | 7.2.8    | Initialization                                        |     |

|   |       | 7.2.9    | Interrupt Support                                     |     |

|   |       | 7.2.10   | DMA Event Support                                     |     |

|   |       | 7.2.11   | Power Management                                      |     |

|   |       | 7.2.12   |                                                       |     |

|   | 7.3   | Registe  | ers                                                   | 265 |

|   |       | 7.3.1    | Receiver Buffer Register (RBR)                        |     |

|   |       | 7.3.2    | Transmitter Holding Register (THR)                    | 267 |

|   |       | 7.3.3    | Interrupt Enable Register (IER)                       | 268 |

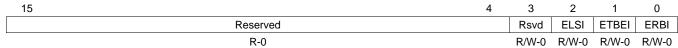

|   |       | 7.3.4    | Interrupt Identification Register (IIR)               | 269 |

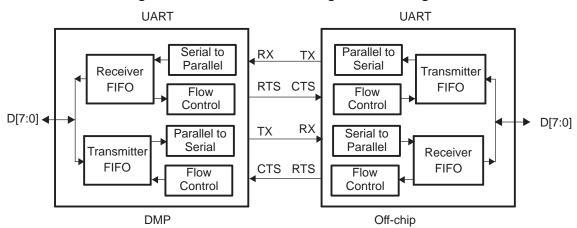

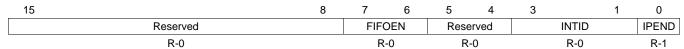

|   |       | 7.3.5    | FIFO Control Register (FCR)                           | 270 |

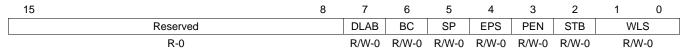

|   |       | 7.3.6    | Line Control Register (LCR)                           | 272 |

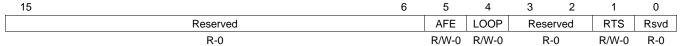

|   |       | 7.3.7    | Modem Control Register (MCR)                          | 274 |

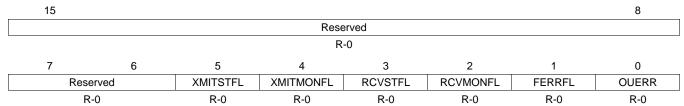

|   |       | 7.3.8    | Line Status Register (LSR)                            | 275 |

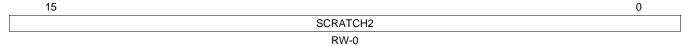

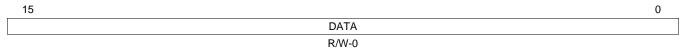

|   |       | 7.3.9    | Scratch Register                                      | 277 |

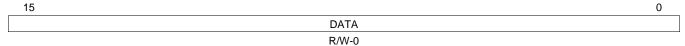

|   |       | 7.3.10   | Divisor Latches (DLL and DLH)                         | 278 |

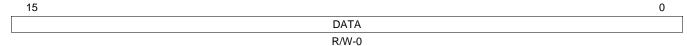

|   |       | 7.3.11   | Power and Emulation Management Register (PWREMU_MGMT) | 279 |

| 8 | Seria | l Parini | heral Interface (SPI)                                 | 280 |

| U | 8.1   | •        | action                                                |     |

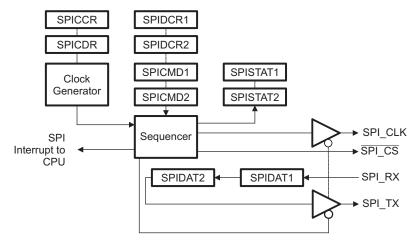

|   | 0.1   | 8.1.1    | Purpose of the Peripheral                             |     |

|   |       | 8.1.2    | Features                                              |     |

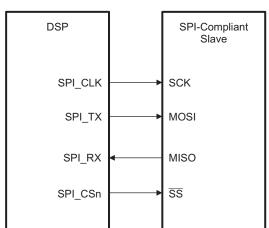

|   |       | 8.1.3    | Functional Block Diagram                              |     |

|   |       | 8.1.4    | Supported Use Case Statement                          |     |

|   |       | 8.1.5    | Industry Standard(s) Compliance Statement             |     |

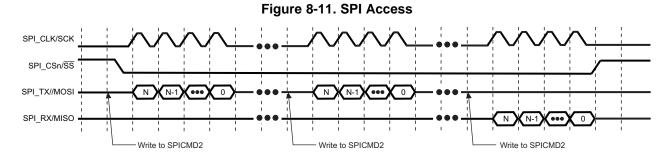

|   | 8.2   | -        | Peripheral Interface Architecture                     |     |

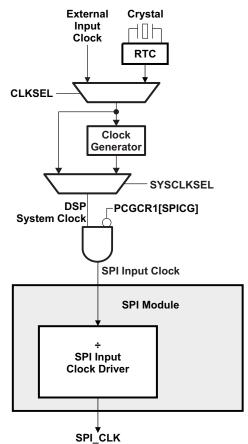

|   | 0.2   | 8.2.1    | Clock Control                                         |     |

|   |       |          |                                                       |     |

|   |       | 8.2.2    | Signal Descriptions                                   |     |

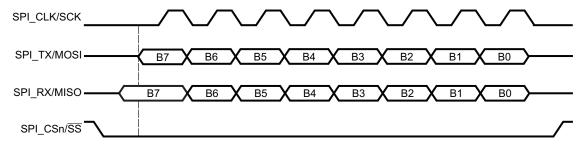

|   |       | 8.2.3    | Units of Data: Characters and Frames                  |     |

|   |       | 8.2.4    | Chip Select Control                                   |     |

|   |       | 8.2.5    | Clock Polarity and Phase                              |     |

|   |       | 8.2.6    | Data Delay                                            |     |

|   |       | 8.2.7    | Data Input and Output                                 | 287 |

|   |       | 8.2.8    | Loopback Mode                                         | 287 |

|   |       | 8.2.9    | Monitoring SPI Activity                               | 287 |

|   |       | 8.2.10   | Slave Access                                          | 288 |

|   |        | 8.2.11   | Reset Considerations                                                | 290 |

|---|--------|----------|---------------------------------------------------------------------|-----|

|   |        | 8.2.12   | Initialization                                                      |     |

|   |        | 8.2.13   | Interrupt Support                                                   | 291 |

|   |        | 8.2.14   | DMA Event Support                                                   | 291 |

|   |        | 8.2.15   | Power Management                                                    |     |

|   |        | 8.2.16   | Emulation Considerations                                            |     |

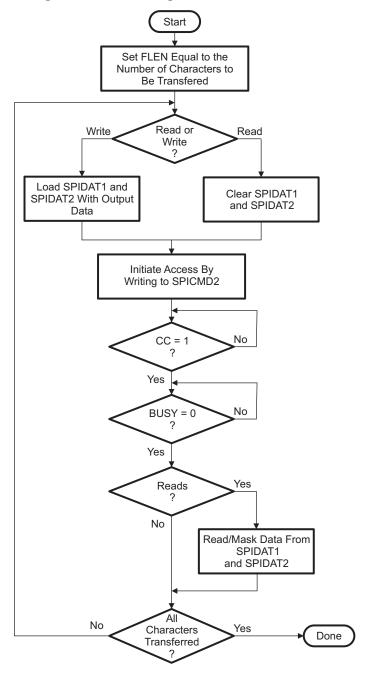

|   | 8.3    | Interfac | cing the SPI to an SPI EEPROM                                       |     |

|   |        | 8.3.1    | Operational Description                                             | 291 |

|   |        | 8.3.2    | Hardware Interface                                                  |     |

|   |        | 8.3.3    | SW Configuration                                                    | 292 |

|   | 8.4    | Registe  | ers                                                                 |     |

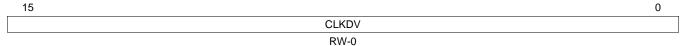

|   |        | 8.4.1    | Clock Divider Register (SPICDR) and Clock Control Register (SPICCR) | 297 |

|   |        | 8.4.2    | Device Configuration Registers (SPIDCR1 and SPIDCR2)                | 297 |

|   |        | 8.4.3    | Command Registers (SPICMD1 and SPICMD2)                             | 299 |

|   |        | 8.4.4    | Status Registers (SPISTAT1 and SPISTAT2)                            | 302 |

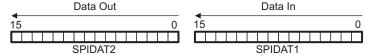

|   |        | 8.4.5    | Data Registers (SPIDAT1 and SPIDAT2)                                | 303 |

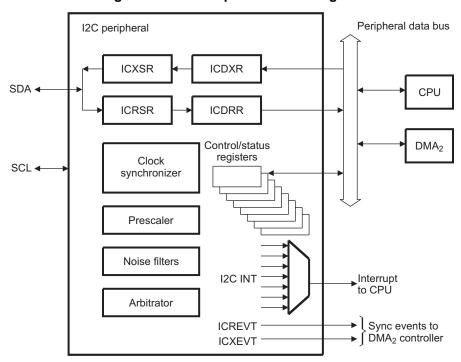

| 9 | Inter- | Integra  | ted Circuit (I2C) Peripheral                                        | 304 |

|   | 9.1    | _        | ction                                                               |     |

|   |        | 9.1.1    | Purpose of the Peripheral                                           |     |

|   |        | 9.1.2    | Features                                                            |     |

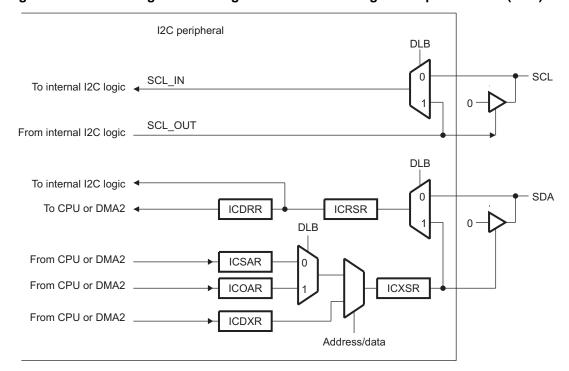

|   |        | 9.1.3    | Functional Block Diagram                                            |     |

|   |        | 9.1.4    | Industry Standard(s) Compliance Statement                           |     |

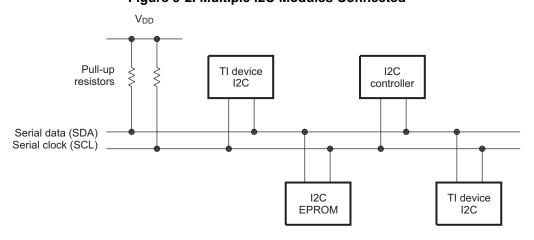

|   | 9.2    | -        | eral Architecture                                                   |     |

|   | 0      | 9.2.1    | Bus Structure                                                       |     |

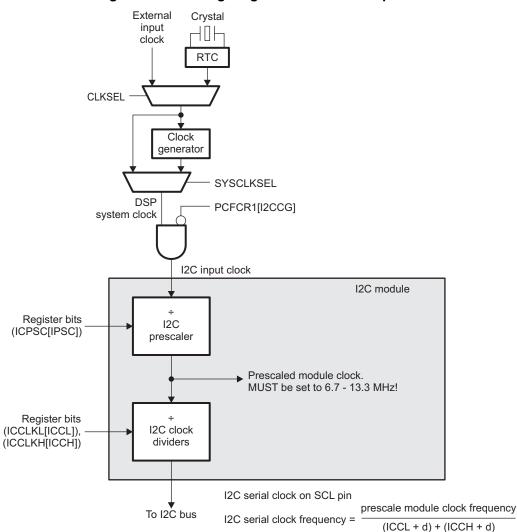

|   |        | 9.2.2    | Clock Generation                                                    |     |

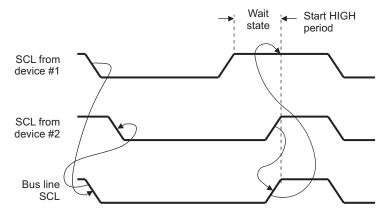

|   |        | 9.2.3    | Clock Synchronization                                               |     |

|   |        | 9.2.4    | Signal Descriptions                                                 |     |

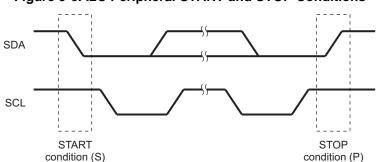

|   |        | 9.2.5    | START and STOP Conditions                                           |     |

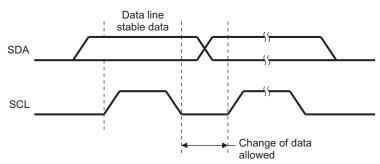

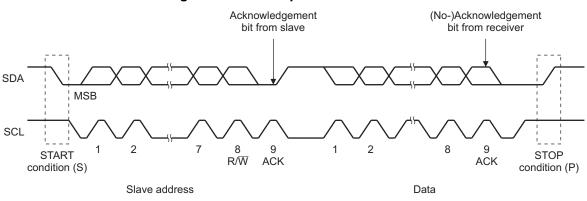

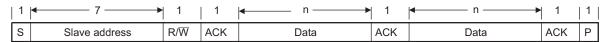

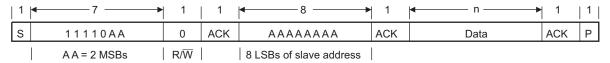

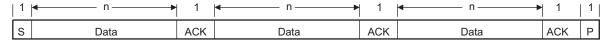

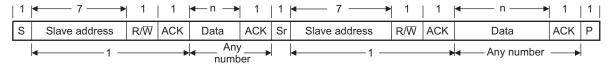

|   |        | 9.2.6    | Serial Data Formats                                                 |     |

|   |        | 9.2.7    | Operating Modes                                                     |     |

|   |        | 9.2.8    | NACK Bit Generation                                                 |     |

|   |        | 9.2.9    | Arbitration                                                         |     |

|   |        | 9.2.10   | Reset Considerations                                                |     |

|   |        | 9.2.11   | Initialization                                                      |     |

|   |        | 9.2.12   | Interrupt Support                                                   |     |

|   |        | -        | DMA Events Generated by the I2C Peripheral                          |     |

|   |        |          | Power Management                                                    |     |

|   |        | 9.2.15   | Emulation Considerations                                            |     |

|   | 9.3    |          | Prs                                                                 |     |

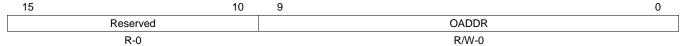

|   | 0.0    | 9.3.1    | I2C Own Address Register (ICOAR)                                    |     |

|   |        | 9.3.2    | I2C Interrupt Mask Register (ICIMR)                                 |     |

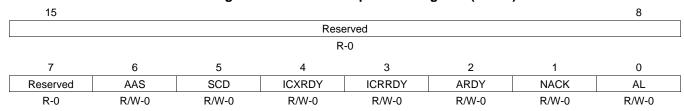

|   |        | 9.3.3    | I2C Interrupt Status Register (ICSTR)                               |     |

|   |        | 9.3.4    | I2C Clock Divider Registers (ICCLKL and ICCLKH)                     |     |

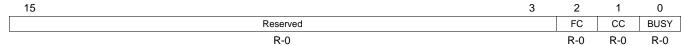

|   |        | 9.3.5    | I2C Data Count Register (ICCNT)                                     |     |

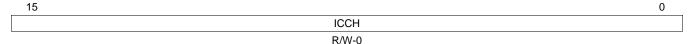

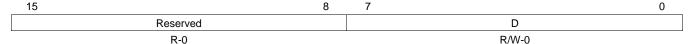

|   |        | 9.3.6    | I2C Data Receive Register (ICDRR)                                   |     |

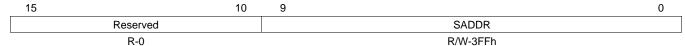

|   |        | 9.3.7    | I2C Slave Address Register (ICSAR)                                  |     |

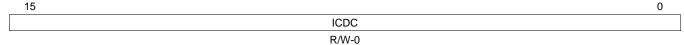

|   |        | 9.3.8    | I2C Data Transmit Register (ICDXR)                                  |     |

|   |        | 9.3.9    |                                                                     |     |

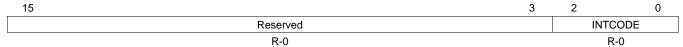

|   |        |          | I2C Interrupt Vector Register (ICIVR)                               |     |

|   |        | 9.3.10   | I2C Interrupt Vector Register (ICIVR)                               |     |

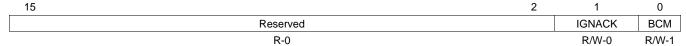

|   |        | 9.3.11   | I2C Extended Mode Register (ICEMDR)                                 |     |

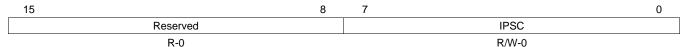

|   |        | 9.3.12   | I2C Prescaler Register (ICPSC)                                      |     |

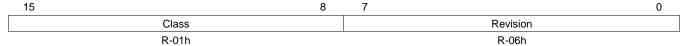

|   |        | 9.3.13   | I2C Peripheral Identification Register (ICPID1)                     |     |

|   |        | 9.3.14   | I2C Peripheral Identification Register (ICPID2)                     | 334 |

| 10 |      | Sound (I2S) Bus                                                             |    |

|----|------|-----------------------------------------------------------------------------|----|

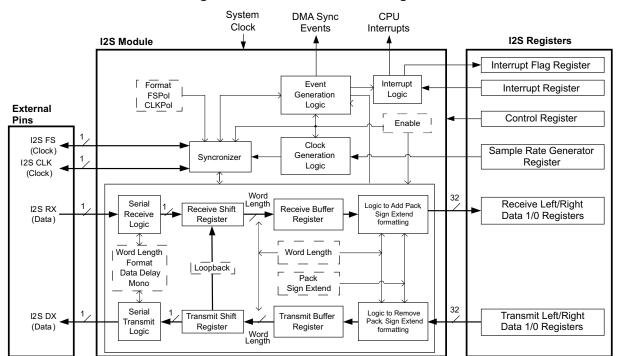

|    | 10.1 | ntroduction                                                                 |    |

|    |      | 10.1.1 Purpose of the Peripheral                                            |    |

|    |      | 10.1.2 Features                                                             |    |

|    |      | 10.1.3 Functional Block Diagram                                             |    |

|    | 40.0 | 10.1.4 Industry Standard(s) Compliance                                      |    |

|    | 10.2 | Architecture                                                                |    |

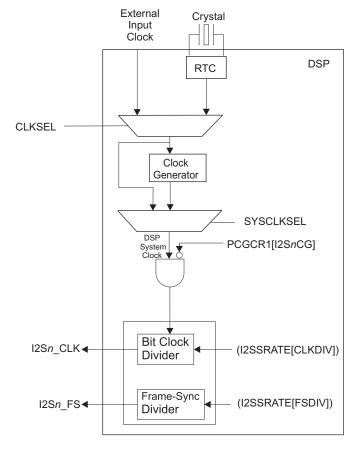

|    |      | 10.2.1 Clock Control                                                        |    |

|    |      | 10.2.2 I2S Clock Generator                                                  |    |

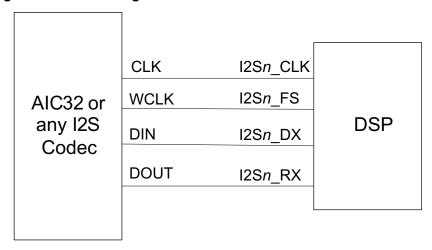

|    |      | 10.2.3 Signal and Pin Descriptions                                          |    |

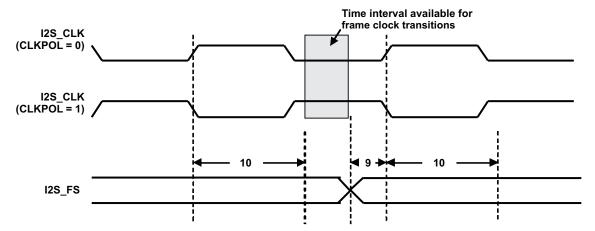

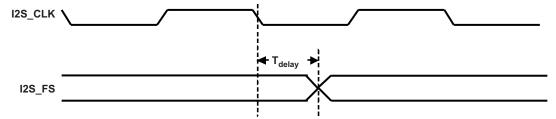

|    |      | 10.2.4 Frame Clock Timing Requirement in Slave Mode                         |    |

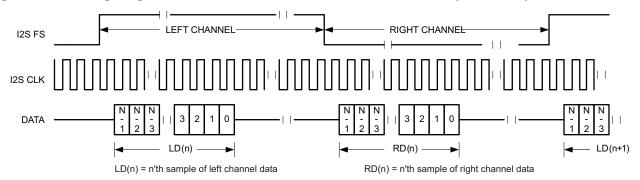

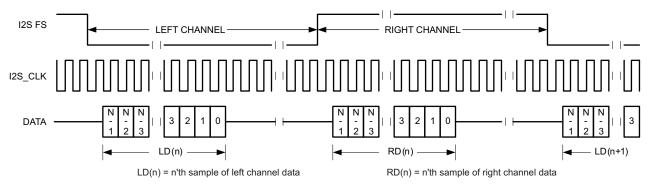

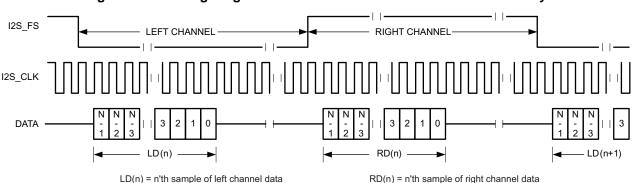

|    |      | 10.2.5 Protocol Description                                                 |    |

|    |      | 10.2.6 I2S Data Transfer and Control Behavior                               |    |

|    |      | 10.2.7 I2S Data Transfer Latency                                            |    |

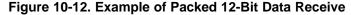

|    |      | 10.2.8 Data Packing and Sign Extension Options                              |    |

|    |      | 10.2.9 Reset Considerations                                                 |    |

|    |      | 10.2.10 Interrupt Support                                                   |    |

|    |      | 10.2.11 DMA Event Support                                                   |    |

|    |      | 10.2.12 Power Management                                                    |    |

|    |      | 10.2.13 Emulation Considerations                                            |    |

|    | 40.0 | 10.2.14 Steps for I2S Configuration and I2S Interrupt Service Routine (ISR) |    |

|    | 10.3 | Registers                                                                   |    |

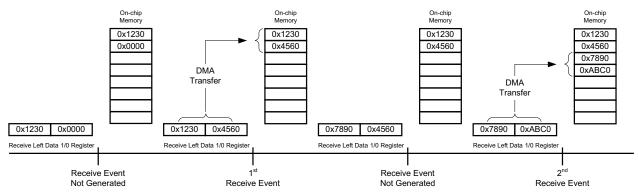

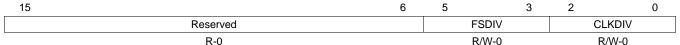

|    |      | 10.3.1 I2Sn Serializer Control Register (I2SSCTRL)                          |    |

|    |      | 10.3.2 I2Sn Sample Rate Generator Register (I2SSRATE)                       |    |

|    |      | 10.3.3 I2Sn Transmit Left Data 0 Register (I2STXLT0)                        |    |

|    |      | 10.3.4 I2Sn Transmit Left Data 1 Register (I2STXLT1)                        |    |

|    |      | 10.3.5 I2Sn Transmit Right Data 0 Register (I2STXRT0)                       |    |

|    |      | 10.3.6 I2S <i>n</i> Transmit Right Data 1 Register (I2STXRT1)               |    |

|    |      | 10.3.7 I2Sn Interrupt Flag Register (I2SINTFL)                              |    |

|    |      | 10.3.8 I2S <i>n</i> Interrupt Mask Register (I2SINTMASK)                    |    |

|    |      | 10.3.9 I2Sn Receive Left Data 0 Register (I2SRXLT0)                         |    |

|    |      | 10.3.10 I2Sn Receive Left Data 1 Register (I2SRXLT1)                        |    |

|    |      | 10.3.11 I2Sn Receive Right Data 0 Register (I2SRXRT0)                       |    |

|    |      | 10.3.12 I2Sn Receive Right Data 1 Register (I2SRXRT1)                       |    |

| 11 | Succ | ssive Approximation (SAR) Analog-to-Digital Converter (ADC)                 |    |

|    | 11.1 | ntroduction                                                                 |    |

|    |      | 11.1.1 Purpose of the 10-bit SAR                                            | 64 |

|    |      | 11.1.2 Features                                                             |    |

|    |      | 11.1.3 Supported Use Case Statement                                         |    |

|    |      | 11.1.4 Industry Standard(s) Compliance Statement                            |    |

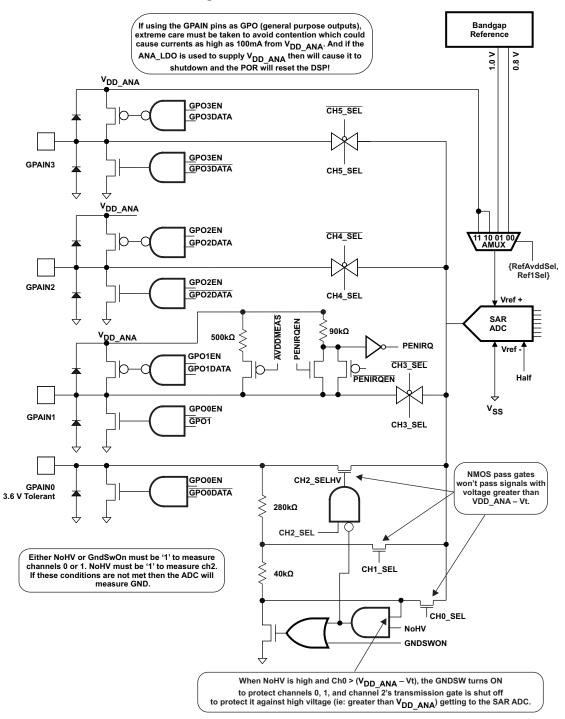

|    |      | 11.1.5 Functional Block Diagram                                             | 65 |

|    | 11.2 | SAR Architecture                                                            | 66 |

|    |      | 11.2.1 SAR Clock Control                                                    | 66 |

|    |      | 11.2.2 Memory Map                                                           | 66 |

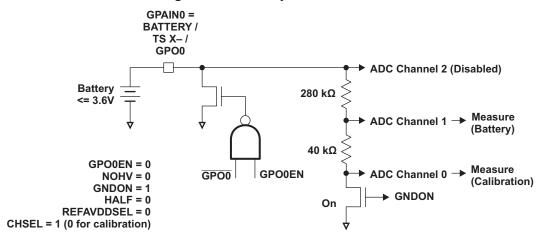

|    |      | 11.2.3 Signal Descriptions                                                  | 66 |

|    |      | 11.2.4 Battery Measurement                                                  | 66 |

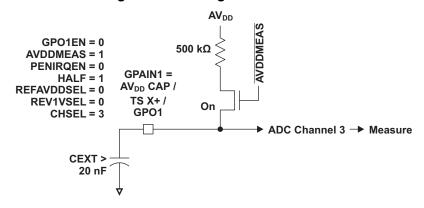

|    |      | 11.2.5 Internal Voltage Measurement                                         | 67 |

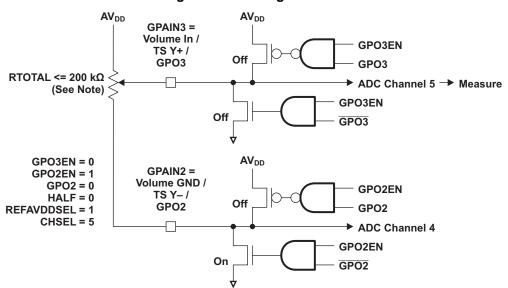

|    |      | 11.2.6 Volume Control                                                       | 67 |

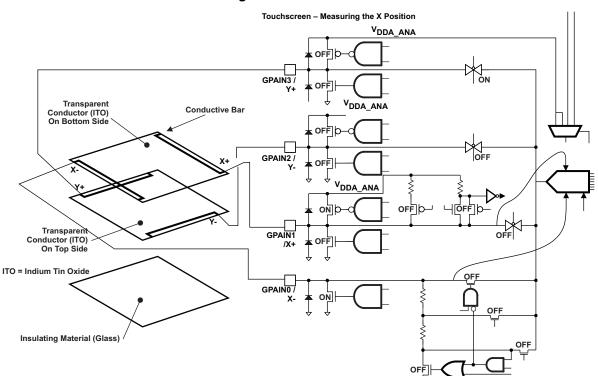

|    |      | 11.2.7 Touch Screen Digitizing                                              | 68 |

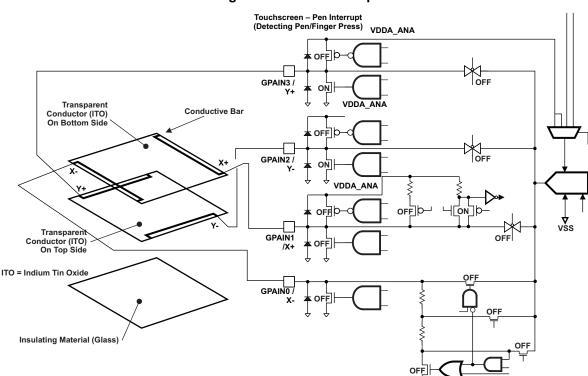

|    |      | 11.2.8 Touch Screen: Pen Press Interrupts                                   | 70 |

|    |      | 11.2.9 General-Purpose Output                                               | 70 |

|    |      | 11.2.10 Reset Considerations                                                | 71 |

|    |      | 11.2.11 A/D Conversion                                                      | 71 |

|    |       |          | Interrupt Support                                                 |      |

|----|-------|----------|-------------------------------------------------------------------|------|

|    |       |          | Emulation Considerations                                          |      |

|    | 11.3  |          | rs                                                                |      |

|    |       |          | SAR A/D Control Register (SARCTRL)                                |      |

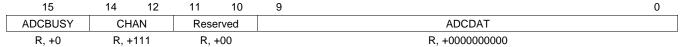

|    |       | 11.3.2   | SAR A/D Data Register (SARDATA)                                   |      |

|    |       | 11.3.3   | SAR A/D Clock Control Register (SARCLKCTRL)                       |      |

|    |       | 11.3.4   | SAR A/D Reference and Pin Control Register (SARPINCTRL)           |      |

|    |       | 11.3.5   | SAR A/D GPO Control Register (SARGPOCTRL)                         | 378  |

|    |       | 11.3.6   | Conversion Example                                                | 379  |

| 12 | Gene  | ral-Pur  | pose Input/Output (GPIO)                                          | 380  |

|    | 12.1  | Introduc | ction                                                             | 381  |

|    |       | 12.1.1   | Purpose of the Peripheral                                         | 381  |

|    |       | 12.1.2   | Features                                                          | 381  |

|    |       | 12.1.3   | Industry Standard(s) Compliance Statement                         | 381  |

|    | 12.2  | Periphe  | ral Architecture                                                  | 381  |

|    |       | 12.2.1   | Clock Control                                                     | 381  |

|    |       | 12.2.2   | Signal Descriptions                                               | 381  |

|    |       | 12.2.3   | GPIO Register Structure                                           | 384  |

|    |       | 12.2.4   | Using a GPIO Signal as an Output                                  | 384  |

|    |       | 12.2.5   | Using a GPIO Signal as an Input                                   | 384  |

|    |       | 12.2.6   | Reset Considerations                                              | 384  |

|    |       | 12.2.7   | Interrupt Support                                                 | 385  |

|    | 12.3  | Registe  | rs                                                                | 386  |

|    |       | -        | GPIO Direction Registers (IODIR1 and IODIR2)                      |      |

|    |       |          | GPIO Data In Registers (IOINDATA1 and IOINDATA2)                  |      |

|    |       |          | GPIO Data Out Registers (IOOUTDATA1 and IOOUTDATA2)               |      |

|    |       |          | GPIO Interrupt Edge Trigger Registers (IOINTEDG1 and IOINTEDG2)   |      |

|    |       | 12.3.5   | GPIO Interrupt Enable Registers (IOINTEN1 and IOINTEN2)           |      |

|    |       | 12.3.6   | GPIO Interrupt Flag Registers (IOINTFLG1 and IOINTFLG2)           |      |

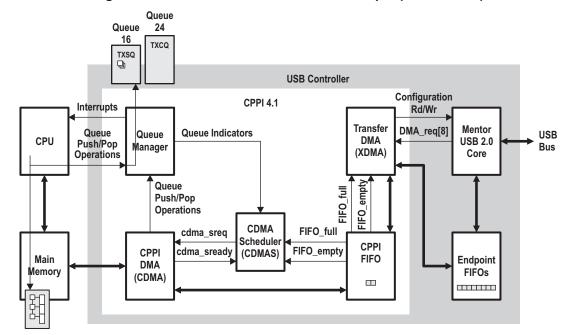

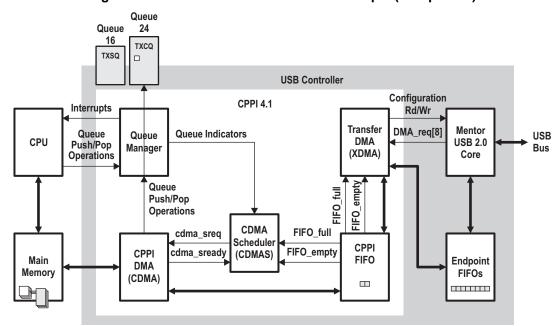

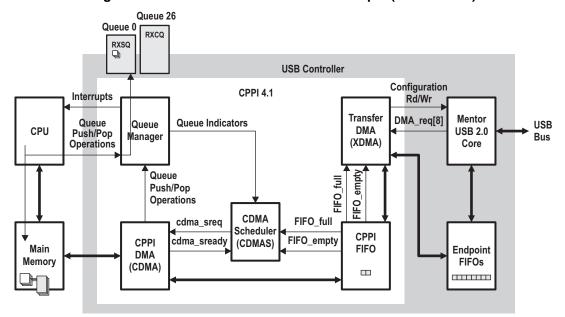

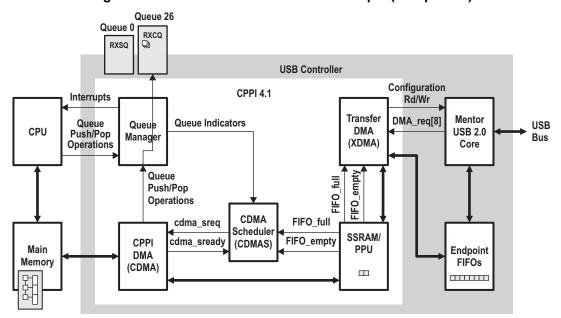

| 13 | Unive | rsal Se  | rial Bus (USB) Controller                                         | 393  |

|    | 13.1  | Introduc | ction                                                             | 394  |

|    |       | 13.1.1   | Purpose of the Peripheral                                         | 394  |

|    |       | 13.1.2   | Features                                                          | 394  |

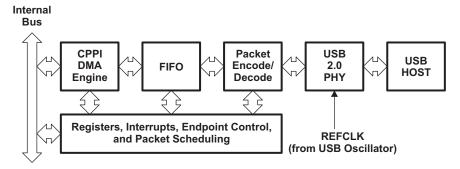

|    |       | 13.1.3   | Functional Block Diagram                                          |      |

|    |       | 13.1.4   | Industry Standard(s) Compliance Statement                         |      |

|    | 13.2  |          | cture                                                             | 395  |

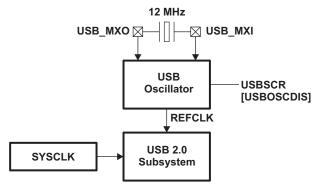

|    |       | 13.2.1   | Clock Control                                                     |      |

|    |       | 13.2.2   | Signal Descriptions                                               |      |

|    |       | 13.2.3   | Memory Map                                                        |      |

|    |       | 13.2.4   | USB_DP/USB_DM Polarity Inversion                                  |      |

|    |       | 13.2.5   | Indexed and Non-Indexed Registers                                 |      |

|    |       | 13.2.6   | USB PHY Initialization                                            |      |

|    |       | 13.2.7   | Dynamic FIFO Sizing                                               |      |

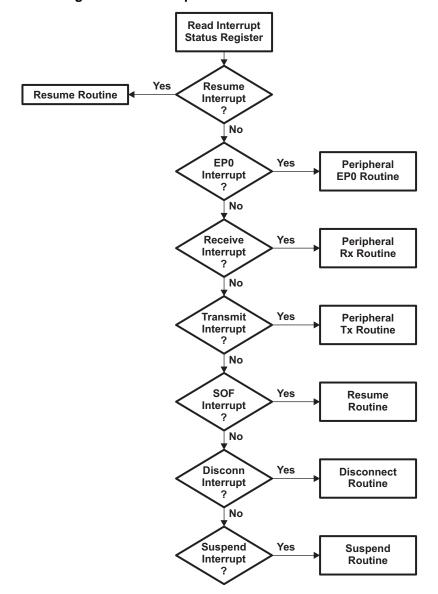

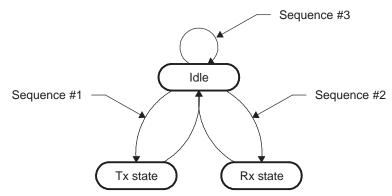

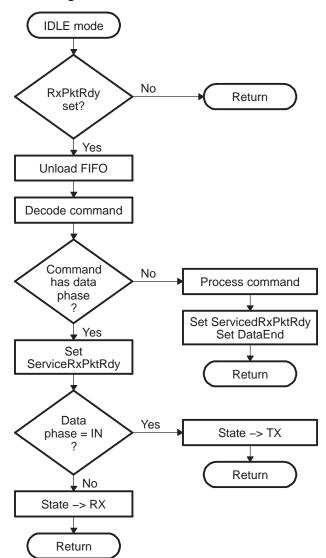

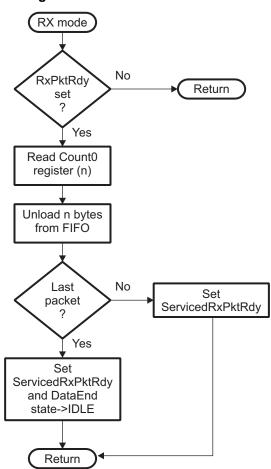

|    |       | 13.2.8   | USB Controller Peripheral Mode Operation                          |      |

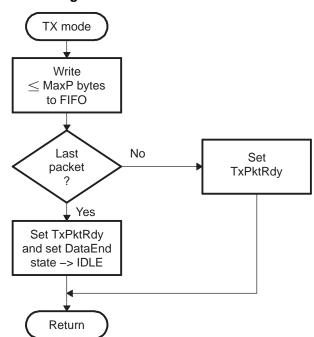

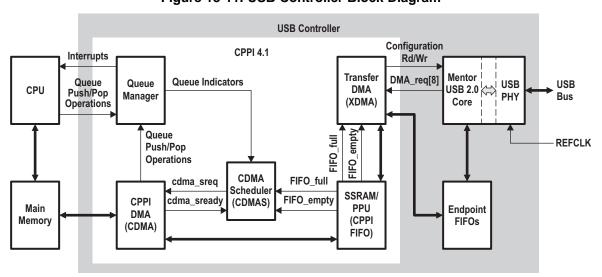

|    |       |          | Communications Port Programming Interface (CPPI) 4.1 DMA Overview |      |

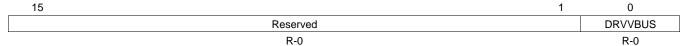

|    |       |          | BYTEMODE Bits of the USB System Control Register                  |      |

|    |       | 13.2.11  |                                                                   |      |

|    |       | 13.2.11  |                                                                   |      |

|    |       | 13.2.12  |                                                                   |      |

|    |       |          | Power Management                                                  |      |

|    | 13.3  | Registe  | ·                                                                 |      |

|    | 10.0  | •        | USB Controller Register Summary                                   |      |

|    |       |          | Revision Identification Registers (REVID1 and REVID2)             |      |

|    |       |          |                                                                   | 1 10 |

| 13.3.3  | Control Register (CTRLR)                                                       | 450 |

|---------|--------------------------------------------------------------------------------|-----|

| 13.3.4  | Status Register (STATR)                                                        | 450 |

| 13.3.5  | Emulation Register (EMUR)                                                      | 451 |

| 13.3.6  | Mode Registers (MODE1 and MODE2)                                               | 452 |

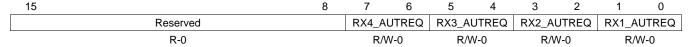

| 13.3.7  | Auto Request Register (AUTOREQ)                                                | 454 |

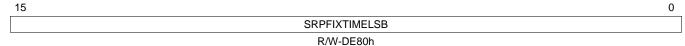

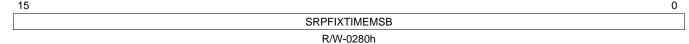

| 13.3.8  | SRP Fix Time Registers (SRPFIXTIME1 and SRPFIXTIME2)                           | 455 |

| 13.3.9  | Teardown Registers (TEARDOWN1 and TEARDOWN2)                                   | 456 |

| 13.3.10 | USB Interrupt Source Registers (INTSRCR1 and INTSRCR2)                         | 457 |

| 13.3.11 | USB Interrupt Source Set Registers (INTSETR1 and INTSETR2)                     | 458 |

| 13.3.12 | USB Interrupt Source Clear Registers (INTCLRR1 and INTCLRR2)                   | 459 |

| 13.3.13 | USB Interrupt Mask Registers (INTMSKR1 and INTMSKR2)                           | 460 |

| 13.3.14 | USB Interrupt Mask Set Registers (INTMSKSETR1 and INTMSKSETR2)                 | 461 |

| 13.3.15 | USB Interrupt Mask Clear Registers (INTMSKCLRR1 and INTMSKCLRR2)               | 462 |

| 13.3.16 | USB Interrupt Source Masked Registers (INTMASKEDR1 and INTMASKEDR2)            | 463 |

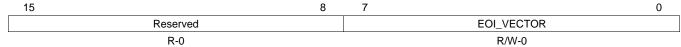

| 13.3.17 | USB End of Interrupt Register (EOIR)                                           | 464 |

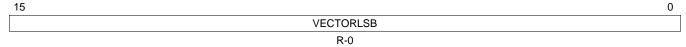

| 13.3.18 | USB Interrupt Vector Registers (INTVECTR1 and INTVECTR2)                       | 464 |

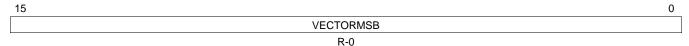

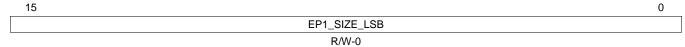

| 13.3.19 | Generic RNDIS EP1 Size Registers (GREP1SZR1 and GREP1SZR2)                     | 465 |

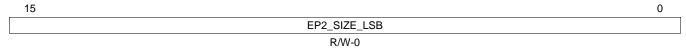

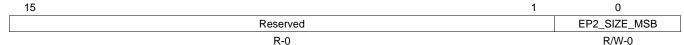

| 13.3.20 | Generic RNDIS EP2 Size Registers (GREP2SZR1 and GREP2SZR2)                     | 466 |

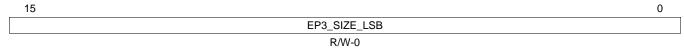

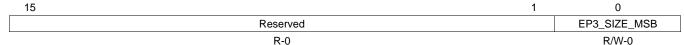

| 13.3.21 | Generic RNDIS EP3 Size Registers (GREP3SZR1 and GREP3SZR2)                     | 467 |

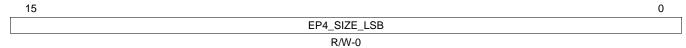

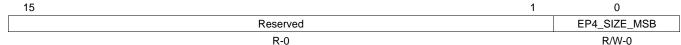

| 13.3.22 | Generic RNDIS EP4 Size Registers (GREP4SZR1 and GREP4SZR2)                     | 468 |

| 13.3.23 | Function Address Register (FADDR)                                              | 469 |

| 13.3.24 | Power Management Register (POWER)                                              | 469 |

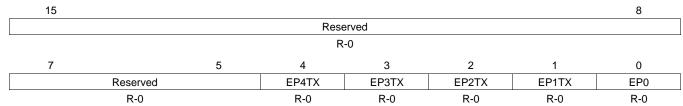

| 13.3.25 | Interrupt Register for Endpoint 0 Plus Transmit Endpoints 1 to 4 (INTRTX)      | 470 |

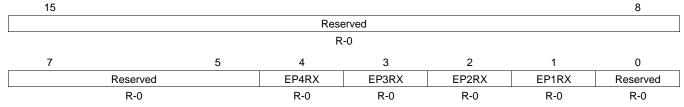

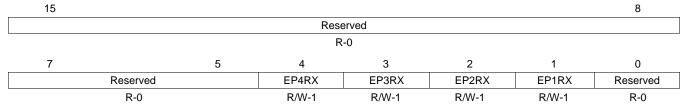

| 13.3.26 | Interrupt Register for Receive Endpoints 1 to 4 (INTRRX)                       | 470 |

| 13.3.27 | Interrupt Enable Register for INTRTX (INTRTXE)                                 | 471 |

| 13.3.28 | Interrupt Enable Register for INTRRX (INTRRXE)                                 | 471 |

| 13.3.29 | Interrupt Register for Common USB Interrupts (INTRUSB)                         | 472 |

| 13.3.30 | Interrupt Enable Register for INTRUSB (INTRUSBE)                               | 473 |

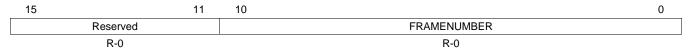

| 13.3.31 | Frame Number Register (FRAME)                                                  | 473 |

| 13.3.32 | Index Register for Selecting the Endpoint Status and Control Registers (INDEX) | 474 |

| 13.3.33 | Register to Enable the USB 2.0 Test Modes (TESTMODE)                           | 474 |

| 13.3.34 | Maximum Packet Size for Peripheral/Host Transmit Endpoint (TXMAXP)             | 475 |

| 13.3.35 | Control Status Register for Peripheral Endpoint 0 (PERI_CSR0)                  | 476 |

| 13.3.36 | Control Status Register for Peripheral Transmit Endpoint (PERI_TXCSR)          | 477 |

| 13.3.37 | Maximum Packet Size for Peripheral Receive Endpoint (RXMAXP)                   | 478 |

| 13.3.38 |                                                                                |     |

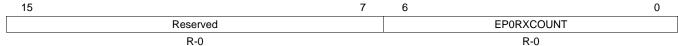

| 13.3.39 | Count 0 Register (COUNT0)                                                      | 480 |

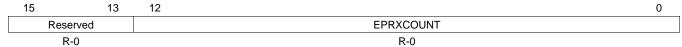

| 13.3.40 | Receive Count Register (RXCOUNT)                                               | 480 |

| 13.3.41 | Configuration Data Register (CONFIGDATA)                                       | 481 |

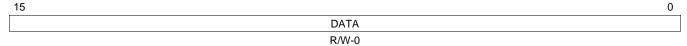

| 13.3.42 | Transmit and Receive FIFO Registers for Endpoint 0 (FIFO0R1 and FIFO0R2)       | 482 |

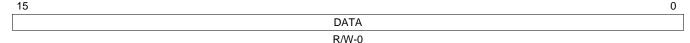

| 13.3.43 | Transmit and Receive FIFO Registers for Endpoint 1 (FIFO1R1 and FIFO1R2)       | 483 |

| 13.3.44 | Transmit and Receive FIFO Registers for Endpoint 2 (FIFO2R1 and FIFO2R2)       | 484 |

| 13.3.45 | Transmit and Receive FIFO Registers for Endpoint 3 (FIFO3R1 and FIFO3R2)       | 485 |

| 13.3.46 | Transmit and Receive FIFO Registers for Endpoint 4 (FIFO4R1 and FIFO4R2)       | 486 |

| 13.3.47 |                                                                                |     |

| 13.3.48 | ·                                                                              |     |

| 13.3.49 | Receive Endpoint FIFO Size (RXFIFOSZ)                                          | 488 |

| 13.3.50 | Transmit Endpoint FIFO Address (TXFIFOADDR)                                    | 489 |

| 13.3.51 | Hardware Version Register (HWVERS)                                             | 489 |

| 13.3.52 | ·                                                                              |     |

| 13.3.53 | ·                                                                              |     |

| 13.3.54 | ·                                                                              |     |

| 13.3.55 | CDMA Emulation Control Register (DMAEMU)                                       | 491 |

|    |       | 13.3.56      | CDMA Transmit Channel n Global Configuration Registers (TXGCR1[n] and TXGCR2[n])              | 492 |

|----|-------|--------------|-----------------------------------------------------------------------------------------------|-----|

|    |       | 13.3.57      | CDMA Receive Channel n Global Configuration Registers (RXGCR1[n] and RXGCR2[n])               | 493 |

|    |       | 13.3.58<br>F | CDMA Receive Channel n Host Packet Configuration Registers A (RXHPCR1A[n] and RXHPCR2A[n])    | 495 |

|    |       | 13.3.59<br>F | CDMA Receive Channel n Host Packet Configuration Registers B (RXHPCR1B[n] and RXHPCR2B[n])    | 496 |

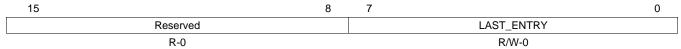

|    |       | 13.3.60      | CDMA Scheduler Control Register (DMA_SCHED_CTRL1 and DMA_SCHED_CTRL2)                         | 497 |

|    |       | 13.3.61      | CDMA Scheduler Table Word n Registers (ENTRYLSW[n]-ENTRYMSW[n])                               | 498 |

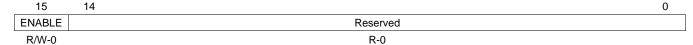

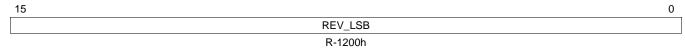

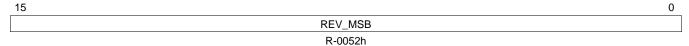

|    |       | 13.3.62      | Queue Manager Revision Identification Registers (QMGRREVID1 and QMGRREVID2)                   | 499 |

|    |       | 13.3.63      | Queue Manager Queue Diversion Registers (DIVERSION1 and DIVERSION2)                           | 500 |

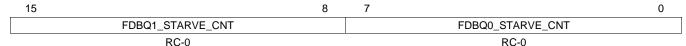

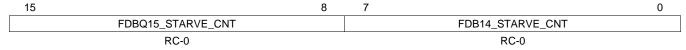

|    |       | 13.3.64      | Queue Manager Free Descriptor/Buffer Starvation Count Register 0 (FDBSC0)                     | 501 |

|    |       | 13.3.65      | Queue Manager Free Descriptor/Buffer Starvation Count Register 1 (FDBSC1)                     | 501 |

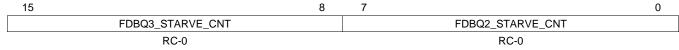

|    |       | 13.3.66      | Queue Manager Free Descriptor/Buffer Starvation Count Register 2 (FDBSC2)                     | 502 |

|    |       | 13.3.67      | Queue Manager Free Descriptor/Buffer Starvation Count Register 3 (FDBSC3)                     | 502 |

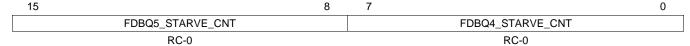

|    |       | 13.3.68      | Queue Manager Free Descriptor/Buffer Starvation Count Register 4 (FDBSC4)                     | 503 |

|    |       | 13.3.69      | Queue Manager Free Descriptor/Buffer Starvation Count Register 5 (FDBSC5)                     | 503 |

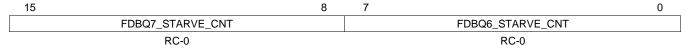

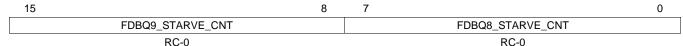

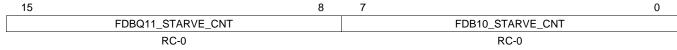

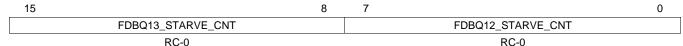

|    |       | 13.3.70      | Queue Manager Free Descriptor/Buffer Starvation Count Register 6 (FDBSC6)                     | 504 |

|    |       | 13.3.71      | Queue Manager Free Descriptor/Buffer Starvation Count Register 7 (FDBSC7)                     | 504 |

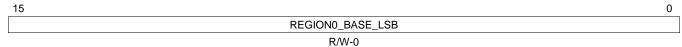

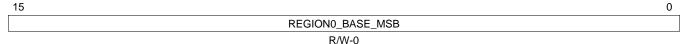

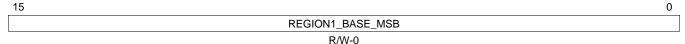

|    |       |              | Queue Manager Linking RAM Region 0 Base Address Registers (LRAM0BASE1 and RAM0BASE2)          | 505 |

|    |       | 13.3.73      | Queue Manager Linking RAM Region 0 Size Register (LRAM0SIZE)                                  | 506 |

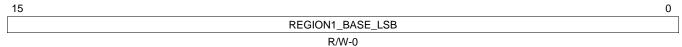

|    |       | 13.3.74      | Queue Manager Linking RAM Region 1 Base Address Registers (LRAM1BASE1 and RAM1BASE2)          |     |

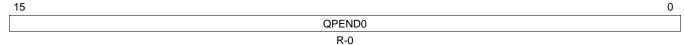

|    |       |              | Queue Manager Queue Pending Register 0 (PEND0)                                                |     |

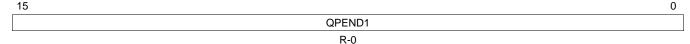

|    |       | 13.3.76      | Queue Manager Queue Pending Register 1 (PEND1)                                                | 508 |

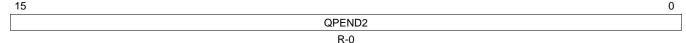

|    |       | 13.3.77      | Queue Manager Queue Pending Register 2 (PEND2)                                                | 509 |

|    |       |              | Queue Manager Queue Pending Register 3 (PEND3)                                                |     |

|    |       | 13.3.79      | Queue Manager Queue Pending Register 4 (PEND4)                                                | 510 |

|    |       | 13.3.80      | Queue Manager Queue Pending Register 5 (PEND5)                                                | 510 |

|    |       | 13.3.81<br>C | Queue Manager Memory Region <i>R</i> Base Address Registers (QMEMRBASE1[R] and QMEMRBASE2[R]) | 511 |

|    |       | 13.3.82      | Queue Manager Memory Region R Control Registers (QMEMRCTRL1[R] and QMEMRCTRL2[R])             | 512 |

|    |       |              | Queue Manager Queue N Control Register D (CTRL1D[N] and CTRL2D[N])                            |     |

|    |       |              | Queue Manager Queue N Status Register A (QSTATA[N])                                           |     |

|    |       |              | Queue Manager Queue N Status Registers B (QSTAT1B[N] and QSTAT2B[N])                          |     |

|    |       | 13.3.86      | Queue Manager Queue N Status Register C (QSTATC[N])                                           | 515 |

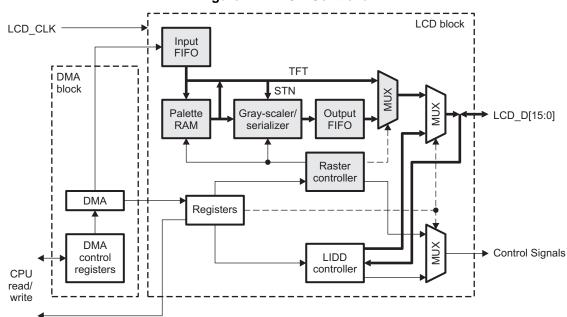

| 14 | Liqui | d Crysta     | I Display Controller (LCDC)                                                                   | 516 |

| •  | 14.1  |              | ion                                                                                           |     |

|    |       |              | Purpose of the Peripheral                                                                     |     |

|    |       |              | Terminology Used in this Document                                                             |     |

|    |       |              | LCD External I/O Signals                                                                      |     |

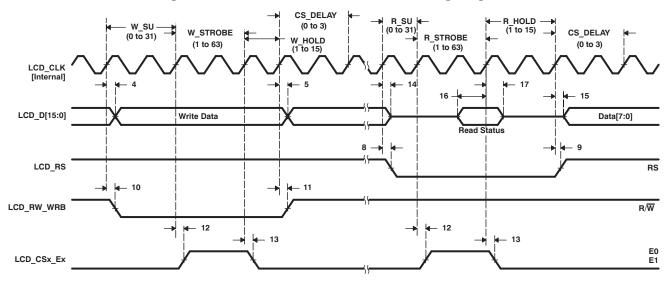

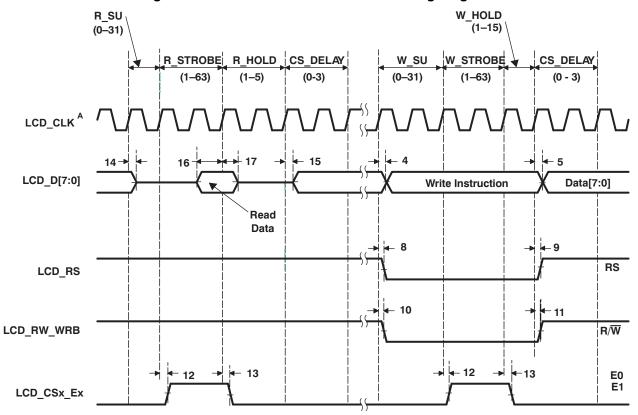

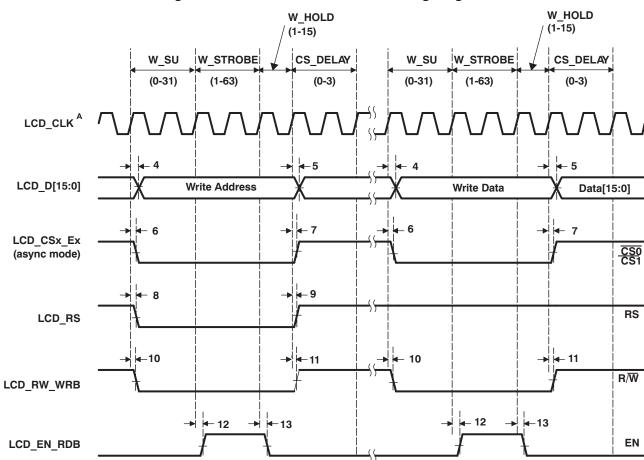

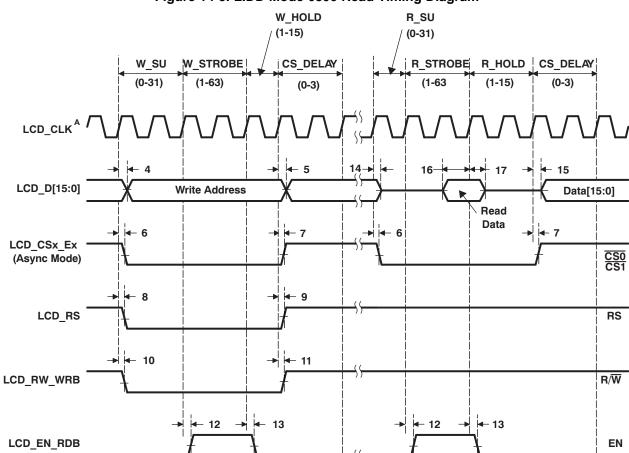

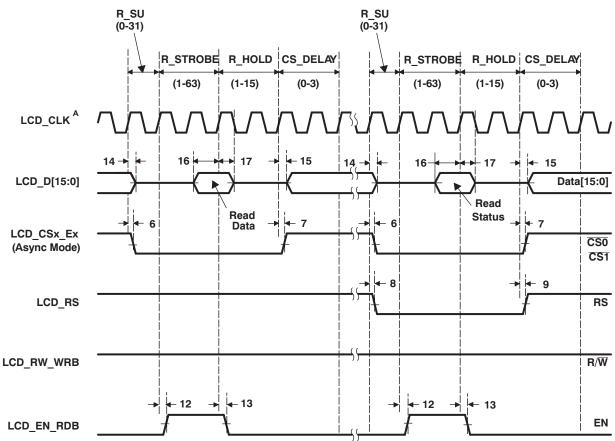

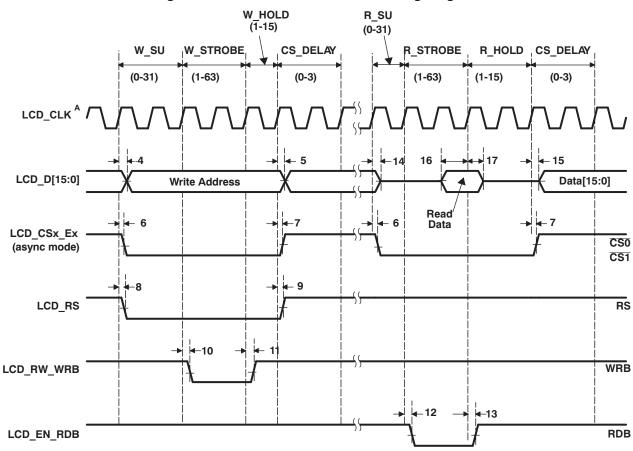

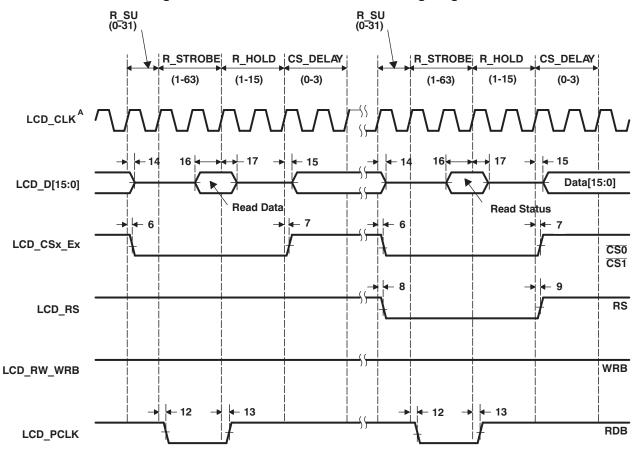

|    |       |              | LCD Interface Display Driver Details (LIDD) Controller                                        |     |

|    |       |              | LIDD Controller Timing                                                                        |     |

|    |       |              | DMA Engine                                                                                    |     |

|    | 14.2  |              | t Mapping                                                                                     |     |

|    | 14.3  |              | S                                                                                             |     |

|    |       | •            | LCD Minor Revision Register (LCDREVMIN)                                                       |     |

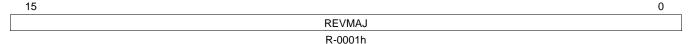

|    |       |              | LCD Major Revision Register (LCDREVMAJ)                                                       |     |

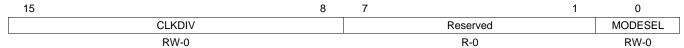

|    |       |              | LCD Control Register (LCDCR)                                                                  |     |

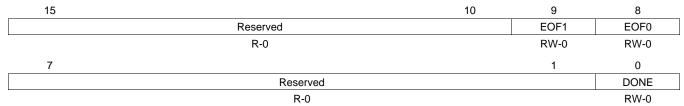

|    |       |              | LCD Status Register (LCDSR)                                                                   |     |

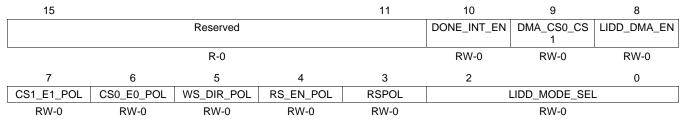

|    |       |              | LCD LIDD Control Register (LCDLIDDCR)                                                         |     |

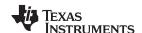

|    |       | 14.3.6       | LCD LIDD CS0 and CS1 Configuration Register 0 (LCDLIDDCS0CONFIG0 and CDLIDDCS1CONFIG0)        |     |

|    |       |              | LCD LIDD CS0 and CS1 Configuration Register 1 (LCDLIDDCS0CONFIG1 and                          |     |

|   | LCDLIDDCS1CONFIG1)                                                                   |       | 536         |

|---|--------------------------------------------------------------------------------------|-------|-------------|

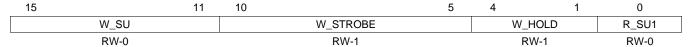

|   | 14.3.8 LCD LIDD CS0 and CS1 Address Read/Write Register (LCDLIDDCS0A LCDLIDDCS1ADDR) |       | 537         |

|   | 14.3.9 LCD LIDD CS0 and CS1 Data Read/Write Register (LCDLIDDCS0DAT, LCDLIDDCS1DATA) | A and |             |

|   | 14.3.10 LCD DMA Control Register (LCDDMACR)                                          |       |             |

|   | 14.3.11 LCD DMA Frame Buffer 0 Base Address Register 0 (LCDDMAFB0BAI                 |       |             |

|   | 14.3.12 LCD DMA Frame Buffer 0 Base Address Register 1 (LCDDMAFB0BAI                 | R1)   | 540         |

|   | 14.3.13 LCD DMA Frame Buffer 0 Ceiling Address Register 0 (LCDDMAFB0C                | AR0)  | 541         |

|   | 14.3.14 LCD DMA Frame Buffer 0 Ceiling Address Register 1 (LCDDMAFB0C                | AR1)  | 541         |

|   | 14.3.15 LCD DMA Frame Buffer 1 Base Address Register 0 (LCDDMAFB1BAI                 | RO)   | 542         |

|   | 14.3.16 LCD DMA Frame Buffer 1 Base Address Register 1 (LCDDMAFB1BAI                 | R1)   | 542         |

|   | 14.3.17 LCD DMA Frame Buffer 1 Ceiling Address Register 0 (LCDDMAFB1C                |       |             |

|   | 14.3.18 LCD DMA Frame Buffer 1 Ceiling Address Register 1 (LCDDMAFB1C                | AR1)  | <b>54</b> 3 |

| Α | Revision History                                                                     |       | 544         |

## **List of Figures**

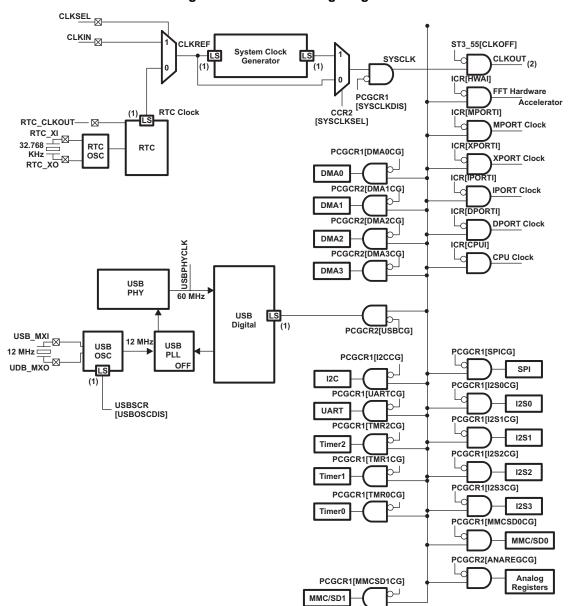

| 1-1.  | Functional Block Diagram                                             | 36         |

|-------|----------------------------------------------------------------------|------------|

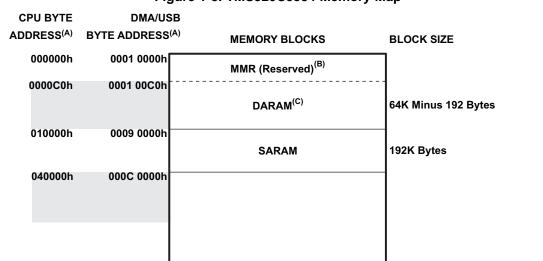

| 1-2.  | TMS320C5535 Memory Map                                               | 40         |

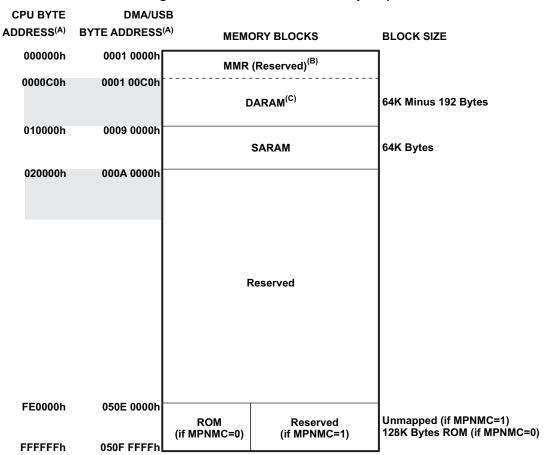

| 1-3.  | TMS320C5534 Memory Map                                               | 41         |

| 1-4.  | TMS320C5533 Memory Map                                               | 42         |

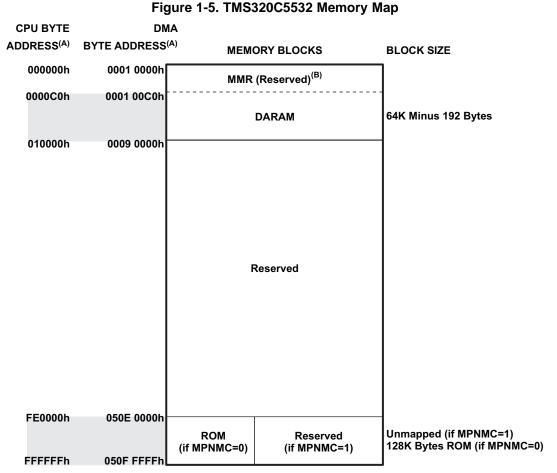

| 1-5.  | TMS320C5532 Memory Map                                               | 43         |

| 1-6.  | DSP Clocking Diagram                                                 | 47         |

| 1-7.  | Clock Generator                                                      | 49         |

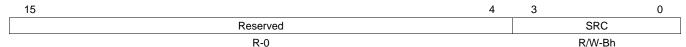

| 1-8.  | CLKOUT Control Source Select Register (CCSSR) [1C24h]                | 50         |

| 1-9.  | Clock Generator Control Register 1 (CGCR1) [1C20h]                   | 56         |

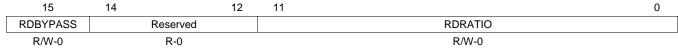

| 1-10. | Clock Generator Control Register 2 (CGCR2) [1C21h]                   | 56         |

| 1-11. | Clock Generator Control Register 3 (CGCR3) [1C22h]                   | 57         |

| 1-12. | Clock Generator Control Register 4 (CGCR4) [1C23h]                   | 57         |

| 1-13. | Clock Configuration Register 2 (CCR2) [1C1Fh]                        |            |

| 1-14. | Idle Configuration Register (ICR) [0001h]                            | 62         |

| 1-15. | Idle Status Register (ISTR) [0002h]                                  |            |

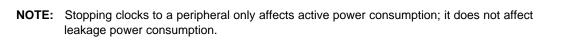

| 1-16. | Peripheral Clock Gating Configuration Register 1 (PCGCR1) [1C02h]    | 65         |

| 1-17. | Peripheral Clock Gating Configuration Register 2 (PCGCR2) [1C03h]    |            |

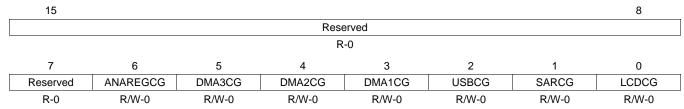

| 1-18. | Peripheral Clock Stop Request/Acknowledge Register (CLKSTOP) [1C3Ah] |            |

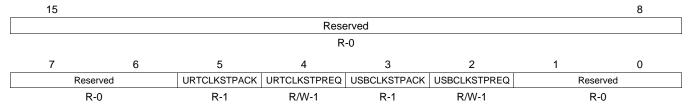

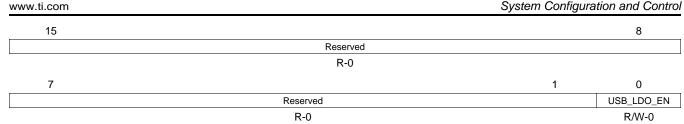

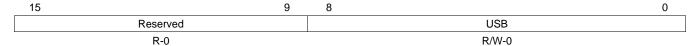

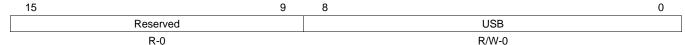

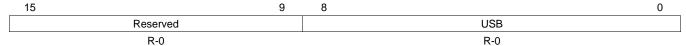

| 1-19. | USB System Control Register (USBSCR) [1C32h]                         | 70         |

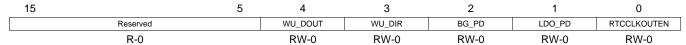

| 1-20. | RTC Power Management Register (RTCPMGT) [1930h]                      | 72         |

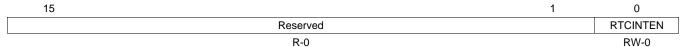

| 1-21. | RTC Interrupt Flag Register (RTCINTFL) [1920h]                       | 73         |

| 1-22. | RAM Sleep Mode Control Register1 [0x1C28]                            | 74         |

| 1-23. | RAM Sleep Mode Control Register2 [0x1C2A]                            | 75         |

| 1-24. | RAM Sleep Mode Control Register3 [0x1C2B]                            | 75         |

| 1-25. | RAM Sleep Mode Control Register4 [0x1C2C]                            | 75         |

| 1-26. | RAM Sleep Mode Control Register5 [0x1C2D]                            | 75         |

| 1-27. | RTC Power Management Register (RTCPMGT) [1930h]                      | 78         |

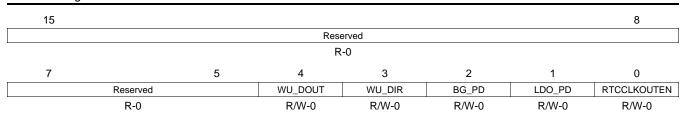

| 1-28. | LDO Control Register (LDOCNTL) [7004h]                               | <b>7</b> 9 |

| 1-29. | IFR0 and IER0 Bit Locations                                          | 87         |

| 1-30. | IFR1 and IER1 Bit Locations                                          | 88         |

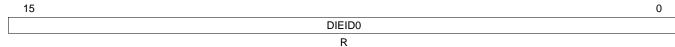

| 1-31. | Die ID Register 0 (DIEIDR0) [1C40h]                                  | 91         |

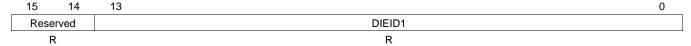

| 1-32. | Die ID Register 1 (DIEIDR1) [1C41h]                                  | 91         |

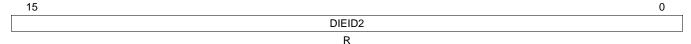

| 1-33. | Die ID Register 2 (DIEIDR2) [1C42h]                                  | 91         |

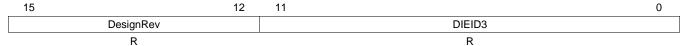

| 1-34. | Die ID Register 3 (DIEIDR3[15:0]) [1C43h]                            | 92         |

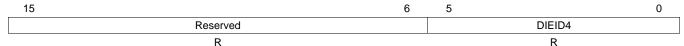

| 1-35. | Die ID Register 4 (DIEIDR4) [1C44h]                                  | 92         |

| 1-36. | Die ID Register 5 (DIEIDR5) [1C45h]                                  | 92         |

| 1-37. | Die ID Register 6 (DIEIDR6) [1C46h]                                  | 93         |

| 1-38. | Die ID Register 7 (DIEIDR7) [1C47h]                                  | 93         |

| 1-39. | External Bus Selection Register (EBSR) [1C00h]                       | 94         |

| 1-40. | RTC Power Management Register (RTCPMGT) [1930h]                      | 96         |

| 1-41. | LDO Control Register (LDOCNTL) [7004h]                               | 97         |

| 1-42. | RTC Power Management Register (RTCPMGT) [1930h]                      | 98         |

| 1-43. | LDO Control Register (LDOCNTL) [7004h]                               | 99         |

| 1-44. | Output Slew Rate Control Register (OSRCR) [1C16h]                    | 100        |

| 1-45. |                                                                      | 101        |

| 1-46. |                                                                      | 102        |

| 1-47. | Pull-Down Inhibit Register 3 (PDINHIBR3) [1C19h]                     | 103        |

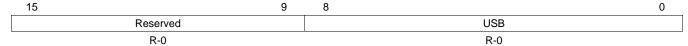

| 1-48. | DMA Interrupt Flag Register (DMAIFR) [1C30h]                                      | 106 |

|-------|-----------------------------------------------------------------------------------|-----|

| 1-49. | DMA Interrupt Enable Register (DMAIER) [1C31h]                                    | 106 |

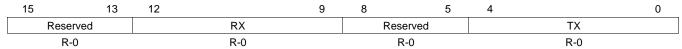

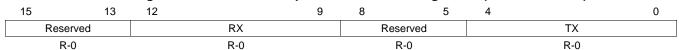

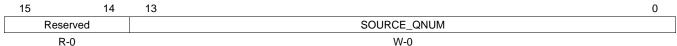

| 1-50. | DMAn Channel Event Source Register 1 (DMAnCESR1) [1C1Ah, 1C1Ch, 1C36h, and 1C38h] | 107 |

| 1-51. | DMAn Channel Event Source Register 2 (DMAnCESR2) [1C1Bh, 1C1Dh, 1C37h, and 1C39h] | 107 |

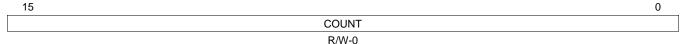

| 1-52. | Peripheral Software Reset Counter Register (PSRCR) [1C04h]                        | 108 |

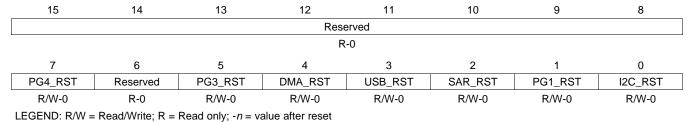

| 1-53. | Peripheral Reset Control Register (PRCR) [1C05h]                                  | 108 |

| 2-1.  | DIT Radix 2 Butterfly                                                             | 113 |

| 2-2.  | DIT Radix 2 8-point FFT                                                           | 114 |

| 2-3.  | Graphical FFT Computation                                                         | 115 |

| 2-4.  | Block Diagram                                                                     | 117 |

| 2-5.  | Bit Reversed Input Buffer                                                         | 122 |

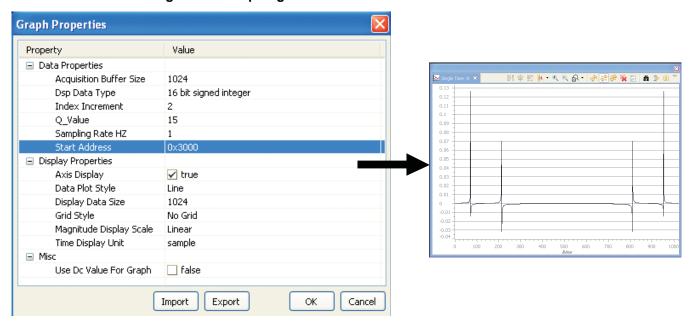

| 2-6.  | Graphing the Real Part of the FFT Result in CCS4                                  |     |

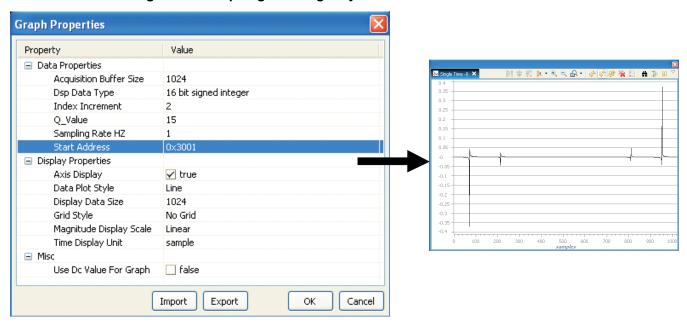

| 2-7.  | Graphing the Imaginary Part of the FFT Result in CCS4                             | 127 |

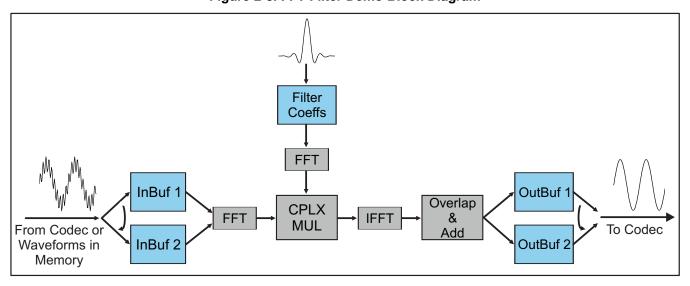

| 2-8.  | FFT Filter Demo Block Diagram                                                     | 130 |

| 3-1.  | Conceptual Block Diagram of the DMA Controller                                    |     |

| 3-2.  | Clocking Diagram for the DMA Controller                                           | 138 |

| 3-3.  | Two-Part DMA Transfer                                                             | 139 |

| 3-4.  | Registers for Controlling the Context of a Channel                                | 140 |

| 3-5.  | Ping-Pong Mode for DMA Data Transfer                                              |     |

| 3-6.  | Block Move Example                                                                |     |

| 3-7.  | Block Move Example DMA Configuration                                              |     |

| 3-8.  | Servicing Incoming I2C Data Example                                               |     |

| 3-9.  | Servicing Incoming I2C Data Example DMA Configuration                             |     |

| 3-10. | Servicing Incoming UART Data Example                                              |     |

| 3-11. | Servicing Incoming UART Data Example DMA Configuration                            |     |

| 3-12. | Servicing Incoming I2S Data Example in Ping-Pong DMA Mode                         |     |

| 3-13. | Servicing Incoming I2S Data Example DMA Configuration                             |     |

| 3-14. | Source Start Address Register - Lower Part (DMACHmSSAL)                           |     |

| 3-15. | Source Start Address Register - Upper Part (DMACHmSSAU)                           |     |

| 3-16. | Destination Start Address Register - Lower Part (DMACHmDSAL)                      |     |

| 3-17. | Destination Start Address Register - Upper Part (DMACHmDSAU)                      |     |

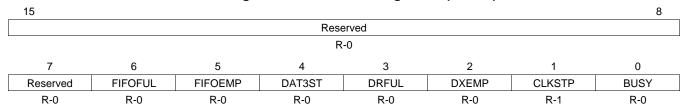

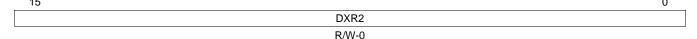

| 3-18. | Transfer Control Register 1 (DMACH <i>m</i> TCR1)                                 |     |

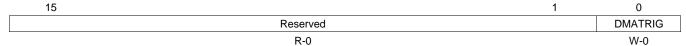

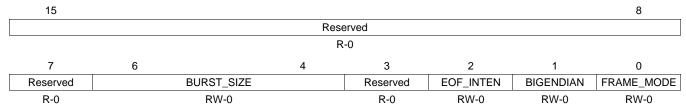

| 3-19. | Transfer Control Register 2 (DMACH <i>m</i> TCR2)                                 |     |

| 4-1.  | Block Diagram                                                                     | 162 |

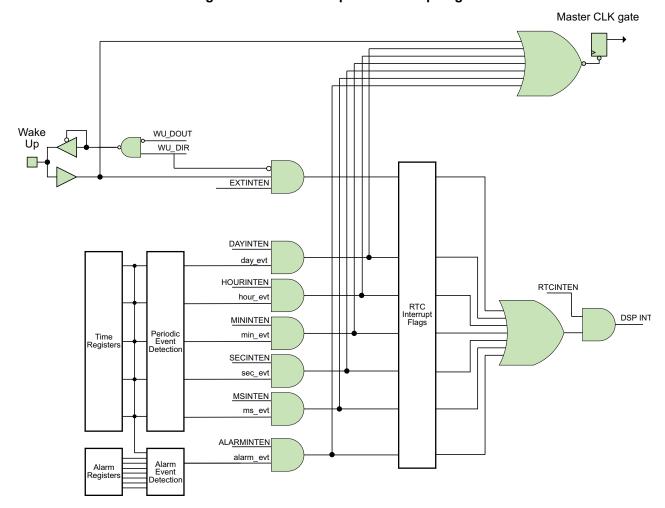

| 4-2.  | RTC Interrupt and Wakeup Logic                                                    | 167 |

| 4-3.  | RTC Interrupt Enable Register (RTCINTEN).                                         | 171 |

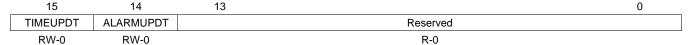

| 4-4.  | RTC Update Register (RTCUPDATE)                                                   | 171 |

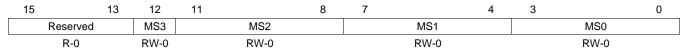

| 4-5.  | Milliseconds Register (RTCMIL)                                                    | 172 |

| 4-6.  | Milliseconds Alarm Register (RTCMILA)                                             | 172 |

| 4-7.  | Seconds Register (RTCSEC)                                                         | 173 |

| 4-8.  | Seconds Alarm Register (RTCSECA)                                                  | 173 |

| 4-9.  | Minutes Register (RTCMIN)                                                         | 174 |

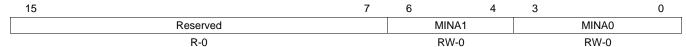

| 4-10. | Minutes Alarm Register (RTCMINA)                                                  | 174 |

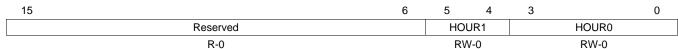

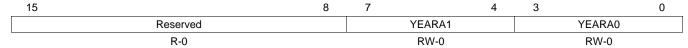

| 4-11. | Hours Register (RTCHOUR)                                                          | 175 |

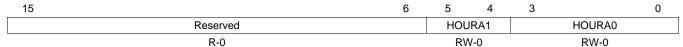

| 4-12. | Hours Alarm Register (RTCHOURA)                                                   | 175 |

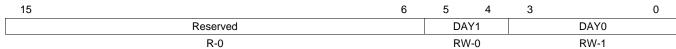

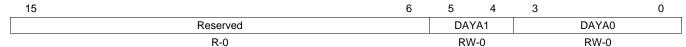

| 4-13. | Days Alarm Register (RTCDAYA)                                                     | 176 |

| 4-14. | Days Alarm Register (RTCDAYA)                                                     | 176 |

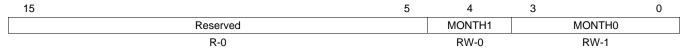

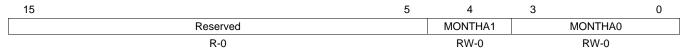

| 4-15. | Months Register (RTCMONTH)                                                        | 177 |

| 4-16. | Months Alarm Register (RTCMONTHA)                                                 | 177 |

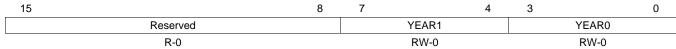

| 4-17. | Years Register (RTCYEAR)                                           | 178 |

|-------|--------------------------------------------------------------------|-----|

| 4-18. | Years Alarm Register (RTCYEARA)                                    | 178 |

| 4-19. | RTC Interrupt Flag Register (RTCINTFL)                             | 179 |

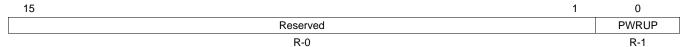

| 4-20. | RTC Lost Power Status Register (RTCNOPWR)                          | 180 |

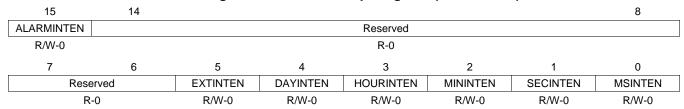

| 4-21. | RTC Interrupt Register (RTCINTREG)                                 | 181 |

| 4-22. | RTC Compensation Register (RTCDRIFT)                               | 182 |

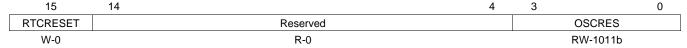

| 4-23. | RTC Oscillator Register (RTCOSC)                                   | 182 |

| 4-24. | RTC Power Management Register (RTCPMGT)                            | 183 |

| 4-25. | RTC LSW Scratch Register 1 (RTCSCR1)                               | 184 |

| 4-26. | RTC MSW Scratch Register 2 (RTCSCR2)                               | 184 |

| 4-27. | RTC LSW Scratch Register 3 (RTCSCR3)                               | 185 |

| 4-28. | RTC MSW Scratch Register 4 (RTCSCR4)                               | 185 |

| 5-1.  | The Architecture and Operation of the GP Timers                    | 188 |

| 5-2.  | 32-Bit GP Timer With a 13-Bit Prescaler                            | 188 |

| 5-3.  | Watchdog Kick Lock Register (WDKCKLK)                              | 192 |

| 5-4.  | Watchdog Kick Register (WDKICK)                                    | 192 |

| 5-5.  | Watchdog Start Value Lock Register (WDSVLR)                        | 193 |

| 5-6.  | Watchdog Start Value Register (WDSVR)                              | 193 |

| 5-7.  | Watchdog Enable Lock Register (WDENLOK)                            | 194 |

| 5-8.  | Watchdog Enable Register (WDEN)                                    | 194 |

| 5-9.  | Watchdog Prescaler Lock Register (WDPSLR)                          | 195 |

| 5-10. | Watchdog Prescaler Register (WDPS)                                 | 195 |

| 5-11. | Timer <i>n</i> Control Register (TCR)                              | 196 |

| 5-12. | Timer <i>n</i> Period Register 1 (TIMPRD1)                         | 197 |

| 5-13. | Timer <i>n</i> Period Register 2 (TIMPRD2)                         | 197 |

| 5-14. | Timer <i>n</i> Counter Register 1 (TIMCNT1)                        | 198 |

| 5-15. | Timer <i>n</i> Counter Register (TIMCNT2)                          | 198 |

| 5-16. | Timer Interrupt Aggregation Flag Register (TIAFR)                  | 199 |

| 6-1.  | eMMC/SD Card Controller Block Diagram                              | 202 |

| 6-2.  | MMC/SD Controller Interface Diagram                                |     |

| 6-3.  | eMMC Configuration and SD Configuration Diagram                    | 203 |

| 6-4.  | eMMC/SD Controller Clocking Diagram                                |     |

| 6-5.  | eMMC/SD Mode Write Sequence Timing Diagram                         | 205 |

| 6-6.  | eMMC/SD Mode Read Sequence Timing Diagram                          | 206 |

| 6-7.  | FIFO Operation Diagram                                             | 207 |

| 6-8.  | Little-Endian Access to SDDXR/SDDRR1 and 2 From the CPU or the DMA | 208 |

| 6-9.  | Big-Endian Access to SDDXR/SDDRR1 and 2 From the CPU or the DMA    | 209 |

| 6-10. | FIFO Operation During Card Read Diagram                            | 211 |

| 6-11. | FIFO Operation During Card Write Diagram                           | 212 |

| 6-12. | Card Identification (Native eMMC/SD Mode)                          | 218 |

| 6-13. | eMMC/SD Mode Single-Block Write Operation                          | 220 |

| 6-14. | eMMC/SD Mode Single-Block Read Operation                           | 222 |

| 6-15. | eMMC/SD Multiple-Block Write Operation                             | 224 |

| 6-16. | eMMC/SD Mode Multiple-Block Read Operation                         | 226 |

| 6-17. | SD Control Register (SDCTL)                                        | 230 |

| 6-18. | SD Memory Clock Control Register (SDCLK)                           | 231 |

| 6-19. | SD Status Register 0 (SDST0)                                       | 232 |

| 6-20. | SD Status Register 1 (SDST1)                                       | 234 |

| 6-21. | SD Interrupt Mask Register (SDIM)                                  | 235 |

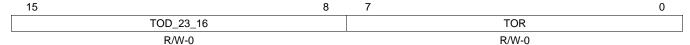

| 6-22. | SD Response Time-Out Register (SDTOR)                     | 236 |

|-------|-----------------------------------------------------------|-----|

| 6-23. | SD Data Read Time-Out Register (SDTOD)                    | 237 |

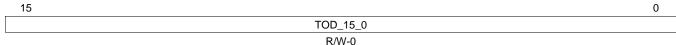

| 6-24. | SD Block Length Register (SDBLEN)                         | 237 |

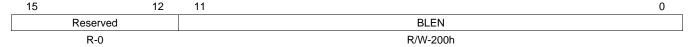

| 6-25. | SD Number of Blocks Register (SDNBLK)                     | 238 |

| 6-26. | SD Number of Blocks Counter Register (SDNBLC)             | 238 |

| 6-27. | SD Data Receive Register (SDDRR1)                         | 239 |

| 6-28. | SD Data Receive Register (SDDRR2)                         | 239 |

| 6-29. | SD Data Transmit Register (SDDXR)                         | 240 |

| 6-30. | SD Data Transmit Register (SDDXR2)                        | 240 |

| 6-31. | eMMC Command Register 1 (MMCSD1)                          | 241 |

| 6-32. | eMMC Command Register 2 (MMCSD2)                          | 242 |

| 6-33. | Command Format                                            | 242 |

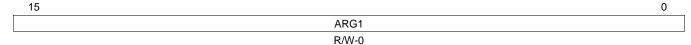

| 6-34. | SD Data Transmit Register (SDARG1)                        | 243 |

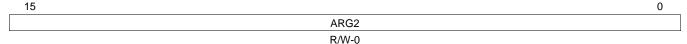

| 6-35. | SD Data Transmit Register (SDARG2)                        | 243 |

| 6-36. | SD Response Register 0 (SDRSP0)                           | 244 |

| 6-37. | SD Response Register 1 (SDRSP1)                           | 244 |

| 6-38. | SD Response Register 2 (SDRSP2)                           | 244 |

| 6-39. | SD Response Register 3 (SDRSP3)                           | 244 |

| 6-40. | SD Response Register 4 (SDRSP4)                           | 244 |

| 6-41. | SD Response Register 5 (SDRSP5)                           | 244 |

| 6-42. | SD Response Register 6 (SDRSP6)                           | 244 |

| 6-43. | SD Response Register 7 (SDRSP7)                           | 245 |

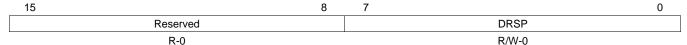

| 6-44. | SD Data Response Register (SDDRSP)                        | 246 |

| 6-45. | SD Command Index Register (SDCIDX)                        | 246 |

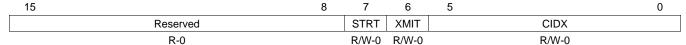

| 6-46. | SDIO Control Register (SDIOCTL)                           | 247 |

| 6-47. | SDIO Status Register 0 (SDIOST0)                          | 247 |

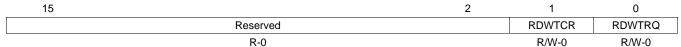

| 6-48. | SDIO Interrupt Enable Register (SDIOIEN)                  | 248 |

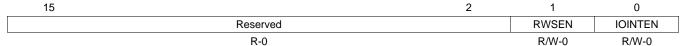

| 6-49. | SDIO Interrupt Status Register (SDIOIST)                  | 248 |

| 6-50. | SD FIFO Control Register (SDFIFOCTL)                      | 249 |

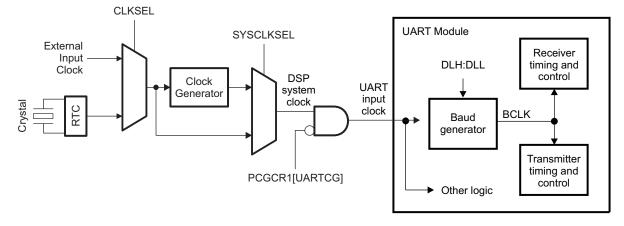

| 7-1.  | UART Block Diagram                                        | 253 |

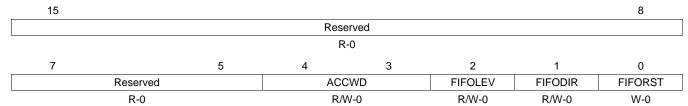

| 7-2.  | UART Clock Generation Diagram                             | 254 |

| 7-3.  | Relationship between Data Bit, BCLK, and UART Input Clock | 255 |

| 7-4.  | UART Example Protocol Formats                             | 257 |

| 7-5.  | UART Interface Using Autoflow Diagram                     | 260 |

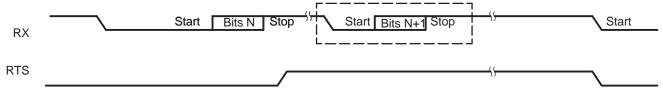

| 7-6.  | Autoflow Functional Timing Waveforms for RTS              | 260 |

| 7-7.  | Autoflow Functional Timing Waveforms for CTS              | 260 |

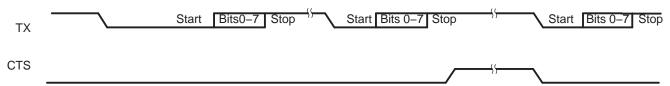

| 7-8.  | UART Interrupt Request Enable Paths                       | 263 |

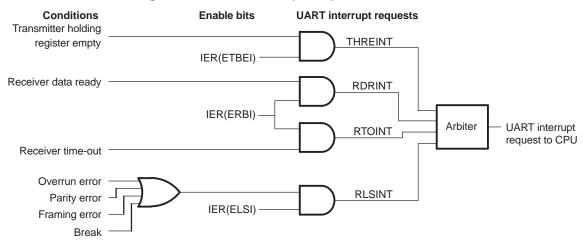

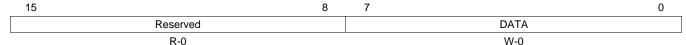

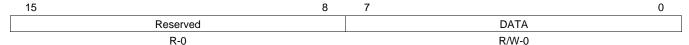

| 7-9.  | Receiver Buffer Register (RBR)                            | 266 |

| 7-10. | Transmitter Holding Register (THR)                        | 267 |

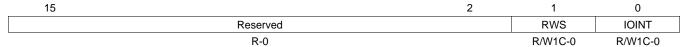

| 7-11. | Interrupt Enable Register (IER)                           | 268 |

| 7-12. | Interrupt Identification Register (IIR)                   | 269 |

| 7-13. | FIFO Control Register (FCR)                               | 271 |

| 7-14. | Line Control Register (LCR)                               | 272 |

| 7-15. | Modem Control Register (MCR)                              | 274 |

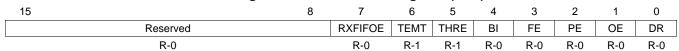

| 7-16. | Line Status Register (LSR)                                | 275 |

| 7-17. | Scratch Register                                          | 277 |

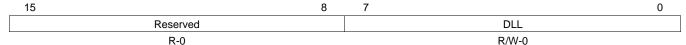

| 7-18. | Divisor LSB Latch (DLL)                                   | 278 |

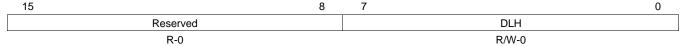

| 7-19. | Divisor MSB Latch (DLH)                                   | 278 |

| 7-20. | Power and Emulation Management Register (PWREMU_MGMT)     | 279 |

| \ <b>\</b> \\\\\ | ۸/ tı | .com |

|------------------|-------|------|

|                  |       |      |

| 8-1.  | Serial Peripheral Interface (SPI) Block Diagram                                                                      | 281 |

|-------|----------------------------------------------------------------------------------------------------------------------|-----|

| 8-2.  | Typical SPI Interface                                                                                                | 282 |

| 8-3.  | Clocking Diagram for the SPI                                                                                         | 283 |

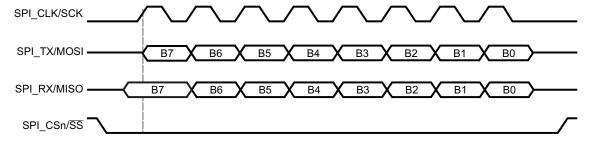

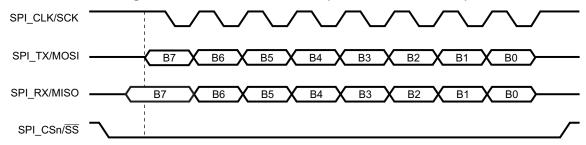

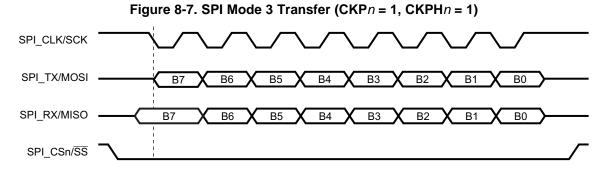

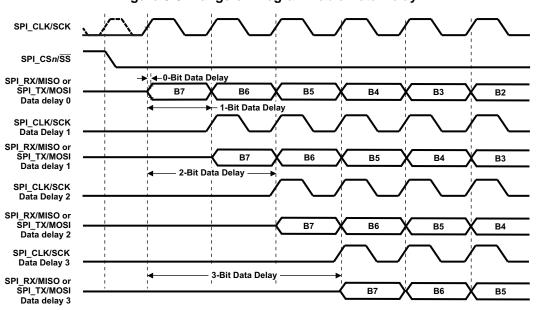

| 8-4.  | SPI Mode 0 Transfer (CKP $n = 0$ , CKPH $n = 0$ )                                                                    | 285 |