# Tiva<sup>™</sup> C Series TM4C129x Microcontrollers Silicon Revisions 1 and 2

## **Silicon Errata**

Literature Number: SPMZ850A October 2013–Revised October 2013

## **Contents**

| 1      | Introduction                                         | 3  |

|--------|------------------------------------------------------|----|

| 2      | Device Nomenclature                                  | 3  |

| 3      | Device Markings                                      | 4  |

| 4      | Advisory to Silicon Revision Correlation             | 5  |

| 5      | Known Design Exceptions to Functional Specifications | 7  |

| 6      | Appendix 1                                           | 55 |

| 7      | Appendix 2                                           | 61 |

| Revisi | ion History                                          | 70 |

2

## Tiva<sup>™</sup> C Series TM4C129x Microcontrollers Silicon Revisions 1 and 2

### 1 Introduction

This document describes known exceptions to the functional specifications for all of the Tiva<sup>™</sup> C Series TM4C129x microcontrollers. Note that some features are not available on all devices in the series, so not all errata may apply to your device. See your device-specific data sheet for more details.

For details on ARM® Cortex<sup>™</sup>-M4F CPU advisories, see the ARM Core Cortex<sup>™</sup>-M4 (AT520) and Cortex-M4F (AT521) Errata Notice (literature number: <u>SPMZ637</u>).

## 2 Device Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all microcontroller (MCU) devices. Each Tiva C series family member has one of two prefixes: XM4C or TM4C (for example, **XM4C**129XNCPDTI). These prefixes represent evolutionary stages of product development from engineering prototypes (XM4C) through fully qualified production devices (TM4C).

Device development evolutionary flow:

- **XM4C** Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- **TM4C** Production version of the silicon die that is fully qualified.

XM4C devices are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TM4C devices have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (XM4C) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

Tiva is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

٦

4

#### 3 **Device Markings**

Figure 1 shows an example of the Tiva™ C Series TM4C129x microcontroller package symbolization.

**Device Revision Code**

Figure 1. Example of Device Part Markings

This identifying number contains the following information:

- Lines 1 and 5: Internal tracking numbers

- Lines 2 and 3: Part number

For example, TM4C129C on the second line followed by NCPDTI on the third line indicates orderable part number TM4C129CNCPDTI. Note that the first letter in the part number indicates the product status. A T indicates the part is fully qualified and released to production; an X indicates the part is experimental (preproduction) and requires a waiver. Pre-production parts also include a revision number in the part number, for example, XM4C129C followed by NCPDTI2 indicates revision 2. Production parts do not include a revision number in the part number. The DID0 register identifies the version of the microcontroller, as shown in Table 1. The MAJOR and MINOR bit fields indicate the die revision number. Combined, the MAJOR and MINOR bit fields indicate the TM4C129x microcontroller silicon revision number.

| Table 1. Tiva <sup>™</sup> C Series TM4C129x Silicon Re | Revision Codes |

|---------------------------------------------------------|----------------|

|---------------------------------------------------------|----------------|

| MAJOR<br>Bit Field Value | MINOR<br>Bit Field Value | Die Revision | Silicon Revision |

|--------------------------|--------------------------|--------------|------------------|

| 0x0                      | 0x0                      | A0           | 1                |

| 0x0                      | 0x1                      | A1           | 2                |

Line 4: Date code The first two characters on the fourth line indicate the date code, followed by internal tracking numbers. The two-digit date code YM indicates the last digit of the year, then the month. For example, a 34 for the first two digits of the fourth line indicates a date code of April 2013.

## 4 Advisory to Silicon Revision Correlation

| Table 2. | Advisory to | Silicon | Revision | Matrix |

|----------|-------------|---------|----------|--------|

|          | Advisory to |         | 11011011 | matrix |

| Advisory<br>Number | Advisory Title                                                                                                          |   | Silicon<br>Revision(s)<br>Affected |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------|---|------------------------------------|--|

|                    |                                                                                                                         | 1 | 2                                  |  |

|                    | ADC                                                                                                                     |   |                                    |  |

| ADC#09             | First two ADC Samples From the Internal Temperature Sensor Must be Ignored                                              | Х | Х                                  |  |

| ADC#13             | A Glitch can Occur on pin PE3 When Using any ADC Analog Input Channel to Sample                                         | Х | Х                                  |  |

| ADC#14             | The First two ADC Samples may be Incorrect                                                                              | Х | Х                                  |  |

| ADC#15             | ADC Global Synchronization does not function                                                                            | Х |                                    |  |

|                    | CRC                                                                                                                     |   |                                    |  |

| CRC#01             | Any Data Read From a Non-CRC Register After Accessing the CRCRSLTPP Register is<br>Incorrect                            | х |                                    |  |

|                    | DMA                                                                                                                     |   |                                    |  |

| DMA#02             | $\mu\text{DMA}$ Data may be Corrupted if Transferred or Received While Entering or Exiting Deep-Sleep Mode              | Х | Х                                  |  |

|                    | ELEC                                                                                                                    |   |                                    |  |

| ELEC#02            | $V_{\text{BAT}}$ Supply pin may be Damaged if the pin Voltage Ramps Faster Than 0.7 V/µs                                | Х | Х                                  |  |

|                    | EPI                                                                                                                     |   |                                    |  |

| EPI#01             | Data Reads can be Corrupted when the Code Address Space in the EPI Module is Used                                       | Х | X                                  |  |

|                    | Ethernet                                                                                                                |   |                                    |  |

| ETH#01             | The LED Polarity Bit in the Ethernet MAC Clock Configuration Register Does Not Function                                 | Х |                                    |  |

|                    | GPIO                                                                                                                    |   |                                    |  |

| GPIO#03            | GPIO Pins may Glitch on Power up                                                                                        | Х |                                    |  |

|                    | General-Purpose Timers                                                                                                  |   |                                    |  |

| GPTM#09            | General-Purpose Timers do not Synchronize When Configured for RTC Mode                                                  | Х | X                                  |  |

| GPTM#12            | The GPTMPP Register Does not Correctly Indicate Alternate Clock Capability                                              |   |                                    |  |

| GPTM#13            | Reading the CPTMTnV, the CPTMTnR, or the CPTMRTCPD Registers may Return Incorrect                                       |   | ×                                  |  |

| GPTM#14            | General-Purpose Timer ADC and uDMA Triggers may not be Cantured in Certain Modes                                        |   |                                    |  |

| GPTM#15            | Counter Does not Immediately Clear to 0 When MATCH is Reached In Edge Count Up Mode                                     | Х | Х                                  |  |

| GPTM#16            | Special Configuration is Required when Operating the GPTM in 32-bit Mode with the Alternate Clock Source                | Х |                                    |  |

| GPTM#17            | The GPTMSYNC Register Bits Must be Manually Cleared when Using an Alternate Clock Source                                | Х |                                    |  |

|                    | Hibernation                                                                                                             |   |                                    |  |

| HIB#10             | If MEMCLR is set to a Non-Zero Value, a Tamper Event may not Clear all of the Bits in the HIBDATA Register              | Х | X                                  |  |

| HIB#12             | Tamper Logging Failure on XOSC Fail Event                                                                               | Х |                                    |  |

| HIB#13             | Tamper Events may be Missed in log                                                                                      | Х |                                    |  |

| HIB#15             | The VDDFAIL Interrupt bit in the HIBIC Register is not Properly Cleared                                                 |   |                                    |  |

| HIB#16             | Application Code May Miss New Tamper Event During Clear                                                                 |   | Х                                  |  |

| HIB#17             | WAKE Cannot be Used to Wake From Hibernate Mode                                                                         |   |                                    |  |

| HIB#18             | Can get two Matches per day in Calendar Mode                                                                            | Х | X                                  |  |

|                    | LCD                                                                                                                     |   |                                    |  |

| LCD#01             | LIDD-Mode DMA Transactions in the LCD Controller Cause the Microcontroller to Become Unresponsive                       | Х | Х                                  |  |

| LCD#02             | LCD DMA FIFO Underflow Interrupt Occurs When EPI is Mapped to an External SDRAM With an Address That is not 0x1000.0000 | Х | Х                                  |  |

<sup>(1)</sup> Applicable to devices with date codes earlier than 0x38 (August 2013).

6

www.ti.com

| Advisory<br>Number | Advisory Title                                                                                                                                         | Revis | con<br>ion(s)<br>cted |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|

|                    |                                                                                                                                                        | 1     | 2                     |

| LCD#03             | LCD Module Does not Restart if an Underflow Occurs                                                                                                     | Х     | Х                     |

|                    | Memory                                                                                                                                                 |       |                       |

| MEM#03             | EEPROM Data May be Corrupted if an EEPROM Write or Erase is Interrupted                                                                                | Х     |                       |

| MEM#09             | ROM_SysCtlClockFreqSet() does not Properly Configure MOSC                                                                                              | Х     |                       |

|                    | ONEWIRE                                                                                                                                                |       |                       |

| ONEWIRE#01         | A Delay is Needed for the 1-Wire Receive Configuration                                                                                                 | Х     |                       |

|                    | PWM                                                                                                                                                    |       |                       |

| PWM#01             | Under Certain Circumstances, the PWM Load Interrupt is Triggered as Soon as the PWM is Enabled                                                         | Х     |                       |

| PWM#02             | Setting the PWMSYNC Bits May Not Synchronize the PWM Counters if PWMDIV is Used                                                                        | Х     |                       |

| PWM#03             | The PWM Generators May Not Generate Interrupts or ADC Triggers                                                                                         | Х     |                       |

|                    | QEI                                                                                                                                                    |       |                       |

| QEI#01             | When Using the Index Pulse to Reset the Counter, a Specific Initial Condition in the QEI Module Causes the Direction for the First Count to be Misread | Х     | Х                     |

|                    | SSI                                                                                                                                                    |       | 1                     |

| SSI#03             | SSI1 can Only be Used in Legacy Mode                                                                                                                   | Х     | Х                     |

| SSI#04             | The First Byte Sent by the QSSI in Master Mode is Incorrect when Using the Alternate Clock                                                             | Х     |                       |

| SSI#05             | Bus Contention in Bi- and Quad-Mode of SSI                                                                                                             | Х     | Х                     |

|                    | System Control                                                                                                                                         |       | 1                     |

| SYSCTL#03          | The MOSC Verification Circuit Does not Detect a Loss of Clock After the Clock has been Successfully Operating                                          | Х     | Х                     |

| SYSCTL#09          | Some Devices may not Start Properly During Power Up if $V_{\mbox{\tiny DDC}}$ is Decaying Between 200 and 100 mV When Power is Reapplied               | х     |                       |

| SYSCTL#12          | MOSC Does not Power Down in Deep-Sleep when it is not the Deep-Sleep Clock Source                                                                      | Х     |                       |

| SYSCTL#13          | The NMIC register does not indicate NMI sources when read                                                                                              | Х     |                       |

| SYSCTL#14          | Power Consumption is Higher When MOSC is Used in Single-Ended Mode                                                                                     | Х     |                       |

| SYSCTL#15          | Watchdog Reset Improperly Updates the NMIC Register                                                                                                    | Х     |                       |

|                    | UART                                                                                                                                                   |       |                       |

| UART#01            | When UART SIR Mode is Enabled, µDMA Burst Transfer Does not Occur                                                                                      | Х     | Х                     |

|                    | USB                                                                                                                                                    |       |                       |

| USB#02             | USB Controller Sends EOP at end of Device Remote Wake-Up                                                                                               | Х     |                       |

| USB#03             | Any Data Read From a Non-USB Register After Accessing the USBPP, USBPC, or the USBCC Register is Incorrect                                             | Х     |                       |

|                    | Watchdog Timers                                                                                                                                        |       |                       |

| WDT#08             | Reading the WDTVALUE Register may Return Incorrect Values When Using Watchdog Timer 1                                                                  | Х     | x                     |

## Table 2. Advisory to Silicon Revision Matrix (continued)

TEXAS INSTRUMENTS

www.ti.com

Title

Page

7

## 5 Known Design Exceptions to Functional Specifications Table 3. Advisory List

| ADC#09 — First two ADC Samples From the Internal Temperature Sensor Must be Ignored                                                                                    | 9  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| ADC#13 — A Glitch can Occur on pin PE3 When Using any ADC Analog Input Channel to Sample                                                                               | 10 |

| ADC#15 — ADC Global Synchronization Does not Function                                                                                                                  | 11 |

| <b>CRC#01</b> — Any Data Read From a Non-CRC Register After Accessing the CRCRSLTPP Register is Incorrect                                                              | 12 |

| DMA#02 — µDMA Data may be Corrupted if Transferred or Received While Entering or Exiting Deep-Sleep Mode                                                               | 13 |

| <b>ELEC#02</b> — V <sub>BAT</sub> Supply pin may be Damaged if the pin Voltage Ramps Faster Than 0.7 V/µs                                                              | 14 |

| EPI#01 — Data Reads can be Corrupted when the Code Address Space in the EPI Module is Used                                                                             | 15 |

| ETH#01 — The LED Polarity Bit in the Ethernet MAC Clock Configuration Register Does Not Function                                                                       | 16 |

| GPIO#03 — GPIO Pins may Glitch on Power up                                                                                                                             | 17 |

| <b>GPTM#09</b> — General-Purpose Timers do not Synchronize When Configured for RTC Mode                                                                                | 18 |

| GPTM#12 — The GPTMPP Register Does not Correctly Indicate Alternate Clock Capability                                                                                   | 19 |

| GPTM#13 — Reading the GPTMTnV, the GPTMTnR, or the GPTMRTCPD Registers may Return Incorrect Values<br>When Using an Alternate Clock Source                             | 20 |

| GPTM#14 — General-Purpose Timer ADC and µDMA Triggers may not be Captured in Certain Modes When Using PIOSC                                                            | 21 |

| GPTM#15 — Counter Does not Immediately Reset to 0 When MATCH is Reached In Edge Count Up Mode                                                                          | 22 |

| GPTM#16 — Special Configuration is Required when Operating the GPTM in 32-bit Mode with the Alternate Clock Source                                                     | 23 |

| GPTM#17 — The GPTMSYNC Register Bits Must be Manually Cleared when Using an Alternate Clock Source                                                                     | 24 |

| HIB#10 — If MEMCLR is set to a Non-Zero Value, a Tamper Event may not Clear all of the Bits in the HIBDATA Register.                                                   | 25 |

| HIB#12 — Tamper Logging Failure on XOSC Fail Event                                                                                                                     | 26 |

| HIB#13 — Tamper Events may be Missed in log                                                                                                                            | 27 |

| HIB#15 — The VDDFAIL Interrupt bit in the HIBIC Register is not Properly Cleared                                                                                       | 28 |

| HIB#16 — Application Code May Miss New Tamper Event During Clear                                                                                                       | 29 |

| HIB#17 — WAKE Cannot be Used to Wake From Hibernate Mode                                                                                                               | 30 |

| HIB#18 — Can get two Matches per day in Calendar Mode                                                                                                                  | 31 |

| LCD#01 — LIDD-Mode DMA Transactions in the LCD Controller Cause the Microcontroller to Become                                                                          |    |

|                                                                                                                                                                        | 32 |

| LCD#02 — LCD DMA FIFO Underflow Interrupt Occurs When EPI is Mapped to an External SDRAM With an Address That is not 0x1000.0000                                       | 33 |

| LCD#03 — LCD Module Does not Restart if an Underflow Occurs                                                                                                            |    |

| MEM#03 — EEPROM Data May be Corrupted if an EEPROM Write is Interrupted                                                                                                |    |

| MEM#09 — ROM_SysCtlClockFreqSet() Does not Properly Configure MOSC                                                                                                     |    |

| <b>ONEWIRE#01</b> — A Delay is Needed for the 1-Wire µDMA Receive Configuration                                                                                        |    |

| <b>PWM#01</b> —Under Certain Circumstances, the PWM Load Interrupt is Triggered as Soon as the PWM is Enabled                                                          |    |

| <b>PWM#02</b> — Setting the PWMSYNC Bits May Not Synchronize the PWM Counters if PWMDIV is Used                                                                        | 39 |

| PWM#03 — The PWM Generators May Not Generate Interrupts or ADC Triggers                                                                                                | 40 |

| <b>QEI#01</b> — When Using the Index Pulse to Reset the Counter, a Specific Initial Condition in the QEI Module Causes the Direction for the First Count to be Misread | 41 |

| SSI#03 — SSI1 can Only be Used in Legacy Mode                                                                                                                          | 42 |

| SSI#04 — The First Byte Sent by the SSI in Master Mode is Incorrect when Using the Alternate Clock                                                                     | 43 |

| SSI#05 —Bus Contention in Bi- and Quad-Mode of SSI                                                                                                                     | 44 |

| SYSCTL#03 — The MOSC Verification Circuit Does not Detect a Loss of Clock After the Clock has been<br>Successfully Operating                                           | 45 |

| SYSCTL#09 — Some Devices may not Start Properly During Power up                                                                                                        | 46 |

| SYSCTL#12 — MOSC Does not Power Down in Deep-Sleep when it is not the Deep-Sleep Clock Source                                                                          | 47 |

| SYSCTL#13 — The NMIC Register Does not Indicate NMI Sources when Read                                                                                                  | 48 |

| SYSCTL#14 — Power Consumption is Higher When MOSC is Used in Single-Ended Mode                                                                                         | 49 |

8

## Table 3. Advisory List (continued)

| SYSCTL#15 — Watchdog Reset Improperly Updates the NMIC Register                                                            | 50 |

|----------------------------------------------------------------------------------------------------------------------------|----|

| UART#01 — When UART SIR Mode is Enabled, µDMA Burst Transfer Does not Occur                                                | 51 |

| USB#02 — USB Controller Sends EOP at end of Device Remote Wake-Up                                                          | 52 |

| <b>USB#03</b> — Any Data Read From a Non-USB Register After Accessing the USBPP, USBPC, or the USBCC Register is Incorrect | 53 |

| WDT#08 — Reading the WDTVALUE Register may Return Incorrect Values When Using Watchdog Timer 1                             | 54 |

| Known Design | Exceptions t | to Functional | Specifications |

|--------------|--------------|---------------|----------------|

|              |              |               |                |

| ADC#09                | First two ADC Samples From the Internal Temperature Sensor Must be Ignored                                                                                                                                                                                                                                            |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                                              |

| Description:          | The analog source resistance ( $R_s$ ) to the ADC from the internal temperature sensor exceeds the specified amount of 500 $\Omega$ . This causes a settling time requirement that is longer than the sampling interval to the converter.                                                                             |

| Workaround(s):        | A small delay must be inserted between samples to allow enough time for the voltage to settle. Configure the respective ADC Sample Sequence n Sample and Hold Time (ADCSSTSH) register for a sample and hold width of at least 16 ADC clocks (TSHx = 0x4).                                                            |

|                       | Alternatively, three consecutive samples from the same channel must be taken to accurately sample the internal temperature sensor using the ADC. The first two consecutive samples should be discarded and the third sample can be kept. These consecutive samples cannot be interrupted by sampling another channel. |

9

| ADC#13                | A Glitch can Occur on pin PE3 When Using any ADC Analog Input Channel to Sample                                                                                                                                                                                                                                                                                         |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                                                                                                |

| Description           | A glitch may occur on PE3 when using any ADC analog input channel (AINx) to sample.<br>This glitch can occur when PE3 is configured as a GPIO input or as a GPIO open drain<br>and happens at the end of the ADC conversion. These glitches will not affect analog<br>measurements on PE3 when configured as AINO as long as the specified source<br>resistance is met. |

| Workaround(s)         | A 1k $\Omega$ external pull-up or pull-down on PE3 will help to minimize the magnitude of the glitch to 200 mV or less.                                                                                                                                                                                                                                                 |

| www.ti.com            | Known Design Exceptions to Functional Specifications                                                                                                                                             |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC#15                | ADC Global Synchronization Does not Function                                                                                                                                                     |

| Revision(s) Affected: | 1 only.                                                                                                                                                                                          |

| Description:          | The SYNCWAIT and GSYNC bits in the ADC Processor Sample Sequence Initiate (ADCPSSI) register are set to allow sample sequencers in ADC0 and ADC1 to be synchronized. These bits do not function. |

| Workaround(s):        | None                                                                                                                                                                                             |

| CRC#01                | Any Data Read From a Non-CRC Register After Accessing the CRCRSLTPP<br>Register is Incorrect                                                                                                   |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected: | 1 only.                                                                                                                                                                                        |  |

| Description:          | A CRC Post Processing Result (CRCRSLTPP) register read followed by a read from any other non-CRC register on the AHB results in incorrect data in the non-CRC register.                        |  |

| Workaround(s):        | Read any CRC register after reading the CRCRSLTPP register and before reading any other register on the AHB. To determine which modules are on the AHB, refer to Figure 1-1 in the data sheet. |  |

| DMA#02                | μDMA Data may be Corrupted if Transferred or Received While Entering or Exiting<br>Deep-Sleep Mode                                                                                                                                                                                                |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                          |  |

| Description:          | Transferred or received data using the $\mu$ DMA from either the UART or the SSI peripherals may get corrupted when entering Deep-Sleep mode from Run mode or exiting Deep-Sleep mode to Run mode if the Run mode clock configuration is not the same as the Deep-Sleep mode clock configuration. |  |

| Workaround(s):        | Program the Run mode clock configuration to match the Deep-Sleep mode clock configuration right before entering Deep-Sleep mode.                                                                                                                                                                  |  |

Switch

www.ti.com

| ELEC#02               | $V_{\scriptscriptstyle BAT}$ Supply pin may be Damaged if the pin Voltage Ramps Faster Than 0.7 V/µs                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

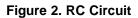

| Description           | The V <sub>BAT</sub> supply pin may be damaged if the pin voltage ramps faster than 0.7 V/µs. Fast V <sub>BAT</sub> ramps are a concern when a battery is being connected or the V <sub>BAT</sub> supply is hard switched.                                                                                                                                                                                                                                                                |  |  |  |

| Workaround(s)         | An RC circuit as shown should be added to the V <sub>BAT</sub> pin to prevent the damage. The R <sub>1</sub> and C <sub>1</sub> should be placed close to the microcontroller for best protection. In systems that do not require Hibernate when the VDD supply is off, the V <sub>BAT</sub> pin should be tied to the VDD supply, which typically ramps at a rate slower than 0.7 V/µs. The R1 and C1 components are not required for a V <sub>BAT</sub> supply ramp less than 0.7 V/µs. |  |  |  |

|                       | VBAT<br>Source Optional<br>Voltage C <sub>1</sub> VBAT                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

<u>+</u>

| www.ti.com            | Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EPI#01                | Data Reads can be Corrupted when the Code Address Space in the EPI Module is<br>Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Description:          | The external code address space at address 0x1000.0000 is specified for the EPI module using the ECSZ and ECADR fields in the EPI Address Map (EPIADDRMAP). However, data reads can be corrupted when using this address space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Workaround(s):        | Code cannot be executed from the 0x1000.0000 address space. The EPI address spaces at 0x6000.0000 and 0x8000.0000 can be used instead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                       | In addition, when reading from EPI memory mapped to the code address space at 0x1000.0000, replace direct EPI memory reads via pointers with calls to the EPIWorkaroundWordRead(), EPIWorkaroundHWordRead() or EPIWorkaroundByteRead() functions depending on the data size for the read operation. Similarly, when writing to the EPI code address space, replace direct writes with calls to the EPIWorkaroundWordWrite(), EPIWorkaroundHWordWrite() or EPIWorkaroundByteWrite() functions. These APIs are new and can be found in Appendix 2. For Keil, IAR, GCC, and Code Bench, these functions are defined as inline functions in the epi.h file in <i>C:\trlTivaWare_C_Series-2.0\driverlib</i> . For CCS, which doesn't support this structure, these should be added to a new file placed in the \driverlib directory called epi_workaround_ccs.s, and this file should be added to the project. Note that the new DriverLib APIs and the CCS file mentioned in Appendix 2 are included in TivaWare release 2.0.1 and later releases. |  |

| ETH#01                | The LED Polarity Bit in the Ethernet MAC Clock Configuration Register Does Not<br>Function                                                                                                                    |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected: | 1 only.                                                                                                                                                                                                       |  |

| Description:          | The LED Polarity bit (POL) in the Ethernet MAC Clock Configuration Register (EMACCC) does not function. The LED outputs coming from the Ethernet PHY are active high and their polarity cannot be configured. |  |

| Workaround(s):        | None.                                                                                                                                                                                                         |  |

| www.ti.com            | Known Design Exceptions to Functional Specifications                                                                      |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| GPIO#03               | GPIO Pins may Glitch on Power up                                                                                          |  |

| Revision(s) Affected: | 1 only.                                                                                                                   |  |

| Description:          | Some devices may drive the GPIOs to ground during power up for less than 5 $\mu s$ when $V_{\text{DDC}}$ is ~ 400-500 mV. |  |

| Workaround(s):        | None.                                                                                                                     |  |

| GPTM#09               | General-Purpose Timers do not Synchronize When Configured for RTC Mode                                                                                                                                                                             |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                           |  |

| Description:          | When attempting to synchronize the General-Purpose Timers using the GPTM Synchronize (GPTMSYNC) register, they do not synchronize if any of the timers are configured for RTC mode. This applies even if the timers are using the alternate clock. |  |

| Workaround(s):        | None.                                                                                                                                                                                                                                              |  |

| www.ti.com            | Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPTM#12               | The GPTMPP Register Does not Correctly Indicate Alternate Clock Capability                                                                                                                                                                                                                                                                                                                                                                                                       |

| Revision(s) Affected: | 1 only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Description           | The ALTCLK bit in the GPTM Peripheral Properties (GPTMPP) register reads as 0x0, the ALTCLK source is available to the timer. When the ALTCLK bit reads as 0x1, the ALTCLK source is not available to the timer. This is opposite from the intended implementation of these bits. The ALTCLK bit should read as 0x0 when the ALTCLK source is not available for use by the timer and the ALTCLK bit should read as 0x1 when the ALTCLK source is available for use by the timer. |

| Workaround(s)         | None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GPTM#13               | Reading the GPTMTnV, the GPTMTnR, or the GPTMRTCPD Registers may Return<br>Incorrect Values When Using an Alternate Clock Source                                                       |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                               |  |

| Description           | Incorrect values may be read from the GPTM Timer n Value (GPTMTnV), the GPTM Timer n (GPTMTnR), and the GPTM RTC Predivide (GPTMRTCPD) registers when using an alternate clock source. |  |

| Workaround(s)         | None.                                                                                                                                                                                  |  |

| GPTM        | GPTM#14 General-Purpose Timer ADC and µDMA Triggers may not be Captured in C<br>Modes When Using PIOSC |                                                                                                                                                                                                                                                         | nay not be Captured in Certain |                  |

|-------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|

| Revisio     | on(s) Affected:                                                                                        | 1 only.                                                                                                                                                                                                                                                 |                                |                  |

| Description |                                                                                                        | An ADC or $\mu$ DMA event that is triggered by the general-purpose timer may not be triggered when the timer is configured to use the alternate clock and the system clock frequency is greater than 17 MHz. This affects the following counting modes: |                                |                  |

|             |                                                                                                        | Mode                                                                                                                                                                                                                                                    | Direction                      | Trigger Affected |

|             | Edge Count                                                                                             |                                                                                                                                                                                                                                                         | Down                           | Capture Match    |

|             | O                                                                                                      | ne-shot                                                                                                                                                                                                                                                 | Up                             | Time Out         |

|             | 0                                                                                                      | ne-shot                                                                                                                                                                                                                                                 | Down                           | Time Out         |

Workaround(s)

None.

| GPTM#15               | Counter Does not Immediately Reset to 0 When MATCH is Reached In Edge Count<br>Up Mode                                                                                                                                                                                                         |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                       |  |

| Description           | When configured for input edge count mode and count up mode, after counting to the match value, the counter uses one additional edge to reset the timer to 0. As a result, after the first match event, all subsequent match events occur after the programmed number of edge events plus one. |  |

| Workaround(s)         | In software, account for one additional edge in the programmed edge count after the first match interrupt is received.                                                                                                                                                                         |  |

| www.ti.com            | Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                         |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPTM#16               | Special Configuration is Required when Operating the GPTM in 32-bit Mode with the Alternate Clock Source                                                                                                                                                                                                                                                                                     |  |

| Revision(s) Affected: | 1 only.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Description:          | When the alternate clock source is selected by setting the ALTCLK bit in the GPTM Clock Configuration (GPTMCC) register and the timer is in 32-bit mode, the GPTM Timer B Match (GPTMTBMATCHR) and GPTM Timer B Interval Load (GPTMTBILR) registers are not writable. As a result, special configuration is required when operating the GPTM in 32-bit mode with the alternate clock source. |  |

| Workaround(s):        | Clear the ALTCLK bit before configuring the GPTMTBMATCHR and GPTMTBILR registers and then set the ALTCLK bit prior to enabling the timer.                                                                                                                                                                                                                                                    |  |

| GPTM#17               | The GPTMSYNC Register Bits Must be Manually Cleared when Using an Alternate Clock Source                                                                                                                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 only.                                                                                                                                                                                                                                                                    |

| Description:          | If an alternate clock source is configured in the Alternate Clock Configuration (ALTCLKCFG) register and enabled using the GPTM Clock Configuration (GPTMCC) register, the bits in the GPTM Synchronize (GPTMSYNC) register are not cleared automatically after being set. |

| Workaround(s):        | When using the bits in the GPTMSYNC register, software must clear the bits prior to setting them for a subsequent update.                                                                                                                                                  |

| HIB#10                | If MEMCLR is set to a Non-Zero Value, a Tamper Event may not Clear all of the<br>Bits in the HIBDATA Register                                                                                                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                                                    |

| Description:          | If the MEMCLR bit field in the HIB Tamper Control (HIBTPCTL) register is set to a non-<br>zero value, the Hibernation Data (HIBDATA) register may not clear the specified bits.<br>The MEMCLR bit field provides the option to clear all, the upper half, lower half, or none<br>of the Hibernate memory on a tamper event. |

| Workaround(s):        | After clearing the tamper event by setting the TPCLR bit, the application should clear the data in the Hibernate memory in the HIBDATA register (write either the upper half, the lower half, or all of the bits to all zeros).                                                                                             |

| HIB#12                | Tamper Logging Failure on XOSC Fail Event                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 only.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Description:          | When XOSC failure is created in the Tamper module, the XOSC bit does not get set in HIBTPLOG1, HIBTPLOG3, HIBTPLOG5, or HIBTPLOG7. The XOSC fail can be a result of shorting or grounding one of the XOSC pins or by removing the 32.768-kHz oscillator source. The user will know the XOSC fail has occurred by reading the XOSCFAIL bit in the HIBTPSTAT register. The user may not be able to correlate with an RTC time stamp. |

| Workaround(s):        | None.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HIB#13                | Tamper Events may be Missed in log                                                                                                                                                                                                                                            |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 only.                                                                                                                                                                                                                                                                       |

| Description:          | The HIB Tamper module log captures up to four events. Events 1, 2, 3 and the last event are captured. However, events 4 through the last event minus one are overwritten. If an event occurs after the 3rd and then de-asserts before the last entry, the event will be lost. |

| Workaround(s):        | Systems that have VDD available can be configured to wake up on a tamper event and clear the log.                                                                                                                                                                             |

| HIB#15                | The VDDFAIL Interrupt bit in the HIBIC Register is not Properly Cleared                                                                               |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 only.                                                                                                                                               |

| Description:          | The VDDFAIL bit in the Hibernation Interrupt Clear (HIBIC) register should be cleared by writing a 1 to bit 7 of the register, but it is not cleared. |

| Workaround(s):        | To clear the VDDFAIL bit, write a 1 to both bit 7 and the reserved bit 1 of the HIBIC register.                                                       |

| www.ti.com            | Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                         |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIB#16                | Application Code May Miss New Tamper Event During Clear                                                                                                                                                                                                                                                                      |

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                                                     |

| Description:          | During the clear of a tamper event, a new tamper event could be missed or the tamper log could be corrupted. The clear of a tamper event starts with the Tamper Clear (TPCLR) bit in the HIB Tamper Control register (HIBTPCTL) being written. The write takes 3 rising edges of the 32.768-kHz clock to complete the clear. |

| Workaround(s):        | To prevent missing a tamper event during these three Hibernate clock cycles and restoring the tamper log to its reset state, workaround code must be implemented in the NMI handler as shown in Appendix 1. The new DriverLib APIs mentioned in Appendix 1 are included in TivaWare release 2.0.1 and later releases.        |

| HIB#17                | WAKE Cannot be Used to Wake From Hibernate Mode                                                                                                                                                                                                       |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 only. Applicable to devices with date codes before 0x38 (August, 2013). See Section 3 on how to read the date code.                                                                                                                                 |

| Description:          | The external $\overline{\text{WAKE}}$ pin cannot be used to wake from Hibernate mode. In addition, the WAKENC bit in the Hibernation Peripheral Properties (HIBPP) register that indicates the presence of the $\overline{\text{WAKE}}$ pin is clear. |

| Workaround(s):        | <ul> <li>Use any of the following methods of waking from Hibernate mode:</li> <li>RTC match wake event</li> <li>Low battery wake event</li> <li>External RST</li> <li>GPIO K[7:4]</li> <li>Tempor TMPPI2:01</li> </ul>                                |

Tamper TMPR[3:0] ٠

| HIB#18                | Can get two Matches per day in Calendar Mode                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                                                                                                               |

| Description:          | When the CAL24 bit in the Hibernation Calendar Control (HIBCALCTL) register is clear, the RTC counts in 12 hour, AM/PM mode. The AM/PM bit in the Hibernation Calendar Match 0 (HIBCALM0) specifies whether the match should occur in the AM or the PM. However, this bit is ignored when determining if a match is occurring. As a result, an RTC match could occur twice in one day. |

| Workaround(s):        | Adjust the match time to 24 hour mode before configuring the HIBCALM0 register and set the CAL24 bit. Alternatively, when the match occurs, check the AM/PM bit in the Hibernation Calendar (HICAL0) register to determine if the match is correct.                                                                                                                                    |

| LCD#01                | LIDD-Mode DMA Transactions in the LCD Controller Cause the Microcontroller to Become Unresponsive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1 and 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Description:          | Whenever a LIDD-mode DMA transaction is requested by setting the DMAEN bit of the LCD LIDD Control (LCDLIDDCTL) register, after setting the LCD DMA frame buffer n base and ceiling addresses in the LCDDMABAFB and LCDDMACAFB registers, respectively, the next attempt to access any LCD controller register causes the microcontroller and the JTAG connection to become unresponsive. A power-on reset recovers the device.                                                                                                                                                                                                                                                                                                                                                         |