# Stellaris® LM3S9B90 RevB1 Errata

This document contains known errata at the time of publication for the Stellaris LM3S9B90 microcontroller. The table below summarizes the errata and lists the affected revisions. See the data sheet for more details.

See also the ARM® Cortex™-M3 errata, ARM publication number PR326-PRDC-009450 v2.0.

**Table 1. Revision History**

| Date         | Revision | Description                                                                                                                                                                       |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 2013 | 4.3      | Added issue "Chip select operation is not correct when using dual chip selects in Host Bus Continuous<br>Read mode" on page 16.                                                   |

|              |          | ■ Removed issue "Flash Write Buffer does not function above 50 MHz" and added issue "Flash memory may be corrupted if programmed at system clock speeds above 50 MHz" on page 28. |

|              |          | Added issue "iRDY timing in General-Purpose mode is not as specified in the data sheet" on page 34                                                                                |

|              |          | ■ Added issue "Simultaneous sampling on both ADC modules yields incorrect samples" on page 44                                                                                     |

|              |          | ■ Added issue "Phase offset does not delay as expected if sample sequencers are not triggered at the same time" on page 44.                                                       |

| October 2012 | 4.2      | ■ Added issue "Non-word-aligned write to SRAM can cause incorrect value to be loaded" on page 11                                                                                  |

|              |          | ■ Added issue "Internal reset supervisors may not prevent incorrect device operation during power transitions" on page 13.                                                        |

|              |          | <ul> <li>Added issue "Watchdog clear mechanism described in the data sheet does not work for the Watchdog<br/>Timer 1 module" on page 39.</li> </ul>                              |

|              |          | <ul> <li>Added issue "Watchdog Timer 1 module asserts reset signal even if not programmed to<br/>reset" on page 40.</li> </ul>                                                    |

|              |          | ■ Added issue "WDTLOAD yields an incorrect value when read back" on page 40.                                                                                                      |

|              |          | ■ Added issue "Digital comparator in last step of sequence does not trigger or interrupt" on page 42                                                                              |

|              |          | ■ Added issue "Digital comparator interrupts do not trigger or interrupt as expected" on page 43.                                                                                 |

|              |          | ■ Added issue "Missing trigger or interrupt when multiple sequences configured for processor trigge and different trigger" on page 43.                                            |

|              |          | ■ Added issue "ADC sample sequencers priorities are different than expected" on page 43.                                                                                          |

|              |          | ■ Added issue "When UART LIN or SIR mode is enabled, µDMA burst transfer does not occur" on page 47.                                                                              |

|              |          | Added issue "UART transfers fail at certain system clock frequency and baud rate<br>combinations" on page 47.                                                                     |

|              |          | ■ Added issue "Freescale SPI Mode at low SSIClk frequencies can yield data corruption" on page 48                                                                                 |

|              |          | Added issue "First two ADC samples from the internal temperature sensor must be<br>ignored" on page 59.                                                                           |

| June 2012    | 4.1      | Clarified how to read the date code on Stellaris devices.                                                                                                                         |

| Date           | Revision | Description                                                                                                                                                                                                 |

|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2011     | 4.0      | ■ Added issue "In Host-Bus 16 mode, only one byte select is asserted if only 8 bits are read" on page 32.                                                                                                   |

|                |          | ■ Added issue "When non-blocking reads are pending, EPI accesses can cause the NBRFIFO counter to be incorrectly decremented" on page 32.                                                                   |

|                |          | ■ Added issue "In General-Purpose mode, the framing signal is output regardless of the state of the FRMPIN bit" on page 33.                                                                                 |

|                |          | ■ Added issue "In General-Purpose mode, the maximum time to wait for the iRDY signal is derived from the system clock, not the EPI clock" on page 33.                                                       |

| September 2011 | 3.9      | ■ Added issue "Boundary scan is not functional" on page 9.                                                                                                                                                  |

|                |          | ■ Added issue "At EPI clock speeds over 15 MHz, SDRAM initialization delay is not long enough" on page 32.                                                                                                  |

|                |          | ■ Added issue "LIN mode Sync Break does not have the correct length" on page 46.                                                                                                                            |

| August 2011    | 3.8      | ■ Clarified issue "PB1 has permanent internal pull-up resistance" on page 30.                                                                                                                               |

|                |          | Added additional details to issue "MCU may fail USB certification if the EPI module is operating" on page 53.                                                                                               |

|                |          | ■ Clarified issue "Special considerations for PB1" on page 55.                                                                                                                                              |

|                |          | Added issue "Cannot communicate with a low-speed Device through a hub" on page 55.                                                                                                                          |

| July 2011      | 3.7      | ■ Corrected the read portion of the diagram in issue "Clock signal in EPI General-Purpose mode is inverted" on page 31.                                                                                     |

|                |          | Added issue "Writes to Hibernation module registers may change the value of the RTC" on page 22.                                                                                                            |

|                |          | ■ Added issue "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values" on page 22.                                                                          |

|                |          | ■ Added issue "Retriggering a sample sequencer before it has completed the current sequence results in continuous sampling" on page 42.                                                                     |

|                |          | ■ Added issue "MCU may fail USB certification if the EPI module is operating" on page 53.                                                                                                                   |

|                |          | Added issue "Special considerations for PB1" on page 55.                                                                                                                                                    |

| March 2011     | 3.6      | ■ Clarified which registers are affected by issue "Writes to certain Hibernation module registers sometimes fail" on page 21.                                                                               |

|                |          | ■ Changed title of issue "GPTM 2A and 2B are not usable with µDMA" to "The µDMA does not generate a completion interrupt when transferring to and from GPTM 2A and 2B" on page 28 and reworded description. |

|                |          | Removed Appendix A since information is now in the data sheet.                                                                                                                                              |

| February 2011  | 3.5      | ■ Clarified issue "The PIOSC is not trimmed by the factory" on page 11.                                                                                                                                     |

|                |          | ■ Added issue "Flash memory endurance cycle specification is 100 cycles" on page 27.                                                                                                                        |

|                |          | ■ Added issue "The µDMA does not generate a completion interrupt when transferring to and from GPTM 2A and 2B" on page 28.                                                                                  |

|                |          | ■ Added issue "PB1 has permanent internal pull-up resistance" on page 30.                                                                                                                                   |

|                |          | Added issue "Differential pair encodings are incorrect" on page 41.                                                                                                                                         |

|                |          | ■ Added Appendix A.                                                                                                                                                                                         |

| January 2011   | 3.4      | ■ Added issue "PB1 has permanent internal pull-up resistance" on page 30.                                                                                                                                   |

| Date           | Revision | Description                                                                                                                                                                                                                                     |

|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2010  | 3.2      | ■ Added clarification to issue "Flash Write Buffer does not function above 50 MHz".                                                                                                                                                             |

| October 2010   | 3.0      | ■ Added issue "The WRC bit in the Hibernation Control register is R/W" on page 21.                                                                                                                                                              |

|                |          | ■ Added issue "ROM_USBHostMode function is incorrect".                                                                                                                                                                                          |

|                |          | ■ Added issue "ROM_CANBitRateSet function is incorrect".                                                                                                                                                                                        |

|                |          | Added issue "USB compliance test issue: USB full-speed, far-end signal compliance tests fail with 5 m cable" on page 52.                                                                                                                        |

|                |          | Added issue "USB compliance test issue: USB embedded host low-speed, far-end signal compliance tests fail" on page 52.                                                                                                                          |

| September 2010 | 2.9      | ■ Removed the "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values" because this information has been added to the data sheet.                                                               |

|                |          | ■ Removed the "ROM_I2CMasterErr function is incorrect" issue because the data sheet has been changed such that the ERROR bit no longer is set when the ARBLST bit is set.                                                                       |

|                |          | ■ Additional minor clarifications and corrections.                                                                                                                                                                                              |

| July 2010      | 2.8      | ■ Added issue "The RTRIS bit in the UARTRIS register is only set when the interrupt is enabled" on page 46.                                                                                                                                     |

| June 2010      | 2.7      | ■ Added issue "Wake-up time from Hibernation may exceed specifications" on page 20.                                                                                                                                                             |

|                |          | ■ Minor edits.                                                                                                                                                                                                                                  |

| April 2010     | 2.6      | ■ The description of "VDD3ON mode may not be used" on page 19 was reworded.                                                                                                                                                                     |

|                |          | ■ The description of "Writes to certain Hibernation module registers sometimes fail" on page 21 was reworded.                                                                                                                                   |

|                |          | Added issue "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values".                                                                                                                           |

|                |          | ■ Based on further examination of the "I <sup>2</sup> C arbitration may be lost when operating as a master" issue, this issue has been moved to the GPIO section and renamed as "Schmitt input feature does not function correctly" on page 29. |

|                |          | ■ Added issue "Encoding error in the Ethernet MAC LED Encoding (MACLED) register" on page 51.                                                                                                                                                   |

|                |          | ■ Added information about items fixed on Rev C3.                                                                                                                                                                                                |

| March 2010     | 2.5      | ■ Added issue "The prescaler does not work correctly when counting up in periodic or one-shot mode" on page 38.                                                                                                                                 |

|                |          | ■ Added issue "Snapshot must be enabled in both Timer A and B when in 32-bit snapshot mode" on page 39.                                                                                                                                         |

|                |          | ■ Added issue "Phantom interrupts occur in Smart Card mode" on page 45.                                                                                                                                                                         |

|                |          | ■ Added issue "I <sup>2</sup> C arbitration may be lost when operating as a master".                                                                                                                                                            |

| Date     | Revision | Description                                                                                                                                                                            |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mar 2010 | 2.4      | ■ Added issue "The option to force the ROM boot loader to execute at reset with an external pin does not function" on page 26.                                                         |

|          |          | ■ Amended the workaround for issue "A spurious DMA request is generated when the timer rolls over in Input-Edge Time mode" on page 36.                                                 |

|          |          | Reworded description of issue "The value of the prescaler register is not readable in Edge-Count mode" on page 36.                                                                     |

|          |          | ■ Removed "Prescaler register must have a non-zero value in 16-bit Edge-Time mode" as it has been determined this item was included erroneously.                                       |

|          |          | ■ Added issue "ADC trigger and Wait-on-Trigger may assert when the timer is disabled" on page 37.                                                                                      |

|          |          | ■ Added issue "Wait-on-Trigger does not assert unless the TnOTE bit is set" on page 37 .                                                                                               |

|          |          | ■ Added issue "Do not enable match and timeout interrupts in 16-bit PWM mode" on page 37.                                                                                              |

|          |          | ■ Added issue "Do not use µDMA with 16-bit PWM mode" on page 38.                                                                                                                       |

|          |          | ■ Added issue "Writing the GPTMTnV register does not change the timer value when counting up" on page 38.                                                                              |

| Feb 2010 | 2.3      | <ul> <li>Added issue "A spurious DMA request is generated when the timer rolls over the 16-bit<br/>boundary" on page 36.</li> </ul>                                                    |

|          |          | ■ Added issue "The value of the prescaler register is not readable in Edge-Count mode" on page 36.                                                                                     |

|          |          | ■ Added issue "Prescaler register must have a non-zero value in 16-bit Edge-Time mode."                                                                                                |

|          |          | ■ Added issue "The ADCSPC register does not function" on page 41.                                                                                                                      |

| Jan 2010 | 2.2      | ■ Modified description for "The General-Purpose Timer match register does not function correctly in 32-bit mode" on page 35 to include DMA operation.                                  |

|          |          | ■ Added issue "A spurious DMA request is generated when the timer rolls over in Input-Edge Time mode" on page 36.                                                                      |

|          |          | ■ Changed workaround for "Latch-up may occur if power is applied to the VBUS pin but not to VDD" on page 51 and changed status to "Fixed in Rev C."                                    |

| Dec 2009 | 2.1      | ■ The status of "The Recover Locked Device sequence does not work as expected" on page 9 has been changed to "Fixed in Rev C."                                                         |

|          |          | ■ "Hard Fault possible when waking from Sleep or Deep-Sleep modes and Cortex-M3 Debug Access Port (DAP) is enabled" has been removed and the content added to the LM3S9B90 data sheet. |

|          |          | ■ The status of "VDD3ON mode may not be used" on page 19 has been changed to "Not fixed in Rev C."                                                                                     |

|          |          | ■ Added additional APIs to "Some ROM functions are unsupported" on page 23.                                                                                                            |

|          |          | ■ "The µDMA controller fails to generate capture mode DMA requests from Timer A in the Timer modules" on page 28 has been added.                                                       |

|          |          | ■ "Ethernet packet count decremented before the FCS is read" has been removed and the content added to the LM3S9B90 data sheet.                                                        |

|          |          | ■ The status of "Latch-up may occur if power is applied to the VBUS pin but not to VDD" on page 51 has been changed to "Not fixed in Rev C."                                           |

| Nov 2009 | 2.0      | Started tracking revision history.                                                                                                                                                     |

**Table 2. List of Errata**

| Erratum<br>Number | Erratum Title Module Affected                                                                          |                    | Revision(s)<br>Affected |  |

|-------------------|--------------------------------------------------------------------------------------------------------|--------------------|-------------------------|--|

| 1.1               | JTAG INTEST instruction does not work                                                                  | JTAG               | B1                      |  |

| 1.2               | The Recover Locked Device sequence does not work as expected                                           | JTAG               | B1                      |  |

| 1.3               | Boundary scan is not functional                                                                        | JTAG               | B1, C3, C5              |  |

| 2.1               | Sleep and Deep-Sleep mode not usable at higher speeds when ISRs reside in Flash memory                 | System Control     | B1                      |  |

| 2.2               | Device Capabilities registers may not accurately reflect available signals                             | System Control     | B1                      |  |

| 2.3               | The PIOSC is not trimmed by the factory                                                                | System Control     | B1                      |  |

| 2.4               | Non-word-aligned write to SRAM can cause incorrect value to be loaded                                  | System Control     | B1, C3, C5              |  |

| 2.5               | Internal reset supervisors may not prevent incorrect device operation during power transitions         | System Control     | B1, C3, C5              |  |

| 2.6               | Chip select operation is not correct when using dual chip selects in Host Bus Continuous Read mode     | System Control     | B1, C3, C5              |  |

| 3.1               | Hibernation module may have higher current draw than specified in data sheet under certain conditions  | Hibernation Module | B1                      |  |

| 3.2               | Hibernate POR may not reset the Hibernation module until $V_{\text{DD}}$ is applied                    | Hibernation Module | B1                      |  |

| 3.3               | Power consumption increases if $V_{\text{DD}}$ is not restored after wake from Hibernation mode        | Hibernation Module | B1                      |  |

| 3.4               | ESD protection on the V <sub>BAT</sub> pin does not meet specifications                                | Hibernation Module | B1                      |  |

| 3.5               | VDD3ON mode may not be used                                                                            | Hibernation Module | B1, C3, C5              |  |

| 3.6               | Hibernate module power consumption higher than expected in event wakeup configuration                  | Hibernation Module | B1                      |  |

| 3.7               | The Real-Time Clock gains or loses time going in and out of hibernation when using a crystal           | Hibernation Module | B1                      |  |

| 3.8               | Wake-up time from Hibernation may exceed specifications                                                | Hibernation Module | B1                      |  |

| 3.9               | Low-battery detect circuit is powered down during hibernate                                            | Hibernation Module | B1                      |  |

| 3.10              | Writes to certain Hibernation module registers sometimes fail                                          | Hibernation Module | B1, C3, C5              |  |

| 3.11              | The WRC bit in the Hibernation Control register is R/W                                                 | Hibernation Module | B1, C3, C5              |  |

| 3.12              | Writes to Hibernation module registers may change the value of the RTC                                 | Hibernation Module | B1, C3, C5              |  |

| 3.13              | Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values | Hibernation Module | B1, C3, C5              |  |

| 4.1               | Ethernet fails to connect when using the Boot Loader software in ROM                                   | ROM                | B1                      |  |

| 4.2               | Some ROM functions are unsupported                                                                     | ROM                | B1                      |  |

| 4.3               | ROM mapping check for the Boot loader does not function properly                                       | ROM                | B1                      |  |

| Erratum<br>Number | Erratum Title                                                                                                             | Module Affected        | Revision(s)<br>Affected |

|-------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|

| 4.4               | ROM_SSIConfigSetExpClk function is incorrect                                                                              | ROM                    | B1                      |

| 4.5               | ROM_USBFIFOFlush function is incorrect                                                                                    | ROM                    | B1                      |

| 4.6               | The option to force the ROM boot loader to execute at reset with an external pin does not function                        | ROM                    | B1                      |

| 5.1               | Cumulative page erases may introduce bit errors in Flash memory                                                           | Flash Memory           | B1                      |

| 5.2               | Flash memory endurance cycle specification is 100 cycles                                                                  | Flash Memory           | B1, C3, C5              |

| 5.3               | Flash memory may be corrupted if programmed at system clock speeds above 50 MHz                                           | Flash Memory           | B1, C3, C5              |

| 6.1               | The µDMA controller fails to generate capture mode DMA requests from Timer A in the Timer modules                         | μDMA                   | B1, C3, C5              |

| 6.2               | The µDMA does not generate a completion interrupt when transferring to and from GPTM 2A and 2B                            | μDMA                   | B1, C3, C5              |

| 7.1               | Port B [1:0] pins require external pull-up resistors                                                                      | GPIO                   | B1                      |

| 7.2               | Schmitt input feature does not function correctly                                                                         | GPIO                   | B1                      |

| 7.3               | PB1 has permanent internal pull-up resistance                                                                             | GPIO                   | B1, C3, C5              |

| 8.1               | EPI dual-chip select function does not work                                                                               | EPI                    | B1                      |

| 8.2               | EPI Host-Bus 16 mode does not work                                                                                        | EPI                    | B1                      |

| 8.3               | Clock signal in EPI General-Purpose mode is inverted                                                                      | EPI                    | B1                      |

| 8.4               | At EPI clock speeds over 15 MHz, SDRAM initialization delay is not long enough                                            | EPI                    | B1, C3, C5              |

| 8.5               | In Host-Bus 16 mode, only one byte select is asserted if only 8 bits are read                                             | EPI                    | B1, C3, C5              |

| 8.6               | When non-blocking reads are pending, EPI accesses can cause the NBRFIFO counter to be incorrectly decremented             | EPI                    | B1, C3, C5              |

| 8.7               | In General-Purpose mode, the framing signal is output regardless of the state of the FRMPIN bit                           | EPI                    | B1, C3, C5              |

| 8.8               | In General-Purpose mode, the read and write strobes are output regardless of the state of the RW bit                      | EPI                    | B1, C3, C5              |

| 8.9               | In General-Purpose mode, the maximum time to wait for the iRDY signal is derived from the system clock, not the EPI clock | EPI                    | B1, C3, C5              |

| 8.10              | iRDY timing in General-Purpose mode is not as specified in the data sheet                                                 | EPI                    | B1, C3, C5              |

| 9.1               | The General-Purpose Timer match register does not function correctly in 32-bit mode                                       | General-Purpose Timers | B1, C3, C5              |

| 9.2               | A spurious DMA request is generated when the timer rolls over in Input-Edge Time mode                                     | General-Purpose Timers | B1, C3, C5              |

| 9.3               | A spurious DMA request is generated when the timer rolls over the 16-bit boundary                                         | General-Purpose Timers | B1, C3, C5              |

| 9.4               | The value of the prescaler register is not readable in Edge-Count mode                                                    | General-Purpose Timers | B1, C3, C5              |

| Erratum<br>Number | Erratum Title                                                                                               | Module Affected        | Revision(s)<br>Affected |

|-------------------|-------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|

| 9.5               | ADC trigger and Wait-on-Trigger may assert when the timer is disabled  General-Purpose Timers               |                        | B1, C3, C5              |

| 9.6               | Wait-on-Trigger does not assert unless the TnOTE bit is set                                                 | General-Purpose Timers | B1, C3, C5              |

| 9.7               | Do not enable match and timeout interrupts in 16-bit PWM mode                                               | General-Purpose Timers | B1, C3, C5              |

| 9.8               | Do not use μDMA with 16-bit PWM mode                                                                        | General-Purpose Timers | B1, C3, C5              |

| 9.9               | Writing the GPTMTnV register does not change the timer value when counting up                               | General-Purpose Timers | B1, C3, C5              |

| 9.10              | The prescaler does not work correctly when counting up in periodic or one-shot mode                         | General-Purpose Timers | B1, C3, C5              |

| 9.11              | Snapshot must be enabled in both Timer A and B when in 32-bit snapshot mode                                 | General-Purpose Timers | B1, C3, C5              |

| 10.1              | Writes to Watchdog Timer 1 module WDTLOAD register sometimes fail                                           | Watchdog Timers        | B1, C3, C5              |

| 10.2              | Watchdog clear mechanism described in the data sheet does not work for the Watchdog Timer 1 module          | Watchdog Timers        | B1, C3, C5              |

| 10.3              | Watchdog Timer 1 module asserts reset signal even if not programmed to reset                                | Watchdog Timers        | B1, C3, C5              |

| 10.4              | WDTLOAD yields an incorrect value when read back                                                            | Watchdog Timers        | B1, C3, C5              |

| 11.1              | ADC hardware averaging produces erroneous results in differential mode                                      | ADC                    | B1, C3, C5              |

| 11.2              | The ADCSPC register does not function                                                                       | ADC                    | B1                      |

| 11.3              | Differential pair encodings are incorrect                                                                   | ADC                    | B1, C3, C5              |

| 11.4              | Retriggering a sample sequencer before it has completed the current sequence results in continuous sampling | ADC                    | B1, C3, C5              |

| 11.5              | Digital comparator in last step of sequence does not trigger or interrupt                                   | ADC                    | B1, C3, C5              |

| 11.6              | Digital comparator interrupts do not trigger or interrupt as expected                                       | ADC                    | B1, C3, C5              |

| 11.7              | Missing trigger or interrupt when multiple sequences configured for processor trigger and different trigger | ADC                    | B1, C3, C5              |

| 11.8              | ADC sample sequencers priorities are different than expected                                                | ADC                    | B1, C3, C5              |

| 11.9              | Simultaneous sampling on both ADC modules yields incorrect samples                                          | ADC                    | B1, C3, C5              |

| 11.10             | Phase offset does not delay as expected if sample sequencers are not triggered at the same time             | ADC                    | B1, C3, C5              |

| 12.1              | UART Smart Card (ISO 7816) mode does not function                                                           | UART                   | B1                      |

| 12.2              | When in IrDA mode, the UnRx signal requires configuration even if not used                                  | UART                   | B1                      |

| 12.3              | Phantom interrupts occur in Smart Card mode                                                                 | UART                   | B1                      |

| 12.4              | The RTRIS bit in the UARTRIS register is only set when the interrupt is enabled                             | UART                   | B1, C3, C5              |

| Erratum<br>Number | Erratum Title                                                                                  | Module Affected            | Revision(s)<br>Affected |  |

|-------------------|------------------------------------------------------------------------------------------------|----------------------------|-------------------------|--|

| 12.5              | LIN mode Sync Break does not have the correct length                                           | UART                       | B1, C3, C5              |  |

| 12.6              | When UART LIN or SIR mode is enabled, µDMA burst transfer does not occur                       | UART                       | B1, C3, C5              |  |

| 12.7              | UART transfers fail at certain system clock frequency and baud rate combinations               | UART                       | B1, C3, C5              |  |

| 13.1              | An interrupt is not generated when using µDMA with the SSI module if the EOT bit is set        | SSI                        | B1                      |  |

| 13.2              | Freescale SPI Mode at low SSICIk frequencies can yield data corruption                         | SSI                        | B1, C3, C5              |  |

| 14.1              | Some bits in the I2SMCLKCFG register do not function                                           | I2S                        | B1                      |  |

| 14.2              | I <sup>2</sup> S SCLK signal is inverted in certain modes                                      | 12S                        | B1                      |  |

| 15.1              | Ethernet receive packet corruption may occur when using optional auto-clock gating             | Ethernet Controller        | B1                      |  |

| 15.2              | Ethernet packet loss with cables longer than 50 meters                                         | Ethernet Controller        | B1                      |  |

| 15.3              | Ethernet PHY interrupts do not function correctly                                              | Ethernet Controller        | B1                      |  |

| 15.4              | Encoding error in the Ethernet MAC LED Encoding (MACLED) register                              |                            |                         |  |

| 16.1              | USB0ID and USB0VBUS signals are required to be connected regardless of mode  USB               |                            | B1                      |  |

| 16.2              | Latch-up may occur if power is applied to the VBUS pin but not to VDD                          |                            | B1                      |  |

| 16.3              | USB compliance test issue: USB full-speed, far-end signal compliance tests fail with 5 m cable |                            | B1, C3                  |  |

| 16.4              | USB compliance test issue: USB embedded host low-speed, far-end signal compliance tests fail   | USB                        | B1, C3                  |  |

| 16.5              | MCU may fail USB certification if the EPI module is operating                                  | USB                        | B1, C3, C5              |  |

| 16.6              | Special considerations for PB1                                                                 | USB                        | B1, C3, C5              |  |

| 16.7              | Cannot communicate with a low-speed Device through a hub                                       | USB                        | B1, C3, C5              |  |

| 16.8              | USB0DM may be driven after reset                                                               | USB                        |                         |  |

| 17.1              | Momentarily exceeding V <sub>IN</sub> ratings on any pin can cause latch-up                    | Electrical Characteristics | B1                      |  |

| 17.2              | Power-on event may disrupt operation                                                           | Electrical Characteristics | B1                      |  |

| 17.3              | First two ADC samples from the internal temperature sensor must be ignored                     | Electrical Characteristics | B1, C3, C5              |  |

# 1 JTAG

# 1.1 JTAG INTEST instruction does not work

# **Description:**

The JTAG INTEST (Boundary Scan) instruction does not properly capture data.

|     | Workaround:                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|     | None.                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|     | Silicon Revision Affected:                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|     | B1                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|     | Fixed:                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|     | Fixed in Rev C.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 1.2 | The Recover Locked Device sequence does not work as expected                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|     | Description:                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|     | If software configures any of the JTAG/SWD pins as GPIO or loses the ability to communicate with the debugger, there is a debug sequence that can be used to recover the microcontroller, called the Recover Locked Device sequence. After reconfiguring the JTAG/SWD pins, using the Recover Locked Device sequence does not recover the device. |  |  |  |  |  |

|     | Workaround:                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|     | To get the device unlocked, follow these steps:                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|     | <ol> <li>Power cycle the board and run the debug port unlock procedure in LM Flash Programmer. DO<br/>NOT power cycle when LM Flash Programmer tells you to.</li> </ol>                                                                                                                                                                           |  |  |  |  |  |

|     | <ol><li>Go to the Flash Utilities tab in LM Flash Programmer and do a mass erase operation (check<br/>"Entire Flash" and then click the Erase button). This erase appears to have failed, but that is<br/>okay.</li></ol>                                                                                                                         |  |  |  |  |  |

|     | 3. Power cycle the board.                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|     | 4. Go to the Flash Utilities tab in LM Flash Programmer and do another mass erase operation (check "Entire Flash" and then click the Erase button).                                                                                                                                                                                               |  |  |  |  |  |

|     | Silicon Revision Affected:                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|     | B1                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|     | Fixed:                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|     | Fixed in Rev C.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 1.3 | Boundary scan is not functional                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|     | Description:                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|     | The boundary scan is not functional on this device.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|     | Workaround:                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|     | None.                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|     | Silicon Revision Affected:                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

B1, C3, C5

#### Fixed:

Fixed on devices with date codes of 1A (October, 2011) or later.

**Note:** To determine the date code of your part, look at the first two characters following the dash on the third line of the part markings (highlighted in red in the following figure). The first number after the dash indicates the last decimal digit of the year. The second character indicates the month. Therefore, the following example shows a date code of 9B which indicates November 2009.

# 2 System Control

# 2.1 Sleep and Deep-Sleep mode not usable at higher speeds when ISRs reside in Flash memory

#### **Description:**

Sleep and Deep-Sleep modes cannot be used when running the processor at 66 or 80 MHz when the Interrupt Service Routines (ISRs) and vector table reside in Flash memory. If Sleep or Deep-Sleep mode is used at those speeds, an invalid PC is sometimes returned for the interrupt vector address when exiting sleep mode.

#### Workaround:

There are two possible workarounds for this issue:

- Store the ISRs and vector table in the on-chip SRAM when running the processor at 66 or 80 MHz.

- 2. Run the processor at 50 MHz.

#### Silicon Revision Affected:

В1

## Fixed:

Fixed in Rev C.

# 2.2 Device Capabilities registers may not accurately reflect available signals

## **Description:**

Some of the Device Capabilities register bits reflect the presence of specific pins on the microcontroller. These bits do not always properly reflect the available signals. Bits affected include **DC3** [31:0], **DC4** [15:14], **DC5** [27:24] and [7:0], and **DC8** [31:0]. Do not rely on the value of these bits in system design.

#### Workaround:

None.

#### Silicon Revision Affected:

**B1**

#### Fixed:

Fixed in Rev C.

# 2.3 The PIOSC is not trimmed by the factory

#### **Description:**

The PIOSC is not trimmed by the factory prior to shipment. When the PIOSC is not trimmed, its accuracy is ±18.75%.

#### Workaround:

For parts that have a Hibernation module, the PIOSC can be user calibrated. The PIOSC cannot be calibrated on parts without a Hibernation module. For more information, see the section entitled, "Precision Internal Oscillator Operation (PIOSC)" in the System Control chapter in the data sheet.

#### Silicon Revision Affected:

В1

#### Fixed:

Not fixed.

# 2.4 Non-word-aligned write to SRAM can cause incorrect value to be loaded

### **Description:**

If a word-aligned value is loaded from an SRAM location into a core register, then altered by storing a byte or halfword at an unaligned offset, the altered word-aligned value is not correctly indicated when loaded into a core register. The loaded value from the SRAM location into a core register reflects the original value, not the modified value.

The following assembly sequence causes the altered value loaded into a core register to not load the correct value, even though the correct value is visible in the SRAM memory location.

```

//

// Load a word-aligned value from an SRAM location into a

// core register (such as R0)

//

LDR R0, [SP, #+0];

//

// Store byte or halfword from the core register to

// the SRAM location at a non-word-aligned offset

//

STRB R0, [SP, #+1];

OR

STRB R0, [SP, #+2];

```

```

OR

STRB R0, [SP, #+3];

OR

STRH R0, [SP, #+1];

//

// Load the same word-aligned value of the same SRAM location

// into a core register (such as R0)

//

LDR R0, [SP, #+0];

```

This assembly sequence causes erroneous values only if these three instructions are executed in this order. However, the three instructions do not have to be consecutive, which means that other instructions can be placed in between the first and the second instructions, or the second and the third instructions, and the false value still occurs. Other instructions include, but are not limited to, branches in Flash, accesses to non-SRAM locations such as peripherals, and writes to other SRAM locations.

Pointers, structures, and unions are common C code methods that can be found in user code that may generate this assembly sequence and, therefore, result in incorrect values for variables. If using interrupts, it is possible to continue the assembly sequence in the interrupt handler, which could also return incorrect data.

For more information about this erratum as well as C code examples that may generate this assembly sequence, refer to the document, *Non-Word-Aligned Write to SRAM Additional Information* (SPMA047).

#### Workaround:

The type of compiler and optimization settings used in your application affects whether the problematic assembly code is generated from your user code. Each compiler behaves a little differently with respect to this erratum. The behavior for each compiler is not guaranteed due to the large number of compiler and tool version combinations.

At the assembly level, loading a volatile 32-bit-aligned word value from a different address in SRAM after storing and before loading in the assembly instruction sequence yields a correct value. A dummy SRAM load of a volatile 32-bit-aligned word from a different SRAM memory location should be inserted after the second assembly instruction (storing a byte or halfword from the core register to the desired SRAM location at a non-word-aligned offset) and before the third assembly instruction (loading the same word-aligned value of the desired SRAM location into a core register). This also means that a dummy SRAM load of a volatile 32-bit-aligned word from a different SRAM memory location should also be placed at the beginning of any interrupt routine, in case the third assembly instruction is executed before leaving the handler.

For more information about this erratum as well as C code examples that may generate this assembly sequence, refer to the document, *Non-Word-Aligned Write to SRAM Additional Information* (SPMA047).

#### Silicon Revision Affected:

B1, C3, C5

#### Fixed:

Not yet fixed.

# 2.5 Internal reset supervisors may not prevent incorrect device operation during power transitions

# **Description:**

This microcontroller incorporates internal Power-On Reset (POR) and Brown-Out Reset (BOR) supervisors to ensure that code only executes when power to the device is within specification. However, gaps in the voltage and timing thresholds of the internal supervisors result in a risk of incorrect operation during VDD power transitions.

Unexpected operation may occur that can include brief execution of random sections of user code including ROM functions and random instructions, as well as incorrect power-up initialization. The uncontrolled brief execution of random instructions may result in the undesired erasing or writing of non-volatile memories and GPIO state changes. There is also the possibility that the device may be left in a state where it does not operate correctly until a clean power cycle has been completed.

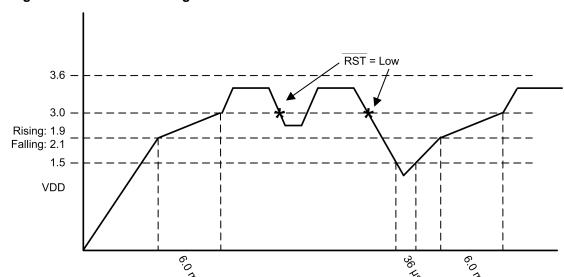

The Power-On Reset gap occurs because the supervisor can release internal state machine operation as soon as 6.0 ms after the VDD supply reaches 1.9 V. If VDD is still below the minimum operating voltage of 3.0 V after 6.0 ms, the power-up state machine may not function correctly, resulting in the effects described above. The  $\overline{\tt RST}$  pin of the device has no effect on the initialization state machine, therefore, a complete power-cycle is required to restore the initialization state machine.

The Brown-Out Reset threshold ( $V_{BTH}$ ) gap occurs because the brown-out supervisor has a threshold as low as 2.85 V, which is less than the minimum operating voltage on VDD, and also because it can take several microseconds to respond. BOR gaps can be encountered after power up, during steady state operation power-on, if the VDD rail has glitches, and also during power-down.

#### Workaround:

After initial power-up, any processor operation with VDD below 3.0 V may result in unexpected code execution resulting in the effects described above. The processor must be halted or the  $\overline{\tt RST}$  signal must be driven Low prior to VDD dropping below 3.0 V and stay in that state until VDD is above 3.0 V

If VDD falls below 2.1 V, it must continue to fall until it reaches 1.5 V. VDD must stay below 1.5 V for at least 36  $\mu$ s to ensure that a POR is triggered correctly. Additionally, the VDD power-up time between 1.9 V and 3.0 V must be at most 6.0 ms. If VDD falls below 3.0 V but stays above 2.1 V, it is not necessary for the voltage to continue falling below 2.1 V. VDD can come back up to 3.0 V without any additional timing requirements.

The system designer must ensure they meet the requirements listed below for power-up, steady state, and power-down:

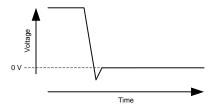

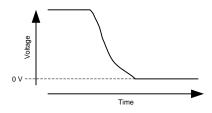

- 1. The VDD power-up, steady state, and power-down waveform meets the timing requirements shown in Figure 1 on page 14.

- 2. The power-up transition of VDD between 1.9 V and 3.0 V must not have any points where it decreases in voltage (must be monotonic).

- **3.** The power-down transition of VDD between 3.0 V and 1.5 V must not have any points where it increases in voltage (must be monotonic).

- **4.** Once steady-state operation between 3.0 V and 3.6 V is achieved, RST must go Low or the CPU execution must be halted prior to VDD falling below 3.0 V.

- 5. The **Brown-Out Reset Control (PBORCTL)** register must be set so that a brown-out event causes a reset.

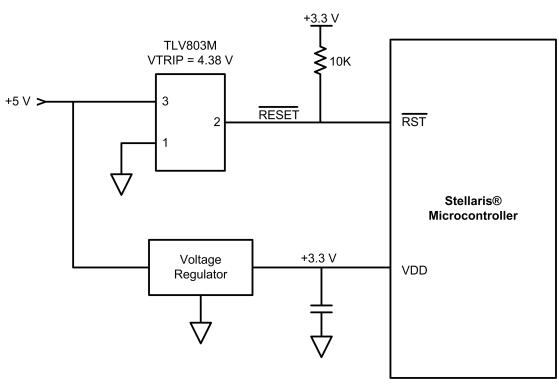

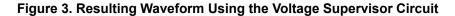

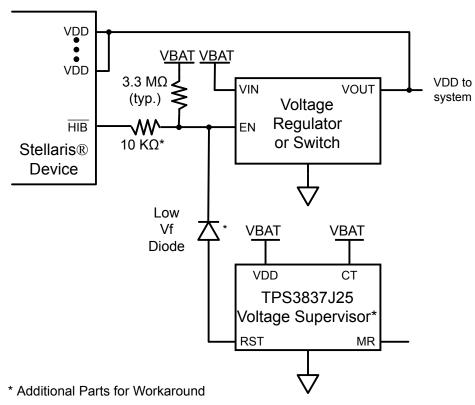

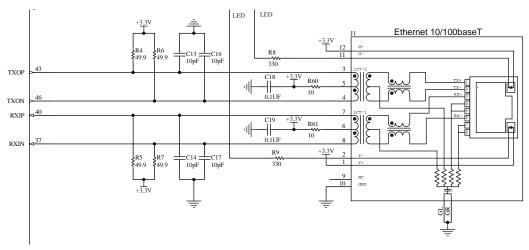

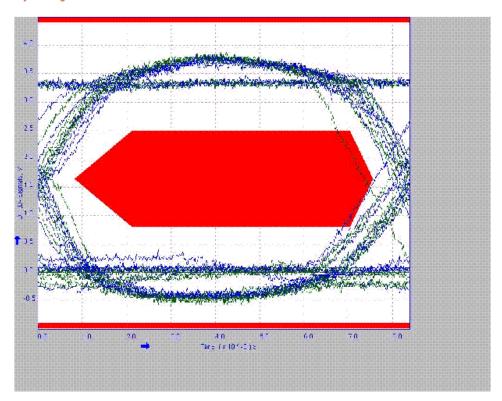

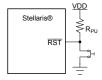

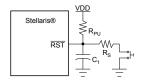

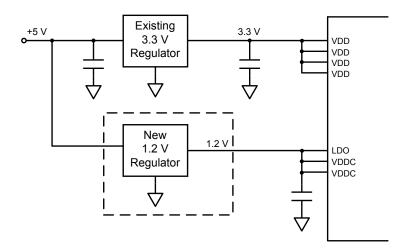

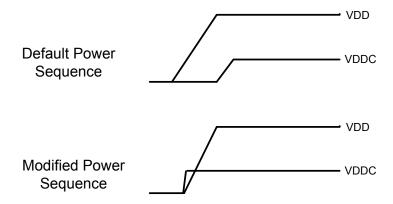

Depending on the system environment requirement, items 3, 4, and 5 in the above list may be met by using a voltage supervisor, such as the TLV803M, to monitor a higher voltage rail from which the VDD supply is regulated. Figure 2 on page 15 shows this implementation with a voltage supervisor monitoring the 5-V rail and a voltage trip point of 4.38 V. A voltage supervisor with a lower voltage trip point can be used to monitor the VDD (3.3-V) rail, however this supervisor must assert reset before VDD reaches 3.0 V. Regardless of the implemented voltage supervisor circuit, the system designer must ensure that there is enough time to assert  $\overline{\text{RST}}$  Low prior to VDD falling below 3.0 V. Figure 3 on page 15 shows the resulting waveform of the circuit shown in Figure 2 on page 15.

Figure 1. VDD Waveform Signature Limits

Figure 2. Using a Voltage Supervisor to Monitor the Voltage Rail

#### Silicon Revision Affected:

B1, C3, C5

#### Fixed:

Not yet fixed.

# 2.6 Chip select operation is not correct when using dual chip selects in Host Bus Continuous Read mode

### **Description:**

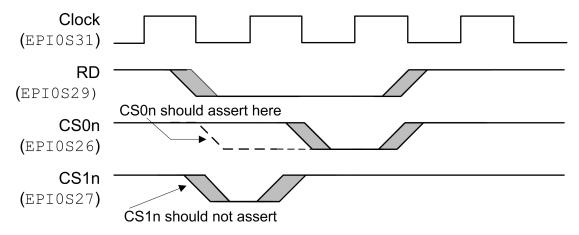

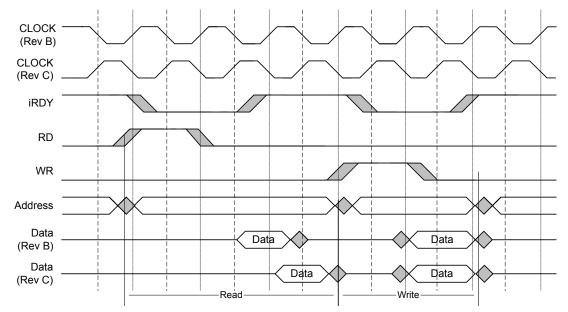

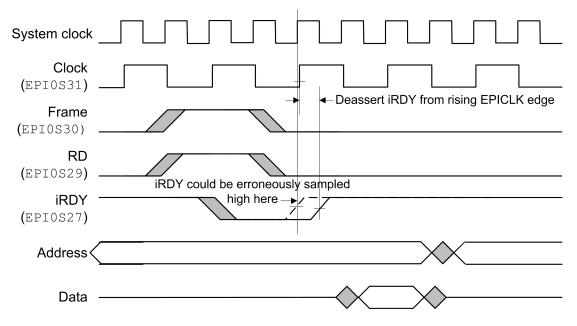

Chip select operation for the first read is not correct when the EPI module is in Host Bus mode and is configured to use dual chip selects (the CSCFG field in the EPIHBnCFG2 register is 0x2) and Continuous Read mode (the MODE field in the EPIHBnCFG register is 0x2). When accessing a memory region assigned to one chip select, the other chip select is asserted first along with the RD strobe. This incorrect chip select is de-asserted before the next EPI clock edge and the correct chip select is asserted on that EPI clock edge. The RD strobe remains asserted, but the number of cycles that it is asserted includes the time that it is asserted with the incorrect chip select.

For example, if the RD strobe is programmed to be asserted for two clocks (the RDWS field in the **EPIHBnCFG** register is 0x0), the signal is asserted for one clock cycle with the incorrect chip select and one clock cycle with the correct chip select. As long as the width of the RD strobe is adjusted for this one clock difference, data is read correctly in this mode. Figure 4 on page 16 shows the read and chip select timing of this example when accessing a memory region assigned to CS0n.

Subsequent reads while the OE signal is asserted operate as expected.

#### Workaround:

Use a value in the RDWS field in the **EPIHBnCFG** register that is 1 more than required for the peripheral in the system.

For example, if the peripheral requires a read strobe that is 4 EPI clocks wide, set the MODE field to be 0x2 (6 clocks) to account for the 1 clock difference in the strobe width.

Figure 4. Chip Selects

#### Silicon Revision Affected:

B1, C3, C5

#### Fixed:

Not yet fixed.

# 3 Hibernation Module

# 3.1 Hibernation module may have higher current draw than specified in data sheet under certain conditions

### **Description:**

If a battery voltage is applied to the VBAT power pin prior to power being applied to the VDD power pins of the device, the current draw from the VBAT pin is greater than expected. The current may be as high as 1.6 mA instead of the data sheet specified 17  $\mu$ A. The condition exists until power is applied to the VDD pin. Once the VDD pin has been powered, the VBAT current draw functions as expected. The VDD pin can then be powered up and down as required and the VBAT pin current specification is maintained.

#### Workaround:

The VBAT pin higher-than-specified current draw condition can be avoided if the microcontroller's VDD power pins are powered on prior to the time a battery voltage is initially applied to the VBAT pin.

#### Silicon Revision Affected:

B1

#### Fixed:

Fixed in Rev C.

# 3.2 Hibernate POR may not reset the Hibernation module until $V_{DD}$ is applied

#### **Description:**

If  $V_{DD}$  is not powered when voltage is first applied to  $V_{BAT}$ , the state of the Hibernation module is indeterminate and the  $\overline{\mathtt{HIB}}$  signal may be asserted. In this indeterminate state, a lock condition can occur in which the Hibernation module waits for a power-on-reset, but that reset cannot occur until the module deasserts  $\overline{\mathtt{HIB}}$ . This issue is related to the errata "Hibernation module may have higher current draw than specified in data sheet under certain conditions" on page 17.

### Workaround:

The workaround implementation depends on the system-level power supply configuration. For systems that use a battery as the primary power source, an external voltage supervisor (TPS383J25DBV or similar) circuit can be added to force the  $V_{DD}$  power supply to start when the battery voltage is first applied (see Figure 5). The voltage supervisor requires only 220 nA and generates a 200-ms positive pulse to turn on the  $V_{DD}$  regulator and activate the microcontroller's internal POR circuit.

Figure 5. Workaround Circuit to Ensure Initial Power Up

Silicon Revision Affected:

В1

#### Fixed:

Fixed in Rev C.

# 3.3 Power consumption increases if V<sub>DD</sub> is not restored after wake from Hibernation mode

## **Description:**

If a wake event occurs and  $V_{DD}$  does not rise to specified levels, then the wake event is held off until  $V_{DD}$  is within specified levels. If a large delay occurs between the wake event and VDD reaching specified levels, the  $V_{BAT}$  current increases substantially to a typical value of 255  $\mu$ A until  $V_{DD}$  reaches the specified levels, at which point the microcontroller comes out of hibernation and power consumption returns to expected levels.

### Workaround:

Ensure that  $V_{\text{DD}}$  reaches specified levels within 250  $\mu s$  after the wake event occurs.

## Silicon Revision Affected:

**B1**

#### Fixed:

Fixed in Rev C.

# 3.4 ESD protection on the V<sub>BAT</sub> pin does not meet specifications

## **Description:**

The ESD protection on the  $V_{BAT}$  pin fails when tested at 2 kV.

#### Workaround:

Extra precaution should be taken to protect the part from ESD events. Some applications may require system-level ESD protection on this pin.

#### Silicon Revision Affected:

**B1**

#### Fixed:

Fixed in Rev C.

# 3.5 VDD3ON mode may not be used

#### **Description:**

The VDD3ON mode may not be used.

#### Workaround:

None. Do not use the VDD3ON mode to enter hibernation.

### Silicon Revision Affected:

B1, C3, C5

#### Fixed:

Not yet fixed.

# 3.6 Hibernate module power consumption higher than expected in event wakeup configuration

#### **Description:**

With the Hibernation module configured for an external event wakeup, the current consumption of the device is higher than expected. The Hibernation module clock does not shut down properly during the hibernate asynchronous external wake mode resulting in extra current consumption. Some devices properly shut down the clock the first time entering this mode and others do not. When waking from a hibernate event, the Hibernation module clock is always enabled. In subsequent hibernate cycles, the oscillator is not shut down properly and remains active. Hibernate module current consumption averages 21µA with the clock disabled. The current consumption averages 31µA with the Hibernation module clock enabled.

#### Workaround:

When the Hibernation module clock is not required during hibernation, software can disable it by clearing the CLK32EN bit in the **Hibernation Control (HIBCTL)** register before going into Hibernation mode.

#### Silicon Revision Affected:

**B1**

### Fixed:

Fixed in Rev C.

# 3.7 The Real-Time Clock gains or loses time going in and out of hibernation when using a crystal

## **Description:**

When using a 4.194304-MHz crystal, the Real-Time clock in the Hibernation module gains or loses a small amount of time (on the order of one second over a 24-hour period when cycling hibernate mode 4 times a minute) when going in and out of hibernation.

#### Workaround:

Use an external 32.768-kHz oscillator as the source for the Hibernation module clock.

#### Silicon Revision Affected:

B1

#### Fixed:

Fixed in Rev C.

# 3.8 Wake-up time from Hibernation may exceed specifications

#### **Description:**

The Hibernation module is specified to resume operation after the  $\overline{WAKE}$  signal is asserted within 124 µs, however operation may not resume for 30 ms in some cases. (The "Hibernation Module AC Characteristics" table in the DS indicates 10 ms.)

#### Workaround:

None.

#### Silicon Revision Affected:

В1

## Fixed:

Fixed in Rev C3.

# 3.9 Low-battery detect circuit is powered down during hibernate

## **Description:**

The low-battery detect feature on the  $V_{BAT}$  input is only valid when  $V_{DD}$  power is present. As a result:

- Because the battery is not electrically loaded when V<sub>DD</sub> is present, the low-battery detect circuit may not reflect the actual battery status.

- In Hibernate mode, a low-battery condition may prevent wake until the battery is completely depleted.

|      | Workaround:                                                                                                                                                                                                                                                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | None.                                                                                                                                                                                                                                                                                                             |

|      | Silicon Revision Affected:                                                                                                                                                                                                                                                                                        |

|      | B1                                                                                                                                                                                                                                                                                                                |

|      | Fixed:                                                                                                                                                                                                                                                                                                            |

|      | Fixed in Rev C.                                                                                                                                                                                                                                                                                                   |

| 3.10 | Writes to certain Hibernation module registers sometimes fail                                                                                                                                                                                                                                                     |

|      | Description:                                                                                                                                                                                                                                                                                                      |

|      | Due to a synchronization issue with the independent clock domain of the Hibernation module, writes to certain registers may sometimes fail, even though the WRC bit in the HIBCTL register is set after the write occurs. Registers affected include HIBRTCC, HIBRTCM0, HIBRTCM1, HIBRTCLD, HIBRTCT, and HIBDATA. |

|      | Workaround:                                                                                                                                                                                                                                                                                                       |

|      | After performing a write to the listed Hibernation module registers or non-volatile memory, read the contents back and verify that they are correct. If they are incorrect, perform the write operation again                                                                                                     |

|      | Silicon Revision Affected:                                                                                                                                                                                                                                                                                        |

|      | B1, C3, C5                                                                                                                                                                                                                                                                                                        |

|      | Fixed:                                                                                                                                                                                                                                                                                                            |

|      | Not yet fixed.                                                                                                                                                                                                                                                                                                    |

| 3.11 | The WRC bit in the Hibernation Control register is R/W                                                                                                                                                                                                                                                            |

|      | Description:                                                                                                                                                                                                                                                                                                      |

|      | The WRC bit in the <b>Hibernation Control (HIBCTL)</b> register can be written. This bit should be a read-only bit.                                                                                                                                                                                               |

|      | Workaround:                                                                                                                                                                                                                                                                                                       |

|      | Wait until the WRC bit is set before writing to the <b>HIBCTL</b> register. Always use a read-modify-write sequence when writing to the register to avoid changing the state of the WRC bit. Changing the value of the WRC bit can cause improper operation.                                                      |