# Tiva<sup>™</sup> TM4C129DNCPDT Microcontroller

TECHNICAL BRIEF

# Copyright

Copyright © 2007-2013 Texas Instruments Incorporated. Tiva and TivaWare are trademarks of Texas Instruments Incorporated. ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited. All other trademarks are the property of others.

Portions Copyright © 2011 Synopsys, Inc. Used with permission. All rights reserved. Synopsys & DesignWare are registered trademarks of Synopsys, Inc.

Portions Copyright © 2007 Mentor Graphics Corporation. Used with permission. All rights reserved. Mentor Graphics is a registered trademark of Mentor Graphics Corporation.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

A Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Texas Instruments Incorporated 108 Wild Basin, Suite 350 Austin, TX 78746 http://www.ti.com/tm4c

http://www-k.ext.ti.com/sc/technical-support/product-information-centers.htm

WARNING – EXPORT NOTICE: Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU, and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from Disclosing party under this Agreement, or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S. or other applicable laws, without obtaining prior authorization from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws.

According to our best knowledge of the state and end-use of this product or technology, and in compliance with the export control regulations of dual-use goods in force in the origin and exporting countries, this technology is classified as follows:

■ US ECCN: EAR99

**EU ECCN: EAR99**

And may require export or re-export license for shipping it in compliance with the applicable regulations of certain countries.

# **Table of Contents**

| 1      | Architectural Overview                                     | 6  |  |  |

|--------|------------------------------------------------------------|----|--|--|

| 1.1    | Tiva™ C Series Overview                                    | 6  |  |  |

| 1.2    | TM4C129DNCPDT Microcontroller Overview                     | 7  |  |  |

| 1.3    | TM4C129DNCPDT Microcontroller Features                     | 10 |  |  |

| 1.3.1  | ARM Cortex-M4F Processor Core                              | 10 |  |  |

| 1.3.2  | On-Chip Memory                                             | 12 |  |  |

| 1.3.3  | External Peripheral Interface                              | 14 |  |  |

| 1.3.4  | Cyclical Redundancy Check (CRC)                            | 15 |  |  |

| 1.3.5  | .5 Advanced Encryption Standard (AES) Accelerator          |    |  |  |

| 1.3.6  | Data Encryption Standard (DES) Accelerator                 | 17 |  |  |

| 1.3.7  | Secure Hash Algorithm / Message Digest Algorithm (SHA/MD5) | 17 |  |  |

| 1.3.8  | Serial Communications Peripherals                          | 17 |  |  |

| 1.3.9  | System Integration                                         | 24 |  |  |

| 1.3.10 | Advanced Motion Control                                    | 30 |  |  |

| 1.3.11 | Analog                                                     | 32 |  |  |

| 1.3.12 | JTAG and ARM Serial Wire Debug                             | 34 |  |  |

| 1.3.13 | Packaging and Temperature                                  | 35 |  |  |

| 1.4    | Kits                                                       | 35 |  |  |

| 1.5    | Support Information                                        | 35 |  |  |

| 2      | Pin Diagram                                                | 36 |  |  |

| 3      | Signal Tables                                              | 37 |  |  |

| 3.1    | Signals by Pin Number                                      |    |  |  |

| 3.2    | Signals by Signal Name                                     |    |  |  |

| 3.3    | Signals by Function, Except for GPIO                       |    |  |  |

| 3.4    | GPIO Pins and Alternate Functions                          |    |  |  |

| 3.5    | Possible Pin Assignments for Alternate Functions           |    |  |  |

| 3.6    | Connections for Unused Signals                             |    |  |  |

| Α      | Package Information                                        | 85 |  |  |

| A.1    | Orderable Devices                                          |    |  |  |

| A.2    | Packaging Diagram                                          | 86 |  |  |

# **List of Figures**

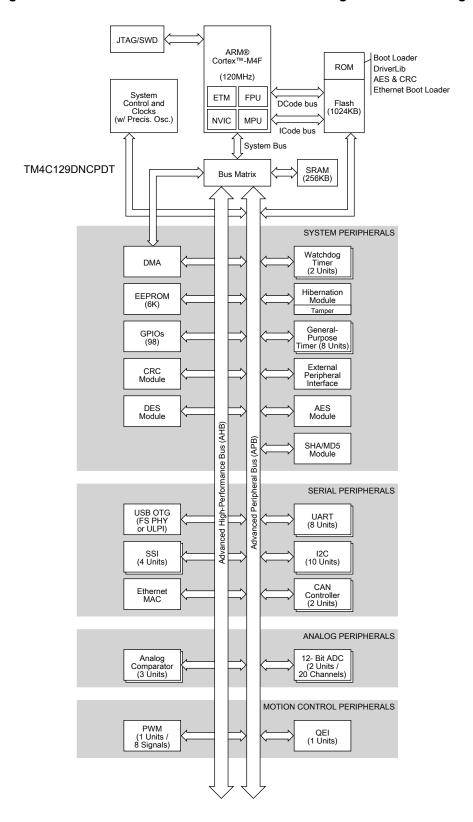

| Figure 1-1. | Tiva <sup>™</sup> TM4C129DNCPDT Microcontroller High-Level Block Diagram | 9  |

|-------------|--------------------------------------------------------------------------|----|

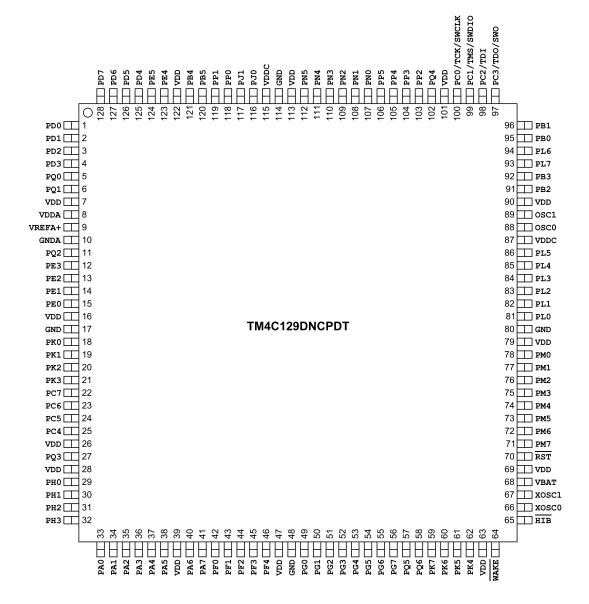

| Figure 2-1. | 128-Pin TQFP Package Pin Diagram                                         | 36 |

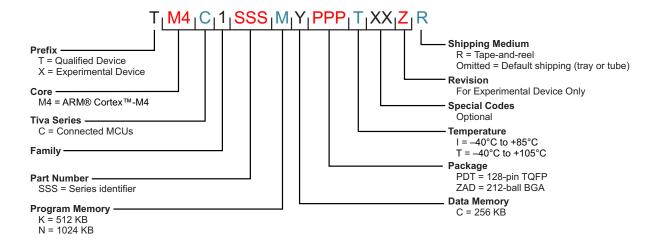

| Figure A-1. | Key to Part Numbers                                                      | 85 |

| Figure A-2. | TM4C129DNCPDT 128-Pin TQFP Package Diagram                               | 86 |

# **List of Tables**

| Table 1-1. | TM4C129DNCPDT Microcontroller Features           | 7  |

|------------|--------------------------------------------------|----|

| Table 3-1. | GPIO Pins With Default Alternate Functions       | 37 |

| Table 3-2. | Signals by Pin Number                            | 38 |

| Table 3-3. | Signals by Signal Name                           | 51 |

| Table 3-4. | Signals by Function, Except for GPIO             | 63 |

| Table 3-5. | GPIO Pins and Alternate Functions                | 74 |

| Table 3-6. | Possible Pin Assignments for Alternate Functions | 78 |

| Table 3-7. | Connections for Unused Signals (128-Pin TQFP)    | 84 |

| Table A-1. | Orderable Part Numbers                           | 85 |

# 1 Architectural Overview

Texas Instrument's Tiva™ C Series microcontrollers provide designers a high-performance ARM<sup>®</sup> Cortex™-M-based architecture with a broad set of integration capabilities and a strong ecosystem of software and development tools. Targeting performance and flexibility, the Tiva™ C Series architecture offers a 120 MHz Cortex-M with FPU, a variety of integrated memories and multiple programmable GPIO. Tiva™ C Series devices offer consumers compelling cost-effective solutions by integrating application-specific peripherals and providing a comprehensive library of software tools which minimize board costs and design-cycle time. Offering quicker time-to-market and cost savings, the Tiva™ C Series microcontrollers are the leading choice in high-performance 32-bit applications.

This chapter contains an overview of the Tiva™ C Series microcontrollers as well as details on the TM4C129DNCPDT microcontroller:

- "Tiva™ C Series Overview" on page 6

- "TM4C129DNCPDT Microcontroller Overview" on page 7

- "TM4C129DNCPDT Microcontroller Features" on page 10

- "Kits" on page 35

- "Support Information" on page 35

# 1.1 Tiva™ C Series Overview

The Tiva™ C Series ARM Cortex-M4 microcontrollers provide top performance and advanced integration. The product family is positioned for cost-effective applications requiring significant control processing and connectivity capabilities such as:

- Industrial communication equipment

- Network appliances, gateways & adapters

- Residential & commercial site monitoring & control

- Remote connectivity & monitoring

- Security/access systems

- HMI control panels

- Factory automation control

- Test and measurement equipment

- Fire & security systems

- Motion control & power inversion

- Medical instrumentation

- Gaming equipment

- Electronic point-of-sale (POS) displays

- Smart Energy/Smart Grid solutions

- Intelligent lighting control

- Vehicle tracking

Tiva™ C Series microcontrollers integrate a large variety of rich communication features to enable a new class of highly connected designs with the ability to allow critical, real-time control between performance and power. The microcontrollers feature integrated communication peripherals along with other high-performance analog and digital functions to offer a strong foundation for many

different target uses, spanning from human machine interface to networked system management controllers.

In addition, Tiva™ C Series microcontrollers offer the advantages of ARM's widely available development tools, System-on-Chip (SoC) infrastructure, and a large user community. Additionally, these microcontrollers use ARM's Thumb®-compatible Thumb-2 instruction set to reduce memory requirements and, thereby, cost. Finally, the TM4C129DNCPDT microcontroller is code-compatible to all members of the extensive Tiva™ C Series, providing flexibility to fit precise needs.

Texas Instruments offers a complete solution to get to market quickly, with evaluation and development boards, white papers and application notes, an easy-to-use peripheral driver library, and a strong support, sales, and distributor network.

# 1.2 TM4C129DNCPDT Microcontroller Overview

The TM4C129DNCPDT microcontroller combines complex integration and high performance with the features shown in Table 1-1.

Table 1-1. TM4C129DNCPDT Microcontroller Features

| Feature                                             | Description                                                                                |  |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Performance                                         |                                                                                            |  |  |

| Core                                                | ARM Cortex-M4F processor core                                                              |  |  |

| Performance                                         | 120-MHz operation; 150 DMIPS performance                                                   |  |  |

| Flash                                               | 1024 KB Flash memory                                                                       |  |  |

| System SRAM                                         | 256 KB single-cycle System SRAM                                                            |  |  |

| EEPROM                                              | 6KB of EEPROM                                                                              |  |  |

| Internal ROM                                        | Internal ROM loaded with TivaWare™ for C Series software                                   |  |  |

| External Peripheral Interface (EPI)                 | 8-/16-/32- bit dedicated interface for peripherals and memory                              |  |  |

| Security                                            |                                                                                            |  |  |

| Cyclical Redundancy Check (CRC) Hardware            | 16-/32-bit Hash function that supports four CRC forms                                      |  |  |

| Advanced Encryption Standard (AES)                  | Hardware accelerated data encryption and decryption based on 128-, 192-, and 256-bit keys  |  |  |

| Data Encryption Standard (DES)                      | Block cipher implementation with 168-bit effective key length                              |  |  |

| Hardware Accelerated Hash (SHA/MD5)                 | Advanced hash engine that supports SHA-1, SHA-2 or MD5 Hash computation                    |  |  |

| Tamper                                              | Support for four tamper inputs and configurable tamper event response                      |  |  |

| Communication Interfaces                            |                                                                                            |  |  |

| Universal Asynchronous Receivers/Transmitter (UART) | Eight UARTs                                                                                |  |  |

| Quad Synchronous Serial Interface (QSSI)            | Four SSI modules with Bi-, Quad- and advanced SSI support                                  |  |  |

| Inter-Integrated Circuit (I <sup>2</sup> C)         | Ten I <sup>2</sup> C modules with four transmission speeds including high-speed mode       |  |  |

| Controller Area Network (CAN)                       | Two CAN 2.0 A/B controllers                                                                |  |  |

| Ethernet MAC                                        | 10/100 Ethernet MAC with Media Independent Interface (MII) and Reduced MII (RMII)          |  |  |

| Universal Serial Bus (USB)                          | USB 2.0 OTG/Host/Device with ULPI interface option and Link Power Management (LPM) support |  |  |

| System Integration                                  |                                                                                            |  |  |

| Micro Direct Memory Access (μDMA)                   | ARM® PrimeCell® 32-channel configurable µDMA controller                                    |  |  |

Table 1-1. TM4C129DNCPDT Microcontroller Features (continued)

| Feature                             | Description                                                                                       |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| General-Purpose Timer (GPTM)        | Eight 16/32-bit GPTM blocks                                                                       |  |  |

| Watchdog Timer (WDT)                | Two watchdog timers                                                                               |  |  |

| Hibernation Module (HIB)            | Low-power battery-backed Hibernation module                                                       |  |  |

| General-Purpose Input/Output (GPIO) | 15 physical GPIO blocks                                                                           |  |  |

| Advanced Motion Control             |                                                                                                   |  |  |

| Pulse Width Modulator (PWM)         | One PWM module, with four PWM generator blocks and a control block, for a total of 8 PWM outputs. |  |  |

| Quadrature Encoder Interface (QEI)  | One QEI module                                                                                    |  |  |

| Analog Support                      |                                                                                                   |  |  |

| Analog-to-Digital Converter (ADC)   | Two 12-bit ADC modules, each with a maximum sample rate of one million samples/second             |  |  |

| Analog Comparator Controller        | Three independent integrated analog comparators                                                   |  |  |

| Digital Comparator                  | 16 digital comparators                                                                            |  |  |

| JTAG and Serial Wire Debug (SWD)    | One JTAG module with integrated ARM SWD                                                           |  |  |

| Package Information                 |                                                                                                   |  |  |

| Package                             | 128-pin TQFP                                                                                      |  |  |

| Operating Range (Ambient)           | Industrial (-40°C to 85°C) temperature range                                                      |  |  |

|                                     | Extended (-40°C to 105°C) temperature range                                                       |  |  |

Figure 1-1 on page 9 shows the features on the TM4C129DNCPDT microcontroller. Note that there are two on-chip buses that connect the core to the peripherals. The Advanced Peripheral Bus (APB) bus is the legacy bus. The Advanced High-Performance Bus (AHB) bus provides better back-to-back access performance than the APB bus.

Figure 1-1. Tiva<sup>™</sup> TM4C129DNCPDT Microcontroller High-Level Block Diagram

October 21, 2013 9

# 1.3 TM4C129DNCPDT Microcontroller Features

The TM4C129DNCPDT microcontroller component features and general function are discussed in more detail in the following section.

#### 1.3.1 ARM Cortex-M4F Processor Core

All members of the Tiva™ C Series, including the TM4C129DNCPDT microcontroller, are designed around an ARM Cortex-M processor core. The ARM Cortex-M processor provides the core for a high-performance, low-cost platform that meets the needs of minimal memory implementation, reduced pin count, and low power consumption, while delivering outstanding computational performance and exceptional system response to interrupts.

#### 1.3.1.1 Processor Core

- 32-bit ARM Cortex-M4F architecture optimized for small-footprint embedded applications

- 120-MHz operation; 150 DMIPS performance

- Outstanding processing performance combined with fast interrupt handling

- Thumb-2 mixed 16-/32-bit instruction set delivers the high performance expected of a 32-bit ARM core in a compact memory size usually associated with 8- and 16-bit devices, typically in the range of a few kilobytes of memory for microcontroller-class applications

- Single-cycle multiply instruction and hardware divide

- Atomic bit manipulation (bit-banding), delivering maximum memory utilization and streamlined peripheral control

- Unaligned data access, enabling data to be efficiently packed into memory

- IEEE754-compliant single-precision Floating-Point Unit (FPU)

- 16-bit SIMD vector processing unit

- Fast code execution permits slower processor clock or increases sleep mode time

- Harvard architecture characterized by separate buses for instruction and data

- Efficient processor core, system and memories

- Hardware division and fast digital-signal-processing orientated multiply accumulate

- Saturating arithmetic for signal processing

- Deterministic, high-performance interrupt handling for time-critical applications

- Memory protection unit (MPU) to provide a privileged mode for protected operating system functionality

- Enhanced system debug with extensive breakpoint and trace capabilities

- Serial Wire Debug and Serial Wire Trace reduce the number of pins required for debugging and tracing

- Migration from the ARM7<sup>™</sup> processor family for better performance and power efficiency

- Optimized for single-cycle Flash memory usage up to specific frequencies; see the data sheet for more information.

- Ultra-low power consumption with integrated sleep modes

#### 1.3.1.2 System Timer (SysTick)

ARM Cortex-M4F includes an integrated system timer, SysTick. SysTick provides a simple, 24-bit, clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used in several different ways, for example:

- An RTOS tick timer that fires at a programmable rate (for example, 100 Hz) and invokes a SysTick routine

- A high-speed alarm timer using the system clock

- A variable rate alarm or signal timer—the duration is range-dependent on the reference clock used and the dynamic range of the counter

- A simple counter used to measure time to completion and time used

- An internal clock-source control based on missing/meeting durations

#### 1.3.1.3 Nested Vectored Interrupt Controller (NVIC)

The TM4C129DNCPDT controller includes the ARM Nested Vectored Interrupt Controller (NVIC). The NVIC and Cortex-M4F prioritize and handle all exceptions in Handler Mode. The processor state is automatically stored to the stack on an exception and automatically restored from the stack at the end of the Interrupt Service Routine (ISR). The interrupt vector is fetched in parallel to the state saving, enabling efficient interrupt entry. The processor supports tail-chaining, meaning that back-to-back interrupts can be performed without the overhead of state saving and restoration. Software can set eight priority levels on 7 exceptions (system handlers) and 106 interrupts.

- Deterministic, fast interrupt processing: always 12 cycles, or just 6 cycles with tail-chaining (these values reflect no FPU stacking)

- External non-maskable interrupt signal (NMI) available for immediate execution of NMI handler for safety critical applications

- Dvnamically reprioritizable interrupts

- Exceptional interrupt handling via hardware implementation of required register manipulations

## 1.3.1.4 System Control Block (SCB)

The SCB provides system implementation information and system control, including configuration, control, and reporting of system exceptions.

## 1.3.1.5 Memory Protection Unit (MPU)

The MPU supports the standard ARM7 Protected Memory System Architecture (PMSA) model. The MPU provides full support for protection regions, overlapping protection regions, access permissions, and exporting memory attributes to the system.

## 1.3.1.6 Floating-Point Unit (FPU)

The FPU fully supports single-precision add, subtract, multiply, divide, multiply and accumulate, and square root operations. It also provides conversions between fixed-point and floating-point data formats, and floating-point constant instructions.

- 32-bit instructions for single-precision (C float) data-processing operations

- Combined multiply and accumulate instructions for increased precision (Fused MAC)

- Hardware support for conversion, addition, subtraction, multiplication with optional accumulate, division, and square-root

- Hardware support for denormals and all IEEE rounding modes

- 32 dedicated 32-bit single-precision registers, also addressable as 16 double-word registers

- Decoupled three stage pipeline

# 1.3.2 On-Chip Memory

The TM4C129DNCPDT microcontroller is integrated with the following set of on-chip memory and features:

- 256 KB single-cycle SRAM

- 1024 KB Flash memory

- 6KB EEPROM

- Internal ROM loaded with TivaWare<sup>™</sup> for C Series software:

- TivaWare<sup>™</sup> Peripheral Driver Library

- TivaWare Boot Loader

- Advanced Encryption Standard (AES) cryptography tables

- Cyclic Redundancy Check (CRC) error detection functionality

#### 1.3.2.1 SRAM

The TM4C129DNCPDT microcontroller provides 256 KB of single-cycle on-chip SRAM. The internal SRAM of the device is located at offset 0x2000.0000 of the device memory map.

The SRAM is implemented using four 32-bit wide interleaving SRAM banks (separate SRAM arrays) which allow for increased speed between memory accesses. The SRAM memory provides nearly 2 GB/s memory bandwidth at a 120 MHz clock frequency.

Because read-modify-write (RMW) operations are very time consuming, ARM has introduced *bit-banding* technology in the Cortex-M4F processor. With a bit-band-enabled processor, certain regions in the memory map (SRAM and peripheral space) can use address aliases to access individual bits in a single, atomic operation.

Data can be transferred to and from SRAM by the following masters:

- µDMA

- USB

- Ethernet Controller

#### 1.3.2.2 Flash Memory

The TM4C129DNCPDT microcontroller provides 1024 KB of on-chip Flash memory. The Flash memory is configured as four banks of 16K x 128 bits (4 \* 256 KB total) which are two-way interleaved. Memory blocks can be marked as read-only or execute-only, providing different levels of code protection. Read-only blocks cannot be erased or programmed, protecting the contents of those blocks from being modified. Execute-only blocks cannot be erased or programmed, and can only be read by the controller instruction fetch mechanism, protecting the contents of those blocks from being read by either the controller or by a debugger.

The TM4C129DNCPDT microcontroller provides enhanced performance and power savings by implementation of two sets of instruction prefetch buffers. Each prefetch buffer is  $2 \times 256$  bits and can be combined as a  $4 \times 256$ -bit prefetch buffer.

#### 1.3.2.3 ROM

The TM4C129DNCPDT ROM is preprogrammed with the following software and programs:

- TivaWare Peripheral Driver Library

- TivaWare Boot Loader

- Advanced Encryption Standard (AES) cryptography tables

- Cyclic Redundancy Check (CRC) error-detection functionality

The TivaWare Peripheral Driver Library is a royalty-free software library for controlling on-chip peripherals with a boot-loader capability. The library performs both peripheral initialization and control functions, with a choice of polled or interrupt-driven peripheral support. In addition, the library is designed to take full advantage of the stellar interrupt performance of the ARM Cortex-M4F core. No special pragmas or custom assembly code prologue/epilogue functions are required. For applications that require in-field programmability, the royalty-free TivaWare Boot Loader can act as an application loader and support in-field firmware updates.

The Advanced Encryption Standard (AES) is a publicly defined encryption standard used by the U.S. Government. AES is a strong encryption method with reasonable performance and size. In addition, it is fast in both hardware and software, is fairly easy to implement, and requires little memory. The Texas Instruments encryption package is available with full source code, and is based on Lesser General Public License (LGPL) source. An LGPL means that the code can be used within an application without any copyleft implications for the application (the code does not automatically become open source). Modifications to the package source, however, must be open source.

CRC (Cyclic Redundancy Check) is a technique to validate a span of data has the same contents as when previously checked. This technique can be used to validate correct receipt of messages (nothing lost or modified in transit), to validate data after decompression, to validate that Flash memory contents have not been changed, and for other cases where the data needs to be validated. A CRC is preferred over a simple checksum (e.g. XOR all bits) because it catches changes more readily.

**Note:** CRC and AES software programs are available in the TivaWare<sup>™</sup> for C Series software for backward-compatibility. A device that has enhanced CRC and AES integrated modules should utilize this hardware for best performance.

#### 1.3.2.4 **EEPROM**

The TM4C129DNCPDT microcontroller includes an EEPROM with the following features:

- 6Kbytes of memory accessible as 1536 32-bit words

- 96 blocks of 16 words (64 bytes) each

- Built-in wear leveling

- Access protection per block

- Lock protection option for the whole peripheral as well as per block using 32-bit to 96-bit unlock codes (application selectable)

- Interrupt support for write completion to avoid polling

- Endurance of 500K writes (when writing at fixed offset in every alternate page in circular fashion) to 15M operations (when cycling through two pages ) per each 2-page block.

# 1.3.3 External Peripheral Interface

The External Peripheral Interface (EPI) provides access to external devices using a parallel path. Unlike communications peripherals such as SSI, UART, and I<sup>2</sup>C, the EPI is designed to act like a bus to external peripherals and memory.

The EPI has the following features:

- 8/16/32-bit dedicated parallel bus for external peripherals and memory

- Memory interface supports contiguous memory access independent of data bus width, thus enabling code execution directly from SDRAM, SRAM and Flash memory

- Blocking and non-blocking reads

- Separates processor from timing details through use of an internal write FIFO

- Efficient transfers using Micro Direct Memory Access Controller (μDMA)

- Separate channels for read and write

- Read channel request asserted by programmable levels on the internal Non-Blocking Read FIFO (NBRFIFO)

- Write channel request asserted by empty on the internal Write FIFO (WFIFO)

The EPI supports three primary functional modes: Synchronous Dynamic Random Access Memory (SDRAM) mode, Traditional Host-Bus mode, and General-Purpose mode. The EPI module also provides custom GPIOs; however, unlike regular GPIOs, the EPI module uses a FIFO in the same way as a communication mechanism and is speed-controlled using clocking.

- Synchronous Dynamic Random Access Memory (SDRAM) mode

- Supports x16 (single data rate) SDRAM at up to 60 MHz

- Supports low-cost SDRAMs up to 64 MB (512 megabits)

- Includes automatic refresh and access to all banks/rows

- Includes a Sleep/Standby mode to keep contents active with minimal power draw

- Multiplexed address/data interface for reduced pin count

- Host-Bus mode

- Traditional x8 and x16 MCU bus interface capabilities

- Similar device compatibility options as PIC, ATmega, 8051, and others

- Access to SRAM, NOR Flash memory, and other devices, with up to 1 MB of addressing in unmultiplexed mode and 256 MB in multiplexed mode (512 MB in Host-Bus 16 mode with no byte selects)

- Support for up to 512 Mb PSRAM in quad chip select mode, with dedicated configuration register read and write enable.

- Support of both muxed and de-muxed address and data

- Access to a range of devices supporting the non-address FIFO x8 and x16 interface variant, with support for external FIFO (XFIFO) EMPTY and FULL signals

- Speed controlled, with read and write data wait-state counters

- Support for read/write burst mode to Host Bus

- Multiple chip select modes including single, dual, and quad chip selects, with and without ALE

- External iRDY signal provided for stall capability of reads and writes

- Manual chip-enable (or use extra address pins)

- General-Purpose mode

- Wide parallel interfaces for fast communications with CPLDs and FPGAs

- Data widths up to 32 bits

- Data rates up to 150 MB/second

- Optional "address" sizes from 4 bits to 20 bits

- Optional clock output, read/write strobes, framing (with counter-based size), and clock-enable input

- General parallel GPIO

- 1 to 32 bits, FIFOed with speed control

- Useful for custom peripherals or for digital data acquisition and actuator controls

# 1.3.4 Cyclical Redundancy Check (CRC)

The TM4C129DNCPDT microcontroller includes a CRC computation module for uses such as message transfer and safety system checks. This module can be used in conjunction with the AES and DES modules. The CRC has the following features:

- Support four major CRC forms:

- CRC16-CCITT as used by CCITT/ITU X.25

- CRC16-IBM as used by USB and ANSI

- CRC32-IEEE as used by IEEE802.3 and MPEG2

- CRC32C as used by G.Hn

- Allows word and byte feed

- Supports auto-initialization and manual initialization

- Supports MSb and LSb

- Supports CCITT post-processing

- Can be fed by µDMA, Flash memory and code

# 1.3.5 Advanced Encryption Standard (AES) Accelerator

The advanced encryption standard (AES) accelerator module provides hardware-accelerated data encryption and decryption operations based on a binary key. The AES module is a symmetrical cipher modules that supports a 128-bit, 192-bit, or 256-bit key in hardware for both encryption and decryption.

The AES has following features:

- Support for basic AES encrypt and decrypt operations:

- Galois/Counter Mode (GCM), with basic GHASH operation

- Counter Mode with CBC-MAC (CCM)

- XTS Mode

- Availability of the following feedback operating modes:

- Electronic Code Book Mode (ECB)

- Cipher Block Chaining Mode (CBC)

- Counter Mode (CTR)

- Cipher Feedback Mode (CFB), 128-bit

- F8 Mode

- Key sizes 128-, 192- and 256-bits

- Support for CBC\_MAC and Fedora 9 (F9) authentication modes

- Basic GHASH operation (when selecting no encryption)

- Key scheduling in hardware

- Support for µDMA transfers

- Fully synchronous design

# 1.3.6 Data Encryption Standard (DES) Accelerator

The DES module provides hardware accelerated data encryption and decryption functions. The module runs either the single DES or the triple DES (3DES) algorithm and supports electronic codebook (ECB), cipher block chaining (CBC), and cipher feedback (CFB) modes of operation.

The DES accelerator includes the following main features:

- DES/3DES encryption and decryption.

- Feedback modes: ECB, CBC, CFB

- Host interrupt or μDMA driven modes of operation. μDMA support for data and context in/result out

- Fully synchronous design

- Internal wide-bus interface

# 1.3.7 Secure Hash Algorithm / Message Digest Algorithm (SHA/MD5)

The SHA/MD5 module provides hardware-accelerated hash functions and can run:

- MD5 message digest algorithm developed by Ron Rivest in 1991

- SHA-1 algorithm compliant with the FIPS 180-3 standard

- SHA-2 (SHA-224 and SHA-256) algorithm compliant with the FIPS 180-3 standard

- Hash message authentication code (HMAC) operation

The algorithms produce a condensed representation of a message or a data file which can then be used to verify the message integrity.

The SHA/MD5 accelerator module includes the following main features:

- Hashing of 0 to 2 <sup>33</sup> 2 bytes of data (of which 2 <sup>32</sup> 1 bytes are in one pass) using the MD5, SHA-1, SHA-224, or SHA-256 hash algorithm (byte granularity only, no support for bit granularity)

- Automatic HMAC key pre-processing for HMAC keys up to 64 bytes

- Host-assisted HMAC key pre-processing for HMAC keys larger than 64 bytes

- HMAC from pre-computes (inner/outer digest) for improved performance on small blocks

- Supports µDMA operation for data and context in/result out transfers

- Supports interrupt to read the digest (signature)

# 1.3.8 Serial Communications Peripherals

The TM4C129DNCPDT controller supports both asynchronous and synchronous serial communications with:

- 10/100 Ethernet MAC with Advanced IEEE 1588 PTP hardware and both Media Independent Interface (MII) and Reduced MII (RMII) support

- Two CAN 2.0 A/B controllers

- USB 2.0 Controller OTG/Host/Device with optional high speed using external PHY through ULPI interface

- Eight UARTs with IrDA, 9-bit and ISO 7816 support.

- Ten I<sup>2</sup>C modules with four transmission speeds including high-speed mode

- Four Quad Synchronous Serial Interface modules (QSSI) with bi- and quad-SSI support

The following sections provide more detail on each of these communications functions.

#### 1.3.8.1 Ethernet MAC

The TM4C129DNCPDT Ethernet Controller consists of a fully integrated media access controller (MAC) with the following features:

- Conforms to the IEEE 802.3 specification

- 10BASE-T/100BASE-TX IEEE-802.3 compliant

- Supports 10/100 Mbps data transmission rates

- Supports full-duplex and half-duplex (CSMA/CD) operation

- Supports flow control and back pressure

- Full-featured and enhanced auto-negotiation

- Supports IEEE 802.1Q VLAN tag detection

- Conforms to IEEE 1588-2002 Timestamp Precision Time Protocol (PTP) protocol and the IEEE 1588-2008 Advanced Timestamp specification

- Transmit and Receive frame time stamping

- Precision Time Protocol

- Flexible pulse per second output

- Supports coarse and fine correction methods

- Multiple addressing modes

- Four MAC address filters

- Programmable 64-bit Hash Filter for multicast address filtering

- Promiscuous mode support

- Processor offloading

- Programmable insertion (TX) or deletion (RX) of preamble and start-of-frame data

- Programmable generation (TX) or deletion (RX) of CRC and pad data

- IP header and hardware checksum checking (IPv4, IPv6, TCP/UDP/ICMP)

- Highly configurable

- Supports network statistics with RMON/MIB counters

- Supports Magic Packet and wakeup frames

- Efficient transfers using integrated Direct Memory Access (DMA)

- Dual-buffer (ring) or linked-list (chained) descriptors

- Round-robin or fixed priority arbitration between TX/RX

- Descriptors support up to 8 kB transfer blocks size

- Programmable interrupts for flexible system implementation

- MII and RMII interface support

#### 1.3.8.2 Controller Area Network (CAN)

Controller Area Network (CAN) is a multicast shared serial-bus standard for connecting electronic control units (ECUs). CAN was specifically designed to be robust in electromagnetically noisy environments and can utilize a differential balanced line like RS-485 or twisted-pair wire. Originally created for automotive purposes, it is now used in many embedded control applications (for example, industrial or medical). Bit rates up to 1 Mbps are possible at network lengths below 40 meters. Decreased bit rates allow longer network distances (for example, 125 Kbps at 500m).

A transmitter sends a message to all CAN nodes (broadcasting). Each node decides on the basis of the identifier received whether it should process the message. The identifier also determines the priority that the message enjoys in competition for bus access. Each CAN message can transmit from 0 to 8 bytes of user information.

The TM4C129DNCPDT microcontroller includes two CAN units with the following features:

- CAN protocol version 2.0 part A/B

- Bit rates up to 1 Mbps

- 32 message objects with individual identifier masks

- Maskable interrupt

- Disable Automatic Retransmission mode for Time-Triggered CAN (TTCAN) applications

- Programmable loopback mode for self-test operation

- Programmable FIFO mode enables storage of multiple message objects

- Gluelessly attaches to an external CAN transceiver through the CANnTX and CANnRX signals

#### 1.3.8.3 Universal Serial Bus (USB)

Universal Serial Bus (USB) is a serial bus standard designed to allow peripherals to be connected and disconnected using a standardized interface without rebooting the system.

The TM4C129DNCPDT microcontroller has one USB controller that supports high and full speed multi-point communications and complies with the USB 2.0 standard for high-speed function. The USB controller can have three configurations: USB Device, USB Host, and USB On-The-Go (negotiated on-the-go as host or device when connected to other USB-enabled systems). Support for full-speed communication is provided by using the integrated USB PHY or optionally, a high-speed ULPI interface can communicate to an external PHY.

The USB module has the following features:

- Complies with USB-IF (Implementer's Forum) certification standards

- USB 2.0 high-speed (480 Mbps) operation with the integrated ULPI interface communicating with an external PHY

- Link Power Management support which uses link-state awareness to reduce power usage

- 4 transfer types: Control, Interrupt, Bulk, and Isochronous

- 16 endpoints

- 1 dedicated control IN endpoint and 1 dedicated control OUT endpoint

- 7 configurable IN endpoints and 7 configurable OUT endpoints

- 4 KB dedicated endpoint memory: one endpoint may be defined for double-buffered 1023-byte isochronous packet size

- VBUS droop detection and interrupt

- Integrated USB DMA with bus master capability

- Up to eight RX Endpoint channels and up to eight TX Endpoint channels are available.

- Each channel can be separately programmed to operate in different modes

- Incremental burst transfers of 4-, 8-, 16- or unspecified length supported

#### 1.3.8.4 UART

A Universal Asynchronous Receiver/Transmitter (UART) is an integrated circuit used for RS-232C serial communications, containing a transmitter (parallel-to-serial converter) and a receiver (serial-to-parallel converter), each clocked separately.

The TM4C129DNCPDT microcontroller includes eight fully programmable 16C550-type UARTs. Although the functionality is similar to a 16C550 UART, this UART design is not register compatible. The UART can generate individually masked interrupts from the Rx, Tx, modem flow control, modem status, and error conditions. The module generates a single combined interrupt when any of the interrupts are asserted and are unmasked.

The eight UARTs have the following features:

Programmable baud-rate generator allowing speeds up to 7.5 Mbps for regular speed (divide by 16) and 15 Mbps for high speed (divide by 8)

- Separate 16x8 transmit (TX) and receive (RX) FIFOs to reduce CPU interrupt service loading

- Programmable FIFO length, including 1-byte deep operation providing conventional double-buffered interface

- FIFO trigger levels of 1/8, 1/4, 1/2, 3/4, and 7/8

- Standard asynchronous communication bits for start, stop, and parity

- Line-break generation and detection

- Fully programmable serial interface characteristics

- 5, 6, 7, or 8 data bits

- Even, odd, stick, or no-parity bit generation/detection

- 1 or 2 stop bit generation

- IrDA serial-IR (SIR) encoder/decoder providing

- Programmable use of IrDA Serial Infrared (SIR) or UART input/output

- Support of IrDA SIR encoder/decoder functions for data rates up to 115.2 Kbps half-duplex

- Support of normal 3/16 and low-power (1.41-2.23 µs) bit durations

- Programmable internal clock generator enabling division of reference clock by 1 to 256 for low-power mode bit duration

- Support for communication with ISO 7816 smart cards

- Modem functionality available on the following UARTs:

- UART0 (modem flow control and modem status)

- UART1 (modem flow control and modem status)

- UART2 (modem flow control)

- UART3 (modem flow control)

- UART4 (modem flow control)

- EIA-485 9-bit support

- Standard FIFO-level and End-of-Transmission interrupts

- Efficient transfers using Micro Direct Memory Access Controller (µDMA)

- Separate channels for transmit and receive

- Receive single request asserted when data is in the FIFO; burst request asserted at programmed FIFO level

- Transmit single request asserted when there is space in the FIFO; burst request asserted at programmed FIFO level

Global Alternate Clock (ALTCLK) resource or System Clock (SYSCLK) can be used to generate baud clock

#### 1.3.8.5 I<sup>2</sup>C

The Inter-Integrated Circuit ( $I^2C$ ) bus provides bi-directional data transfer through a two-wire design (a serial data line SDA and a serial clock line SCL). The  $I^2C$  bus interfaces to external  $I^2C$  devices such as serial memory (RAMs and ROMs), networking devices, LCDs, tone generators, and so on. The  $I^2C$  bus may also be used for system testing and diagnostic purposes in product development and manufacture.

Each device on the I<sup>2</sup>C bus can be designated as either a master or a slave. I<sup>2</sup>C module supports both sending and receiving data as either a master or a slave and can operate simultaneously as both a master and a slave. Both the I<sup>2</sup>C master and slave can generate interrupts.

The TM4C129DNCPDT microcontroller includes I<sup>2</sup>C modules with the following features:

- Devices on the I<sup>2</sup>C bus can be designated as either a master or a slave

- Supports both transmitting and receiving data as either a master or a slave

- Supports simultaneous master and slave operation

- Four I<sup>2</sup>C modes

- Master transmit

- Master receive

- Slave transmit

- Slave receive

- Two 8-entry FIFOs for receive and transmit data

- FIFOs can be independently assigned to master or slave

- Four transmission speeds:

- Standard (100 Kbps)

- Fast-mode (400 Kbps)

- Fast-mode plus (1 Mbps)

- High-speed mode (3.33 Mbps)

- Glitch suppression

- SMBus support through software

- Clock low timeout interrupt

- Dual slave address capability

- Quick command capability

- Master and slave interrupt generation

- Master generates interrupts when a transmit or receive operation completes (or aborts due to an error)

- Slave generates interrupts when data has been transferred or requested by a master or when a START or STOP condition is detected

- Master with arbitration and clock synchronization, multimaster support, and 7-bit addressing mode

- Efficient transfers using Micro Direct Memory Access Controller (µDMA)

- Separate channels for transmit and receive

- Ability to execute single data transfers or burst data transfers using the RX and TX FIFOs in the I<sup>2</sup>C

#### 1.3.8.6 QSSI

Quad Synchronous Serial Interface (QSSI) is a bi-directional communications interface that converts data between parallel and serial. The QSSI module performs serial-to-parallel conversion on data received from a peripheral device, and parallel-to-serial conversion on data transmitted to a peripheral device. The QSSI module can be configured as either a master or slave device. As a slave device, the QSSI module can also be configured to disable its output, which allows a master device to be coupled with multiple slave devices. The TX and RX paths are buffered with separate internal FIFOs.

The QSSI module also includes a programmable bit rate clock divider and prescaler to generate the output serial clock derived from the QSSI module's input clock. Bit rates are generated based on the input clock and the maximum bit rate is determined by the connected peripheral.

The TM4C129DNCPDT microcontroller includes four QSSI modules with the following features:

- Four QSSI channels with Advanced, Bi- and Quad-SSI functionality

- Programmable interface operation for Freescale SPI or Texas Instruments synchronous serial interfaces in Legacy Mode. Support for Freescale interface in Bi- and Quad-SSI mode.

- Master or slave operation

- Programmable clock bit rate and prescaler

- Separate transmit and receive FIFOs, each 16 bits wide and 8 locations deep

- Programmable data frame size from 4 to 16 bits

- Internal loopback test mode for diagnostic/debug testing

- Standard FIFO-based interrupts and End-of-Transmission interrupt

- Efficient transfers using Micro Direct Memory Access Controller (µDMA)

- Separate channels for transmit and receive

- Receive single request asserted when data is in the FIFO; burst request asserted when FIFO contains 4 entries

- Transmit single request asserted when there is space in the FIFO; burst request asserted when four or more entries are available to be written in the FIFO

- Maskable µDMA interrupts for receive and transmit complete

- Global Alternate Clock (ALTCLK) resource or System Clock (SYSCLK) can be used to generate baud clock.

## 1.3.9 System Integration

The TM4C129DNCPDT microcontroller provides a variety of standard system functions integrated into the device, including:

- Direct Memory Access Controller (DMA)

- System control and clocks including on-chip precision 16-MHz oscillator

- Eight 32-bit timers (each of which can be configured as two 16-bit timers)

- Lower-power battery-backed Hibernation module

- Real-Time Clock in Hibernation module

- Two Watchdog Timers

- One timer runs off the main oscillator

- One timer runs off the precision internal oscillator

- Up to 98 GPIOs, depending on configuration

- Highly flexible pin muxing allows use as GPIO or one of several peripheral functions

- Independently configurable to 2-, 4-, 8-, 10-, or 12-mA drive capability

- Up to 4 GPIOs can have 18-mA drive capability

The following sections provide more detail on each of these functions.

#### 1.3.9.1 Direct Memory Access

The TM4C129DNCPDT microcontroller includes a Direct Memory Access (DMA) controller, known as micro-DMA ( $\mu$ DMA). The  $\mu$ DMA controller provides a way to offload data transfer tasks from the Cortex-M4F processor, allowing for more efficient use of the processor and the available bus bandwidth. The  $\mu$ DMA controller can perform transfers between memory and peripherals. It has dedicated channels for each supported on-chip module and can be programmed to automatically perform transfers between peripherals and memory as the peripheral is ready to transfer more data. The  $\mu$ DMA controller provides the following features:

- ARM PrimeCell® 32-channel configurable µDMA controller

- Support for memory-to-memory, memory-to-peripheral, and peripheral-to-memory in multiple transfer modes

- Basic for simple transfer scenarios

- Ping-pong for continuous data flow

- Scatter-gather for a programmable list of up to 256 arbitrary transfers initiated from a single request

- Highly flexible and configurable channel operation

- Independently configured and operated channels

- Dedicated channels for supported on-chip modules

- Flexible channel assignments

- One channel each for receive and transmit path for bidirectional modules

- Dedicated channel for software-initiated transfers

- Per-channel configurable priority scheme

- Optional software-initiated requests for any channel

- Two levels of priority

- Design optimizations for improved bus access performance between µDMA controller and the processor core

- µDMA controller access is subordinate to core access

- RAM striping

- Peripheral bus segmentation

- Data sizes of 8, 16, and 32 bits

- Transfer size is programmable in binary steps from 1 to 1024

- Source and destination address increment size of byte, half-word, word, or no increment

- Maskable peripheral requests

- Interrupt on transfer completion, with a separate interrupt per channel

### 1.3.9.2 System Control and Clocks

System control determines the overall operation of the device. It provides information about the device, controls power-saving features, controls the clocking of the device and individual peripherals, and handles reset detection and reporting.

- Device identification information: version, part number, SRAM size, Flash memory size, and so on

- Power control

- On-chip fixed Low Drop-Out (LDO) voltage regulator

- Hibernation module handles the power-up/down 3.3 V sequencing and control for the core digital logic and analog circuits

- Low-power options for microcontroller: Sleep and Deep-sleep modes with clock gating

- Low-power options for on-chip modules: software controls shutdown of individual peripherals and memory

- 3.3-V supply brown-out detection and reporting via interrupt or reset

- Multiple clock sources for microcontroller system clock. The TM4C129DNCPDT microcontroller is clocked by the system clock (SYSCLK) that is distributed to the processor and integrated peripherals after clock gating. The SYSCLK frequency is based on the frequency of the clock source and a divisor factor. A PLL is provided for the generation of system clock frequencies in excess of the reference clock provided. The reference clocks for the PLL are the PIOSC and the main crystal oscillator. The following clock sources are provided to the TM4C129DNCPDT microcontroller:

- 16-MHz Precision Oscillator (PIOSC)

- Main Oscillator (MOSC): A frequency-accurate clock source by one of two means: an external single-ended clock source is connected to the OSC0 input pin, or an external crystal is connected across the OSC0 input and OSC1 output pins.

- Low Frequency Internal Oscillator (LFIOSC): On-chip resource used during power-saving modes

- Hibernate RTC oscillator (RTCOSC) clock that can be configured to be the 32.768-kHz external oscillator source from the Hibernation (HIB) module or the HIB Low Frequency clock source (HIB LFIOSC), which is located within the Hibernation Module.

- Flexible reset sources

- Power-on reset (POR)

- Reset pin assertion

- Brown-out reset (BOR) detector alerts to system power drops

- Software reset

- Watchdog timer reset

- Hibernation module event

- MOSC failure

#### 1.3.9.3 Programmable Timers

Programmable timers can be used to count or time external events that drive the Timer input pins. Each 16/32-bit GPTM block provides two 16-bit timers/counters that can be configured to operate independently as timers or event counters, or configured to operate as one 32-bit timer or one 32-bit Real-Time Clock (RTC). Timers can also be used to trigger analog-to-digital (ADC) conversions and DMA transfers.

The General-Purpose Timer Module (GPTM) contains eight 16/32-bit GPTM blocks with the following functional options:

- Operating modes:

- 16- or 32-bit programmable one-shot timer

- 16- or 32-bit programmable periodic timer

- 16-bit general-purpose timer with an 8-bit prescaler

- 32-bit Real-Time Clock (RTC) when using an external 32.768-KHz clock as the input

- 16-bit input-edge count- or time-capture modes with an 8-bit prescaler

- 16-bit PWM mode with an 8-bit prescaler and software-programmable output inversion of the PWM signal

- The System Clock or a global Alternate Clock (ALTCLK) resource can be used as timer clock source. The global ALTCLK can be:

- PIOSC

- Hibernation Module Real-time clock output (RTCOSC)

- Low-frequency internal oscillator (LFIOSC)

- Count up or down

- Twelve 16/32-bit Capture Compare PWM pins (CCP)

- Daisy chaining of timer modules to allow a single timer to initiate multiple timing events

- Timer synchronization allows selected timers to start counting on the same clock cycle

- ADC event trigger

- User-enabled stalling when the microcontroller asserts CPU Halt flag during debug (excluding RTC mode)

- Ability to determine the elapsed time between the assertion of the timer interrupt and entry into the interrupt service routine

- Efficient transfers using Micro Direct Memory Access Controller (µDMA)

- Dedicated channel for each timer

- Burst request generated on timer interrupt

#### 1.3.9.4 CCP Pins

Capture Compare PWM pins (CCP) can be used by the General-Purpose Timer Module to time/count external events using the CCP pin as an input. Alternatively, the GPTM can generate a simple PWM output on the CCP pin.

The TM4C129DNCPDT microcontroller includes twelve 16/32-bit CCP pins that can be programmed to operate in the following modes:

- Capture: The GP Timer is incremented/decremented by programmed events on the CCP input. The GP Timer captures and stores the current timer value when a programmed event occurs.

- Compare: The GP Timer is incremented/decremented by programmed events on the CCP input. The GP Timer compares the current value with a stored value and generates an interrupt when a match occurs.

■ PWM: The GP Timer is incremented/decremented by the system clock. A PWM signal is generated based on a match between the counter value and a value stored in a match register and is output on the CCP pin.

#### 1.3.9.5 Hibernation Module (HIB)

The Hibernation module provides logic to switch power off to the main processor and peripherals and to wake on external or time-based events. The Hibernation module includes power-sequencing logic and has the following features:

- 32-bit real-time seconds counter (RTC) with 1/32,768 second resolution and a 15-bit sub-seconds counter

- 32-bit RTC seconds match register and a 15-bit sub seconds match for timed wake-up and interrupt generation with 1/32,768 second resolution

- RTC predivider trim for making fine adjustments to the clock rate

- Hardware Calendar Function

- Year, Month, Day, Day of Week, Hours, Minutes, Seconds

- Four-year leap compensation

- 24-hour or AM/PM configuration

- Two mechanisms for power control

- System power control using discrete external regulator

- On-chip power control using internal switches under register control

- $V_{DD}$  supplies power when valid, even if  $V_{BAT} > V_{DD}$

- Dedicated pin for waking using an external signal

- Capability to configure external reset (RST) pin and/or up to four GPIO port pins as wake source, with programmable wake level

- Tamper Functionality

- Support for four tamper inputs

- Configurable level, weak pullup, and glitch filter

- Configurable tamper event response

- Logging of up to four tamper events

- Optional BBRAM erase on tamper detection

- Tamper wake from hibernate capability

- Hibernation clock input failure detect with a switch to the internal oscillator on detection

- RTC operational and hibernation memory valid as long as V<sub>DD</sub> or V<sub>BAT</sub> is valid

- Low-battery detection, signaling, and interrupt generation, with optional wake on low battery

- GPIO pin state can be retained during hibernation

- Clock source from an internal low frequency oscillator (HIB LFIOSC) or a 32.768-kHz external crystal or oscillator

- Sixteen 32-bit words of battery-backed memory to save state during hibernation

- Programmable interrupts for:

- RTC match

- External wake

- Low battery

## 1.3.9.6 Watchdog Timers

A watchdog timer is used to regain control when a system has failed due to a software error or to the failure of an external device to respond in the expected way. The TM4C129DNCPDT Watchdog Timer can generate an interrupt, a non-maskable interrupt, or a reset when a time-out value is reached. In addition, the Watchdog Timer is ARM FiRM-compliant and can be configured to generate an interrupt to the microcontroller on its first time-out, and to generate a reset signal on its second timeout. Once the Watchdog Timer has been configured, the lock register can be written to prevent the timer configuration from being inadvertently altered.

The TM4C129DNCPDT microcontroller has two Watchdog Timer modules: Watchdog Timer 0 uses the system clock for its timer clock; Watchdog Timer 1 uses the PIOSC as its timer clock. The Watchdog Timer module has the following features:

- 32-bit down counter with a programmable load register

- Separate watchdog clock with an enable

- Programmable interrupt generation logic with interrupt masking and optional NMI function

- Lock register protection from runaway software

- Reset generation logic with an enable/disable

- User-enabled stalling when the microcontroller asserts the CPU Halt flag during debug

### 1.3.9.7 Programmable GPIOs

General-purpose input/output (GPIO) pins offer flexibility for a variety of connections. The TM4C129DNCPDT GPIO module is comprised of 15 physical GPIO blocks, each corresponding to an individual GPIO port. The GPIO module is FiRM-compliant (compliant to the ARM Foundation IP for Real-Time Microcontrollers specification) and supports 0-98 programmable input/output pins. The number of GPIOs available depends on the peripherals being used (see "Signal Tables" on page 37 for the signals available to each GPIO pin).

- Up to 98 GPIOs, depending on configuration

- Highly flexible pin muxing allows use as GPIO or one of several peripheral functions

- 3.3-V-tolerant in input configuration

- Advanced High Performance Bus accesses all ports:

- Ports A-H and J; Ports K-N and P-Q

- Fast toggle capable of a change every clock cycle for ports on AHB

- Programmable control for GPIO interrupts

- Interrupt generation masking

- Edge-triggered on rising, falling, or both

- Level-sensitive on High or Low values

- Per-pin interrupts available on Port P and Port Q

- Bit masking in both read and write operations through address lines

- Can be used to initiate an ADC sample sequence or a µDMA transfer

- Pin state can be retained during Hibernation mode; pins on port P can be programmed to wake on level in Hibernation mode

- Pins configured as digital inputs are Schmitt-triggered

- Programmable control for GPIO pad configuration

- Weak pull-up or pull-down resistors

- 2-mA, 4-mA, 6-mA, 8-mA, 10-mA and 12-mA pad drive for digital communication; up to four pads can sink 18-mA for high-current applications

- Slew rate control for 8-mA, 10-mA and 12-mA pad drive

- Open drain enables

- Digital input enables

#### 1.3.10 Advanced Motion Control

The TM4C129DNCPDT microcontroller provides motion control functions integrated into the device, including:

- Eight advanced PWM outputs for motion and energy applications

- Four fault inputs to promote low-latency shutdown

- One Quadrature Encoder Input (QEI)

The following provides more detail on these motion control functions.

#### 1.3.10.1 PWM

The TM4C129DNCPDT microcontroller contains one PWM module, with four PWM generator blocks and a control block, for a total of 8 PWM outputs. Pulse width modulation (PWM) is a powerful technique for digitally encoding analog signal levels. High-resolution counters are used to generate a square wave, and the duty cycle of the square wave is modulated to encode an analog signal.

Typical applications include switching power supplies and motor control. The TM4C129DNCPDT PWM module consists of four PWM generator block and a control block. Each PWM generator block contains one timer (16-bit down or up/down counter), two comparators, a PWM signal generator, a dead-band generator, and an interrupt/ADC-trigger selector. Each PWM generator block produces two PWM signals that can either be independent signals or a single pair of complementary signals with dead-band delays inserted.

Each PWM generator has the following features:

- Four fault-condition handling inputs to quickly provide low-latency shutdown and prevent damage to the motor being controlled

- One 16-bit counter

- Runs in Down or Up/Down mode

- Output frequency controlled by a 16-bit load value

- Load value updates can be synchronized

- Produces output signals at zero and load value

- Two PWM comparators

- Comparator value updates can be synchronized

- Produces output signals on match

- PWM signal generator

- Output PWM signal is constructed based on actions taken as a result of the counter and PWM comparator output signals

- Produces two independent PWM signals

- Dead-band generator

- Produces two PWM signals with programmable dead-band delays suitable for driving a half-H bridge

- Can be bypassed, leaving input PWM signals unmodified

- Can initiate an ADC sample sequence

The control block determines the polarity of the PWM signals and which signals are passed through to the pins. The output of the PWM generation blocks are managed by the output control block before being passed to the device pins. The PWM control block has the following options:

- PWM output enable of each PWM signal

- Optional output inversion of each PWM signal (polarity control)

- Optional fault handling for each PWM signal

- Synchronization of timers in the PWM generator blocks

- Synchronization of timer/comparator updates across the PWM generator blocks

- Extended PWM synchronization of timer/comparator updates across the PWM generator blocks

- Interrupt status summary of the PWM generator blocks

- Extended PWM fault handling, with multiple fault signals, programmable polarities, and filtering

- PWM generators can be operated independently or synchronized with other generators

#### 1.3.10.2 QEI

A quadrature encoder, also known as a 2-channel incremental encoder, converts linear displacement into a pulse signal. By monitoring both the number of pulses and the relative phase of the two signals, the position, direction of rotation, and speed can be tracked. In addition, a third channel, or index signal, can be used to reset the position counter. The TM4C129DNCPDT quadrature encoder with index (QEI) module interprets the code produced by a quadrature encoder wheel to integrate position over time and determine direction of rotation. In addition, it can capture a running estimate of the velocity of the encoder wheel. The input frequency of the QEI inputs may be as high as 1/4 of the processor frequency (for example, 30 MHz for a 120-MHz system).

The TM4C129DNCPDT microcontroller includes two QEI modules providing control of two motors at the same time with the following features:

- Position integrator that tracks the encoder position

- Programmable noise filter on the inputs

- Velocity capture using built-in timer

- The input frequency of the QEI inputs may be as high as 1/4 of the processor frequency (for example, 12.5 MHz for a 50-MHz system)

- Interrupt generation on:

- Index pulse

- Velocity-timer expiration

- Direction change

- Quadrature error detection

# 1.3.11 Analog

The TM4C129DNCPDT microcontroller provides analog functions integrated into the device, including:

- Two 12-bit Analog-to-Digital Converters (ADC), with a total of 20 analog input channels and each with a sample rate of one million samples/second

- Three analog comparators

- On-chip voltage regulator

The following provides more detail on these analog functions.

#### 1.3.11.1 ADC

An analog-to-digital converter (ADC) is a peripheral that converts a continuous analog voltage to a discrete digital number. The TM4C129DNCPDT ADC module features 12-bit conversion resolution and supports 20 input channels plus an internal temperature sensor. Four buffered sample sequencers allow rapid sampling of up to 20 analog input sources without controller intervention. Each sample sequencer provides flexible programming with fully configurable input source, trigger events, interrupt generation, and sequencer priority. Each ADC module has a digital comparator function that allows the conversion value to be diverted to a comparison unit that provides eight digital comparators.

The TM4C129DNCPDT microcontroller provides two ADC modules, each with the following features:

- 20 shared analog input channels

- 12-bit precision ADC

- Single-ended and differential-input configurations

- On-chip internal temperature sensor

- Maximum sample rate of one million samples/second

- Optional phase shift in sample time programmable from 22.5° to 337.5°

- Four programmable sample conversion sequencers from one to eight entries long, with corresponding conversion result FIFOs

- Flexible trigger control

- Controller (software)

- Timers

- Analog Comparators

- PWM

- GPIO

- Hardware averaging of up to 64 samples

- Eight digital comparators

- Converter uses signals VREFA+ and GNDA as the voltage reference

- Power and ground for the analog circuitry is separate from the digital power and ground

- Efficient transfers using Micro Direct Memory Access Controller (µDMA)

- Dedicated channel for each sample sequencer

- ADC module uses burst requests for DMA

- Global Alternate Clock (ALTCLK) resource or System Clock (SYSCLK) can be used to generate ADC clock

#### 1.3.11.2 Analog Comparators

An analog comparator is a peripheral that compares two analog voltages and provides a logical output that signals the comparison result. The TM4C129DNCPDT microcontroller provides three independent integrated analog comparators that can be configured to drive an output or generate an interrupt or ADC event.

The comparator can provide its output to a device pin, acting as a replacement for an analog comparator on the board, or it can be used to signal the application via interrupts or triggers to the ADC to cause it to start capturing a sample sequence. The interrupt generation and ADC triggering logic is separate. This means, for example, that an interrupt can be generated on a rising edge and the ADC triggered on a falling edge.

The TM4C129DNCPDT microcontroller provides three independent integrated analog comparators with the following functions:

- Compare external pin input to external pin input or to internal programmable voltage reference

- Compare a test voltage against any one of the following voltages:

- An individual external reference voltage

- A shared single external reference voltage

- A shared internal reference voltage

# 1.3.12 JTAG and ARM Serial Wire Debug

The Joint Test Action Group (JTAG) port is an IEEE standard that defines a Test Access Port and Boundary Scan Architecture for digital integrated circuits and provides a standardized serial interface for controlling the associated test logic. The TAP, Instruction Register (IR), and Data Registers (DR) can be used to test the interconnections of assembled printed circuit boards and obtain manufacturing information on the components. The JTAG Port also provides a means of accessing and controlling design-for-test features such as I/O pin observation and control, scan testing, and debugging. Texas Instruments replaces the ARM SW-DP and JTAG-DP with the ARM Serial Wire JTAG Debug Port (SWJ-DP) interface. The SWJ-DP interface combines the SWD and JTAG debug ports into one module providing all the normal JTAG debug and test functionality plus real-time access to system memory without halting the core or requiring any target resident code. The SWJ-DP interface has the following features:

- IEEE 1149.1-1990 compatible Test Access Port (TAP) controller

- Four-bit Instruction Register (IR) chain for storing JTAG instructions

- IEEE standard instructions: BYPASS, IDCODE, SAMPLE/PRELOAD, and EXTEST

- ARM additional instructions: APACC, DPACC and ABORT

- Integrated ARM Serial Wire Debug (SWD)

- Serial Wire JTAG Debug Port (SWJ-DP)

- Flash Patch and Breakpoint (FPB) unit for implementing breakpoints

- Data Watchpoint and Trace (DWT) unit for implementing watchpoints, trigger resources, and system profiling

- Instrumentation Trace Macrocell (ITM) for support of printf style debugging

- Embedded Trace Macrocell (ETM) for instruction trace capture

- Trace Port Interface Unit (TPIU) for bridging to a Trace Port Analyzer

# 1.3.13 Packaging and Temperature

- 128-pin RoHS-compliant TQFP package

- Industrial (-40°C to 85°C) ambient temperature range

- Extended (-40°C to 105°C) ambient temperature range

# **1.4** Kits

The Tiva™ C Series provides the hardware and software tools that engineers need to begin development quickly.

- Reference Design Kits accelerate product development by providing ready-to-run hardware and comprehensive documentation including hardware design files

- Evaluation Kits provide a low-cost and effective means of evaluating TM4C129DNCPDT microcontrollers before purchase

- Development Kits provide you with all the tools you need to develop and prototype embedded applications right out of the box

See the Tiva series website at <a href="http://www.ti.com/tiva-c">http://www.ti.com/tiva-c</a> for the latest tools available, or ask your distributor.

# 1.5 Support Information

For support on Tiva™ C Series products, contact the TI Worldwide Product Information Center nearest you.

# 2 Pin Diagram

The TM4C129DNCPDT microcontroller pin diagram is shown below.

Each GPIO signal is identified by its GPIO port unless it defaults to an alternate function on reset. In this case, the GPIO port name is followed by the default alternate function. To see a complete list of possible functions for each pin, see Table 3-5 on page 74.

Figure 2-1. 128-Pin TQFP Package Pin Diagram

## 3 Signal Tables

The following tables list the signals available for each pin. Signals are configured as GPIOs on reset, except for those noted below. Use the **GPIOAMSEL** register to select analog mode. For a GPIO pin to be used for an alternate digital function, the corresponding bit in the **GPIOAFSEL** register must be set. Further pin muxing options are provided through the PMCx bit field in the **GPIOPCTL** register, which selects one of several available peripheral functions for that GPIO.

Important: All GPIO pins are configured as GPIOs by default with the exception of the pins shown in the table below. A Power-On-Reset (POR) or asserting RST puts the pins back to their default state.

| GPIO Pin | Default State     | GPIOAFSEL Bit | GPIOPCTL PMCx Bit Field |

|----------|-------------------|---------------|-------------------------|

| PA[1:0]  | UART0             | 0             | 0x1                     |

| PA[5:2]  | SSI0              | 0             | 0x1                     |

| PB[3:2]  | I <sup>2</sup> C0 | 0             | 0x1                     |

| PC[3:0]  | JTAG/SWD          | 1             | 0x3                     |

**Table 3-1. GPIO Pins With Default Alternate Functions**

Table 3-2 on page 38 shows the pin-to-signal-name mapping, including functional characteristics of the signals. Each possible alternate analog and digital function is listed for each pin.

Table 3-3 on page 51 lists the signals in alphabetical order by signal name. If it is possible for a signal to be on multiple pins, each possible pin assignment is listed. The "Pin Mux" column indicates the GPIO and the encoding needed in the PMCx bit field in the **GPIOPCTL** register.

Table 3-4 on page 63 groups the signals by functionality, except for GPIOs. If it is possible for a signal to be on multiple pins, each possible pin assignment is listed.

Table 3-5 on page 74 lists the GPIO pins and their analog and digital alternate functions. The  $\mathtt{AINx}$  analog signals are not 5-V tolerant and go through an isolation circuit before reaching their circuitry. These signals are configured by clearing the corresponding  $\mathtt{DEN}$  bit in the **GPIO Digital Enable** (**GPIODEN**) register and setting the corresponding  $\mathtt{AMSEL}$  bit in the **GPIO Analog Mode Select** (**GPIOAMSEL**) register. Other analog signals are 3.3-V tolerant and are connected directly to their circuitry ( $\mathtt{CO-}$ ,  $\mathtt{CO+}$ ,  $\mathtt{C1-}$ ,  $\mathtt{C1+}$ ,  $\mathtt{C2-}$ ,  $\mathtt{C2+}$ ,  $\mathtt{USBOVBUS}$ ,  $\mathtt{USBOID}$ ). These signals are configured by clearing the  $\mathtt{DEN}$  bit in the **GPIO Digital Enable** (**GPIODEN**) register. The digital signals are enabled by setting the appropriate bit in the **GPIO Alternate Function Select** (**GPIOAFSEL**) and **GPIODEN** registers and configuring the  $\mathtt{PMCx}$  bit field in the **GPIO Port Control** (**GPIOPCTL**) register to the numeric enoding shown in the table below. Table entries that are shaded gray are the default values for the corresponding GPIO pin.

Table 3-6 on page 78 lists the signals based on number of possible pin assignments. This table can be used to plan how to configure the pins for a particular functionality. Application Note AN01274 Configuring Tiva™ C Series Microcontrollers with Pin Multiplexing provides an overview of the pin muxing implementation, an explanation of how a system designer defines a pin configuration, and examples of the pin configuration process.

Note: All digital inputs are Schmitt triggered.

## 3.1 Signals by Pin Number

Table 3-2. Signals by Pin Number

| Pin Number | Pin Name  | Pin Type | Buffer Type | Description                                                                                                                                                                                                                                                                                                       |

|------------|-----------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | PD0       | I/O      | TTL         | GPIO port D bit 0.                                                                                                                                                                                                                                                                                                |

|            | AIN15     | I        | Analog      | Analog-to-digital converter input 15.                                                                                                                                                                                                                                                                             |

|            | C0o       | 0        | TTL         | Analog comparator 0 output.                                                                                                                                                                                                                                                                                       |