# DisplayPort™1:1 Re-Driver with Link Training

Check for Samples: SN75DP130

#### **FEATURES**

- Supports DP v1.1a and DP v1.2 Signaling Including HBR2 Data Rates to 5.4Gbps

- Supports HDMI 1.4a with TMDS Clock Frequencies up to 340MHz

- Glue-Less interface to AMD, Intel, and NVIDIA Graphics Processors

- Auto-Configuration Through Link Training

- Output Signal Conditioning with Tunable Voltage Swing and Pre-Emphasis Gain

- Highly Configurable Input Variable Equalizer

- Two Device Options Including a Dual Power Supply Configuration for Lowest Power

- 2kV ESD HBM Protection

- Temperature Range: 0°C to 85°C

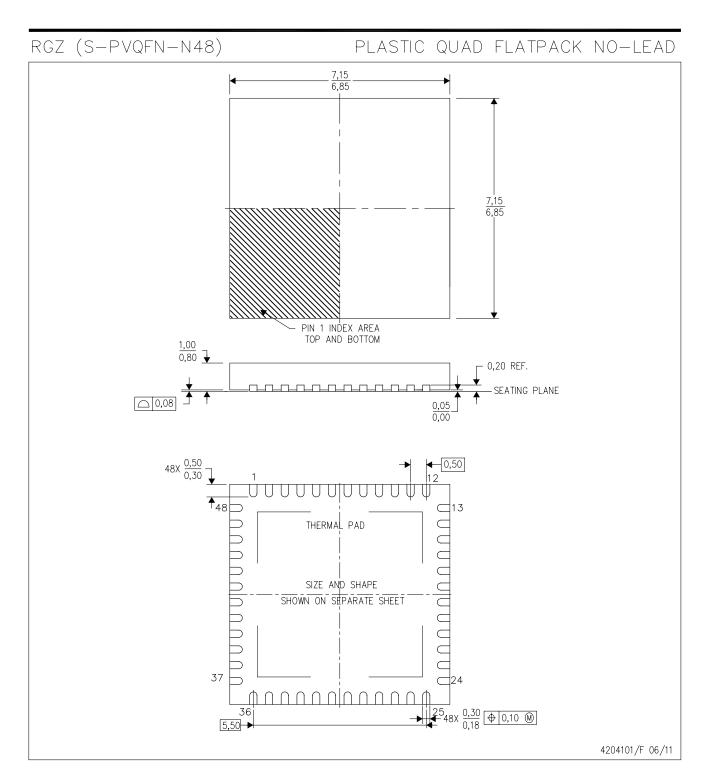

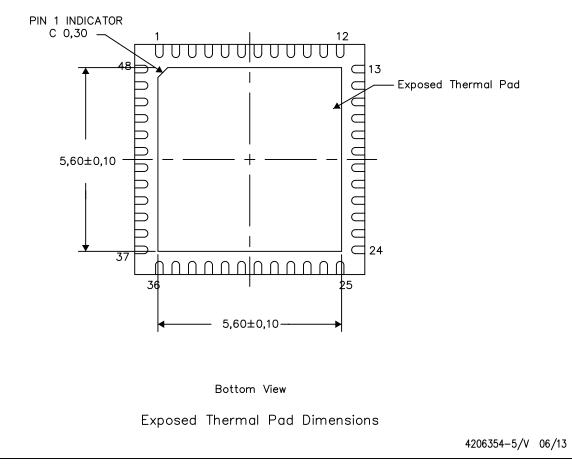

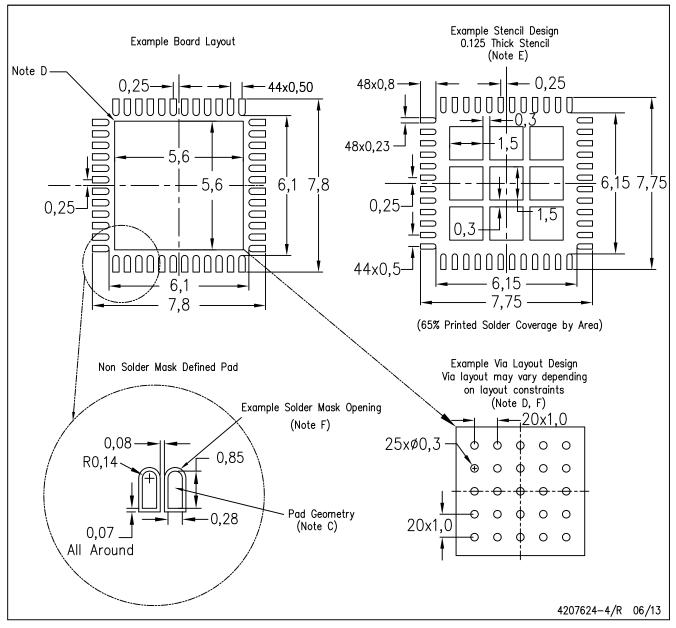

- 48 Pin 7mm × 7mm QFN Package

#### **APPLICATIONS**

- Notebook PC

- Desktop PC

- PC Docking Station

- PC Standalone Video Card

#### **DESCRIPTION**

The SN75DP130 is a single channel DisplayPort™ (DP) re-driver that regenerates the DP high speed digital link. The device complies with the VESA DisplayPort Standard Version 1.2, and supports a four lane Main Link interface signaling up to HBR2 rates at 5.4Gbps per lane, and supports DP++ Dual-Mode; offering TMDS signaling for DVI and full HDMI Version 1.4a support.

The device compensates for PCB related frequency loss and switching related loss to provide the optimum DP electrical performance from source to sink. The Main Link signal inputs feature configurable equalizers with selectable boost settings. At the Main Link output, four primary levels of differential output voltage swing (VOD) and four primary levels of pre-emphasis are available, as well as a secondary level of boost adjustment, programmed through I<sup>2</sup>C, for fine-tuning the Main Link output. The device can monitor the AUX channel and automatically adjust the output signaling levels and input equalizers in response to Link Training commands. Additionally, the SN75DP130 output signal conditioning and EQ parameters are fully programmable through the I<sup>2</sup>C interface.

The SN75DP130 offers separate AUX and DDC source interfaces that connect to a single AUX sink channel. This minimizes component count when implemented with a graphics processor (GPU) comprising separate DDC and AUX interfaces. For GPUs with combined DDC/AUX, the device can operate as a FET switch to short circuit the AUX channel AC coupling caps while connected to a TMDS sink device. Other sideband circuits such as Hot Plug Detect (HPD) are optimized to reduce external components, providing a seamless connection to Intel, AMD, and NVIDIA graphics processors.

The SN75DP130 is optimized for mobile applications, and contains activity detection circuitry on the Main Link input that transitions to a low-power Output Disable mode in the absence of a valid input signal. Other low power modes are supported, including a Standby mode with typical dissipation of ~2mW when no video sink (e.g., monitor) is connected.

The device is characterized for an extended operational temperature range from 0°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### TYPICAL IMPLEMENTATIONS

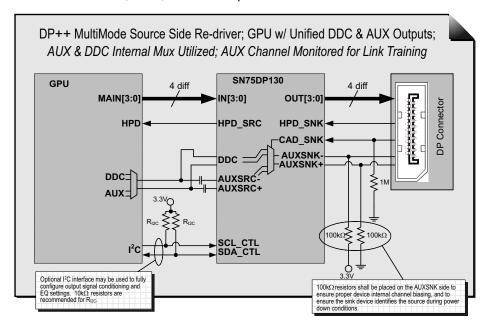

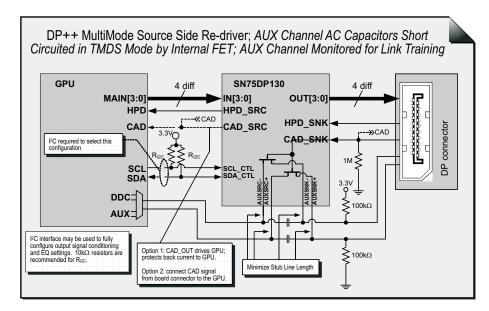

The configuration shown in Figure 1 supports a GPU with unified AUX/DDC interfaces. This circuit provides back current protection into the GPU AUX, HPD, and CAD inputs.

Figure 1. DP++ Dual-Mode in a Unified AUX/DDC Configuration

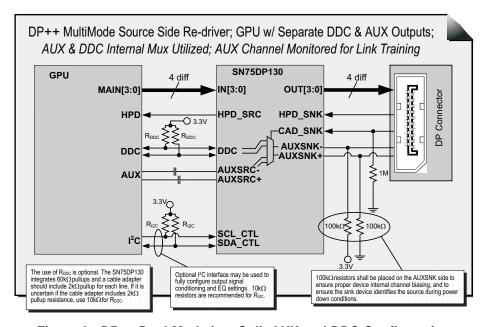

The configuration shown in Figure 2 supports a GPU with separate DDC and AUX interfaces, and overcomes the need for an external AUX to DDC switch. This circuit provides back current protection into the GPU AUX, HPD, and CAD inputs.

Figure 2. DP++ Dual-Mode in a Split AUX and DDC Configuration

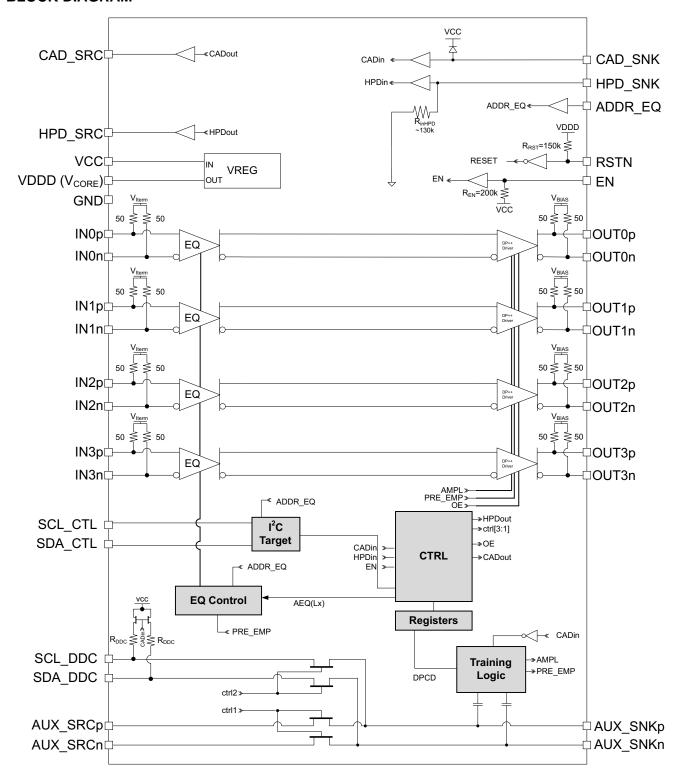

#### **BLOCK DIAGRAM**

#### **TERMINAL ASSIGNMENTS**

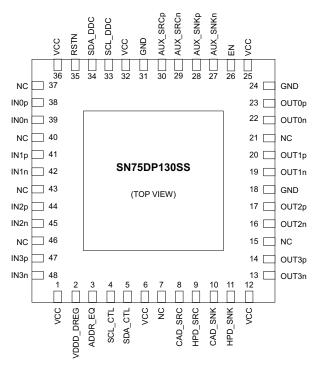

Figure 3. SN75DP130SS Single Supply

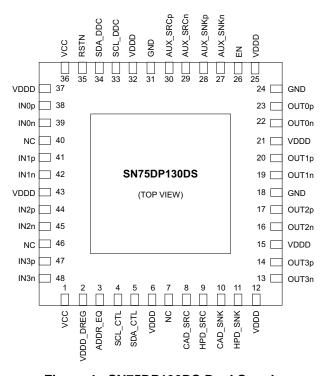

Figure 4. SN75DP130DS Dual Supply

### **PIN FUNCTIONS**

| PIN                   |                    |                                 | PERCENTION                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------|--------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                  | NO.                | 1/0                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |  |  |  |

| MAIN LINK TERMINALS   |                    | 1                               |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| IN0p, IN0n            | 38, 39             |                                 | DisplayPort Main Link Lane 0 Differential Input                                                                                                                                                                                                                                                                                         |  |  |  |

| IN1p, IN1n            | 41, 42             | Input                           | DisplayPort Main Link Lane 1 Differential Input                                                                                                                                                                                                                                                                                         |  |  |  |

| IN2p, IN2n            | 44, 45             | (100Ω diff)                     | DisplayPort Main Link Lane 2 Differential Input                                                                                                                                                                                                                                                                                         |  |  |  |

| IN3p, IN3n            | 47, 48             | -                               | DisplayPort Main Link Lane 3 Differential Input                                                                                                                                                                                                                                                                                         |  |  |  |

| OUT0p, OUT0n          | 23, 22             |                                 | DisplayPort Main Link Lane 0 Differential Output                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT1p, OUT1n          | 20, 19             | Output                          | DisplayPort Main Link Lane 1 Differential Output                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT2p, OUT2n          | 17, 16             | (100Ω diff)                     | DisplayPort Main Link Lane 2 Differential Output                                                                                                                                                                                                                                                                                        |  |  |  |

| OUT3p, OUT3n          | 14, 13             |                                 | DisplayPort Main Link Lane 3 Differential Output                                                                                                                                                                                                                                                                                        |  |  |  |

| AUX CHANNEL AND DD    | C DATA TE          | RMINALS                         |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| AUX_SRCp,<br>AUX_SRCn | 30, 29             | I/O<br>(100Ω diff)              | Source Side Bidirectional DisplayPort Auxiliary Data Channel. If the AUX_SNK channel is used for monitoring only, these signals are not used and may be left open.                                                                                                                                                                      |  |  |  |

| AUX_SNKp, AUX_SNKn    | 28, 27             | I/O<br>(100Ω diff)              | Sink Side Bidirectional DisplayPort Auxiliary Data Channel.                                                                                                                                                                                                                                                                             |  |  |  |

| SCL_DDC, SDA_DDC      | 33, 34             | I/O                             | Bidirectional I $^2$ C Display Data Channel (DDC) for TMDS mode. These signals may be utilized together with AUX_SNK to form a FET switch to short-circuit the AC coupling capacitors during TMDS operation in a DP++ Dual-Mode configuration. These terminals include integrated 60 k $\Omega$ pull-up resistors                       |  |  |  |

| HPD, CAD, and CONTRO  | L TERMINA          | ALS                             |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| HPD_SRC               | 9                  | 0                               | Hot Plug Detect Output to the DisplayPort Source.                                                                                                                                                                                                                                                                                       |  |  |  |

|                       |                    |                                 | DisplayPort Hot Plug Detect Input from Sink. This device input is 5V tolerant.                                                                                                                                                                                                                                                          |  |  |  |

| HPD_SNK               | 11                 | I                               | Note: Pull this input high during compliance testing or use ${}^{\rho}C$ control interface to go into compliance test mode and control HPD_SNK and HPD_SRC by software.                                                                                                                                                                 |  |  |  |

| CAD_SRC               | 8                  | 0                               | DP Cable Adapter Detect Output. This output typically drives the GPU CAD input.                                                                                                                                                                                                                                                         |  |  |  |

| CAD_SNK               | 10                 | ı                               | DisplayPort Cable Adapter Detect Input. This input tolerates a 5V supply with a supply impedance higher than $90k\Omega$ . A device internal zener diode limits the input voltage to 3.3V. An external $1M\Omega$ resistor to GND is recommended. This terminal is used to select DP mode or TMDS mode in a DP++ Dual-Mode application. |  |  |  |

| SCL_CTL, SDA_CTL      | 4, 5               | I/O                             | Bidirectional I <sup>2</sup> C interface to configure the SN75DP130. This interface is active independent of the EN input but inactive when RSTN is low.                                                                                                                                                                                |  |  |  |

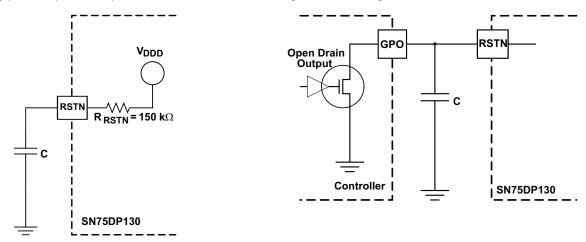

|                       |                    |                                 | Active Low Device Reset. This input includes a $150 \mathrm{k}\Omega$ resistor to the VDDD core supply. An external capacitor to GND is recommended on the RSTN input to provide a power-up delay (see the $V_{IL}$ and $V_{IH}$ specifications in the RECOMMENDED OPERATION CONDITIONS table).                                         |  |  |  |

| RSTN                  | 35                 | I                               | This signal is used to place the SN75DP130 into Shutdown mode for the lowest power consumption. When the RSTN input is asserted, all outputs (excluding HPD_SRC and CAD_SRC) are high-impedance, and inputs (excluding HPD_SNK and CAD_SNK) are ignored; all I <sup>2</sup> C and DPCD registers are reset to their default values.     |  |  |  |

|                       |                    |                                 | At power up, the RSTN input must not be de-asserted until the VCC and VDDD supplies have reached at least the minimum recommended supply voltage level (see Figure 5 for timing requirements).                                                                                                                                          |  |  |  |

| EN                    | 26                 | ı                               | Device Enable. This input incorporates an internal pullup of 200kΩ.                                                                                                                                                                                                                                                                     |  |  |  |

| ADDR_EQ               | 3                  | 3-level Input                   | I <sup>2</sup> C Target Address Select and EQ Configuration Input. If the I <sup>2</sup> C bus is used, this input setting selects the I <sup>2</sup> C target address, as described in Table 7. This input also configures the input EQ to the device, as described in Table 5.                                                        |  |  |  |

| SUPPLY AND GROUND     | TERMINALS          | S                               |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VDDD                  | 6, 12, 15, 2       | DP130DS<br>1, 25, 32, 37,<br>43 | Digital low voltage core and Main Link supply for SN75DP130DS device option. Nominally 1.1V.                                                                                                                                                                                                                                            |  |  |  |

| vcc                   | 1, 6, 12,<br>SN75D | P130SS<br>25, 32, 36<br>P130DS  | 3.3V Supply                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                       | 1,                 | , 36                            |                                                                                                                                                                                                                                                                                                                                         |  |  |  |

#### PIN FUNCTIONS (continued)

| PIN       |                                                                         | 1/0 | DESCRIPTION                                                                                                                                                                                         |  |

|-----------|-------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | NO.                                                                     | I/O | DESCRIPTION                                                                                                                                                                                         |  |

| VDDD_DREG | 2<br>18, 24, 31, and                                                    |     | SN75DP130SS: Digital voltage regulator decoupling; install 1µF to GND. SN75DP130DS: Treat same as VDDD; this pin will be most noisy of all VDDD terminals and needs a de-coupling capacitor nearby. |  |

| GND       |                                                                         |     | Ground. Reference GND connections include the device package exposed thermal pad.                                                                                                                   |  |

| NC        | NC SN75DP130SS<br>7, 15, 21, 37, 40, 43, 46<br>SN75DP130DS<br>7, 40, 46 |     | No Connect. These terminals may be left unconnected, or connect to CND                                                                                                                              |  |

| NC        |                                                                         |     | No Connect. These terminals may be left unconnected, or connect to GND.                                                                                                                             |  |

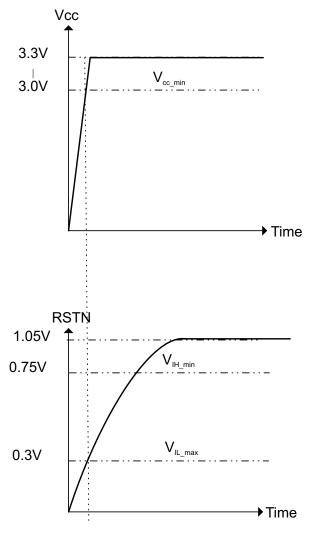

#### **DP130 POWER SEQUENCING**

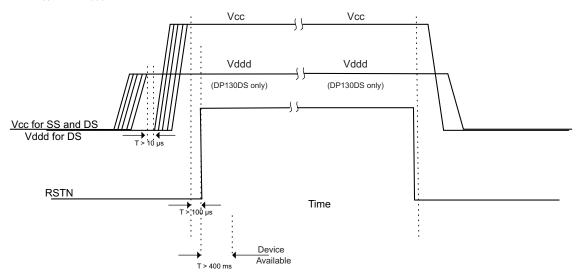

The following power-up and power-down sequences describe how the RSTN signal is applied to the SN75DP130.

#### **Power-Up Sequence:**

- 1. Apply  $V_{cc}$  with less than a 10-ms ramp time for the DP130SS and for the DP130DS, apply  $V_{ddd}$  then  $V_{cc}$  (both having less than 10-ms ramp time) devices.  $V_{ddd}$  must be asserted first and stable for greater than 10 µs before  $V_{cc}$  is applied.

- 2. RSTN must remain asserted until  $V_{cc}/V_{ddd}$  voltage has reached minimum recommended operation for more than 100  $\mu$ s.

- 3. De-assert RSTN (Note: This RSTN is a 1.05-V interface and is internally connected to  $V_{ddd\_dreg}$  through a 150-k $\Omega$  resistor).

- 4. Device will be available for operation approximately 400 ms after a valid reset.

#### **Power-Down Sequence:**

- 1. Assert RSTN to the device.

- 2. Remove  $V_{cc}$  and  $V_{ddd}$ .

Figure 5. Power-Up and Power-Down Sequence

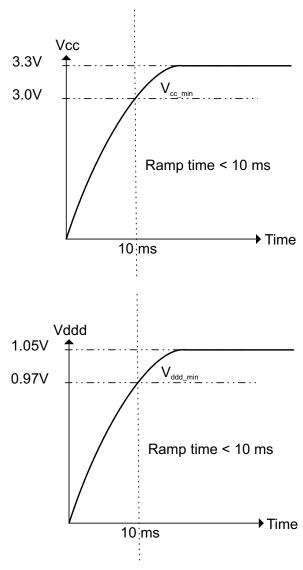

Figure 6. V<sub>CC</sub>/V<sub>ddd</sub> Ramp Recommendation

Figure 7. RSTN Voltage Thresholds

# ORDERING INFORMATION(1)

| PART NUMBER     | PART MARKING | PACKAGE                        |

|-----------------|--------------|--------------------------------|

| SN75DP130DSRGZR | DP130DS      | 48-pin QFN reel                |

| SN75DP130SSRGZR | DP130SS      | 48-pin QFN reel                |

| SN75DP130DSRGZT | DP130DS      | 48-pin QFN small quantity tape |

| SN75DP130SSRGZT | DP130SS      | 48-pin QFN small quantity tape |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                         |                             |                                                                                                                                                                                          | VALUE                                         | UNIT |  |

|-------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|--|

| Supply voltage          | V <sub>CC</sub>             | -0.3 to 4.0                                                                                                                                                                              | V                                             |      |  |

| range                   | $V_{DDD}$ , $V_{DDD\_DREG}$ |                                                                                                                                                                                          |                                               | V    |  |

|                         | Main link I/O diffe         | rential voltage                                                                                                                                                                          | -0.3 to 1.3 V<br>-0.3 to 5.5 V<br>-0.3 to 4 V |      |  |

| Voltage range           | HPD_SNK                     | -0.3 to 4.0 V -0.3 to 1.3 V ential voltage -0.3 to 1.3 V -0.3 to 5.5 V -0.3 to 5.5 V -0.3 to 4 V -65 to 150 °C  Main Link I/O, AUX_SNK, HPD_SNK, CAD_SNK ±2 kV All Other Terminals ±2 kV | HPD_SNK                                       |      |  |

|                         | All other terminals         | 3                                                                                                                                                                                        | -0.3 to 4                                     | V    |  |

| Storage temperature     | T <sub>S</sub>              |                                                                                                                                                                                          | -65 to 150                                    | °C   |  |

|                         | Human Body                  | Main Link I/O, AUX_SNK, HPD_SNK, CAD_SNK                                                                                                                                                 | ±2                                            | kV   |  |

| Electrostatic discharge | Model <sup>(2)</sup>        | All Other Terminals                                                                                                                                                                      | ±2                                            | kV   |  |

| alcorial go             | Charged-device n            | nodel <sup>(3)</sup>                                                                                                                                                                     | ±500                                          | V    |  |

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Tested in accordance with JEDEC Standard 22, Test Method A114-B

(3) Tested in accordance with JEDEC Standard 22, Test Method C101-A

#### THERMAL INFORMATION

|                  | TUEDMAL METDIO(1)                                          | SN75DP130     | LINUTO |

|------------------|------------------------------------------------------------|---------------|--------|

|                  | THERMAL METRIC <sup>(1)</sup>                              | QFN (48) PINS | UNITS  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance                     | 35.1          |        |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance                  | 21.5          |        |

| $\theta_{JB}$    | Junction-to-board thermal resistance                       | 11.7          | 00/11/ |

| Ψлт              | Junction-to-top characterization parameter, high-k board   | 1.2           | °C/W   |

| ΨЈВ              | Junction-to-board characterization parameter, high-k board | 11.9          |        |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance               | 6.7           |        |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Product Folder Links: SN75DP130

### SLLSE57D - APRIL 2011 - REVISED JULY 2013

### **POWER DISSIPATION**

|                                                                  | PARAMETER                                | TEST CONDITIONS <sup>(1)</sup> | MIN | TYP                                                                                                  | MAX                                                                       | UNIT |

|------------------------------------------------------------------|------------------------------------------|--------------------------------|-----|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|

|                                                                  |                                          | SN75DP130SS; 4 DP Lanes.       |     | 468                                                                                                  | 828                                                                       | mW   |

|                                                                  |                                          | SN75DP130DS; 4 DP Lanes.       |     | 174                                                                                                  | 304                                                                       | mW   |

| _                                                                | Device account and a second constitution | SN75DP130SS; 2 DP Lanes        |     | 252                                                                                                  | 450                                                                       | mW   |

| P <sub>SBY</sub>                                                 | Device power under normal operation      | SN75DP130DS; 2 DP Lanes.       |     | 102                                                                                                  | 178                                                                       | mW   |

|                                                                  |                                          | SN75DP130SS; 1 DP Lanes        |     | 144                                                                                                  | 252                                                                       | mW   |

|                                                                  |                                          | SN75DP130DS; 1 DP Lanes.       |     | 66                                                                                                   | 112                                                                       | mW   |

| _                                                                | Object designs and designs disciplined   | SN75DP130SS; 4 DP Lanes.       |     |                                                                                                      | 14.4                                                                      | mW   |

| $P_{SD}$                                                         | Shutdown mode power dissipation          | SN75DP130DS; 4 DP Lanes.       |     | 174 304<br>252 450<br>102 178<br>144 252<br>66 111<br>14.<br>7.:<br>14.<br>7.:<br>54<br>46<br>126 18 | 7.2                                                                       | mW   |

| _                                                                | Charadha ann de ann an dinain ation      | SN75DP130SS; 4 DP Lanes.       |     |                                                                                                      | 14.4                                                                      | mW   |

| PSBY                                                             | Standby mode power dissipation           | SN75DP130DS; 4 DP Lanes.       |     |                                                                                                      | 828<br>304<br>450<br>178<br>252<br>112<br>14.4<br>7.2                     | mW   |

| Ъ                                                                | D2 names damp made dissination           | SN75DP130SS; 4 DP Lanes.       |     |                                                                                                      | 450<br>178<br>252<br>112<br>14.4<br>7.2<br>14.4<br>7.2<br>54<br>46<br>180 | mW   |

| $P_{D3}$                                                         | D3 power down mode dissipation           | SN75DP130DS; 4 DP Lanes.       |     | 7                                                                                                    | 46                                                                        | mW   |

| _                                                                | Output disable (associate) made assument | SN75DP130SS; 4 DP Lanes.       |     | 126                                                                                                  | 180                                                                       | mW   |

| P <sub>SD</sub> P <sub>SBY</sub> P <sub>D3</sub> P <sub>OD</sub> | Output disable (squelch) mode current    | SN75DP130DS; 4 DP Lanes.       |     | 58                                                                                                   | 88                                                                        | mW   |

<sup>(1)</sup> Test conditions correspond to Power Supply test conditions in Electrical Characteristics

www.ti.com

# **RECOMMENDED OPERATING CONDITIONS**

|                          |                                                                               |                                                                  | MIN                | NOM  | MAX                                                                                                         | UNIT      |

|--------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------|------|-------------------------------------------------------------------------------------------------------------|-----------|

| V <sub>CC</sub>          | Supply voltage                                                                |                                                                  | 3                  | 3.3  | 3.6                                                                                                         | V         |

| $V_{DDD}$                | Digital core and Main Link supply vo                                          | oltage                                                           | 0.97               | 1.05 | 1.2                                                                                                         | V         |

| T <sub>A</sub>           | Operating free-air temperature                                                |                                                                  | 0                  |      | 85                                                                                                          | °C        |

| T <sub>CASE</sub>        | Case temperature                                                              |                                                                  |                    |      | 103.1                                                                                                       | °C        |

| V <sub>IH(HPD)</sub>     | High-level input voltage HPD_SNK                                              |                                                                  | 1.9                |      | 5.5                                                                                                         | V         |

|                          | High-level input voltage for device                                           |                                                                  | 1.9                |      | 3.6                                                                                                         |           |

| $V_{IH}$                 | control signals                                                               | RSTN pin (typical hysteresis of 80mV)                            |                    | 0.75 |                                                                                                             | V         |

|                          | Low-level input voltage for device                                            |                                                                  | 0                  |      | 0.8                                                                                                         | .,        |

| $V_{IL}$                 | control signals                                                               | RSTN pin (typical hysteresis of 80mV)                            |                    | 0.30 |                                                                                                             | V         |

| MAIN LINK                | TERMINALS                                                                     |                                                                  |                    |      |                                                                                                             |           |

| V <sub>ID</sub>          | Peak-to-peak input differential volta                                         | ge; RBR, HBR, HBR2                                               | 0.30               |      | 1.40                                                                                                        | Vpp       |

| $d_R$                    | Data rate                                                                     |                                                                  |                    |      | 5.4                                                                                                         | Gbps      |

| C <sub>AC</sub>          | AC coupling capacitance (each inpu                                            | ut and each output line)                                         | 75                 |      | 200                                                                                                         | nF        |

| R <sub>tdiff</sub>       | Differential output termination resist                                        | ance                                                             | 80                 | 100  | 120                                                                                                         | Ω         |

| V <sub>Oterm</sub>       | Output termination voltage (AC coup                                           | pled)                                                            | 0                  |      | 2                                                                                                           | V         |

|                          | Intra-pair skew at the input at                                               | When used as re-driver in DP source                              |                    |      | 20                                                                                                          |           |

| t <sub>SK(in HBR2)</sub> | 5.4Gbps                                                                       | When used as receiver equalizer in DP sink                       |                    |      | 100                                                                                                         | ps        |

| t <sub>SK(in HBR)</sub>  | Intra-pair skew at the input at 2.7Gb                                         | pps                                                              | 100                |      |                                                                                                             |           |

| t <sub>SK(in RBR)</sub>  | Intra-pair skew at the input at 1.62G                                         | Intra-pair skew at the input at 1.62Gbps                         |                    |      |                                                                                                             | ps        |

| AUX CHAN                 | NEL DATA TERMINALS                                                            |                                                                  |                    |      |                                                                                                             |           |

|                          |                                                                               | AUX_SRCp and AUX_SNKp in DP mode                                 | -0.5               | 0.3  | 0.4                                                                                                         |           |

| V <sub>I-DC</sub>        | DC input voltage                                                              | AUX_SRCn and AUX_SNKn in DP mode                                 | 2.0                | 3.0  | 3.6                                                                                                         | V         |

|                          |                                                                               | AUX_SRCp/n and AUX_SNKp/n in TMDS mode                           | -0.5               |      | 1.40<br>5.4<br>200<br>100<br>120<br>2<br>20<br>100<br>100<br>300<br>3.6<br>3.6<br>1.40<br>100<br>100<br>300 |           |

| V <sub>ID</sub>          | Differential input voltage amplitude                                          | (DP mode only)                                                   | 300                |      | 1400                                                                                                        | $mV_{PP}$ |

| d <sub>R(AUX)</sub>      | Data rate (before Manchester encode                                           | ding)                                                            | 0.8                | 1    | 1.2                                                                                                         | Mbps      |

| d <sub>R(FAUX)</sub>     | Data rate Fast AUX (300ppm freque                                             | ency tolerance)                                                  |                    | 720  |                                                                                                             | Mbps      |

| t <sub>jccin_adj</sub>   | Cycle-to-cycle AUX input jitter adjac                                         | cent cycle (DP mode only)                                        |                    |      | 0.05                                                                                                        | UI        |

| t <sub>jccin</sub>       | Cycle-to-cycle AUX input jitter within                                        | n one cycle (DP mode only)                                       |                    |      | 0.1                                                                                                         | UI        |

| C <sub>AC</sub>          | AUX AC coupling capacitance (DP                                               | mode only)                                                       | 75                 |      | 200                                                                                                         | nF        |

| V <sub>srcCMM</sub>      | AUX source common mode voltage CAD = V <sub>IL</sub> ; measured on AUX source | (only applies to DP mode)<br>ce and sink before AC coupling caps | 0                  |      | 2000                                                                                                        | mV        |

| DDC AND I                | <sup>2</sup> C TERMINALS                                                      |                                                                  |                    |      |                                                                                                             |           |

| $V_{I}$                  | Input voltage                                                                 |                                                                  | -0.5               |      | 3.6                                                                                                         | V         |

| d <sub>R</sub>           | Data rate                                                                     |                                                                  |                    |      | 100                                                                                                         | kbps      |

| $V_{IH}$                 | High-level input voltage                                                      |                                                                  | 0.7V <sub>CC</sub> |      |                                                                                                             | V         |

| V <sub>IL</sub>          | Low-level input voltage                                                       |                                                                  |                    |      | 0.3V <sub>CC</sub>                                                                                          | V         |

| f <sub>SCL</sub>         | SCL clock frequency standard I <sup>2</sup> C n                               | node                                                             |                    |      |                                                                                                             | kHz       |

| $t_{w(L)}$               | SCL clock low period standard I <sup>2</sup> C r                              | mode                                                             | 4.7                |      |                                                                                                             | μs        |

| t <sub>w(H)</sub>        | SCL clock high period standard I <sup>2</sup> C                               | mode                                                             | 4.0                |      |                                                                                                             | μs        |

| C <sub>bus</sub>         | Total capacitive load for each bus li                                         | ne                                                               |                    |      | 400                                                                                                         | pF        |

### POWER SUPPLY ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                        | PARAMETER <sup>(1)</sup>    | TEST CONDITIONS                                                                                                                                                               | MIN | TYP | MAX | UNIT |

|------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>CCDP1HBR2</sub> | Supply Current 1 DP Lanes   | Maximum conditions: IN/OUT at 5.4Gbps                                                                                                                                         |     | 40  | 70  | mA   |

| I <sub>CCDP2HBR2</sub> | Supply Current 2 DP Lanes   | PRBS, $V_{OD} = 510 \text{mVpp}$ , $P_E = 6 \text{dB}$ ; AUX at 1Mbps                                                                                                         |     | 70  | 125 | mA   |

| I <sub>CCDP4HBR2</sub> | Supply Current 4 DP Lanes   | PRBS, V <sub>ID</sub> = 1000mVpp; EQ = 3dB Typical Conditions: IN/OUT at 5.4Gbps PRBS,V <sub>OD</sub> = 510mVpp, P <sub>E</sub> = 0dB AUX and I <sup>2</sup> C Idle; EQ = 3dB |     | 130 | 230 | mA   |

| I <sub>CCDP1HBR</sub>  | Supply Current 1 DP Lanes   | M: I: I to TOL DDDO V 540 V                                                                                                                                                   |     | 40  |     | mA   |

| I <sub>CCDP2HBR</sub>  | Supply Current 2 DP Lanes   | Main Link at 2.7Gbps PRBS, V <sub>OD</sub> =510mVpp,  P <sub>E</sub> = 0dB; AUX and I <sup>2</sup> C Idle; EQ at 3dB fixed gain                                               |     | 70  |     | mA   |

| I <sub>CCDP4HBR</sub>  | Supply Current 4 DP Lanes   | TE = Odb, AOX and TO Idic, EQ at Sub lixed gain                                                                                                                               |     | 130 |     | mA   |

| I <sub>CCTMDS</sub>    | Supply Current TMDS<br>Mode | Main Link at 2.5Gbps PRBS, $V_{ID} = V_{OD} = 600 \text{mVpp}$ ; AUX Idle                                                                                                     |     |     | 170 | mA   |

| I <sub>SD</sub>        | Shutdown supply current     | Shutdown mode                                                                                                                                                                 |     | 3   | 4   | mA   |

| I <sub>SBY</sub>       | Standby supply current      | Standby mode                                                                                                                                                                  |     | 3   | 4   | mA   |

| I <sub>D3</sub>        | D3 supply current           | D3 power down mode                                                                                                                                                            |     | 10  | 15  | mA   |

| I <sub>OD</sub>        | Squelch supply current      | Output disable (Squelch) mode                                                                                                                                                 |     | 35  | 50  | mA   |

<sup>(1)</sup> Values are  $V_{DDD}$  supply measurements;  $V_{CC}$  supply (DS package option) measurements are 5mA (typical) and 8mA (max), with zero current in shutdown and standby modes.

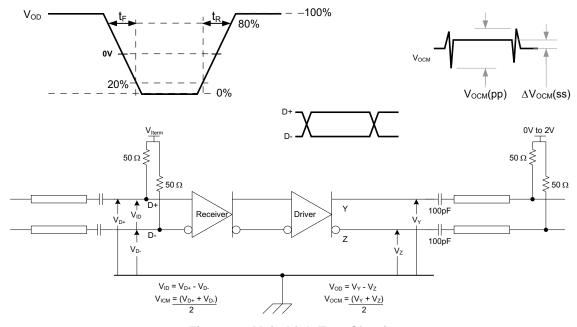

### MAIN LINK ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                         | PARAMETER                                   | TEST CONDITIONS                                                             | MIN | TYP  | MAX  | UNIT      |

|-------------------------|---------------------------------------------|-----------------------------------------------------------------------------|-----|------|------|-----------|

| V <sub>OD(L0)</sub>     |                                             |                                                                             | 238 | 340  | 442  | $mV_{PP}$ |

| V <sub>OD(L1)</sub>     | Output differential voltage swing           | V . 675Mbps D40 2 Test Dettern, BOOST 04                                    | 357 | 510  | 663  | $mV_{PP}$ |

| V <sub>OD(L2)</sub>     | Output differential voltage swing           | V <sub>PRE(L0)</sub> ; 675Mbps D10.2 Test Pattern; BOOST=01                 | 484 | 690  | 897  | $mV_{PP}$ |

| V <sub>OD(L3)</sub>     |                                             |                                                                             | 700 | 1000 | 1300 | $mV_{PP}$ |

| V <sub>OD(TMDS)</sub>   |                                             | 675Mbps D10.2 Test Pattern; BOOST=01                                        | 420 | 600  | 780  | $mV_{PP}$ |

| $\Delta V_{OD(L0L1)}$   |                                             | $\Delta V_{ODn} = 20 \times \log(V_{ODL(n+1)} / V_{ODL(n)})$ measured in    | 1.7 | 3.5  | 5.3  | dB        |

| $\Delta V_{OD(L1L2)}$   | voltage delta                               | compliance with PHY CTS1.1D15 section 3.2 at                                | 1.6 | 2.5  | 3.5  | dB        |

| $\Delta V_{OD(L2L3)}$   | - Voltago della                             | test point TP2 using special CTS test board                                 | 8.0 | 3.5  | 6.0  | dB        |

| V <sub>PRE(L0)</sub>    |                                             | All V <sub>OD</sub> options                                                 |     | 0    | 0.25 | dB        |

| V <sub>PRE(L1)</sub>    | (default)                                   | $V_{OD} = V_{OD(L0)}, V_{OD(L1)}, \text{ or } V_{OD(L2)}; \text{ BOOST=01}$ |     | 3.5  |      | dB        |

| V <sub>PRE(L2)</sub>    |                                             | $V_{OD} = V_{OD(L0)}$ or $V_{OD(L1)}$ ; BOOST=01                            |     | 6.0  |      | dB        |

| V <sub>PRE(L3)</sub>    |                                             | V <sub>OD</sub> = V <sub>OD(L0)</sub> ; BOOST=01                            |     | 9.5  |      | dB        |

| V                       | Output Vppc boost                           | BOOST=10                                                                    |     | 10%  |      | dB        |

| V <sub>PRE(BOOST)</sub> |                                             | BOOST=00                                                                    |     | -10% |      | dB        |

| ΔV <sub>PRE(L1L0)</sub> |                                             | Measured in compliance with PHY CTS1.1D15                                   | 2.0 |      |      | dB        |

| $\Delta V_{PRE(L2L1)}$  | Pre-emphasis delta                          | section 3.3 at test point TP2 using special CTS test                        | 1.6 |      |      | dB        |

| $\Delta V_{PRE(L3L2)}$  |                                             | board                                                                       | 1.6 |      |      | dB        |

| $\Delta V_{ConsBit}$    | Non-transition bit voltage variation        | See CTS spec section 3.3.5                                                  |     |      | 30%  |           |

| A <sub>EQ(HBR)</sub>    | Equalizer gain for RBR/HBR                  | See Table 5 and for EQ setting details:                                     |     |      | 9    | dB        |

| A <sub>EQ(HBR2)</sub>   | Equalizer gain for HBR2                     | Max value represents the typical value for the                              |     |      | 18   | dB        |

| A <sub>EQ(TMDS)</sub>   | Equalizer gain for TMDS                     | maximum configurable EQ setting                                             |     |      | 3    | dB        |

| R <sub>OUT</sub>        | Driver output impedance                     |                                                                             |     | 50   |      | Ω         |

| R <sub>IN</sub>         | Input termination impedance                 |                                                                             | 40  | 50   | 60   | Ω         |

| V <sub>Iterm</sub>      | Input termination voltage                   | AC coupled; self-biased                                                     | 0   |      | 2    | V         |

| V <sub>OCM(SS)</sub>    | Steady state output common-<br>mode voltage |                                                                             | 0   |      | 2    | V         |

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

# MAIN LINK ELECTRICAL CHARACTERISTICS (continued)

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                              | TEST CONDITIONS                                             | MIN | TYP | MAX | UNIT           |

|----------------------|------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|----------------|

| $\Delta V_{OCM(SS)}$ | Change in steady state output common-mode voltage between logic levels | Tested in compliance to section 3.10 in CTS 1.1a            |     | 10  |     | $mV_PP$        |

| V                    | Outst                                                                  | LIDDO                                                       |     | 20  |     | $mV_{RMS}$     |

| V <sub>OCM(PP)</sub> | Output common-mode noise                                               | HBR2                                                        |     | 30  |     | $\rm mV_{RMS}$ |

| V <sub>SQUELCH</sub> | Squelch threshold voltage                                              | Programable via I <sup>2</sup> C; default at 80mVpp typical |     | 80  |     | $mV_{PP}$      |

| I <sub>TXSHORT</sub> | Short circuit current limit                                            | Main Link outputs shorted to GND                            |     |     | 50  | mA             |

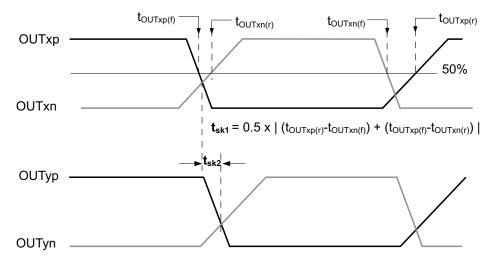

### MAIN LINK SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                          | TEST CONDITIONS                                                                                                                                           | MIN | TYP | MAX | UNIT |

|-----------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>PD</sub>       | Propagation delay time             | See Figure 8                                                                                                                                              |     | 300 |     | ps   |

| t <sub>SK(1)</sub>    | Intra-pair output skew             | Signal input skew = 0ps; d <sub>R</sub> = 2.7Gbps, V <sub>PRE</sub> = 0dB,                                                                                |     |     | 20  | ps   |

| t <sub>SK(2)</sub>    | Inter-pair output skew             | 800mVp-p, D10.2 clock pattern at device input; See Figure 9                                                                                               |     |     | 100 | ps   |

| Δt <sub>jit</sub>     | Total peak-to-peak residual jitter | V <sub>OD(L0)</sub> ; V <sub>PRE(L0)</sub> ; EQ = 8dB; clean source; minimum input and output cabling; 1.62Gbps, 2.7Gbps, and 5.4Gbps PRBS7 data pattern. |     |     | 15  | ps   |

| t <sub>sq_enter</sub> | Squelch entry time                 | Time from active DP signal turned off to ML output off with noise floor minimized                                                                         | 10  |     | 120 | μs   |

| t <sub>sq_exit</sub>  | Squelch exit time                  | Time from DP signal on to ML output on                                                                                                                    | 0   |     | 1   | μs   |

Figure 8. Main Link Test Circuit

Figure 9. Main Link Skew Measurements

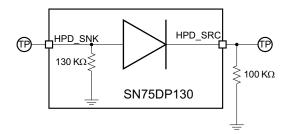

#### HPD/CAD ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                   | TEST CONDITIONS                                                         | MIN | TYP | MAX | UNIT |

|---------------------|---------------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| HPD_SR              | C, CAD_SRC                                  |                                                                         |     |     |     |      |

| V <sub>OH</sub>     | High-level output voltage                   | I <sub>OH</sub> = 500μA                                                 | 2.7 |     | 3.6 | V    |

| V <sub>OL</sub>     | Low-level output voltage                    | I <sub>OH</sub> = 500μA                                                 | 0   |     | 0.1 | V    |

| R <sub>outCAD</sub> | CAD series output resistance <sup>(1)</sup> | EN=RSTN=V <sub>CC</sub> ; HPD_SNK=CAD_SNK=V <sub>CC</sub>               |     | 150 |     | Ω    |

| R <sub>outHPD</sub> | HPD series output resistance                | EN=RSTN=V <sub>CC</sub> ; HPD_SNK=CAD_SNK=V <sub>CC</sub>               |     | 150 |     | Ω    |

|                     |                                             | V <sub>CC</sub> = 0V, V(pin) = 1.2V; RSTN                               |     |     | 20  |      |

| I <sub>LEAK</sub>   | Leakage current <sup>(2)</sup>              | $V_{CC}$ = 0V, V(pin) = 3.3V; SCL/SDA_CTL, AUX_SNKp/n                   |     |     | 20  | μA   |

|                     | -                                           | V <sub>CC</sub> = 0V, V(pin) = 3.3V; HPD_SNK                            | 40  |     |     |      |

|                     |                                             | $V_{CC}$ = 0V, $V(pin)$ = 3.3V; $AUX_SRCp/n$                            |     |     | 60  |      |

| HPD_SNI             | Κ                                           |                                                                         |     |     |     |      |

| I <sub>H</sub>      | High-level input current                    | $V_{IH}$ = 1.9V (leakage includes the 130k $\Omega$ pull-down resistor) | -30 |     | 30  | μΑ   |

| IL                  | Low-level input current                     | $V_{IL}$ = 0.8V (leakage includes the 130k $\Omega$ pull-down resistor) | -30 |     | 30  | μΑ   |

| V <sub>TH+</sub>    | Positive going input threshold voltage      |                                                                         |     | 1.4 |     | V    |

| R <sub>pdHPD</sub>  | HPD input termination to GND                | V <sub>CC</sub> =0V                                                     | 100 | 130 | 160 | kΩ   |

| CAD_SNI             | K                                           |                                                                         |     |     |     |      |

| I <sub>H</sub>      | High-level input current                    | V <sub>IH</sub> = 1.9V                                                  | -1  |     | 1   | μΑ   |

| IL                  | Low-level input current                     | V <sub>IL</sub> = 0.8V                                                  | -1  |     | 1   | μΑ   |

| V <sub>TH+</sub>    | Positive going input threshold voltage      |                                                                         |     | 1.4 |     | V    |

- A series output resistance of  $100k\Omega$  may be added in series to the CAD\_SRC output to mimic a cable adapter. Applies to failsafe inputs: RSTN, SDA\_CTL, SCL\_CTL, SDA\_DDC, SCL\_DDC, AUX\_SNK P/N, AUX\_SRC P/N, HPD\_SNK

#### HPD/CAD SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                      | 5                                    | ,                                     |     |     |     |      |

|----------------------|--------------------------------------|---------------------------------------|-----|-----|-----|------|

|                      | PARAMETER                            | TEST CONDITIONS                       | MIN | TYP | MAX | UNIT |

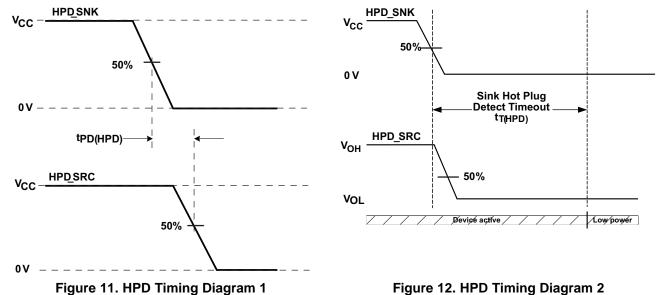

| t <sub>PD(HPD)</sub> | Propagation delay HPD_SNK to HPD_SRC | V 2.0V/. Can Figure 44                |     |     | 50  | ns   |

| t <sub>PD(CAD)</sub> | Propagation delay CAD_SNK to CAD_SRC | V <sub>CC</sub> = 3.0V; See Figure 11 |     |     | 50  | ns   |

| t <sub>T(HPD)</sub>  | HPD logic shut off time              | V <sub>CC</sub> = 3.0V; See Figure 12 |     |     | 400 | ms   |

Figure 10. HPD Test Circuit

Figure 12. HPD Timing Diagram 2

### AUX/DDC/I<sup>2</sup>C ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                             | TEST CONDITIONS                                                                                                                                                        |     | TYP | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>PASS</sub>    | DDC mode passthrough voltage                                          | $V_{CAD\_SNK} = V_{IH}$ ; $I_O = 100 \mu A$                                                                                                                            | 1.9 |     |     | V    |

| C <sub>IO</sub>      | I/O capacitance                                                       | V <sub>IO</sub> = 0 V; f(test) = 1 MHz                                                                                                                                 |     | 10  |     | pF   |

|                      | On resistance AUX_SRCn to AUX_SNKn in DP mode                         | $V_{CC} = 3.0 \text{ V W/ V}_1 = 2.85 \text{V or} $<br>$V_{CC} = 3.6 \text{ V W/ V}_1 = 3.4 \text{ V; I}_0 = 5 \text{ mA}$                                             |     | 5   | 10  | Ω    |

| r <sub>ON</sub>      | On resistance SCL/SDA_DDC to AUX_SNK in TMDS mode                     | I <sub>O</sub> = 3 mA                                                                                                                                                  |     | 15  | 30  | Ω    |

|                      | On resistance AUX_SRC to AUX_SNK in TMDS mode                         | I <sub>O</sub> = 3 mA                                                                                                                                                  |     | 10  | 20  | Ω    |

| Δr <sub>ON</sub>     | On resistance variation with input signal voltage change in DP mode   | $V_{CC} = 3.6 \text{ V, } I_O = 5 \text{ mA, } V_I = 2.6 \text{ to } 3.4 \text{ V,} \ V_{CC} = 3.0 \text{ V, } I_O = 5 \text{ mA, } V_I = 0 \text{ to } 0.4 \text{ V}$ |     |     | 5   | Ω    |

| V <sub>ID(HYS)</sub> | Differential input hysterisis                                         | By design (simulation only)                                                                                                                                            |     | 50  |     | mV   |

| I <sub>H</sub>       | High-level input current                                              | $V_{I} = V_{CC}$                                                                                                                                                       | -5  |     | 5   | μΑ   |

|                      | Low level input current                                               | V <sub>I</sub> = GND; CAD_SNK = V <sub>IH</sub>                                                                                                                        | -5  |     | 5   |      |

| IL                   | Low-level input current                                               | V <sub>I</sub> = GND; At DDC inputs                                                                                                                                    |     |     | 80  | μA   |

| V <sub>AUX+</sub>    | Voltage on the Aux+ for PHY-CTS 3.19                                  | 1M (5%) pullup to V <sub>CC</sub> and 100k $\Omega$ pulldown to GND on AUX+; V <sub>CC</sub> = 3.3 V                                                                   | 0   |     | 0.4 | V    |

| V <sub>AUX</sub> -   | Voltage on the Aux- for PHY-CTS 3.18                                  | 100kΩ pullup to $V_{CC}$ and 1M (5%) pulldown to GND on AUX-; $V_{CC}$ = 3.3 V                                                                                         | 2.4 |     | 3.6 | V    |

| S <sub>1122</sub>    | Differential line insertion loss                                      | $V_{ID}$ = 400 mV, AC coupled; p-channel biasing 0.3 V and n-channel 3.0V; 360 MHz sine wave; CAD_SNK=V $_{IL}$                                                        |     | 1.6 | 3   | dB   |

| R <sub>DDC</sub>     | Switcheable pul-lup resistor on DDC at source side (SCL_DDC, SDA_DDC) | CAD_SNK = V <sub>IH</sub>                                                                                                                                              | 48  | 60  | 72  | kΩ   |

Copyright © 2011–2013, Texas Instruments Incorporated

#### **AUX/DDC/I<sup>2</sup>C SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                           | TEST CONDITIONS                                                                                | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------|------------------------------------------------------------------------------------------------|-----|-----|-----|------|

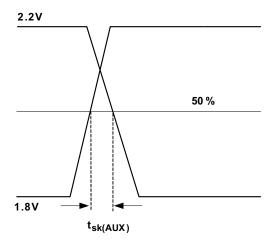

| t <sub>sk(AUX)</sub>  | Intra-pair skew                     | V <sub>ID</sub> = 400 mV, AC coupled; p-channel biasing 0.3V and n-channel 3.0V; See Figure 13 |     |     | 400 | ps   |

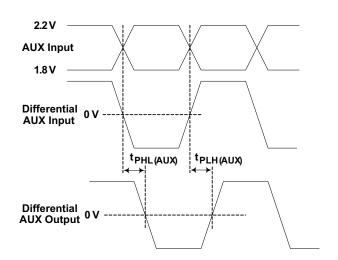

| t <sub>PLH(DP)</sub>  | Propagation delay time, low to high | CAR IV AMbro rottom Coo Figure 44                                                              |     |     | 3   | ns   |

| t <sub>PHL(DP)</sub>  | Propagation delay time, high to low | CAD = V <sub>IL</sub> ; 1Mbps pattern;See Figure 14                                            |     |     | 3   | ns   |

| t <sub>PLH(DDC)</sub> | Propagation delay time, low to high | CAD = V <sub>IH</sub> ; 100kbps pattern                                                        |     |     | 50  | ns   |

| t <sub>PHL(DDC)</sub> | Propagation delay time, high to low |                                                                                                |     |     | 50  | ns   |

| t <sub>PU(AUX)</sub>  | Main Link D3 wakeup time            | V <sub>ID</sub> = 0.1 V, V <sub>ICMM</sub> = 2 V source side (before AC coupling caps)         |     |     | 50  | μs   |

| I <sup>2</sup> C      |                                     | -                                                                                              |     |     |     |      |

Refer to the  $I^2$ C-Bus Specification, Version 2.1 (January 2000); SN75DP130 meets the switching characteristics for standard mode transfers up to 100 kbps.

Figure 13. AUX Skew Measurement

Figure 14. AUX Delay Measurement

#### **TYPICAL CHARACTERISTICS**

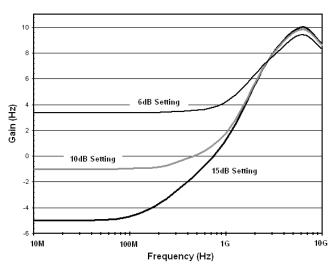

A. Gain represents SN75DP130 design simulation

Figure 15. Typical EQ Gain Curves

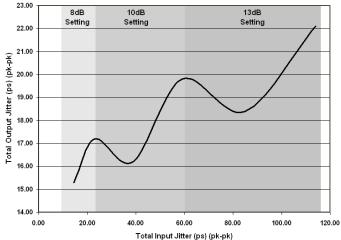

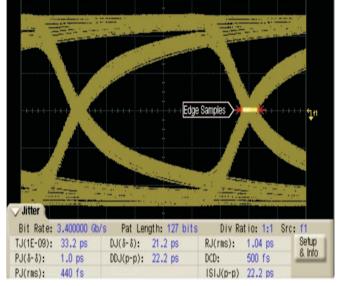

A. DisplayPort output jitter measured at the surface mount pins connected to the main link output channels on the SN75DP130 characterization test board; input jitter generated from test board with variable input trace lengths using 4 mil traces of lengths 2 inches to 22 inches generating the typical input jitter as represented in Table 1.

Figure 16. DisplayPort Sink Jitter Performance with Optimal EQ Settings

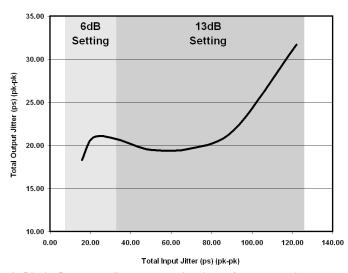

Table 1. Characterization Test Board Trace Lengths Related to Input Jitter

| INPUT MODE         | TRACE LENGTH (inches) | TOTAL INPUT JITTER (ps) | RECOMMENDED EQ SETTING |

|--------------------|-----------------------|-------------------------|------------------------|

|                    | 2                     | 14.4                    | 8                      |

|                    | 6                     | 23.1                    | 8                      |

| Dianley Dort LIDDS | 10                    | 38.8                    | 10                     |

| Display Port HBR2  | 14                    | 58.9                    | 10                     |

|                    | 18                    | 84.8                    | 13                     |

|                    | 22                    | 113.9                   | 13                     |

|                    | 2                     | 15.8                    | 6                      |

|                    | 6                     | 21.3                    | 6                      |

| TMDC 2.4 Char      | 10                    | 33.2                    | 6                      |

| TMDS 3.4 Gbps      | 14                    | 49.9                    | 13                     |

|                    | 18                    | 70.5                    | 13                     |

|                    | 22                    | 91.5                    | 13                     |

Copyright © 2011–2013, Texas Instruments Incorporated Submit Documentation Feedback

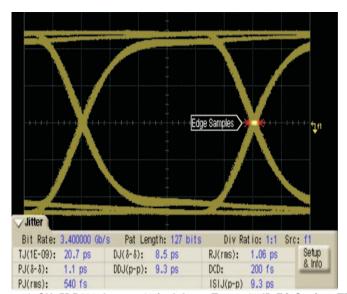

A. DisplayPort output jitter measured at the surface mount pins connected to the main link output channels on the SN75DP130 characterization test board; input jitter generated from test board with variable input trace lengths using 4 mil traces of lengths 2 inches to 22 inches generating the typical input jitter as represented in Table 1.

Figure 17. TMDS Sink jitter Performance with Optimal EQ Settings

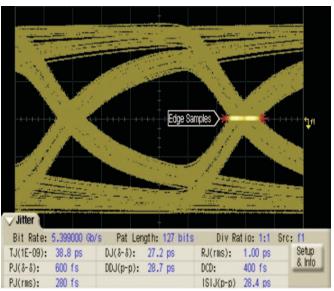

Figure 18. Main Link Input with 10 inch Trace; DisplayPort Sink

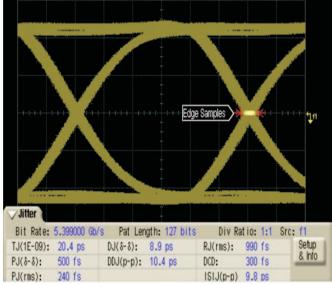

Figure 19. SN75DP130 Output; 10 inch Input Trace; 13dB EQ Setting; DP Sink

Figure 20. Main Link Input with 10 inch Trace; TMDS Sink

Figure 21. SN75DP130 Output; 10 inch Input Trace; 13dB EQ Setting; TMDS Sink

#### **APPLICATION INFORMATION**

#### ADDITIONAL TYPICAL IMPLEMENTATIONS

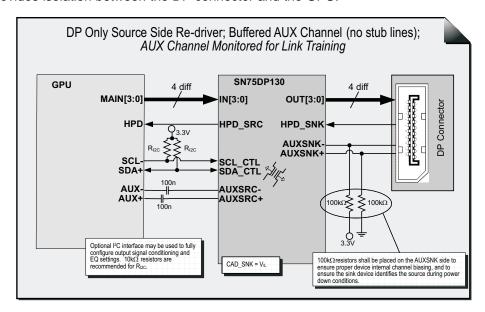

The configuration shown in Figure 22 is preferred to avoid very long AUX signal stub lines. Furthermore, this configuration provides isolation between the DP connector and the GPU.

Figure 22. DP Only Configuration with AUX Pass Through

The configuration shown in Figure 23 enables the SN75DP130 in DP++ Dual-Mode with the AUX input only monitoring the AUX channel. Use this setting when AUX stub lines can be kept short and minimum AUX attenuation is desired. For DP v1.1a, the stub length shall not exceed 4cm each, and for DP v1.2 with FAUX support each stub line shall be shorter than 1cm.

Figure 23. DP++ Dual-Mode Configuration with AUX Monitor

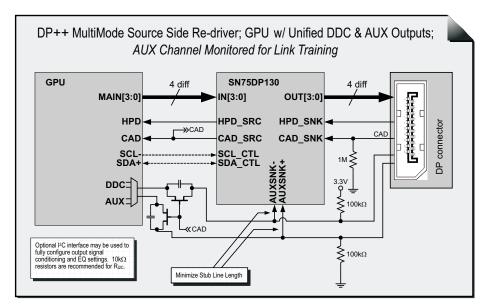

The alternate configuration shown in Figure 24 allows a reduced BOM by eliminating the need for external FET switches while routing AUX and DDC externally, which eliminates any insertion loss cases of AUX is brought through the SN75DP130. For DP v1.2 with FAUX support each stub line shall be shorter than 1cm.

Figure 24. Alternate Low-BOM DP++ Dual-Mode Configuration

#### **OPERATING MODES OVERVIEW**

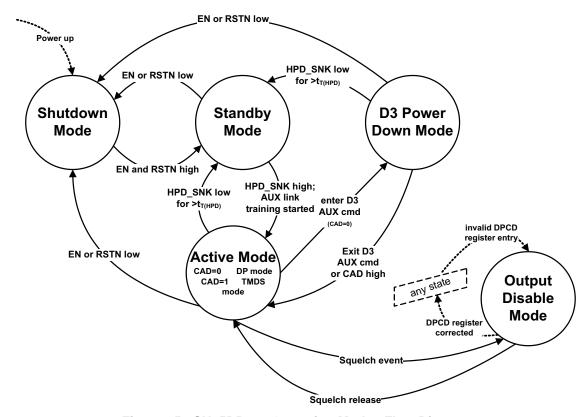

Figure 25. SN75DP130 Operating Modes Flow Diagram

### Table 2. Description of SN75DP130 Operating Modes

| MODE                    | CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CONDITIONS                                                                                                                                |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Shutdown Mode           | Least amount of power consumption (most circuitry turned off); HPD_SRC reflects HPD_SNK state; all other outputs are high-impedance; if RSTN is high local I <sup>2</sup> C IF remains active; if RSTN is low local I <sup>2</sup> C interface is turned off, all other inputs are ignored, and AUX DPCD is reset. (EN=low does not reset DPCD)                                                                                                                                                                                         | EN or RSTN is low;<br>Power on default mode                                                                                               |

| Standby Mode            | Low power consumption (I <sup>2</sup> C IF is active; AUX monitor is inactive); Main Link outputs are disabled;                                                                                                                                                                                                                                                                                                                                                                                                                         | EN and RSTN are high;<br>HPD_SNK low longer than t <sub>T(HPD)</sub>                                                                      |

| D3 Power Down<br>Mode   | Low power consumption (I <sup>2</sup> C IF is active; AUX monitor active in DP mode); Main Link outputs are disabled;                                                                                                                                                                                                                                                                                                                                                                                                                   | EN and RSTN are high;<br>AUX cmd requested DP sink to<br>enter D3 power saving mode                                                       |

|                         | Data transfer (normal operation); The device is either in TMDS mode (CAD_SNK=high) or DP mode (CAD_SNK=low);                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                           |