SLIS128A-NOVEMBER 2011-REVISED JANUARY 2013

# LIN PHYSICAL INTERFACE

Check for Samples: SN65HVDA100-Q1

## FEATURES

- Qualified for Automotive Applications

- Local Interconnect Network (LIN) Physical Layer Specification Revision 2.1 Compliant and Conforms to SAEJ2602 Recommended Practice for LIN

- Extended Operation With Supply From 5 V to 27 V DC (LIN Specification 7 V to 18 V)

- LIN Transmit Speed up to 20-kbps LIN Specified Maximum, High Speed Receive Capable

- Sleep Mode: Ultra-low Current Consumption Allows Wake-Up Events From: LIN Bus, Wake-Up Input (External Switch) or Host MCU

- Wake-Up Request on RXD Pin

- Wake-Up Source Recognition on TXD Pin

- Interfaces to MCU With 5-V or 3.3-V I/O Pins

- High Electromagnetic Compatibility (EMC)

- Control of External Voltage Regulator (INH Pin)

- Supports ISO9141 (K-Line) Like Functions

- Protection

- ESD Protection to ±12 kV (Human-Body Model) on LIN Pin

- LIN Pin Handles Voltage From –27 V to 45 V (Short to Battery or Ground)

- Survives Transient Damage in Automotive Environment (ISO 7637)

- Undervoltage protection on V<sub>SUP</sub>

- TXD Dominant State Timeout Protection

- Prevention of False Wake Ups with Bus Stuck Dominant Fault

- Thermal Shut Down

- Unpowered Node or Ground Disconnection Failsafe at System Level, Node Does Not Disturb Bus (No load on bus)

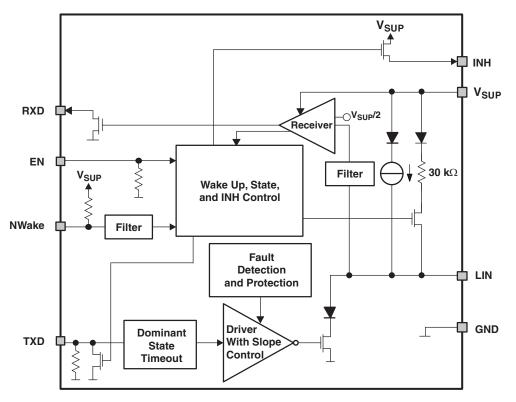

## FUNCTIONAL BLOCK DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

$\overline{M}$

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# DESCRIPTION

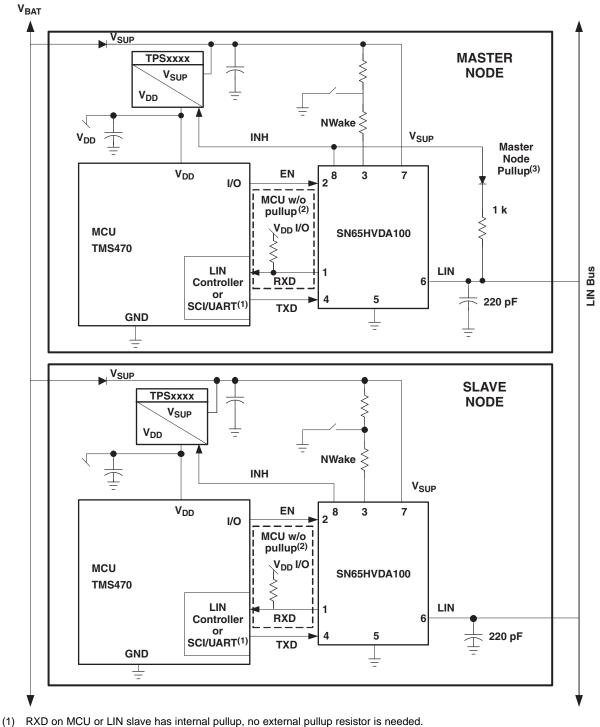

The SN65HVDA100 is the Local Interconnect Network (LIN) physical interface, which integrates the serial transceiver with wake-up and protection features. The LIN bus is a single-wire bidirectional bus typically used for low-speed in-vehicle networks using data rates between 2.4 kbps and 20 kbps. The LIN protocol output data stream on TXD is converted by the SN65HVDA100 into the LIN bus signal through a current-limited wave-shaping driver as outlined by the LIN Physical Layer Specification. The receiver converts the data stream from the LIN bus and outputs the data stream via RXD. The LIN bus has two states: dominant state (voltage near ground) and recessive state (voltage near battery). In the recessive state, the LIN bus is pulled high by the internal pullup resistor (30 k $\Omega$ ) and series diode, so no external pullup components are required for slave applications. Master applications require an external pullup resistor (1 k $\Omega$ ) plus a series diode per the LIN specification.

In sleep mode, low quiescent current is needed even though the wake-up circuits remain active and allow for remote wake up via the LIN bus or local wake up via the NWake or EN pins.

The SN65HVDA100 has been designed for operation in the harsh automotive environment. The device also prevents back-feed current through LIN to the supply input in case of a ground shift or supply voltage disconnection. It also features undervoltage, overtemperature, and loss-of-ground protection. In the event of a fault condition, the transmitter is immediately switched off and remains off until the fault condition is removed.

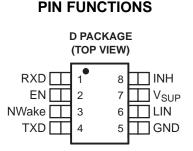

#### **PIN ASSIGNMENTS**

| PIN              |     | TYPE   | DECODIDITION                                                                                |  |  |  |

|------------------|-----|--------|---------------------------------------------------------------------------------------------|--|--|--|

| NAME             | NO. | TYPE   | DESCRIPTION                                                                                 |  |  |  |

| RXD              | 1   | 0      | RXD output (open drain) interface reporting state of LIN bus voltage                        |  |  |  |

| EN               | 2   | I      | Enable input                                                                                |  |  |  |

| NWake            | 3   | I      | High voltage input for device wake up                                                       |  |  |  |

| TXD              | 4   | I      | TXD input interface to control state of LIN output                                          |  |  |  |

| GND              | 5   | GND    | Ground                                                                                      |  |  |  |

| LIN              | 6   | I/O    | LIN bus single-wire transmitter and receiver                                                |  |  |  |

| V <sub>SUP</sub> | 7   | Supply | Device supply voltage (connected to battery in series with external reverse blocking diode) |  |  |  |

| INH              | 8   | 0      | Inhibit controls external voltage regulator with inhibit input                              |  |  |  |

#### ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACK     | AGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|----------|--------------------|-----------------------|------------------|

| -40°C to 125°C | SOIC – D | Reel of 2500       | SN65HVDA100QDRQ1      | A100Q            |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

#### LIN (Local Interconnect Network) Bus

This I/O pin is the single-wire LIN bus transmitter and receiver. The LIN pin can survive excessive dc and transient voltages. There are no reverse currents from the LIN to supply ( $V_{SUP}$ ), even in the event of a ground shift or loss of supply ( $V_{SUP}$ ).

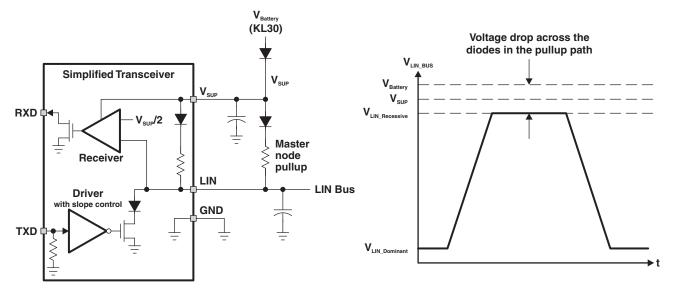

#### LIN Transmitter Characteristics

The transmitter has thresholds and ac parameters according to the LIN specification. It is a low-side transistor with internal current limitation and thermal shutdown. During a thermal shutdown condition, the transmitter is disabled to protect the device. There is an internal pullup resistor with a serial diode structure to  $V_{SUP}$ , so no external pullup components are required for LIN slave mode applications. An external pullup resistor and a series diode to  $V_{SUP}$  must be added when the device is used for master node applications.

#### LIN Receiver Characteristics

The receiver's characteristic thresholds are ratio-metric with the device supply pin according to the LIN specification.

The receiver is capable of receiving higher data rates (>100 kbps) than supported by LIN or SAEJ2602 specifications. This allows the SN65HVDA100 to be used for high-speed downloads at end-of-line production or other applications. The actual data rates achievable depend on system time constants (bus capacitance and pullup resistance) and driver characteristics used in the system.

#### Termination

There is an internal pullup resistor with a serial diode structure from LIN to  $V_{SUP}$ , so no external pullup components are required for LIN slave mode applications. An external pullup resistor (1k $\Omega$ ) and a series diode to  $V_{SUP}$  must be added when the device is used for master node applications per the LIN specification.

V<sub>Battery</sub> = Vehicle battery supply

V<sub>SUP</sub> = Electronic module supply (reverse battery diode blocked V<sub>Battery</sub>)

Figure 1. Definition of Voltage Levels

www.ti.com

## TXD (Transmit Input / Output)

TXD is the interface to the MCU's LIN protocol controller or SCI/UART that is used to control the state of the LIN output. When TXD is low, the LIN output is dominant (near ground). When TXD is high, the LIN output is recessive (near battery). The TXD input structure is compatible with microcontrollers with 3.3-V and 5-V I/O. TXD has an internal pulldown resistor. The LIN bus is protected from being stuck dominant via a system failure driving TXD low via the dominant state timeout timer. The TXD pin is pulled down strongly in standby mode after a wake-up event on the NWake pin.

## **RXD (Receive Output)**

RXD is the interface to the MCU's LIN protocol controller or SCI/UART, which reports the state of the LIN bus voltage. LIN recessive (near battery) is represented by a high level on RXD and LIN dominant (near ground) is represented by a low level on RXD. The RXD output structure is an open-drain output stage. This allows the device to be used with 3.3-V and 5-V I/O microcontrollers. If the microcontroller's RXD pin does not have an integrated pullup, an external pullup resistor to the microcontroller I/O supply voltage is required. In standby mode the RXD pin is driven low to indicate a wake up request from LIN or NWake.

### V<sub>SUP</sub> (Supply Voltage)

$V_{SUP}$  is the power supply pin.  $V_{SUP}$  is connected to the battery through an external reverse battery blocking diode. If there is a loss of power at the ECU level, the device has extremely low leakage from the LIN pin, which does not load the bus down. This is optimal for LIN systems in which some of the nodes are unpowered (ignition supplied) while the rest of the network remains powered (battery supplied).

### GND (Ground)

GND is the device ground connection. The device can operate with a ground shift as long as the ground shift does not reduce  $V_{SUP}$  below the minimum operating voltage. If there is a loss of ground at the ECU level, the device has extremely low leakage from the LIN pin, which does not load the bus down. This is optimal for LIN systems in which some of the nodes are unpowered (ignition supplied) while the rest of the network remains powered (battery supplied).

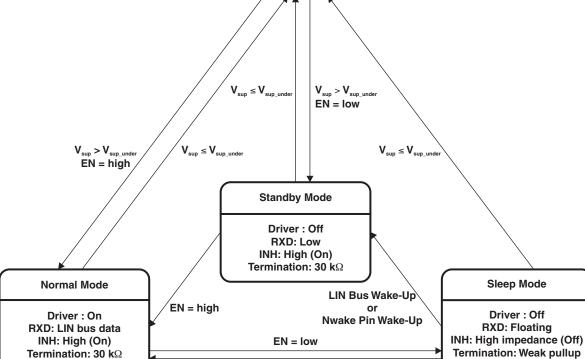

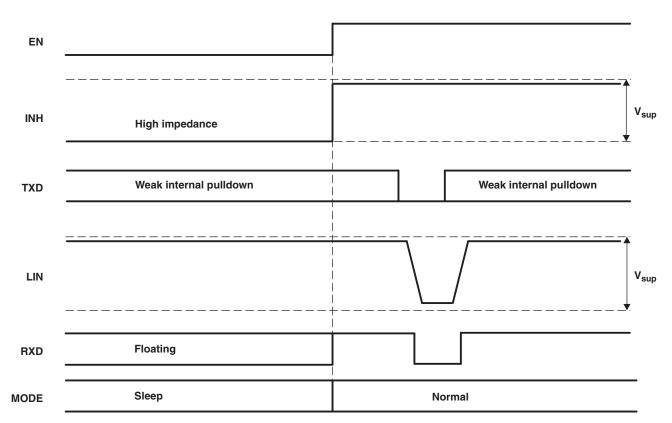

## EN (Enable Input)

EN controls the operational modes of the device. When EN is high, the device is in normal mode, allowing a transmission path from TXD to LIN and from LIN to RXD. When EN is low, the device is put into sleep mode and there are no transmission paths available. The device can enter normal mode only after wake up. EN has an internal pulldown resistor to ensure the device remains in low-power mode even if EN floats.

#### NWake (High Voltage Wake Up Input)

NWake is a high-voltage input used to wake up from sleep mode. NWake is usually connected to an external switch in the application. A low on NWake that is asserted longer than the filter time ( $t_{NWAKE}$ ) results in a local wake-up. NWake provides an internal pullup source to  $V_{SUP}$ .

## INH (Inhibit Output)

INH is used to control an external voltage regulator that has an inhibit or enable input. When the device is in normal operating mode, the inhibit switch is enabled and the external voltage regulator is activated. When device is in sleep mode, the inhibit switch is disabled, which turns off the system voltage regulator. A wake-up event transitions the device to standby by mode and re-enables INH which, in turn, restarts the system by turning on the voltage regulators. INH can also drive an external transistor connected to an MCU interrupt input.

## EN = high

Figure 2. Operating States Diagram

| Table | 1. | Operating | Modes |

|-------|----|-----------|-------|

|-------|----|-----------|-------|

| MODE    | EN   | RXD          | LIN BUS<br>TERMINATION | INH            | TRANSMITTER | COMMENTS                                         |

|---------|------|--------------|------------------------|----------------|-------------|--------------------------------------------------|

| Sleep   | Low  | Floating     | Weak current pullup    | High impedance | Off         |                                                  |

| Standby | Low  | Low          | 30 kΩ (typ)            | High           | Off         | Wake-up event detected, waiting on MCU to set EN |

| Normal  | High | LIN bus data | 30 kΩ (typ)            | High           | On          | LIN transmission up to 20 kbps                   |

## **Normal Mode**

This is the normal operational mode, in which the receiver and driver are active, and LIN transmission up to the LIN specified maximum of 20 kbps is supported. The receiver detects the data stream on the LIN bus and outputs it on RXD for the LIN controller, where recessive on the LIN bus is a digital high, and dominate on the LIN bus is digital low. The driver transmits input data on TXD to the LIN bus. Normal mode is entered as EN transitions high while the SN65HVDA100 is in sleep or standby mode.

SLIS128A-NOVEMBER 2011-REVISED JANUARY 2013

# OPERATING STATES

**Unpowered System**

$V_{\mathsf{sup}} \leq V_{\mathsf{sup\_under}}$

www.ti.com

www.ti.com

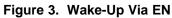

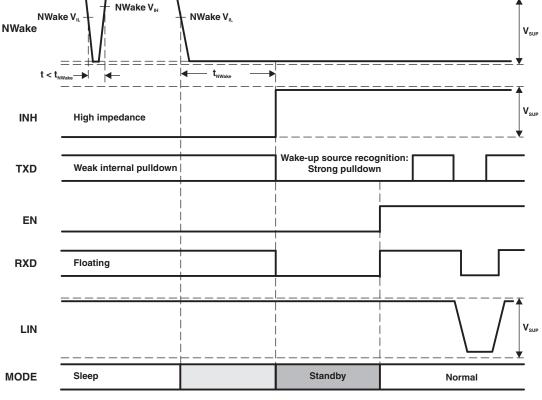

### Sleep Mode

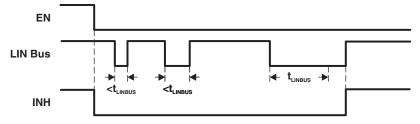

Sleep mode is the power saving mode for the SN65HVDA100. Even with the extremely low current consumption in this mode, the SN65HVDA100 can still wake up from LIN bus via a wake-up signal, a low on NWake, or if EN is set high. The LIN bus and NWake are filtered to prevent false wake-up events. The wake-up events must be active for their respective time periods ( $t_{LINBUS}$ ,  $t_{NWake}$ ).

The sleep mode is entered by setting EN low.

While the device is in sleep mode, the following conditions exist:

- The LIN bus driver is disabled and the internal LIN bus termination is switched off (to minimize power loss if LIN is short circuited to ground). However, the weak current pullup is active to prevent false wake-up events in case an external connection to the LIN bus is lost.

- The normal receiver is disabled.

- INH is high impedance.

- EN input, NWake input, and the LIN wake-up receiver are active.

### Wake-Up Events

There are three ways to wake up from sleep mode:

- Remote wake-up via recessive (high) to dominant (low) state transition on LIN bus. The dominant state must be held for t<sub>LINBUS</sub> filter time and then the bus must return to the recessive state (to eliminate false wake-ups from disturbances on the LIN bus or if the bus is shorted to ground).

- Local wake-up via a low on NWake, which is asserted low longer than the filter time t<sub>NWake</sub> (to eliminate false wake-ups from disturbances on NWake)

- Local wake-up via EN being set high

#### Wake-Up Request (RXD)

When the device encounters a wake-up event from the LIN bus or NWake pin, RXD goes low, and the device transitions to standby mode (until EN is reasserted high and the device enters normal mode). Once the device enters normal mode, the RXD pin is releasing the wake-up request signal, and the RXD pin then reflects the receiver output from the bus.

#### Wake-Up Source Recognition (TXD)

When the device encounters a wake-up event from the LIN bus or NWake pin, TXD indicates the source while the device enters and remains in standby mode (until EN is reasserted high and the device enters normal mode). In addition to the internal pullup resistor on TXD, typically an external pullup resistor (~5 k $\Omega$ ) is used in the system's I/O supply voltage. A high on TXD in standby mode indicates a remote wake-up via the LIN bus, and a low (strong pulldown) on the TXD pin indicates a local wake-up via the NWAKE pin.

#### Standby Mode

This mode is entered whenever a wake-up event occurs via LIN bus or NWake while the device is in sleep mode. The LIN bus slave termination circuit and INH are turned on when standby mode is entered. The application system powers up once INH is turned on, assuming the system is using a voltage regulator connected via INH. Standby mode is signaled via a low level on RXD.

When EN is set high while the device is in standby mode the device returns to normal mode and the normal transmission paths from TXD to LIN bus and LIN bus to RXD are enabled.

During power up if EN is low the device goes into Standby mode and if EN is high the device goes into Normal mode. EN has an internal pull down resistor, so if the pin is floating in the system, the internal pull down will ensure it is pulled low.

**Application Hint**: if the INH output of the HVDA100 is not used to control the system power management (voltage regulators) and monitor wake up sources, but sleep mode is used to reduce system current the RXD pin can be monitored to ensure HVDA100 remains in sleep mode. If the HVDA100 detects an undervoltage on  $V_{SUP}$  the RXD pin transitions low and would signal to the software that the HVDA100 is in standby mode and should be returned to sleep mode to return to the lowest power state.

SLIS128A-NOVEMBER 2011-REVISED JANUARY 2013

Figure 5. Wake-Up Via NWake

## PROTECTION AND FAILSAFE FEATURES

## TXD Dominant State Timeout

During normal mode, if TXD is inadvertently driven permanently low by a hardware or software application failure, the LIN bus is protected by the dominant state timeout timer. This timer is triggered by a falling edge on TXD. If the low signal remains on TXD for longer than  $t_{DST}$ , the transmitter is disabled, thus allowing the LIN bus to return to the recessive state and communication to resume on the bus. The protection is cleared and the  $t_{DST}$  timer is reset by a rising edge on TXD. The TXD pin has an internal pulldown to ensure the device fails to a known state if TXD is disconnected. During this fault, the transceiver remains in normal mode (assuming no change of state request on EN), the transmitter is disabled, the RXD pin reflects the LIN bus, INH remains on, and the LIN bus pullup termination remains on.

**APPLICATION NOTE:** The maximum dominant TXD time allowed by the TXD Dominant state time out limits the minimum possible data rate of the device. The LIN protocol has differenct constraints for master and slave applications thus there are different the maximum consecutive dominant bits for each application case and thus different minimum data rates.

**Master node:** The maximum continuous dominant is the maximum dominant of the SYNC BREAK FIELD,  $t_{SYNC_DOM(max)}$ . The SYN BREAK FIELD notifies the 'start of frame' to all LIN slaves. It consists of 13 to 26 dominant bits (low phase) followed by a delimiter. Thus the minimum TXD dominant time out,  $t_{DST(min)}$  and the maximum SYNC BREAK FIELD for the master determine the minimum data rate for a master node, which may be calculated by the following equation:

$DataRate_{Master(min)} = t_{SYNC_DOM(max)} / t_{DST(min)}$

**Slave node:** sends the response part of the LIN message frame which has a maximum consecutive dominant length of 9 bits (start bit + 8 data bits). As a result the minimum baud rate of a slave can be calculated by the following equation:

$DataRate_{Slave(min)} = 9 + n_{margin} / t_{DST(min)}$  where  $n_{margin}$  is a saftey margin.

8

#### Thermal Shutdown

The LIN transmitter is protected via a current limit, however, if the junction temperature of the device exceeds the thermal shutdown threshold, the device turns off the LIN transmitter circuit. Once the overtemperature fault condition has been removed and the junction temperature has cooled beyond the hysteresis temperature, the transmitter is re-enabled, assuming the device remained in the normal mode. During this fault, the transceiver remains in normal mode (assuming no change of state request on EN), the transmitter is disabled, the RXD pin reflects the LIN bus, INH remains on, and the LIN bus pullup termination remains on.

www.ti.com

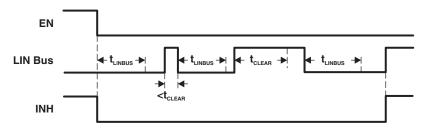

### Bus Stuck Dominant System Fault: False Wake Up Lock Out

The device contains logic to detect bus stuck dominant system faults and prevent the device from waking up falsely during this system fault. Upon entering sleep mode, the device detects the state of the LIN bus. If the bus is dominant, the wake up logic is locked out until a valid recessive on the bus "clears" the bus stuck dominant condition. This logic prevents the potential for a cyclical false wake up of the system if the bus is stuck dominant, preventing excessive current use. Figure 6 and Figure 7 show the behavior of this protection feature.

#### Figure 6. No Bus Fault: Entering Sleep Mode With Bus Recessive Condition and Wake Up

#### Figure 7. Bus Fault: Entering Sleep Mode With Bus Stuck Dominant Fault, Clearing, and Wake Up

#### Undervoltage on V<sub>SUP</sub>

The device contains a power-on reset circuit to avoid false bus messages during undervoltage conditions when  $V_{SUP}$  is less than  $UV_{VSUP}$ .

#### **Unpowered Device Does Not Affect the LIN Bus**

The device has extremely low unpowered leakage current from the bus, so an unpowered node does not affect the network or load it down. This is optimal for LIN systems in which some of the nodes are unpowered (ignition supplied) while the rest of the network remains powered (battery supplied).

SLIS128A - NOVEMBER 2011 - REVISED JANUARY 2013

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup> <sup>(2)</sup>

|     |                    |                                                           |              | UNITS                  |

|-----|--------------------|-----------------------------------------------------------|--------------|------------------------|

| 1.1 | V <sub>SUP</sub>   | Supply line supply voltage (LIN 2.1 Param 11)             |              | –0.3 V to 45 V         |

| 1.2 | V <sub>LIN</sub>   | LIN input voltage                                         |              | –27 V to 45 V          |

| 1.3 | V <sub>NWAKE</sub> | NWake input voltage (via serial resistor $\ge 2k\Omega$ ) |              | –0.3 V to 45 V         |

| 1.4 | I <sub>O</sub>     | Output current                                            |              |                        |

| 1.5 | V <sub>INH</sub>   | INH voltage                                               |              | –0.3 V to Vsup + 0.3 V |

| 1.6 | V <sub>Logic</sub> | Logic pin voltage                                         | RXD, TXD, EN | –0.3 V to 5.5 V        |

| 1.7 | T <sub>A</sub>     | Operational free-air (ambient) temperature range          |              | -40°C to 125°C         |

| 1.8 | TJ                 | Junction temperature range                                |              | -40°C to 150°C         |

| 1.9 | T <sub>LEAD</sub>  | Lead temperature (soldering, 10 seconds)                  |              | 260°C                  |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to GND.

## TRANSIENT AND ELECTROSTATIC DISCHARGE PROTECTION

| 2.1 | Electrostatic discharge |                                 | All pins                   | -4 kV to 4 kV     |

|-----|-------------------------|---------------------------------|----------------------------|-------------------|

| 2.2 |                         | Human-Body Model <sup>(1)</sup> | LIN bus pin <sup>(2)</sup> | -12 kV to 12 kV   |

| 2.3 |                         |                                 | NWake pin <sup>(3)</sup>   | –11 kV to 11 kV   |

| 2.4 |                         | Charged-Device Model            | All pins <sup>(4)</sup>    | –1.5 kV to 1.5 kV |

(1) Tested in accordance to AEC-Q100-002.

(2) Test method based upon AEC-Q100-002, LIN bus pin stressed with respect to GND.

(3) Test method based upon AEC-Q100-002, NWake pin stressed with respect to GND.

(4) Tested in accordance to AEC-Q100-011.

## **RECOMMENDED OPERATING CONDITIONS**

|     |                    |                                                                      | MIN | MAX  | UNIT |

|-----|--------------------|----------------------------------------------------------------------|-----|------|------|

| 3.1 | V <sub>SUP</sub>   | Supply line supply voltage (LIN 2.1 Param 10)                        | 5   | 27   | V    |

| 3.2 | V <sub>LIN</sub>   | LIN input voltage                                                    | 0   | 18   | V    |

| 3.3 | V <sub>NWake</sub> | NWake input voltage                                                  | 0   | 27   | V    |

| 3.4 | V <sub>INH</sub>   | INH voltage                                                          | 0   | 27   | V    |

| 3.5 | V <sub>Logic</sub> | Logic voltage                                                        | 0   | 5.25 | V    |

| 3.6 | T <sub>A</sub>     | Operational free-air temperature (see Thermal Characteristics table) | -40 | 125  | °C   |

Texas Instruments

www.ti.com

## **ELECTRICAL CHARACTERISTICS**

$V_{SUP}$  = 5V to 27 V,  $T_{J}$  = –40°C to 150°C (unless otherwise noted)

|                    | PARA                  | METER                                                              | TEST CONDITIONS / COMMENT MIN TYP <sup>(1)</sup> MAX UN                                                                                                                                                         |      | UNIT |      |    |

|--------------------|-----------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| V <sub>SUP</sub> S | UPPLY                 |                                                                    |                                                                                                                                                                                                                 |      |      |      |    |

| 4.1                | V <sub>SUP</sub>      | Operational supply<br>voltage (LIN 2.1<br>Param 10) <sup>(2)</sup> | Device is operational beyond the LIN defined nominal supply line voltage range of 5 V < $V_{SUP}$ < 27 V                                                                                                        | 5    | 14   | 27   | V  |

|                    | .,                    | Nominal supply                                                     | Normal and standby modes                                                                                                                                                                                        | 7    | 14   | 18   | ., |

| 4.2                | V <sub>SUP</sub>      | voltage (LIN 2.1<br>Param 10)                                      | Sleep mode                                                                                                                                                                                                      | 7    | 12   | 18   | V  |

| 4.3                | UV <sub>SUP</sub>     | Undervoltage V <sub>SUP</sub> th                                   | reshold                                                                                                                                                                                                         | 4.35 |      | 4.65 | V  |

| 4.4                | UV <sub>HYS</sub>     | Delta hysteresis volta                                             | ge for $V_{SUP}$ undervoltage threshold                                                                                                                                                                         |      | 0.2  |      | V  |

| 4.5                |                       |                                                                    | Normal mode, EN = high, Bus dominant<br>(total bus load where $R_{LIN} \ge 500 \Omega$ and<br>$C_{LIN} \le 10 \text{ nF}$ (see Figure 10) <sup>(3)</sup> ,<br>INH = V <sub>SUP</sub> , NWake = V <sub>SUP</sub> |      | 1.2  | 7.5  | mA |

| 4.6                |                       |                                                                    | Standby mode, EN = low, Bus dominant<br>(total bus load where $R_{LIN} \ge 500 \Omega$ and<br>$C_{LIN} \le 10 \text{ nF}$ (see Figure 10) <sup>(3)</sup> ,<br>INH = V <sub>SUP</sub> , NWake = V <sub>SUP</sub> |      | 1    | 2.1  | mA |

| 4.7                | I <sub>SUP</sub>      | Supply current                                                     | Normal mode, EN = high, Bus recessive,<br>LIN = $V_{SUP}$ , INH = $V_{SUP}$ , NWake = $V_{SUP}$                                                                                                                 |      | 450  | 775  | μΑ |

| 4.8                |                       |                                                                    | Standby mode, EN = low, Bus recessive, LIN = $V_{SUP}$ , INH = $V_{SUP}$ , NWake = $V_{SUP}$                                                                                                                    |      | 450  | 775  | μA |

| 4.9                |                       |                                                                    | Sleep mode, 7 V < $V_{SUP} \le 14$ V,<br>LIN = $V_{SUP}$ , NWake = $V_{SUP}$ , EN = 0 V,<br>TXD and RXD floating                                                                                                |      | 10   | 20   | μA |

| 4.10               |                       |                                                                    | Sleep mode, 14 V < $V_{SUP}$ < 27 V,<br>LIN = $V_{SUP}$ , NWake = $V_{SUP}$ , EN = 0 V,<br>TXD and RXD floating                                                                                                 |      |      | 30   | μA |

| RXD O              | utput Pin (o          | pen drain)                                                         | •                                                                                                                                                                                                               |      |      |      |    |

| 5.1                | Vo                    | Output voltage <sup>(4)</sup>                                      |                                                                                                                                                                                                                 | -0.3 |      | 5.5  | V  |

| 5.2                | I <sub>OL</sub>       | Low-level output<br>current, open drain                            | LIN = 0 V, RXD = 0.4 V                                                                                                                                                                                          | 3.5  |      |      | mA |

| 5.3                | I <sub>IKG</sub>      | Leakage current,<br>high-level                                     | $LIN = V_{SUP}, RXD = 5 V$                                                                                                                                                                                      | -5   | 0    | 5    | μA |

| TXD In             | put / Output          | Pin                                                                |                                                                                                                                                                                                                 |      |      |      |    |

| 6.1                | VIL                   | Low-level input voltag                                             | e                                                                                                                                                                                                               | -0.3 |      | 0.8  | V  |

| 6.2                | V <sub>IH</sub>       | High-level input voltage                                           | je                                                                                                                                                                                                              | 2    |      | 5.5  | V  |

| 6.3                | V <sub>IT</sub>       | Input threshold hyster                                             | esis voltage                                                                                                                                                                                                    | 30   |      | 500  | mV |

| 6.4                |                       | Pulldown resistor                                                  |                                                                                                                                                                                                                 | 125  | 350  | 800  | kΩ |

| 6.5                | IIL                   | Low-level input<br>leakage current                                 | TXD = Low                                                                                                                                                                                                       | -5   | 0    | 5    | μA |

| 6.6                | I <sub>TXD_Wake</sub> | Local wake up<br>source re recognition<br>TXD open drain<br>drive  | Standby mode after a local wake up event, $V_{LIN} = V_{SUP}$ , NWake = 0 V, TXD = 1 V                                                                                                                          | 1.3  | 4.6  | 8    | mA |

(1) Typical values are given for  $V_{SUP} = 14 \text{ V}$  at 25°C, except for low power mode where typical values are given for  $V_{SUP} = 12 \text{ V}$  at 25°C. (2) All voltages are defined with respect to ground; positive currents flow into the SN65HVDA100 device.

(2) All voltages are defined with respect to ground; positive currents flow into the SN65HVDA100 device.

(3) In the dominant state, the supply current increases as the supply voltage increases due to the integrated LIN slave termination resistance. At higher voltages the majority of supply current is through the termination resistance. The minimum resistance of the LIN slave termination is 20 kΩ, so the maximum supply current attributed to the termination is:I<sub>SUP</sub> (dom) max termination *\** (V<sub>SUP</sub> – (V<sub>LIN\_Dominant</sub> + 0.7 V) / 20 kΩ

(4) RXD pin output is open drain. Output voltage is via external pull up resistance to logic supply of the system and impedance of the RXD pin.

#### www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{SUP}$  = 5V to 27 V,  $T_{\rm J}$  = –40°C to 150°C (unless otherwise noted)

|            | PARA                          | METER                                                                    | <b>TEST CONDITIONS / COMMENT</b>                                                                | MIN                      | TYP <sup>(1)</sup>     | MAX                      | UNIT |

|------------|-------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------|------------------------|--------------------------|------|

| LIN Pin    | (Reference                    | d to V <sub>SUP</sub> )                                                  |                                                                                                 |                          |                        |                          |      |

| 7.1        | V <sub>OH</sub>               | High-level output voltage                                                | LIN recessive, TXD = high, $I_O = 0$ mA, $V_{SUP} = 14$ V                                       | V <sub>SUP</sub> – 1     |                        |                          | V    |

| 7.2        | V <sub>OL</sub>               | Low-level output voltage                                                 | LIN dominant, TXD = low, $I_0$ = 40 mA, $V_{SUP}$ = 14 V                                        |                          |                        | $0.2 \times V_{SUP}$     | V    |

| 7.3        | IL                            | Limiting current (LIN 2.1 Param 12)                                      | TXD = 0 V, $V_{LIN}$ = 7 V to 27 V                                                              | 40                       | 90                     | 200                      | mA   |

| 7.4        |                               | Receiver leakage<br>current, dominant<br>(LIN 2.1 Param 13)              | LIN = 0 V, 7V $\leq$ V <sub>SUP</sub> $\leq$ 18 V, Driver off                                   | -1                       |                        |                          | mA   |

| 7.5        | I <sub>LKG</sub>              | Receiver leakage                                                         | LIN ≥ $V_{SUP}$ , 7 ≤ $V_{SUP}$ ≤18 V, Driver off                                               |                          |                        | 20                       |      |

| 7.6        |                               | current, recessive<br>(LIN 2.1 Param 14)                                 | LIN = V <sub>SUP</sub> , driver off                                                             | -5                       |                        | 5                        | μA   |

| 7.7        | I <sub>LKG</sub>              | Leakage current,<br>loss of ground (LIN<br>2.1 Param 15)                 |                                                                                                 | -1                       |                        | 1                        | mA   |

| 7.8<br>7.9 | I <sub>LKG</sub>              | Leakage current,<br>loss of supply (LIN<br>2.1 Param 16)                 | 7 V < LIN $\leq$ 12 V, V <sub>SUP</sub> = GND<br>12 V < LIN $\leq$ 18 V, V <sub>SUP</sub> = GND |                          |                        | 5<br>10                  | μA   |

| 7.10       | V <sub>IL</sub>               | Low-level input<br>voltage (LIN 2.1<br>Param 17)                         | LIN dominant (including LIN dominant for wake up)                                               |                          |                        | 0.4 × V <sub>SUP</sub>   | V    |

| 7.11       | V <sub>IH</sub>               | High-level input<br>voltage (LIN 2.1<br>Param 18)                        | LIN recessive                                                                                   | 0.6 × V <sub>SUP</sub>   |                        |                          | V    |

| 7.12       | V <sub>BUS_CNT</sub>          | Receiver center<br>threshold (LIN 2.1<br>Param 19)                       | $V_{BUS_{CNT}} = (V_{IL} + V_{IH}) / 2$                                                         | 0.475 x V <sub>SUP</sub> | 0.5 × V <sub>SUP</sub> | 0.525 x V <sub>SUP</sub> | V    |

| 7.13       | V <sub>HYS</sub>              | Hysteresis voltage<br>(LIN 2.1 Param 20)                                 | $V_{HYS} = (V_{IL} - V_{IH})$                                                                   | 0.05 × V <sub>SUP</sub>  |                        | 0.175 × V <sub>SUP</sub> | V    |

| 7.14       | V <sub>SERIAL_</sub><br>DIODE | Serial diode in LIN<br>termination pull up<br>path (LIN 2.1 Param<br>21) | By design and characterization                                                                  | 0.4                      | 0.7                    | 1.0                      | V    |

| 7.15       | R <sub>SLAVE</sub>            | Pullup resistor to $V_{SUP}$ (LIN 2.1 Param 26)                          | Normal and standby modes                                                                        | 20                       | 30                     | 60                       | kΩ   |

| 7.16       | R <sub>SLEEP</sub>            | Pullup current source to V <sub>SUP</sub>                                | Sleep mode, $V_{SUP}$ = 14 V, LIN = GND                                                         | -2                       |                        | -20                      | μA   |

| EN Inp     | ut Pin                        |                                                                          |                                                                                                 |                          |                        |                          |      |

| 8.1        | V <sub>IL</sub>               | Low-level input voltage                                                  |                                                                                                 | -0.3                     |                        | 0.8                      | V    |

| 8.2        | V <sub>IH</sub>               | High-level input voltage                                                 |                                                                                                 | 2                        |                        | 5.5                      | V    |

| 8.3        | V <sub>hys</sub>              | Hysteresis voltage                                                       | By design and characterization                                                                  | 30                       |                        | 500                      | mV   |

| 8.4        |                               | Pulldown resistor                                                        |                                                                                                 | 125                      | 350                    | 800                      | kΩ   |

| 8.5        | IIL                           | Low-level input<br>current                                               | EN = Low                                                                                        | -5                       | 0                      | 5                        | μA   |

| INH Ou     | itput Pin                     |                                                                          | ·                                                                                               | ·                        |                        |                          |      |

| 9.1        | R <sub>DS(on)</sub>           | On-state resistance                                                      | Between V <sub>SUP</sub> and INH, INH = 2-<br>mA drive, Normal or standby mode                  |                          | 25                     | 50                       | Ω    |

| 9.2        | I <sub>IKG</sub>              | Leakage current                                                          | Low-power mode, 0 < INH < V <sub>SUP</sub>                                                      | -5                       | 0                      | 5                        | μA   |

INSTRUMENTS

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{SUP} = 5V$  to 27 V,  $T_J = -40^{\circ}C$  to 150°C (unless otherwise noted)

|       | PAR                 | AMETER                                                                   | <b>TEST CONDITIONS / COMMENT</b>                                                                                                                                                                                                                                 | MIN                  | TYP <sup>(1)</sup> | MAX                    | UNIT |

|-------|---------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|------------------------|------|

| NWake | e Input Pin         |                                                                          |                                                                                                                                                                                                                                                                  |                      |                    |                        |      |

| 10.1  | V <sub>IL</sub>     | Low-level input voltage                                                  |                                                                                                                                                                                                                                                                  | -0.3                 |                    | V <sub>SUP</sub> – 3.3 | V    |

| 10.2  | V <sub>IH</sub>     | High-level input voltage                                                 |                                                                                                                                                                                                                                                                  | V <sub>SUP</sub> – 1 |                    | V <sub>SUP</sub> + 0.3 | V    |

| 10.3  |                     | Pullup current                                                           | NWake = 0 V                                                                                                                                                                                                                                                      | -45                  | -10                | -2                     | μA   |

| 10.4  | I <sub>IKG</sub>    | Leakage current                                                          | V <sub>SUP</sub> = NWake                                                                                                                                                                                                                                         | -5                   | 0                  | 5                      | μA   |

| AC Ch | aracteristic        | s                                                                        |                                                                                                                                                                                                                                                                  |                      |                    |                        |      |

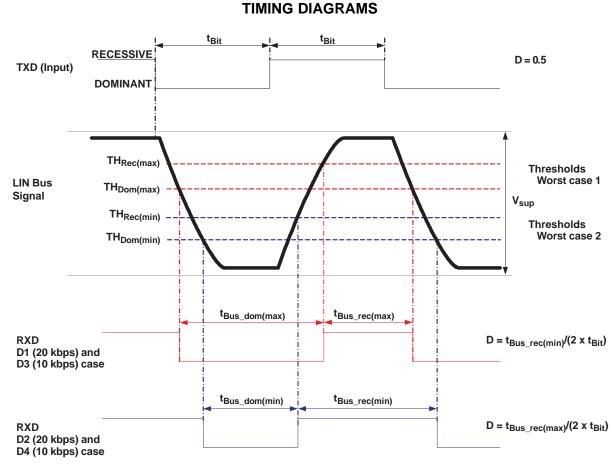

| 11.1  | D1                  | Duty cycle 1 <sup>(5)</sup> (LIN<br>2.1 Param 27)                        | $\begin{array}{l} TH_{REC(max)} = 0.744 \times V_{SUP}, \\ TH_{DOM(max)} = 0.581 \times V_{SUP}, \\ V_{SUP} = 7 \ V \ to \ 18 \ V, \ t_{BIT} = 50 \ \mu s \ (20 \ kbps), \\ D1 = t_{Bus\_rec(min)'} \ (2 \times t_{BIT}) \ (see \ Figure \ 8) \end{array}$       | 0.396                |                    |                        |      |

| 11.2  | D2                  | Duty cycle 2 <sup>(5)</sup> (LIN<br>2.1 Param 28)                        | $\begin{array}{l} TH_{REC(min)} = 0.422 \times V_{SUP}, \\ TH_{DOM(min)} = 0.284 \times V_{SUP}, \\ V_{SUP} = 7.6 \ V \ to \ 18 \ V, \\ t_{BIT} = 50 \ \mu s \ (20 \ kbps), \\ D2 = t_{Bus\_rec(max)} / \ (2 \times t_{BIT}) \ (see \ Figure \ 8) \end{array}$   |                      |                    | 0.581                  |      |

| 11.3  | D3                  | Duty cycle 3 <sup>(5)</sup> (LIN<br>2.1 Param 29)                        | $\begin{array}{l} TH_{REC(max)} = 0.778 \times V_{SUP}, \\ TH_{DOM(max)} = 0.616 \times V_{SUP}, \\ V_{SUP} = 7 \ V \ to \ 18 \ V, \\ t_{BIT} = 96 \ \mu s \ (10.4 \ kbps), \\ D3 = t_{Bus\_rec(min)}/ \ (2 \times t_{BIT}) \ (see \ Figure \ 8) \end{array}$    | 0.417                |                    |                        |      |

| 11.4  | D4                  | Duty cycle 4 <sup>(5)</sup> (LIN<br>2.1 Param 30)                        | $\begin{array}{l} TH_{REC(min)} = 0.389 \times V_{SUP}, \\ TH_{DOM(min)} = 0.251 \times V_{SUP}, \\ V_{SUP} = 7.6 \ V \ to \ 18 \ V, \\ t_{BIT} = 96 \ \mu s \ (10.4 \ kbps), \\ D4 = t_{Bus\_rec(max)} / \ (2 \times t_{BIT}) \ (see \ Figure \ 8) \end{array}$ |                      |                    | 0.59                   |      |

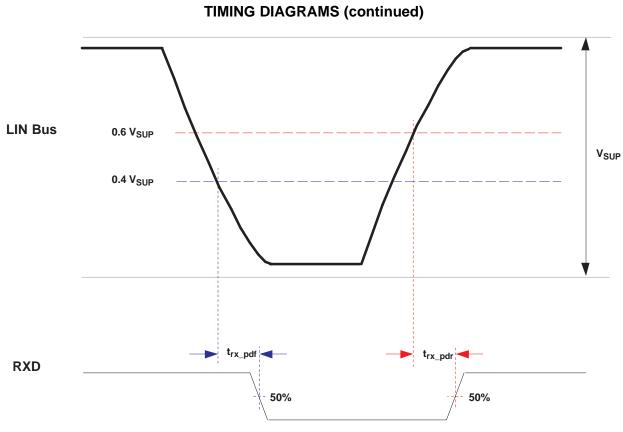

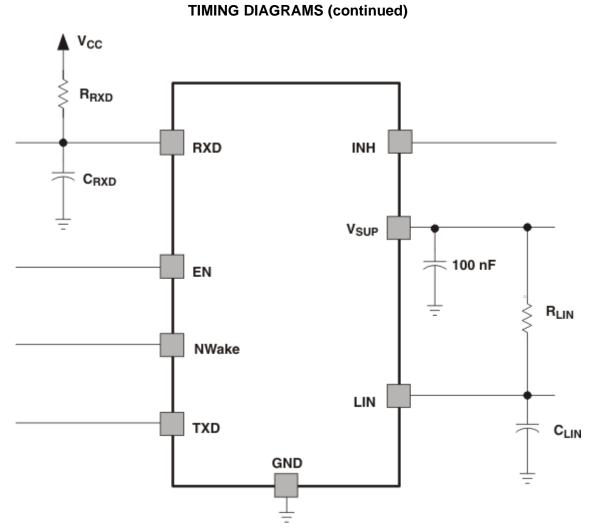

| 11.5  | t <sub>rx_pdr</sub> | Receiver rising<br>propagation delay<br>time (LIN 2.1 Param<br>31)       | $R_{RXD} = 2.4 \text{ k}\Omega$ , $C_{RXD} = 20 \text{ pF}$<br>(see Figure 9 and Figure 10)                                                                                                                                                                      |                      |                    | 6                      | μs   |

| 11.6  | t <sub>rx_pdf</sub> | Receiver falling<br>propagation delay<br>time (LIN 2.1 Param<br>31)      | $R_{RXD} = 2.4 \text{ k}\Omega$ , $C_{RXD} = 20 \text{ pF}$<br>(see Figure 9 and Figure 10)                                                                                                                                                                      |                      |                    | 6                      | μs   |

| 11.7  | t <sub>rx_sym</sub> | Symmetry of<br>receiver propagation<br>delay time (LIN 2.1<br>Param 32)  | Rising edge with respect to falling edge<br>$(t_{r_{X}\_sym} = t_{r_{X}\_pdf} - t_{r_{X}\_pdr}) R_{RXD} = 2.4 k\Omega,$<br>$C_{RXD} = 20 \text{ pF}$ (see Figure 9 and<br>Figure 10)                                                                             | -2                   |                    | 2                      | μs   |

| 11.8  | t <sub>NWake</sub>  | NWake filter time for local wake-up                                      | See Figure 5                                                                                                                                                                                                                                                     | 25                   | 50                 | 150                    | μs   |

| 11.9  | t <sub>LINBUS</sub> | LIN wake-up time<br>(Minimum dominant<br>time on LIN bus for<br>wake-up) | See Figure 6, Figure 7, and Figure 4                                                                                                                                                                                                                             | 25                   | 100                | 150                    | μs   |

(5) Duty cycles: LIN driver bus load conditions (C<sub>LINBUS</sub>, R<sub>LINBUS</sub>): Load1 = 1 nF, 1 kΩ; Load2 = 10 nF, 500 Ω. Duty cycles 3 and 4 are defined for 10.4-kbps operation. The SN65HVDA100 also meets these lower data rate requirements, while it is capable of the higher speed 20-kbps operation as specified by duty cycles 1 and 2. SAEJ2602 derives propagation delay equations from the LIN 2.0 duty cycle definitions, for details see the SAEJ2602 specification.

www.ti.com

# ELECTRICAL CHARACTERISTICS (continued)

$V_{SUP} = 5V$  to 27 V,  $T_J = -40^{\circ}C$  to 150°C (unless otherwise noted)

| PARAMETER |                              | AMETER                                                                                                                                                                  | TEST CONDITIONS / COMMENT                                                                     | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|-----------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| 11.10     | tclear                       | Time to clear false<br>wake-up prevention<br>logic if LIN Bus had<br>bus stuck dominant<br>fault (recessive time<br>on LIN bus to clear<br>bus stuck dominant<br>fault) | See Figure 7                                                                                  | 8   | 17                 | 50  | μs   |

| 11.11     | t <sub>DST</sub>             | Dominant state timeout <sup>(6)</sup>                                                                                                                                   |                                                                                               | 20  | 34                 | 80  | ms   |

| 11.12     | t <sub>MODE_</sub><br>CHANGE | Mode change delay time                                                                                                                                                  | Time to change from standby mode to<br>normal mode or normal mode to sleep<br>mode via EN pin |     |                    | 5   | μs   |

(6) TXD Dominant state timeout limits the minimum data rate to 650bps. The minimum datarates may be calculated by the following forumulas. DataRate<sub>Master(min)</sub> = t<sub>SYNC\_DOM(max)</sub> / t<sub>DST(min)</sub> and DataRate<sub>Slave(min)</sub> = 9 + n<sub>margin</sub> / t<sub>DST(min)</sub> where n<sub>margin</sub> is a saftey margin. For slave node cases where n<sub>margin</sub> ≤ 4, the master node case will be the limiting calculation.

#### THERMAL INFORMATION

|                         | THERMAL METRIC <sup>(1)</sup>                | SN65HVDA  | 100-Q1     |       |

|-------------------------|----------------------------------------------|-----------|------------|-------|

|                         |                                              | D (8 PI   | NS)        | UNITS |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 112.5     | 5          |       |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance    | 66.3      |            |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 52.9      |            | °C/W  |

| Ψ <sub>JT</sub>         | Junction-to-top characterization parameter   | 19.3      |            | °C/W  |

| Ψ <sub>JB</sub>         | Junction-to-board characterization parameter | 52.4      |            |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | N/A       |            |       |

|                         | Thermal shutdown temperature                 | 180       |            | °C    |

|                         | Thermal shutdown hysteresis                  | 15        |            | °C    |

| P <sub>D</sub>          | Power Dissipation in normal mode (dominant)  | Тур<br>17 | Max<br>230 | mW    |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Texas Instruments

#### SLIS128A-NOVEMBER 2011-REVISED JANUARY 2013

www.ti.com

Figure 8. Definition of Bus Timing Parameters

# SN65HVDA100-Q1

SLIS128A-NOVEMBER 2011-REVISED JANUARY 2013

Figure 9. Propagation Delay

TEXAS INSTRUMENTS

SLIS128A-NOVEMBER 2011-REVISED JANUARY 2013

www.ti.com

Figure 10. Test Circuit for AC Characteristics

# SN65HVDA100-Q1

SLIS128A-NOVEMBER 2011-REVISED JANUARY 2013

#### **APPLICATION INFORMATION**

(2) RXD on MCU or LIN slave without internal pullup, requires external pullup resistor.

(3) Master node applications require an external  $1-k\Omega$  pullup resistor and serial diode.

Figure 11.

#### TEXAS INSTRUMENTS

www.ti.com

## Device Comparison: TPIC1021 vs SN65HVDA100

The SN65HVDA100 is pin-to-pin compatible to the TPIC1021 device. The SN65HVDA100 is an enhanced LIN transceiver, including enhanced immunity to RF disturbances. Table 2 is a summary of the differences between the two devices.

#### Table 2. SN65HVDA100 vs TPIC1021 Differences

| SPECIFICATION                                                                          | SN65HVDA100                                                                                                                                                                                | TPIC1021                                                                                                                              |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| LIN termination                                                                        | Weak current pullup in sleep mode                                                                                                                                                          | High $\Omega$ in low-power mode                                                                                                       |

| LIN receiver                                                                           | Enhanced high-speed receive capable                                                                                                                                                        | High-speed receive capable                                                                                                            |

| LIN leakage current<br>(unpowered device):<br>7 V < LIN < 12 V, V <sub>SUP</sub> = GND | <5 µA at 12 V (max)                                                                                                                                                                        | <10 µA at 12 V (typ)                                                                                                                  |

| LIN bus wake-up                                                                        | Remote wake-up via recessive-to-dominant transition on LIN bus where dominant bus state is held for at least $t_{\text{LINBUS}}$ time followed by a transition back to the recessive state | Remote wake-up via recessive-to-dominant transition on LIN bus where dominant bus state is held for at least t <sub>LINBUS</sub> time |

| Low-power current                                                                      | <20 µA at 14 V (max)                                                                                                                                                                       | <50 µA at 14 V (max)                                                                                                                  |

| INH pin                                                                                | Enhanced driving of bus master termination via lower $\ensuremath{R_{\text{on}}}$                                                                                                          | Driving of bus master termination                                                                                                     |

| Source wake up recognition (TXD pin)                                                   | TXD pin reflects the source of the wake-up event (LIN or NWake)                                                                                                                            | Not applicable                                                                                                                        |

| Default power up state                                                                 | Standby mode                                                                                                                                                                               | Sleep mode                                                                                                                            |

# www.ti.com

## **REVISION HISTORY**

| Cł | nanges from Original (November 2011) to Revision A                                                                   | Page |

|----|----------------------------------------------------------------------------------------------------------------------|------|

| •  | Added 1.4 row to the abs max table by copying from the 9.2 row in the elec char table                                | 11   |

| •  | Deleted -03V to 45V from the 1.5 row in the abs max table, units column                                              | 11   |

| •  | Changed added Delta and corrected Hysteresis in elec chara table, row 4.4 and changed the TYP column from 4.5 to 0.2 | 12   |

| •  | Deleted rows 9.1 and 9.2 from the elec chara table                                                                   | 13   |

| •  | Added Minimum to the statement in parens in front of dominant, row 11.9 of elec chara table                          | 14   |

17-Apr-2013

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        |                  | (3)                 |              | (4)               |         |

| SN65HVDA100QDRQ1 | ACTIVE | SOIC         | D       | 8    | 2500    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 125   | A100Q             | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

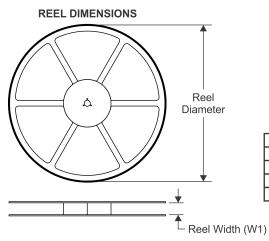

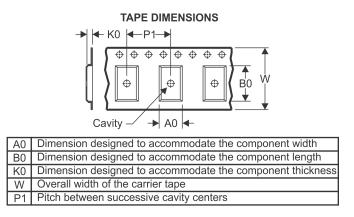

## TAPE AND REEL INFORMATION

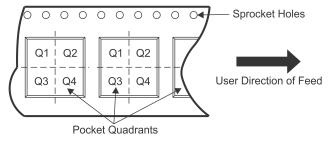

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| SN65HVDA100QDRQ1            | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

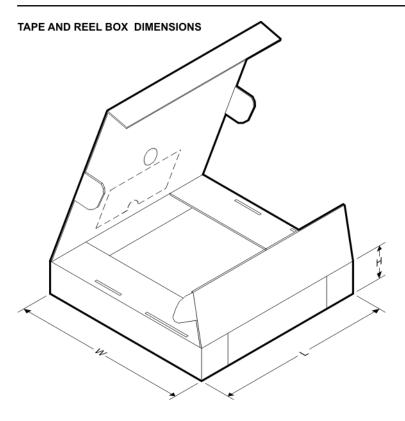

# PACKAGE MATERIALS INFORMATION

3-Jan-2013

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65HVDA100QDRQ1 | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

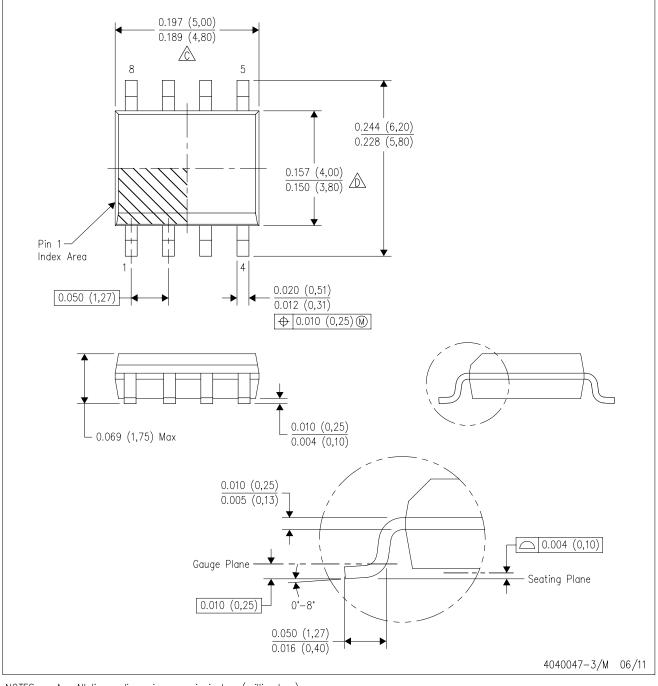

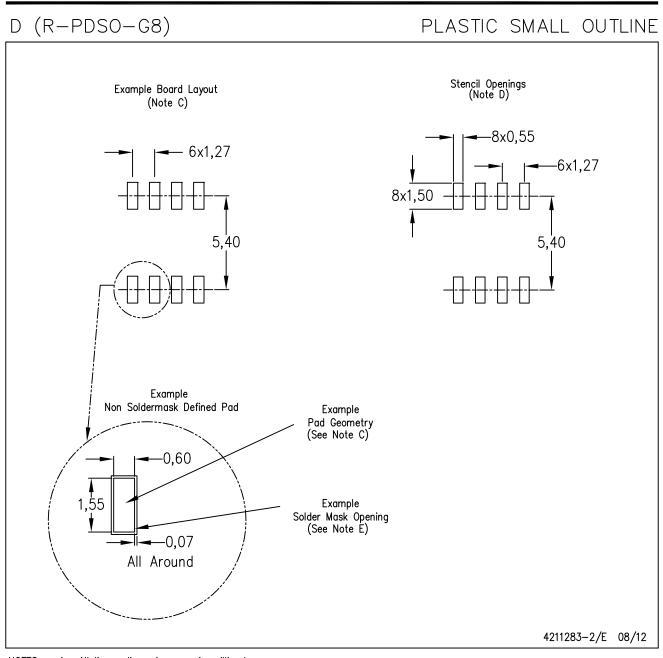

D (R-PDSO-G8)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated