# Controller for RF Power Amplifier Boost Converter

#### **FEATURES**

- High Frequency Switching (up to 2 MHz)

- Optimized Output Drive Current (350 mA)

- Standby Mode

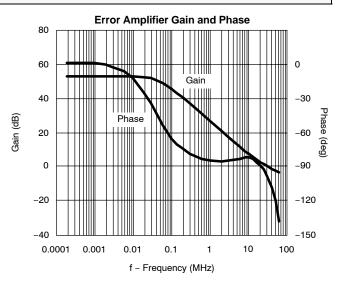

- Wide Bandwidth Feedback Amplifier

- Single-Cell Lilon and Three-cell NiCd or NiMH Operation

## **DESCRIPTION**

The Si9160 Controller for RF Power Amplifier Boost Converter is a fixed-frequency, pulse-width-modulated power conversion controller designed for use with the Si6801 application specific MOSFET. The Si9160 and the Si6801 are optimized for high efficiency switched-mode power conversion at 1 MHz and over. The device has an enable pin which can be used to put the converter in a low-current mode compatible with the standby mode of most cellular phones. A wide bandwidth feedback amplifier minimizes transient response time allowing the device to meet the instantaneous current demands of today's digital protocols. The input voltage range accommodates minimal size and cost battery pack configurations.

Frequency control in switching is important to noise management techniques in RF communications. The Si9160 is easily synchronized for high efficiency power conversion at frequencies in excess of 1 MHz.

Optimizing the controller and the synchronous FETs results in the highest conversion efficiency over a wide load range at the switching frequencies of interest (1 MHz or greater). It also minimizes the overshoot and gate ringing associated with drive current and gate charge mismatches.

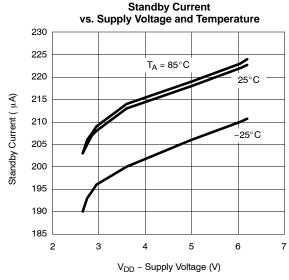

When disabled, the converter requires less than 330  $\mu A$ . This capability minimizes the impact of the converter on battery life when the phone is in the standby mode.

Finally, operating voltage is optimized for Lilon battery operation (2.7 V to 4.5 V) and can also be used with three-cell NiCd or NiMH (3 V to 3.6 V), as well as four-cell NiCd or NiMH (4 V to 4.8 V) battery packs.

The Si9160 is available in both standard and lead (Pb)-free packages.

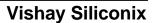

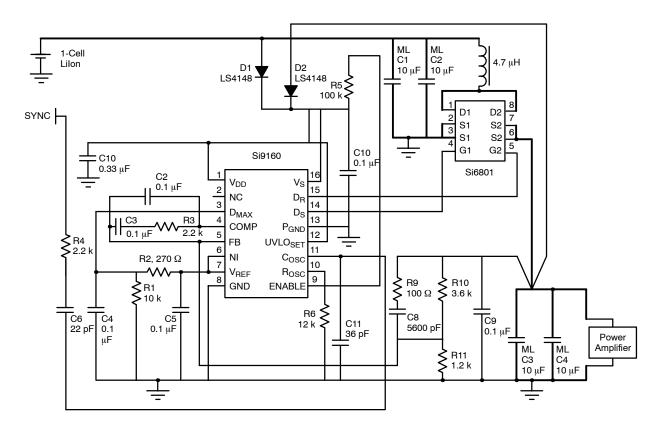

## **APPLICATION CIRCUIT**

Document Number: 70029 S-40700—Rev. H, 19-Apr-04

# **ABSOLUTE MAXIMUM RATINGS**

| Voltages Referenced to GND.                                                                           | Power Dissipation (Package) <sup>a</sup>                          |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| V <sub>DD</sub> , V <sub>S</sub>                                                                      | / 16-Pin TSSOP (Q Suffix) <sup>a, b</sup> 925 mW                  |

| P <sub>GND</sub>                                                                                      | I nermai impedance (CZ iA) <sup>a</sup>                           |

| Linear Inputs                                                                                         | 16-Pin ISSOP135°C/W                                               |

| Logic Inputs         -0.3 V to V <sub>DD</sub> +0.3           Peak Output Drive Current         350 n |                                                                   |

| Storage Temperature                                                                                   | Notes                                                             |

| Operating Junction Temperature                                                                        | a. Device mounted with all leads soldered of weided to 1 o board. |

<sup>\* .</sup> Exposure to Absolute Maximum rating conditions for extended periods may affect device reliability. Stresses above Absolute Maximum rating may cause permanent damage. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

| SPECIFICATIONS                        |                        |                                                                                                                                                          |                       |                                |      |       |      |  |

|---------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------|------|-------|------|--|

|                                       |                        | Test Conditions Unless Otherwise Specified <sup>a</sup> $2.7 \text{ V} \leq \text{V}_{DD}, \text{V}_{S} \leq 6.0 \text{ V}, \text{GND} = \text{P}_{GND}$ |                       | Limits<br>B Suffix -25 to 85°C |      |       |      |  |

| Parameter                             | Symbol                 |                                                                                                                                                          |                       | Minb                           | Тур  | Maxb  | Unit |  |

| Reference                             |                        |                                                                                                                                                          |                       |                                |      |       |      |  |

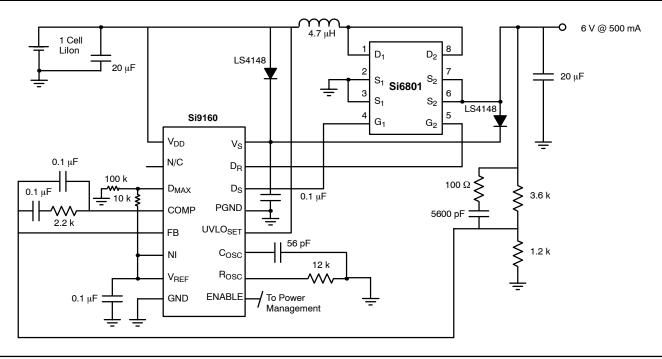

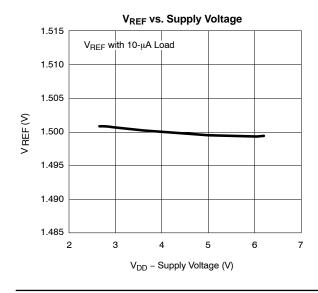

| 0.441/-4                              |                        | I <sub>REF</sub> = -10 μA                                                                                                                                |                       | 1.455                          |      | 1.545 | .,   |  |

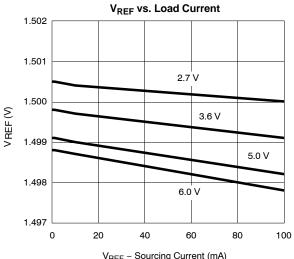

| Output Voltage                        | V <sub>REF</sub>       |                                                                                                                                                          | T <sub>A</sub> = 25°C | 1.477                          | 1.50 | 1.523 | - V  |  |

| Oscillator                            |                        |                                                                                                                                                          |                       |                                |      |       |      |  |

| Maximum Frequency <sup>c</sup>        | f <sub>MAX</sub>       | $V_{DD}$ = 5 V, $C_{OSC}$ = 47 pF, $R_{OSC}$ = 5.0 k $\Omega$                                                                                            |                       | 2.0                            |      |       | MHz  |  |

| Oscillator Frequency Accuracy         |                        | $V_{DD}$ = 3.0 V, $f_{OSC}$ = 1 MHz (nominal) $C_{OSC}$ = 100 pF, $R_{OSC}$ = 7.0 k $\Omega$ , $T_A$ = 25°C                                              |                       | -15                            |      | 15    | %    |  |

| R <sub>OSC</sub> Peak Voltage         | V <sub>ROSC</sub>      |                                                                                                                                                          |                       |                                | 1.0  |       | V    |  |

| Voltage Stability <sup>c</sup>        | A 515                  | $4 \text{ V} \leq \text{V}_{DD} \leq 6 \text{ V}$ , Ref to $5 \text{ V}$ , $\text{T}_{A} = 25^{\circ}\text{C}$ Referenced to $25^{\circ}\text{C}$        |                       | -8                             |      | 8     | - %  |  |

| Temperature Stability <sup>c</sup>    | Δf/f                   |                                                                                                                                                          |                       |                                | ±5   |       |      |  |

| Error Amplifier (C <sub>OSC</sub> = G | ND, OSC DISABLE        | ED)                                                                                                                                                      |                       |                                |      |       |      |  |

| Input Bias Current                    | I <sub>B</sub>         | V <sub>NI</sub> = V <sub>REF</sub> , V <sub>FB</sub> = 1.0 V                                                                                             |                       | -1.0                           |      | 1.0   | μΑ   |  |

| Open Loop Voltage Gain                | A <sub>VOL</sub>       |                                                                                                                                                          |                       | 47                             | 55   |       | dB   |  |

| Offset Voltage                        | V <sub>OS</sub>        | V <sub>NI</sub> = V <sub>REF</sub>                                                                                                                       |                       | -15                            | 0    | 15    | mV   |  |

| Unity Gain Bandwidth <sup>c</sup>     | BW                     |                                                                                                                                                          |                       |                                | 10   | İ     | MHz  |  |

| Output Current                        |                        | Source (V <sub>FB</sub> = 1 V, NI = V <sub>REF</sub> )                                                                                                   |                       |                                | -2.0 | -1.0  | mA   |  |

|                                       | Гоит                   | Sink ( $V_{FB} = 2 V$ , $NI = V_{REF}$ )                                                                                                                 |                       | 0.4                            | 0.8  |       |      |  |

| Power Supply Rejection <sup>c</sup>   | PSRR                   | 4 V < V <sub>DD</sub> < 6 V                                                                                                                              |                       |                                | 60   |       | dB   |  |

| UVLO <sub>SET</sub> Voltage Monitor   | •                      |                                                                                                                                                          |                       |                                |      |       |      |  |

| Under Voltage Lockout                 | V <sub>UVLOHL</sub>    | UVLO <sub>SET</sub> High                                                                                                                                 | to Low                | 0.85                           | 1.0  | 1.15  |      |  |

|                                       | V <sub>UVLOLH</sub>    | UVLO <sub>SET</sub> Low                                                                                                                                  | to High               |                                | 1.2  |       | _ V  |  |

| Hysteresis                            | V <sub>HYS</sub>       | Vuvlolh – Vuvlohl                                                                                                                                        |                       |                                | 200  |       | mV   |  |

| UVLO Input Current                    | I <sub>UVLO(SET)</sub> | V <sub>UVLO</sub> = 0 to V <sub>DD</sub>                                                                                                                 |                       | -100                           |      | 100   | nA   |  |

| SPECIFICATIONS                                    |                      |                                                                                                                                                          |                           |                             |      |                     |            |

|---------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------|------|---------------------|------------|

|                                                   |                      | Test Conditions Unless Otherwise Specified <sup>a</sup> $2.7 \text{ V} \leq \text{V}_{DD}, \text{V}_{S} \leq 6.0 \text{ V}, \text{GND} = \text{P}_{GND}$ |                           | Limits B Suffix -25 to 85°C |      |                     |            |

| Parameter                                         | Symbol               |                                                                                                                                                          |                           | Min <sup>b</sup>            | Тур  | Max <sup>b</sup>    | Unit       |

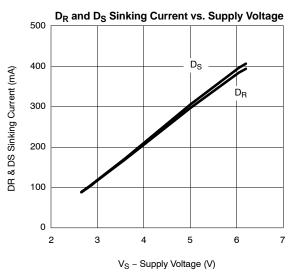

| Output Drive (D <sub>R</sub> and D <sub>S</sub> ) | ·                    |                                                                                                                                                          |                           | •                           |      |                     |            |

| Output High Voltage                               | V <sub>OH</sub>      | V <sub>DD</sub> = 2.7 V                                                                                                                                  | I <sub>OUT</sub> = -10 mA | 5.15                        | 5.2  |                     | V          |

| Output Low Voltage                                | V <sub>OL</sub>      | $V_{S} = 5.3 \text{ V}$                                                                                                                                  | I <sub>OUT</sub> = 10 mA  |                             | 0.06 | 0.15                | 7 V        |

| Peak Source Output Current                        | I <sub>SOURCE</sub>  | $V_{DD} = 2.7 \text{ V}, V_{S} = 5.3 \text{ V}$                                                                                                          |                           |                             | -300 | -250                |            |

| Peak Sink Output Current                          | I <sub>SINK</sub>    |                                                                                                                                                          |                           | 250                         | 300  |                     | mA         |

| Break-Before-Make                                 | t <sub>BBM</sub>     | V <sub>DD</sub> = 6.0 V                                                                                                                                  |                           |                             | 40   |                     | ns         |

| Logic                                             | <u>.</u>             |                                                                                                                                                          |                           |                             |      |                     |            |

| ENABLE Delay to Output                            | td <sub>EN</sub>     | ENABLE Rising to OUTPUT, V <sub>DD</sub> = 6.0 V                                                                                                         |                           |                             | 1.4  |                     | μs         |

| ENABLE Logic Low                                  | V <sub>ENL</sub>     |                                                                                                                                                          |                           |                             |      | 0.2 V <sub>DD</sub> | <b>.</b> , |

| ENABLE Logic High                                 | V <sub>ENH</sub>     |                                                                                                                                                          |                           | 0.8 V <sub>DD</sub>         |      |                     | V          |

| ENABLE Input Current                              | I <sub>EN</sub>      | ENABLE = 0 to V <sub>DD</sub>                                                                                                                            |                           | -1.0                        |      | 1.0                 | μА         |

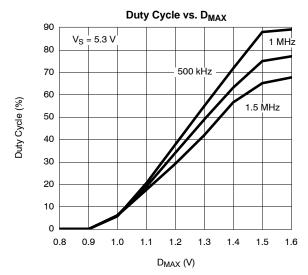

| Duty Cycle                                        | ·                    |                                                                                                                                                          |                           |                             |      |                     |            |

| Maximum Duty Cycle                                | CYCLE <sub>MAX</sub> | V <sub>DD</sub> = 6.0 V                                                                                                                                  |                           |                             | 80   | 95                  | %          |

| D <sub>MAX</sub> /SS Input Current                | I <sub>DMAX</sub>    | $D_{MAX} = 0 \text{ to } V_{DD}$                                                                                                                         |                           | -100                        |      | 100                 | nA         |

| Supply                                            |                      |                                                                                                                                                          |                           |                             |      |                     |            |

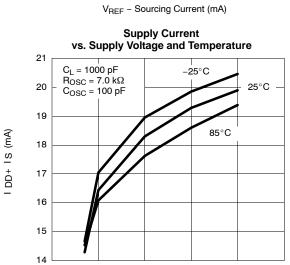

| 0 10 11 111                                       |                      | f <sub>OSC</sub> = 1 MHz                                                                                                                                 | V <sub>DD</sub> = 2.7 V   |                             | 1.1  | 1.5                 |            |

| Supply Current—Normal Mode                        | I <sub>DD</sub>      | $R_{OSC} = 7.0 \text{ k}\Omega$                                                                                                                          | V <sub>DD</sub> = 4.5 V   |                             | 1.6  | 2.3                 | mA         |

| Supply Current—Standby Mode                       |                      | ENABLE = Low                                                                                                                                             |                           |                             | 250  | 330                 | μА         |

#### Notes

es C<sub>STRAY</sub> < 5 pF on C<sub>OSC</sub>. After Start-Up, V<sub>DD</sub> of ≥ 3 V. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

Guaranteed by design, not subject to production testing.

## TYPICAL CHARACTERISTICS (25°C UNLESS OTHERWISE NOTED)

# TYPICAL CHARACTERISTICS (25°C UNLESS OTHERWISE NOTED)

6

7

5

4

V<sub>DD</sub> - Supply Voltage (V)

2

3

# TYPICAL CHARACTERISTICS (25°C UNLESS OTHERWISE NOTED)

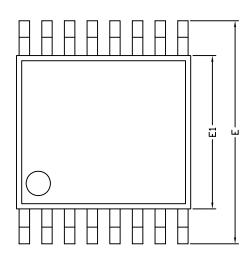

## PIN CONFIGURATION AND ORDERING INFORMATION

#### TSSOP-16 16 $V_{DD}$ I 1 $V_S$ 15 N/C 2 $D_{R}$ 14 $D_S$ $D_{MAX}$ COMP 13 $\mathsf{P}_{\mathsf{GND}}$ 4 **UVLO<sub>SET</sub>** FΒ NI 11 Cosc 10 $R_{OSC}$ $V_{REF}$ GND 8 **ENABLE**

Top View

Order Number: Si9160BQ-T1

# ORDERING INFORMATION Part Number Temperature Range Package Si9160BQ-T1 -25 to 85°C TSSOP-16

## **PIN DESCRIPTION**

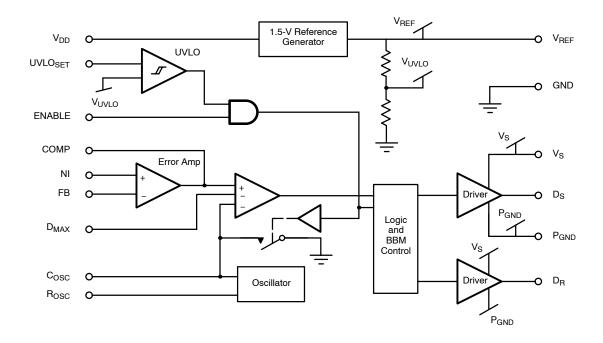

Pin 1: V<sub>DD</sub>

The positive power supply for all functional blocks except output driver. A bypass capacitor of 0.1  $\mu F$  (minimum) is recommended.

Pin 2: N/C

There is no internal connection to this pin.

Pin 3: D<sub>MAX</sub>

Used to set the maximum duty cycle.

Pin 4: COMP

This pin is the output of the error amplifier. A compensation network is connected from this pin to the FB pin to stabilize the system. This pin drives one input of the internal pulse width modulation comparator.

Pin 5: FB

The inverting input of the error amplifier. An external resistor divider is connected to this pin to set the regulated output voltage. The compensation network is also connected to this pin.

Pin 6: NI

The non-inverting input of the error amplifier. In normal operation it is externally connected to  $V_{\mbox{\scriptsize REF}}$  or an external reference.

Pin 7: V<sub>REF</sub>

This pin supplies a 1.5-V reference.

Pin 8: GND (Ground)

Pin 9: ENABLE

A logic high on this pin allows normal operation. A logic low places the chip in the standby mode. In standby mode, normal

operation is disabled, supply current is reduced, the oscillator stops, and  $D_{\rm S}$  goes low while  $D_{\rm B}$  goes high.

Pin 10: Rosc

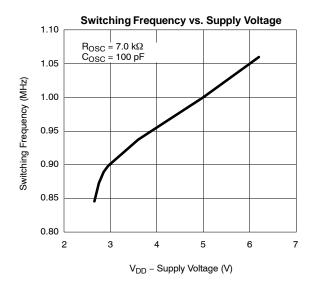

A resistor connected from this pin to ground sets the oscillator's capacitor ( $C_{OSC}$ ) charge and discharge current. See the oscillator section of the description of operation.

Pin 11: Cosc

An external capacitor is connected to this pin to set the oscillator frequency.

$$f_{OSC} \simeq \frac{0.70}{R_{OSC} \times C_{OSC}} \qquad \quad \text{(at V}_{DD} = 5.0 \text{ V)} \label{eq:fosc}$$

Pin 12: UVLO<sub>SET</sub>

This pin will place the chip in the standby mode if the  $UVLO_{SET}$  voltage drops below 1.2 V. Once the  $UVLO_{SET}$  voltage exceeds 1.2 V, the chip operates normally. There is a built-in hysteresis of 200 mV.

Pin 13: P<sub>GND</sub>

The negative return for the  $V_S$  supply.

Pin 14: D<sub>S</sub>

This CMOS push-pull output pin drives the external n-channel MOSFET. This pin will be low in the standby mode. A break-before-make function between  $D_{\rm S}$  and  $D_{\rm R}$  is built-in.

Pin 15: D<sub>R</sub>

This CMOS push-pull output pin drives the external p-channel MOSFET. This pin will be high in the standby mode. A break-before-make function between the  $D_S$  and  $D_R$  is built-in.

Pin 16: V<sub>S</sub>

The positive terminal of the power supply which powers the CMOS output drivers. A bypass capacitor is required.

# **FUNCTIONAL BLOCK DIAGRAM**

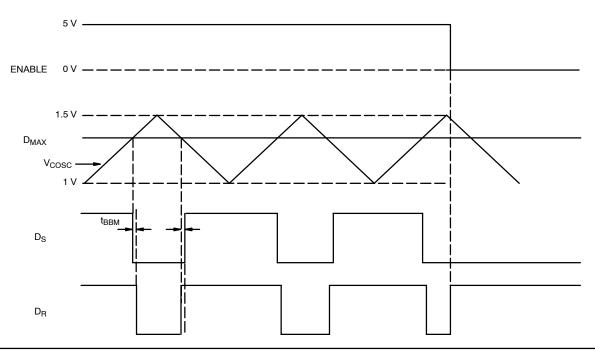

# **TIMING WAVEFORMS**

#### **OPERATION OF THE SI9160 BOOST CONVERTER**

The Si9160 combined with optimized complementary MOSFETs provides the ideal solution to small, high efficiency, synchronous boost power conversion. Optimized for a 1-cell lithium ion, or 3-cell to 4-cell Nickel metal hydride battery, it is capable of switching at frequencies of up to 2 MHz. Combined with the Si6801, a complimentary high-frequency MOSFET, efficiencies of over 90% are easily achieved in a very small area.

#### **PWM Controller**

The Si9160 implements a synchronous voltage mode PWM control topology and is especially designed for battery power conversion. Voltage-mode control results in the most efficient power conversion solution. Figure 1 below illustrates a schematic for a synchronous boost converter with an input range of 2.7 V to 5 V which covers the range of 1-cell Lilon and 3-cell or 4-cell NiMH/NiCd battery input respectively, and an output voltage of 6 V. Note the maximum input voltage is limited to the output voltage for a boost converter.

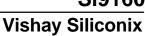

The switching frequency is determined by an external capacitor and resistor connected to  $C_{\rm osc}$  and  $R_{\rm osc}$  pins. The graph on page 5 in the Typical Characteristics section shows

the typical  $C_{\rm osc}$  and  $R_{\rm osc}$  values for various switching frequency. Si9160 oscillator frequency can be easily synchronized to external frequency as long as external switching frequency is higher than the internal oscillator frequency. The synchronization circuit is a series resistor and capacitor fed into the  $C_{\rm osc}$  pin of the Si9160. The synchronization pulse should be greater than 1.5 V in amplitude and a near square wave pulsed clock. Figure 1 shows typical values for the synchronization components.

#### Startup

Designed to operate with single cell Lithium Ion battery voltage, the Si9160 has an operating range of 2.7 V to 6.0 V. During start-up, the device requires 3.0 V to guarantee proper operation, although it will typically start up at less than 2.2 V. Once powered, Si9160 will continue to operate until the voltage at  $V_{DD}$  is 2.7 V; at this point, the battery is basically dead. During start-up, power for the chip is provided by the battery through schottky diode D1 to  $V_{DD}$  and  $V_{S}$  pins. Once the converter is fully operating, supply power is provided by the converter output through diode D2, which overrides the D1 diode. This self perpetuating method of powering further improves the converter efficiency by utilizing higher gate drive to lower the on-resistance loss of the MOSFET.

FIGURE 1. Si9160 Boost Converter

Another benefit of powering from the output voltage is it provides minimum load on the converter. This prevents the converter from skipping frequency pulses typically referred to as Burst or Pulse-Skipping modes. Pulse skipping mode could be dangerous, especially if it generates noise in RF, IF, or signal processing frequency bands.

## **Enable and Under Voltage Shutdown**

The Si9160 is designed with programmable under-voltage lockout and enable features. These features give designers flexibility to customize the converter design. The under-voltage lockout threshold is 1.2 V. With a simple resistor divider from  $V_{DD},\,Si9160$  can be programmed to turn-on at any  $V_{DD}$  voltage. The ENABLE pin, a TTL logic compatible input, allows remote shutdown as needed.

#### Gate Drive and MOSFETs

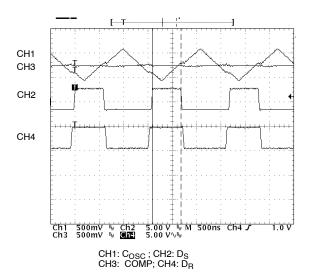

The gate drive section is designed to drive the high-side p-channel switch and low-side n-channel switch. The internal 40 ns break-before-make (BBM) timing prevents both MOSFETs from turning-on simultaneously. The BBM circuit monitors both drive voltages, once the gate-to-source voltage drops below 2.5 V, the other gate drive is delayed 40-ns before it is allowed to drive the external MOSFET (see Figure 2 for timing diagram). This smart gate drive control provides additional assurance that shoot-through current will not occur.

FIGURE 2. Gate Drive Timing Diagrams

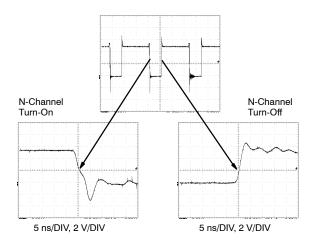

The MOSFET used is the Si6801, an n- and p-channel in a single package TSSOP-8. The Si6801 is optimized to have very low gate charge and gate resistance. This results in a great reduction in gate switching power losses. The average time to switch on and off a MOSFET in a conventional structure is about 20 ns. The Si6801 will switch on and off in < 5 ns, see Figure 3.

#### Note the Speed

These MOSFETs have switching speeds of <5 ns. This high speed is due to the fast, high current output drive of the Si9160 and the optimized gate charge of the Si6801.

FIGURE 3. Gate Switching Times

## **Stability Components**

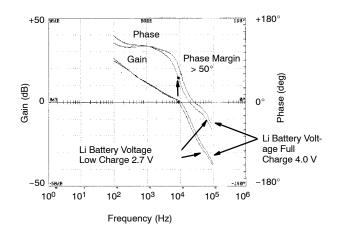

A voltage mode boost converter is normally stabilized with simple lag compensation due to the additional 90° phase lag introduced by the additional right hand plane zero, as well as having a duty factor dependent resonant frequency for the output filter. The stability components shown in Figure 1 have been chosen to ensure stability under all battery conditions while maintaining maximum transient response. To do this we have used a 2-pole-zero pair configuration (type 3 amplifier configuration). Figure 4 shows the bode plot for the above circuit, maintaining > 50° phase margin over the entire battery voltage range.

FIGURE 4. Stability, with 1-cell Li battery input, 5 V @ 600-mA output.

# VISHAY

#### **Energy Storage Components**

The input and output ripple voltage is determined by the switching frequency, and the inductor and capacitor values. The higher the frequency, inductance, or capacitance values, the lower the ripple. The efficiency of the converter is also improved with higher inductance by reducing the conduction loss in the switch, synchronous rectifier, and the inductor itself. In the past, Tantalum was the preferred material for the input and output capacitors. Now, with 2-MHz switching frequencies, Tantalum capacitors are being replaced with smaller surface mount ceramic capacitors. Ceramic capacitors have almost no equivalent series resistance (ESR). Tantalum capacitors have at least  $0.1-\Omega$  ESR. By reducing ESR, converter efficiency is improved while decreasing the input and output ripple voltage. With ceramic capacitors, output ripple voltage is a function of capacitance only. The equation for determining output capacitance is stated below.

$$C = \frac{I_{OUT} \cdot (V_{OUT} - V_{IN})}{V_{OUT} \cdot \Delta V_{BIPPLE} \cdot f}$$

I<sub>OUT</sub> = output dc load current

$V_{OUT}$  = output voltage  $V_{IN}$  = input voltage

$\Delta V_{RIPPLE}$  = desired output ripple voltage

f = switching frequency

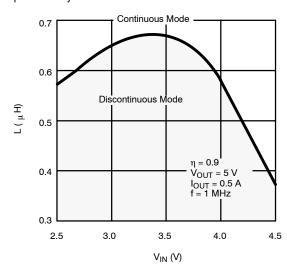

The inductance value for the converter is a function of the desired ripple voltage and efficiency as stated below. In order to keep the ripple small and improve efficiency, the inductance needs to be large enough to maintain continuous current mode. Continuous current mode has lower RMS current compared to discontinuous current mode since the peak current is lower. This lowers the conduction loss and improves

efficiency. The equation that shows the critical inductance which separates continuous and discontinuous current mode at any given output current is stated below. This equation is also plotted in Figure 5 as a function of input voltage.

Designed with small surface mount inductors and capacitors, the Si9160 solution can fit easily within a small space such as a battery pack. Another distinct advantage of a smaller converter size is that it reduces the noise generating area by reducing the high current path; therefore radiated and conducted noise is less likely to couple into sensitive circuits.

$$L \; = \; \frac{V_{IN}^{\;\;2} \; \cdot \; \left(V_{OUT}^{\;\;} - V_{IN}^{\;\;}\right) \; \cdot \; \eta}{2 \; \cdot \; V_{OUT}^{\;\;2} \; \cdot \; I_{OUT}^{\;\;} \; \cdot \; f} \label{eq:loss}$$

η = efficiency

FIGURE 5. Continuous and Discontinuous Inductance Curve

## **RESULTS SECTION**

The following section shows the actual results obtained with the circuit diagram shown in Figure 1.

## **Efficiency**

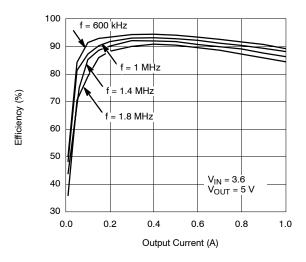

The Figure 6 shows the efficiency of the above design at various constant switching frequencies. The frequencies were generated using a 3-V square wave of the desired frequency to the sync input to the circuit. The input voltage to the circuit is 3.6-V dc.

#### **Output Noise**

The noise generated by a dc-dc converter is always an issue within the mobile phone. The Si9160 offers two benefits.

The noise spectrum is a constant, i.e. no random noise or random harmonic generation.

The switching fundamental can be synchronized to a known frequency, e.g. 812.5 kHz which is  $^{1}/_{16}$ -th of the GSM/DCS system clock, 1.23 MHz which is the channel spacing frequency for CDMA, etc.

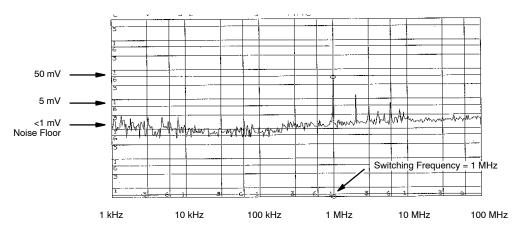

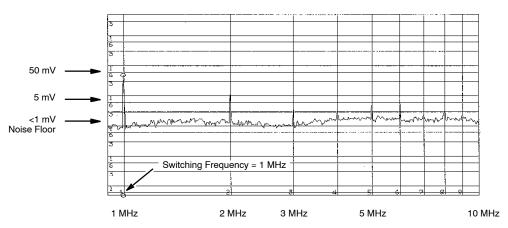

Figures 7 through 9 show the output noise and output spectrum analysis.

#### **Output Noise Spectrum**

Note there is no random noise, only switching frequency harmonics. This is very good news for the RF stages, where an unknown, or random noise spectrum will cause problems.

FIGURE 6. Efficiency of Si9160 and Si6801 Boost converter at various fixed frequencies

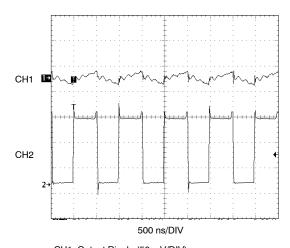

CH1: Output Ripple (50 mV/DIV) CH2: P- and N-Channel Drain Voltage (2 V/DIV)

FIGURE 7. Output noise of the Si9160 demo board

FIGURE 8. Spectrum response for the Si9160 demo board output voltage

FIGURE 9. Higher resolution of noise spectrum

# Conclusion

Switching at high, known frequencies results in a smaller footprint while maintaining high efficiency. Efficiencies at high switching frequencies can be improved by using Si6801

optimized low gate charge and low gate resistance MOSFET. Additionally, synchronization to an external high frequency clock eliminates or greatly reduces any radio interference concerns and pushes harmonics out beyond signal processing frequencies.

# **Legal Disclaimer Notice**

Vishay

# **Notice**

Specifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.

www.vishay.com Revision: 08-Apr-05

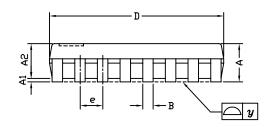

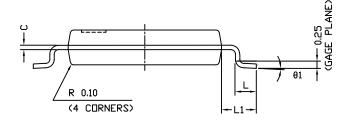

**TSSOP: 16-LEAD**

|                           | DIMENSIONS IN MILLIMETERS |          |      |  |  |

|---------------------------|---------------------------|----------|------|--|--|

| Symbols                   | Min                       | Nom      | Max  |  |  |

| А                         | =                         | 1.10     | 1.20 |  |  |

| A1                        | 0.05                      | 0.10     | 0.15 |  |  |

| A2                        | =                         | 1.00     | 1.05 |  |  |

| В                         | 0.22                      | 0.28     | 0.38 |  |  |

| С                         | =                         | 0.127    | -    |  |  |

| D                         | 4.90                      | 5.00     | 5.10 |  |  |

| E                         | 6.10                      | 6.40     | 6.70 |  |  |

| E1                        | 4.30                      | 4.40     | 4.50 |  |  |

| е                         | -                         | 0.65     | -    |  |  |

| L                         | 0.50                      | 0.60     | 0.70 |  |  |

| L1                        | 0.90                      | 1.00     | 1.10 |  |  |

| у                         | =                         | -        | 0.10 |  |  |

| θ1                        | 0°                        | 3°       | 6°   |  |  |

| ECN: S-61920-Rev. D. 23-0 | Oct-06                    | <u> </u> |      |  |  |

DWG: 5624

Document Number: 74417 www.vishay.com 23-Oct-06

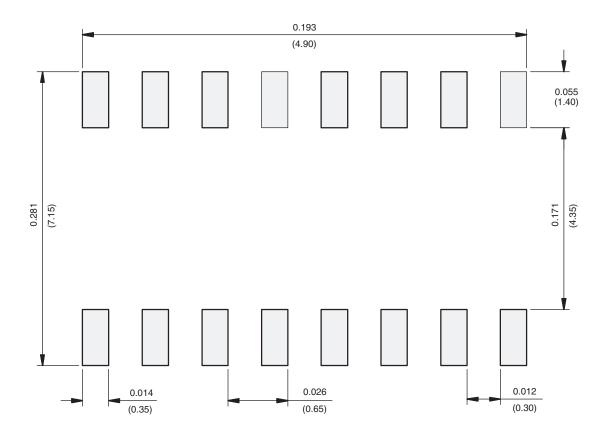

## **RECOMMENDED MINIMUM PAD FOR TSSOP-16**

Recommended Minimum Pads Dimensions in inches (mm)

# **Legal Disclaimer Notice**

Vishay

# **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

# **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.

Revision: 02-Oct-12 Document Number: 91000