# RX111 Group

User's Manual: Hardware

RENESAS 32-Bit MCU RX Family / RX100 Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics

does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages

incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### NOTES FOR CMOS DEVICES

- (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN: Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between VIL (MAX) and VIH (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between VIL (MAX) and VIH (MIN).

- (2) HANDLING OF UNUSED INPUT PINS: Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

- (3) PRECAUTION AGAINST ESD: A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

- (4) STATUS BEFORE INITIALIZATION: Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

- (5) POWER ON/OFF SEQUENCE: In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current. The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

- (6) INPUT OF SIGNAL DURING POWER OFF STATE: Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

#### **General Precautions in the Handling of MPU/MCU Products**

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access

these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

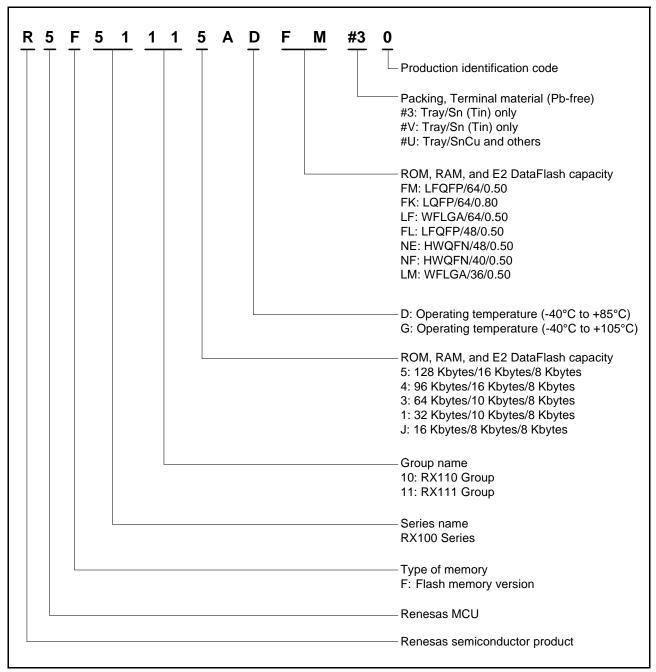

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

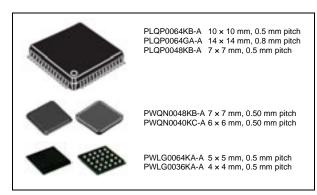

# Specification Differences between Products

There are the following specification differences in these MCU products depending on the package.

Table 1

Specification Differences Depending on Packages

| Chapter                       |                             | Specification Differences     |                                                                                                                 |  |

|-------------------------------|-----------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| One                           | iptei                       | Products with 40 pins or less | Products with 48 pins or more                                                                                   |  |

| 9.Clock Generation<br>Circuit | 9.8.4 Notes on<br>Sub-Clock |                               | At a cold start, initialize the sub-clock control circuit regardless of whether the sub-clock is in use or not. |  |

## How to Use This Manual

## 1. Objective and Target Users

This manual was written to explain the hardware functions and electrical characteristics of this LSI to the target users, i.e. those who will be using this LSI in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logic circuits, and microcomputers.

This manual is organized in the following items: an overview of the product, descriptions of the CPU, system control functions, and peripheral functions, electrical characteristics of the device, and usage notes.

When designing an application system that includes this LSI, take all points to note into account. Points to note are given in their contexts and at the final part of each section, and in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier versions. It does not cover all revised items. For details on the revised points, see the actual locations in the manual.

The following documents have been prepared for the RX111 Group. Before using any of the documents, please visit our website to verify that you have the most up-to-date available version of the document.

| Document Type               | Contents                                                                                                                                                       | Document Title                            | Document No.  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------|

| DataSheet                   | Overview of hardware and electrical characteristics                                                                                                            | _                                         | _             |

| User's Manual:<br>Hardware  | Hardware specifications (pin assignments, memory maps, peripheral specifications, electrical characteristics, and timing charts) and descriptions of operation | RX111 Group<br>User's Manual:<br>Hardware | This document |

| User's Manual:<br>Software  | Detailed descriptions of the CPU and instruction set                                                                                                           | RX Family<br>User's Manual:<br>Software   | REJ09B0435    |

| Application Note            | Examples of applications and sample programs                                                                                                                   | _                                         | _             |

| Renesas<br>Technical Update | Preliminary report on the specifications of a product, document, etc.                                                                                          | _                                         | _             |

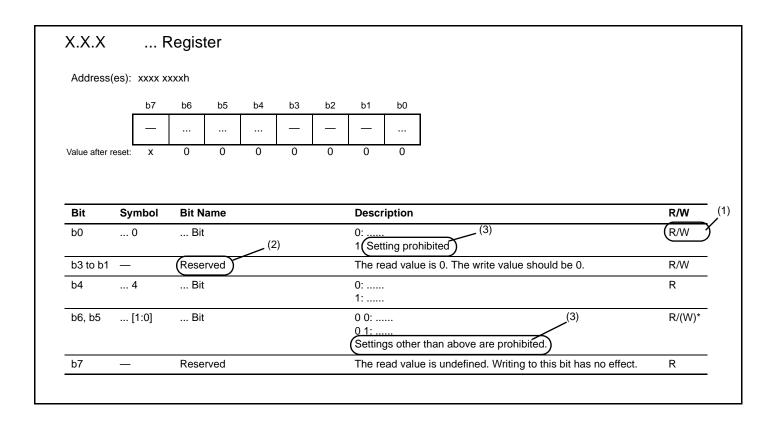

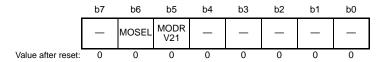

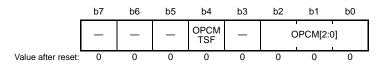

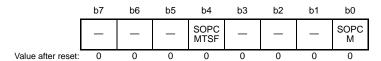

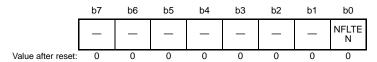

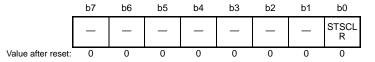

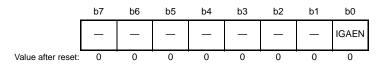

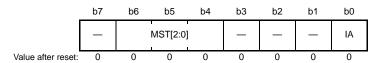

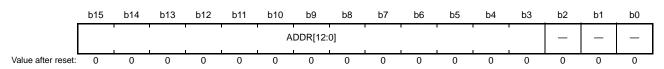

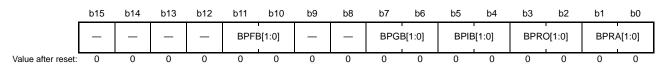

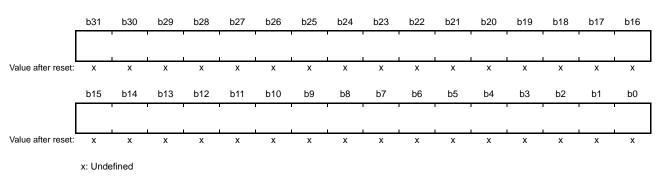

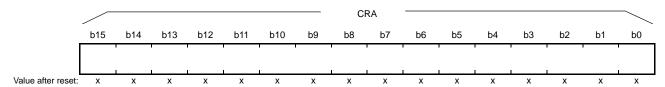

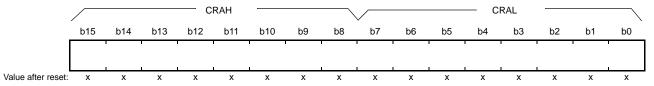

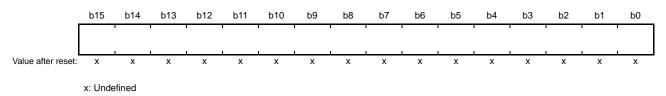

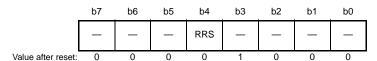

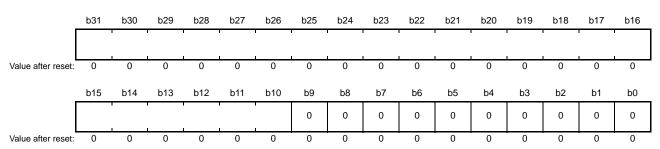

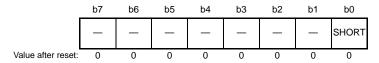

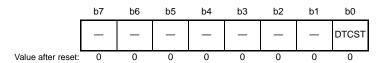

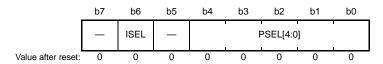

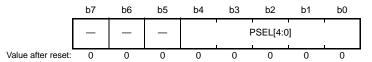

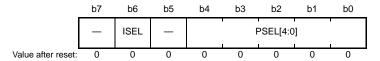

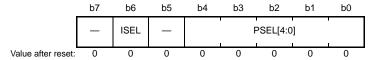

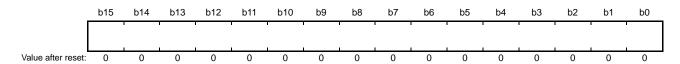

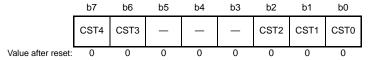

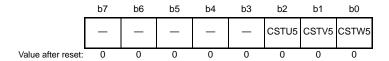

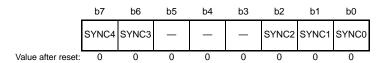

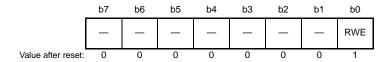

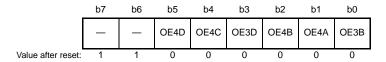

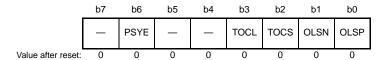

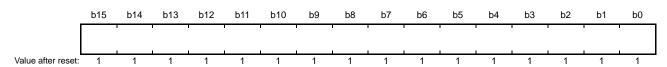

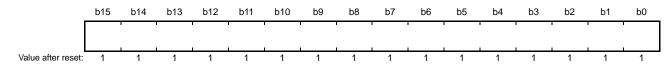

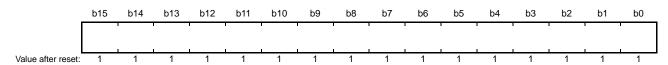

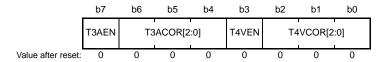

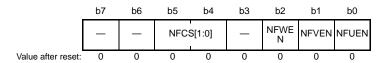

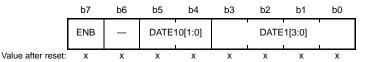

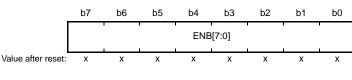

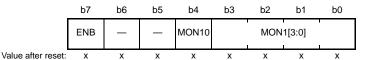

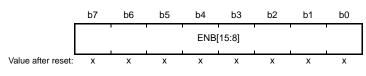

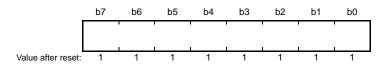

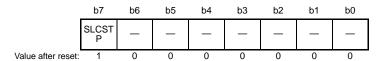

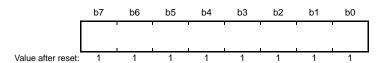

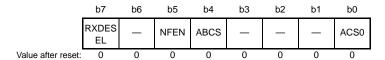

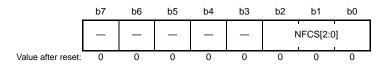

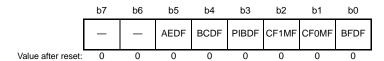

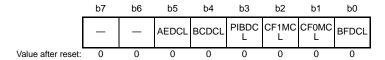

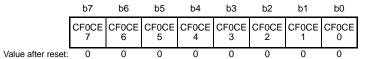

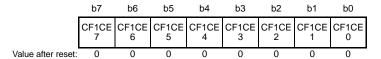

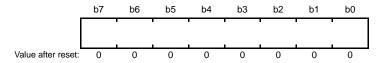

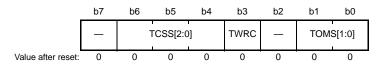

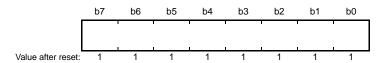

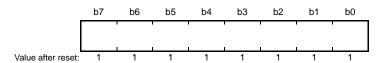

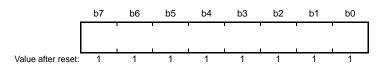

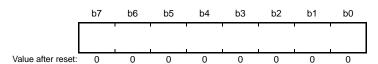

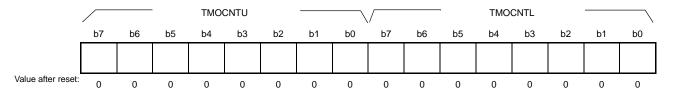

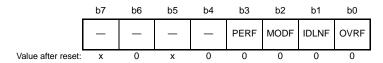

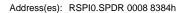

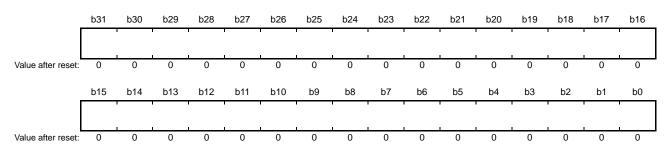

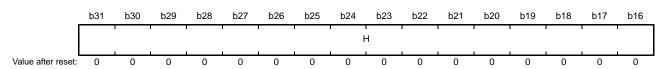

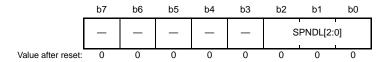

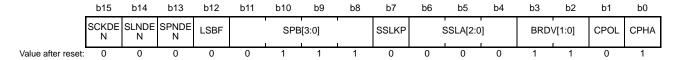

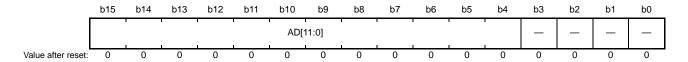

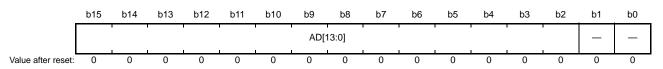

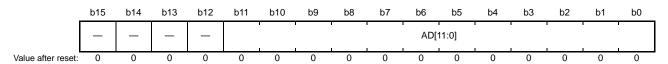

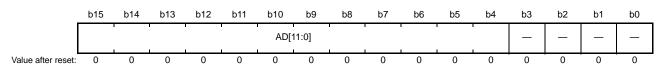

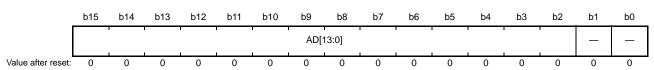

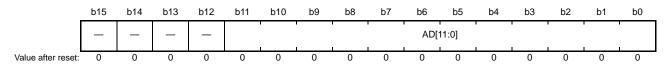

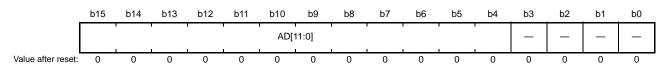

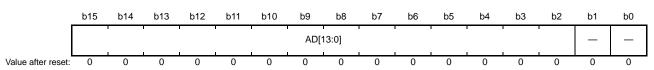

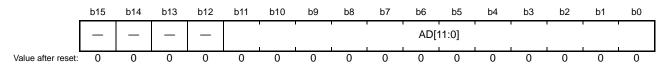

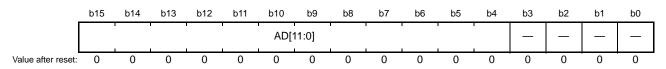

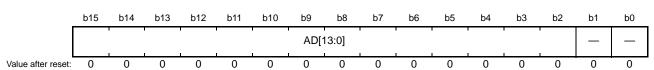

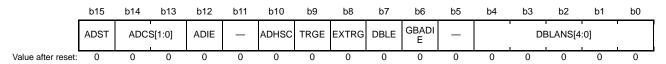

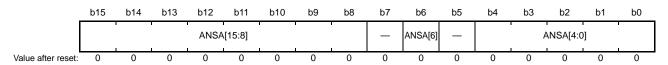

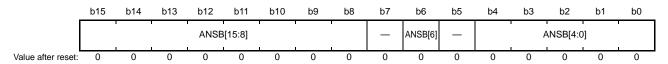

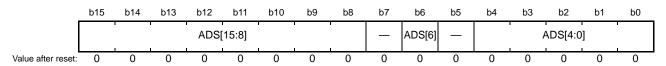

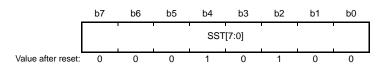

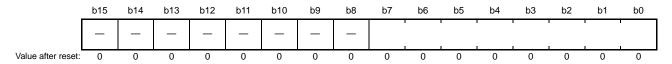

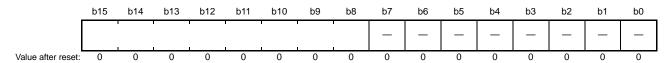

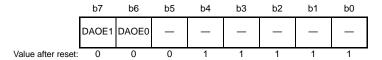

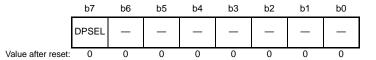

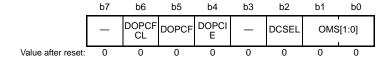

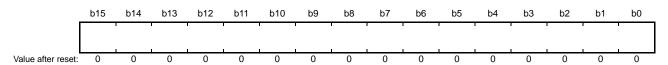

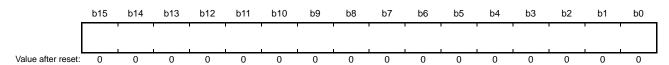

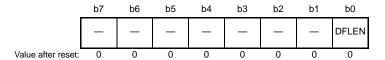

## 2. Description of Registers

Each register description includes a bit chart, illustrating the arrangement of bits, and a table of bits, describing the meanings of the bit settings. The standard format and notation for bit charts and tables are described below.

(1) R/W: The bit or field is readable and writable.

R/(W): The bit or field is readable and writable. However, writing to this bit or field has some limitations. For details on the limitations, see the description or notes of respective registers.

R: The bit or field is readable. Writing to this bit or field has no effect.

- (2) Reserved. Make sure to use the specified value when writing to this bit or field; otherwise, the correct operation is not guaranteed.

- (3) Setting prohibited. The correct operation is not guaranteed if such a setting is performed.

## 3. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment Bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connect                                  |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

All trademarks and registered trademarks are the property of their respective owners.

SuperFlash® is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

# Contents

| Fe | atures  |                                                                                   | 37 |

|----|---------|-----------------------------------------------------------------------------------|----|

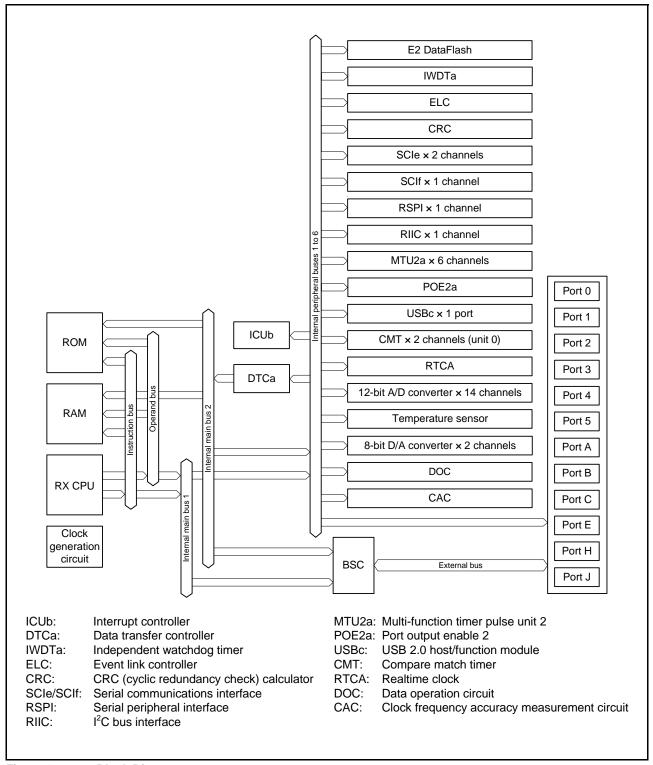

| 1. | Overvie | w                                                                                 | 38 |

|    | 1.1 O   | Outline of Specifications                                                         | 38 |

|    | 1.2 L   | ist of Products                                                                   | 42 |

|    | 1.3 B   | lock Diagram                                                                      | 45 |

|    | 1.4 P   | in Functions                                                                      | 46 |

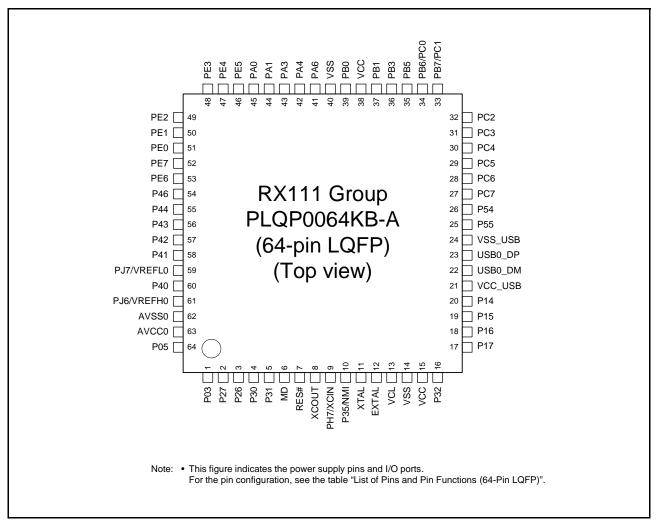

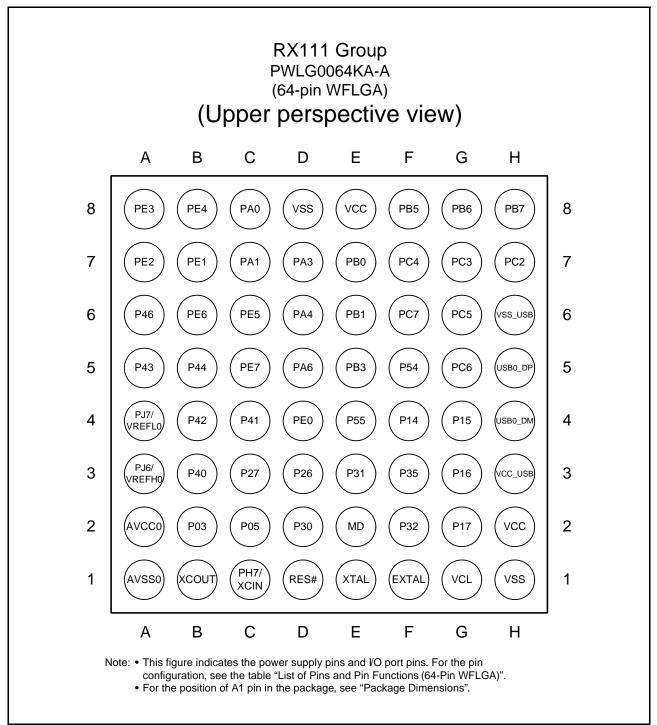

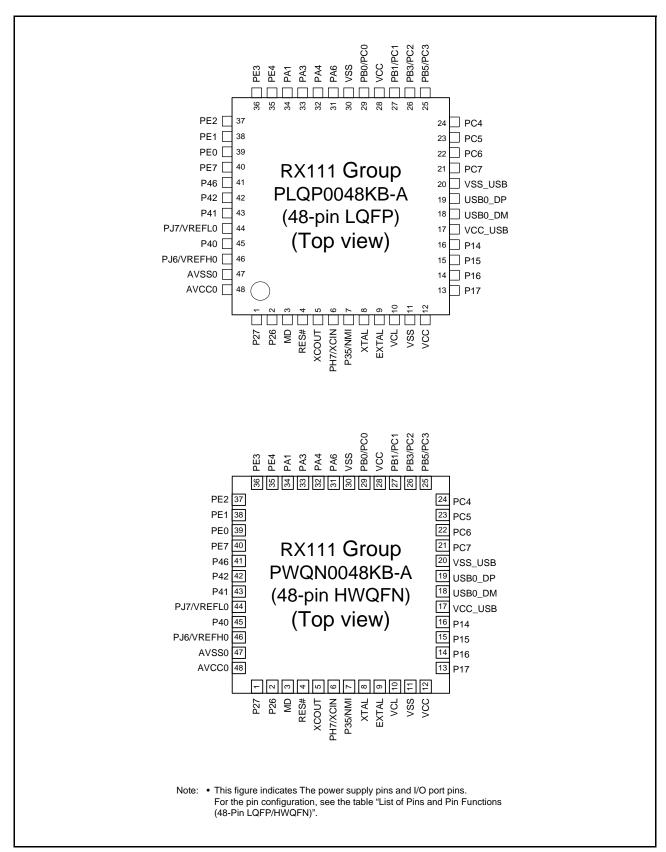

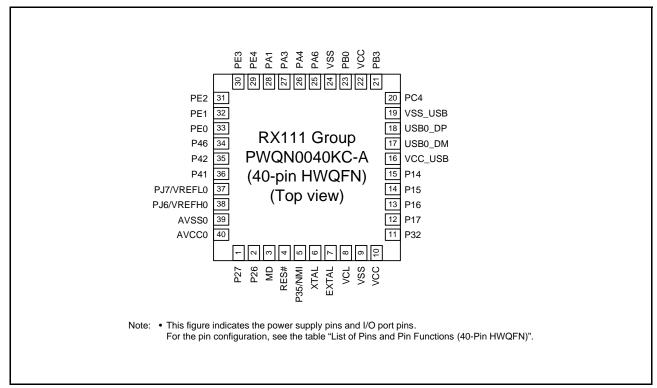

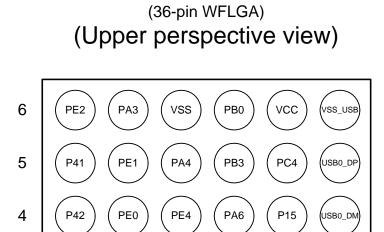

|    | 1.5 P   | in Assignments                                                                    | 49 |

| 2. | CPU     |                                                                                   | 63 |

|    | 2.1 F   | eatures                                                                           | 63 |

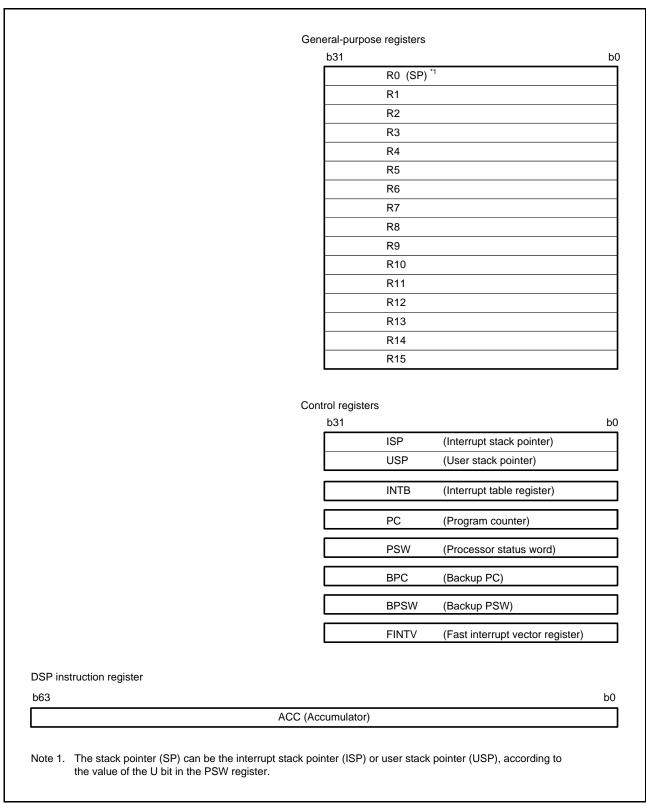

|    | 2.2 R   | egister Set of the CPU                                                            | 64 |

|    | 2.2.1   | General-Purpose Registers (R0 to R15)                                             | 65 |

|    | 2.2.2   | Control Registers                                                                 | 65 |

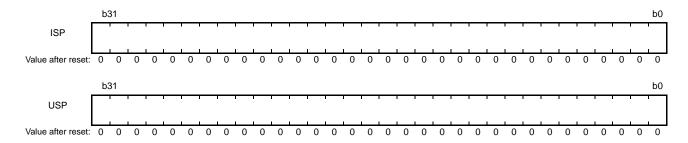

|    | 2.2.2   | 2.1 Interrupt Stack Pointer (ISP)/User Stack Pointer (USP)                        | 66 |

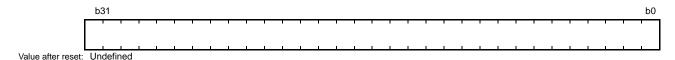

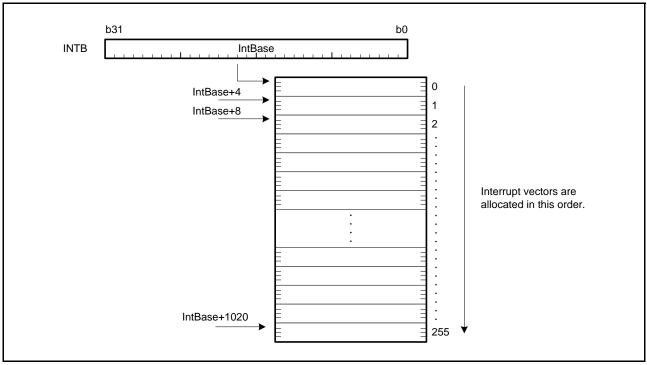

|    | 2.2.2   | 2.2 Interrupt Table Register (INTB)                                               | 66 |

|    | 2.2.2   | Program Counter (PC)                                                              | 66 |

|    | 2.2.2   | 2.4 Processor Status Word (PSW)                                                   | 67 |

|    | 2.2.2   | 2.5 Backup PC (BPC)                                                               | 68 |

|    | 2.2.2   | 2.6 Backup PSW (BPSW)                                                             | 69 |

|    | 2.2.2   | 2.7 Fast Interrupt Vector Register (FINTV)                                        | 69 |

|    | 2.2.3   | Register Associated with DSP Instructions                                         | 69 |

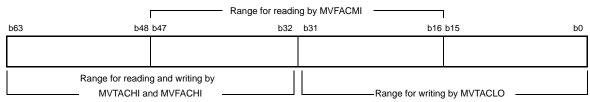

|    | 2.2.3   | 3.1 Accumulator (ACC)                                                             | 69 |

|    | 2.3 P   | rocessor Mode                                                                     | 70 |

|    | 2.3.1   | Supervisor Mode                                                                   | 70 |

|    | 2.3.2   | User Mode                                                                         | 70 |

|    | 2.3.3   | Privileged Instruction                                                            | 70 |

|    | 2.3.4   | Switching between Processor Modes                                                 | 70 |

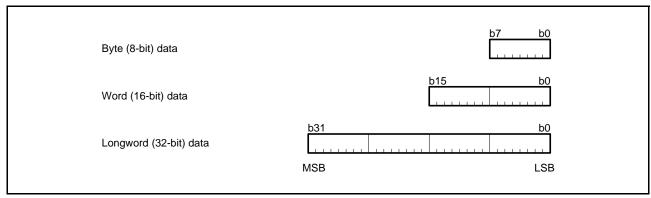

|    | 2.4 D   | Pata Types                                                                        | 71 |

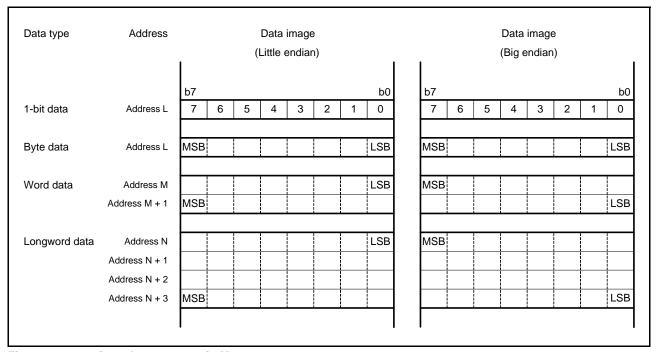

|    | 2.5 E   | ndian                                                                             | 71 |

|    | 2.5.1   | Switching the Endian                                                              | 71 |

|    | 2.5.2   | Access to I/O Registers                                                           | 75 |

|    | 2.5.3   | Notes on Access to I/O Registers                                                  | 75 |

|    | 2.5.4   | Data Arrangement                                                                  | 75 |

|    | 2.5.4   | Data Arrangement in Registers                                                     | 75 |

|    | 2.5.4   | Data Arrangement in Memory                                                        | 76 |

|    | 2.5.5   | Notes on the Allocation of Instruction Codes                                      |    |

|    | 2.6 V   | ector Table                                                                       | 77 |

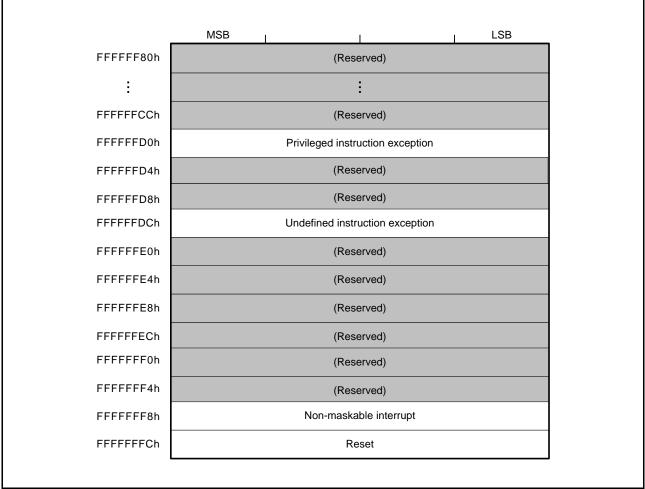

|    | 2.6.1   | Fixed Vector Table                                                                | 77 |

|    | 2.6.2   | Relocatable Vector Table                                                          | 78 |

|    | 2.7 O   | peration of Instructions                                                          | 79 |

|    | 2.7.1   | Data Prefetching by the RMPA Instruction and the String-Manipulation Instructions | 79 |

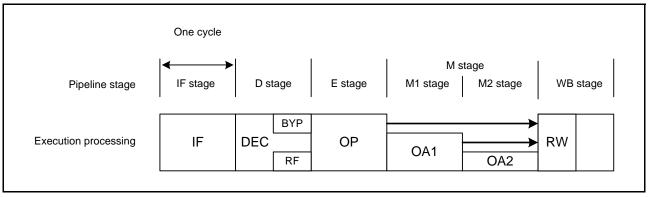

|    | 2.8 P   | ipeline                                                                           | 79 |

|    | 2.8.1 | Overview                                                                            | 79  |

|----|-------|-------------------------------------------------------------------------------------|-----|

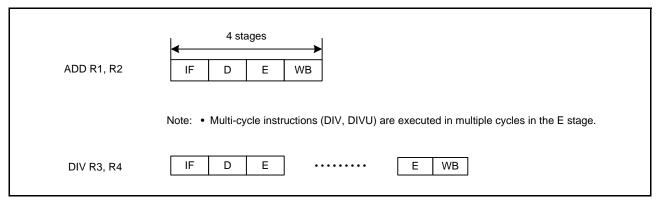

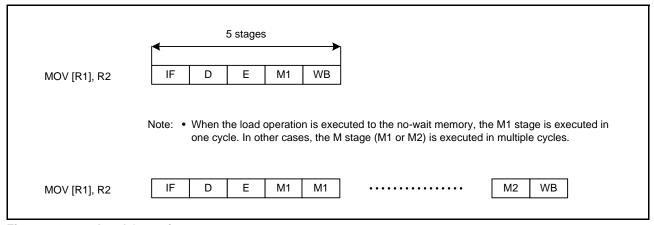

|    | 2.8.2 | Instructions and Pipeline Processing                                                | 81  |

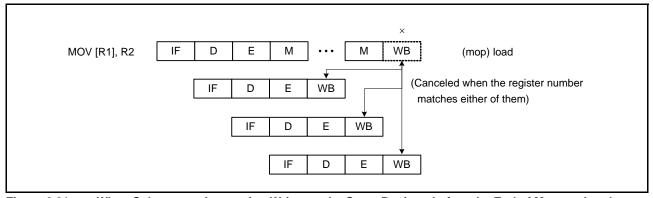

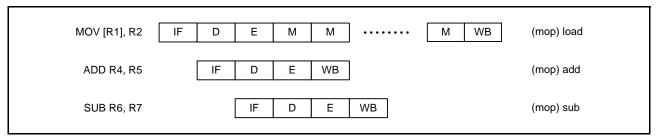

|    | 2.    | 3.2.1 Instructions Converted into Single Micro-Operation and Pipeline Processing    | 81  |

|    | 2.    | 3.2.2 Instructions Converted into Multiple Micro-Operations and Pipeline Processing | ;83 |

|    | 2.    | 3.2.3 Pipeline Basic Operation                                                      | 86  |

|    | 2.8.3 | Calculation of the Instruction Processing Time                                      | 88  |

|    | 2.8.4 | Numbers of Cycles for Response to Interrupts                                        | 89  |

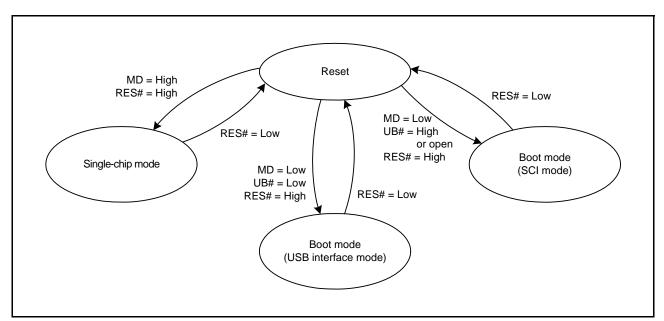

| 3. | Opera | ting Modes                                                                          | 90  |

|    | 3.1   | Operating Mode Types and Selection                                                  | 90  |

|    | 3.2   | Register Descriptions                                                               | 91  |

|    | 3.2.1 | Mode Monitor Register (MDMONR)                                                      | 91  |

|    | 3.2.2 | System Control Register 1 (SYSCR1)                                                  | 92  |

|    | 3.3   | Details of Operating Modes                                                          | 93  |

|    | 3.3.1 | Single-Chip Mode                                                                    | 93  |

|    | 3.3.2 | Boot Mode                                                                           | 93  |

|    | 3.    | Boot Mode (USB Interface Mode)                                                      | 93  |

|    | 3.    | 3.2.2 Boot Mode (SCI Mode)                                                          | 93  |

|    | 3.4   | Transitions of Operating Modes                                                      |     |

|    | 3.4.1 | Mode Setting Pin Levels and Operating Mode Transitions                              | 93  |

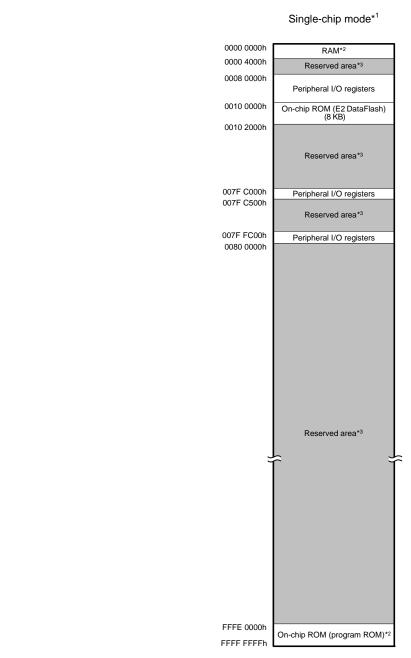

| 4. | Addre | ss Space                                                                            | 94  |

|    | 4.1   | Address Space                                                                       | 94  |

| 5. | I/O R | gisters                                                                             | 96  |

|    | 5.1   | I/O Register Addresses (Address Order)                                              | 98  |

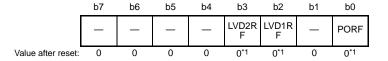

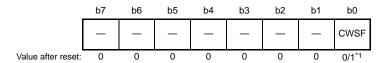

| 6. | Rese  | S                                                                                   | 114 |

|    | 6.1   | Overview                                                                            | 114 |

|    | 6.2   | Register Descriptions                                                               | 116 |

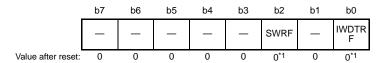

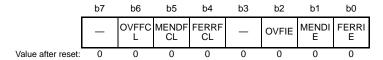

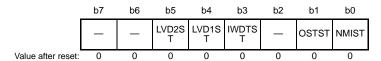

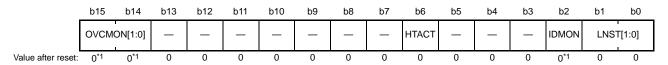

|    | 6.2.1 | Reset Status Register 0 (RSTSR0)                                                    | 116 |

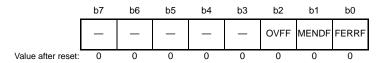

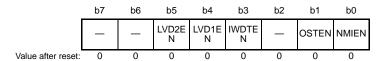

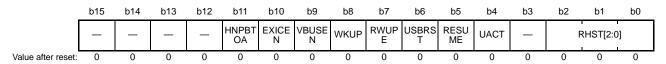

|    | 6.2.2 | Reset Status Register 1 (RSTSR1)                                                    | 117 |

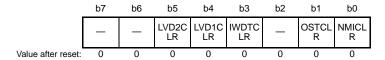

|    | 6.2.3 | Reset Status Register 2 (RSTSR2)                                                    | 118 |

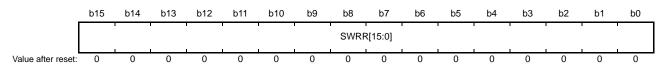

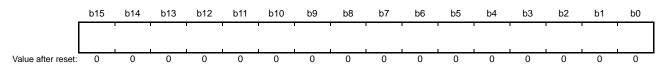

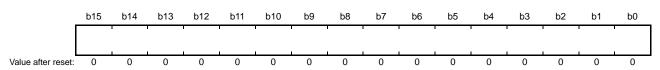

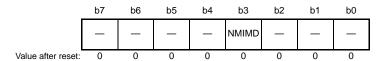

|    | 6.2.4 | Software Reset Register (SWRR)                                                      | 119 |

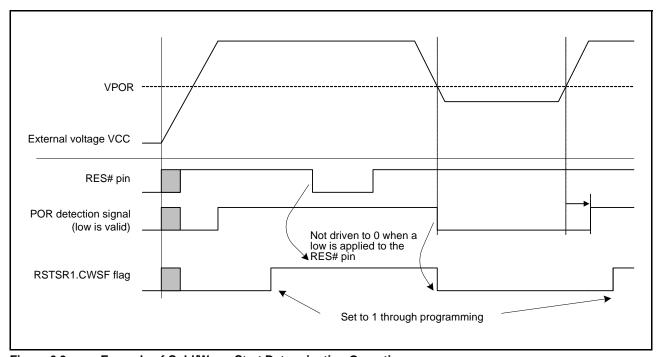

|    | 6.3   | Operation                                                                           | 120 |

|    | 6.3.1 | RES# Pin Reset                                                                      |     |

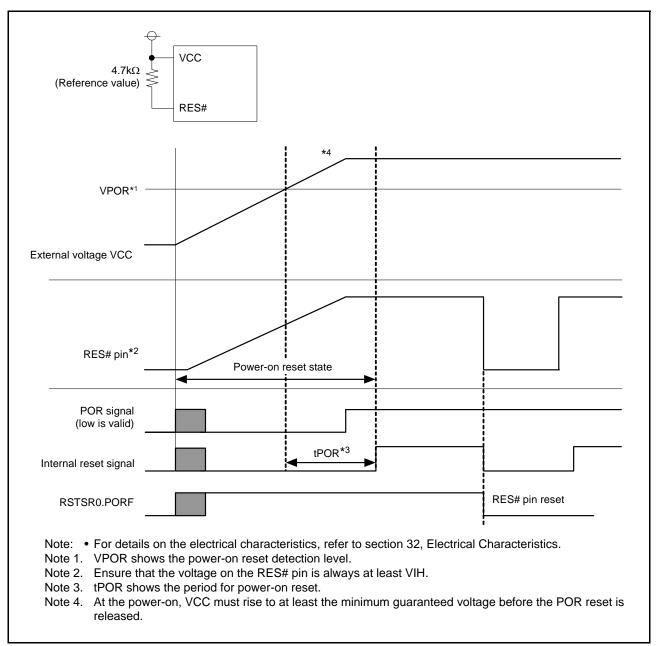

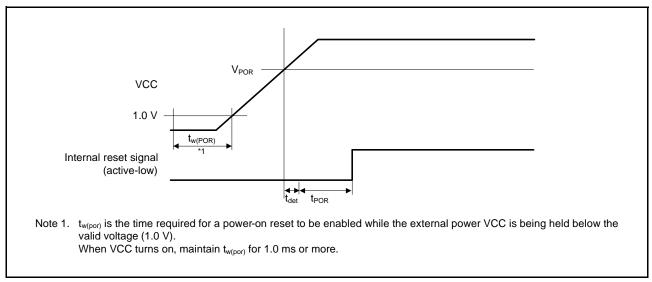

|    | 6.3.2 | Power-On Reset                                                                      | 120 |

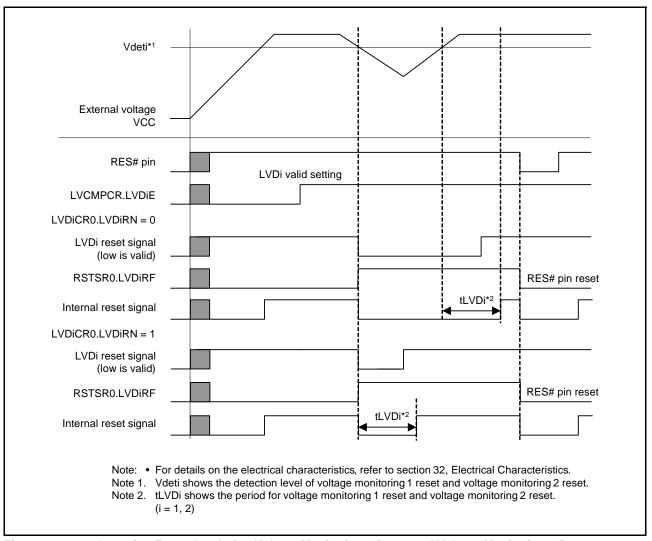

|    | 6.3.3 | Voltage Monitoring 1 Reset and Voltage Monitoring 2 Reset                           |     |

|    | 6.3.4 | Independent Watchdog Timer Reset                                                    | 123 |

|    | 6.3.5 | Software Reset                                                                      | 124 |

|    | 6.3.6 | Determination of Cold/Warm Start                                                    |     |

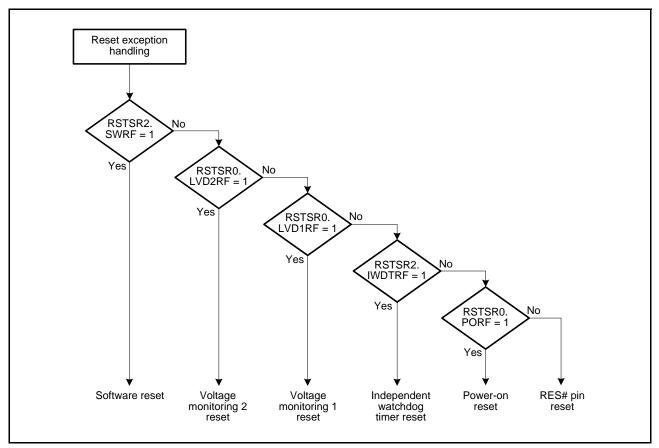

|    | 6.3.7 | Determination of Reset Generation Source                                            | 125 |

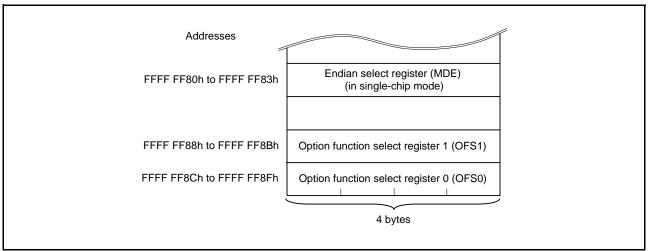

| 7. | Optio | -Setting Memory                                                                     | 126 |

|    | 7.1   | Overview                                                                            | 126 |

|    | 7.2   | Register Descriptions                                                               | 127 |

|    | 7.2.1  | Option Function Select Register 0 (OFS0)                       | 127 |

|----|--------|----------------------------------------------------------------|-----|

|    | 7.2.2  | Option Function Select Register 1 (OFS1)                       | 129 |

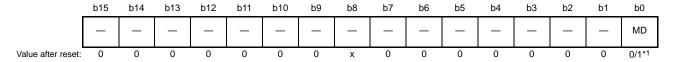

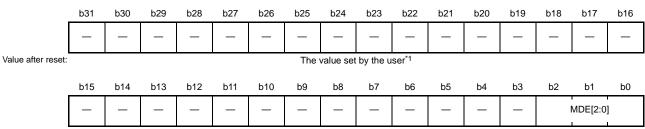

|    | 7.2.3  | Endian Select Register (MDE)                                   | 131 |

|    | 7.3    | Usage Note                                                     | 132 |

|    | 7.3.1  | Setting Example of Option-Setting Memory                       | 132 |

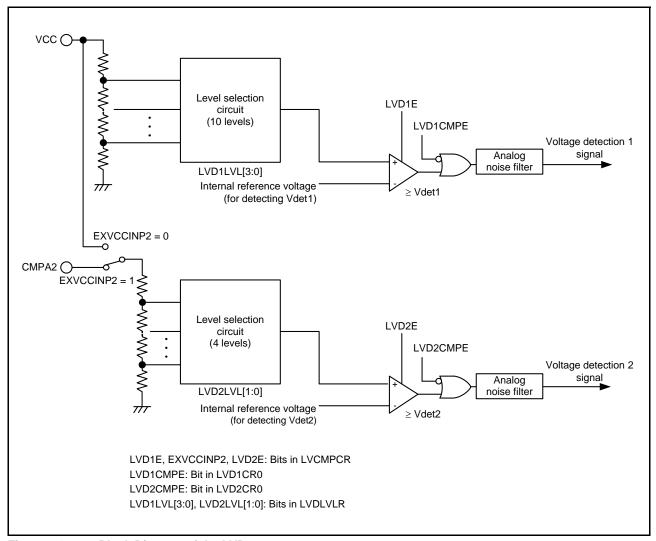

| 8. | Voltag | ge Detection Circuit (LVDAa)                                   | 133 |

|    | 8.1    | Overview                                                       | 133 |

|    | 8.2    | Register Descriptions                                          | 136 |

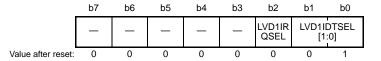

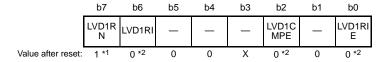

|    | 8.2.1  | Voltage Monitoring 1 Circuit Control Register 1 (LVD1CR1)      | 136 |

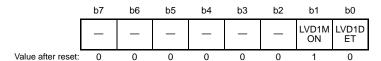

|    | 8.2.2  | Voltage Monitoring 1 Circuit Status Register (LVD1SR)          | 137 |

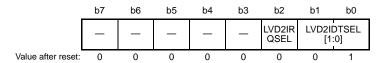

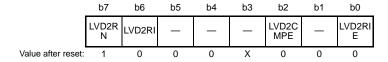

|    | 8.2.3  | Voltage Monitoring 2 Circuit Control Register 1 (LVD2CR1)      | 138 |

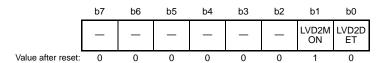

|    | 8.2.4  | Voltage Monitoring 2 Circuit Status Register (LVD2SR)          | 139 |

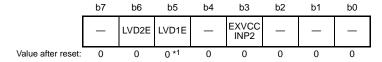

|    | 8.2.5  | Voltage Monitoring Circuit Control Register (LVCMPCR)          | 140 |

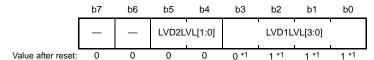

|    | 8.2.6  | Voltage Detection Level Select Register (LVDLVLR)              | 141 |

|    | 8.2.7  | Voltage Monitoring 1 Circuit Control Register 0 (LVD1CR0)      | 142 |

|    | 8.2.8  | Voltage Monitoring 2 Circuit Control Register 0 (LVD2CR0)      | 143 |

|    | 8.3    | VCC Input Voltage Monitor                                      | 144 |

|    | 8.3.1  | Monitoring Vdet1                                               | 144 |

|    | 8.3.2  | Monitoring Vdet2                                               | 144 |

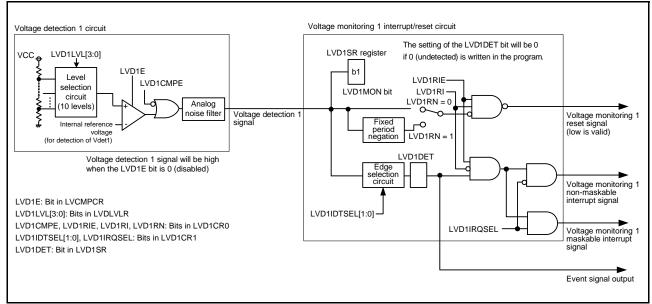

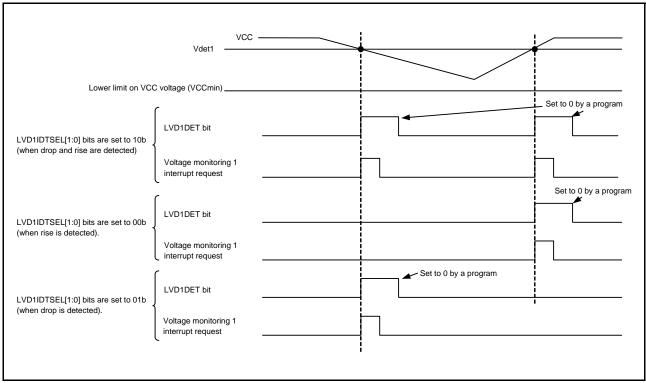

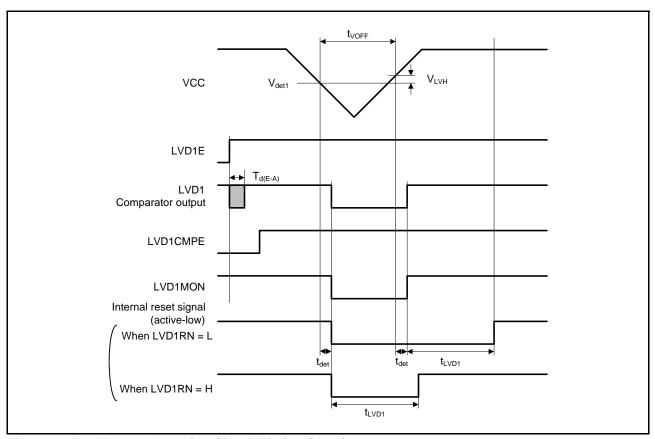

|    | 8.4    | Interrupt and Reset from Voltage Monitoring 1                  | 145 |

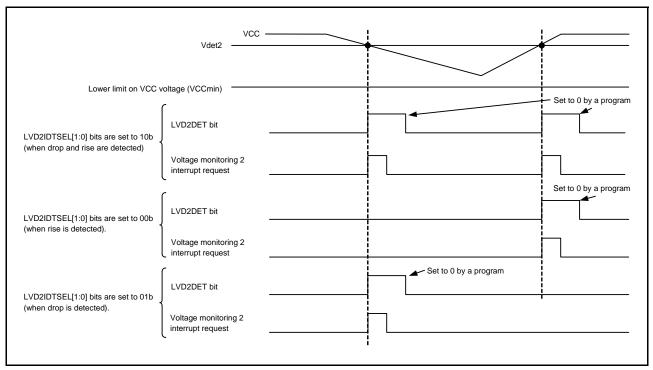

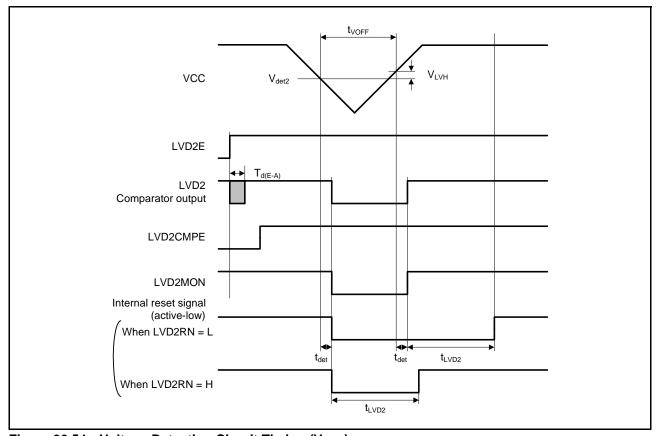

|    | 8.5    | Interrupt and Reset from Voltage Monitoring 2                  | 147 |

|    | 8.6    | Event Link Output                                              | 149 |

|    | 8.6.1  | Interrupt Handling and Event Linking                           | 149 |

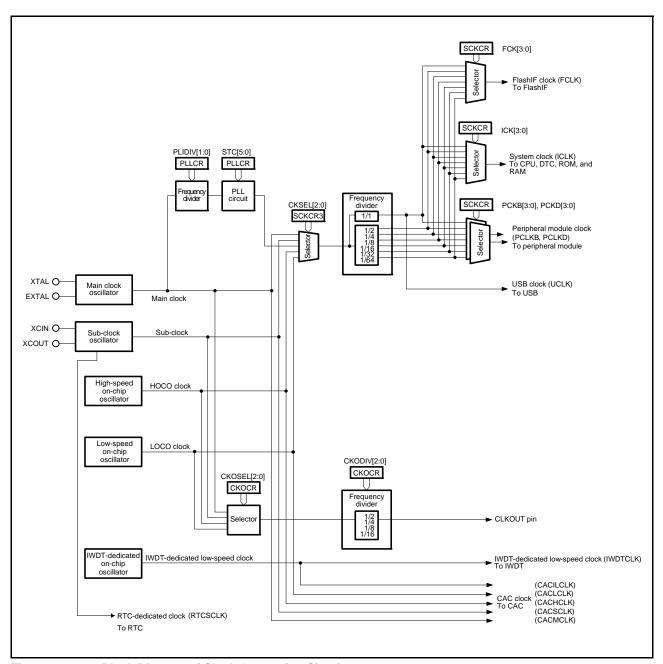

| 9. | Clock  | Generation Circuit                                             | 150 |

|    | 9.1    | Overview                                                       | 150 |

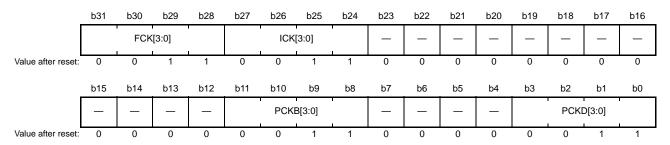

|    | 9.2    | Register Descriptions                                          | 152 |

|    | 9.2.1  | System Clock Control Register (SCKCR)                          | 152 |

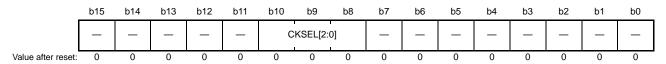

|    | 9.2.2  | System Clock Control Register 3 (SCKCR3)                       | 154 |

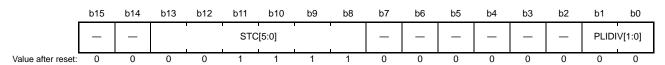

|    | 9.2.3  | PLL Control Register (PLLCR)                                   | 155 |

|    | 9.2.4  | PLL Control Register 2 (PLLCR2)                                | 156 |

|    | 9.2.5  | Main Clock Oscillator Control Register (MOSCCR)                | 157 |

|    | 9.2.6  | Sub-Clock Oscillator Control Register (SOSCCR)                 | 158 |

|    | 9.2.7  | Low-Speed On-Chip Oscillator Control Register (LOCOCR)         | 159 |

|    | 9.2.8  | IWDT-Dedicated On-Chip Oscillator Control Register (ILOCOCR)   | 160 |

|    | 9.2.9  | High-Speed On-Chip Oscillator Control Register (HOCOCR)        | 161 |

|    | 9.2.10 | Oscillation Stabilization Flag Register (OSCOVFSR)             | 162 |

|    | 9.2.1  | Oscillation Stop Detection Control Register (OSTDCR)           | 164 |

|    | 9.2.12 | Oscillation Stop Detection Status Register (OSTDSR)            | 165 |

|    | 9.2.1  | Main Clock Oscillator Wait Control Register (MOSCWTCR)         | 166 |

|    | 9.2.1  | High-Speed On-Chip Oscillator Wait Control Register (HOCOWTCR) | 167 |

|    | 9.2.1  | 5 CLKOUT Output Control Register (CKOCR)                       | 168 |

|    |        |                                                                |     |

| 9.2.16       | Main Clock Oscillator Forced Oscillation Control Register (MOFCR) | 169 |

|--------------|-------------------------------------------------------------------|-----|

| 9.3 Ma       | ain Clock Oscillator                                              | 170 |

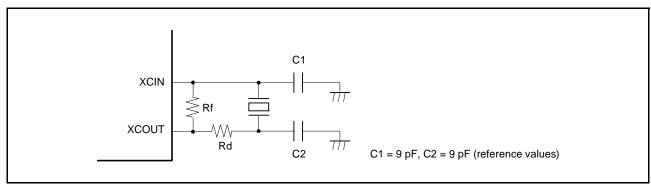

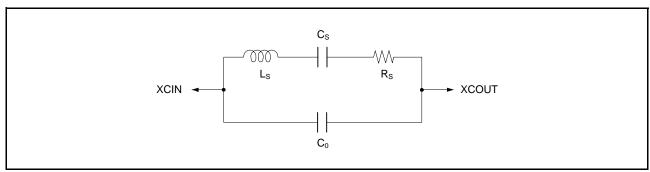

| 9.3.1        | Connecting a Crystal                                              | 170 |

| 9.3.2        | External Clock Input                                              | 171 |

| 9.3.3        | Handling of Pins When the Main Clock is Not Used                  | 171 |

| 9.3.4        | Notes on the External Clock Input                                 | 171 |

| 9.4 Su       | b-Clock Oscillator                                                | 172 |

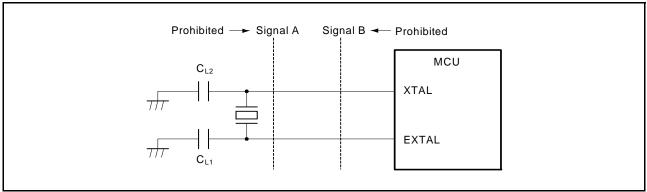

| 9.4.1        | Connecting 32.768-kHz Crystal                                     | 172 |

| 9.4.2        | Handling of Pins When Sub-Clock is Not Used                       | 173 |

| 9.5 Os       | cillation Stop Detection Function                                 | 174 |

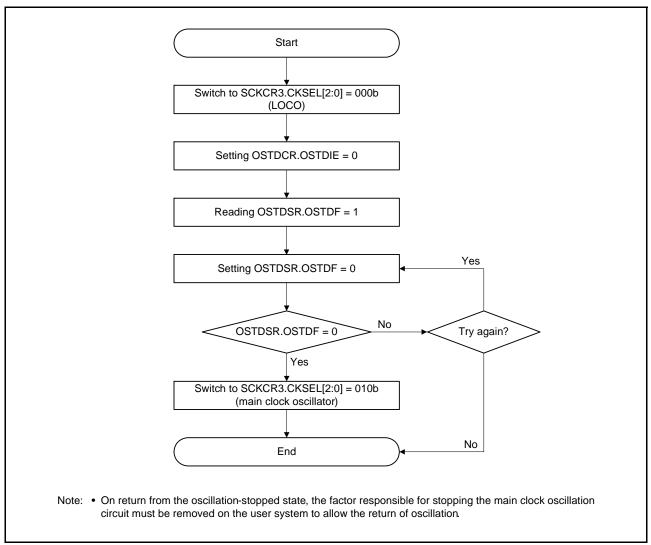

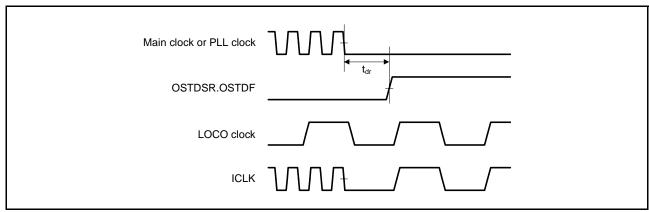

| 9.5.1        | Oscillation Stop Detection and Operation after Detection          | 174 |

| 9.5.2        | Oscillation Stop Detection Interrupts                             | 175 |

| 9.6 PL       | L Circuit                                                         | 176 |

| 9.7 Int      | ernal Clock                                                       | 176 |

| 9.7.1        | System Clock                                                      | 176 |

| 9.7.2        | Peripheral Module Clock                                           | 176 |

| 9.7.3        | FlashIF Clock                                                     | 176 |

| 9.7.4        | USB Clock                                                         | 176 |

| 9.7.5        | CAC Clock                                                         | 176 |

| 9.7.6        | RTC-Dedicated Clock                                               | 17  |

| 9.7.7        | IWDT-Dedicated Clock                                              | 17  |

| 9.8 Us       | age Notes                                                         | 178 |

| 9.8.1        | Notes on Clock Generation Circuit                                 | 178 |

| 9.8.2        | Notes on Resonator                                                | 178 |

| 9.8.3        | Notes on Board Design                                             | 178 |

| 9.8.4        | Notes on Sub-Clock                                                | 179 |

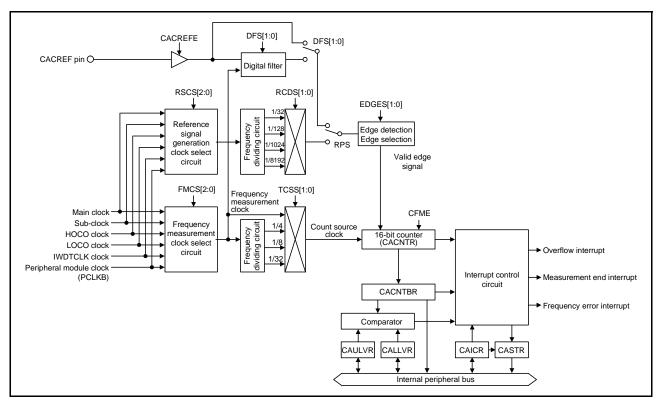

| 0. Clock Fre | equency Accuracy Measurement Circuit (CAC)                        | 183 |

| 10.1 Ov      | rerview                                                           | 183 |

| 10.2 Re      | gister Descriptions                                               | 184 |

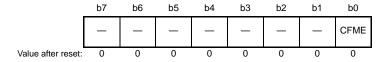

| 10.2.1       | CAC Control Register 0 (CACR0)                                    | 184 |

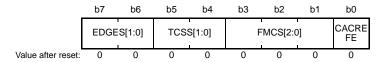

| 10.2.2       | CAC Control Register 1 (CACR1)                                    | 185 |

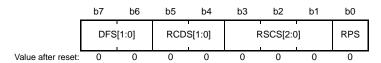

| 10.2.3       | CAC Control Register 2 (CACR2)                                    | 186 |

| 10.2.4       | CAC Interrupt Control Register (CAICR)                            | 187 |

| 10.2.5       | CAC Status Register (CASTR)                                       | 188 |

| 10.2.6       | CAC Upper-Limit Value Setting Register (CAULVR)                   | 189 |

| 10.2.7       | CAC Lower-Limit Value Setting Register (CALLVR)                   | 189 |

| 10.2.8       | CAC Counter Buffer Register (CACNTBR)                             | 189 |

| 10.3 Op      | eration                                                           | 190 |

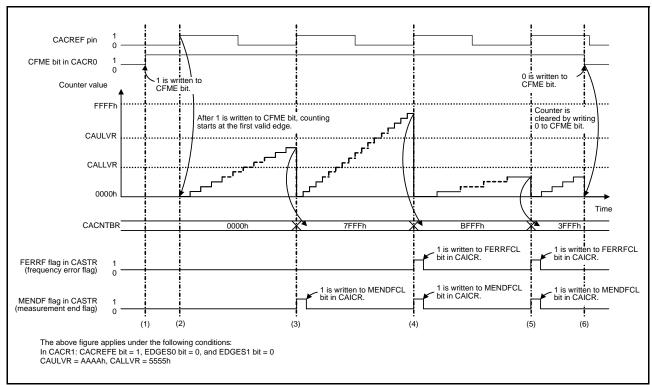

| 10.3.1       | Measuring Clock Frequency Based on CACREF Pin Input               | 190 |

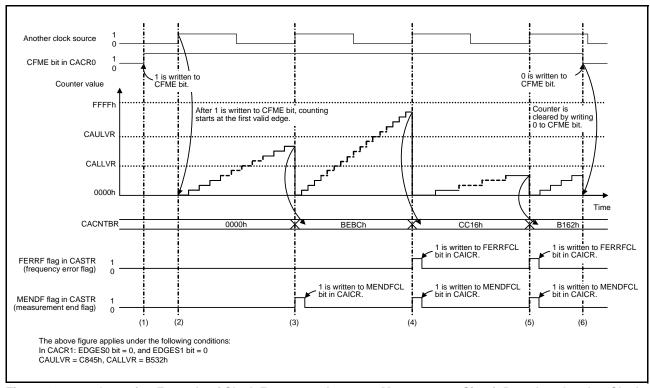

| 10.3.2       | Measuring Clock Frequency Based on Another Clock Source           | 19  |

| 10.3.3       | Digital Filtering of Signals on the CACREF Pin                    | 192 |

|     | 10.4   | Inter   | rupt Requests                                               | 192 |

|-----|--------|---------|-------------------------------------------------------------|-----|

|     | 10.5   | Usag    | e Notes                                                     | 192 |

|     | 10.5.1 | 1       | Module Stop Function Setting                                | 192 |

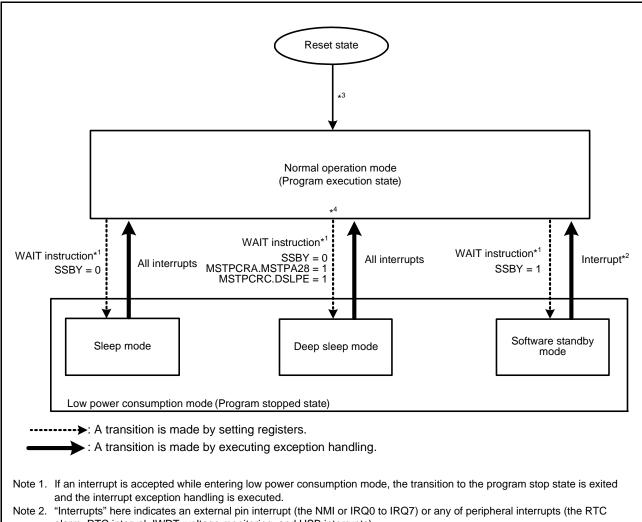

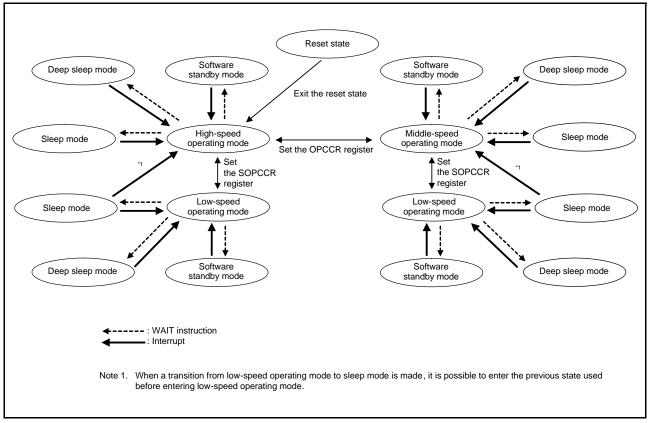

| 11. | Low F  | Power   | Consumption                                                 | 193 |

|     | 11.1   | Over    | view                                                        | 193 |

|     | 11.2   | Regi    | ster Descriptions                                           | 197 |

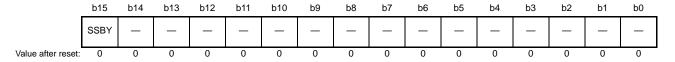

|     | 11.2.1 | 1       | Standby Control Register (SBYCR)                            | 197 |

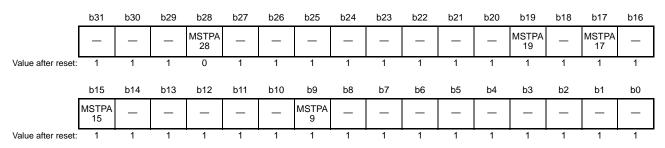

|     | 11.2.2 | 2       | Module Stop Control Register A (MSTPCRA)                    | 198 |

|     | 11.2.3 | 3       | Module Stop Control Register B (MSTPCRB)                    | 199 |

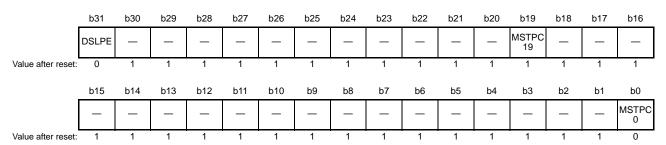

|     | 11.2.4 | 4       | Module Stop Control Register C (MSTPCRC)                    | 200 |

|     | 11.2.5 | 5       | Operating Power Control Register (OPCCR)                    | 201 |

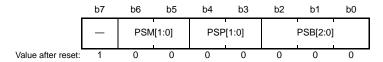

|     | 11.2.6 | 5       | Sub Operating Power Control Register (SOPCCR)               | 203 |

|     | 11.2.7 | 7       | Sleep Mode Return Clock Source Switching Register (RSTCKCR) | 208 |

|     | 11.3   | Redu    | cing Power Consumption by Switching Clock Signals           | 210 |

|     | 11.4   | Mod     | ıle Stop Function                                           | 210 |

|     | 11.5   | Func    | tion for Lower Operating Power Consumption                  | 210 |

|     | 11.5.1 | 1       | Setting Operating Power Control Mode                        | 210 |

|     | 11.6   | Low     | Power Consumption Modes                                     | 212 |

|     | 11.6.1 | 1       | Sleep Mode                                                  | 212 |

|     | 11     | .6.1.1  | Entry to Sleep Mode                                         | 212 |

|     | 11     | .6.1.2  | Exit from Sleep Mode                                        | 213 |

|     | 11     | .6.1.3  | Sleep Mode Return Clock Source Switching Function           | 213 |

|     | 11.6.2 | 2       | Deep Sleep Mode                                             | 214 |

|     | 11     | .6.2.1  | Entry to Deep Sleep Mode                                    | 214 |

|     | 11     | .6.2.2  | Exit from Deep Sleep Mode                                   | 215 |

|     | 11.6.3 | 3       | Software Standby Mode                                       | 216 |

|     | 11     | .6.3.1  | Entry to Software Standby Mode                              | 216 |

|     | 11     | .6.3.2  | Exit from Software Standby Mode                             | 217 |

|     | 11     | .6.3.3  | Example of Software Standby Mode Application                | 218 |

|     | 11.7   | Usag    | e Notes                                                     | 219 |

|     | 11.7.1 | 1       | I/O Port States                                             | 219 |

|     | 11.7.2 | 2       | Module Stop State of DTC                                    | 219 |

|     | 11.7.3 | 3       | On-Chip Peripheral Module Interrupts                        | 219 |

|     | 11.7.4 | 4       | Write Access to MSTPCRA, MSTPCRB, and MSTPCRC               | 219 |

|     | 11.7.5 | 5       | Timing of WAIT Instructions                                 | 219 |

|     | 11.7.6 | 5       | Rewrite the Register by DTC in Sleep Mode                   | 219 |

| 12. | Regis  | ter W   | rite Protection Function                                    | 220 |

|     | 12.1   | Regi    | ster Descriptions                                           | 221 |

|     | 12.1.1 | 1       | Protect Register (PRCR)                                     | 221 |

| 13. | Excep  | otion I | Handling                                                    | 222 |

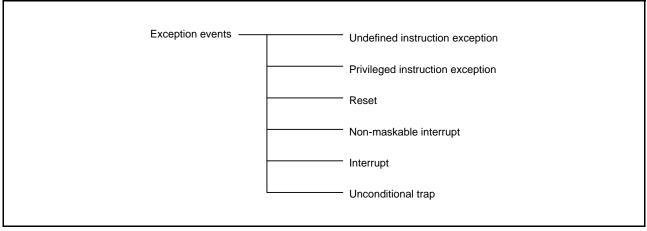

|     | 13.1   | Exce    | ption Events                                                | 222 |

|    | 13.1    | 1.1 Undefined Instruction Exception                                     | 223 |

|----|---------|-------------------------------------------------------------------------|-----|

|    | 13.1    | 1.2 Privileged Instruction Exception                                    | 223 |

|    | 13.1    | 1.3 Reset                                                               | 223 |

|    | 13.1    | 1.4 Non-Maskable Interrupt                                              | 223 |

|    | 13.1    | 1.5 Interrupts                                                          | 223 |

|    | 13.1    | 1.6 Unconditional Trap                                                  | 223 |

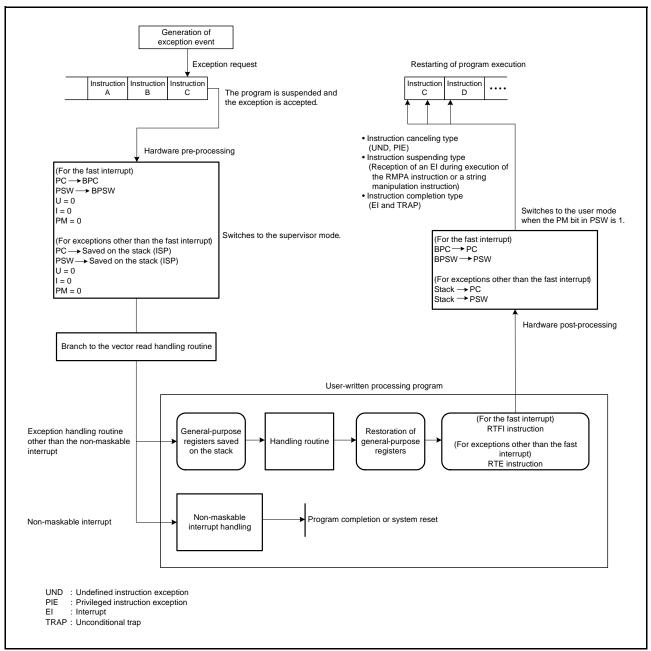

|    | 13.2    | Exception Handling Procedure                                            | 224 |

|    | 13.3    | Acceptance of Exception Events                                          | 226 |

|    | 13.3    | 3.1 Acceptance Timing and Saved PC Value                                | 226 |

|    | 13.3    | 3.2 Vector and Site for Saving the Values in the PC and PSW             | 226 |

|    | 13.4    | Hardware Processing for Accepting and Returning from Exceptions         | 227 |

|    | 13.5    | Hardware Pre-Processing                                                 | 228 |

|    | 13.5    | Undefined Instruction Exception                                         | 228 |

|    | 13.5    | 5.2 Privileged Instruction Exception                                    | 228 |

|    | 13.5    | 5.3 Reset                                                               | 228 |

|    | 13.5    | Non-Maskable Interrupt                                                  | 228 |

|    | 13.5    | 5.5 Interrupt                                                           | 229 |

|    | 13.5    | 5.6 Unconditional Trap                                                  | 229 |

|    | 13.6    | Return from Exception Handling Routine                                  | 230 |

|    | 13.7    | Priority of Exception Events                                            | 230 |

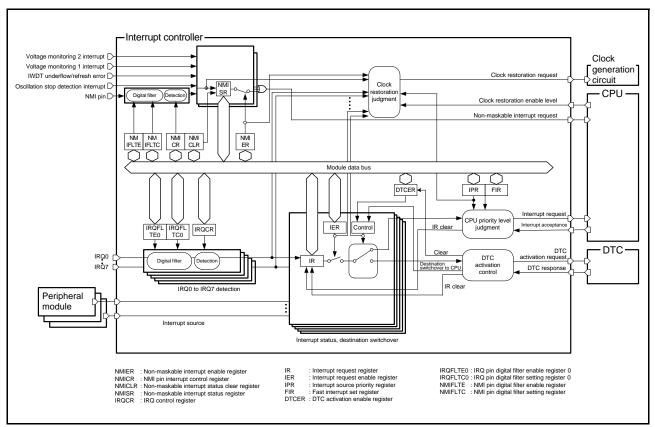

| 14 | . Inter | rrupt Controller (ICUb)                                                 | 231 |

|    | 14.1    | Overview                                                                | 231 |

|    | 14.2    | Register Descriptions                                                   | 233 |

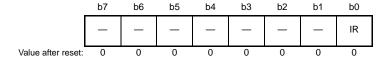

|    | 14.2    | 2.1 Interrupt Request Register n (IRn) (n = interrupt vector number)    | 233 |

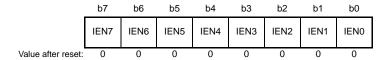

|    | 14.2    | 2.2 Interrupt Request Enable Register m (IERm) (m = 02h to 1Fh)         | 234 |

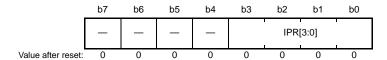

|    | 14.2    | 2.3 Interrupt Source Priority Register n (IPRn) (n = 000 to 249)        | 235 |

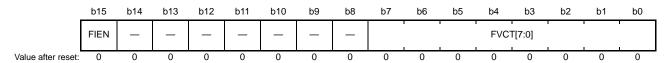

|    | 14.2    | 2.4 Fast Interrupt Set Register (FIR)                                   | 236 |

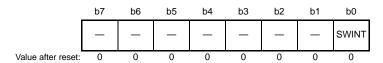

|    | 14.2    | 2.5 Software Interrupt Activation Register (SWINTR)                     | 237 |

|    | 14.2    | DTC Activation Enable Register n (DTCERn) (n = interrupt vector number) | 238 |

|    | 14.2    | 2.7 IRQ Control Register i (IRQCRi) (i = 0 to 7)                        | 239 |

|    | 14.2    | 2.8 IRQ Pin Digital Filter Enable Register 0 (IRQFLTE0)                 | 240 |

|    | 14.2    | 2.9 IRQ Pin Digital Filter Setting Register 0 (IRQFLTC0)                | 241 |

|    | 14.2    | 2.10 Non-Maskable Interrupt Status Register (NMISR)                     | 242 |

|    | 14.2    | 2.11 Non-Maskable Interrupt Enable Register (NMIER)                     | 244 |

|    | 14.2    | Non-Maskable Interrupt Status Clear Register (NMICLR)                   | 245 |

|    | 14.2    | 2.13 NMI Pin Interrupt Control Register (NMICR)                         | 246 |

|    | 14.2    | NMI Pin Digital Filter Enable Register (NMIFLTE)                        | 246 |

|    | 14.2    | 2.15 NMI Pin Digital Filter Setting Register (NMIFLTC)                  | 247 |

|    | 14.3    | Vector Table                                                            | 248 |

|    | 14.3    | 3.1 Interrupt Vector Table                                              | 248 |

|    | 14.3    | 3.2 Fast Interrupt Vector Table                                         | 256 |

|   | 14.3.3     | Non-maskable Interrupt Vector Table                          | 256 |

|---|------------|--------------------------------------------------------------|-----|

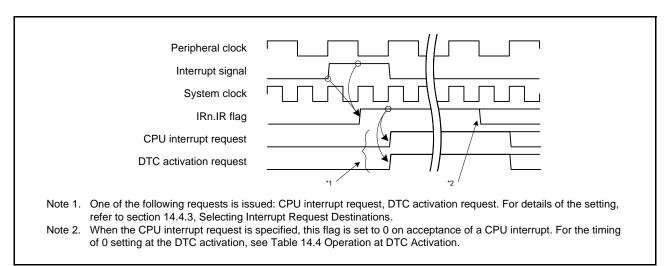

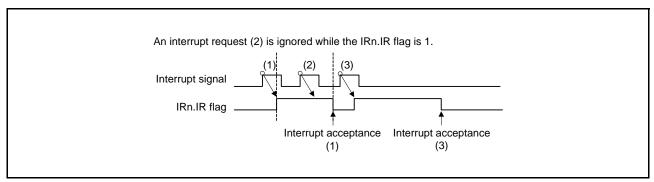

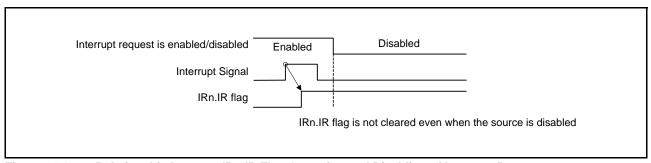

|   | 14.4 In    | nterrupt Operation                                           | 256 |

|   | 14.4.1     | Detecting Interrupts                                         | 256 |

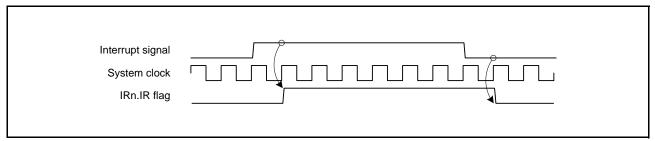

|   | 14.4       | .1.1 Operation of Status Flags for Edge-Detected Interrupts  | 256 |

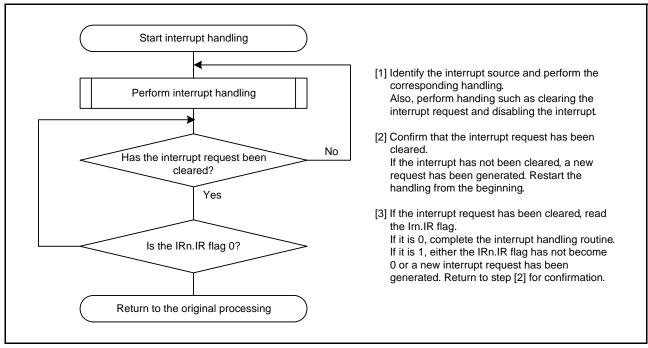

|   | 14.4       | .1.2 Operation of Status Flags for Level-Detected Interrupts | 258 |

|   | 14.4.2     | Enabling and Disabling Interrupt Sources                     | 259 |

|   | 14.4.3     | Selecting Interrupt Request Destinations                     | 259 |

|   | 14.4.4     | Determining Priority                                         | 260 |

|   | 14.4.5     | Fast Interrupt                                               | 260 |

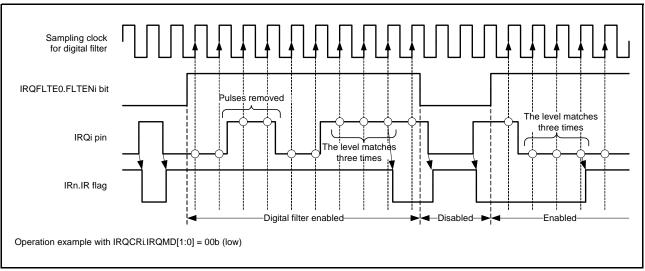

|   | 14.4.6     | Digital Filter                                               | 261 |

|   | 14.4.7     | External Pin Interrupts                                      | 261 |

|   | 14.5 N     | Jon-maskable Interrupt Operation                             | 262 |

|   | 14.6 R     | Leturn from Power-Down States                                | 263 |

|   | 14.6.1     | Return from Sleep Mode or Deep Sleep Mode                    | 263 |

|   | 14.6.2     | Return from Software Standby Mode                            | 263 |

|   | 14.7 U     | Jsage Note                                                   | 263 |

|   | 14.7.1     | Note on WAIT Instruction Used with Non-Maskable Interrupt    | 263 |

| 1 | 5. Buses . |                                                              | 264 |

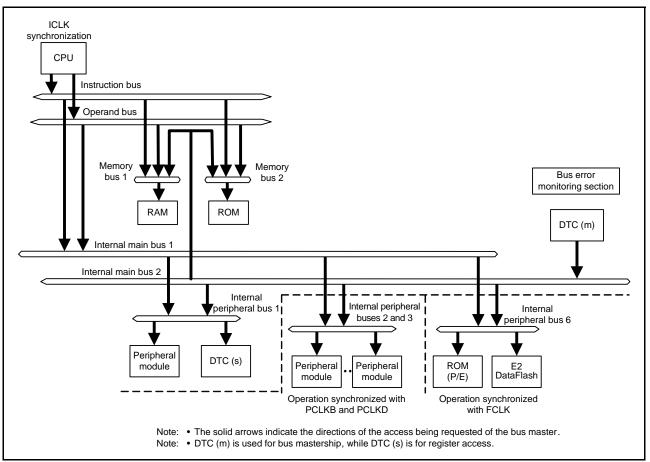

|   | 15.1 C     | Overview                                                     | 264 |

|   | 15.2 D     | Description of Buses                                         | 266 |

|   | 15.2.1     | CPU Buses                                                    | 266 |

|   | 15.2.2     | Memory Buses                                                 | 266 |

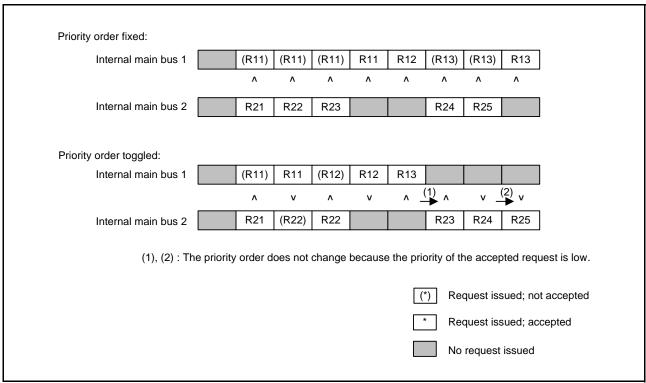

|   | 15.2.3     | Internal Main Buses                                          | 266 |

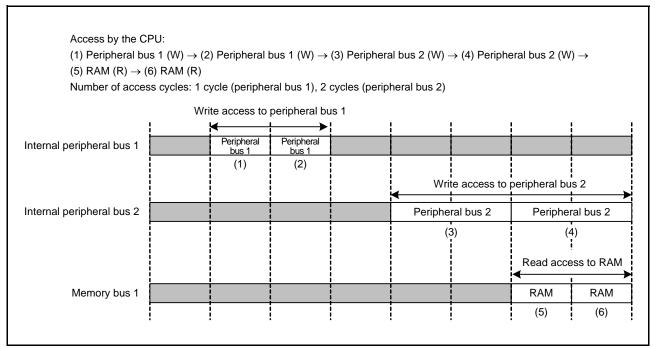

|   | 15.2.4     | Internal Peripheral Buses                                    | 267 |

|   | 15.2.5     | Write Buffer Function (Internal Peripheral Bus)              | 268 |

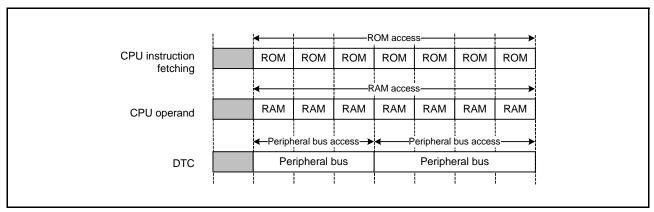

|   | 15.2.6     | Parallel Operation                                           | 269 |

|   | 15.2.7     | Restrictions                                                 | 269 |

|   | 15.3 R     | Legister Descriptions                                        | 270 |

|   | 15.3.1     | Bus Error Status Clear Register (BERCLR)                     | 270 |

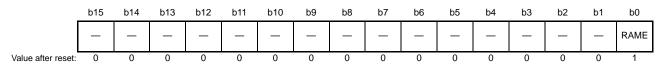

|   | 15.3.2     | Bus Error Monitoring Enable Register (BEREN)                 | 270 |

|   | 15.3.3     | Bus Error Status Register 1 (BERSR1)                         | 271 |

|   | 15.3.4     | Bus Error Status Register 2 (BERSR2)                         | 271 |

|   | 15.3.5     | Bus Priority Control Register (BUSPRI)                       | 272 |

|   | 15.4 B     | Sus Error Monitoring Section                                 | 274 |

|   | 15.4.1     | Type of Bus Error                                            | 274 |

|   | 15.4       | .1.1 Illegal Address Access                                  | 274 |

|   | 15.4.2     | Operations When a Bus Error Occurs                           | 274 |

|   | 15.4.3     | Conditions Leading to Bus Errors                             | 275 |

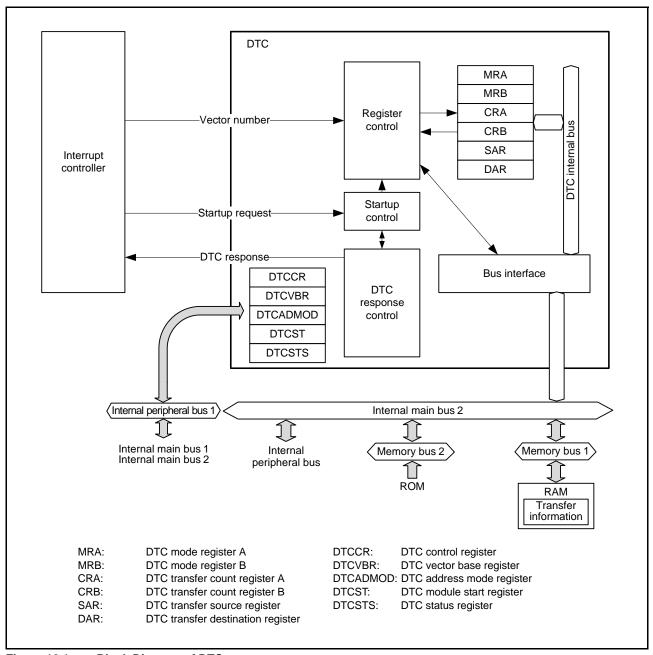

| 1 | 6. Data Tr | ansfer Controller (DTCa)                                     | 276 |

|   | 16.1 C     | Overview                                                     | 276 |

|   | 16.2 R     | Legister Descriptions                                        | 278 |

|   |            |                                                              |     |

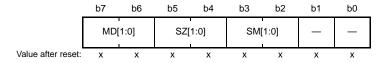

|     | 16.2. | .1 DTC Mode Register A (MRA)                                                        | 278 |

|-----|-------|-------------------------------------------------------------------------------------|-----|

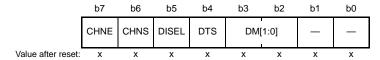

|     | 16.2. | .2 DTC Mode Register B (MRB)                                                        | 279 |

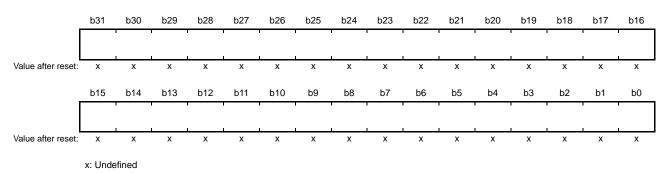

|     | 16.2. | .3 DTC Transfer Source Register (SAR)                                               | 280 |

|     | 16.2. | .4 DTC Transfer Destination Register (DAR)                                          | 280 |

|     | 16.2. | .5 DTC Transfer Count Register A (CRA)                                              | 281 |

|     | 16.2. | .6 DTC Transfer Count Register B (CRB)                                              | 282 |

|     | 16.2. | .7 DTC Control Register (DTCCR)                                                     | 282 |

|     | 16.2. | .8 DTC Vector Base Register (DTCVBR)                                                | 283 |

|     | 16.2. | .9 DTC Address Mode Register (DTCADMOD)                                             | 283 |

|     | 16.2. | .10 DTC Module Start Register (DTCST)                                               | 284 |

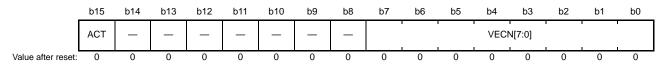

|     | 16.2. | .11 DTC Status Register (DTCSTS)                                                    | 285 |

|     | 16.3  | Sources of Activation                                                               | 286 |

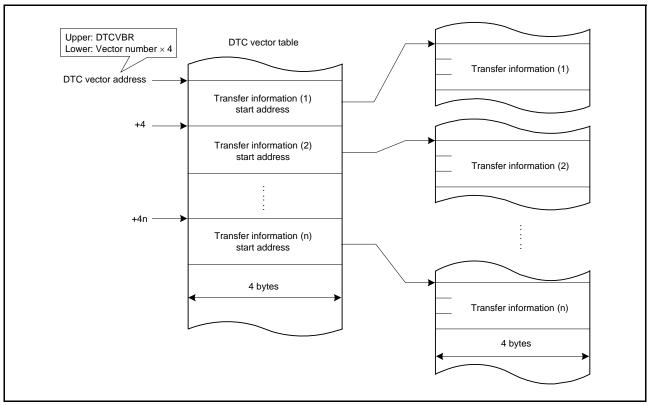

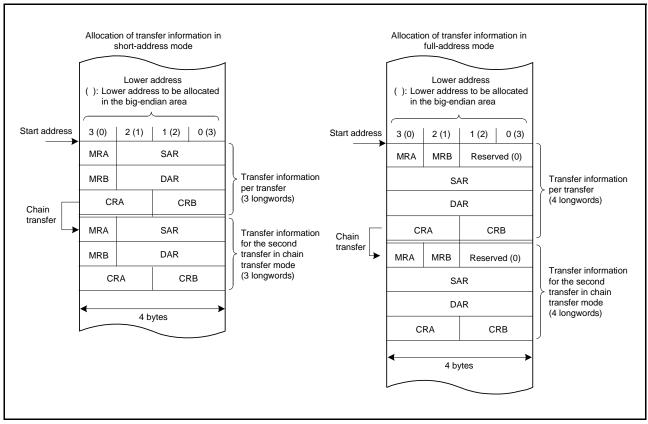

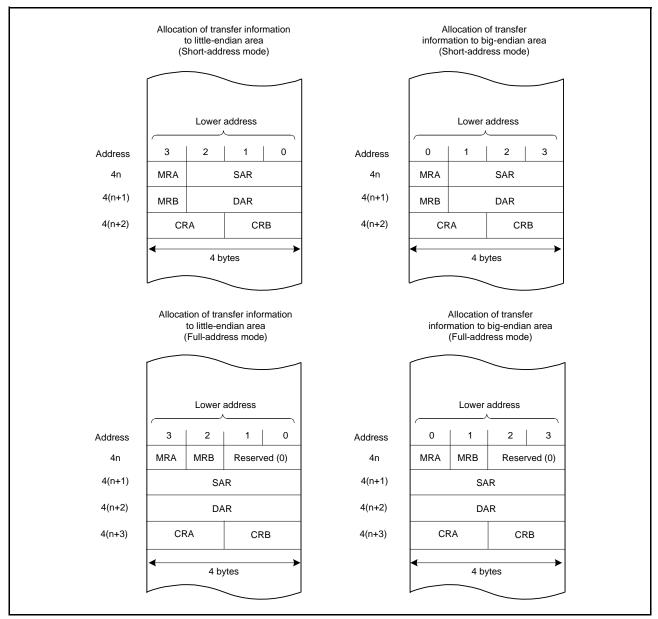

|     | 16.3. | .1 Allocating Transfer Information and DTC Vector Table                             | 286 |

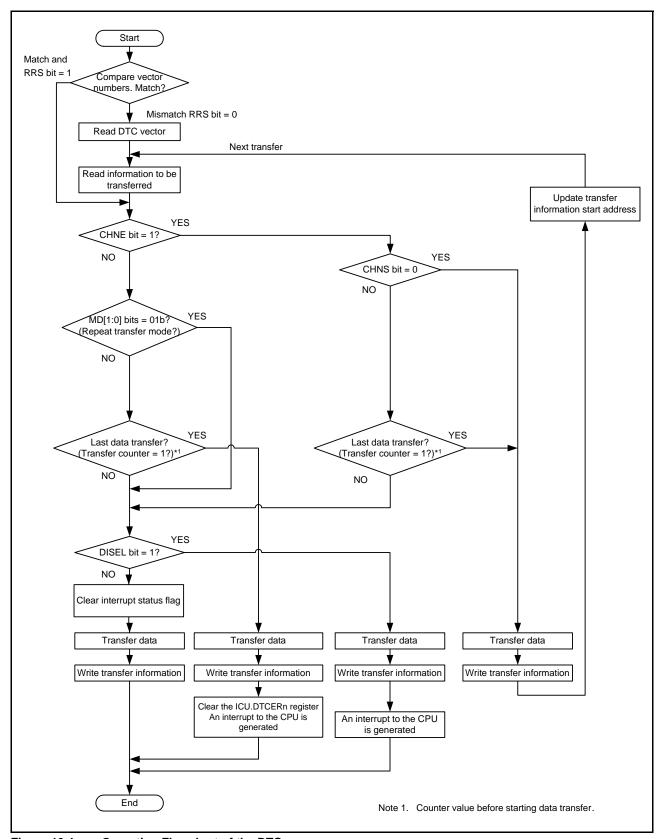

|     | 16.4  | Operation                                                                           | 288 |

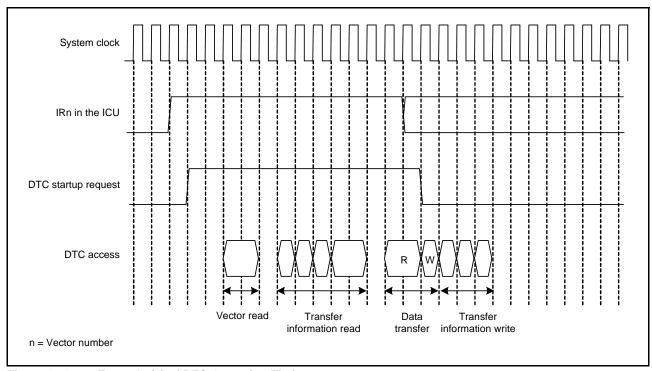

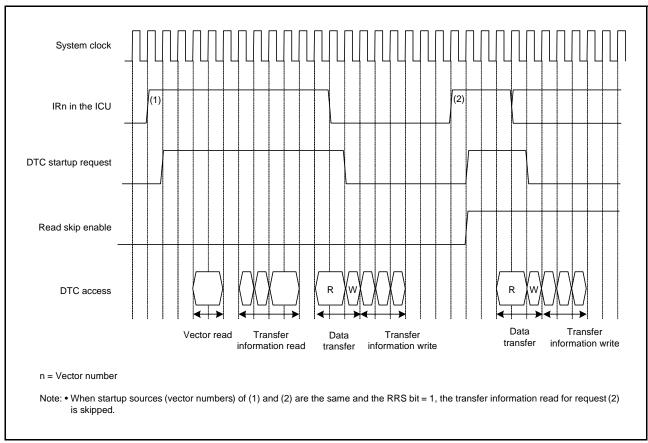

|     | 16.4. | .1 Transfer Information Read Skip Function                                          | 290 |

|     | 16.4. | .2 Transfer Information Write-Back Skip Function                                    | 291 |

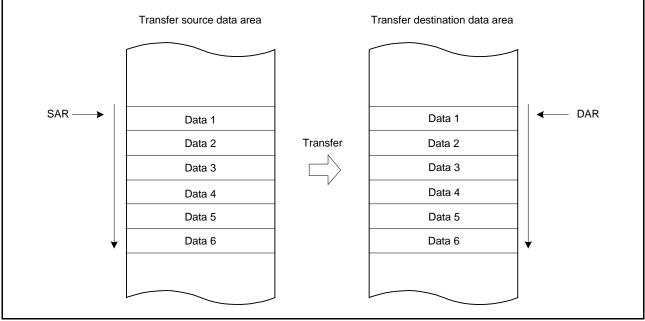

|     | 16.4. | .3 Normal Transfer Mode                                                             | 292 |

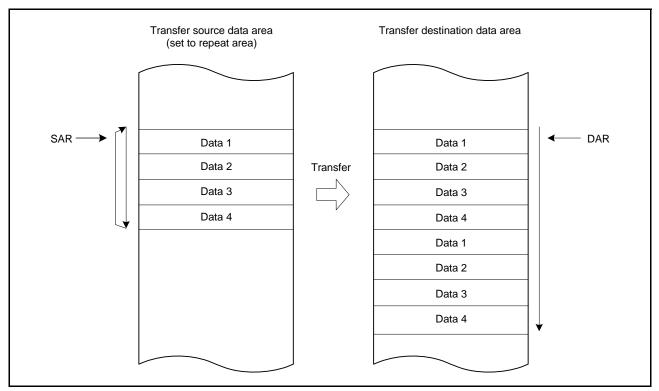

|     | 16.4. | .4 Repeat Transfer Mode                                                             | 293 |

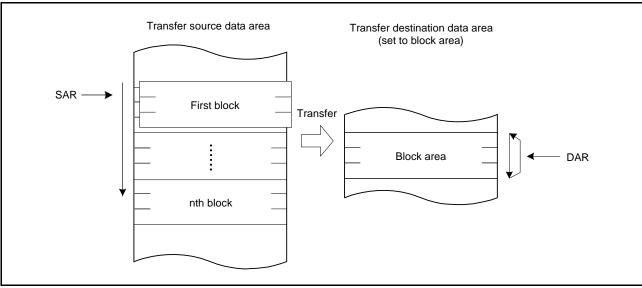

|     | 16.4. | .5 Block Transfer Mode                                                              | 294 |

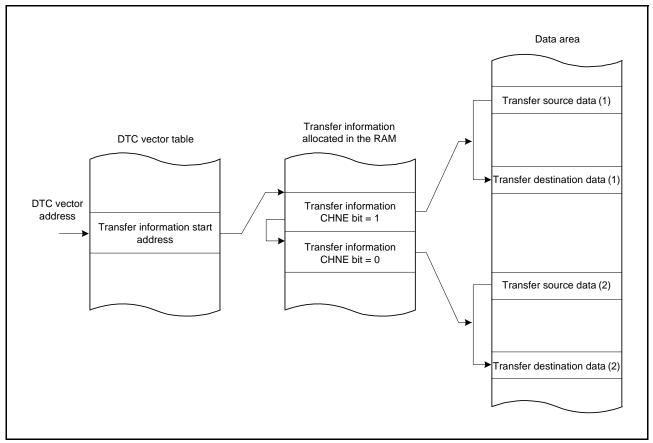

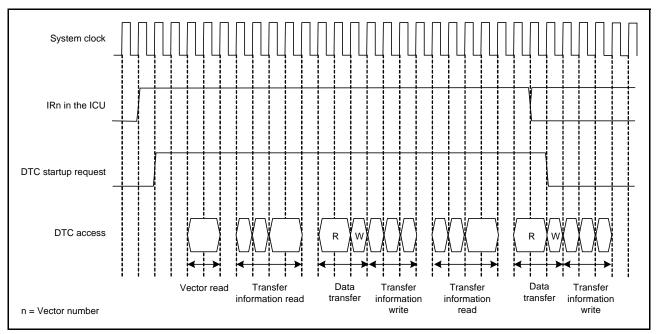

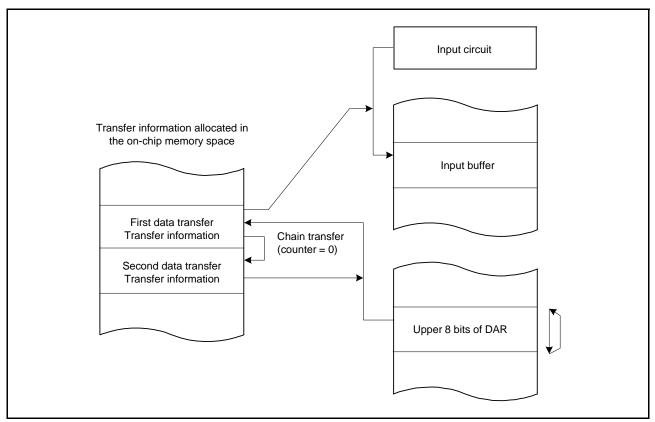

|     | 16.4. | .6 Chain Transfer                                                                   | 295 |

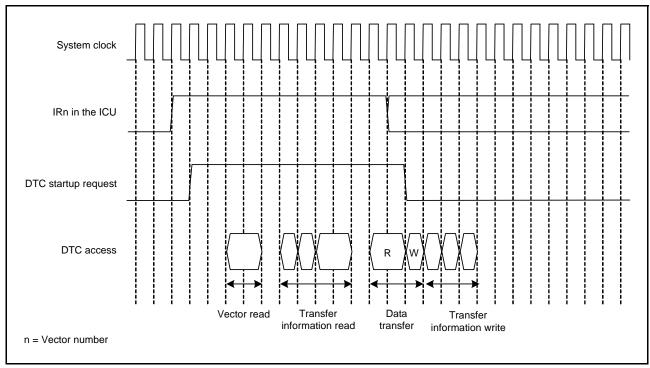

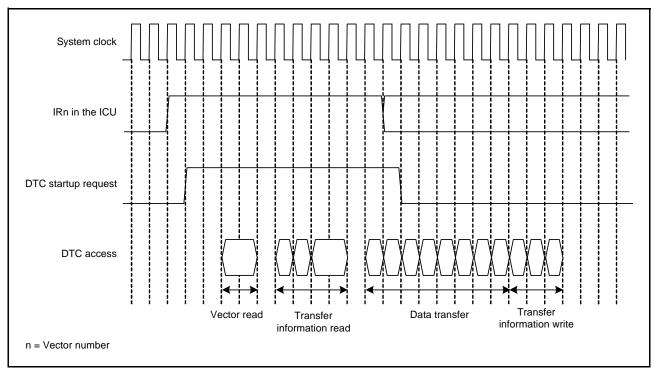

|     | 16.4. | .7 Operation Timing                                                                 | 296 |

|     | 16.4. | .8 Execution Cycles of the DTC                                                      | 299 |

|     | 16.4. | .9 DTC Bus Mastership Release Timing                                                | 299 |

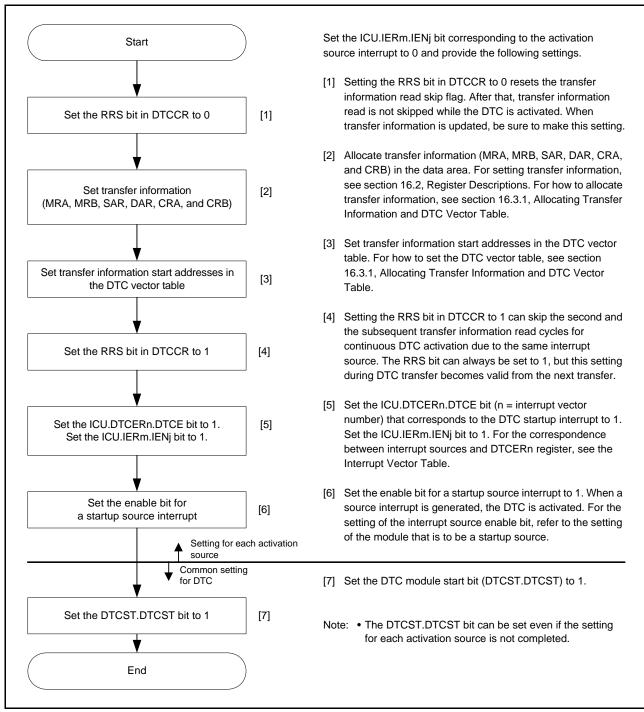

|     | 16.5  | DTC Setting Procedure                                                               | 300 |

|     | 16.6  | Examples of DTC Usage                                                               | 301 |

|     | 16.6. | .1 Normal Transfer                                                                  | 301 |

|     | 16.6. | .2 Chain Transfer when Counter = 0                                                  | 302 |

|     | 16.7  | Interrupt Source                                                                    | 303 |

|     | 16.8  | Event Link                                                                          | 303 |

|     | 16.9  | Low Power Consumption Function                                                      | 304 |

|     | 16.10 | Usage Notes                                                                         | 305 |

|     | 16.10 | 0.1 Transfer Information Start Address                                              | 305 |

|     | 16.10 | 0.2 Allocating Transfer Information                                                 | 305 |

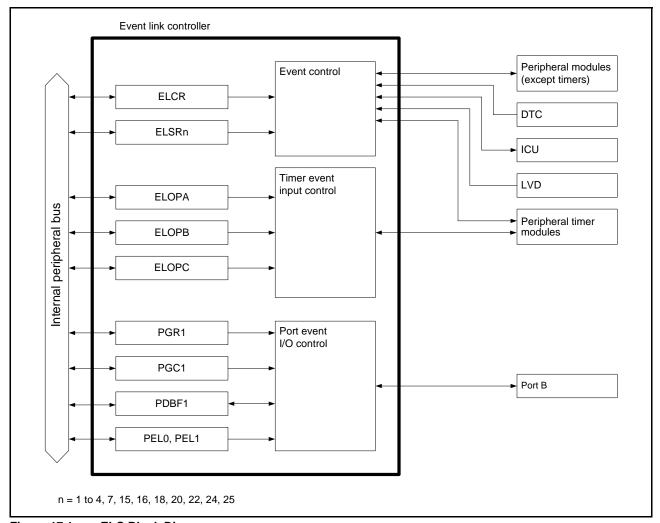

| 17. | Even  | t Link Controller (ELC)                                                             | 306 |

|     | 17.1  | Overview                                                                            | 306 |

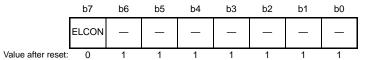

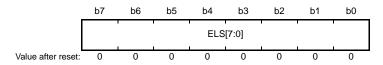

|     | 17.2  | Register Descriptions                                                               | 307 |

|     | 17.2. | .1 Event Link Control Register (ELCR)                                               | 307 |

|     | 17.2. | 2 Event Link Setting Register n (ELSRn) (n = 1 to 4, 7, 15, 16, 18, 20, 22, 24, 25) | 308 |

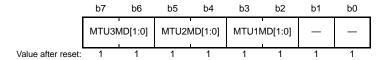

|     | 17.2. | .3 Event Link Option Setting Register A (ELOPA)                                     | 310 |

|     | 17.2. | .4 Event Link Option Setting Register B (ELOPB)                                     | 311 |

|     | 17.2. | .5 Event Link Option Setting Register C (ELOPC)                                     | 311 |

| 17.2.6        | Port Group Setting Register 1 (PGR1)                        | 312 |

|---------------|-------------------------------------------------------------|-----|

| 17.2.7        | Port Group Control Register 1 (PGC1)                        | 313 |

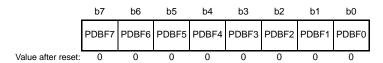

| 17.2.8        | Port Buffer Register 1 (PDBF1)                              | 314 |

| 17.2.9        | Event Link Port Setting Register n (PELn) (n = 0, 1)        | 315 |

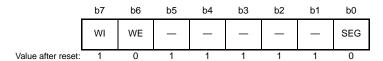

| 17.2.10       | Event Link Software Event Generation Register (ELSEGR)      | 316 |

| 17.3 Ope      | eration                                                     | 317 |

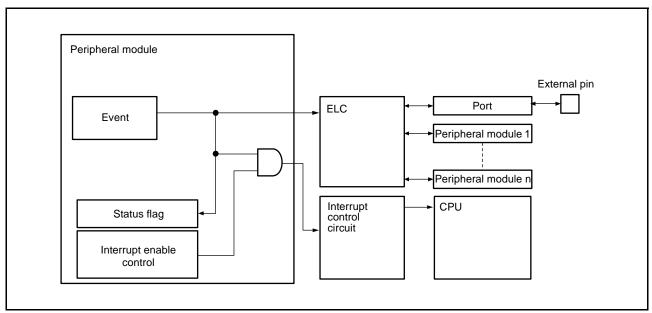

| 17.3.1        | Relation between Interrupt Handling and Event Linking       | 317 |

| 17.3.2        | Event Linkage                                               | 318 |

| 17.3.3        | Operation of Peripheral Timer Modules When Event is Input   | 319 |

| 17.3.4        | Operation of A/D and D/A Converters when Event is Input     | 319 |

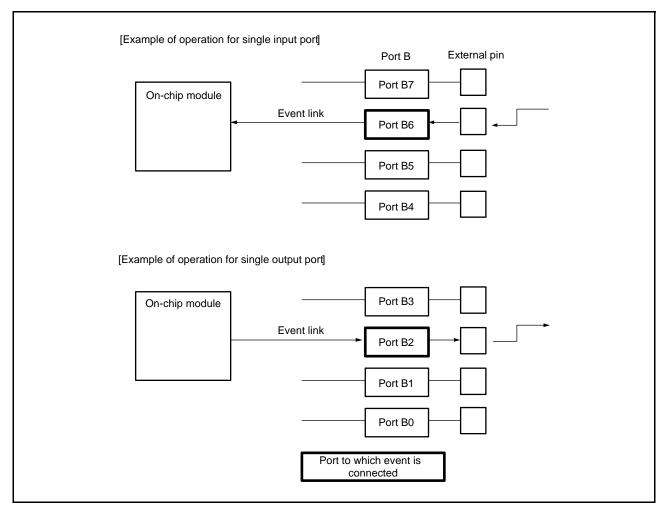

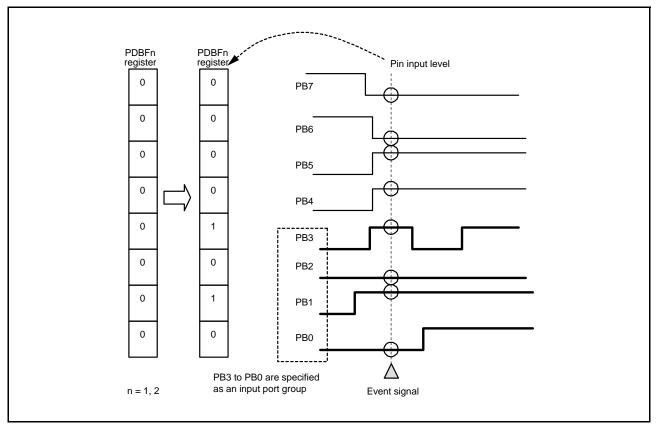

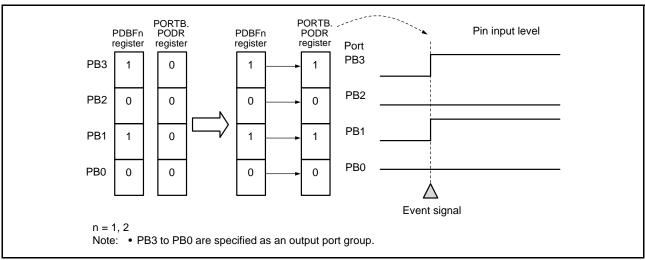

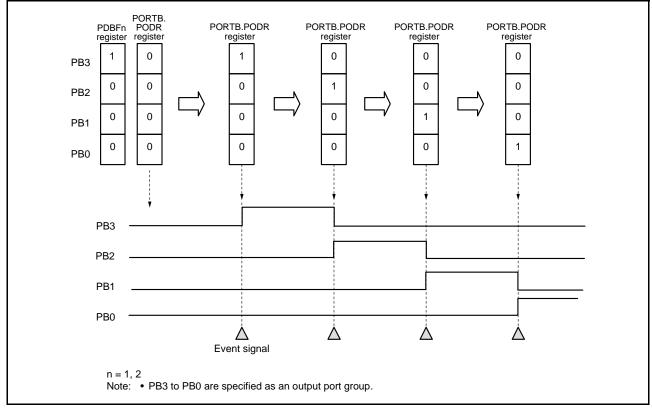

| 17.3.5        | I/O Port Operation upon Event Input and Event Generation    | 319 |

| 17.3.6        | Procedure for Linking Events                                | 323 |

| 17.4 Usa      | ge Notes                                                    | 324 |

| 17.4.1        | Setting ELSRn Register                                      | 324 |

| 17.4.2        | Setting Bit-Rotating Operation of Output Port Groups        | 324 |

| 17.4.3        | Linking DTC Transfer End Signals as Events                  | 324 |

| 17.4.4        | Setting Clocks                                              | 324 |

| 17.4.5        | Enabling and Disabling the ELC                              | 324 |

| 18. I/O Ports |                                                             | 325 |

|               | erview                                                      |     |

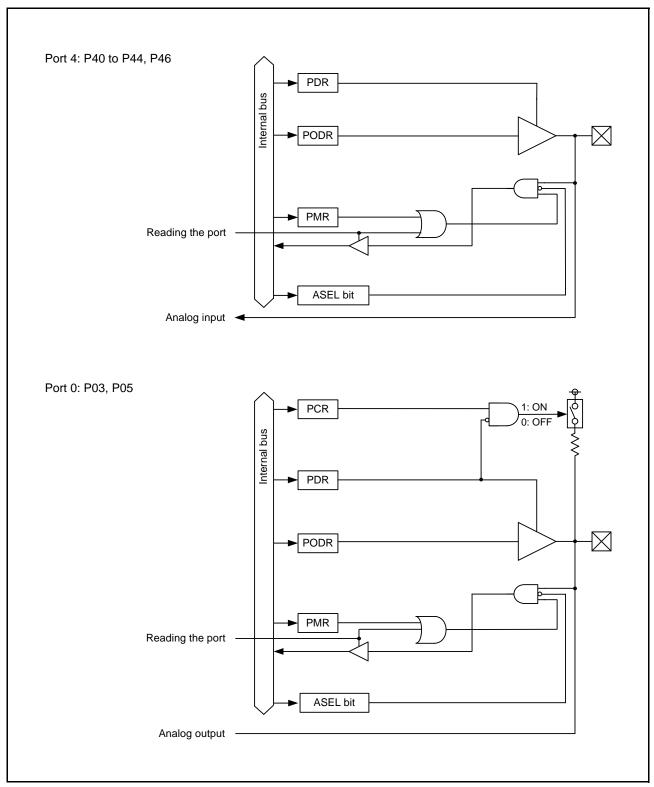

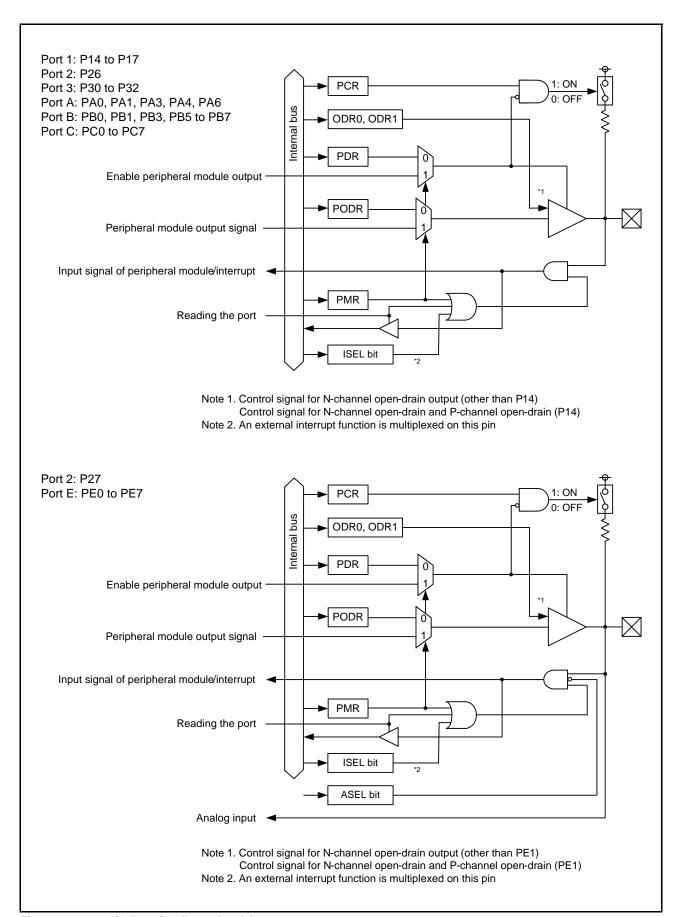

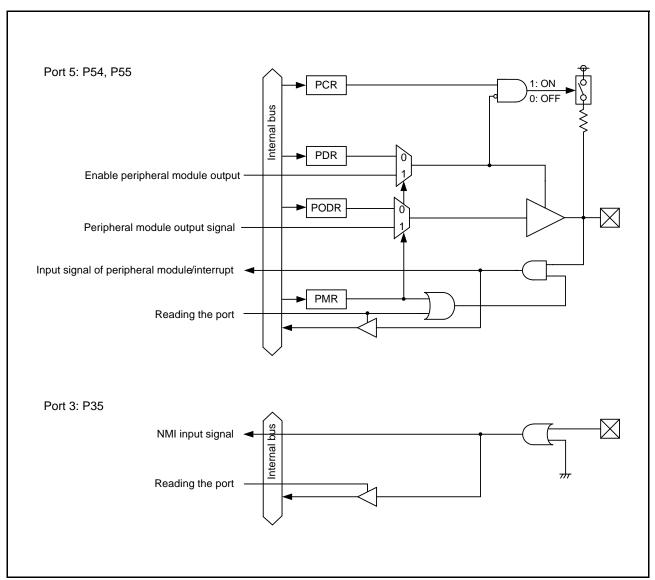

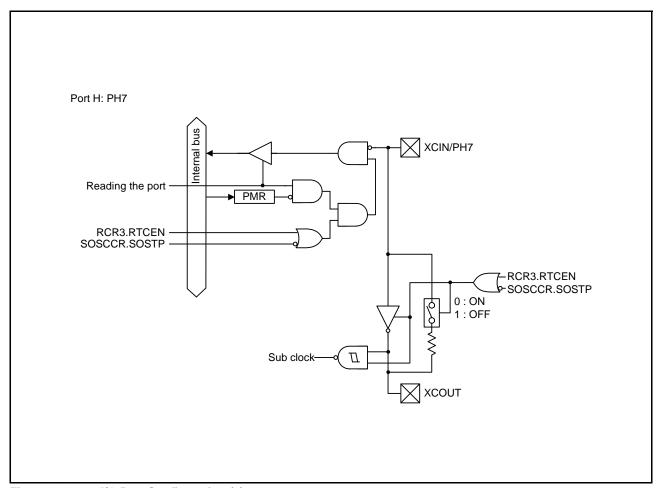

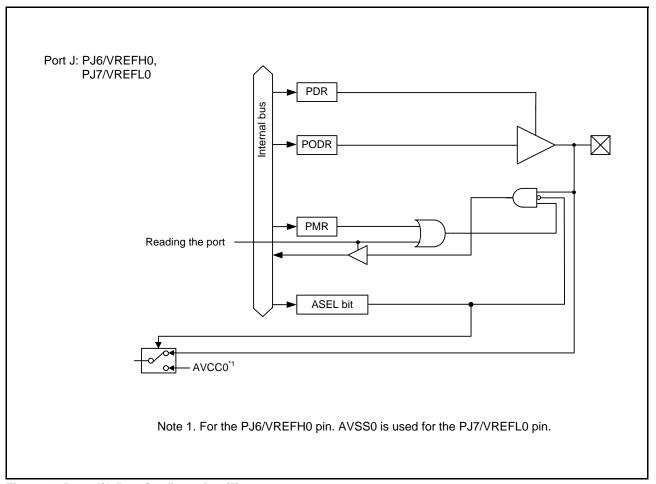

| 18.2 I/C      | Port Configuration                                          | 327 |

| 18.3 Reg      | rister Descriptions                                         | 332 |

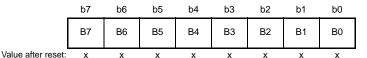

| 18.3.1        | Port Direction Register (PDR)                               | 332 |

| 18.3.2        | Port Output Data Register (PODR)                            | 333 |

| 18.3.3        | Port Input Data Register (PIDR)                             | 334 |

| 18.3.4        | Port Mode Register (PMR)                                    | 335 |

| 18.3.5        | Open Drain Control Register 0 (ODR0)                        | 336 |

| 18.3.6        | Open Drain Control Register 1 (ODR1)                        | 337 |

| 18.3.7        | Pull-Up Control Register (PCR)                              | 338 |

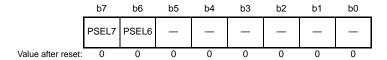

| 18.3.8        | Port Switching Register A (PSRA)                            | 339 |

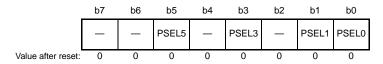

| 18.3.9        | Port Switching Register B (PSRB)                            | 340 |

| 18.4 Har      | ndling of Unused Pins                                       | 341 |

| 19. Multi-Fun | ction Pin Controller (MPC)                                  | 342 |

|               | erview                                                      |     |

| 19.2 Reg      | rister Descriptions                                         | 347 |

| 19.2.1        | Write-Protect Register (PWPR)                               |     |

| 19.2.2        | P0n Pin Function Control Register (P0nPFS) (n = 3, 5)       |     |

| 19.2.3        | P1n Pin Function Control Registers (P1nPFS) (n = 4 to 7)    |     |

| 19.2.4        | P2n Pin Function Control Registers (P2nPFS) (n = 6 to 7)    |     |

| 19.2.5        | P3n Pin Function Control Registers (P3nPFS) (n = 0 to 2, 5) |     |

| 19.2.6        | P4n Pin Function Control Registers (P4nPFS) (n = 0 to 4, 6) |     |

| 19.2.7        | P5n Pin Function Select Registers (P5nPFS) (n = 4, 5)                               | 353 |

|---------------|-------------------------------------------------------------------------------------|-----|

| 19.2.8        | PAn Pin Function Control Registers (PAnPFS) (n = 0, 1, 3, 4, 6)                     | 354 |

| 19.2.9        | PBn Pin Function Control Registers (PBnPFS) (n = 0, 1, 3, 5 to 7)                   | 357 |

| 19.2.10       | PCn Pin Function Control Registers (PCnPFS) (n = 2 to 7)                            | 359 |

| 19.2.11       | PEn Pin Function Control Registers (PEnPFS) (n = 0 to 7)                            | 361 |

| 19.2.12       | PJn Pin Function Control Registers (PJnPFS) (n = 6, 7)                              | 363 |

| 19.3 Usa      | age Notes                                                                           | 364 |

| 19.3.1        | Procedure for Specifying Input/Output Pin Functions                                 | 364 |

| 19.3.2        | Notes on MPC Register Setting                                                       | 364 |

| 19.3.3        | Note on Using Analog Functions                                                      | 365 |

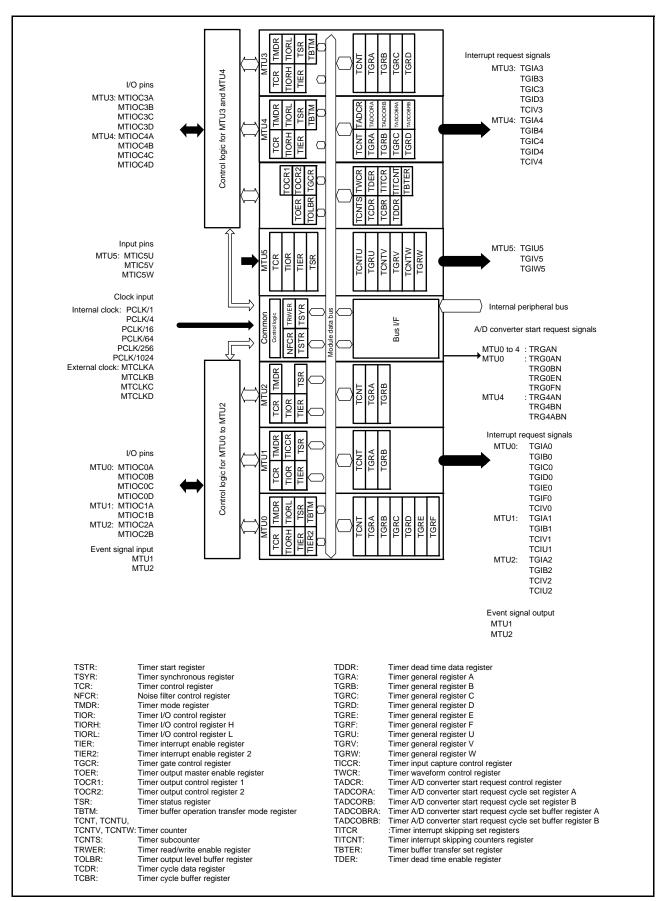

| 20. Multi-Fun | ction Timer Pulse Unit 2 (MTU2a)                                                    | 366 |

| 20.1 Ove      | erview                                                                              | 366 |

| 20.2 Reg      | gister Descriptions                                                                 | 371 |

| 20.2.1        | Timer Control Register (TCR)                                                        | 371 |

| 20.2.2        | Timer Mode Register (TMDR)                                                          | 374 |

| 20.2.3        | Timer I/O Control Register (TIOR)                                                   | 376 |

| 20.2.4        | Timer Compare Match Clear Register (TCNTCMPCLR)                                     | 387 |

| 20.2.5        | Timer Interrupt Enable Register (TIER)                                              | 388 |

| 20.2.6        | Timer Status Register (TSR)                                                         | 391 |

| 20.2.7        | Timer Buffer Operation Transfer Mode Register (TBTM)                                | 392 |

| 20.2.8        | Timer Input Capture Control Register (TICCR)                                        | 393 |

| 20.2.9        | Timer A/D Converter Start Request Control Register (TADCR)                          | 394 |

| 20.2.10       | Timer A/D Converter Start Request Cycle Set Registers A and B (TADCORA and TADCORB) | 395 |

| 20.2.11       | Timer A/D Converter Start Request Cycle Set Buffer Registers A and B                |     |

|               | (TADCOBRA and TADCOBRB)                                                             | 395 |

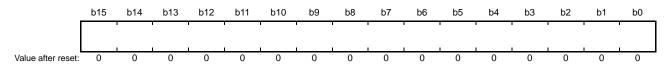

| 20.2.12       | Timer Counter (TCNT)                                                                | 396 |

| 20.2.13       | Timer General Register (TGR)                                                        | 396 |

| 20.2.14       | Timer Start Registers (TSTR)                                                        | 397 |

| 20.2.15       | Timer Synchronous Registers (TSYR)                                                  | 399 |

| 20.2.16       | Timer Read/Write Enable Registers (TRWER)                                           | 400 |

| 20.2.17       | Timer Output Master Enable Registers (TOER)                                         | 401 |

| 20.2.18       | Timer Output Control Registers 1 (TOCR1)                                            | 402 |

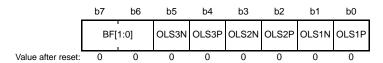

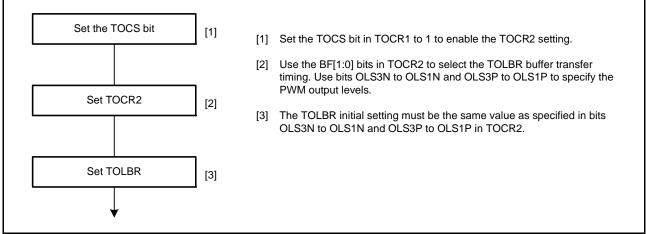

| 20.2.19       | Timer Output Control Registers 2 (TOCR2)                                            | 404 |

| 20.2.20       | Timer Output Level Buffer Registers (TOLBR)                                         | 407 |

| 20.2.21       | Timer Gate Control Registers (TGCR)                                                 | 408 |

| 20.2.22       | Timer Subcounters (TCNTS)                                                           | 409 |

| 20.2.23       | Timer Dead Time Data Registers (TDDR)                                               | 409 |

| 20.2.24       | Timer Cycle Data Registers (TCDR)                                                   |     |

| 20.2.25       | Timer Cycle Buffer Registers (TCBR)                                                 |     |

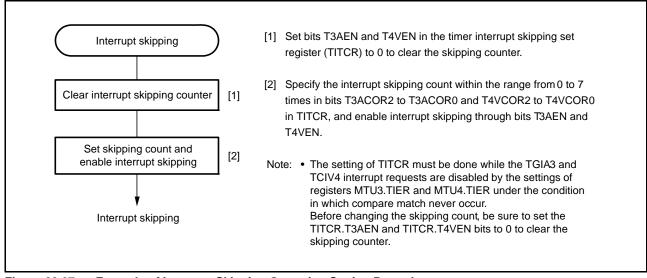

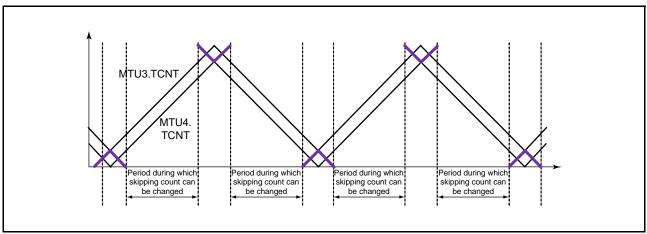

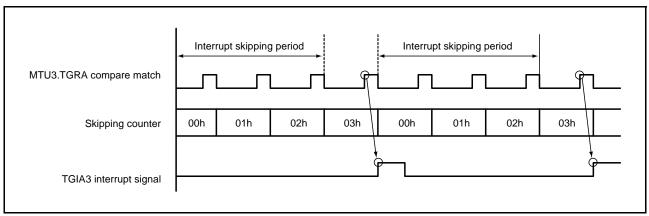

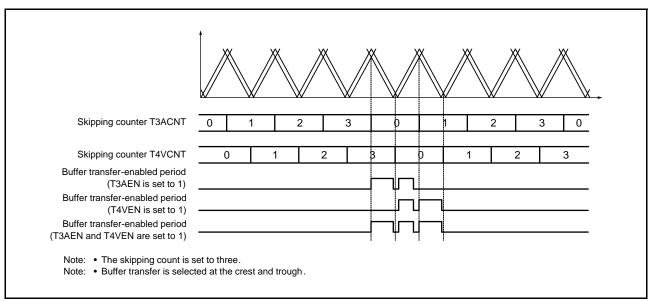

| 20.2.26       | Timer Interrupt Skipping Set Registers (TITCR)                                      | 411 |

|    | 20.2.27  | Timer Interrupt Skipping Counters (TITCNT)                                                 | 413 |

|----|----------|--------------------------------------------------------------------------------------------|-----|

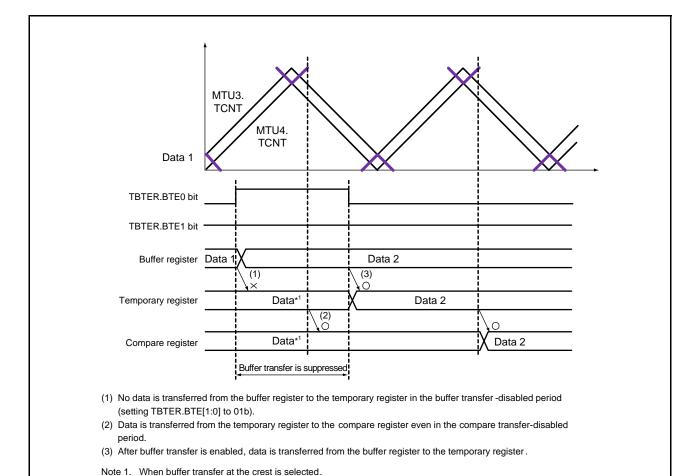

|    | 20.2.28  | Timer Buffer Transfer Set Registers (TBTER)                                                | 414 |

|    | 20.2.29  | Timer Dead Time Enable Registers (TDER)                                                    | 415 |

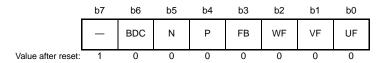

|    | 20.2.30  | Timer Waveform Control Registers (TWCR)                                                    | 416 |

|    | 20.2.31  | Noise Filter Control Registers (NFCR)                                                      | 417 |

|    | 20.2.32  | Bus Master Interface                                                                       | 420 |

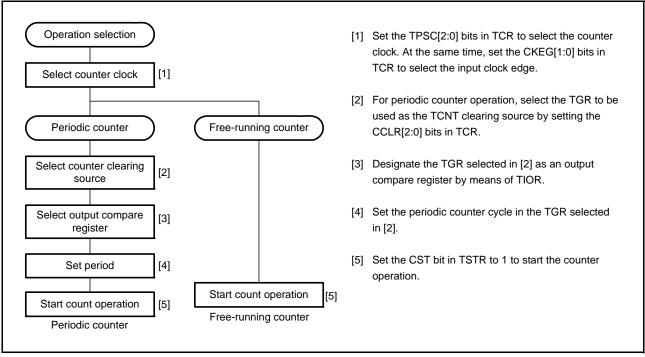

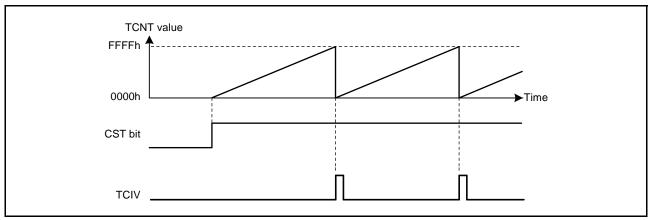

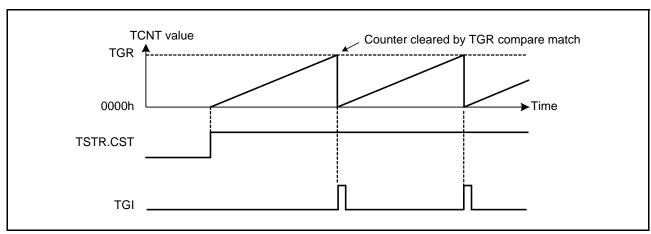

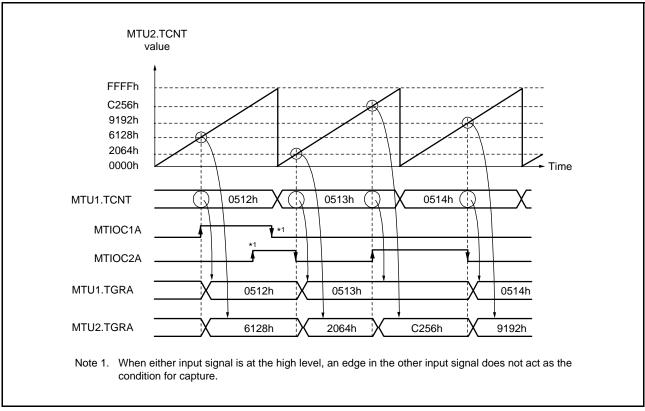

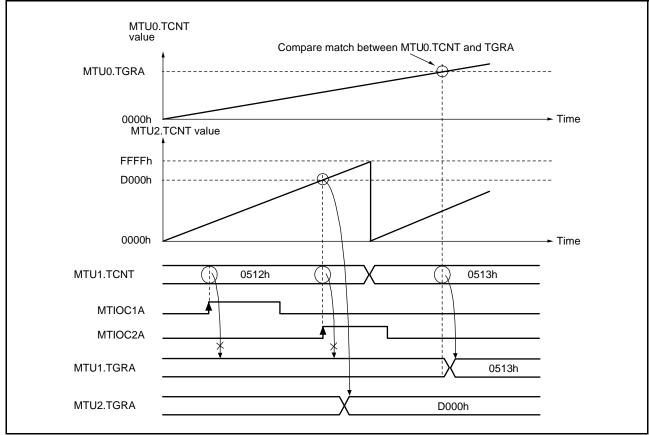

| 20 | .3 Oper  | ration                                                                                     | 421 |

|    | 20.3.1   | Basic Functions                                                                            | 421 |

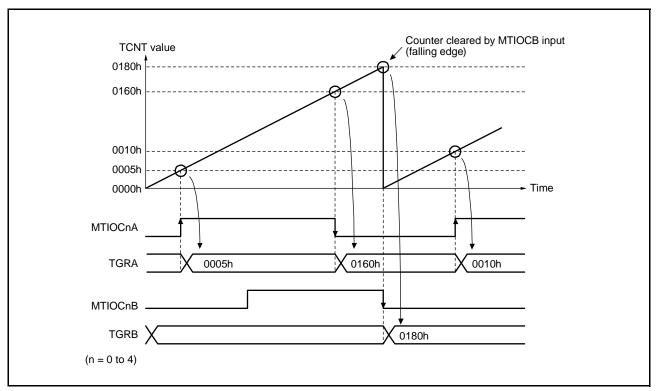

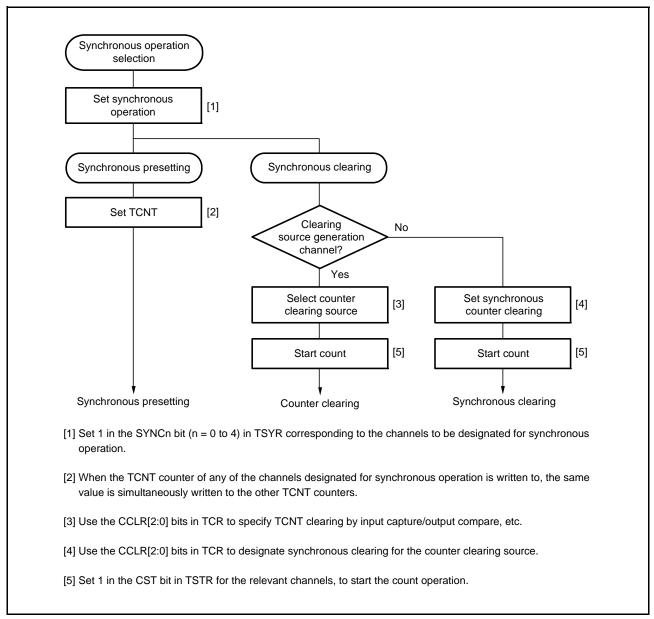

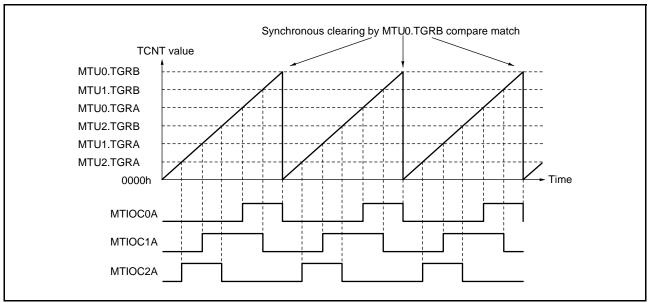

|    | 20.3.2   | Synchronous Operation                                                                      | 427 |

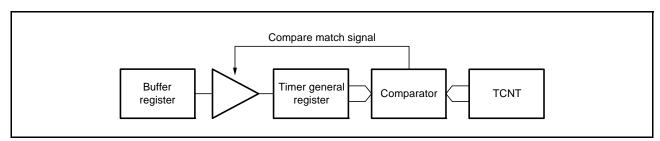

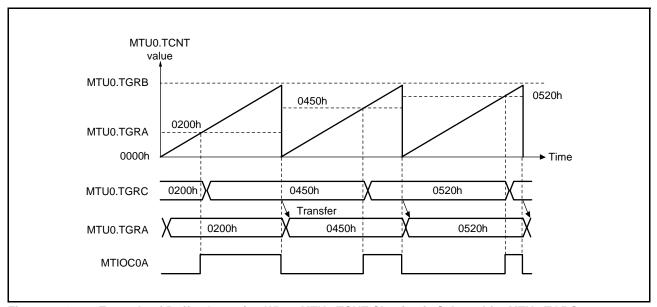

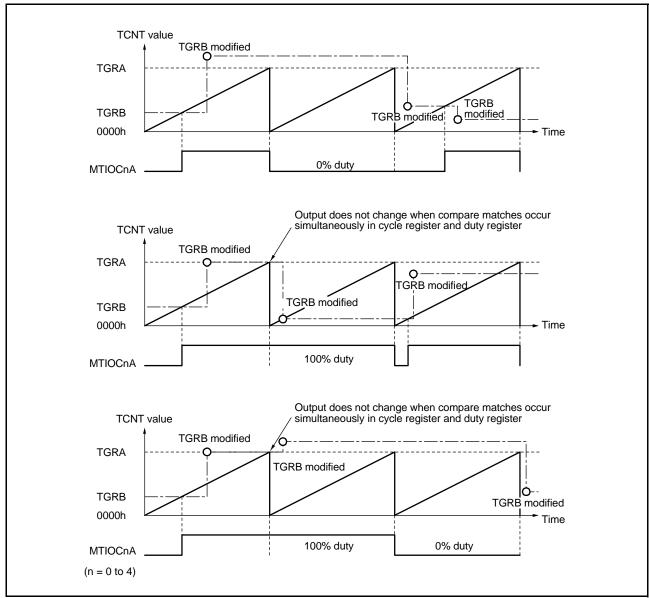

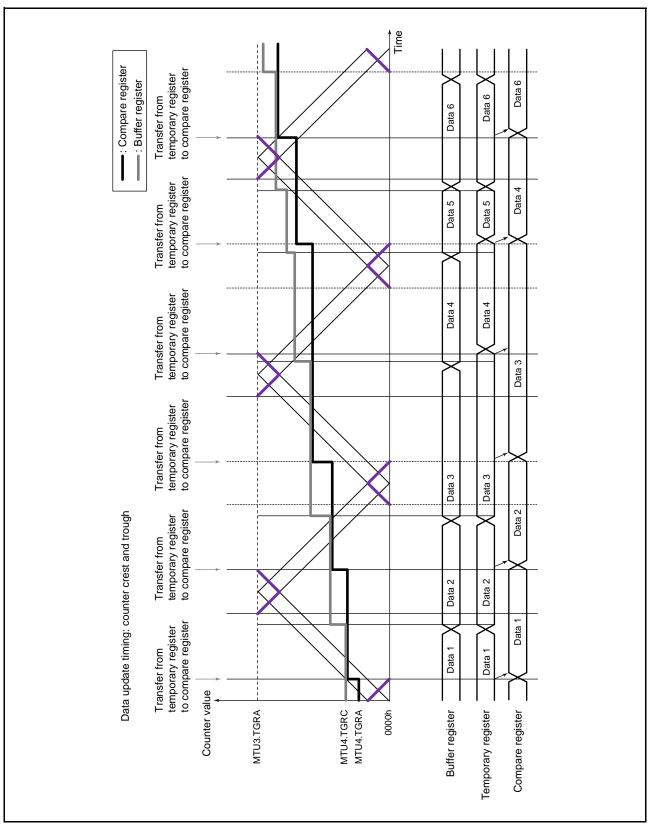

|    | 20.3.3   | Buffer Operation                                                                           | 429 |

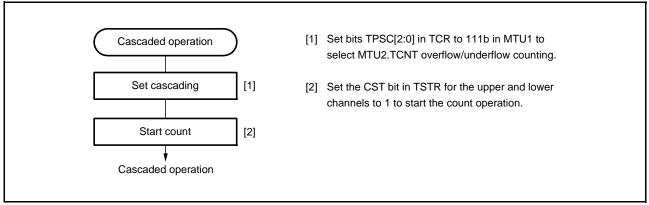

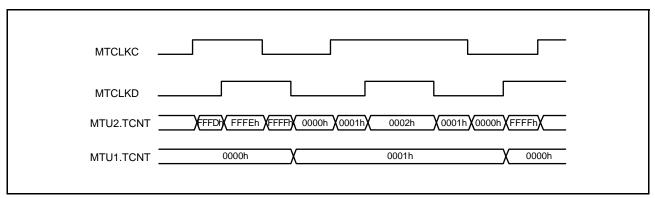

|    | 20.3.4   | Cascaded Operation                                                                         | 434 |

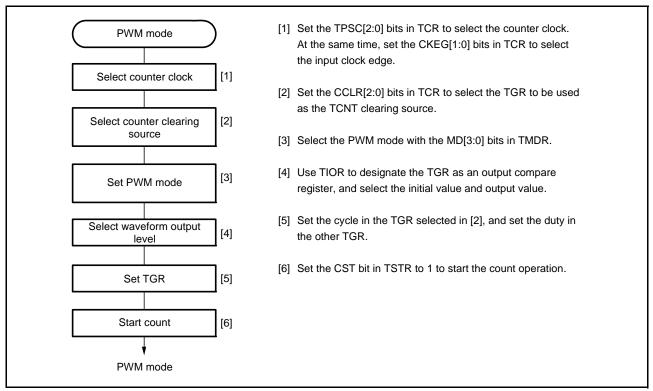

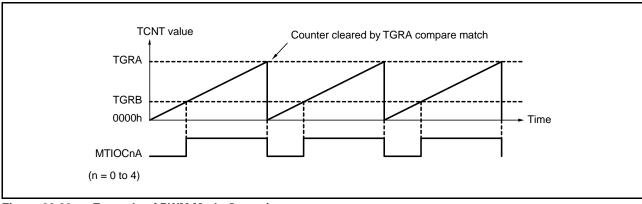

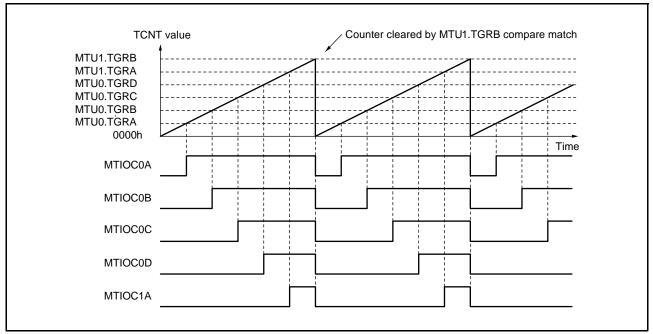

|    | 20.3.5   | PWM Modes                                                                                  | 439 |

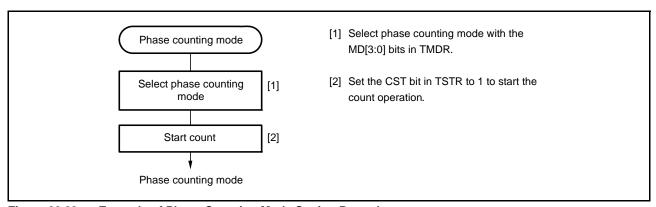

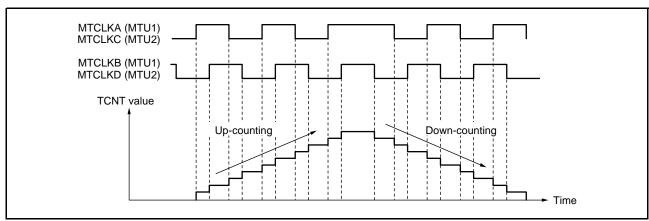

|    | 20.3.6   | Phase Counting Mode                                                                        | 443 |

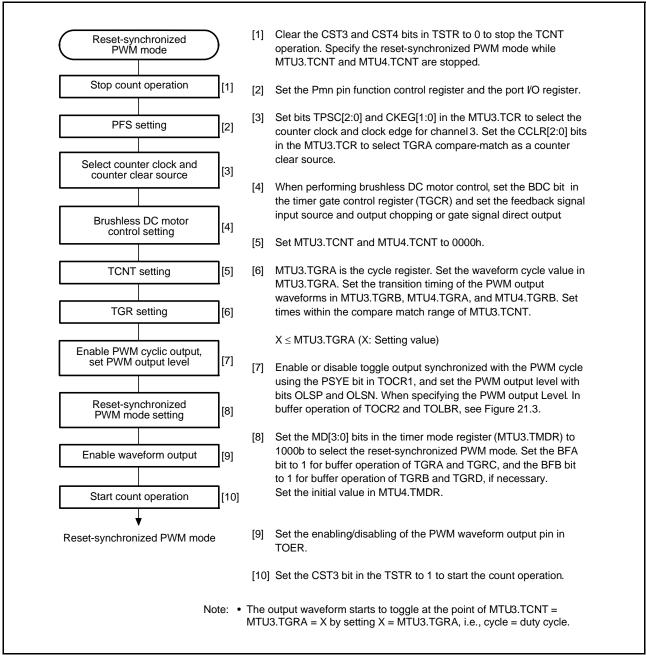

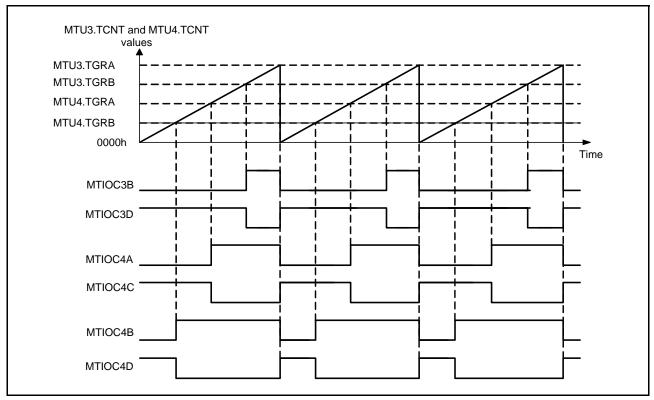

|    | 20.3.7   | Reset-Synchronized PWM Mode                                                                | 449 |

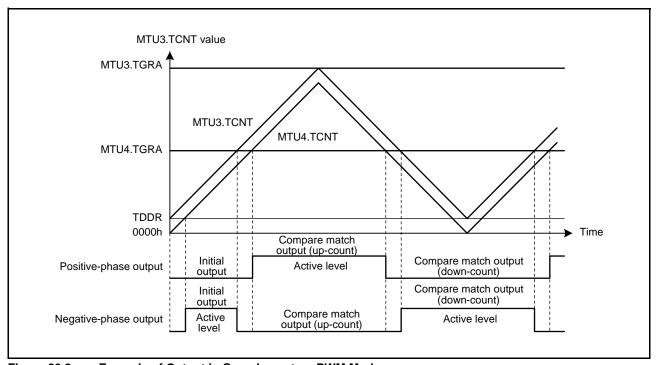

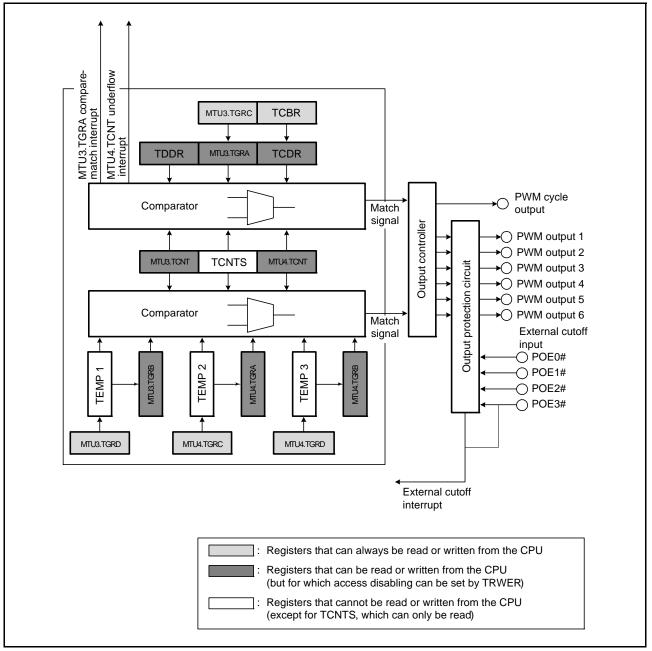

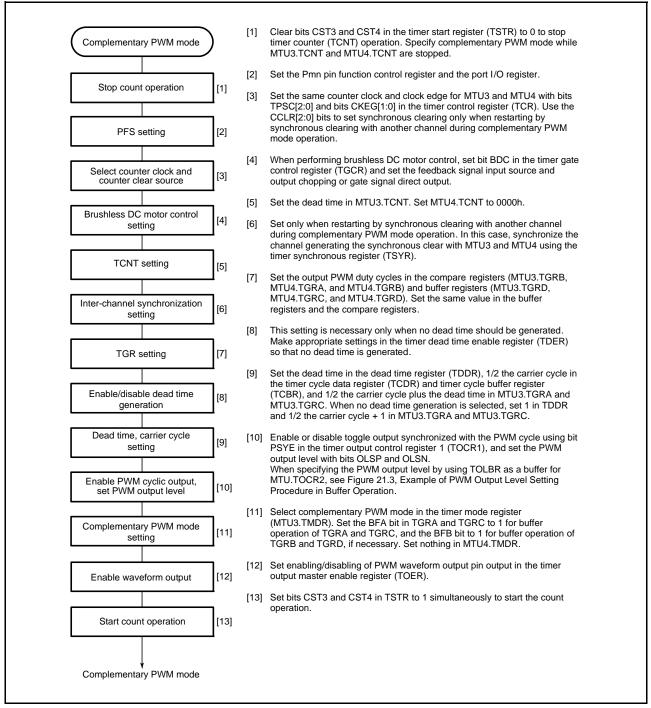

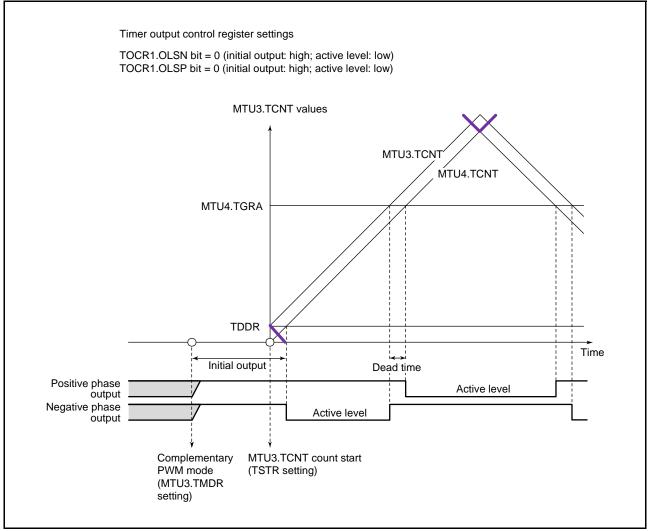

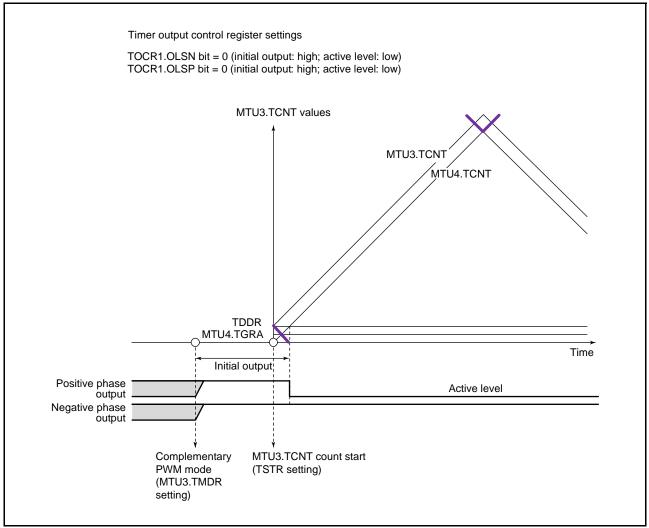

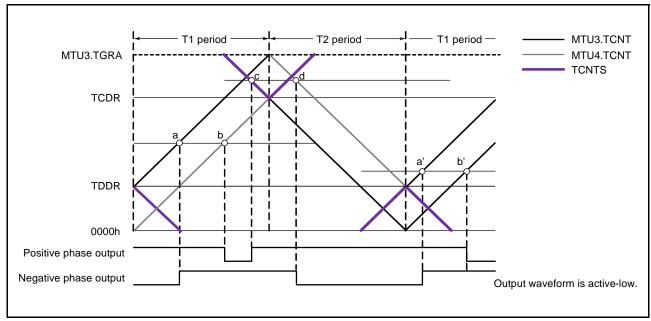

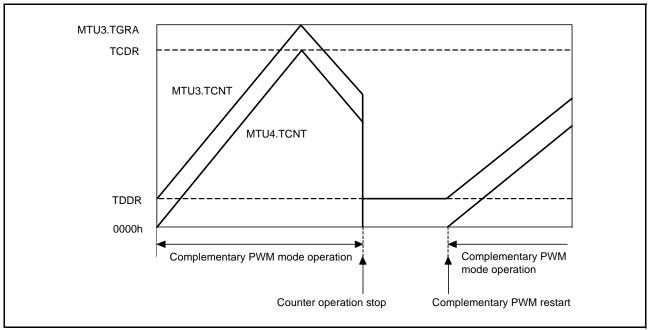

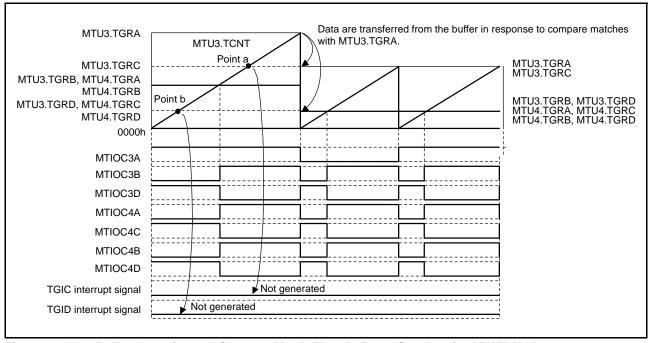

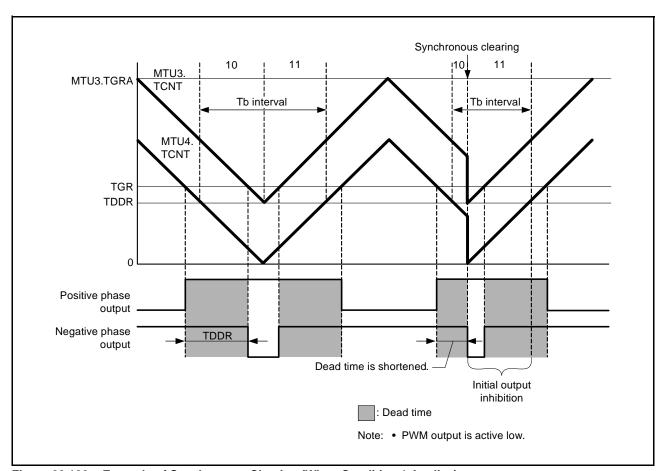

|    | 20.3.8   | Complementary PWM Mode                                                                     | 452 |

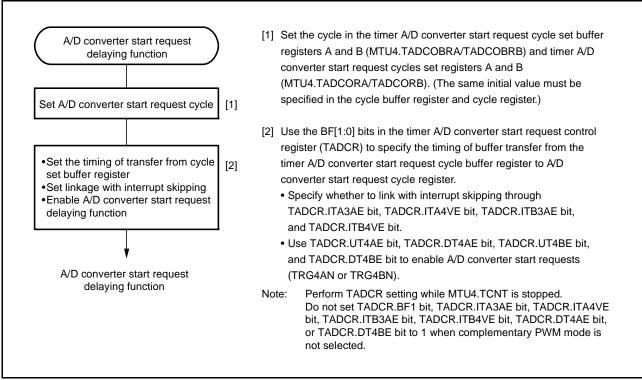

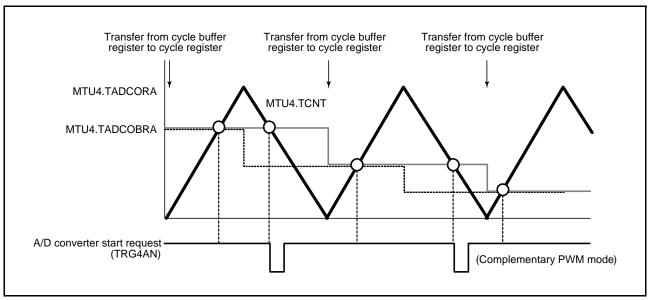

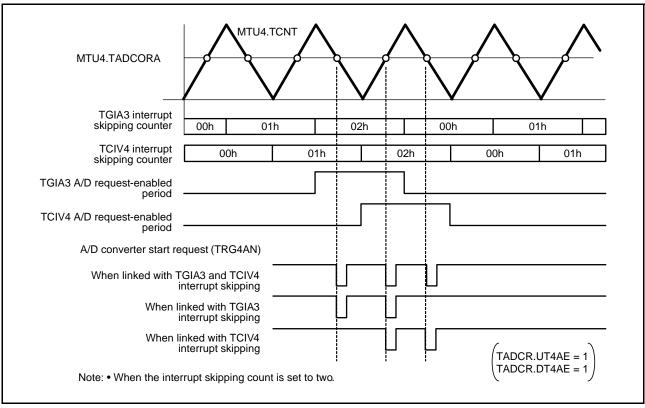

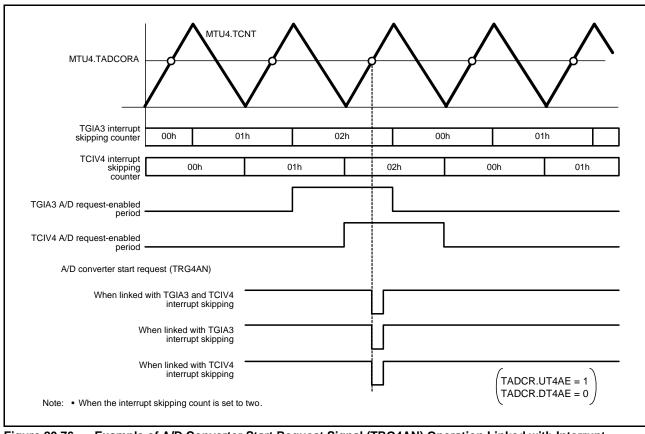

|    | 20.3.9   | A/D Converter Start Request Delaying Function                                              | 484 |

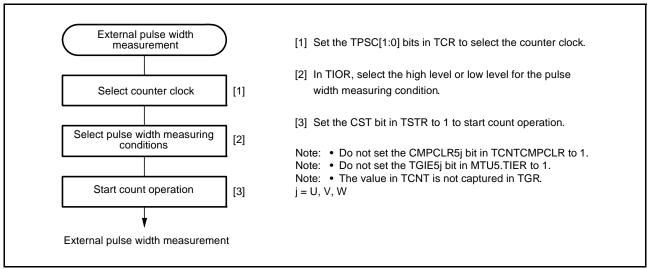

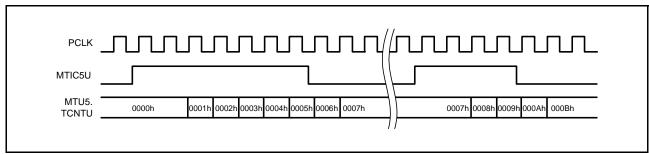

|    | 20.3.10  | External Pulse Width Measurement                                                           | 487 |

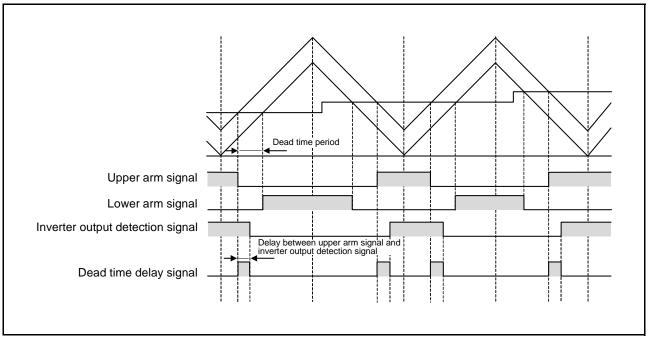

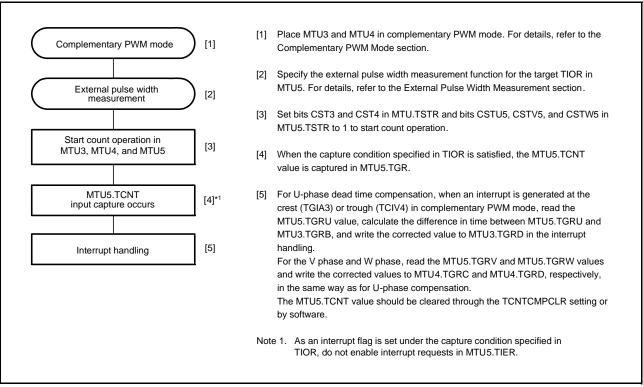

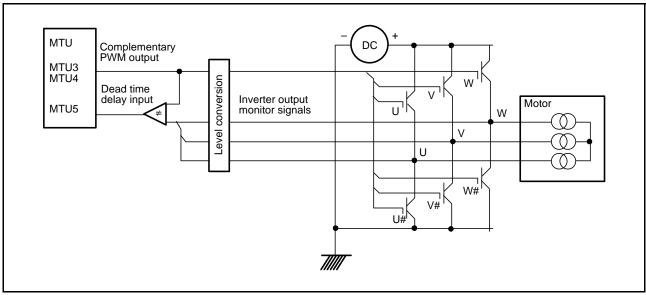

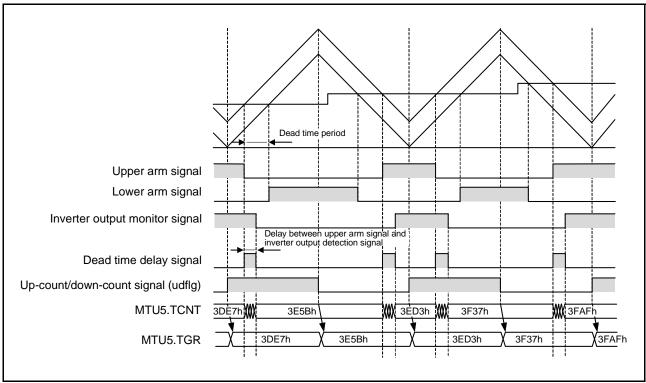

|    | 20.3.11  | Dead Time Compensation                                                                     | 488 |

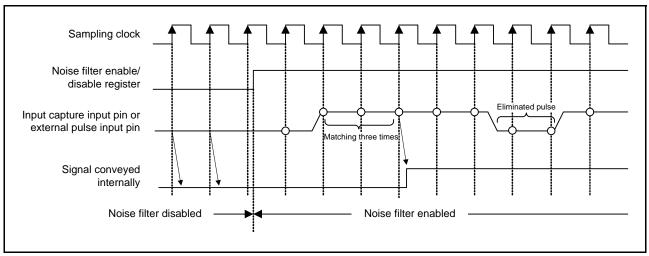

|    | 20.3.12  | Noise Filter                                                                               | 491 |

| 20 | .4 Inter | rupt Sources                                                                               | 492 |

|    | 20.4.1   | Interrupt Sources and Priorities                                                           | 492 |

|    | 20.4.2   | DTC Activation                                                                             | 493 |

|    | 20.4.3   | A/D Converter Activation                                                                   | 493 |

| 20 | .5 Oper  | ration Timing                                                                              | 495 |

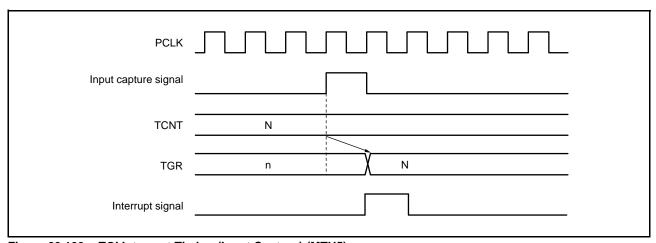

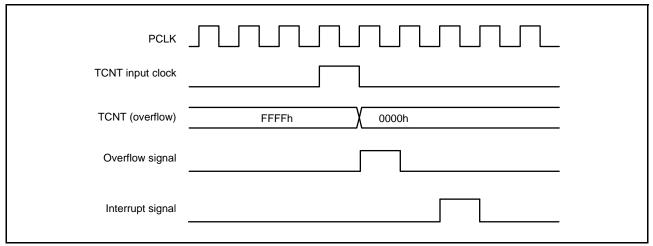

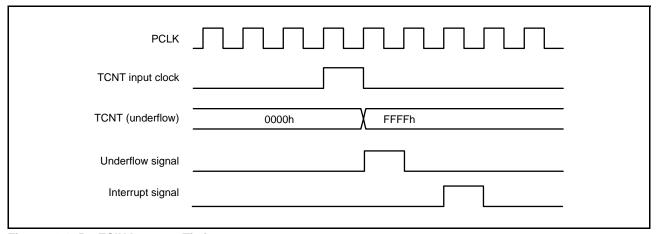

|    | 20.5.1   | Input/Output Timing                                                                        | 495 |

|    | 20.5.2   | Interrupt Signal Timing                                                                    | 501 |

| 20 | .6 Usag  | ge Notes                                                                                   | 504 |

|    | 20.6.1   | Module Clock Stop Mode Setting                                                             | 504 |

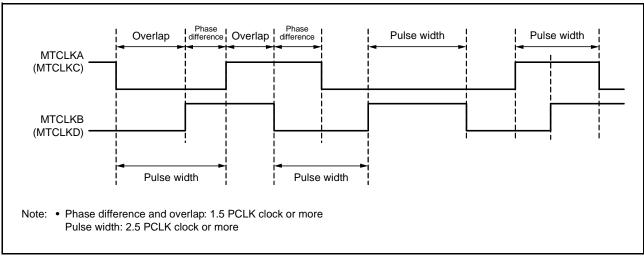

|    | 20.6.2   | Input Clock Restrictions                                                                   | 504 |

|    | 20.6.3   | Note on Cycle Setting                                                                      | 505 |

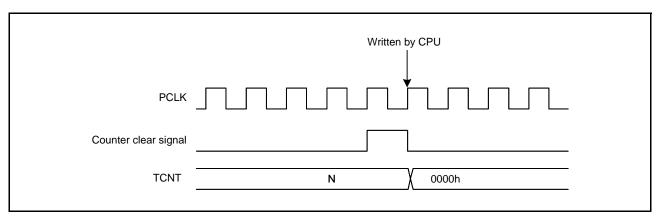

|    | 20.6.4   | Contention between TCNT Write and Clear Operations                                         | 505 |

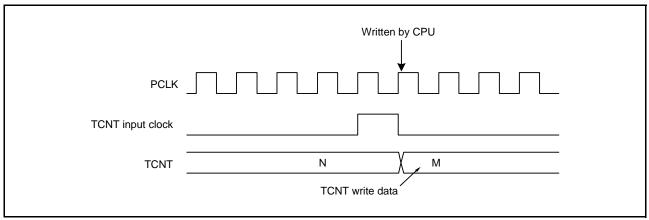

|    | 20.6.5   | Contention between TCNT Write and Increment Operations                                     | 506 |

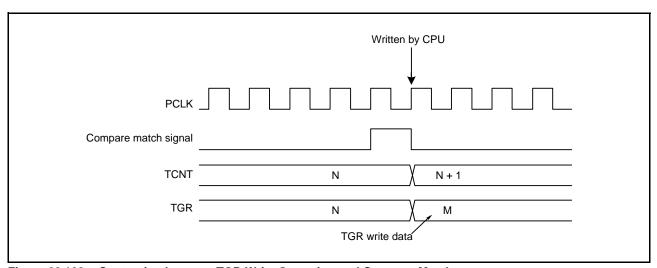

|    | 20.6.6   | Contention between TGR Write Operation and Compare Match                                   | 506 |

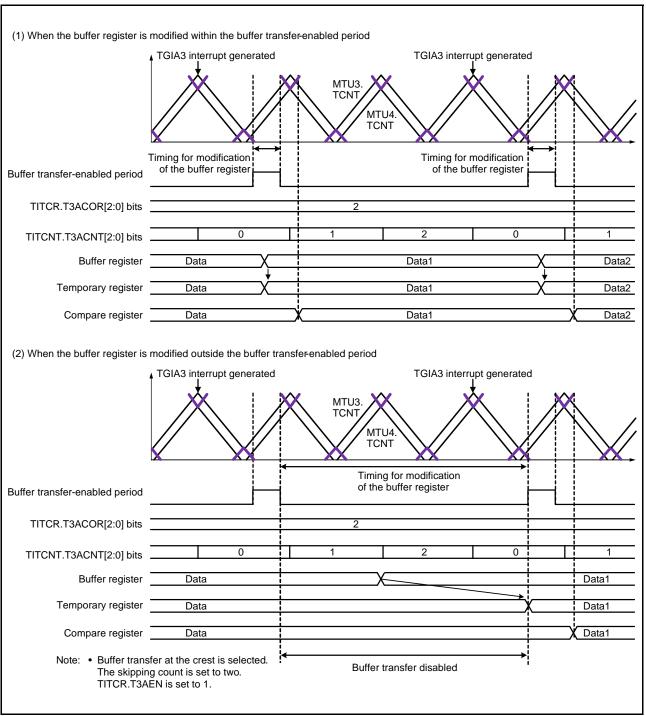

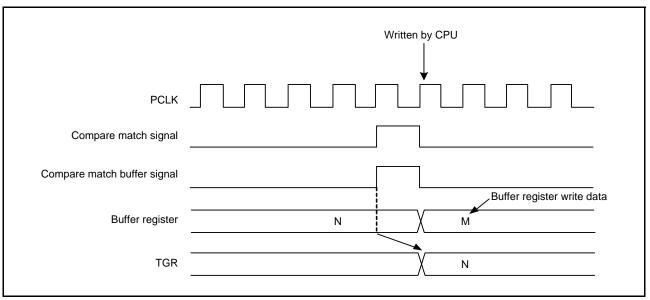

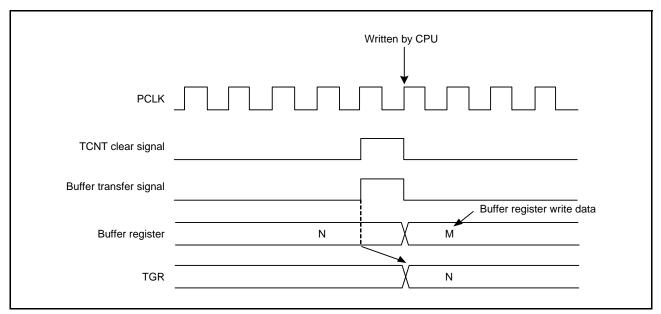

|    | 20.6.7   | Contention between Buffer Register Write Operation and Compare Match                       | 507 |

|    | 20.6.8   | Contention between Buffer Register Write and TCNT Clear Operations                         | 508 |

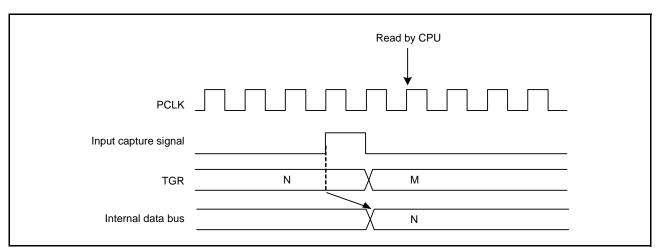

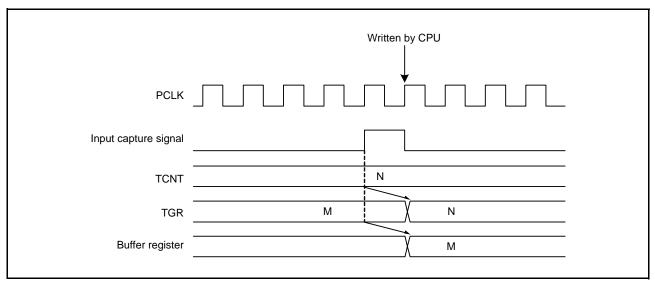

|    | 20.6.9   | Contention between TGR Read Operation and Input Capture                                    | 509 |

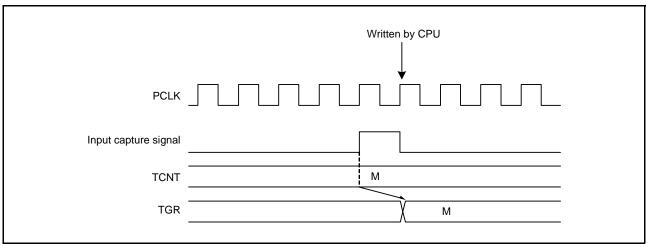

|    | 20.6.10  | Contention between TGR Write Operation and Input Capture                                   | 510 |

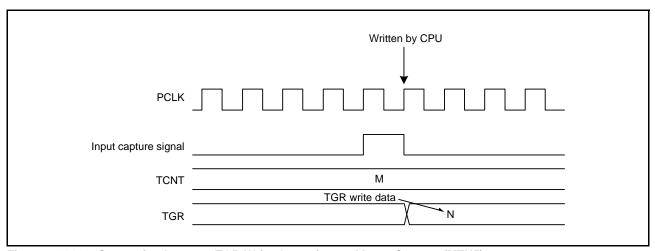

|    | 20.6.11  | Contention between Buffer Register Write Operation and Input Capture                       | 511 |

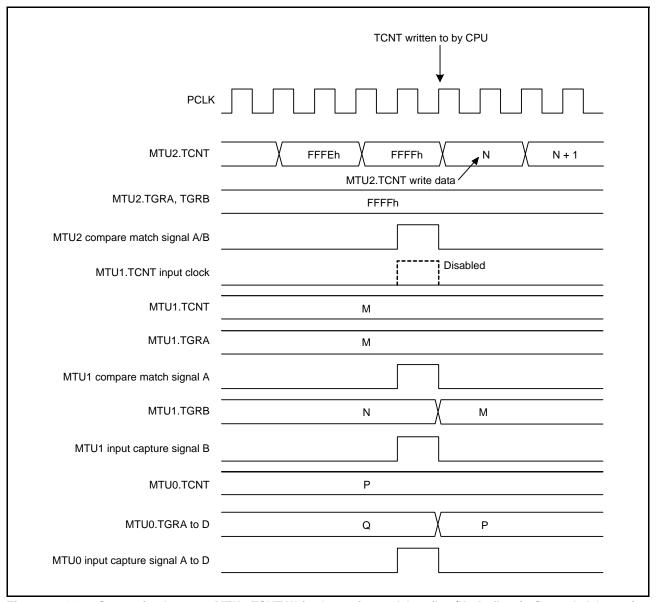

|    | 20.6.12  | Contention between MTU2.TCNT Write Operation and Overflow/ Underflow in Cascaded Operation | 512 |

|    | 20.6.13  | Counter Value when Stopped in Complementary PWM Mode                                       |     |

|    |          |                                                                                            |     |

|     | 20.6.14      | Buffer Operation Setting in Complementary PWM Mode                                                  | 513 |

|-----|--------------|-----------------------------------------------------------------------------------------------------|-----|

|     | 20.6.15      | Buffer Operation and Compare Match Flags in Reset-Synchronized PWM Mode                             | 514 |

|     | 20.6.16      | Overflow Flags in Reset-Synchronized PWM Mode                                                       | 515 |

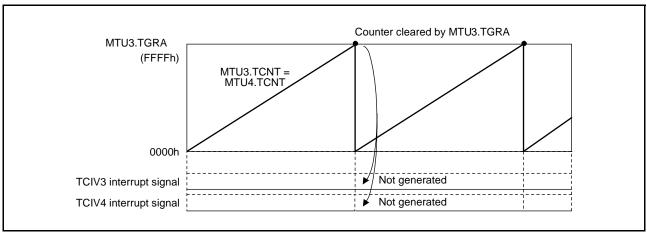

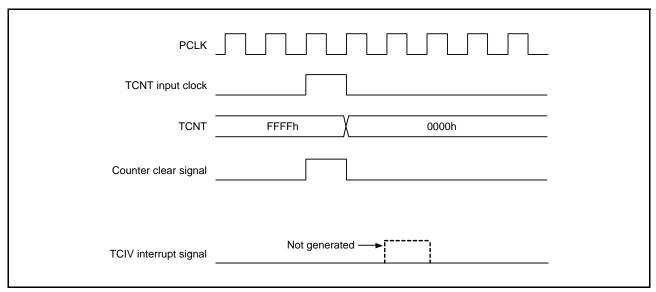

|     | 20.6.17      | Contention between Overflow/Underflow and Counter Clearing                                          | 516 |

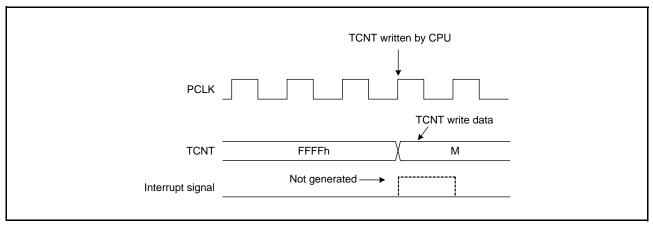

|     | 20.6.18      | Contention between TCNT Write Operation and Overflow/Underflow                                      | 517 |

|     | 20.6.19      | Note on Transition from Normal Mode or PWM Mode 1 to<br>Reset-Synchronized PWM Mode                 | 517 |

|     | 20.6.20      | Output Level in Complementary PWM Mode or Reset-Synchronized PWM Mode                               | 517 |

|     | 20.6.21      | Interrupts during Periods in the Module-Stop State                                                  | 517 |

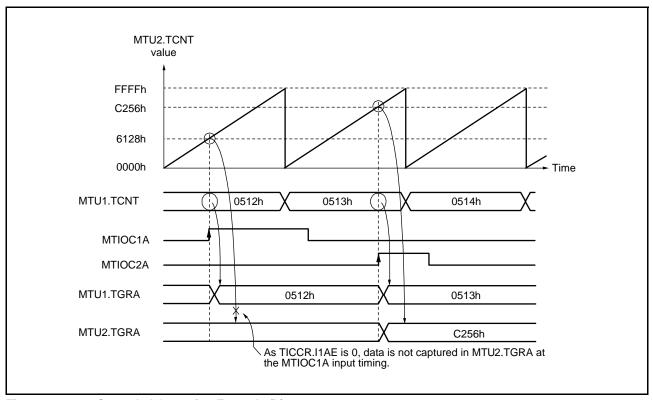

|     | 20.6.22      | Simultaneous Input Capture in MTU1.TCNT and MTU2.TCNT in Cascade Connection                         | 518 |

|     | 20.6.23      | Notes When Complementary PWM Mode Output Protection Functions are Not Used                          | 518 |

|     | 20.6.24      | Point for Caution Regarding MTU5.TCNT and MTU5.TGR Registers                                        | 518 |

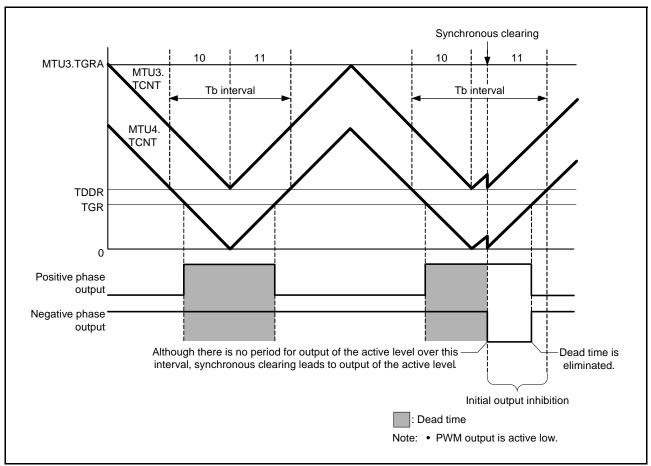

|     | 20.6.25      | Points for Caution to Prevent Malfunctions in Synchronous Clearing for Complementary PWM Mode       | 519 |

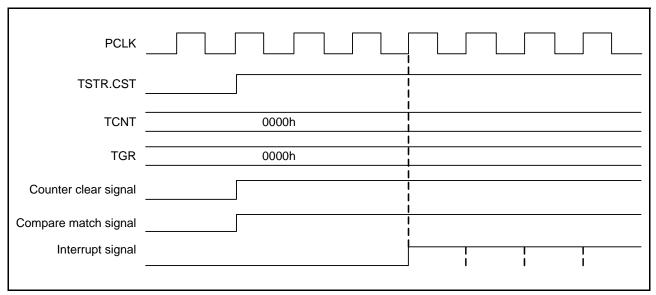

|     | 20.6.26      | Continuous Output of Interrupt Signal in Response to a Compare Match                                | 521 |

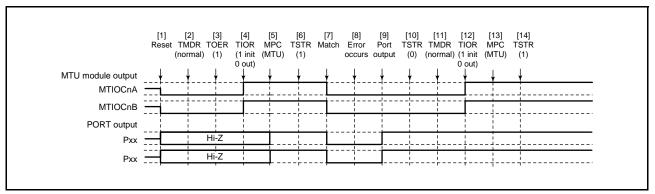

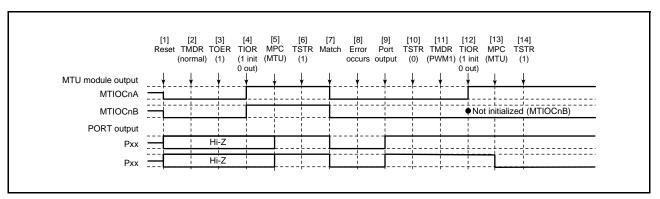

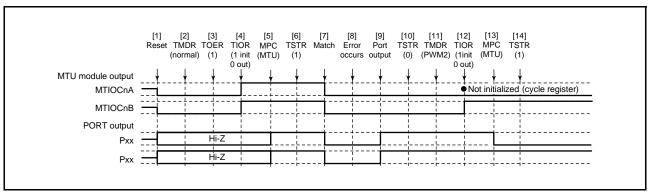

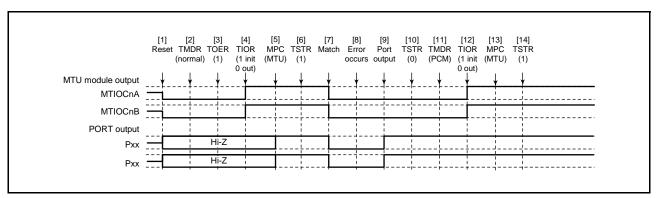

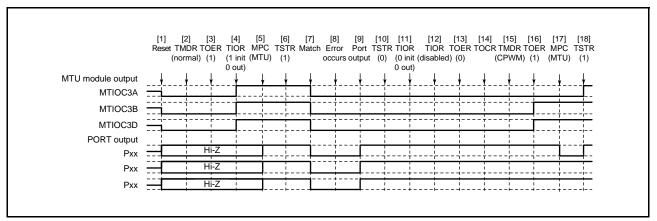

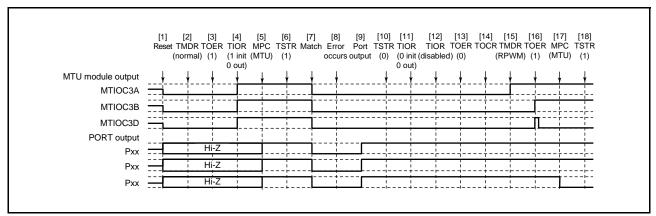

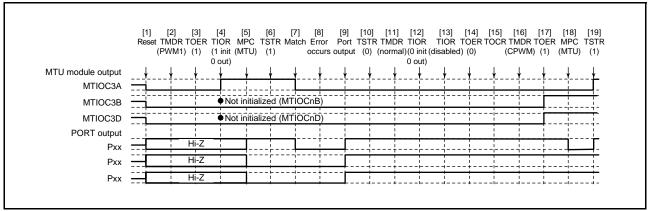

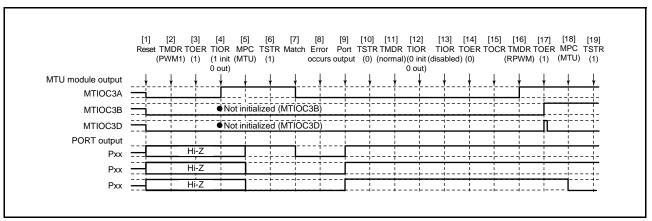

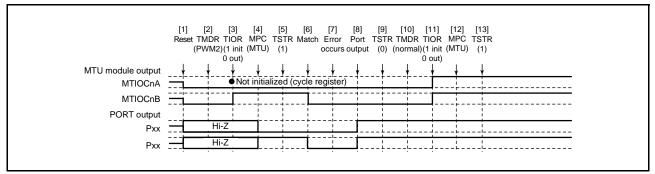

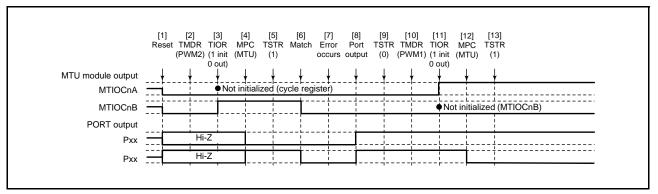

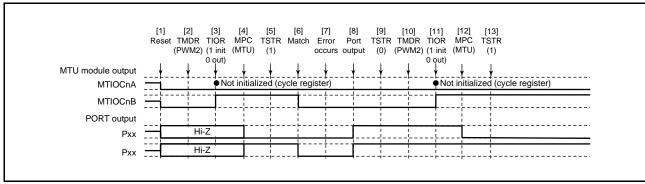

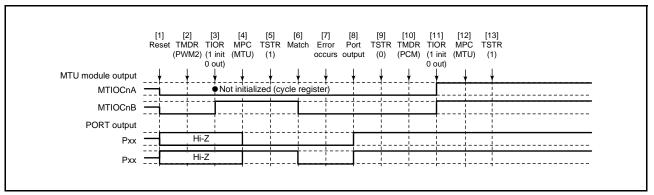

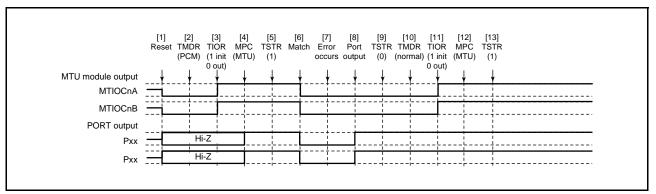

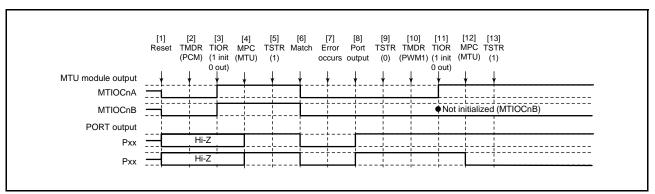

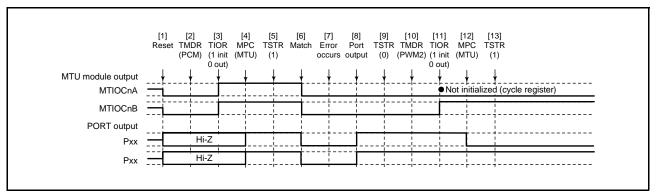

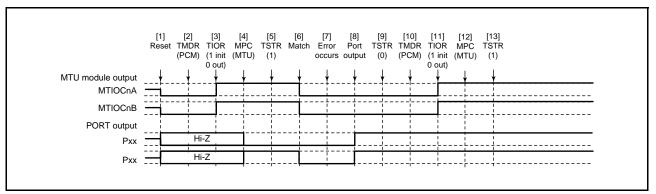

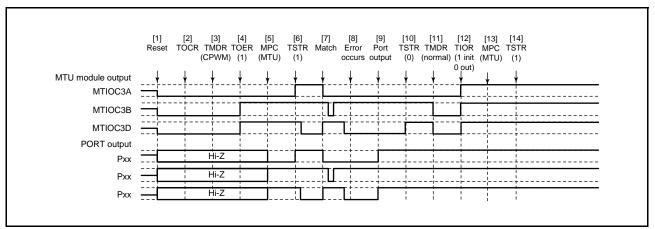

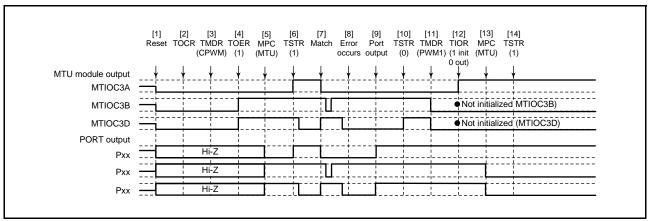

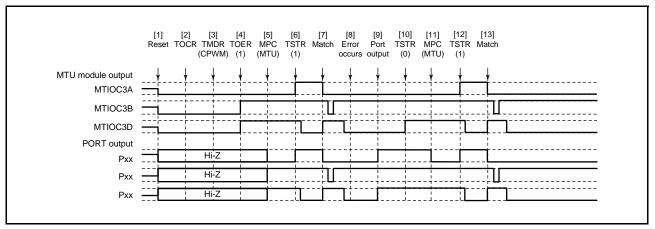

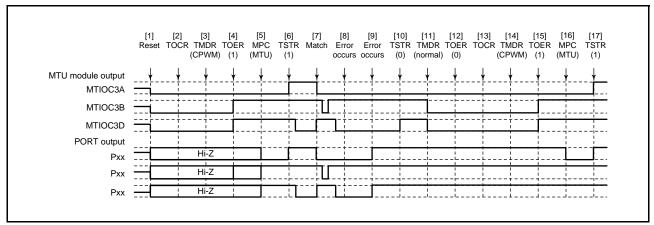

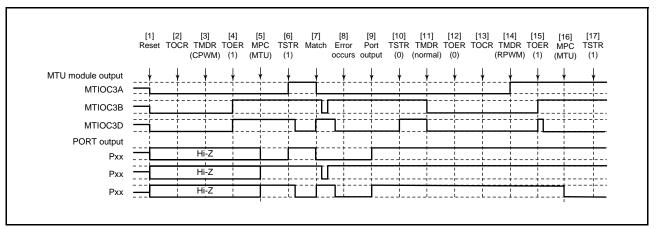

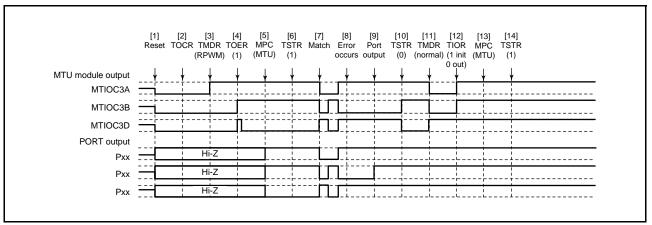

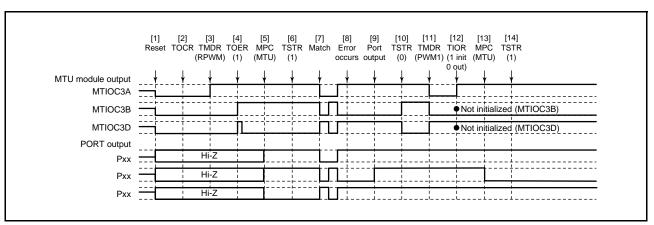

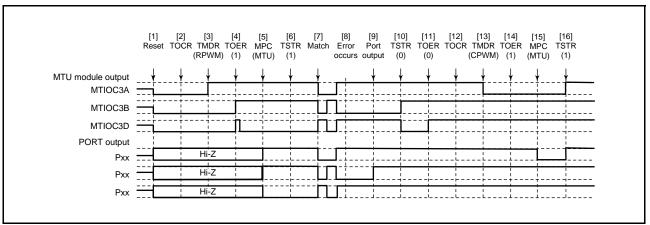

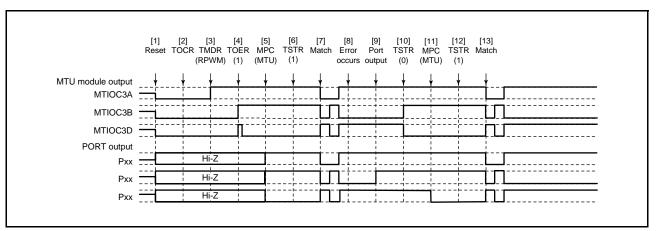

|     | 20.7 MT      | U Output Pin Initialization                                                                         | 522 |

|     | 20.7.1       | Operating Modes                                                                                     | 522 |

|     | 20.7.2       | Operation in Case of Re-Setting Due to Error during Operation                                       | 522 |

|     | 20.7.3       | Overview of Pin Initialization Procedures and<br>Mode Transitions in Case of Error during Operation | 523 |

|     | 20.8 Link    | Operation by ELC                                                                                    | 552 |

|     | 20.8.1       | Event Signal Output to ELC                                                                          | 552 |

|     | 20.8.2       | MTU Operation by Event Signal Reception from ELC                                                    | 552 |

|     | 20.8.3       | Usage Notes on MTU by Event Signal Reception from ELC                                               | 553 |

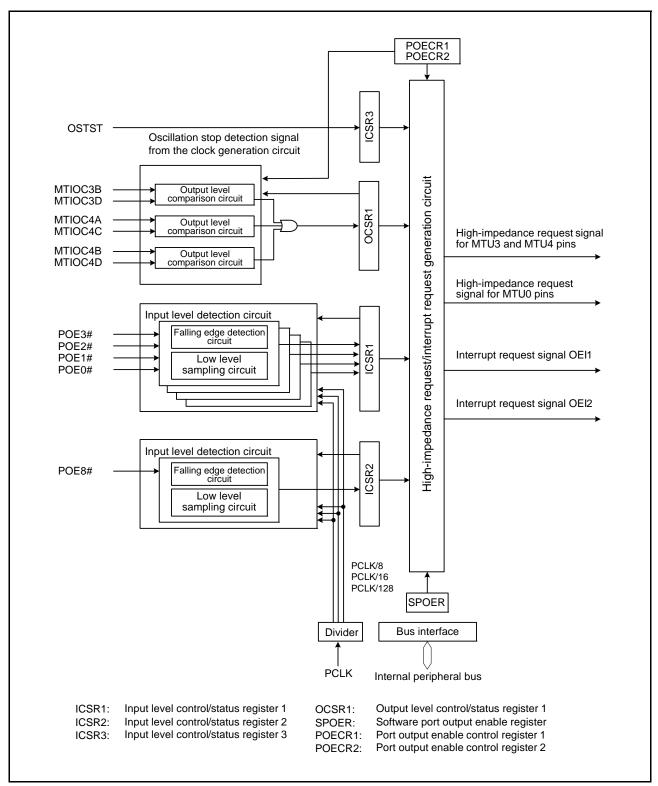

| 21. | . Port Outpu | ıt Enable 2 (POE2a)                                                                                 | 554 |

|     | 21.1 Ove     | rview                                                                                               | 554 |

|     | 21.2 Reg     | ister Descriptions                                                                                  | 557 |

|     | 21.2.1       | Input Level Control/Status Register 1 (ICSR1)                                                       | 557 |

|     | 21.2.2       | Output Level Control/Status Register 1 (OCSR1)                                                      | 559 |

|     | 21.2.3       | Input Level Control/Status Register 2 (ICSR2)                                                       | 560 |

|     | 21.2.4       | Software Port Output Enable Register (SPOER)                                                        | 561 |

|     | 21.2.5       | Port Output Enable Control Register 1 (POECR1)                                                      | 562 |

|     | 21.2.6       | Port Output Enable Control Register 2 (POECR2)                                                      | 563 |

|     | 21.2.7       | Input Level Control/Status Register 3 (ICSR3)                                                       | 564 |

|     | 21.3 Ope     | ration                                                                                              | 565 |

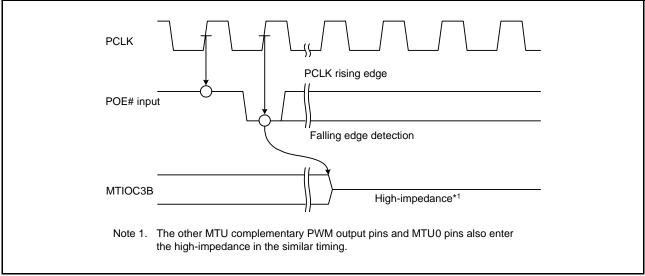

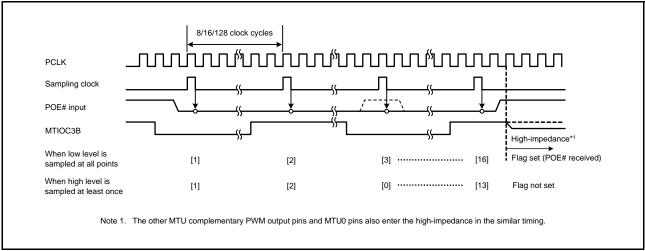

|     | 21.3.1       | Input Level Detection Operation                                                                     | 567 |

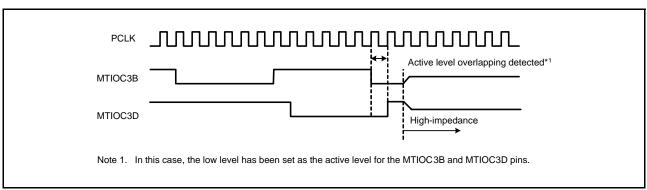

|     | 21.3.2       | Output-Level Compare Operation                                                                      | 568 |

|     | 21.3.3       | High-Impedance Control Using Registers                                                              | 569 |

|     | 21.3.4       | High-Impedance Control on Detection of Stopped Oscillation                                          | 569 |

|     | 21.3.5       | Release from the High-Impedance                                                                     | 569 |

|     | 21.4 Inter   | тupts                                                                                               | 570 |

|     | 21.5 Usaş    | ge Notes                                                                                            | 570 |

|     | 21.5.1  | Transitions to Software Standby Mode                                             | 570 |

|-----|---------|----------------------------------------------------------------------------------|-----|

|     | 21.5.2  | When POE Is Not Used                                                             | 570 |

|     | 21.5.3  | Specifying Pins Corresponding to the MTU                                         | 570 |

| 22. | Comp    | are Match Timer (CMT)                                                            | 571 |

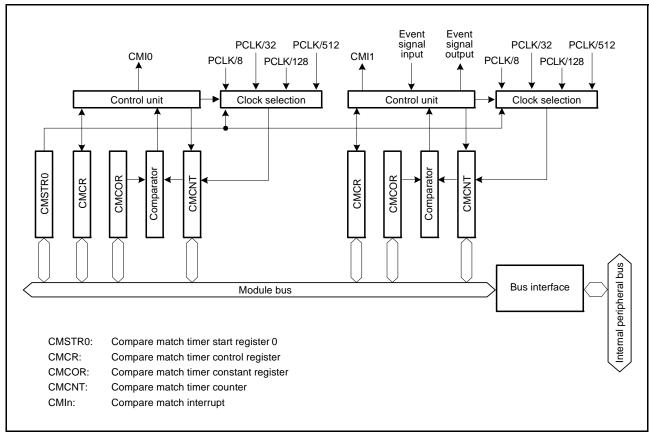

|     | 22.1    | Overview                                                                         | 571 |

|     | 22.2    | Register Descriptions                                                            | 572 |

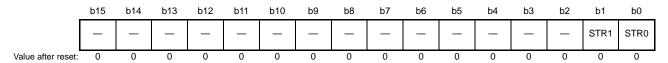

|     | 22.2.1  | Compare Match Timer Start Register 0 (CMSTR0)                                    | 572 |

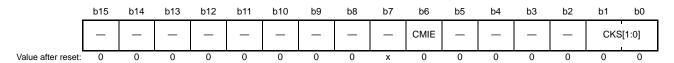

|     | 22.2.2  | Compare Match Timer Control Register (CMCR)                                      | 572 |

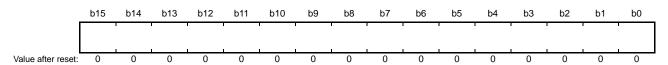

|     | 22.2.3  | Compare Match Counter (CMCNT)                                                    | 573 |

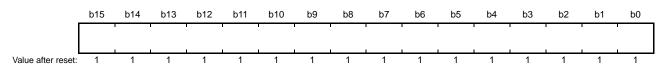

|     | 22.2.4  | Compare Match Constant Register (CMCOR)                                          | 573 |

|     | 22.3    | Operation                                                                        | 574 |

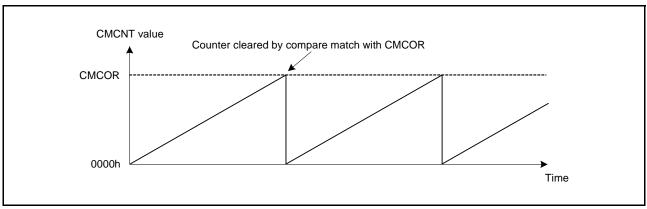

|     | 22.3.1  | Periodic Count Operation                                                         | 574 |

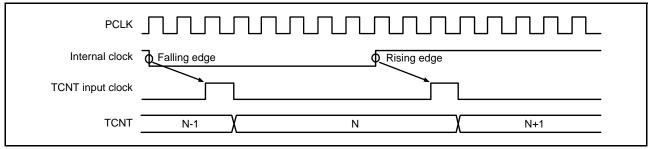

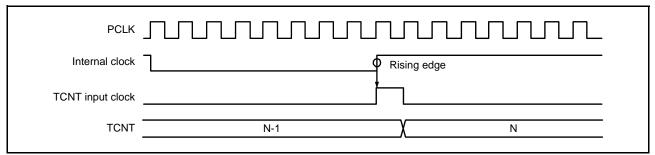

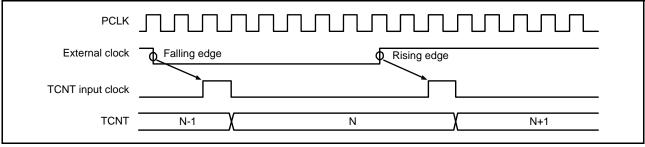

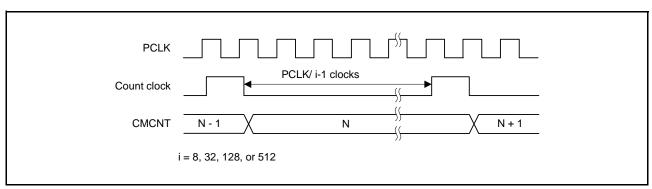

|     | 22.3.2  | CMCNT Count Timing                                                               | 574 |

|     | 22.4    | Interrupts                                                                       | 575 |

|     | 22.4.1  | Interrupt Sources                                                                | 575 |

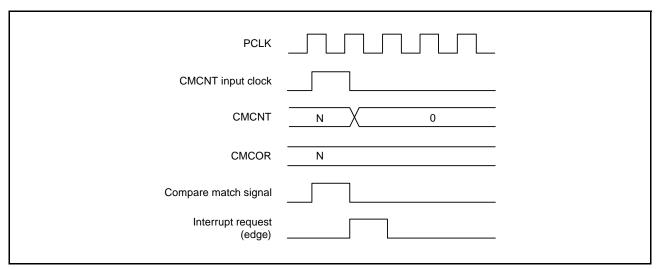

|     | 22.4.2  | Timing of Compare Match Interrupt Generation                                     | 575 |

|     | 22.5    | Link Operations by ELC                                                           | 576 |

|     | 22.5.1  | Event Signal Output to ELC                                                       | 576 |

|     | 22.5.2  | CMT Operation when Receiving an Event Signal from ELC                            | 576 |

|     | 22.5.3  | Notes on Operating CMT According to an Event Signal from ELC                     | 576 |

|     | 22.6    | Usage Notes                                                                      | 577 |

|     | 22.6.1  | Setting the Module Stop Function                                                 | 577 |

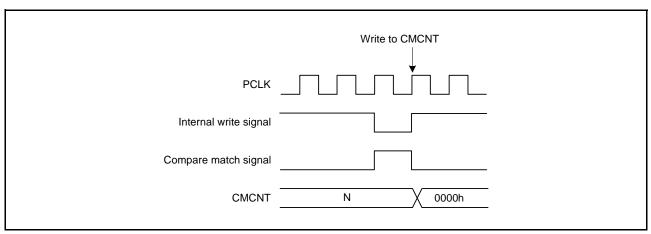

|     | 22.6.2  | Conflict between Write and Compare-Match Processes of CMCNT                      | 577 |

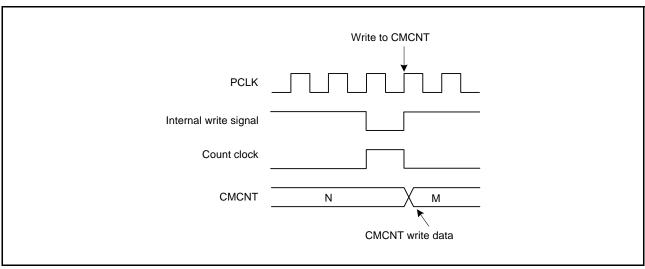

|     | 22.6.3  | Conflict between Write and Count-Up Processes of CMCNT                           | 577 |

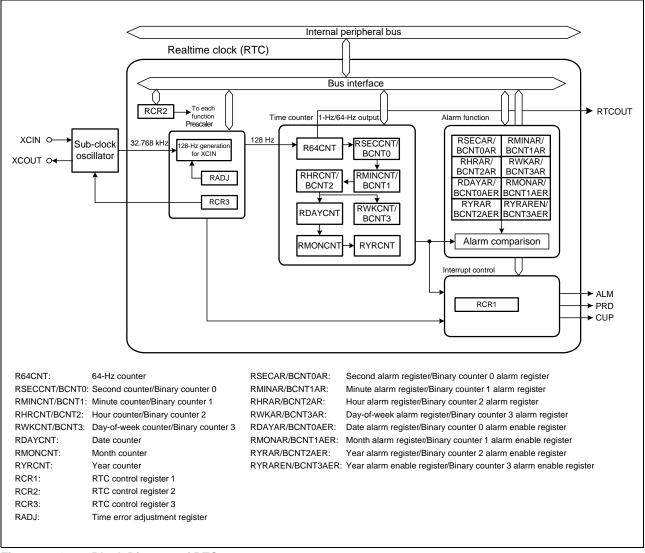

| 23. | Realtii | me Clock (RTCA)                                                                  | 578 |

|     | 23.1    | Overview                                                                         | 578 |

|     | 23.2    | Register Descriptions                                                            | 580 |

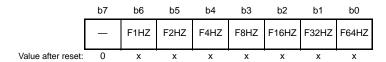

|     | 23.2.1  | 64-Hz Counter (R64CNT)                                                           | 580 |

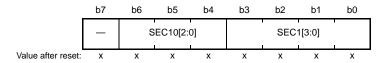

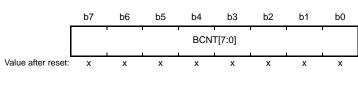

|     | 23.2.2  | Second Counter (RSECCNT)/Binary Counter 0 (BCNT0)                                | 581 |

|     | 23.2.3  | Minute Counter (RMINCNT)/Binary Counter 1 (BCNT1)                                | 582 |

|     | 23.2.4  | Hour Counter (RHRCNT)/Binary Counter 2 (BCNT2)                                   | 583 |

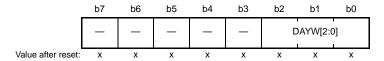

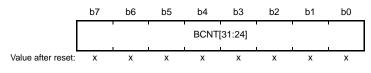

|     | 23.2.5  | Day-of-Week Counter (RWKCNT)/Binary Counter 3 (BCNT3)                            | 584 |

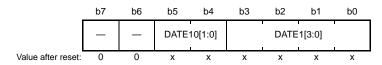

|     | 23.2.6  | Date Counter (RDAYCNT)                                                           | 585 |

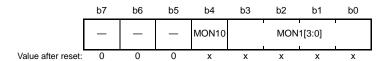

|     | 23.2.7  | Month Counter (RMONCNT)                                                          | 586 |

|     | 23.2.8  | Year Counter (RYRCNT)                                                            | 586 |

|     | 23.2.9  | Second Alarm Register (RSECAR)/Binary Counter 0 Alarm Register (BCNT0AR)         | 587 |

|     | 23.2.1  | 0 Minute Alarm Register (RMINAR)/Binary Counter 1 Alarm Register (BCNT1AR)       | 588 |

|     | 23.2.1  | 1 Hour Alarm Register (RHRAR)/Binary Counter 2 Alarm Register (BCNT2AR)          | 589 |

|     | 23.2.1  | 2 Day-of-Week Alarm Register (RWKAR)/Binary Counter 3 Alarm Register (BCNT3AR) . | 590 |

|     | 23.2.1  | Date Alarm Register (RDAYAR)/Binary Counter 0 Alarm Enable Register (BCNT0AER)   | 591 |

|     |         |                                                                                  |     |

| 23     | 3.2.14   | Month Alarm Register (RMONAR)/Binary Counter 1 Alarm Enable Register (BCNT1AER)        | 592 |

|--------|----------|----------------------------------------------------------------------------------------|-----|