Product Innovation From

Power Operational Amplifier

## FEATURES

- A Unique (Patent Pending) Technique for Very Low Quiescent Current

- ♦ Over 350 V/µs Slew Rate

- Wide Supply Voltage

- Single Supply: 20V To 200V

- Split Supplies: ± 10V To ± 100V

- ♦ Output Current 75mA Cont.; 100mA Pk

- Up to 23 Watt Dissipation Capability

- Over 200 kHz Power Bandwidth

# **APPLICATIONS**

- Piezoelectric Positioning and Actuation

- Electrostatic Deflection

- Deformable Mirror Actuators

- Chemical and Biological Stimulators

# DESCRIPTION

The PA69 is a high voltage, high speed, low idle current op-amp capable of delivering up to 100mA peak output current. Due to the dynamic biasing of the input stage, it can achieve slew rates over 350V/µs, while only consuming less than 1mA of idle current. External phase compensation allows great flexibility for the user to optimize bandwidth and stability.

The output stage is protected with user selected current limit resistor. For the selection of this current limiting resistor, pay close attention to the SOA curves for each package type. Proper heatsinking is required for maximum reliability.

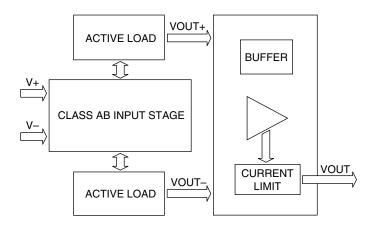

# **BLOCK DIAGRAM**

12-Pin SIP PACKAGE STYLE EU LEAD FORM EW

# CHARACTERISTICS AND SPECIFICATIONS

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                | Symbol | Min            | Max             | Units |

|------------------------------------------|--------|----------------|-----------------|-------|

| SUPPLY VOLTAGE, $+V_s$ to $-V_s$         |        |                | 200             | V     |

| OUTPUT CURRENT, peak (200ms), within SOA |        |                | 200             | mA    |

| POWER DISSIPATION, internal, DC          |        |                | 23              | W     |

| INPUT VOLTAGE, differential              |        | -15            | 15              | V     |

| INPUT VOLTAGE, common mode               |        | V <sub>s</sub> | +V <sub>s</sub> | V     |

| TEMPERATURE, pin solder, 10s             |        |                | 260             | °C    |

| TEMPERATURE, junction (Note 2)           |        |                | 150             | °C    |

| TEMPERATURE RANGE, storage               |        | -55            | 125             | °C    |

| OPERATING TEMPERATURE, case              |        | -40            | 125             | °C    |

## **SPECIFICATIONS**

| Parameter                            | Test Conditions                                 | Min | Тур                    | Мах                   | Units  |

|--------------------------------------|-------------------------------------------------|-----|------------------------|-----------------------|--------|

| INPUT                                | · · · · ·                                       |     |                        |                       |        |

| OFFSET VOLTAGE                       |                                                 | -25 | 8                      | 25                    | mV     |

| OFFSET VOLTAGE vs. temperature       | 0 to 125°C (Case Temperature)                   |     | -63                    |                       | μV/°C  |

| OFFSET VOLTAGE vs. supply            |                                                 |     |                        | 32                    | μV/V   |

| BIAS CURRENT, initial                |                                                 |     | 8.5                    | 200                   | pА     |

| OFFSET CURRENT, initial              |                                                 |     | 12                     | 400                   | рА     |

| INPUT RESISTANCE, DC                 |                                                 |     | 10 <sup>8</sup>        |                       | Ω      |

| COMMON MODE VOLTAGE RANGE, pos.      |                                                 |     | +V <sub>s</sub> - 2    |                       | V      |

| COMMON MODE VOLTAGE RANGE, neg.      |                                                 |     | -V <sub>s</sub> + 5.5  |                       | V      |

| COMMON MODE REJECTION, DC            |                                                 | 90  | 118                    |                       | dB     |

| NOISE                                | 700KHz                                          |     | 418                    |                       | µV RMS |

| NOISE, V <sub>o</sub> NOISE          |                                                 |     | 500                    |                       | nV/√Hz |

| GAIN                                 |                                                 |     |                        |                       |        |

| OPEN LOOP @ 1Hz                      |                                                 | 89  | 120                    |                       | dB     |

| GAIN BANDWIDTH PRODUCT @ 1MHz        |                                                 |     | 1                      |                       | MHz    |

| PHASE MARGIN                         | Full temperature range                          |     | 50                     |                       | 0      |

| OUTPUT                               | · · · · · ·                                     |     |                        |                       |        |

| VOLTAGE SWING                        | I <sub>o</sub> = 10mA                           |     | V <sub>s</sub>   - 2   |                       | V      |

| VOLTAGE SWING                        | I <sub>o</sub> = 75mA                           |     | V <sub>s</sub>   - 8.6 | V <sub>s</sub>   - 12 | V      |

| CURRENT, continuous, DC              |                                                 | 75  |                        |                       | mA     |

| SLEW RATE                            | Package Tab connected to GND                    | 100 | 350                    |                       | V/µS   |

| SETTLING TIME, to 0.1%               | 5V Step (No Compensation)                       |     | 1                      |                       | μS     |

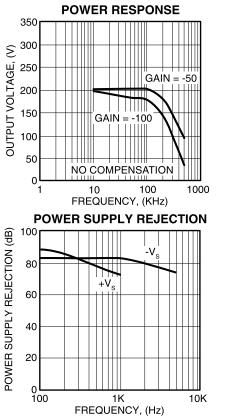

| POWER BANDWIDTH, 300V <sub>P.P</sub> | +V <sub>s</sub> = 160V, -V <sub>s</sub> = -160V |     | 200                    |                       | kHz    |

| OUTPUT RESISTANCE, No load           | R <sub>cl</sub> = 6.2Ω                          |     | 44                     |                       | Ω      |

| POWER SUPPLY                         | · · · · · · · · · · · · · · · · · · ·           |     |                        |                       |        |

| VOLTAGE                              |                                                 | ±10 | ±50                    | ±100                  | V      |

| CURRENT, quiescent (Note 5)          | ±100V Supply                                    | 0.2 | 0.7                    | 2.5                   | mA     |

| Parameter                        | Test Conditions        | Min | Тур   | Max | Units |

|----------------------------------|------------------------|-----|-------|-----|-------|

| THERMAL                          |                        |     |       |     |       |

| RESISTANCE, DC, junction to case | Full temperature range |     | 5.5   |     | °C/W  |

| RESISTANCE, DC, junction to air  | Full temperature range |     | 12.21 |     | °C/W  |

| TEMPERATURE RANGE, case          |                        | -40 |       | 125 | °C    |

- NOTES: 1. Unless otherwise noted:  $T_c = 25^{\circ}C$ , DC input specifications are ± value given, power supply voltage is typical rating.

- 2. Long term operation at the maximum junction temperature will result in reduced product life. Derate power dissipation to achieve high MTTF.

- 3.  $+V_s$  and  $-V_s$  denote the positive and negative supply voltages of the output stage.

- 4. Rating applies if output current alternates between both output transistors at a rate faster than 60Hz.

- 5. Supply current increases with signal frequency. See graph on page 4.

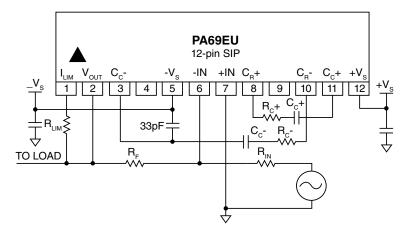

#### **EXTERNAL CONNECTIONS**

#### **TYPICAL APPLICATION CIRCUIT**

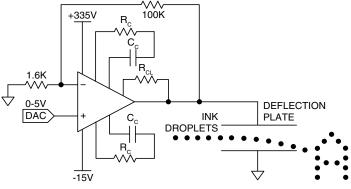

The PA69 is ideally suited for driving continuous drop ink jet printers, in both piezo actuation and deflection applications. The high voltage of the amplifier creates an electrostatic field on the deflection plates to control the position of the ink droplets. The rate at which droplets can be printed is directly related to the rate at which the amplifier can drive the plate to a different electrostatic field strength.

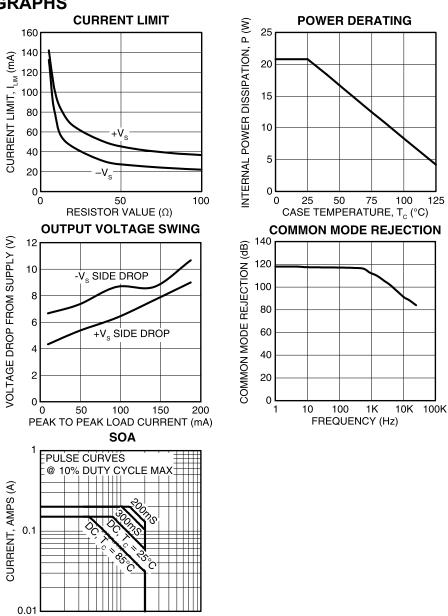

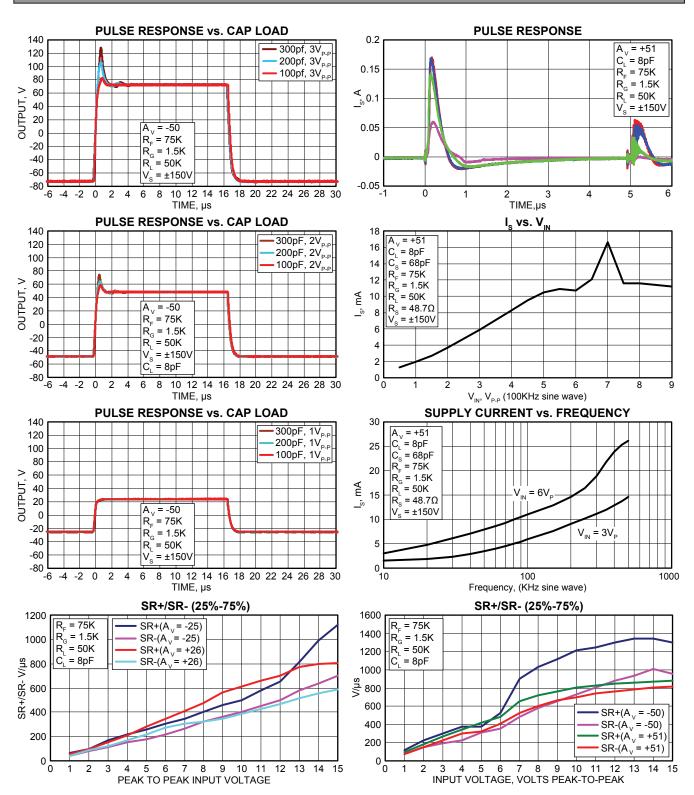

### **TYPICAL PERFORMANCE GRAPHS**

$\begin{array}{c} 10 \\ 10 \\ \text{SUPPLY TO OUTPUT DIFFERENTIAL, V}_{\text{S}} \cdot \text{V}_{\text{O}} (\text{V}) \end{array}$

**PA69**

PA69

#### GENERAL

Please read Application note 1 "General operating considerations" which covers stability, power supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit <u>www.cirrus.com</u> for design tools that help automate tasks such as calculations for stability, internal power dissipation, and current limit. There you will also find a complete application notes library, technical seminar workbook, and evaluation kits.

# THEORY OF OPERATION

The PA69 is designed specifically as a high speed pulse amplifier. In order to achieve high slew rates with low idle current, the internal design is quite different from traditional voltage feedback amplifiers. Basic op amp behaviors like high input impedance and high open loop gain still apply. But there are some notable differences, such as signal dependent supply current, bandwidth and output impedance, among others. The impact of these differences varies depending on application performance requirements and circumstances. These different behaviors are ideal for some applications but can make designs more challenging in other circumstances.

## SUPPLY CURRENT AND BYPASS CAPACITANCE

A traditional voltage feedback amplifier relies on fixed current sources in each stage to drive the parasitic capacitances of the next stage. These currents combine to define the idle or quiescent current of the amplifier. By design, these fixed currents are often the limiting parameter for slew rate and bandwidth of the amplifier. Amplifiers which are high voltage and have fast slew rates typically have high idle currents and dissipate notable power with no signal applied to the load. At the heart of the PA69 design is a signal dependent current source which strikes a new balance between supply current and dynamic performance. With small input signals, the supply current of the PA69 is very low, idling at less than 1 mA. With large transient input signals, the supply currents increase dramatically to allow the amplifier stages to respond quickly. The Pulse Response plot in the typical performance section of this datasheet describes the dynamic nature of the supply current with various input transients.

Choosing proper bypass capacitance requires careful consideration of the dynamic supply currents. High frequency ceramic capacitors of  $0.1\mu$ F or more should be placed as close as possible to the amplifier supply pins. The inductance of the routing from the supply pins to these ceramic capacitors will limit the supply of peak current during transients, thus reducing the slew rate of the PA69. The high frequency capacitance should be supplemented by additional bypass capacitance not more than a few centimeters from the amplifier. This additional bypass can be a slower capacitor technology, such as electrolytic, and is necessary to keep the supplies stable during sustained output currents. Generally, a few microfarad is sufficient.

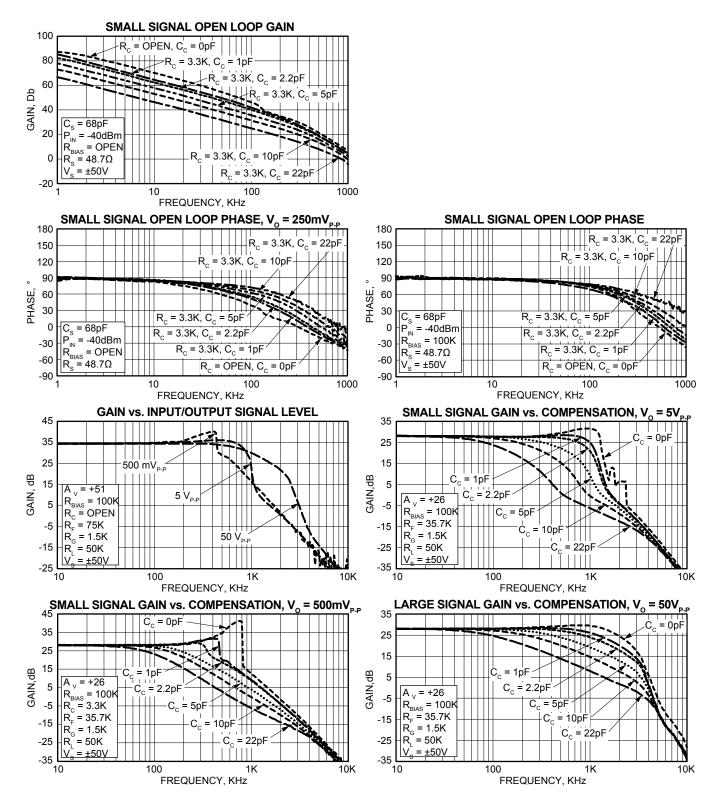

#### SMALL SIGNAL PERFORMANCE

The small signal performance plots in the typical performance section of this datasheet describe the behavior when the dynamic current sources described previously are near the idle state. The selection of compensation capacitor directly affects the open loop gain and phase performance.

Depending on the configuration of the amplifier, these plots show that the phase margin can diminish to very low levels when left uncompensated. This is due to the amount of bias current in the input stage when the part is in standby. An increase in the idle current in the output stage of the amplifier will improve phase margin for small signals although will increase the overall supply current.

Current can be injected into the output stage by adding a resistor, Rbias, between  $C_c$ - and  $V_s$ +. The size of Rbias will depend upon the application but 500µA of added bias current shows significant improvement in the small signal phase plots. Adding this resistor has little to no impact on small signal gain or large signal performance as under these conditions the current in the input stage is elevated over its idle value. It should also be noted that connecting a resistor to the upper supply only injects a fixed current and if the upper supply is fixed and well bypassed. If the application includes variable or adjustable supplies, a current source diode could also be used. These two terminal components combine a JFET and resistor connected within the package to behave like a current source.

As a second stability measure, the PA69 is externally compensated and performance can be optimized to the application. Unlike the Rbias technique, external phase compensation maintains the low idle current but does affect the large signal response of the amplifier. Refer to the small and large signal response plots as a guide in making the tradeoffs between bandwidth and stability. Due to the unique design of the PA69, two symmetric compensation

networks are required. The compensation capacitor  $C_c$  must be rated for a working voltage of the full operating supply voltage (+V<sub>s</sub> to -V<sub>s</sub>). NPO capacitors are recommended to maintain the desired level of compensation over temperature.

The PA69 requires an external 33pF capacitor between  $C_c$ - and –Vs to prevent oscillations in the falling edge of the output. This capacitor should be rated for the full supply voltage (+V<sub>s</sub> to –V<sub>s</sub>).

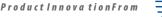

# LARGE SIGNAL PERFORMANCE

As the amplitude of the input signal increases, the internal dynamic current sources increase the operation bandwidth of the amplifier. This unique performance is apparent in its slew rate, pulse response, and large signal performance plots. Recall the previous discussion about the relationships between signal amplitude, supply current, and slew rate. As the amplitude of the input amplitude increases from  $1V_{P,P}$  to  $15V_{P,P}$ , the slew rate increases from  $50V/\mu$ s.

The output becomes clipped by the supply rails and the amplifier is no longer operating in a closed loop fashion. The rise and fall times become faster as the dynamic current sources are providing maximum current for slewing. The result of this amplifier architecture is that it slews fast, but allows good control of overshoot for large input signals. This can be seen clearly in the large signal Transient Response plots.

### HEATSINKING AND SAFE OPERATING AREA

The MOSFET output stage of the PA69 is not limited by second breakdown considerations as in bipolar output stages. Only thermal considerations of the package and current handling capabilities limit the Safe Operating Area. The SOA plots include power dissipation limitations which are dependent upon case temperature. Keep in mind that the dynamic current sources which drive high slew rates can increase the operating temperature of the amplifier during periods of repeated slewing. The plot of supply current V<sub>s</sub> input signal amplitude for a 100 kHz signal provides an indication of the supply current with repeated slewing conditions. This application dependent condition must be considered carefully.

The output stage is self-protected against transient flyback by the parasitic body diodes of the output stage. However, for protection against sustained high energy flyback, external, fast recovery diodes must be used.

#### **CURRENT LIMIT**

For proper operation, the current limit resistor, Rlim, must be connected as shown in the external connections diagram. For maximum reliability and protection, the largest resistor value should be used. The minimum practical value for  $R_{LIM}$  is about 12 $\Omega$ . However, refer to the SOA curves for each package type to assist in selecting the optimum value for  $R_{LIM}$  in the intended application.

#### LAYOUT CONSIDERATIONS

The PA69 is built on a dielectrically isolated process and the package tab is therefore not electrically connected to the amplifier. For high speed operation, the package tab should be connected to a stable reference to reduce capacitive coupling between amplifier nodes and the floating tab. It is often convenient to directly connect the tab to GND or one of the supply rails, but an AC connection through a 1uF capacitor to GND is also sufficient if a DC connection is undesirable

Care should be taken to position the  $R_c / C_c$  compensation networks close to the amplifier compensation pins. Long loops in these paths pick up noise and increase the likelihood of  $L_c$  interactions and oscillations.

#### **ELECTROSTATIC DISCHARGE**

Like many high performance MOSFET amplifiers, the PA69 very sensitive to damage due to electrostatic discharge (ESD). Failure to follow proper ESD handling procedures could have results ranging from reduced operating performance to catastrophic damage. Minimum proper handling includes the use of grounded wrist or shoe straps, grounded work surfaces. Ionizers directed at the work in progress can neutralize the charge build up in the work environment and are strongly recommended.