# Dual, Low-Power, Wideband, Voltage-Feedback OPERATIONAL AMPLIFIER with Disable

### **FEATURES**

- FLEXIBLE SUPPLY RANGE: +2.6V to +12V Single Supply ±1.3V to ±6V Dual Supplies

- UNITY-GAIN STABLE

- WIDEBAND ±5V OPERATION: 60MHz (G = +2V/V)

- OUTPUT VOLTAGE SWING: ±4V

- HIGH SLEW RATE: 250V/μs

- LOW QUIESCENT CURRENT: 460μA/ch

- LOW DISABLE CURRENT: 18μA/ch

### **APPLICATIONS**

- VIDEO LINE DRIVING

- xDSL LINE RECEIVERS

- HIGH-SPEED IMAGING CHANNELS

- ADC BUFFERS

- PORTABLE INSTRUMENTS

- TRANSIMPEDANCE AMPLIFIERS

- ACTIVE FILTERS

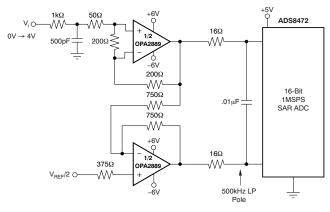

Low Power, DC-Coupled, Single-to-Differential Driver for ≤100kHz Inputs

### DESCRIPTION

The OPA2889 represents a major step forward in unity-gain stable, voltage-feedback op amps. A new internal architecture provides slew rate and full-power bandwidth previously found only in wideband, current-feedback op amps. These capabilities give exceptional full-power bandwidth. Using a dual ±5V supply, the OPA2889 can deliver a ±4V output swing with over 40mA drive current and 60MHz bandwidth. This combination of features makes the OPA2889 an ideal RGB line driver or single-supply analog-to-digital converter (ADC) input driver or low power twisted pair line receiver.

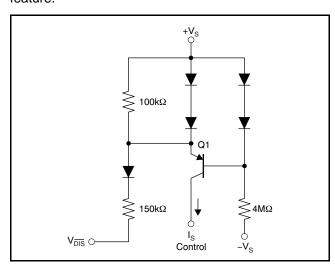

The low 460 $\mu$ A/ch supply current of the OPA2889 is precisely trimmed at +25°C. System power may be reduced further using the optional disable control pin. Leaving this disable pin open, or holding it HIGH, operates the OPA2889 normally. If pulled LOW, the OPA2889 supply current drops to less than 20 $\mu$ A/ch while the output goes into a high-impedance state.

# RELATED OPERATIONAL AMPLIFIER PRODUCTS

|                                                    | SINGLES | DUALS   | TRIPLES |

|----------------------------------------------------|---------|---------|---------|

| Low-Power Voltage-Feedback with Disable            | OPA890  | OPA2890 |         |

| Voltage-Feedback Amplifier with Disable (1800V/μs) | OPA690  | OPA2690 | OPA3690 |

| Current-Feedback Amplifier with Disable (2100V/μs) | OPA691  | OPA2691 | OPA3691 |

| Fixed Gain                                         | OPA692  |         | OPA3692 |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

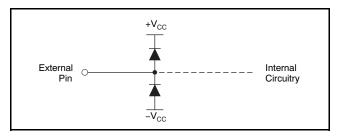

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

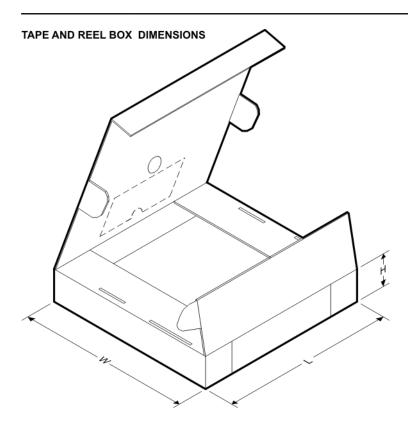

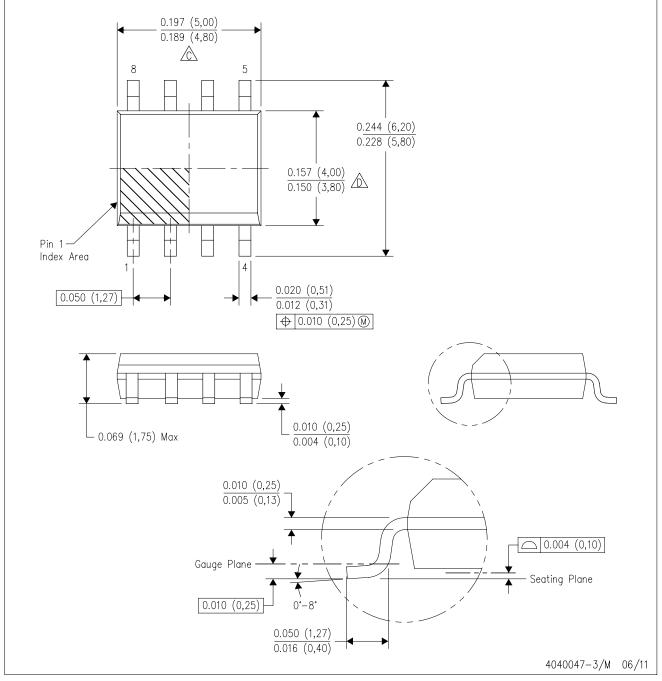

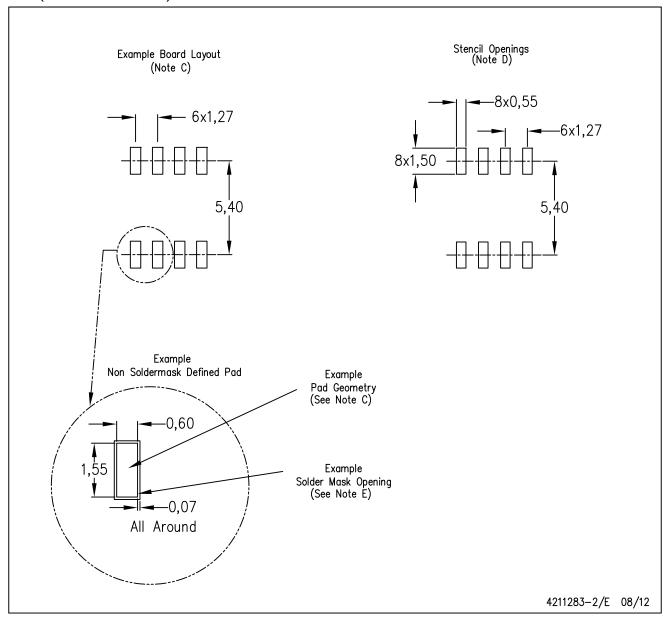

| OPA2889 | SO-8         | D                     | -40°C to +85°C                    | OP2889             | OPA2889ID          | Rail, 75                     |

| UPA2669 | 30-6         | Ь                     | -40 C to +65 C                    | UP2669             | OPA2889IDR         | Tape and Reel, 2500          |

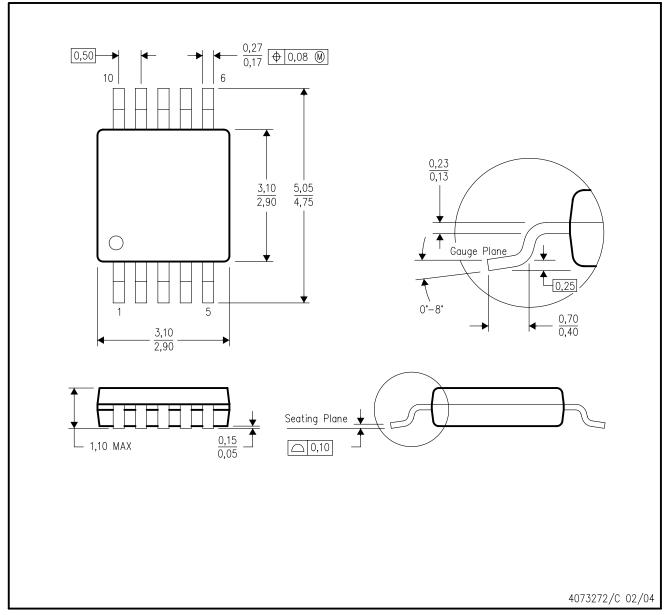

| OPA2889 | MSOP-10      | DGS                   | -40°C to +85°C                    | BZY                | OPA2889IDGST       | Tape and Reel, 250           |

| UPA2009 | M30P-10      | DGS                   | -40°C 10 +65°C                    | DZ I               | OPA2889IDGSR       | Tape and Reel, 2500          |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

### **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                                                                      | OPA2889         | UNIT          |

|----------------------------------------------------------------------|-----------------|---------------|

| Power supply                                                         | ±6.5            | V             |

| Internal power dissipation                                           | See Thermal Ch  | aracteristics |

| Input voltage range                                                  | ±V <sub>S</sub> | V             |

| Storage temperature range                                            | -65 to +125     | °C            |

| Lead temperature (soldering, 10s)                                    | +260            | °C            |

| Maximum junction temperature (T <sub>J</sub> )                       | +150            | °C            |

| Maximum junction temperature (T <sub>J</sub> ), continuous operation | +140            | °C            |

| ESD Rating:                                                          |                 |               |

| Human body model (HBM)                                               | 2000            | V             |

| Charge device model (CDM)                                            | 1000            | V             |

| Machine model (MM)                                                   | 150             | V             |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

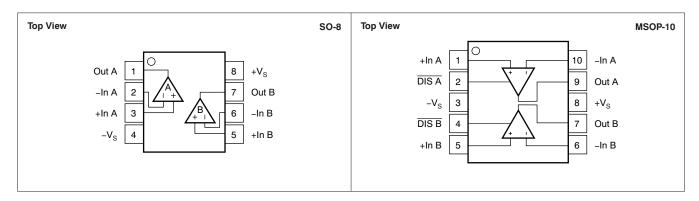

### PIN ASSIGNMENTS

Submit Documentation Feedback

Copyright © 2007–2008, Texas Instruments Incorporated

# **ELECTRICAL CHARACTERISTICS:** V<sub>S</sub> = ±5V

At  $T_A$  = +25°C,  $R_F$  = 750 $\Omega$ , G = +2V/V, and  $R_L$  = 100 $\Omega$ , unless otherwise noted.

|                                               |                                               |            | OPA2889II            | D, IDGS                        |                                  |                    |             |                              |  |

|-----------------------------------------------|-----------------------------------------------|------------|----------------------|--------------------------------|----------------------------------|--------------------|-------------|------------------------------|--|

|                                               |                                               | TYP        |                      | N/MAX OV<br>MPERATU            |                                  |                    |             |                              |  |

| PARAMETER                                     | CONDITIONS                                    | +25°C      | +25°C <sup>(2)</sup> | 0°C to<br>+70°C <sup>(3)</sup> | -40°C to<br>+85°C <sup>(3)</sup> | UNITS              | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |  |

| AC PERFORMANCE                                |                                               |            |                      |                                |                                  |                    |             |                              |  |

| Small-Signal Bandwidth                        | $G = +1V/V, V_O = 100mV_{PP}, R_F = 0\Omega$  | 115        |                      |                                |                                  | MHz                | typ         | С                            |  |

|                                               | $G = +2V/V, V_O = 100mV_{PP}$                 | 60         | 40                   | 36                             | 32                               | MHz                | min         | В                            |  |

|                                               | $G = +10V/V, V_O = 100mV_{PP}$                | 8          | 6                    | 5                              | 4.5                              | MHz                | min         | В                            |  |

| Gain Bandwidth Product                        | G > +20V/V                                    | 75         | 60                   | 50                             | 45                               | MHz                | min         | В                            |  |

| Bandwidth for 0.1dB Flatness                  | $G = +2V/V, V_O = 100mV_{PP}$                 | 14         |                      |                                |                                  | MHz                | typ         | С                            |  |

| Peaking at a Gain of +1V/V                    | $V_O < 100 \text{mV}_{PP}$ , $R_F = 0 \Omega$ | 1          |                      |                                |                                  | dB                 | typ         | С                            |  |

| Large-Signal Bandwidth                        | $G = +2V/V, V_O = 2V_{PP}$                    | 70         |                      |                                |                                  | MHz                | typ         | С                            |  |

| Slew Rate                                     | $G = +2V/V$ , $V_O = 2V$ Step                 | 250        | 175                  | 160                            | 150                              | V/μs               | min         | В                            |  |

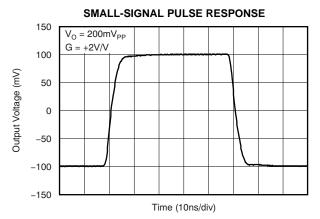

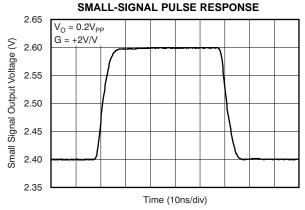

| Rise-and-Fall Time                            | 0.2V Step                                     | 6          |                      |                                |                                  | ns                 | typ         | С                            |  |

| Settling Time to 0.02%                        | $G = +1V/V, V_O = 2V Step$                    | 36         |                      |                                |                                  | ns                 | typ         | С                            |  |

| Settling Time to 0.1%                         |                                               | 25         |                      |                                |                                  | ns                 | typ         | С                            |  |

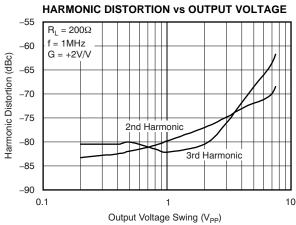

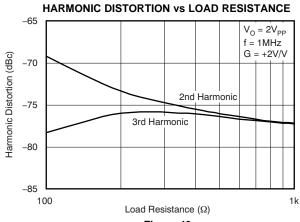

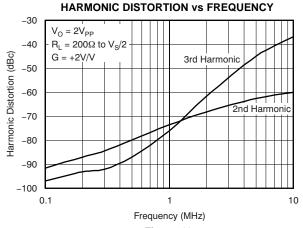

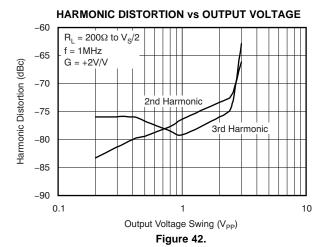

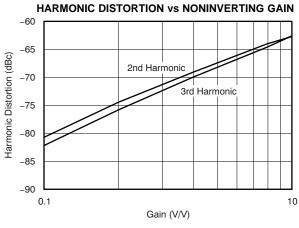

| Harmonic Distortion                           | $G = +2V/V, f = 1MHz, V_O = 2V_{PP}$          |            |                      |                                |                                  |                    |             |                              |  |

| 2nd-Harmonic                                  | $R_L = 200\Omega$                             | -75        | -65                  | -62                            | -60                              | dBc                | max         | В                            |  |

|                                               | R <sub>L</sub> ≥ 500Ω                         | -80        | -73                  | -68                            | -65                              | dBc                | max         | В                            |  |

| 3rd-Harmonic                                  | R <sub>L</sub> = 200Ω                         | -80        | -74                  | -70                            | -68                              | dBc                | max         | В                            |  |

|                                               | R <sub>L</sub> ≥ 500Ω                         | -82        | -80                  | -75                            | -72                              | dBc                | max         | В                            |  |

| Input Voltage Noise                           | f > 100kHz                                    | 8.4        | 10                   | 11.5                           | 12                               | nV/√ <del>Hz</del> | max         | В                            |  |

| Input Current Noise                           | f > 100kHz                                    | 0.7        | 1                    | 1.2                            | 1.4                              | pA/√ <del>Hz</del> | max         | В                            |  |

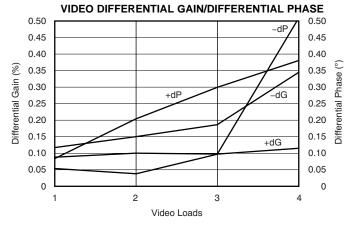

| Differential Gain                             | $G = +2V/V, V_O = 1.4V_{PP}, R_L = 150\Omega$ | 0.06       |                      |                                |                                  | %                  | typ         | С                            |  |

| Differential Phase                            | $G = +2V/V, V_O = 1.4V_{PP}, R_L = 150\Omega$ | 0.04       |                      |                                |                                  | 0                  | typ         | С                            |  |

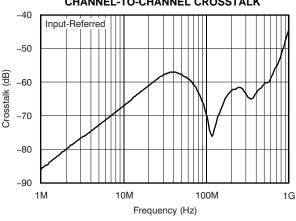

| Channel-to-Channel Crosstalk                  | f = 5MHz, Input-referred                      | -85        |                      |                                |                                  | dB                 | typ         | С                            |  |

| DC PERFORMANCE <sup>(4)</sup>                 |                                               |            |                      |                                |                                  |                    |             |                              |  |

| Open-Loop Voltage Gain (A <sub>OL</sub> )     | $V_{O} = 0V, R_{L} = 100\Omega$               | 66         | 60                   | 58                             | 57                               | dB                 | min         | А                            |  |

| Input Offset Voltage                          | V <sub>CM</sub> = 0V                          | ±1.5       | ±5                   | ±5.9                           | ±6.3                             | mV                 | max         | А                            |  |

| Average Offset Voltage Drift                  | V <sub>CM</sub> = 0V                          |            |                      | ±20                            | ±20                              | μV/°C              | max         | В                            |  |

| Input Bias Current                            | V <sub>CM</sub> = 0V                          | ±150       | ±750                 | ±840                           | ±880                             | nA                 | max         | Α                            |  |

| Average Input Bias Current Drift              | $V_{CM} = 0V$                                 |            |                      | ±2                             | ±2                               | nA/°C              | max         | В                            |  |

| Input Offset Current                          | V <sub>CM</sub> = 0V                          | ±50        | ±200                 | ±225                           | ±235                             | nA                 | max         | Α                            |  |

| Average Input Offset Current<br>Drift         | V <sub>CM</sub> = 0V                          |            |                      | ±0.5                           | ±0.5                             | nA/°C              | max         | В                            |  |

| INPUT                                         |                                               |            |                      |                                |                                  |                    |             |                              |  |

| Common-Mode Input Range (CMIR) <sup>(5)</sup> |                                               | ±3.9       | ±3.8                 | ±3.7                           | ±3.6                             | V                  | min         | А                            |  |

| Common-Mode Rejection Ratio (CMRR)            | V <sub>CM</sub> = 0V, Input-referred          | 70         | 60                   | 59                             | 58                               | dB                 | min         | А                            |  |

| Input Impedance                               |                                               |            |                      |                                |                                  |                    |             |                              |  |

| Differential                                  | V <sub>CM</sub> = 0V                          | 3.5    0.5 |                      |                                |                                  | MΩ    pF           | typ         | С                            |  |

| Common-Mode                                   | V <sub>CM</sub> = 0V                          | 170    0.8 |                      |                                |                                  | MΩ    pF           | typ         | С                            |  |

<sup>(1)</sup> Test levels: (A) 100% tested at +25°C. Over temperature limits set by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

Junction temperature = ambient for +25°C tested specifications.

Junction temperature = ambient at low temperature limit; junction temperature = ambient +4°C at high temperature limit for over temperature specifications.

<sup>(4)</sup> Current is considered positive out-of-node. V<sub>CM</sub> is the input common-mode voltage.

(5) Tested < 3dB below minimum specified CMRR at ±CMIR limits</li>

# ELECTRICAL CHARACTERISTICS: $V_s = \pm 5V$ (continued)

At T<sub>A</sub> = +25°C, R<sub>F</sub> = 750 $\Omega$ , G = +2V/V, and R<sub>L</sub> = 100 $\Omega$ , unless otherwise noted.

|                                                    |                                     |            | OPA2889II            | D, IDGS                        |                                  |       |             |                              |

|----------------------------------------------------|-------------------------------------|------------|----------------------|--------------------------------|----------------------------------|-------|-------------|------------------------------|

|                                                    |                                     | TYP        |                      | N/MAX OV<br>MPERATU            |                                  |       |             |                              |

| PARAMETER                                          | CONDITIONS                          | +25°C      | +25°C <sup>(2)</sup> | 0°C to<br>+70°C <sup>(3)</sup> | -40°C to<br>+85°C <sup>(3)</sup> | UNITS | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

| OUTPUT                                             |                                     |            |                      |                                |                                  |       |             |                              |

| Output Voltage Swing                               | No load                             | ±4.0       | ±3.9                 | ±3.8                           | ±3.7                             | V     | min         | Α                            |

|                                                    | $R_L = 100\Omega$                   | ±3.3       | ±3.0                 | ±2.95                          | ±2.85                            | V     | min         | Α                            |

| Output Current, Sourcing, Sinking                  | $V_O = 0V$                          | ±40        | ±28                  | ±25                            | ±22                              | mA    | min         | Α                            |

| Peak Output Current                                | Output shorted to ground            | ±60        |                      |                                |                                  | mA    | typ         | С                            |

| Closed-Loop Output Impedance                       | G = +2V/V, f = 100kHz               | 0.04       |                      |                                |                                  | Ω     | typ         | С                            |

| DISABLE (MSOP-10 ONLY)                             | Disable LOW                         |            |                      |                                |                                  |       |             |                              |

| Power-Down Supply Current (+V <sub>S</sub> )       | $V_{DIS} = 0$ , Both channels       | 36         | 50                   | 53                             | 55                               | μΑ    | max         | Α                            |

| Disable Time                                       | $V_{IN} = 1V_{DC}$                  | 70         |                      |                                |                                  | μs    | typ         | С                            |

| Enable Time                                        | $V_{IN} = 1V_{DC}$                  | 200        |                      |                                |                                  | ns    | typ         | С                            |

| Off Isolation                                      | G = +2V/V, $f = 5MHz$               | 70         |                      |                                |                                  | dB    | typ         | С                            |

| Output Capacitance in Disable                      |                                     | 4          |                      |                                |                                  | pF    | typ         | С                            |

| Enable Voltage                                     |                                     | 3.3        | 3.4                  | 3.5                            | 3.55                             | V     | min         | Α                            |

| Disable Voltage                                    |                                     | 1.2        | 1.0                  | 0.9                            | 0.85                             | V     | max         | Α                            |

| Control Pin Input Bias Current (V <sub>DIS</sub> ) | V <sub>DIS</sub> = 0V, Each channel | 15         | 25                   | 30                             | 35                               | μΑ    | max         | Α                            |

| POWER SUPPLY                                       |                                     |            |                      |                                |                                  |       |             |                              |

| Specified Operating Voltage                        |                                     | ±5         |                      |                                |                                  | V     | typ         | С                            |

| Minimum Operating Voltage                          |                                     |            | 1.3                  |                                |                                  | V     | typ         | С                            |

| Maximum Operating Voltage                          |                                     |            | ±6.0                 | ±6.0                           | ±6.0                             | V     | max         | Α                            |

| Maximum Quiescent Current                          | $V_S = \pm 5V$ , Both channels      | 0.92       | 1                    | 1.05                           | 1.1                              | mA    | max         | Α                            |

| Minimum Quiescent Current                          | $V_S = \pm 5V$ , Both channels      | 0.92       | 8.0                  | 0.75                           | 0.7                              | mA    | min         | Α                            |

| Power-Supply Rejection (+PSRR)<br>Ratio            | $+V_S = 4.5V$ to 5.5V               | 64         | 62                   | 61                             | 60                               | dB    | min         | Α                            |

| (-PSRR)                                            | $-V_S = -4.5V$ to $-5.5V$           | 74         | 72                   | 71                             | 70                               | dB    | min         | Α                            |

| THERMAL CHARACTERISTICS                            |                                     |            |                      |                                |                                  |       | 1           |                              |

| Specified Operating Range<br>D and DGS Packages    |                                     | -40 to +85 |                      |                                |                                  | °C    | typ         | С                            |

| Thermal Resistance, $\theta_{JA}$                  | Junction-to-ambient                 |            |                      |                                |                                  |       |             |                              |

| D SO-8                                             |                                     | 100        |                      |                                |                                  | °C/W  | typ         | С                            |

| DGS MSOP-10                                        |                                     | 135        |                      |                                |                                  | °C/W  | typ         |                              |

Submit Documentation Feedback

www.ti.com

# ELECTRICAL CHARACTERISTICS: $V_S = +5V$

At  $T_A$  = +25°C,  $R_F$  = 750 $\Omega$ , G = +2V/V, and  $R_L$  = 100 $\Omega$ , unless otherwise noted.

|                                           |                                               |            | OPA2889II            | D, IDGS                        |                                  |                    |             |                              |

|-------------------------------------------|-----------------------------------------------|------------|----------------------|--------------------------------|----------------------------------|--------------------|-------------|------------------------------|

|                                           |                                               | TYP        |                      | N/MAX OV<br>MPERATU            |                                  |                    |             |                              |

| PARAMETER                                 | CONDITIONS                                    | +25°C      | +25°C <sup>(2)</sup> | 0°C to<br>+70°C <sup>(3)</sup> | -40°C to<br>+85°C <sup>(3)</sup> | UNITS              | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

| AC PERFORMANCE                            |                                               |            |                      |                                |                                  |                    |             |                              |

| Small-Signal Bandwidth                    | $G = +1V/V, V_O = 100mV_{PP}, R_F = 0\Omega$  | 100        |                      |                                |                                  | MHz                | typ         | С                            |

|                                           | $G = +2V/V, V_O = 100mV_{PP}$                 | 50         | 30                   | 26                             | 22                               | MHz                | min         | В                            |

|                                           | $G = +10V/V, V_O = 100mV_{PP}$                | 7          | 5.5                  | 4.5                            | 4                                | MHz                | min         | В                            |

| Gain Bandwidth Product                    | G > +20V/V                                    | 70         | 55                   | 45                             | 40                               | MHz                | min         | В                            |

| Bandwidth for 0.1dB Flatness              | $G = +2V/V, V_O = 100mV_{PP}$                 | 14         |                      |                                |                                  | MHz                | typ         | С                            |

| Peaking at a Gain of +1V/V                | $V_O < 100 m V_{PP}$ , $R_F = 0 \Omega$       | 1          |                      |                                |                                  | dB                 | typ         | С                            |

| Large-Signal Bandwidth                    | $G = +2V/V, V_O = 2V_{PP}$                    | 60         |                      |                                |                                  | MHz                | typ         | С                            |

| Slew Rate                                 | $G = +2V/V$ , $V_O = 2V$ Step                 | 200        | 125                  | 110                            | 100                              | V/μs               | min         | В                            |

| Rise-and-Fall Time                        | 0.2V Step                                     | 6.5        |                      |                                |                                  | ns                 | typ         | С                            |

| Settling Time to 0.02%                    | $G = +1V/V, V_O = 2V Step$                    | 38         |                      |                                |                                  | ns                 | typ         | С                            |

| Settling Time to 0.1%                     |                                               | 27         |                      |                                |                                  | ns                 | typ         | С                            |

| Harmonic Distortion                       | $G = +2V/V$ , $f = 1MHz$ , $V_O = 2V_{PP}$    |            |                      |                                |                                  |                    |             |                              |

| 2nd-Harmonic                              | $R_L = 200\Omega$                             | -71        | -61                  | -58                            | -56                              | dBc                | max         | В                            |

|                                           | $R_L \geq 500\Omega$                          | -76        | -69                  | -64                            | -61                              | dBc                | max         | В                            |

| 3rd-Harmonic                              | $R_L = 200\Omega$                             | -76        | -70                  | -66                            | -64                              | dBc                | max         | В                            |

|                                           | $R_L \geq 500\Omega$                          | -76        | -74                  | -69                            | -66                              | dBc                | max         | В                            |

| Input Voltage Noise                       | f > 100kHz                                    | 8.5        | 10.5                 | 12                             | 12.5                             | nV/√ <del>Hz</del> | max         | В                            |

| Input Current Noise                       | f > 100kHz                                    | 0.7        | 1                    | 1.1                            | 1.2                              | pA/√ <del>Hz</del> | max         | В                            |

| Differential Gain                         | $G = +2V/V, V_O = 1.4V_{PP}, R_L = 150\Omega$ | 0.06       |                      |                                |                                  | %                  | typ         | С                            |

| Differential Phase                        | $G = +2V/V, V_O = 1.4V_{PP}, R_L = 150\Omega$ | 0.04       |                      |                                |                                  | ۰                  | typ         | С                            |

| Channel-to-Channel Crosstalk              | f = 5MHz, Input-referred                      | -85        |                      |                                |                                  | dB                 | typ         | С                            |

| DC PERFORMANCE <sup>(4)</sup>             |                                               |            |                      |                                |                                  |                    |             |                              |

| Open-Loop Voltage Gain (A <sub>OL</sub> ) | $V_O = 0V$ , $R_L = 100\Omega$                | 64         | 58                   | 56                             | 55                               | dB                 | min         | Α                            |

| Input Offset Voltage                      | $V_{CM} = 0V$                                 | ±1.5       | ±5                   | ±5.9                           | ±6.3                             | mV                 | max         | Α                            |

| Average Offset Voltage Drift              | $V_{CM} = 0V$                                 |            |                      | ±20                            | ±20                              | μV/°C              | max         | В                            |

| Input Bias Current                        | $V_{CM} = 0V$                                 | ±150       | ±800                 | ±890                           | ±930                             | nA                 | max         | Α                            |

| Average Input Bias Current Drift          | $V_{CM} = 0V$                                 |            |                      | ±2                             | ±2                               | nA/°C              | max         | В                            |

| Input Offset Current                      | $V_{CM} = 0V$                                 | ±50        | ±250                 | ±275                           | ±285                             | nA                 | max         | Α                            |

| Average Input Offset Current<br>Drift     | $V_{CM} = 0V$                                 |            |                      | ±0.5                           | ±0.5                             | nA/°C              | max         | В                            |

| INPUT                                     |                                               |            |                      |                                |                                  |                    |             |                              |

| Most Positive Input Voltage               |                                               | 4          | 3.9                  | 3.8                            | 3.75                             | V                  | min         | Α                            |

| Least Positive Input Voltage              |                                               | 1          | 1.1                  | 1.2                            | 1.25                             | V                  | max         | Α                            |

| Common-Mode Rejection Ratio (CMRR)        | $V_{CM} = 0V$ , Input-referred                | 68         | 58                   | 57                             | 56                               | dB                 | min         | А                            |

| Input Impedance                           |                                               |            |                      |                                |                                  |                    |             |                              |

| Differential                              | $V_{CM} = 0V$                                 | 3.5    0.5 |                      |                                |                                  | MΩ    pF           | typ         | С                            |

| Common-Mode                               | $V_{CM} = 0V$                                 | 170    0.8 |                      |                                |                                  | MΩ    pF           | typ         | С                            |

<sup>(1)</sup> Test levels: **(A)** 100% tested at +25°C. Over temperature limits set by characterization and simulation. **(B)** Limits set by characterization and simulation. **(C)** Typical value only for information.

<sup>(2)</sup> Junction temperature = ambient for +25°C tested specifications.

<sup>(3)</sup> Junction temperature = ambient at low temperature limit; junction temperature = ambient +4°C at high temperature limit for over temperature specifications.

<sup>(4)</sup> Current is considered positive out-of-node. V<sub>CM</sub> is the input common-mode voltage.

# ELECTRICAL CHARACTERISTICS: $V_s = +5V$ (continued)

At  $T_A$  = +25°C,  $R_F$  = 750 $\Omega$ , G = +2V/V, and  $R_L$  = 100 $\Omega$ , unless otherwise noted.

|                                                    |                                     |            | OPA2889I             | D, IDGS                        |                                  |       |             |                              |

|----------------------------------------------------|-------------------------------------|------------|----------------------|--------------------------------|----------------------------------|-------|-------------|------------------------------|

|                                                    |                                     | TYP        |                      | N/MAX OV<br>MPERATU            |                                  |       |             |                              |

| PARAMETER                                          | CONDITIONS                          | +25°C      | +25°C <sup>(2)</sup> | 0°C to<br>+70°C <sup>(3)</sup> | -40°C to<br>+85°C <sup>(3)</sup> | UNITS | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

| ОИТРИТ                                             |                                     |            |                      |                                |                                  |       |             |                              |

| Most Positive Output Voltage                       | No load                             | 4          | 3.9                  | 3.8                            | 3.7                              | V     | min         | Α                            |

|                                                    | $R_L = 100\Omega$                   | 3.85       | 3.7                  | 3.6                            | 3.55                             | V     | min         | Α                            |

| Least Positive Output Voltage                      | No Load                             | 1          | 1.1                  | 1.2                            | 1.3                              | V     | max         | Α                            |

|                                                    | $R_L = 100\Omega$                   | 1.15       | 1.3                  | 1.4                            | 1.45                             | V     | max         | Α                            |

| Output Current, Sourcing, Sinking                  | $V_O = 0V$                          | ±35        | ±24                  | ±21                            | ±18                              | mA    | min         | Α                            |

| Peak Output Current                                | Output shorted to ground            | ±50        |                      |                                |                                  | mA    | typ         | С                            |

| Closed-Loop Output Impedance                       | G = +2V/V, f = 100kHz               | 0.04       |                      |                                |                                  | Ω     | typ         | С                            |

| DISABLE (MSOP-10 ONLY)                             | Disable LOW                         |            |                      |                                |                                  |       |             |                              |

| Power-Down Supply Current (+V <sub>S</sub> )       | $V_{DIS} = 0$ , both channels       | 36         | 50                   | 53                             | 55                               | μΑ    | max         | Α                            |

| Disable Time                                       | $V_{IN} = 1V_{DC}$                  | 70         |                      |                                |                                  | μs    | typ         | С                            |

| Enable Time                                        | $V_{IN} = 1V_{DC}$                  | 200        |                      |                                |                                  | ns    | typ         | С                            |

| Off Isolation                                      | G = +2V/V, $f = 5MHz$               | 70         |                      |                                |                                  | dB    | typ         | С                            |

| Output Capacitance in Disable                      |                                     | 4          |                      |                                |                                  | pF    | typ         | С                            |

| Enable Voltage                                     |                                     | 3.3        | 3.4                  | 3.5                            | 3.55                             | V     | min         | Α                            |

| Disable Voltage                                    |                                     | 1.2        | 1.0                  | 0.9                            | 0.85                             | V     | max         | Α                            |

| Control Pin Input Bias Current (V <sub>DIS</sub> ) | V <sub>DIS</sub> = 0V, Each channel | 15         | 25                   | 30                             | 35                               | μΑ    | max         | Α                            |

| POWER SUPPLY                                       |                                     |            |                      |                                |                                  |       |             |                              |

| Specified Operating Voltage                        |                                     | +5         |                      |                                |                                  | V     | typ         | С                            |

| Minimum Operating Voltage                          |                                     |            | +2.6                 |                                |                                  | V     | typ         | С                            |

| Maximum Operating Voltage                          |                                     |            | +12                  | +12                            | +12                              | V     | max         | Α                            |

| Maximum Quiescent Current                          | $V_S = +5V$ , Both channels         | 0.85       | 0.95                 | 1.0                            | 1.05                             | mA    | max         | Α                            |

| Minimum Quiescent Current                          | $V_S = +5V$ , Both channels         | 0.85       | 0.75                 | 0.7                            | 0.65                             | mA    | min         | Α                            |

| Power-Supply Rejection (+PSRR)<br>Ratio            | $+V_S = 4.5V$ to 5.5V               | 60         |                      |                                |                                  | dB    | typ         | С                            |

| THERMAL CHARACTERISTICS                            |                                     |            |                      |                                |                                  |       |             |                              |

| Specified Operating Range<br>D and DGS Packages    |                                     | -40 to +85 |                      |                                |                                  | °C    | typ         | С                            |

| Thermal Resistance, $\theta_{JA}$                  | Junction-to-ambient                 |            |                      |                                |                                  |       |             |                              |

| D SO-8                                             |                                     | 100        |                      |                                |                                  | °C/W  | typ         | С                            |

| DGS MSOP-10                                        |                                     | 135        |                      |                                |                                  | °C/W  | typ         | С                            |

Submit Documentation Feedback

# TYPICAL CHARACTERISTICS: V<sub>S</sub> = ±5V

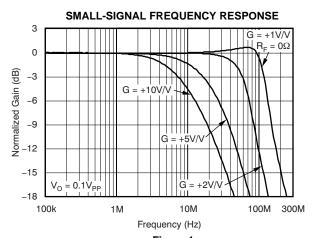

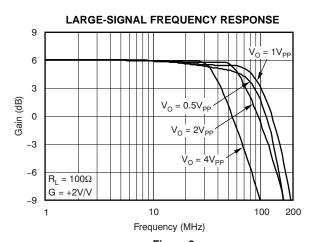

At  $T_A$  = +25°C, G = +2V/V,  $R_F$  = 750 $\Omega$ , and  $R_L$  = 100 $\Omega$ , unless otherwise noted. See Figure 50.

Figure 1.

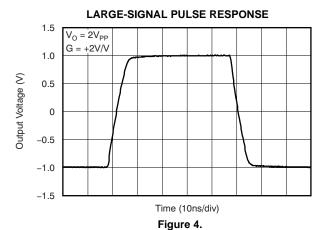

Figure 2.

Figure 3.

**CHANNEL-TO-CHANNEL CROSSTALK**

Figure 5.

Figure 6.

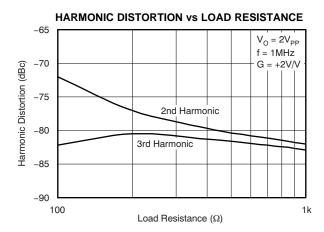

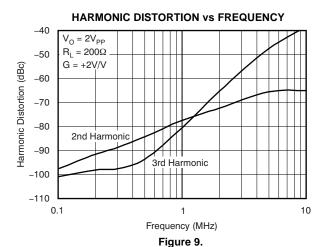

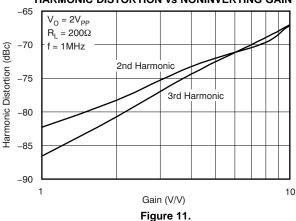

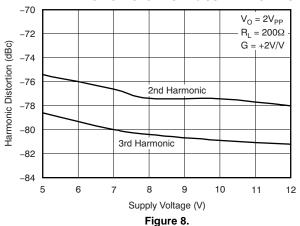

# TYPICAL CHARACTERISTICS: V<sub>s</sub> = ±5V (continued)

At  $T_A = +25$ °C, G = +2V/V,  $R_F = 750\Omega$ , and  $R_L = 100\Omega$ , unless otherwise noted. See Figure 50.

Figure 7.

HARMONIC DISTORTION vs NONINVERTING GAIN

1MHz HARMONIC DISTORTION vs SUPPLY VOLTAGE

Figure 10.

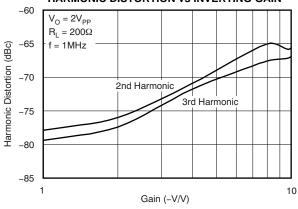

HARMONIC DISTORTION vs INVERTING GAIN

Figure 12.

# TYPICAL CHARACTERISTICS: V<sub>S</sub> = ±5V (continued)

At  $T_A = +25$ °C, G = +2V/V,  $R_F = 750\Omega$ , and  $R_L = 100\Omega$ , unless otherwise noted. See Figure 50.

Figure 13.

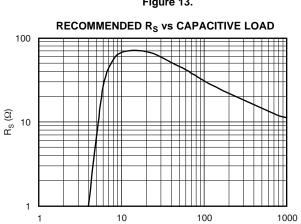

Capacitive Load (pF) Figure 15.

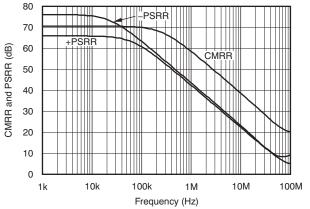

### **COMMON-MODE REJECTION RATIO AND POWER-SUPPLY REJECTION RATIO vs FREQUENCY**

Figure 17.

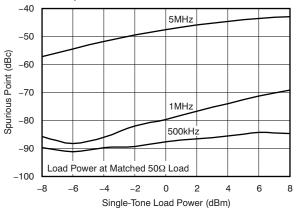

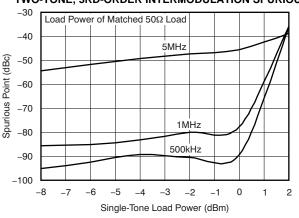

### TWO-TONE, 3RD-ORDER INTERMODULATION SPURIOUS

Figure 14.

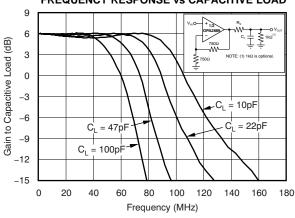

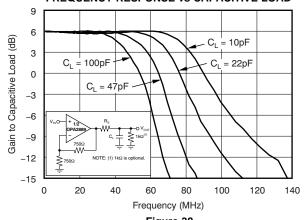

### FREQUENCY RESPONSE vs CAPACITIVE LOAD

Figure 16.

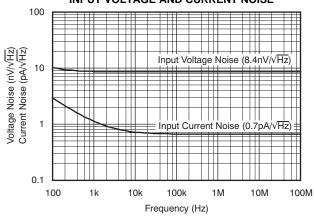

### INPUT VOLTAGE AND CURRENT NOISE

Figure 18.

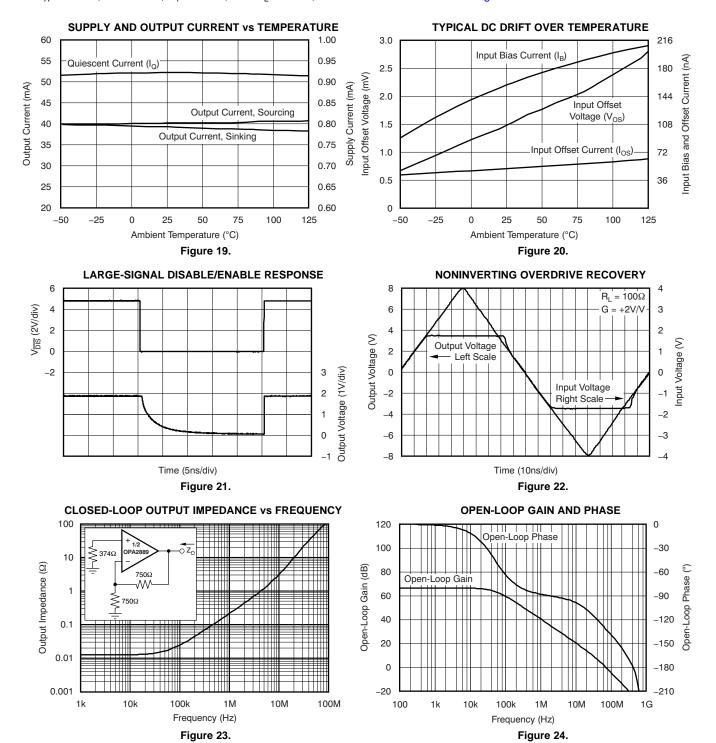

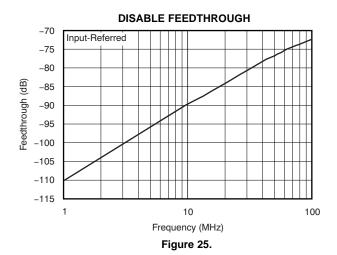

# TYPICAL CHARACTERISTICS: V<sub>s</sub> = ±5V (continued)

At  $T_A$  = +25°C, G = +2V/V,  $R_F$  = 750 $\Omega$ , and  $R_L$  = 100 $\Omega$ , unless otherwise noted. See Figure 50.

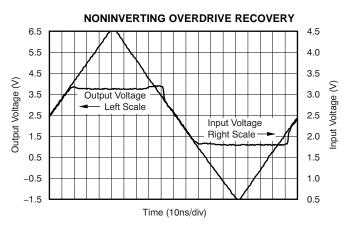

# TYPICAL CHARACTERISTICS: V<sub>s</sub> = ±5V (continued)

At  $T_A$  = +25°C, G = +2V/V,  $R_F$  = 750 $\Omega$ , and  $R_L$  = 100 $\Omega$ , unless otherwise noted. See Figure 50.

### TYPICAL CHARACTERISTICS: $V_S = \pm 5V$ , Differential

At  $T_A = +25$ °C, Differential Gain = +2V/V, and  $R_L = 200\Omega$ , unless otherwise noted. See Figure 52 and Figure 53.

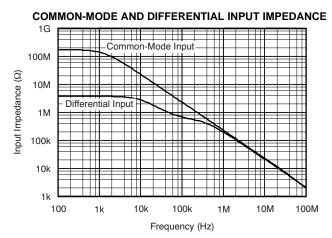

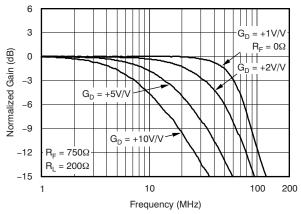

#### **DIFFERENTIAL SMALL-SIGNAL FREQUENCY RESPONSE**

Figure 27.

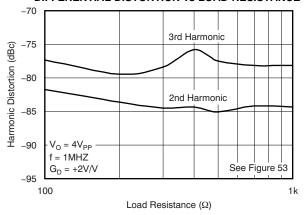

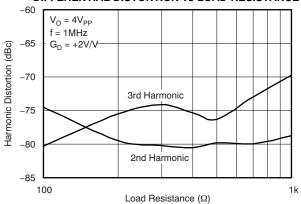

### **DIFFERENTIAL DISTORTION vs LOAD RESISTANCE**

Figure 29.

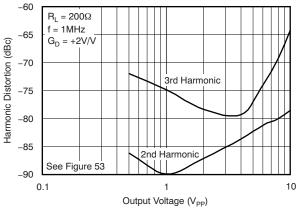

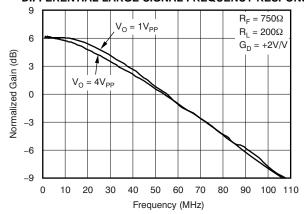

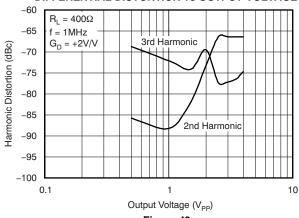

### **DIFFERENTIAL DISTORTION vs OUTPUT VOLTAGE**

Figure 31.

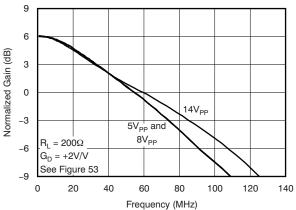

#### **DIFFERENTIAL LARGE-SIGNAL FREQUENCY RESPONSE**

Figure 28.

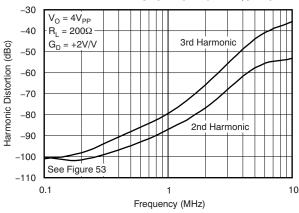

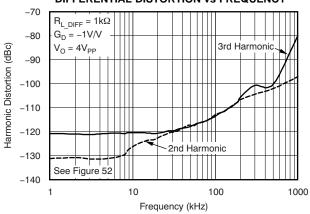

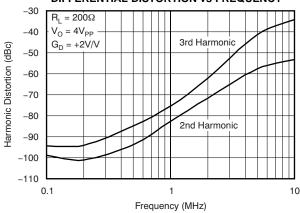

### **DIFFERENTIAL DISTORTION vs FREQUENCY**

Figure 30.

### **DIFFERENTIAL DISTORTION vs FREQUENCY**

Figure 32.

# TYPICAL CHARACTERISTICS: V<sub>s</sub> = +5V

At  $T_A = +25$ °C, G = +2V/V,  $R_F = 750\Omega$ , and  $R_L = 100\Omega$ , unless otherwise noted. See Figure 51.

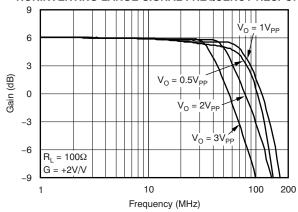

### NONINVERTING SMALL-SIGNAL FREQUENCY RESPONSE

Figure 33.

#### .....

Figure 35.

Capacitive Load (pF) **Figure 37.**

### NONINVERTING LARGE-SIGNAL FREQUENCY RESPONSE

Figure 34.

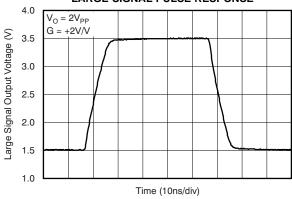

### **LARGE-SIGNAL PULSE RESPONSE**

Figure 36.

### FREQUENCY RESPONSE vs CAPACITIVE LOAD

Figure 38.

# TYPICAL CHARACTERISTICS: V<sub>S</sub> = +5V (continued)

At  $T_A$  = +25°C, G = +2V/V,  $R_F$  = 750 $\Omega$ , and  $R_L$  = 100 $\Omega$ , unless otherwise noted. See Figure 51.

Figure 39.

Figure 40.

Figure 41.

TWO-TONE, 3RD-ORDER INTERMODULATION SPURIOUS

Figure 43.

Figure 44.

Submit Documentation Feedback

# TYPICAL CHARACTERISTICS: V<sub>s</sub> = +5V, Differential

At  $T_A = +25$ °C, Differential Gain = +2V/V, and  $R_L = 200\Omega$ , unless otherwise noted. See Figure 52.

### **DIFFERENTIAL SMALL-SIGNAL FREQUENCY RESPONSE**

Figure 45.

### **DIFFERENTIAL LARGE-SIGNAL FREQUENCY RESPONSE**

Figure 46.

### **DIFFERENTIAL DISTORTION vs LOAD RESISTANCE**

Figure 47.

### **DIFFERENTIAL DISTORTION vs FREQUENCY**

Figure 48.

### **DIFFERENTIAL DISTORTION vs OUTPUT VOLTAGE**

Figure 49.

### APPLICATIONS INFORMATION

# WIDEBAND VOLTAGE-FEEDBACK OPERATION

The OPA2889 provides an exceptional combination of high output power capability in a dual, wideband, unity-gain stable, voltage-feedback op amp using a new high slew rate input stage. Typical differential input stages used for voltage-feedback op amps are designed to steer a fixed-bias current to the compensation capacitor, setting a limit to the achievable slew rate. The OPA2889 uses a new input stage that places the transconductance element between two input buffers, using the output currents as the forward signal. As the error voltage increases across the two inputs, an increasing current is delivered to the compensation capacitor. This configuration provides high slew rate (250V/µs) while consuming very low quiescent current (460µA/ch). This exceptional full-power performance comes at the price of a slightly higher input noise voltage than alternative architectures. The 8.4nV/ $\sqrt{\text{Hz}}$  input voltage noise for the OPA2889 is exceptionally low for this type of input stage.

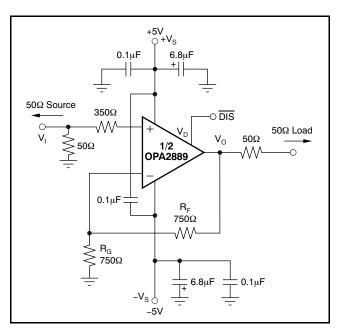

Figure 50 shows the dc-coupled, gain of +2V/V, dual power-supply circuit configuration used as the basis of the ±5V Electrical Characteristics and ±5V Typical Characteristics. This illustration is for one channel: the other channel is connected similarly. For test purposes, the input impedance is set to  $50\Omega$  with a resistor to ground and the output impedance is set to  $100\Omega$ . Voltage swings reported in the Electrical Characteristics are taken directly at the input and output pins, while output powers (dBm) are at the matched  $50\Omega$  load. For the circuit of Figure 50, the total effective load will be  $100\Omega \parallel 1.5k\Omega$ . The disable control line (MSOP-10 package only) is typically left open for normal amplifier operation. Two optional components are included in Figure 50. An additional resistor (350 $\Omega$ ) is included in series with the noninverting input. Combined with the  $25\Omega$  dc source resistance looking back towards the signal generator. this resistor gives an input bias current cancelling resistance that matches the  $375\Omega$  source resistance seen at the inverting input (see the DC Accuracy and Offset Control section). In addition to the usual power-supply decoupling capacitors to ground, a 0.1µF capacitor is included between the two power-supply pins. In practical printed circuit board (PCB) layouts, this optional-added capacitor typically improves the 2nd-harmonic distortion performance by 3dB to 6dB.

Figure 50. DC-Coupled, G = +2, Bipolar Supply, Specification and Test Circuit

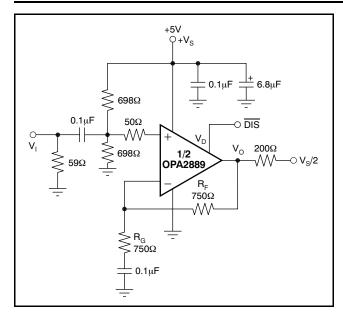

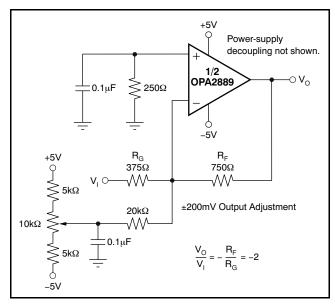

Figure 51 illustrates the ac-coupled, gain of +2V/V, single-supply circuit configuration used as the basis of the +5V Electrical Characteristics and +5V Typical Chararacteristics. Though not a rail-to-rail design, the OPA2889 requires minimal input and output voltage headroom compared to other very wideband voltage-feedback op amps. It delivers a 2.8V<sub>PP</sub> output swing on a single +5V supply with > 50MHz bandwidth. The key requirement of broadband single-supply operation is to maintain input and output signal swings within the usable voltage ranges at both the input and the output. The circuit of Figure 51 establishes an input midpoint bias using a simple resistive divider from the +5V supply (two 698Ω resistors). Separate bias networks would be required at each input. The input signal is then ac-coupled into the midpoint voltage bias. The input voltage can swing to within 1.1V of either supply pin, giving a 2V<sub>PP</sub> input signal range centered between the supply pins. The input impedance matching resistor (59 $\Omega$ ) used for testing is adjusted to give a  $50\Omega$  input load when the parallel combination of the biasing divider network is included.

Figure 51. DC-Coupled, G = +2, Single-Supply, Specification and Test Circuit

Again, an additional resistor ( $50\Omega$  in this case) is included directly in series with the noninverting input. This minimum recommended value provides part of the dc source resistance matching for the noninverting input bias current. It is also used to form a simple parasitic pole to roll off the frequency response at very high frequencies ( > 500 MHz) using the input parasitic capacitance. The gain resistor ( $R_G$ ) is ac-coupled, giving the circuit a dc gain of +1, which puts the input dc bias voltage (2.5V) on the output as well. The output voltage can swing to within 1V of either supply pin while delivering > 40 mA output current.

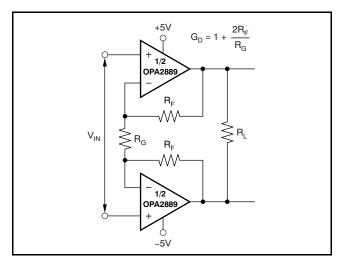

### **DIFFERENTIAL OPERATION**

Figure 52 shows the inverting input differential configuration used as the basis for the ±5V and +5V Typical Characteristics. This circuit offers a combination of excellent distortion with low quiescent current.

The other possibility is using the OPA2889 in a differential configuration as shown in Figure 53. This figure illustrates the differential noninverting input configuration which has the advantage of showing a high input impedance to any prior stage.

Figure 52. Differential Inverting Specification and Test Circuit

Figure 53. Differential Noninverting Specification and Test Circuit

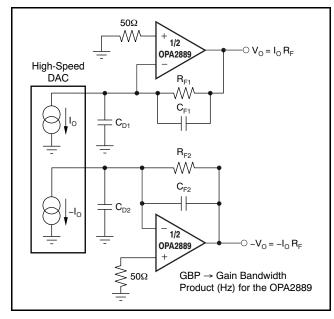

# HIGH-PERFORMANCE DAC TRANSIMPEDANCE AMPLIFIER

High-frequency DDS Digital-to-Analog Converters (DACs) require a low distortion output amplifier to retain their SFDR performance into real-world loads. Figure 54 shows a single-ended output drive implementation. The diagram shows the signal output current(s) connected into the virtual ground summing junction(s) of the OPA2889, which is set up as a transimpedance stage or I-V converter. If the DAC requires that its outputs terminate to a compliance voltage other than ground for operation, the appropriate voltage level may be applied to the noninverting input of the OPA2889. The dc gain for this circuit is equal to R<sub>F</sub>. At high frequencies, the DAC output capacitance (C<sub>D</sub> in Figure 54) produces a zero in the noise gain for the OPA2889 that may cause peaking in the closed-loop frequency response. C<sub>F</sub> is added across R<sub>F</sub> to compensate for this noise gain peaking. To achieve a flat transimpedance frequency response, the pole in each feedback network should be set to:

$$\frac{1}{2\pi R_F C_F} = \sqrt{\frac{GBP}{4\pi R_F C_D}} \tag{1}$$

which gives a cutoff frequency f<sub>-3dB</sub> of approximately:

$$f_{-3dB} = \sqrt{\frac{GBP}{2\pi R_F C_D}}$$

(2)

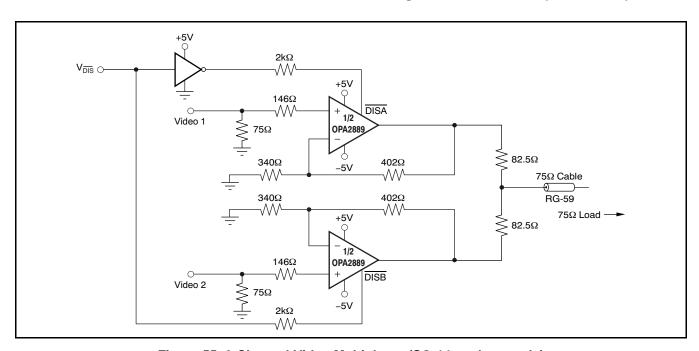

### WIDEBAND VIDEO MULTIPLEXING

One common application for video speed amplifiers that include a disable pin is to wire multiple amplifier outputs together, then select one of several possible video inputs to source onto a single line. This simple wired-OR video multiplexer can be easily implemented using the OP2889IDGS (MSOP-10 package only), as shown in Figure 55.

Figure 54. DAC Transimpedance Amplifier

Figure 55. 2-Channel Video Multiplexer (SO-14 package only)

Typically, channel switching is performed either on sync or retrace time in the video signal. The two inputs are approximately equal at this point. The make-before-break disable characteristic of the OPA2889 ensures that there is always one amplifier controlling the line when using a wired-OR circuit like that shown in Figure 55. Because both inputs may be on for a short period during the transition between channels, the outputs are combined through the output impedance matching resistors (82.5 $\Omega$  in this case). When one channel is disabled, its feedback network forms part of the output impedance and slightly attenuates the signal in getting out onto the cable. The gain and output matching resistor are slightly increased to get a signal gain of +1V/V at the matched load and provide a 75 $\Omega$  output impedance to the cable. The video multiplexer connection (see Figure 55) also ensures that the maximum differential voltage across the inputs of the unselected channel does not exceed the rated ±1.2V maximum for standard video signal levels.

See the *Disable Operation* section for the turn-on and turn-off switching glitches using a 0V input for a single channel is typically less than ±50mV. Where two outputs are switched (see Figure 55), the output line is always under the control of one amplifier or the other as a result of the make-before-break disable timing. In this case, the switching glitches for two 0V inputs drops to < 20mV.

### **HIGH-SPEED DELAY CIRCUIT**

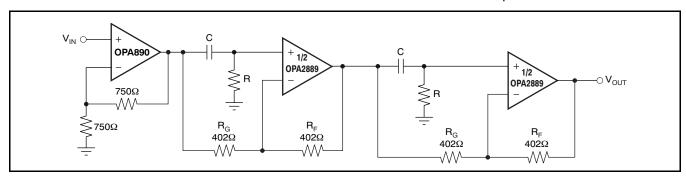

The OPA2889 makes an ideal amplifier for a variety of active filter designs. Figure 56 illustrates a circuit that uses the two amplifiers within the dual OPA2889 to design a 2-stage analog delay circuit. For simplicity, the circuit uses a dual-supply (±5V) operation, but it can also be modified to operate on a signal supply. The input to the first filter stage is driven by the OPA890 as a gain of +2V/V to isolate the signal input from the filter network.

Each of the two filter stages is a 1st-order filter with a voltage gain of +1V/V. The delay time through one filter is given by Equation 3.

$$t_{GR0} = 2RC \tag{3}$$

For a more accurate analysis of the circuit, consider the group delay for the amplifiers. For example, in the case of the OPA2889, the group delay in the bandwidth from 1MHz to 100MHz is approximately 1.0ns. To account for this delay, modify the transfer function, which now comes out to be:

$$t_{GR} = 2 (2RC + T_D) \tag{4}$$

with  $T_D = (1/360) \times (d\phi/df) =$  delay of the op amp itself. The values of resistors  $R_F$  and  $R_G$  should be equal and low to avoid parasitic effects. If the all-pass filter is designed for very low delay times, include parasitic board capacitances to calculate the correct delay time. Simulating this application using the PSPICE model of the OPA2889 allows this design to be tuned to the desired performance.

Figure 56. 2-Stage, All-Pass Network

### **DIFFERENTIAL RECEIVER/DRIVER**

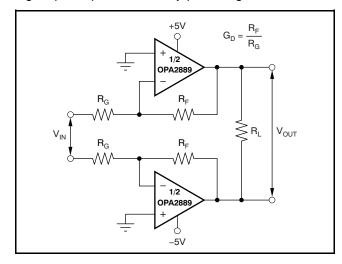

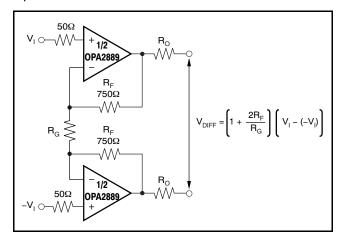

A very versatile application for a dual operational amplifier is the differential amplifier configuration shown in Figure 57. With both amplifiers of the OPA2889 connected for noninverting operation, the circuit provides a high input impedance whereas the gain can easily be set by just one resistor, R<sub>G</sub>. When operated in low gains, the output swing may be limited as a result of the common-mode input swing limits of the amplifier itself. An interesting modification of this circuit is to place a capacitor in series with R<sub>G</sub>. Now the dc gain for each side is reduced to +1V/V, whereas the ac gain still follows the standard transfer function of  $G = 1 + 2R_F/R_G$ . This might be advantageous for applications processing only a frequency band that excludes dc or very low frequencies. An input dc voltage resulting from input bias currents is not amplified by the ac gain and can be kept low. This circuit can be used as a differential line receiver, driver, or as an interface to a differential input ADC.

Figure 57. High-Speed Differential Receiver

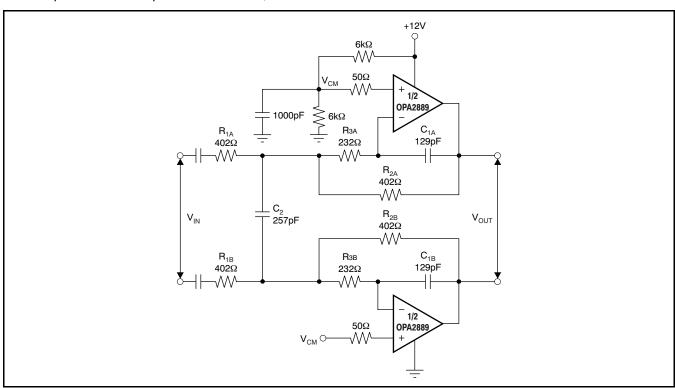

# SINGLE-SUPPLY MFB DIFFERENTIAL ACTIVE FILTER: 2MHz BUTTERWORTH CONFIGURATION

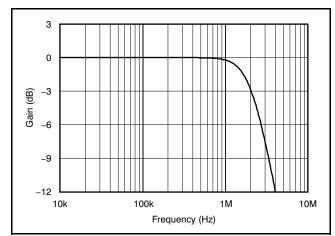

The active filter circuit illustrated in Figure 59 can be easily implemented using the OPA2889. In this configuration, each amplifier of the OPA2889 operates as an integrator. For this reason, this type of application is also called an *infinite gain filter* implementation. A Butterworth filter can be implemented using the following component ratios:

$$\begin{split} f_{O} &= \frac{1}{2 \times \pi \times R \times C} \\ R_{1} &= R_{2} = 0.65 \times R \\ R_{3} &= 0.375 \times R \\ C_{1} &= C \\ C_{2} &= 2 \times C \end{split}$$

The frequency response for a 2MHz Butterworth filter is shown in Figure 58. One advantage for using this type of filter is the independent setting of  $\omega_{o}$  and Q. Q can be easily adjusted by changing the  $R_{3A,\ B}$  resistors without affecting  $\omega_{o}.$

Figure 58. Multiple Feedback Filter Frequency Response

www.ti.com

### LOW POWER, DC-COUPLED, SINGLE-TO-DIFFERENTIAL DRIVER FOR ≤100kHz INPUT

In systems where the input is differential (see front-page figure), the OPA2889 can be used in the inverting configuration with an additional dc bias applied to its positive input so as to keep the input to the ADS8472 within its rated operating voltage range. The dc bias can be derived from the REF3220 or the voltage REF3240 reference ICs. configuration shown on the front page of the data sheet is capable of delivering better than 100dB SNR and -100dBc THD at an input frequency of 200kHz. In case band-pass filters are used to filter the input, care should be taken to ensure that the signal swing at the input of the band-pass filter is small, so as to

minimize the distortion introduced by the filter. In such cases, the gain of the circuit shown on the front page of the data sheet can be increased to keep the input to the ADS8472 large in order to keep the SNR of the system high. Note that the gain of the system from the positive input to the output of the OPA2889 in such a configuration is a function of the ac signal gain. A resistor divider can be used to scale the output of the REF3220 or REF3240 to reduce the voltage at the dc input to OPA2889 to keep the voltage at the input of the converter within its rated operating range.

Figure 59. Single-Supply, MFB Active Filter, 2MHz LP Butterworth

### **DESIGN-IN TOOLS**

### **DEMONSTRATION FIXTURES**

Two printed circuit boards (PCBs) are available to assist in the initial evaluation of circuit performance using the OPA2889 in its two package options. Both of these are offered free of charge as unpopulated PCBs, delivered with a user's guide. The summary information for these fixtures is shown in Table 1.

**Table 1. Demonstration Fixtures by Package**

| PRODUCT     | PACKAGE | ORDERING NUMBER | LITERATURE<br>NUMBER |

|-------------|---------|-----------------|----------------------|

| OPA2889ID   | SO-8    | DEM-OPA-SO-2A   | SBOU003A             |

| OPA2889IDGS | MSOP-10 | DEM-OPA-MSOP-2B | SBOU040              |

The demonstration fixtures can be requested at the Texas Instruments web site (www.ti.com) through the OPA2889 product folder.

### **OPTIMIZING RESISTOR VALUES**

Because the OPA2889 is a unity-gain stable, voltage-feedback op amp, a wide range of resistor values may be used for the feedback and gain setting resistors. The primary limits on these values are set by dynamic range (noise and distortion) and parasitic capacitance considerations. For a noninverting unity-gain follower application, the feedback connection should be made with a direct short. Usually, the feedback resistor value should be between  $200\Omega$  and  $1.5k\Omega$ . Below  $200\Omega$ , the feedback network presents additional output loading which can degrade the harmonic distortion performance of the OPA2889. Above  $1.5k\Omega$ , the typical parasitic capacitance (approximately 0.2pF) across the feedback resistor can cause unintentional band-limiting in the amplifier response.

A good rule of thumb is to target the parallel combination of  $R_{\text{F}}$  and  $R_{\text{G}}$  (see Figure 50) to be less than approximately 400 $\Omega$ . The combined impedance  $R_{\text{F}} \parallel R_{\text{G}}$  interacts with the inverting input capacitance, placing an additional pole in the feedback network and thus, a zero in the forward response. Assuming a 2pF total parasitic on the inverting node, holding  $R_{\text{F}} \parallel R_{\text{G}} < 400\Omega$  keeps this pole above 160MHz. By itself, this constraint implies that the feedback resistor  $R_{\text{F}}$  can increase to several  $k\Omega$  at high gains. This increase in resistor size is acceptable as long as the pole formed by  $R_{\text{F}}$  and any parasitic capacitance appearing in parallel is kept out of the frequency range of interest.

### **MACROMODELS**

Computer simulation of circuit performance using SPICE is often useful when analyzing performance of analog circuits and systems. This principle is particularly true for video and RF amplifier circuits where parasitic capacitance and inductance can have a major effect on circuit performance. A SPICE model for the OPA2889 is available through the Texas Instruments web page (www.ti.com). This model does a good job of predicting small-signal ac and transient performance under a wide variety of operating conditions. It does not do as well in predicting the harmonic distortion or characteristics. This model does not attempt to distinguish between the package types in their small-signal ac performance.

### **OPERATING RECOMMENDATIONS**

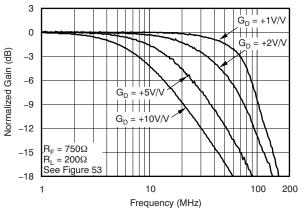

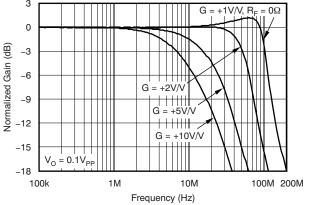

# BANDWIDTH vs GAIN: NONINVERTING OPERATION

Voltage-feedback op amps exhibit decreasing closed-loop bandwidth as the signal gain increases. In theory, this relationship is described by the Gain Bandwidth Product (GBP) shown in the Electrical Characteristics. Ideally, dividing GBP noninverting signal gain (also called the Noise Gain, or NG) predicts the closed-loop bandwidth. In practice, this principle only holds true when the phase margin approaches 90°, as it does in high gain configurations. At low gains (increased feedback factors), most amplifiers exhibit a more complex response with lower phase margin. The OPA2889 is compensated to give a slightly peaked response in a noninverting gain of 2V/V (see Figure 50). This compensation results in a typical gain of +2V/V bandwidth of 60MHz, far exceeding that predicted by dividing the 75MHz GBP by 2. Increasing the gain causes the phase margin to approach 90° and the bandwidth to more closely approach the predicted value of (GBP/NG). At a gain of +10, the 8MHz bandwidth shown in the Electrical Characteristics agrees closely with that predicted using the simple formula and the typical GBP of 75MHz.

The frequency response in a gain of  $\pm 2V/V$  may be modified to achieve exceptional flatness simply by increasing the noise gain to 2.5V/V. One way to modify the response without affecting the  $\pm 2V/V$  signal gain, is to add a  $\pm 7500$  resistor across the two inputs, as shown in the circuit of Figure 50. A similar technique may be used to reduce peaking in unity-gain (voltage follower) applications. For example, by using a  $\pm 7500$  feedback resistor along

Submit Documentation Feedback

www.ti.com

with a  $750\Omega$  resistor across the two op amp inputs, the voltage follower response is similar to the gain of +2V/V response of Figure 51. Reducing the value of the resistor across the op amp inputs further limits the frequency response due to increased noise gain.

The OPA2889 exhibits minimal bandwidth reduction going to single-supply (+5V) operation as compared with ±5V. This behavior occurs because the internal bias control circuitry retains nearly constant quiescent current as the total supply voltage between the supply pins is changed.

### INVERTING AMPLIFIER OPERATION

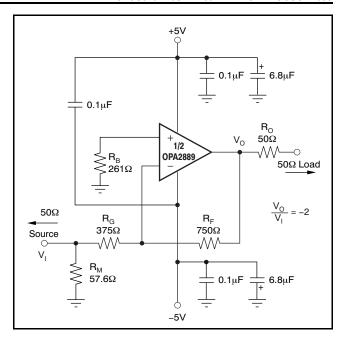

The OPA2889 is a general-purpose, wideband, voltage-feedback op amp; therefore, all of the familiar op amp application circuits are available to the designer. Inverting operation is one of the more common requirements and offers several performance benefits. See Figure 60 for a typical inverting configuration where the I/O impedances and signal gain from Figure 50 are retained in an inverting circuit configuration.

In the inverting configuration, three key design considerations must be noted. The first is that the gain resistor (R<sub>G</sub>) becomes part of the signal channel input impedance. If input impedance matching is desired (which is beneficial whenever the signal is coupled through a cable, twisted-pair, long PCB trace, or other transmission line conductor), R<sub>G</sub> may be set equal to the required termination value and R<sub>F</sub> adjusted to give the desired gain. This consideration is the simplest approach and results in optimum bandwidth and noise performance. However, at low inverting gains, the resultant feedback resistor value can present a significant load to the amplifier output. For an inverting gain of -2V/V, setting  $R_G$  to  $50\Omega$  for input matching eliminates the need for R<sub>M</sub> but requires a  $100\Omega$  feedback resistor. This approach has the interesting advantage that the noise gain becomes equal to 2V/V for a  $50\Omega$  source impedance—the same as the noninverting circuits considered in Figure 60 The amplifier output, however, now sees the  $100\Omega$  feedback resistor in parallel with the external load. In general, the feedback resistor should be limited to the  $200\Omega$  to  $1.5k\Omega$  range. In this case, it is preferable to increase both the R<sub>F</sub> and R<sub>G</sub> values (see Figure 60), and then achieve the input matching impedance with a third resistor (R<sub>M</sub>) to ground. The total input impedance becomes the parallel combination of R<sub>G</sub> and R<sub>M</sub>.

Figure 60. Gain of -2V/V Example Circuit

The second major consideration, touched on in the previous paragraph, is that the signal source impedance becomes part of the noise gain equation and influences the bandwidth. For the example in Figure 60, the  $R_M$  value combined in parallel with the external  $50\Omega$  source impedance yields an effective driving impedance of  $50\Omega$  ||  $57.6\Omega$  =  $26.7\Omega$ . This impedance is added in series with  $R_G$  for calculating the noise gain (NG). The resulting NG is 2.86V/V for Figure 60, as opposed to only 2V/V if  $R_M$  could be eliminated as discussed above. Therefore, the bandwidth is slightly lower for the gain of -2V/V circuit of Figure 60 than for the gain of +2V/V circuit of Figure 50.

The third important consideration in inverting amplifier design is setting the bias current cancellation resistor on the noninverting input ( $R_B$ ). If this resistor is set equal to the total dc resistance looking out of the inverting node, the output dc error, as a result of the input bias currents, is reduced to (Input Offset Current)  $\times$   $R_F$ . If the  $50\Omega$  source impedance is dc-coupled in Figure 60, the total resistance to ground on the inverting input is  $402\Omega$ .

Combining this resistance in parallel with the feedback resistor gives the  $R_B=261\Omega$  used in this example. To reduce the additional high-frequency noise introduced by this resistor, it is sometimes bypassed with a capacitor. As long as  $R_B<350\Omega,$  the capacitor is not required because the total noise contribution of all other terms will be less than that of

the op amp input noise voltage. As a minimum, the OPA2889 requires an  $R_{\text{B}}$  value of  $50\Omega$  to damp out parasitic-induced peaking—a direct short to ground on the noninverting input runs the risk of a very high-frequency instability in the input stage.

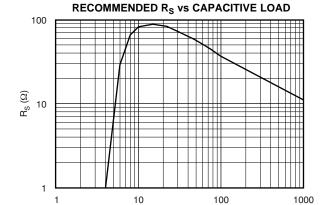

### **DRIVING CAPACITIVE LOADS**

One of the most demanding and yet very common load conditions for an op amp is capacitive loading. Often, the capacitive load is the input of an ADC—including additional external capacitance that may be recommended to improve ADC linearity. A high-speed, high open-loop gain amplifier such as the OPA2889 can be very susceptible to decreased stability and closed-loop response peaking when a capacitive load is placed directly on the output pin. When the open-loop output resistance of the amplifier is considered, this capacitive load introduces an additional pole in the signal path that can decrease the phase margin. Several external solutions to this problem have been suggested. When the primary considerations are frequency response flatness, pulse response fidelity, and/or distortion, the simplest and most effective solution is to isolate the capacitive load from the feedback loop by inserting a series-isolation resistor between the amplifier output and the capacitive load. This solution does not eliminate the pole from the loop response, but rather shifts it and adds a zero at a higher frequency. The additional zero acts to cancel the phase lag from the capacitive load pole, thus increasing the phase margin and improving stability.

Typical Chararacteristics show the recommended R<sub>S</sub> versus capacitive load Figure 15 and Figure 16) and the resulting frequency response at the load. Parasitic capacitive loads greater than 2pF can begin to degrade the performance of the OPA2889. Long PCB traces, unmatched cables, and connections to multiple devices can easily exceed this value. Always consider this effect carefully, and add recommended series resistor as close as possible to the OPA2889 output pin (see the Board Layout Guidelines section).

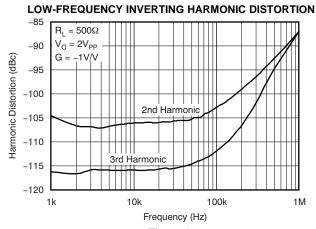

### **DISTORTION PERFORMANCE**

The OPA2889 provides good distortion performance into a  $200\Omega$  load on  $\pm 5V$  supplies. Relative to alternative solutions, it provides exceptional performance into lighter loads and/or operating on a single +5V supply. Generally, until the fundamental signal reaches very high frequency or power levels, the 2nd-harmonic dominates the distortion with a negligible 3rd-harmonic component. Focusing then on the 2nd-harmonic, increasing the load impedance improves distortion directly. Remember that the total load includes the feedback network; in noninverting configuration (see Figure 50), this total is the sum of  $R_{\text{F}}$  +  $R_{\text{G}}$ , while in the inverting configuration it is just  $R_{\text{F}}$ . Also, providing an additional supply-decoupling capacitor (0.1μF) between the supply pins (for bipolar operation) improves the 2nd-order distortion slightly (3dB to Operating differentially also 2nd-harmonic distortion terms (see the plot on the front page).

In most op amps, increasing the output voltage swing increases harmonic distortion directly. The output stage used in the OPA2889 actually holds the difference between fundamental power and the 2ndand 3rd-harmonic powers relatively constant with increasing output power until very large output swings are required ( > 4V<sub>PP</sub>). This result also shows up in the 2-tone, 3rd-order intermodulation spurious (IM3) response curves. The 3rd-order spurious levels are extremely low at low output power levels. The output stage continues to hold them low even as the fundamental power reaches very high levels. As the Characteristics show, the spurious intermodulation powers do not increase as predicted by a traditional intercept model. As the fundamental power level increases, the dynamic range does not decrease significantly. For two tones centered at 1MHz, with 4dBm/tone into a matched  $50\Omega$  load (that is, 1V<sub>PP</sub> for each tone at the load, which requires 4V<sub>PP</sub> for the overall 2-tone envelope at the output pin), the Typical Characteristics show -73dBc difference between the test tone powers and the 3rd-order intermodulation spurious powers. This performance is exceptional for an amplifier with only 4.6mW of internal power dissipation.

Submit Documentation Feedback

### **NOISE PERFORMANCE**

High slew rate, unity-gain stable, voltage-feedback op amps usually achieve the slew rate at the expense of a higher input noise voltage. However, the  $8.4\text{nV}/\sqrt{\text{Hz}}$  input voltage noise for the OPA2889 is much lower than that of comparable amplifiers. The input-referred voltage noise, and the two input-referred current noise terms, combine to give low output noise under a wide variety of operating conditions. Figure 61 shows the op amp noise analysis model with all the noise terms included. In this model, all noise terms are taken to be noise voltage or current density terms in either  $nV/\sqrt{\text{Hz}}$  or  $pA/\sqrt{\text{Hz}}$ .

Figure 61. Op Amp Noise Analysis Model

The total output spot noise voltage can be computed as the square root of the sum of all squared output noise voltage contributors. Equation 5 shows the general form for the output noise voltage using the terms shown in Figure 61.

$$E_{O} = \sqrt{\left[E_{NI}^{2} + (I_{BN}R_{S})^{2} + 4kTR_{S}\right]NG^{2} + (I_{BI}R_{F})^{2} + 4kTR_{F}NG}}$$

(5)

Dividing this expression by the noise gain (NG =  $(1 + R_F/R_G)$ ) gives the equivalent input-referred spot noise voltage at the noninverting input, as shown in Equation 6.

$$E_{N} = \sqrt{E_{NI}^{2} + (I_{BN}R_{S})^{2} + 4kTR_{S} + \left(\frac{I_{BI}R_{F}}{NG}\right)^{2} + \frac{4kTR_{F}}{NG}}$$

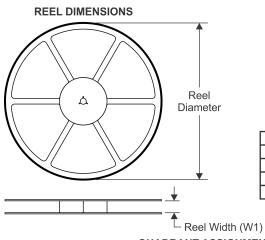

(6)