# LMX2581 Wideband Frequency Synthesizer with Integrated VCO

Check for Samples: LMX2581

## **FEATURES**

#### **GENERAL FEATURES**

- 50 3760 MHz Output Frequency

- Low Voltage Logic Compatibility

- Digital Lock Detect

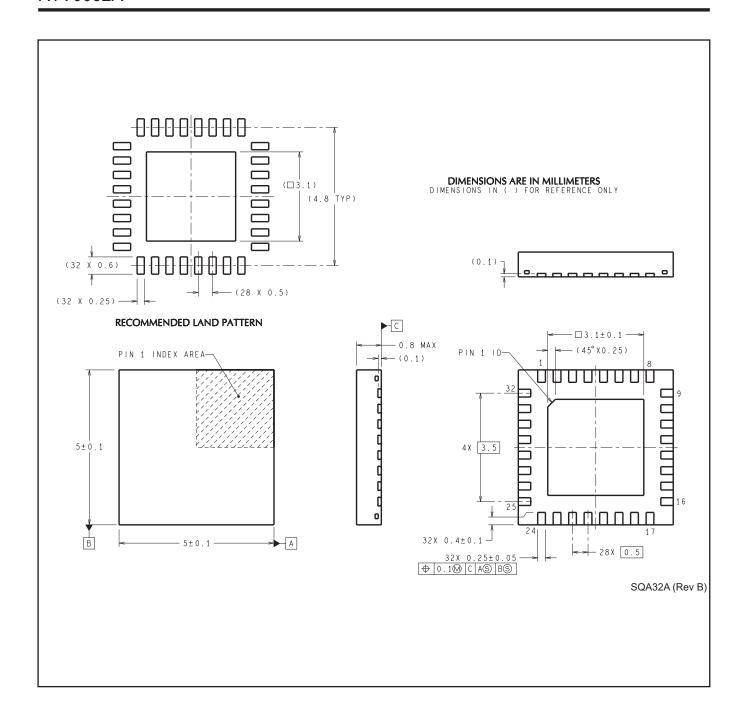

- 32 Pin QFN Package

HIGH PERFORMANCE PLL

- Supports Integer and Fractional Modes

- -229 dBc/Hz Normalized PLL Phase Noise

- -120.8 dBc/Hz Normalized PLL 1/f Noise

- 200 MHz Maximum Phase Detector Frequency

- Programmable Charge Pump Current MULTI-CORE VCO AND OUTPUTS

- VCO Tuning Range: 1880 3760 MHz

- Programmable Option to Use an External VCO

- -137 dBc/Hz Phase Noise @ 1 MHz offset for a 2.5 GHz Carrier

- -155 dBc/Hz Noise Floor

- Programmable to divide by 1 (bypass), 2, 4, 6, 8, ..., 38

Dual Programmable Outputs with Power from -3 to +12 dBm

### TARGET APPLICATIONS

- Wireless Infrastructure (UMTS, LTE, WiMax, Multi-Standard Base Stations)

- Broadband Wireless

- Wireless Meter Reading

- Test and Measurement

- Clock Generation

#### DESCRIPTION

The LMX2581 is an ultra low noise wideband frequency synthesizer which integrates a delta-sigma fractional N PLL, a VCO with fully integrated tank circuit, and an optional frequency divider. This device integrates several low-noise, high precision LDOs to provide superior supply noise immunity and more consistent performance. When combined with a high quality reference oscillator, the LMX2581 generates a very stable, ultra low noise signal. The internal VCO can be bypassed so that an external VCO can be used.

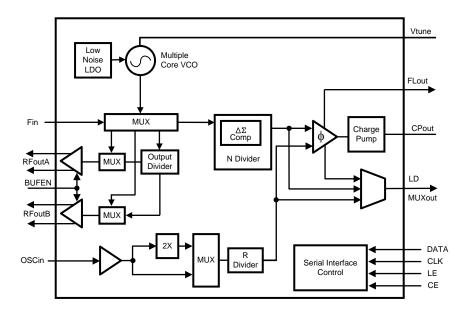

## **FUNCTIONAL BLOCK DIAGRAM**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

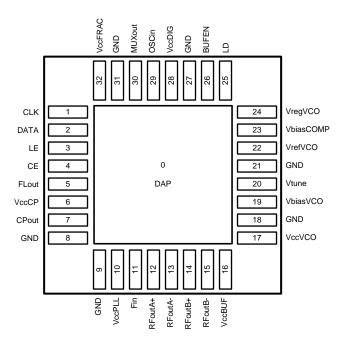

## **CONNECTION DIAGRAM**

**Table 1. Pin Descriptions**

|      | Table 1.1 III Descriptions |        |                                                                                                                                                             |  |  |  |

|------|----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin# | Pin Name                   | Type   | Description                                                                                                                                                 |  |  |  |

| 0    | DAP                        | GND    | The DAP should be grounded.                                                                                                                                 |  |  |  |

| 1    | CLK                        | Input  | MICROWIRE Clock Input. High Impedance CMOS input.                                                                                                           |  |  |  |

| 2    | DATA                       | Input  | IICROWIRE Data. High Impedance CMOS input.                                                                                                                  |  |  |  |

| 3    | LE                         | Input  | MICROWIRE Latch Enable. High Impedance CMOS input.                                                                                                          |  |  |  |

| 4    | CE                         | Input  | Chip Enable Pin.                                                                                                                                            |  |  |  |

| 5    | FLout                      | Output | Fastlock Output that can be high Z or ground.                                                                                                               |  |  |  |

| 6    | VccCP                      | Supply | Charge Pump Supply.                                                                                                                                         |  |  |  |

| 7    | CPout                      | Output | Charge Pump Output.                                                                                                                                         |  |  |  |

| 8    | GND                        | GND    | Ground for the Charge Pump.                                                                                                                                 |  |  |  |

| 9    | GND                        | GND    | Ground for the N and R divider.                                                                                                                             |  |  |  |

| 10   | VccPLL                     | Supply | Supply for the PLL.                                                                                                                                         |  |  |  |

| 11   | Fin                        | Input  | High frequency input pin for an external VCO. Leave Open or Ground if not used.                                                                             |  |  |  |

| 12   | RFoutA+                    | Output | Differential divided output.                                                                                                                                |  |  |  |

| 13   | RFoutA-                    | Output | Differential divided output.                                                                                                                                |  |  |  |

| 14   | RFoutB+                    | Output | Differential divided output.                                                                                                                                |  |  |  |

| 15   | RFoutB-                    | Output | Differential divided output.                                                                                                                                |  |  |  |

| 16   | VccBUF                     | Supply | Supply for the Output Buffer.                                                                                                                               |  |  |  |

| 17   | VccVCO                     | Supply | Supply for the VCO.                                                                                                                                         |  |  |  |

| 18   | GND                        | GND    | Ground Pin for the VCO. This can be attached to the regular ground. Ensure a solid trace connects this pin to the bypass capacitors on pins 19, 23, and 24. |  |  |  |

| 19   | VbiasVCO                   |        | Bias circuitry for the VCO. Place a 2.2 μF capacitor to GND (Preferably close to Pin 18).                                                                   |  |  |  |

| 20   | Vtune                      | Input  | VCO tuning voltage input.                                                                                                                                   |  |  |  |

| 21   | GND                        | GND    | VCO ground.                                                                                                                                                 |  |  |  |

Product Folder Links: LMX2581

Submit Documentation Feedback

# **Table 1. Pin Descriptions (continued)**

| Pin# | Pin Name  | Туре   | Description                                                                                                                                                                                                |  |

|------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 22   | VrefVCO   |        | VCO capacitance. Place a capacitor to GND (Preferably close to Pin 18). This value should be between 5% and 10% of the capacitance at pin 24. Recommended value is 1 uF.                                   |  |

| 23   | VbiasCOMP |        | VCO bias voltage temperature compensation circuit. Place a 10 uF capacitor to GND (Preferably close to Pin 18). If it is possible, put two 10 uF capacitors as this may improve the VCO phase no slightly. |  |

| 24   | VregVCO   |        | VCO regulator output. Place a 10 uF capacitor to GND (Preferably close to Pin 18). If it is possible, put two 10 uF capacitors as this may improve the VCO phase noise slightly.                           |  |

| 25   | LD        | Output | Lock detect output.                                                                                                                                                                                        |  |

| 26   | BUFEN     | Input  | Enable pin for the RF output buffer.                                                                                                                                                                       |  |

| 27   | GND       | GND    | Digital Ground.                                                                                                                                                                                            |  |

| 28   | VccDIG    | Supply | Digital Supply.                                                                                                                                                                                            |  |

| 29   | OSCin     | Input  | Reference input clock.                                                                                                                                                                                     |  |

| 30   | MUXout    | Output | Multiplexed output that can select lock detect, N divider, or R divider.                                                                                                                                   |  |

| 31   | GND       | GND    | Ground for the fractional circuitry.                                                                                                                                                                       |  |

| 32   | VccFRAC   | Vcc    | Supply for the fractional circuitry.                                                                                                                                                                       |  |

## ABSOLUTE MAXIMUM RATINGS(1) (2)

| Parameter                                 | Symbol             | Ratings                                | Units |

|-------------------------------------------|--------------------|----------------------------------------|-------|

| Power Supply Voltage                      | Vcc                | -0.3 to 3.6                            | V     |

| Input Voltage to Pins other than Vcc Pins | V <sub>IN</sub>    | -0.3 to (Vcc + 0.3)                    | V     |

| Storage Temperature Range                 | T <sub>STG</sub>   | -65 to 150                             | °C    |

| Lead Temperature (solder 4 sec.)          | T <sub>L</sub>     | +260                                   | °C    |

| Junction Temperature                      | TJ                 | +150                                   | °C    |

| Voltage on OSCin (Pin29)                  | V <sub>OSCin</sub> | ≤1.8 with Vcc Applied<br>≤1 with Vcc=0 | Vpp   |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" indicate limits beyond which permanent or latent damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics.

## RECOMMENDED OPERATING CONDITIONS

| Parameter            | Symbol         | Min  | Тур | Max  | Units |

|----------------------|----------------|------|-----|------|-------|

| Power Supply Voltage | Vcc            | 3.15 | 3.3 | 3.45 | ٧     |

| Junction Temperature | $T_J$          |      |     | 125  | °C    |

| Ambient Temperature  | T <sub>A</sub> | -40  |     | 85   | °C    |

## THERMAL CHARACTERISTICS

| Thermal Resistance     | Symbol          | Тур | Units |

|------------------------|-----------------|-----|-------|

| Junction to Ambient    | Ø <sub>JA</sub> | 30  | °C/W  |

| Junction to Case (DAP) | Ø <sub>JC</sub> | 4   | °C/W  |

<sup>(2)</sup> This device has an ESD rating of ≥2500 V Human Body Model (HBM), ≥ 1250 V Charged Device Model (CDM), and ≥ 250 V Machine model (MM). It should only be assembled in ESD free workstations.

### **ELECTRICAL CHARACTERISTICS**

$(3.15 \text{ V} \leq \text{Vcc} \leq 3.45 \text{ V}, -40 ^{\circ}\text{C} \leq \text{T}_{A} \leq 85 ^{\circ}\text{C}; \text{ except as specified. Typical values are at Vcc} = 3.3 \text{ V}, 25 ^{\circ}\text{C}.)$

| Symbol                  | Parameter                                | Conditions                           |                           | Min    | Тур     | Max     | Units      |      |

|-------------------------|------------------------------------------|--------------------------------------|---------------------------|--------|---------|---------|------------|------|

|                         | 1                                        | Current Consump                      | otion                     |        |         |         | -11        |      |

| I <sub>CC</sub>         | Entire Chip Supply<br>Current            | One Output Enab<br>OUTx_PWR = 1      |                           |        | 178     |         | mA         |      |

| I <sub>CC</sub> Core    | Supply Current Except for Output Buffers | VCO Divider Bypa                     | ssed                      |        | 134     |         | mA         |      |

| I <sub>CC</sub> RFout   | Additive Current for<br>Output Buffer    | OUTx_PWR = 1                         | 5                         |        | 44      |         | mA         |      |

| I <sub>CC</sub> VCO_DIV | Additive VCO Divider<br>Current          | VCO Divider >                        | 1                         |        | 20      |         | mA         |      |

| I <sub>CC</sub> PD      | Power Down Current                       | Device Powered D<br>(CE Pin = LOW    |                           |        | 7       |         | mA         |      |

|                         | •                                        | OSCin Reference                      | Input                     |        | •       | •       |            |      |

| f                       | OSCin Frequency                          | Doubler Enable                       | d                         | 5      |         | 250     | MHz        |      |

| f <sub>OSCin</sub>      | Range                                    | Doubler Disable                      | ed                        | 5      |         | 900     | IVII IZ    |      |

| V <sub>OSCin</sub>      | OSCin Input Voltage                      | AC Coupled                           |                           | 0.4    |         | 1.7     | Vpp        |      |

| Spur <sub>Foscin</sub>  | Oscin Spur                               |                                      |                           |        | -81     |         | dBc        |      |

|                         |                                          | PLL                                  |                           |        |         |         |            |      |

| f <sub>PD</sub>         | Phase Detector<br>Frequency              | Fractional Mod                       | е                         |        |         | 200     | MHz        |      |

|                         | Charge Pump Gain                         | Gain = 1X                            | Gain = 1X                 |        | 110     |         | _<br>- μA  |      |

| V                       |                                          | Gain = 2X                            |                           |        | 220     |         |            |      |

| $K_PD$                  |                                          |                                      |                           |        |         |         |            |      |

|                         |                                          | Gain = 31X                           |                           |        | 3410    |         |            |      |

| PN <sub>PLL_1/f</sub>   | Normalized PLL 1/f<br>Noise              | Gain > 8X                            |                           |        | - 120.8 |         | dBc<br>/Hz |      |

| PN <sub>PLL_Flat</sub>  | Normalized PLL Noise<br>Floor            | Gain > 8X                            |                           |        | - 229   |         | dBc<br>/Hz |      |

| f <sub>RFin</sub>       | External VCO Input Pin<br>Frequency      | Internal VCOs Bypa<br>(OUTA_PD=OUTB_ |                           | 0.5    |         | 2.2     | GHz        |      |

| PRFin                   | External VCO Input Pin<br>Power          | Internal VCOs Bypa<br>(OUTA_PD=OUTB_ |                           | 0      |         | +8      | dBm        |      |

| Cour                    | Phase Detector Spurs                     | Fpd = 25 MHz                         | :                         |        | -85     |         | dBc        |      |

| Spur <sub>Fpd</sub>     | Fliase Detector Spurs                    | Fpd = 100 MH:                        | Z                         |        | -81     |         | ubc        |      |

|                         |                                          | VCO                                  |                           | -      |         |         |            |      |

| f <sub>VCO</sub>        |                                          | Before the VCO Divider               | All VCO Cores<br>Combined | 1880   |         | 3760    |            |      |

|                         |                                          |                                      | Core 1                    |        | 12 - 24 |         |            |      |

| V                       | VCO Gain                                 | Vtune = 1.3 Volts                    | Vtune = 1.3 Volts         | Core 2 |         | 15 - 30 |            | MHz/ |

| $K_{VCO}$               |                                          | (1)                                  | Core 3                    |        | 20 - 37 |         | V          |      |

|                         |                                          |                                      | Core 4                    |        | 21 - 37 |         |            |      |

|                         | Allowable Temperature                    |                                      | Fvco ≥2.5 GHz             | -125   |         | +125    |            |      |

| $\Delta T_{CL}$         | Drift (2)                                | VCO not being recalibrated           | Fvco < 2.5 GHz            | - 100  |         | +125    | °C         |      |

<sup>(1)</sup> The lower number for the VCO gain applies to the lower end of the tuning range for that VCO core and the upper number for the VCO gain applies to the upper range for that VCO core

gain applies to the upper range for that VCO core.

(2) Continuous tuning range over temperature refers to programming the device at an initial temperature and allowing this temperature to drift WITHOUT reprogramming the device. This drift could be up or down in temperature and the spec does not apply to temperatures that go outside the recommended operating temperatures of the device.

## **ELECTRICAL CHARACTERISTICS (continued)**

(3.15 V ≤ Vcc ≤ 3.45 V, -40°C ≤ T<sub>A</sub> ≤ 85 °C; except as specified. Typical values are at Vcc = 3.3 V, 25 °C.)

| Symbol                  | Parameter                         | Conditions                                                  | _                        | Min   | Тур    | Max | Units      |

|-------------------------|-----------------------------------|-------------------------------------------------------------|--------------------------|-------|--------|-----|------------|

| tuges :                 | VCO Calibration Time              | $f_{OSCin} = 100 \text{ MHz}$<br>$f_{PD} = 100 \text{ MHz}$ | No Pre-<br>programming   |       | 140    |     | us         |

| t <sub>VCOCal</sub>     | (3)                               | Full Band Change 1880 — 3760<br>MHz                         | With Pre-<br>programming |       | 10     |     | us         |

|                         |                                   |                                                             | 10 kHz Offset            |       | -85.4  |     |            |

|                         |                                   |                                                             | 100 kHz Offset           |       | -114.5 |     | dBc<br>/Hz |

|                         |                                   | f <sub>VCO</sub> = 1.9 GHz<br>Core 1                        | 1 MHz Offset             |       | -137.0 |     |            |

|                         |                                   | 33.3                                                        | 10 MHz Offset            |       | -154.2 |     |            |

|                         |                                   |                                                             | 40 MHz Offset            |       | -156.7 |     |            |

|                         |                                   |                                                             | 10 kHz Offset            |       | -84.6  |     |            |

|                         |                                   |                                                             | 100 kHz Offset           |       | -114.1 |     |            |

|                         |                                   | f <sub>VCO</sub> = 2.2 GHz<br>Core 2                        | 1 MHz Offset             |       | -137.5 |     | dBo<br>/Hz |

|                         |                                   | 0010 2                                                      | 10 MHz Offset            |       | -154.5 |     | dBc        |

| DN                      | VCO Phase Noise<br>(OUTx_PWR =15) |                                                             | 40 MHz Offset            |       | -156.1 |     |            |

| $PN_{VCO}$              |                                   |                                                             | 10 kHz Offset            |       | -81.7  |     |            |

|                         |                                   | f <sub>VCO</sub> = 2.7 GHz<br>Core 3                        | 100 kHz Offset           |       | -112.2 |     |            |

|                         |                                   |                                                             | 1 MHz Offset             |       | -136.0 |     |            |

|                         |                                   |                                                             | 10 MHz Offset            |       | -153.1 |     |            |

|                         |                                   |                                                             | 40 MHz Offset            |       | -155.0 |     |            |

|                         |                                   | f <sub>VCO</sub> = 3.3 GHz                                  | 10 kHz Offset            |       | -79.0  |     | dBc<br>/Hz |

|                         |                                   |                                                             | 100 kHz Offset           |       | -108.6 |     |            |

|                         |                                   |                                                             | 1 MHz Offset             |       | -132.6 |     |            |

|                         |                                   |                                                             | 10 MHz Offset            |       | -152.0 |     |            |

|                         |                                   |                                                             | 40 MHz Offset            |       | -155.0 |     |            |

|                         |                                   | Outputs                                                     |                          |       | 1      | 1   |            |

| PRFoutA+/-              | Output Power Level                | Inductor Pull-Up                                            | OUTx_PWR=15              |       | 7.3    |     | -10        |

| PRFoutB+/-              | (4)                               | Fout=2.7 GHz                                                | OUTx_PWR=45              |       | 12     |     | dBn        |

| H2 <sub>RFoutX+/-</sub> | Output Power Level                | Fout = 2.7 GHz                                              | OUTx_PWR=15              |       | -25    |     | dBo        |

|                         | Dig                               | ital Interface (DATA, CLK, LE, CE                           | , MUXout,BUFEN           | , LD) |        | •   | •          |

| $V_{IH}$                | High-Level Input Voltage          |                                                             |                          | 1.4   |        | Vcc | V          |

| V <sub>IL</sub>         | Low Level Input Voltage           |                                                             |                          |       |        | 0.4 | V          |

| I <sub>IH</sub>         | High-Level Input Current          | V <sub>IH</sub> = 1.75 V                                    |                          | -5    |        | 5   | μΑ         |

| I <sub>IL</sub>         | Low-Level Input Current           | V <sub>IL</sub> = 0 V                                       |                          | -5    |        | 5   | μA         |

| V <sub>OH</sub>         | High-Level Output<br>Voltage      | I <sub>OH</sub> = -500 μA                                   |                          | 2     |        |     | V          |

| V <sub>OL</sub>         | Low-Level Output<br>Voltage       | I <sub>OL</sub> = -500 μA                                   |                          |       | 0      | 0.4 | V          |

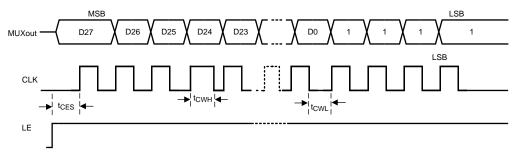

|                         |                                   | MICROWIRE Timing                                            |                          |       |        |     |            |

| t <sub>ES</sub>         | Clock to Enable Low<br>Time       | See Serial Data Input                                       | Timing                   | 35    |        |     | ns         |

<sup>(3)</sup> When the VCO is programmed to a frequency, it goes through a digital calibration where it searches for the correct frequency band until it reaches the final frequency band. After this frequency calibration is done, the VCO will typically be far less than 1 MHz within the final target frequency. This final frequency error is corrected analog lock time, which is totally loop filter dependent, but it can be made <2 us for a wide enough loop filter (perhaps at the expense of fractional spurs). The number reported in the electrical specifications is for this digital VCO calibration time only. The lock time can be greatly reduced if the user can preprogram the device with an initial starting point for which VCO core and what frequency band in the core to start the VCO frequency calibration at. Even if it is the wrong core and the wrong band, it can greatly reduce the lock time provided that this frequency close (<20 MHz) of the final settling frequency.

Product Folder Links: LMX2581

Submit Documentation Feedback

Copyright © 2012-2013, Texas Instruments Incorporated

The output power is dependent of the setup and is also programmable. Consult the Applications section for more information.

The harmonics vary as a function of frequency, output termination, board layout, and output power setting. (5)

## **ELECTRICAL CHARACTERISTICS (continued)**

(3.15 V ≤ Vcc ≤ 3.45 V, -40°C ≤ T<sub>A</sub> ≤ 85 °C; except as specified. Typical values are at Vcc = 3.3 V, 25 °C.)

| Symbol           | Parameter                      | Conditions                   | Min | Тур | Max | Units |

|------------------|--------------------------------|------------------------------|-----|-----|-----|-------|

| t <sub>CS</sub>  | Data to Clock Set Up<br>Time   | See Serial Data Input Timing | 10  |     |     | ns    |

| t <sub>CH</sub>  | Data to Clock Hold Time        | See Serial Data Input Timing | 10  |     |     | ns    |

| t <sub>CWH</sub> | Clock Pulse Width High         | See Serial Data Input Timing | 25  |     |     | ns    |

| t <sub>CWL</sub> | Clock Pulse Width Low          | See Serial Data Input Timing | 25  |     |     | ns    |

| t <sub>CES</sub> | Enable to Clock Set Up<br>Time | See Serial Data Input Timing | 10  |     |     | ns    |

| t <sub>EWH</sub> | Enable Pulse Width<br>High     | See Serial Data Input Timing | 10  |     |     | ns    |

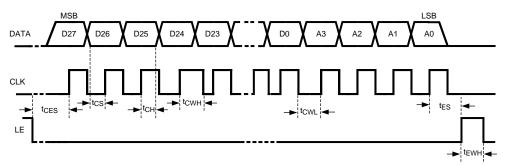

#### **SERIAL DATA TIMING**

## **Serial Data Input Timing**

There are several other considerations for programming:

- A slew rate of at least 30 V/us is recommended for the CLK, DATA, and LE signals

- The DATA is clocked into a shift register on each rising edge of the CLK signal. On the rising edge of the LE signal, the data is sent from the shift registers to an actual counter.

- The LE pin may be held high after programming and this will cause the LMX2581 to ignore clock pulses.

- The CLK signal should not be high when LE transitions to low.

- When CLK and DATA lines are shared between devices, it is recommended to divide down the voltage to the CLK, DATA, and LE pins closer to the minimum voltage. This provides better noise immunity.

- If the CLK and DATA lines are toggled while the in VCO is in lock, as is sometimes the case when these lines are shared with other parts, the phase noise may be degraded during the time of this programming.

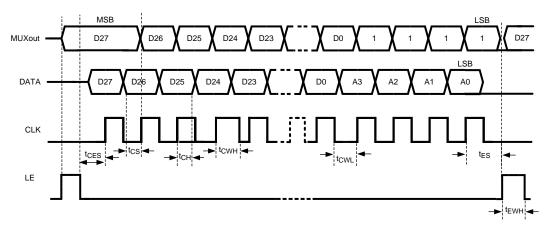

## Serial Data Readback Timing

Readback is done through the the MUXout (or LD) pin with the same clock that is used to clock in the data.

- Choose either the MUXout (or LD) pin for reading back data and program the MUXOUT\_SELECT (or LD\_SELECT) to readback mode.

- Bring the LE pin from low to high to start the readback at the MSB.

- After the signal to the CLK pin goes high, the data will be ready at the readback pin 10 ns afterwards. It is

recommended to read back the data on the falling edge of the clock. Technically, the first bit actually

becomes ready after the rising edge of LE, but it still needs to be clocked out.

- The address being clocked out will all be 1's.

Because the CLK pin is both used to clock in data and clock out data, special care needs to be taken to ensure that erroneous data is not being clocked in during readback. There are two approaches to deal with this. The first approach is to actually send valid data during readback. For this approach, R6 is a recommended register for doing this and this approach is shown:

A second approach is to hold LE high during readback so that the clock pulses do not clock data into the part, but still function for readback purposes. A diagram showing this method is below.

#### **FUNCTIONAL DESCRIPTION**

The LMX2581 is a low power, high performance frequency synthesizer system which includes a PLL (Phased Locked Loop), VCO (Voltage Controlled Oscillator), VCO Divider, and Programmable Output Buffer.

#### **OSCin INPUT and OSCin DOUBLER**

The OSCin pin is driven with a single-ended signal which is used to as a frequency reference. Before the OSCin frequency reaches the phase detector, it may be doubled with the OSCin doubler and/or divided with the PLL R divider.

Because the OSCin signal is used as a clock for the VCO calibration, the OSC\_FREQ field needs to be programmed correctly and a proper signal needs to be applied at the OSCin pin at the time of programming the R0 register order for the VCO calibration to properly work. Higher slew rates tend to yield the best fractional spurs and phase noise, so a square wave signal is best for OSCin. If using a sine wave, higher frequencies tend to yield better phase noise and fractional spurs due to their higher slew rates. The OSCin pin his high impedance, so for optimal performance, it is recommended to use either a shunt resistor or resistive pad to make such that the impedances looking towards our device and from the looking away from our device (as seen by the OSCin pin) are both close to 50 ohms

#### **R DIVIDER**

The R divider divides the OSCin frequency down to the phase detector frequency. With this device, it is possible to use both the doubler and the R divider at the same time.

#### PLL N DIVIDER AND FRACTIONAL CIRCUITRY

The N divider includes fractional compensation and can achieve any fractional denominator (PLL\_DEN) from 1 to 4,194,303. The integer portion, PLL\_N, is the whole part of the N divider value and the fractional portion, PLL\_NUM / PLL\_DEN, is the remaining fraction. PLL\_N, PLL\_NUM, and PLL\_DEN are software programmable. So in general, the total N divider value, N, is determined by: N = PLL\_N + PLL\_NUM / PLL\_DEN The order of the delta sigma modulator is programmable from integer mode to third order. There are also several dithering modes that are also programmable. In order to make the fractional spurs consistent, the modulator is reset any time that the R0 register is programmed.

## PLL PHASE DETECTOR AND CHARGE PUMP

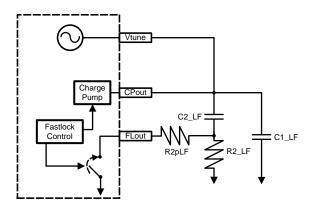

The phase detector compares the outputs of the R and N dividers and generates a correction current corresponding to the phase error. This charge pump current is software programmable to many different levels. The phase detector frequency,  $f_{PD}$ , can be calculated as follows:  $f_{PD} = f_{OSCin} \times OSC_2X / R$ . The charge pump outputs a correction current the loop filter, which is implemented with external components.

#### **EXTERNAL LOOP FILTER**

The LMX2581 requires an external loop filter which is application specific and can be done by software provided on the Texas Instruments website. For the best possible VCO noise, it is recommended that the capacitor on the Vtune pin is at t least 3.3 nF. Not following this guideline will not cause the device to malfunction, but may degrade the VCO phase noise in the 100k-1MHz region, depending on the impedance at lower frequencies as seen by the Vtune pin looking out.

#### LOW NOISE, FULLY INTEGRATED VCO

The VCO takes the voltage from the loop filter and converts this into a frequency. The VCO frequency is related to the other frequencies and divider values as follows:  $f_{VCO} = f_{PD} \times N = f_{OSCin} \times OSC_2X \times N / R$ . The VCO is fully integrated, including the tank inductors.

In order to the reduce the VCO tuning gain and therefore improve the VCO phase noise performance, the internal VCO is actually four VCO cores working in conjunction. These cores starting from lowest frequency to highest frequency are VCO 1, VCO 2, VCO 3, and VCO 4. Each VCO core has 256 different frequency bands. This creates the need for frequency calibration in order to determine the correct VCO core and correct frequency band in that VCO core. The frequency calibration routine is activated any time that the R0 register is programmed with the NO\_FCAL bit equal to zero. In order for this frequency calibration to work properly, the OSC\_FREQ field needs to be set to the correct setting. The are also programmable settings that allow the user to suggest a particular VCO core for the device to choose.

#### PROGRAMMABLE VCO DIVIDER

The VCO divider can be programmed to even values from 2 to 38 as well as bypassed by either one or both of the RFout outputs. When the zero delay mode is not enabled, the VCO divider is not in the feedback path between the VCO and the PLL and therefore has no impact on the PLL loop dynamics. After this programmable divider is changed, it may be beneficial to reprogram the R0 register to recallibrate the VCO . The frequency at the RFout pin is related to the VCO frequency and divider value, VCO\_DIV, as follows:  $f_{RFout} = f_{VCO} / VCO_DIV$  When this divider is enabled, there will be some far-out phase noise contribution to the VCO noise.

When changing to a VCO\_DIV value of 4, either from a state of VCO\_DIV=2 or OUTx\_MUX = 0, it is necessary to program VCO\_DIV first to a value of 6, then to a value of 4. This holds for no other VCO\_DIV value and is not necessary if the VCO frequency (but not VCO\_DIV) is changing

#### **0-DELAY MODE**

When the VCO divider is used, an ambiguous phase relationship is created between the OSCin and RFout pins. 0–Delay mode can be enabled to make this phase relationship deterministic. Note that of the VCO divider is bypassed, then 0-delay mode is not necessary as the phase relationship is already deterministic.

When this mode is used, special care needs to be taken because it does interfere with the VCO calibration if not done correctly. The correct way to use 0–Delay mode is as follows

- 1. If N is not divisible by VCO\_DIV, reduce the phase detector frequency to make it so.

- 2. Program as normal and lock the PLL.

- 3. Program the NO\_FCAL =1.

- 4. Program 0\_DLY = 1. This will cause the PLL to lose lock.

- 5. Program the PLL N value with PLL N\* / VCO DIV, where PLL N\* is the original value.

- 6. The PLL should now be locked in zero delay mode.

### **DETERMINING THE OUTPUT FREQUENCY**

Based on the oscillator input frequency ( $f_{OSC}$ ), PLL R divider value (PLL\_R), PLL N Divider Value (PLL\_N), Fractional Numerator (PLL\_NUM), Fractional Denominator (PLL\_DEN), and VCO divider value (VCO\_DIV), the output frequency of the LMX2581 ( $f_{OLT}$ ) can be determined as follows:

f<sub>OUT</sub> = f<sub>OSC</sub> x OSC\_2X / PLL\_R x (PLL\_N + PLL\_NUM / PLL\_DEN) / VCO\_DIV

## PROGRAMMABLE RF OUTPUT BUFFERS

The output states of the RFoutA and RFoutB pins are controlled by the BUFEN pin as well as the BUFEN\_DIS programming bit. If the pin is powered up, then output power can be programmed to various levels with the OUTx PWR fields.

| OUTA_PD<br>OUTB_PD | BUFEN_DIS | BUFEN Pin | Output State |

|--------------------|-----------|-----------|--------------|

| 1                  | X         | X         | Powered Down |

|                    | 0         | X         | Powered Up   |

| 0                  | 4         | Low       | Powered Down |

|                    | l l       | High      | Powered Up   |

#### **POWERDOWN MODES**

The LMX2581 can be powered down either partially or fully. The partial powerdown powers down the PLL, VCO, and output buffer, but keeps the LDOs running. The full powerdown powers down everything, although register settings are still retained. The type of powerdown is governed by the PWDN\_MODE field and the CE pin in accordance to the following table.

| PWDN_MODE | CE Pin | Device State      |

|-----------|--------|-------------------|

| 0         | Х      | Powered Up        |

| 1         | Х      | Full Powerdown    |

| 3         | Х      | Partial Powerdown |

| 4         | Low    | Full Powerdown    |

| 4         | High   | Powered Up        |

| 0         | Low    | Partial Powerdown |

| 6         | High   | Powered Up        |

| 7         | Low    | Full Powerdown    |

| /         | High   | Partial Powerdown |

| 2,5       | Х      | Invalid State     |

When coming out of a full powerdown state, it is necessary to do the initial power on programming sequence described in later sections. If coming out of a partial powerdown state, it is necessary to do the sequence for switching frequencies after initialization, that is described in later sections.

#### **FASTLOCK**

The LMX2581 includes the Fastlock™ feature that can be used to improve the lock times. When the frequency is changed, a timeout counter is used to engage the fastlock for a programmable amount of time. During the time that the device is in Fastlock, the FLout pin changes from high impedance to low, thus switching in the external resistor R2pLF in parallel with R2\_LF.

| Parameter        | Normal Operation | Fastlock |

|------------------|------------------|----------|

| Charge Pump Gain | CPG              | FL_CPG   |

| FLout Pin        | High Impedance   | Grounded |

Once the loop filter values and charge pump gain are known for normal operation, they can be determined for fastlock operation as well. In normal operation, one can not use the highest charge pump gain and still use fastlock because there will be no larger current to switch in. The resistor and the charge pump current are changed simultaneously so that the phase margin remains the same while the loop bandwidth is by a factor of K as shown in the following table:

| Parameter                    | Symbol | Calculation                      |

|------------------------------|--------|----------------------------------|

| Charge Pump Gain in Fastlock | FL_CPG | Typically use the highest value. |

| Loop Bandwidth Multiplier    | К      | K=sqrt(FL_CPG/CPG)               |

| External Resistor            | R2pLF  | R2 / (K-1)                       |

#### **Lock Detect**

The LMX2581 offers two forms of lock detect, Vtune and Digital Lock Detect, which may be used separately or in conjunction. Digital Lock Detect gives a reliable indication of lock/unlock if programmed correctly with the one exception of when the PLL is locked to a valid OSCin signal and then the OSCin signal is abruptly removed. In this case, digital lock detect can sometimes still indicate a locked state, but Vtune Lock detect will correctly indicate an unlocked state. Therefore, for the most reliable lock detect, it is recommended to use these in conjunction, because they cover the deficits of each other. Note that because the powerdown mode powers down the lock detect circuitry, it is possible to get a high lock detect indication when the device is powered down.

#### Vtune Lock Detect

This style of lock detect only works with the internal VCO. Whenever the tuning voltage goes below the threshold of about 0.5 volts or above the threshold of about 2.2 volts, the internal VCO will become unlocked and the Vtune lock detect will indicate that the device is unlocked. For this reason, when the Vtune lock detect says the PLL is unlocked, one can be certain that it is unlocked.

#### Digital Lock Detect

This lock detect works by comparing the phase error as presented to the phase detector. If the phase error plus the delay as specified by the PFD\_DLY field outside the tolerance as specified by DLD\_TOL, then this comparison would be considered to be an error, otherwise passing. At higher phase detector frequencies, it may be necessary to adjust the DLD\_ERR\_CNT and DLD\_PASS\_CNT. The DLD\_ERR\_CNT specifies how may errors are necessary to cause the circuit to consider the PLL to be unlocked. The DLD\_PASS\_CNT multiplied by 8 specifies how many passing comparisons are necessary to cause the PLL to be considered to be locked and also resets the count for the errors. The DLD\_ERR\_CNT and DLD\_PASS\_CNT values may be decreased to make the circuit more sensitive, but if lock detect is made too sensitive chattering can occur and these values should be increased.

#### PART ID AND REGISTER READBACK

The LMX2581 allows any of its registers to be read back, which could be useful for the following applications below.

- Register Readback

- By reading back the register values, it can be confirmed that the correct information was written. In addition to this, Register R6 has special diagnostic information that could potentially be useful for debugging problems.

- Part ID Readback

- By reading back the part ID, this information may be used by whatever device is programming the LMX2581 to identify this device and know what programming information to send. In addition to this, the BUFEN and CE pins may be used to create 4 unique part ID values. Although these pins can impact the device, they may be overridden in software. It is not necessary to have the device programmed in order to do part ID readback.

The procedure for doing this readback is in the Serial Data Readback Timing section. Depending on the settings for the ID(R0[31]) and RDADDR (R6[8:5]), information a different bit stream will be returned as shown in the following table.

| ID | BUFEN Pin | CE Pin | Read Back Code                       |

|----|-----------|--------|--------------------------------------|

| 0  | X         | X      | Readback register defined by RDADDR. |

|    | 0         | 0      | 0x 00000500                          |

| 4  | 0         | 1      | 0x 00000510                          |

| 1  | 1         | 0      | 0x 00000520                          |

|    | 1         | 1      | 0x 00000530                          |

#### GENERAL PROGRAMMING INFORMATION

The LMX2581 is programmed using several 32-bit registers. A 32-bit shift register is used as a temporary register to indirectly program the on-chip registers. The shift register consists of a data field and an address field. The last 4 bits, ADDR[3:0] form the address field, which is used to decode the internal register address. The remaining 28 bits form the data field DATA[27:0]. While LE is low, serial data is clocked into the shift register upon the rising edge of clock (data is programmed MSB first). When LE goes high, data is transferred from the data field into the selected register bank.

### **Recommended Initial Power on Programming Sequence**

When the device is first powered up, the device needs to be initialized and the ordering of this programming is very important. The following is the sequence. After this sequence is complete, the device should be running and locked to the proper frequency.

- 1. Apply power to the device and ensure the Vcc pins are at the proper levels.

- 2. Ensure that a valid reference is applied to the OSCin pin

- 3. Program register R5 with RESET=1

- 4. Program registers R15,R13,R10,R9,R8,R7,R6,R5,R4,R3,R2,R1,R0

- 5. Wait 20 ms

- 6. Program the R0 register again OR do the recommended sequence for changing frequencies.

## **Recommended Sequence for Changing Frequencies**

After the device has gone through the initial power on programming sequence, it is not necessary to do this again. The recommended sequence for changing frequencies is as follows:

- 1. (optional) If the OUTx\_MUX State is changing, program Register R5

- (optional) If the VCO\_DIV state is changing, program Register R3. See section on VCO\_DIV if programming a to a value of 4.

- 3. (optional) If the MSB of the fractional numerator or charge pump gain is changing, program register R1

- 4. (Required) Program register R0

Although not necessary, it is also acceptable to program the R0 register a second time after this programming sequence.

### **Triggering Registers**

The action of programming certain registers may trigger special actions as shown in the table below.

| Reg | Conditions  | Actions Triggered                                                                                              | Why this is done                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R5  | RESET = 1   | All Registers are reset to power on default values. This takes less than 1 us. The reset bit is self-clearing. | The registers are reset by the power on reset circuitry when power is initially applied. The RESET bit allows the user the option to perform the same functionality of the power on reset through software.                                                                                                                                                                                                                         |

| R0  | NO_FCAL = 0 | —Starts the Frequency Calibration<br>—Engages Fastlock (If FL_TOC>0)                                           | This activates the frequency calibration, which chooses the correct VCO core and also the correct frequency band within that core. This is necessary whenever the frequency is changed. If it is desired that the R0 register be programmed without activating this calibration, then the NO_FCAL bit can be set to zero. If the fastlock timeout counter is programmed to a nonzero value, then this action also engages fastlock. |

| R0  | NO_FCAL = 1 | —Engages Fastlock (If FL_TOC>0)                                                                                | This engages fastlock, which may be used to decrease the lock time in some circumstances.                                                                                                                                                                                                                                                                                                                                           |

# Table 2. Register Map

|          |    |                 |                   |                 |     |    |                                                                                                                        |                  |               |            |              |                   |                 |       |         | _                    | , IVI                   | •                        |                  |                   |    |                |           |       |            |                |               |           |   |       |        |    |

|----------|----|-----------------|-------------------|-----------------|-----|----|------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------|--------------|-------------------|-----------------|-------|---------|----------------------|-------------------------|--------------------------|------------------|-------------------|----|----------------|-----------|-------|------------|----------------|---------------|-----------|---|-------|--------|----|

| Register | 31 | 30              | 29                | 28              | 27  | 26 | 25                                                                                                                     | 24               | 23            | 22         | 21           | 20                | 19              | 18    | 17      | 16                   | 15                      | 14                       | 13               | 12                | 11 | 10             | 9         | 8     | 7          | 6              | 5             | 4         | 3 | 2     | 1      | 0  |

|          |    |                 |                   |                 |     |    |                                                                                                                        |                  |               |            |              |                   |                 | DATA  | [27:0]  |                      |                         |                          |                  |                   |    |                |           |       |            |                |               |           |   | ADDRE | SS[3:0 | )] |

| R15      | 0  | 0               | 0                 | 0               | 0   | 0  | 1                                                                                                                      | 0                | 0             | 0          | 0            | 1                 | 1               | 1     | 1       | 1                    | 1                       | 1                        | 1                | VCO<br>CAP<br>MAN |    |                | VC        | O_CAP | CODE[7     | 7:0]           |               |           | 1 | 1     | 1      | 1  |

| R13      | DL | .D_ERF          | R_CNT             | [3:0]           |     |    | •                                                                                                                      | DLD              | _PASS         | S_CNT[     | 9:0]         | •                 |                 |       |         | DLD_<br>TOL<br>[2:0] |                         | 1                        | 0                | 0                 | 0  | 0              | 0         | 1     | 0          | 0              | 0             | 0         | 1 | 1     | 0      | 1  |

| R10      | 0  | 0               | 1                 | 0               | 0   | 0  | 0                                                                                                                      | 1                | 0             | 0          | 0            | 0                 | 0               | 0     | 0       | 0                    | 0                       | 1                        | 0                | 1                 | 0  | 0              | 0         | 0     | 1          | 1              | 0             | 0         | 1 | 0     | 1      | 0  |

| R9       | 0  | 0               | 0                 | 0               | 0   | 0  | 1                                                                                                                      | 1                | 1             | 1          | 0            | 0                 | 0               | 1     | 1       | 1                    | 1                       | 1                        | 0                | 0                 | 0  | 0              | 0         | 0     | 0          | 0              | 1             | 1         | 1 | 0     | 0      | 1  |

| R8       | 0  | 0               | 1                 | 0               | 0   | 0  | 0                                                                                                                      | 0                | 0             | 1          | 1            | 1                 | 1               | 1     | 0       | 1                    | 1                       | 1                        | 0                | 1                 | 1  | 0              | 1         | 1     | 1          | 1              | 1             | 1         | 1 | 0     | 0      | 0  |

| R7       | 0  |                 | F                 | L_SELE<br>[4:0] | CT  |    | FL.                                                                                                                    | _PINMO<br>[2:0]  | DE            | FL_<br>INV |              | MUXC              | OUT_SE<br>[4:0] | LECT  |         | MUX                  | N<br>F                  | IUXOUT<br>INMOD<br>[2:0] | Γ_<br>•E         |                   | LD | SELE(<br>[4:0] | СТ        |       | LD_<br>INV | PIN            | LD_<br>IMODE[ | [2:0]     | 0 | 1     | 1      | 1  |

| R6       | 0  |                 |                   |                 |     |    | RD_DIAGNOSTICS[19:0] 1                                                                                                 |                  |               |            | 1            | 0                 |                 | RDADE | DR[3:0] |                      | uWI<br>RE_<br>LOC<br>K  | 0                        | 1                | 1                 | 0  |                |           |       |            |                |               |           |   |       |        |    |

| R5       | 0  | 0               | 0                 | 0               | 0   | 0  | 0                                                                                                                      | OUT<br>_LD<br>EN | osc           | _FREC      | [2:0]        | BUF<br>EN_<br>DIS | 0               | 0     | 0       | MC                   | O_<br>EL_<br>DDE<br>:0] |                          | TB_<br>UX<br>:0] | OU<br>_M<br>[1:   | UX | 0_<br>DLY      | MO<br>[1: |       | PW         | DN_M(<br>[2:0] | DDE           | RES<br>ET | 0 | 1     | 0      | 1  |

| R4       | P  | PFD_DL<br>[2:0] | _Y                | FL_<br>FRC<br>E |     |    |                                                                                                                        |                  |               | FL_TO      | C[11:0]      |                   |                 |       |         |                      |                         | FL                       | _CPG[            | 4:0]              |    | 0              |           | C     | PG_BL      | EED[5:         | 0]            |           | 0 | 1     | 0      | 0  |

| R3       | 0  | 0               | 1                 | 0               | 0   | 0  | 0                                                                                                                      | 0                | 0             |            | VCO_DIV[4:0] |                   |                 |       |         |                      | Α                       | 0                        | 0                | 1                 | 1  |                |           |       |            |                |               |           |   |       |        |    |

| R2       | 0  | 0               | OSC<br>_2X        | 0               | СРР | 1  |                                                                                                                        |                  | PLL_DEN[21:0] |            |              |                   |                 |       | 0       | 0                    | 1                       | 0                        |                  |                   |    |                |           |       |            |                |               |           |   |       |        |    |

| R1       |    |                 | CPG[4:            | 0]              |     | S  | VCO_         FRAC_           SEL         PLL_NUM[21:12]         ORDER         PLL_R[7:0]           [1:0]         [2:0] |                  |               |            |              |                   |                 | 0     | 0       | 0                    | 1                       |                          |                  |                   |    |                |           |       |            |                |               |           |   |       |        |    |

| R0       | ID | DIT             | AC_<br>HER<br>:0] | NO_<br>FCA<br>L |     |    |                                                                                                                        |                  |               | PLL_N      | N[11:0]      |                   |                 |       |         |                      |                         |                          |                  |                   | -  | PLL_NU         | IM[11:0]  | ]     |            |                |               |           | 0 | 0     | 0      | 0  |

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

## **Programming Field Descriptions**

#### **REGISTER R15**

The programming of register R15 is not necessary and only needs to be done in situations where the programming fields in this register need to be changed. This is typically for diagnostic purposes or improving the digital VCO calibration time.

## VCO\_CAP\_MAN — Manual VCO Band Select

This bit determines if the value of VCO\_CAPCODE is just used as a starting point for the initial frequency calibration or if the VCO is forced to this value. If this is forced, it is only for diagnostic purposes.

| VCO_CAP_MAN | Impact of VCO_CAPCODE                     | Application                                                             |

|-------------|-------------------------------------------|-------------------------------------------------------------------------|

| 0           |                                           | Setting the VCO_CAPCODE field can improve the digital calibration time. |

| 1           | Forces the band for the VCO all the time. | For diagnostic purposes only.                                           |

## VCO\_CAPCODE[7:0] — Capacitor Value for VCO Band Selection

This field selects the capacitor value that is initially used for the VCO tank when the VCO calibration is run or that is forced when VCO\_CAP\_MAN is set to one. The lower values correspond to less capacitance, which corresponds to a higher VCO Frequency for that given VCO Core. If not using this feature, the default value for this field is 128.

| VCO_CAPCODE | VCO Tank Capacitance | VCO Frequency |

|-------------|----------------------|---------------|

| 0           | Minimum              | Highest       |

|             |                      |               |

| 255         | Maximum              | Lowest        |

#### **REGISTER R13**

Register R13 gives access to fields that are used for the digital lock detect circuitry.

#### DLD\_ERR\_CNT[3:0] - Digital Lock Detect Error Count

This is the amount of phase detector comparisons that may exceed the tolerance as specified in DLD\_TOL before digital lockindicates an unlocked state. The recommended default is 4 for phase detector frequencies of 80 MHz or below, but larger values may be necessary for higher phase detector frequencies.

## DLD\_PASS\_CNT[9:0] - Digital Lock Detect Success Count

This value multiplied by 8 is the amount of amount of phase detector comparisons within the tolerance specified by DLD\_TOL and adjusted by DLD\_ERR\_CNT that are necessary that are necessary to cause the digital lock to indicate a locked state. The recommended default value is 32 for phase detector frequencies of 80 MHz or below, but larger values may be necessary for higher phase detector frequencies.

#### DLD TOL[2:0] — Digital Lock Detect

This is the tolerance that is used to compare with each phase error to decide if it is a success or a fail. Larger settings are generally recommended, but they are limited by several factors such as PFD\_DLY, modulator order, and especially the phase detector frequency.

| DLD_TOL | Phase Error Tolerance (ns) | Typical Phase Detector Frequency            |

|---------|----------------------------|---------------------------------------------|

| 0       | 1                          | Fpd > 130 MHz                               |

| 1       | 1.7                        | 80 MHz < Fpd ≤ 130 MHz                      |

| 2       | 3                          | 60 MHz < Fpd ≤ 80 MHz                       |

| 3       | 6                          | 45 MHz < Fpd ≤ 60 MHz                       |

| 4       | 10                         | 30 MHz <fpd 45="" mhz<="" td="" ≤=""></fpd> |

| 5       | 18                         | Fpd ≤ 30 MHz                                |

| 6–7     | Reserved                   | n/a                                         |

## REGISTERS R10, R9, and R8

These registers have no functions that are disclosed to the user. However, it is still important to program them to the values specified in the register map because they are necessary for proper operation.

#### REGISTER R7

This register has fields that control status pins, which would be LD, MUXout, and FLout

## FL\_PINMODE[2:0], MUXOUT\_PINMODE[2:0], and LD\_PINMODE[2:0] — Output Format for Status Pins

These fields control the state of the output pin

| FL_PINMODE<br>MUXOUT_PINMODE<br>LD_PINMODE | Output Type                                         |

|--------------------------------------------|-----------------------------------------------------|

| 0                                          | TRI-STATE<br>(Default for LD_PINMODE)               |

| 1                                          | Push-Pull<br>(Default for MUXOUT_PINMODE)           |

| 2                                          | Open Drain                                          |

| 3                                          | High Drive Push-Pull<br>(Can drive 5 mA for an LED) |

| 4                                          | High Drive Open Drain                               |

| 5                                          | High Drive Open Source                              |

| 6,7                                        | Reserved                                            |

#### FL\_INV, MUX\_INV, LD\_INV - Inversion for Status Pins

The logic for the LD and MUXOUT pins can be inverted with these bits.

| FL_INV<br>MUX_INV<br>LD_INV | Pin Status       |

|-----------------------------|------------------|

| 0                           | Normal Operation |

| 1                           | Inverted         |

## FL\_SELECT[4:0], MUXOUT\_SELECT[4:0], LD\_SELECT[4:0] — State for Status Pins

This field controls the output state of the MUXout, LD, and FLout pins. Note that during fastlock, the FL\_SELECT field is ignored.

| FL_SELECT MUXOUT_SELECT LD_SELECT | Output                                                      |

|-----------------------------------|-------------------------------------------------------------|

| 0                                 | GND                                                         |

| 1                                 | Digital Lock Detect (Based on Phase Measurement)            |

| 2                                 | Vtune Lock Detect (Based on tuning voltage)                 |

| 3                                 | Lock Detect (Based on Phase Measurement AND tuning voltage) |

| 4                                 | Readback (Default for MUXOUT_SELECT)                        |

| 5                                 | PLL_N divided by 2                                          |

| 6                                 | PLL_N divided by 4                                          |

| 7                                 | PLL_R divided by 2                                          |

| 8                                 | PLL_R divided by 4                                          |

| 9                                 | Analog Lock Detect                                          |

| 10                                | OSCin Detect                                                |

| 11                                | Fin Detect                                                  |

| 12                                | Calibration Running                                         |

## www.ti.com

| FL_SELECT<br>MUXOUT_SELECT<br>LD_SELECT | Output                                                 |

|-----------------------------------------|--------------------------------------------------------|

| 13                                      | Tuning Voltage out of Range                            |

| 14                                      | VCO calibration fails in the low frequency direction.  |

| 15                                      | VCO Calibration fails in the high frequency direction. |

| 16-31                                   | Reserved                                               |

## RD\_DIAGNOSTICS[19:0] — Readback Diagnostics

This field is contains several pieces of information that may be read back for debug and diagnostic purposes.

|    |                |                    |                          |                    |               |                     | RD_D                  | IAGNOIS              | STICS[19     | 9:0]                 |                       |                  |            |                         |                         |                                |

|----|----------------|--------------------|--------------------------|--------------------|---------------|---------------------|-----------------------|----------------------|--------------|----------------------|-----------------------|------------------|------------|-------------------------|-------------------------|--------------------------------|

|    | ?6<br>:29]     | R6<br>[28]         | R6<br>[27]               | R6<br>[26]         | R6<br>[25:22] | R6<br>[21]          | R6<br>[20]            | R6<br>[19]           | R6<br>[18]   | R6<br>[17]           | R6<br>[16]            | R6<br>[15]       | R6<br>[14] | R6<br>[13]              | R6<br>[12]              | R6<br>[11]                     |

| 19 | 18             | 17                 | 16                       | 15                 | [14:11]       | 10                  | 9                     | 8                    | 7            | 6                    | 5                     | 4                | 3          | 2                       | 1                       | 0                              |

| S  | O_<br>EL<br>CT | FIN_<br>DET<br>ECT | OSCI<br>N_<br>DET<br>ECT | VCO_<br>DET<br>ECT | Reserved      | CAL_<br>RUNN<br>ING | VCO_<br>RAIL_<br>HIGH | VCO_<br>RAIL_<br>LOW | Reser<br>ved | VCO_<br>TUNE<br>HIGH | VCO_<br>TUNE<br>VALID | FLOU<br>T_<br>ON | DLD        | LD_<br>PIN<br>STAT<br>E | CE_<br>PIN<br>STAT<br>E | BUFE<br>N_<br>PIN<br>STAT<br>E |

| field Name     | Meaning if Value is One                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCO_ SELECT    | This is the VCO that the device chose to use. 0 = VCO 1, 1 = VCO 2, 2 = VCO 3, 3 = VCO 4                                                                                                                                                                                                |

| FIN_DETECT     | Indicates transitions at the Fin pin have been detected. This could either be the VCO signal or self-oscillation of the Fin pin in the even that no signal is present. This bit needs to be manually reset by programing register R5 with R5[30] = 1, and then again with bit R5[30]=0  |

| OSCIN_DETECT   | Indicates transitions at the OSCin pin have been detected. This could either be a signal at the OSCin pin or self-oscillation at the OSCin pin in the event no signal is present. This bit needs to be manually reset by programming R5 with R5[29] = 1 and then again with R5[29] = 0. |

| CAL_RUNNING    | Indicates that some calibration in the part is currently running.                                                                                                                                                                                                                       |

| VCO_RAIL_HIGH  | Indicates that the VCO frequency calibration failed because the VCO would need to be a higher frequency than it could achieve.                                                                                                                                                          |

| VCO_RAIL_LOW   | Indicates that the VCO frequency calibration failed because the VCO would need to be a lower frequency than it could achieve.                                                                                                                                                           |

| VCO_TUNE_HIGH  | Indicates that the VCO tuning voltage is higher than 2.4 volts and outside the allowable range.                                                                                                                                                                                         |

| VCO_TUNE_VALID | Indicates that the VCO tuning voltage is inside then allowable range.                                                                                                                                                                                                                   |

| FLOUT_ON       | Indicates that the FLout pin is low.                                                                                                                                                                                                                                                    |

| DLD            | Indicates that the digital lock detect phase measurement indicates a locked state. This does not include any consideration of the VCO tuning voltage.                                                                                                                                   |

| LD_PINSTATE    | This is the state of the LD Pin.                                                                                                                                                                                                                                                        |

| CE_PINSTATE    | This is the state of the CE pin.                                                                                                                                                                                                                                                        |

| BUFEN_PINSTATE | This is the state of the BUFEN pin.                                                                                                                                                                                                                                                     |

## RDADDR[3:0] — Readback Address

When the ID bit is set to zero, this designates which register is read back from. When the ID bit is set to one, the unique part ID information is read back.

| ID | RDADDR              | Information Read Back |

|----|---------------------|-----------------------|

| 1  | 1 Don't Care Part I |                       |

| 0  | 0                   | Register R0           |

|    | 1                   | Register R1           |

|    |                     |                       |

|    | 15 (default)        | Register R15          |

## uWIRE\_LOCK - Microwire lock

| uWIRE_LOCK | Microwire                                                            |  |

|------------|----------------------------------------------------------------------|--|

| 0          | Normal Operation                                                     |  |

| 1          | Locked out – All Programming except to the uWIRE_LOCK bit is ignored |  |

#### OUT\_LDEN — Mute Outputs Based on Lock Detect

When this bit is enabled, the RFoutA and RFoutB pins are disabled if the PLL digital lock detect circuitry indicates that the PLL is in the unlocked state.

| OUT_LDEN | PLL Digital Lock Detect Status | RFoutA / RFoutB Pins |

|----------|--------------------------------|----------------------|

| 0        | Don't Care                     | Normal Operation     |

| 1        | Locked                         | Normal Operation     |

| 1        | Unlocked                       | Powered Down         |

## OSC\_FREQ[2:0] — OSCin Frequency for VCO Calibration

This field should be set to in accordance to the OSCin frequency BEFORE the doubler. It is critical for running internal calibrations for this device.

| OSC_FREQ | OSCin Frequency                    |

|----------|------------------------------------|

| 0        | f <sub>OSCin</sub> < 128 MHz       |

| 1        | 128 ≤ f <sub>OSCin</sub> < 256 MHz |

| 2        | 256 ≤ f <sub>OSCin</sub> < 512 MHz |

| 3        | 512 ≤ f <sub>OSCin</sub>           |

| ≥ 4      | Reserved                           |

#### BUFEN\_DIS - Disable for the BUFEN Pin

This pin allows the BUFEN pin to be disabled. This is useful if one does not want to pull this pin high or use it for the readback ID.

| BUFEN_DIS | BUFEN Pin              |

|-----------|------------------------|

| 0         | Impacts Output buffers |

| 1         | Ignored.               |

#### VCO\_SEL\_MODE — Method of Selecting Internal VCO Core

This field allows the user to choose how the VCO selected by the VCO\_SEL field is treated. Note setting 0 should not be used if switching from a frequency above 3 GHz to a frequency below 2.2 GHz.

| VCO_SEL_MODE | VCO Selection                                                                                                                                                                              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|