LMS1487

SNOSA34F-OCTOBER 2002-REVISED APRIL 2013

#### www.ti.com

# LMS1487 5V Low Power RS-485 / RS-422 Differential Bus Transceiver

Check for Samples: LMS1487

#### **FEATURES**

- Meet ANSI Standard RS-485-A and RS-422-B

- Data Rate 2.5 Mbps

- Single Supply Voltage Operation, 5V

- Wide Input and Output Voltage Range

- Thermal Shutdown Protection

- Short Circuit Protection

- Low Quiescent Current 320µA

- Allows Up To 128 Transceivers on the Bus

- · Open Circuit Fail-Safe for Receiver

- Extended Operating Temperature Range -40°C to 85°C

- Drop-In Replacement to MAX1487

- Available in 8-Pin SOIC and 8-Pin PDIP Package

#### **APPLICATIONS**

- Low Power RS-485 Systems

- Network Hubs, Bridges, and Routers

- Point of Sales Equipment (ATM, Barcode Scanners,...)

- Local Area Networks (LAN)

- Integrated Service Digital Network (ISDN)

- Industrial Programmable Logic Controllers

- High Speed Parallel and Serial Applications

- Multipoint Applications with Noisy Environment

#### DESCRIPTION

The LMS1487 is a low power differential bus/line transceiver designed for high speed bidirectional data communication on multipoint bus transmission lines. It is designed for balanced transmission lines. It meets ANSI Standards TIA/EIA RS422-B, TIA/EIA RS485-A and ITU recommendation and V.11 and X.27. The LMS1487 combines a TRI-STATE differential line driver and differential input receiver, both of which operate from a single 5.0V power supply. The driver and receiver have an active high and active low, respectively, that can be externally connected to function as a direction control. The driver and receiver differential inputs are internally connected to form differential input/output (I/O) bus ports that are designed to offer minimum loading to bus whenever the driver is disabled or when V<sub>CC</sub> = 0V. These ports feature wide positive and negative common mode voltage ranges, making the device multipoint applications in suitable for environments. The LMS1487 is available in a 8-Pin SOIC and 8-pin PDIP packages. It is a drop-in socket replacement to Maxim's MAX1487

MA.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

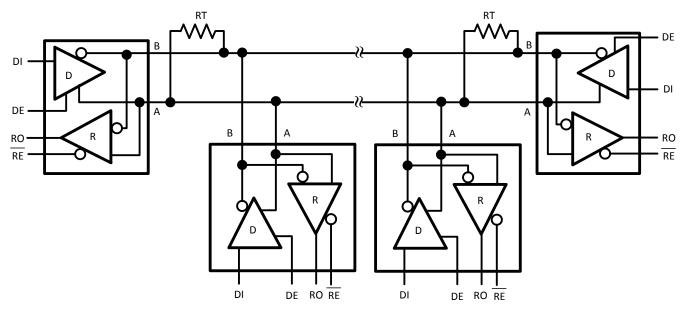

### **Typical Application**

A Typical multipoint application is shown in the above figure. Terminating resistors, RT, are typically required but only located at the two ends of the cable. Pull up and pull down resistors maybe required at the end of the bus to provide fail-safe biasing. The biasing resistors provide a bias to the cable when all drivers are in TRI-STATE, See TI Application Note, AN-847 for further information.

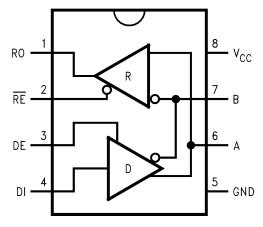

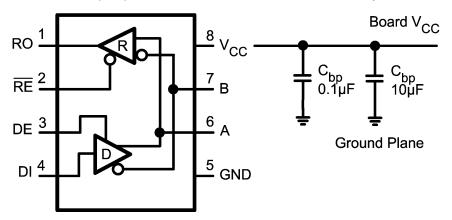

## **Connection Diagram**

Figure 1. 8-Pin SOIC / PDIP Top View

Submit Documentation Feedback

### SNOSA34F - OCTOBER 2002 - REVISED APRIL 2013

### **TRUTH TABLE**

| DRIVER SECTION   |    |           |   |    |  |

|------------------|----|-----------|---|----|--|

| RE               | DE | DI        | Α | В  |  |

| X                | Н  | Н         | Н | L  |  |

| X                | Н  | L         | L | Н  |  |

| X                | L  | X         | Z | Z  |  |

| RECEIVER SECTION |    |           |   |    |  |

| RE               | DE | A-B       |   | RO |  |

| L                | L  | ≥ +0.2V   |   | Н  |  |

| L                | L  | ≤ -0.2V   |   | L  |  |

| Н                | Χ  | X         |   | Z  |  |

| L                | L  | OPEN *(1) |   | Н  |  |

(1) Non Terminated, Open Input only X = Irrelevant Z = TRI-STATE H = High level L = Low level

### **Table 1. PIN DESCRIPTIONS**

| Pin # | I/O | Name            | Function                                                                                                                                                                                |

|-------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 0   | RO              | Receiver Output: If A > B by 200 mV, RO will be high; If A < B by 200mV, RO will be low. RO will be high also if the inputs (A and B) are open (non-terminated                          |

| 2     | I   | RE              | Receiver Output Enable: RO is enabled when RE is low; RO is in TRI-STATE when RE is high                                                                                                |

| 3     | I   | DE              | Driver Output Enable: The driver outputs (A and B) are enabled when DE is high; they are in TRI-STATE when DE is low. Pins A and B also function as the receiver input pins (see below) |

| 4     | I   | DI              | Driver Input: A low on DI forces A low and B high while a high on DI forces A high and B low when the driver is enabled                                                                 |

| 5     | N/A | GND             | Ground                                                                                                                                                                                  |

| 6     | I/O | Α               | Non-inverting Driver Output and Receiver Input pin. Driver Output levels conform to RS-485 signaling levels                                                                             |

| 7     | I/O | В               | Inverting Driver Output and Receiver Input pin. Driver Output levels conform to RS-485 signaling levels                                                                                 |

| 8     | N/A | V <sub>CC</sub> | Power Supply: $4.75V \le V_{CC} \le 5.25V$                                                                                                                                              |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS(1)(2)

| ABOOLOTE MAXIMOM RATINGS                                            |                                  |                            |  |

|---------------------------------------------------------------------|----------------------------------|----------------------------|--|

| Supply Voltage, V <sub>CC</sub> <sup>(3)</sup>                      |                                  | 7V                         |  |

| Input Voltage, V <sub>IN</sub> (DI, DE, or $\overline{\text{RE}}$ ) |                                  | $-0.3V$ to $V_{CC} + 0.3V$ |  |

| Voltage Range at Any Bus Terminal (AB)                              |                                  | -7V to 12V                 |  |

| Receiver Outputs                                                    | $-0.3V$ to $V_{CC} + 0.3V$       |                            |  |

| Package Thermal Impedance, θ <sub>JA</sub>                          | SOIC                             | 125°C/W                    |  |

|                                                                     | PDIP                             | 88°C/W                     |  |

| Junction Temperature <sup>(4)</sup>                                 | 150°C                            |                            |  |

| Operating Free-Air Temperature Range, T <sub>A</sub>                | Commercial                       | 0°C to 70°C                |  |

|                                                                     | Industrial                       | -40°C to 85°C              |  |

| Storage Temperature Range                                           |                                  | −65°C to 150°C             |  |

| Soldering Information                                               | Infrared or Convection (20 sec.) | 235°C                      |  |

|                                                                     | Lead Temperature                 | 260°C                      |  |

| ESD Rating <sup>(5)</sup>                                           |                                  | 7kV                        |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the ELECTRICAL CHARACTERISTICS.

- If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- All voltage values, except differential I/O bus voltage, are with respect to network ground terminal.

- The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly into a PC board. ESD rating based upon human body model, 100pF discharged through 1.5k $\Omega$ .

#### **OPERATING RATINGS**

|                                                            |                           | Min  | Nom | Max  |    |

|------------------------------------------------------------|---------------------------|------|-----|------|----|

| Supply Voltage, V <sub>CC</sub>                            |                           | 4.75 | 5.0 | 5.25 | V  |

| Voltage at any Bus Terminal (Separately or Common Mode)    |                           | -7   |     | 12   | V  |

| V <sub>IN</sub> or V <sub>IC</sub>                         |                           |      |     |      |    |

| High-Level Input Voltage, V <sub>IH</sub> <sup>(1)</sup>   |                           | 2    |     |      | V  |

| Low-Level Input Voltage, V <sub>IL</sub> <sup>(1)</sup>    |                           |      |     | 0.8  | V  |

| Differential Input Voltage, V <sub>ID</sub> <sup>(2)</sup> |                           |      |     | ±12  | V  |

| High-Level Output                                          | Driver, I <sub>OH</sub>   |      |     | -150 | mA |

|                                                            | Receiver, I <sub>OH</sub> |      |     | -42  | mA |

| Low-Level Output                                           | Driver, I <sub>OL</sub>   |      |     | 80   | mA |

|                                                            | Receiver, I <sub>OL</sub> |      |     | 26   | mA |

Voltage limits apply to DI, DE, RE pins.

Differential input/output bus voltage is measured at the non-inverting terminal A with respect to the inverting terminal B.

SNOSA34F - OCTOBER 2002 - REVISED APRIL 2013

#### **ELECTRICAL CHARACTERISTICS**

Over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| Symbol            | Parameter                                                                                         | Conditions                                                      | Min  | Тур | Max  | Units |

|-------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------|-----|------|-------|

| Driver Sec        | tion                                                                                              |                                                                 | ·    |     |      |       |

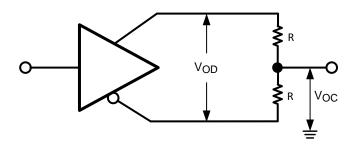

| V <sub>OD1</sub>  | Differential Output Voltage                                                                       | R = ∞ (See Figure 11)                                           |      |     | 5.25 | V     |

| V <sub>OD2</sub>  | Differential Output Voltage                                                                       | $R = 50\Omega$ (See Figure 11),RS-422                           | 2.0  |     |      | V     |

|                   |                                                                                                   | $R = 27\Omega$ (See Figure 11),RS-485                           | 1.5  |     | 5.0  |       |

| ΔV <sub>OD</sub>  | Change in Magnitude of Driver<br>Differential Output Voltage for<br>Complementary Output States   | R = $27\Omega$ or $50\Omega$ (See Figure 11) <sup>(1)</sup>     |      |     | 0.2  | V     |

| V <sub>OC</sub>   | Common-Mode Output Voltage                                                                        | R = 27Ω or $50Ω$ (See Figure 11)                                |      |     | 3.0  | V     |

| ΔV <sub>OC</sub>  | Change in Magnitude of Driver<br>Common-Mode Output Voltage<br>for Complementary Output<br>States | R = $27\Omega$ or $50\Omega$ (See Figure 11) <sup>(1)</sup>     |      |     | 0.2  | V     |

| V <sub>IH</sub>   | CMOS Inout Logic Threshold<br>High                                                                | DE, DI, RE                                                      | 2.0  |     |      | V     |

| V <sub>IL</sub>   | CMOS Input Logic Threshold Low                                                                    | DE, DI, RE                                                      |      |     | 0.8  | V     |

| I <sub>IN1</sub>  | Logic Input Current                                                                               | DE, DI, RE                                                      |      |     | ±2   | μΑ    |

| Receiver S        | Section                                                                                           |                                                                 | ·    |     |      |       |

| I <sub>IN2</sub>  | Input Current (A, B)                                                                              | DE = 0V, V <sub>CC</sub> = 0V or 5.25V<br>V <sub>IN</sub> = 12V |      |     | 0.25 | mA    |

|                   |                                                                                                   | $V_{IN} = -7V$                                                  |      |     | -0.2 |       |

| $V_{TH}$          | Differential Input Threshold Voltage                                                              | -7V ≤ V <sub>CM</sub> ≤ + 12V                                   | -0.2 |     | +0.2 | V     |

| $\Delta V_{TH}$   | Input Hysteresis Voltage (V <sub>TH+</sub> - V <sub>TH-</sub> )                                   | V <sub>CM</sub> = 0                                             |      | 95  |      | mV    |

| V <sub>OH</sub>   | CMOS High-level Output<br>Voltage                                                                 | $I_{OH} = -4mA$ , $V_{ID} = 200mV$                              | 3.5  |     |      | V     |

| V <sub>OL</sub>   | CMOS Low-level                                                                                    | $I_{OL} = 4mA$ , $V_{ID} = -200mV$                              |      |     | 0.40 | V     |

| I <sub>OZR</sub>  | Tristate Output Leakage<br>Current                                                                | $0.4V \le V_0 \le +2.4V$                                        |      |     | ±1   | μΑ    |

| R <sub>IN</sub>   | Input Resistance                                                                                  | - 7V ≤ V <sub>CM</sub> ≤+12V                                    | 48   |     |      | kΩ    |

| Power Sup         | pply Current                                                                                      |                                                                 |      |     |      |       |

| Icc               | Supply Current                                                                                    | $DE = V_{CC}$ , $\overline{RE} = GND$ or $V_{CC}$               |      | 320 | 500  | μΑ    |

|                   |                                                                                                   | DE = 0V, $\overline{RE}$ = GND or V <sub>CC</sub>               |      | 315 | 400  |       |

| I <sub>OSD1</sub> | Driver Short-circuit Output<br>Current                                                            | $V_{O} = high, -7V \le V_{CM} \le + 12V^{(2)}$                  | 35   |     | 250  | mA    |

| I <sub>OSD2</sub> | Driver Short-circuit Output<br>Current                                                            | $V_{O} = low, -7V \le V_{CM} \le +12V^{(2)}$                    | 35   |     | 250  | mA    |

| I <sub>OSR</sub>  | Receiver Short-circuit Output<br>Current                                                          | 0 V ≤V <sub>O</sub> ≤ V <sub>CC</sub>                           | 7    |     | 95   | mA    |

$<sup>|\</sup>Delta V_{OD}|$  and  $|\Delta V_{OC}|$  are changes in magnitude of  $V_{OD}$  and  $V_{OC}$ , respectively when the input changes from high to low levels. Peak current

SNOSA34F-OCTOBER 2002-REVISED APRIL 2013

# **ELECTRICAL CHARACTERISTICS (continued)**

Over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| Symbol                                 | Parameter                            | Conditions                                                                      | Min | Тур | Max | Units |

|----------------------------------------|--------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|-------|

| Switching                              | Characteristics                      |                                                                                 | ·   |     |     |       |

| Driver                                 |                                      |                                                                                 |     |     |     |       |

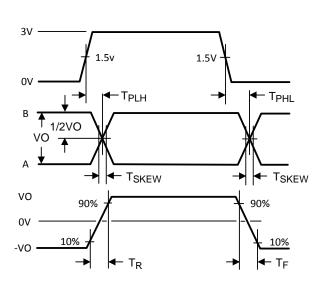

| T <sub>PLH</sub> ,<br>T <sub>PHL</sub> | Propagation Delay Input to<br>Output | $R_L = 54\Omega$ , $C_L = 100pF$<br>(See Figure 13 and Figure 17)               | 10  | 35  | 60  | nS    |

| T <sub>SKEW</sub>                      | Driver Output Skew                   | $R_L = 54\Omega$ , $C_L = 100 pF$<br>(See Figure 13 and Figure 17)              |     | 5   | 10  | nS    |

| T <sub>R</sub> ,                       | Driver Rise and Fall Time            | $R_L = 54\Omega$ , $C_L = 100 pF$<br>(See Figure 13 and Figure 17)              | 3   | 8   | 40  | nS    |

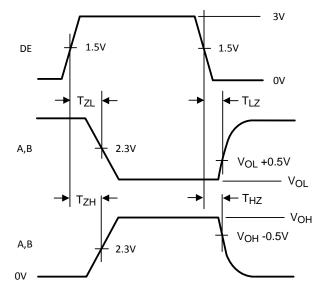

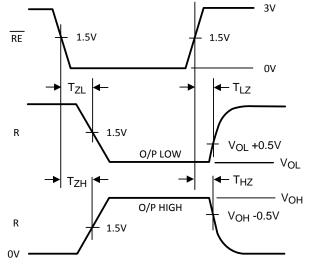

| T <sub>ZH</sub> ,<br>T <sub>ZL</sub>   | Driver Enable to Ouput Valid Time    | $C_L = 100 \text{ pF}, R_L = 500\Omega$<br>(See Figure 14and Figure 18)         |     | 25  | 70  | nS    |

| T <sub>HZ</sub> ,<br>T <sub>LZ</sub>   | Driver Output Disable Time           | $C_L = 15 \text{ pF}, R_L = 500\Omega$<br>(See Figure 14 and Figure 18)         |     | 30  | 70  | nS    |

| Receiver                               |                                      |                                                                                 |     |     |     |       |

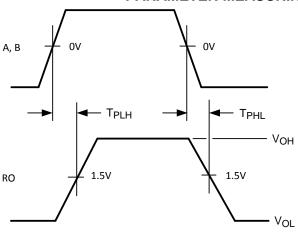

| T <sub>PLH</sub> ,<br>T <sub>PHL</sub> | Propagation Delay Input to Output    | $R_L = 54\Omega$ , $C_L = 100 \text{ pF}$<br>(See Figure 15 and Figure 17)      | 20  | 50  | 200 | nS    |

| T <sub>SKEW</sub>                      | Receiver Output Skew                 | $R_L = 54\Omega$ , $C_L = 100 pF$<br>(See Figure 15 and Figure 17)              |     | 5   |     | nS    |

| T <sub>ZH</sub> ,<br>T <sub>ZL</sub>   | Receiver Enable Time                 | $C_L = 15 \text{ pF}, R_L = 1 \text{ k}\Omega$<br>(See Figure 16 and Figure 20) |     | 20  | 50  | nS    |

|                                        | Receiver Disable Time                |                                                                                 |     | 20  | 50  | nS    |

| F <sub>MAX</sub>                       | Maximum Data Rate                    |                                                                                 | 2.5 |     |     | Mbps  |

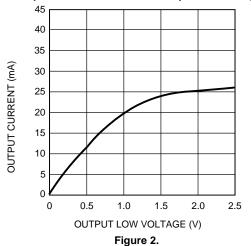

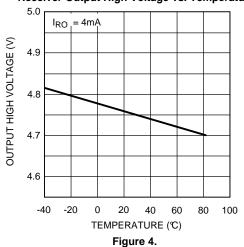

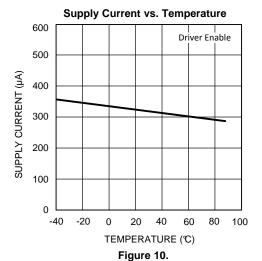

#### TYPICAL PERFORMANCE CHARACTERISTICS

#### **Output Current vs. Receiver Output Low Voltage**

. iguio zi

#### Receiver Output High Voltage vs. Temperature

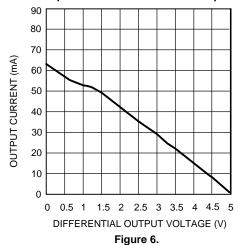

**Driver Output Current vs. Differential Output Voltage**

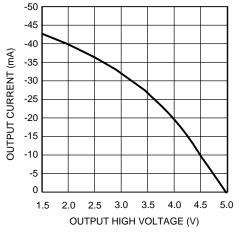

#### **Output Current vs. Receiver Output High Voltage**

Figure 3.

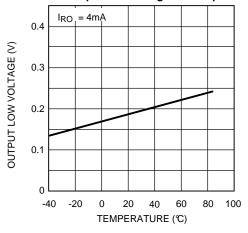

#### Receiver Output Low-Voltage vs. Temperature

Figure 5.

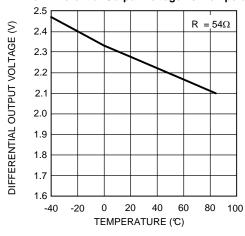

#### **Driver Differential Output Voltage vs. Temperature**

Figure 7.

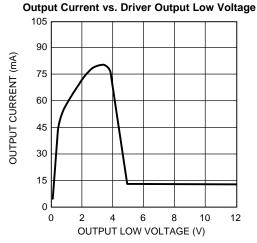

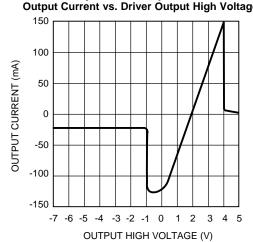

# TYPICAL PERFORMANCE CHARACTERISTICS (continued) ent vs. Driver Output Low Voltage Output Current vs. Driver Output High Voltage

Figure 8.

Figure 9.

#### SNOSA34F - OCTOBER 2002 - REVISED APRIL 2013

#### PARAMETER MEASURING INFORMATION

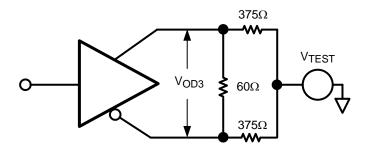

Figure 11. Test Circuit for  $\rm V_{\rm OD}$  and  $\rm V_{\rm OC}$

Figure 12. Test Circuit for  $V_{\text{OD3}}$

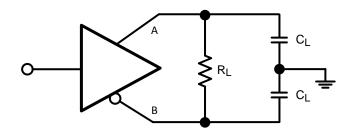

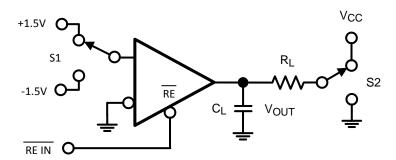

Figure 13. Test Circuit for Driver Propagation Delay

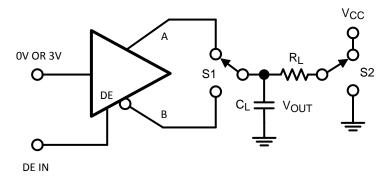

Figure 14. Test Circuit for Driver Enable / Disable

## PARAMETER MEASURING INFORMATION (continued)

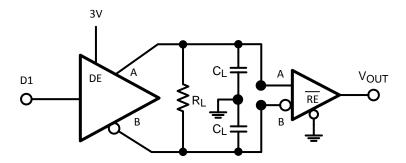

Figure 15. Test Circuit for Receiver Propagation Delay

Figure 16. Test Circuit for Receiver Enable / Disable

## **Switching Characteristics**

Figure 17. Driver Propagation Delay, Rise / Fall

Figure 18. Driver Enable / Disable Time

## **PARAMETER MEASURING INFORMATION (continued)**

Figure 19. Receiver Propagation Delay

Figure 20. Receiver Enable / Disable Time

Copyright © 2002–2013, Texas Instruments Incorporated

Submit Documentation Feedback

#### APPLICATION INFORMATION

#### **Power Line Noise Filtering**

A factor to consider in designing power and ground is noise filtering. A noise filtering circuit is designed to prevent noise generated by the integrated circuit (IC) as well as noise entering the IC from other devices. A common filtering method is to place by-pass capacitors (C<sub>hp</sub>) between the power and ground lines.

Placing a by-pass capacitor ( $C_{bp}$ ) with the correct value at the proper location solves many power supply noise problems. Choosing the correct capacitor value is based upon the desired noise filtering range. Since capacitors are not ideal, they may act more like inductors or resistors over a specific frequency range. Thus, many times two by-pass capacitors may be used to filter a wider bandwidth of noise. It is highly recommended to place a larger capacitor, such as  $10\mu\text{F}$ , between the power supply pin and ground to filter out low frequencies and a  $0.1\mu\text{F}$  to filter out high frequencies.

By-pass capacitors must be mounted as close as possible to the IC to be effective. Longs leads produce higher impedance at higher frequencies due to stray inductance. Thus, this will reduce the by-pass capacitor's effectiveness. Surface mounted chip capacitors are the best solution because they have lower inductance.

Figure 21. Placement of by-pass Capacitors, C<sub>bp</sub>

LMS148

www.ti.com

SNOSA34F - OCTOBER 2002 - REVISED APRIL 2013

## **REVISION HISTORY**

| Cł | Changes from Revision E (April 2013) to Revision F |   |   |  |

|----|----------------------------------------------------|---|---|--|

| •  | Changed layout of National Data Sheet to TI format | 1 | 2 |  |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>