# LMH6559 High-Speed, Closed-Loop Buffer

Check for Samples: LMH6559

#### **FEATURES**

- **Closed-Loop Buffer**

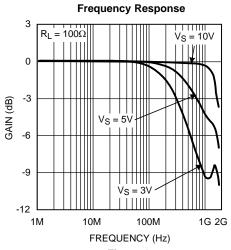

- 1750MHz Small Signal Bandwidth

- 4580V/µs Slew Rate

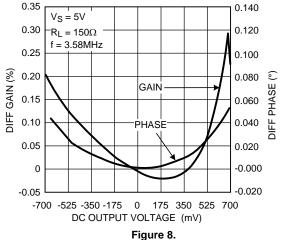

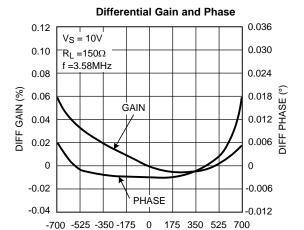

- 0.06% / 0.02° Differential Gain/Phase

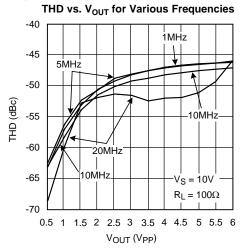

- -52dBc THD at 20MHz

- Single Supply Operation (3V Min.)

- 75mA Output Current

#### **APPLICATIONS**

- Video Switching and Routing

- **Test Point Drivers**

- **High Frequency Active Filters**

- Wideband DC Clamping Buffers

- **High-Speed Peak Detector Circuits**

- **Transmission Systems**

- **Telecommunications**

- Test Equipment and Instrumentation

## DESCRIPTION

The LMH6559 is a high-speed, closed-loop buffer designed for applications requiring the processing of very high frequency signals. While offering a small signal bandwidth of 1750MHz, and an ultra high slew rate of 4580V/µs the LMH6559 consumes only 10mA of quiescent current. Total harmonic distortion into a load of  $100\Omega$  at 20MHz is -52dBc. The LMH6559 is configured internally for a loop gain of one. Input resistance is  $200k\Omega$  and output resistance is but 1.2Ω. These characteristics make the LMH6559 an ideal choice for the distribution of high frequency signals on printed circuit boards. Differential gain and phase specifications of 0.06% and 0.02° respectively at 3.58MHz make the LMH6559 well suited for the buffering of video signals.

The device is fabricated on Texas Instruments' highspeed VIP10 process using TI's proven high performance circuit architectures.

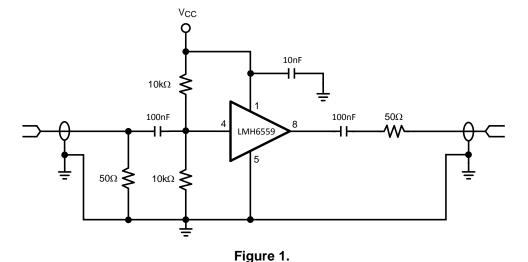

## **Typical Schematic**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

## Absolute Maximum Ratings (1)(2)

| ESD Tolerance <sup>(3)</sup>                      | Human Body Model                 | 2000V                                                  |

|---------------------------------------------------|----------------------------------|--------------------------------------------------------|

|                                                   | Machine Model                    | 200V                                                   |

| Output Short Circuit Duration                     | •                                | See <sup>(4)</sup> , <sup>(5)</sup> and <sup>(6)</sup> |

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) |                                  | 13V                                                    |

| Voltage at Input/Output Pins                      |                                  | V <sup>+</sup> +0.8V, V <sup>−</sup> −0.8V             |

| Soldering Information                             | Infrared or Convection (20 sec.) | 235°C                                                  |

|                                                   | Wave Soldering (10 sec.)         | 260°C                                                  |

| Storage Temperature Range                         | ·                                | −65°C to +150°C                                        |

| Junction Temperature                              |                                  | +150°C                                                 |

- (1) Absolute Maximum Ratings are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

- If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

- Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

- Short circuit test is a momentary test.

- The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

## Operating Ratings<sup>(1)</sup>

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) | 3 - 10V        |         |

|---------------------------------------------------|----------------|---------|

| Temperature Range <sup>(2)(3)</sup>               | -40°C to +85°C |         |

| Package Thermal Resistance (2)(3)                 | 8-Pin SOIC     | 172°C/W |

|                                                   | 5-Pin SOT-23   | 235°C/W |

- (1) Absolute Maximum Ratings are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

- The maximum power dissipation is a function of T<sub>J(MAX)</sub>,  $\theta_{JA}$ , and T<sub>A</sub>. The maximum allowable power dissipation at any ambient

- temperature is  $P_D = (T_{J(MAX)} T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board. Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . There is no specification of parametric performance as indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>. See Applications section for information on temperature de-rating of this device.

#### ±5V Electrical Characteristics

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $V^- = -5V$ ,  $V_O = V_{CM} = 0V$  and  $R_L = 100\Omega$  to 0V. **Boldface** limits apply at the temperature extremes.

| Symbol                    | Parameter                           | Parameter Conditions Min                            |     | Typ (2) | Max<br>(1) | Units  |

|---------------------------|-------------------------------------|-----------------------------------------------------|-----|---------|------------|--------|

| Frequenc                  | y Domain Response                   |                                                     |     | I.      |            |        |

| SSBW                      | Small Signal Bandwidth              | $V_O < 0.5V_{PP}$                                   |     | 1750    |            | MHz    |

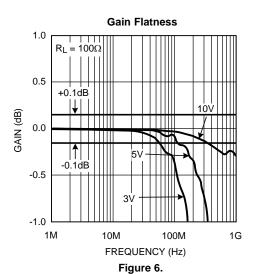

| GFN                       | Gain Flatness < 0.1dB               | V <sub>O</sub> < 0.5V <sub>PP</sub>                 |     | 200     |            | MHz    |

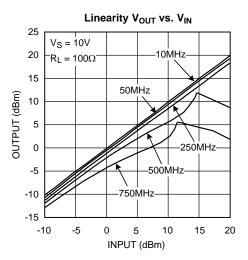

| FPBW                      | Full Power Bandwidth (-3dB)         | $V_O = 2V_{PP} (+10dBm)$                            |     | 1050    |            | MHZ    |

| DG                        | Differential Gain                   | $R_L = 150\Omega$ to 0V,<br>f = 3.58 MHz            |     | 0.06    |            | %      |

| DP                        | Differential Phase                  | $R_L = 150\Omega$ to 0V,<br>f = 3.58 MHz            |     | 0.02    |            | deg    |

| Time Don                  | ain Response                        |                                                     |     |         |            |        |

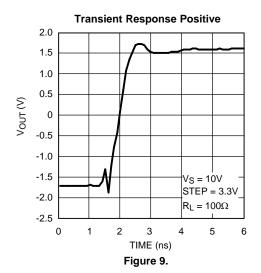

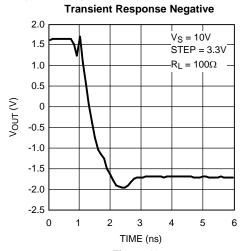

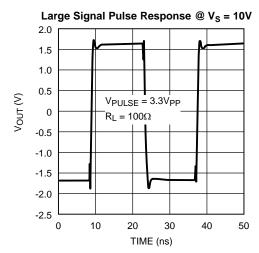

| t <sub>r</sub>            | Rise Time                           | 3.3V Step (20-80%)                                  |     | 0.4     |            | ns     |

| t <sub>f</sub>            | Fall Time                           |                                                     |     | 0.5     |            | ns     |

| t <sub>s</sub>            | Settling Time to ±0.1%              | 3.3V Step                                           |     | 9       |            | ns     |

| os                        | Overshoot                           | 1V Step                                             |     | 4       |            | %      |

| SR                        | Slew Rate                           | See <sup>(3)</sup>                                  |     | 4580    |            | V/µs   |

| Distortion                | And Noise Performance               |                                                     |     |         |            |        |

| HD2                       | 2 <sup>nd</sup> Harmonic Distortion | $V_O = 2V_{PP}$ , $f = 20MHz$                       |     | -58     |            | dBc    |

| HD3                       | 3 <sup>rd</sup> Harmonic Distortion | $V_O = 2V_{PP}$ , $f = 20MHz$                       |     | -53     |            | dBc    |

| THD                       | Total Harmonic Distortion           | $V_O = 2V_{PP}$ , $f = 20MHz$                       |     |         |            | dBc    |

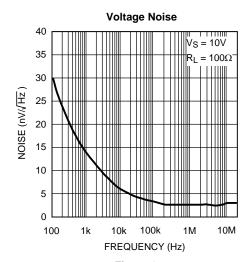

| e <sub>n</sub>            | Input-Referred Voltage Noise        | f = 1MHz                                            |     | 5.7     |            | nV/√Hz |

| СР                        | 1dB Compression point               | f = 10MHz                                           | +23 |         |            | dBm    |

| SNR Signal to Noise Ratio |                                     | f > 100kHz, BW = 5MHz,<br>V <sub>O</sub> = 350mVrms |     |         |            | dB     |

All limits are specified by testing or statistical analysis.

Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

(3) Slew rate is the average of the positive and negative slew rate.

## ±5V Electrical Characteristics (continued)

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $V^- = -5V$ ,  $V_O = V_{CM} = 0V$  and  $R_L = 100\Omega$  to 0V. **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                                     | Conditions                                                    | <b>Min</b><br>(1)   | Typ   | Max<br>(1)            | Units |

|--------------------|-----------------------------------------------|---------------------------------------------------------------|---------------------|-------|-----------------------|-------|

| Static, DC         | Performance                                   |                                                               |                     | 1     | I.                    |       |

| A <sub>CL</sub>    | Small Signal Voltage Gain                     | $V_O = 100 \text{mV}_{PP}$<br>$R_L = 100\Omega \text{ to 0V}$ | .97                 | .996  |                       | V/V   |

|                    |                                               | $V_O = 100 \text{mV}_{PP}$<br>$R_L = 2 \text{k} \Omega$ to 0V | .99                 | .998  |                       | V/V   |

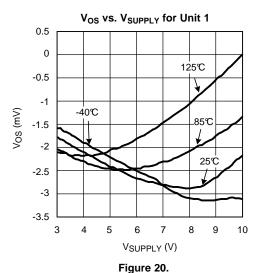

| V <sub>OS</sub>    | Input Offset Voltage                          |                                                               |                     | 3     | 20<br><b>25</b>       | mV    |

| TC V <sub>OS</sub> | Temperature Coefficient Input Offset Voltage  | See <sup>(4)</sup>                                            |                     | 23    |                       | μV/°C |

| I <sub>B</sub>     | Input Bias Current                            | See <sup>(5)</sup>                                            | -10<br><b>-14</b>   | -3    |                       | μA    |

| TC I <sub>B</sub>  | Temperature Coefficient Input Bias<br>Current | See <sup>(4)</sup>                                            |                     | -3.6  |                       | nA/°C |

| R <sub>OUT</sub>   | Output Resistance                             | $R_L = 100\Omega$ to 0V, $f = 100$ kHz                        |                     | 1.2   |                       | 0     |

|                    |                                               | $R_L = 100\Omega$ to 0V, $f = 10MHz$                          |                     | 1.3   |                       | Ω     |

| PSRR               | Power Supply Rejection Ratio                  | $V_S = \pm 5V$ to $V_S = \pm 5.25V$                           | 48<br><b>44</b>     | 63    |                       | dB    |

| I <sub>S</sub>     | Supply Current                                | No Load                                                       |                     | 10    | 14<br><b>17</b>       | mA    |

| Miscellane         | eous Performance                              |                                                               | 1                   | 1     |                       | '     |

| R <sub>IN</sub>    | Input Resistance                              |                                                               |                     | 200   |                       | kΩ    |

| C <sub>IN</sub>    | Input Capacitance                             |                                                               |                     | 1.7   |                       | pF    |

| Vo                 | Output Swing Positive                         | $R_L = 100\Omega$ to 0V                                       | 3.20<br><b>3.18</b> | 3.45  |                       | V     |

|                    |                                               | $R_L = 2k\Omega$ to 0V                                        | 3.55<br><b>3.54</b> | 3.65  |                       | V     |

|                    | Output Swing Negative                         | $R_L = 100\Omega$ to 0V                                       |                     | -3.45 | -3.20<br><b>-3.18</b> | V     |

|                    |                                               | $R_L = 2k\Omega$ to 0V                                        |                     | -3.65 | -3.55<br><b>-3.54</b> | V     |

| I <sub>SC</sub>    | Output Short Circuit Current                  | Sourcing: $V_{IN} = +V_S$ , $V_O = 0V$                        |                     | -83   |                       | m ^   |

|                    |                                               | Sinking: $V_{IN} = -V_S$ , $V_O = 0V$                         |                     | 83    |                       | mA    |

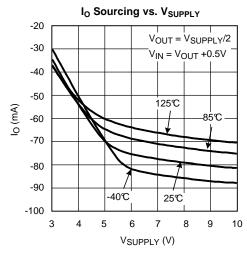

| I <sub>O</sub>     | Linear Output Current                         | Sourcing: $V_{IN} - V_O = 0.5V^{(5)}$                         | -50<br><b>-43</b>   | -74   |                       | m 1   |

|                    |                                               | Sinking: $V_{IN} - V_{O} = -0.5V^{(5)}$                       | 50<br><b>43</b>     | 74    |                       | mA    |

<sup>(4)</sup> Average Temperature Coefficient is determined by dividing the change in a parameter at temperature extremes by the total temperature change.

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

<sup>(5)</sup> Positive current corresponds to current flowing into the device.

#### **5V Electrical Characteristics**

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_O = V_{CM} = V^+/2$  and  $R_L = 100\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                                     | Conditions                                                                   | <b>Min</b><br>(1) | Typ  | Max<br>(1)      | Units  |

|--------------------|-----------------------------------------------|------------------------------------------------------------------------------|-------------------|------|-----------------|--------|

| Frequency          | Domain Response                               |                                                                              |                   |      |                 |        |

| SSBW               | Small Signal Bandwidth                        | $V_O < 0.5V_{PP}$                                                            |                   | 745  |                 | MHz    |

| GFN                | Gain Flatness < 0.1dB                         | $V_O < 0.5V_{PP}$                                                            |                   | 90   |                 | MHz    |

| FPBW               | Full Power Bandwidth (-3dB)                   | $V_O = 2V_{PP} (+10dBm)$                                                     |                   | 485  |                 | MHZ    |

| DG                 | Differential Gain                             | $R_L = 150\Omega \text{ to V}^+/2,$<br>f = 3.58 MHz                          |                   | 0.29 |                 | %      |

| DP                 | Differential Phase                            | $R_L = 150\Omega \text{ to V}^+/2,$<br>f = 3.58 MHz                          |                   | 0.06 |                 | deg    |

| Time Dom           | ain Response                                  |                                                                              |                   |      |                 |        |

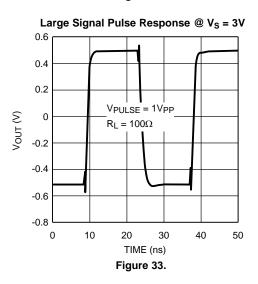

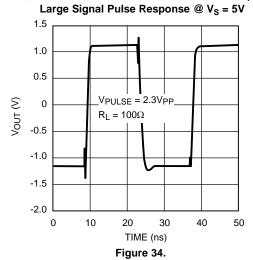

| t <sub>r</sub>     | Rise Time                                     | 2.3V <sub>PP</sub> Step (20-80%)                                             |                   | 0.6  |                 | ns     |

| t <sub>f</sub>     | Fall Time                                     |                                                                              |                   | 0.9  |                 | ns     |

| t <sub>s</sub>     | Settling Time to ±0.1%                        | 2.3V Step                                                                    |                   | 9.6  |                 | ns     |

| OS                 | Overshoot                                     | 1V Step                                                                      |                   | 3    |                 | %      |

| SR                 | Slew Rate                                     | See <sup>(3)</sup>                                                           |                   | 2070 |                 | V/µs   |

| Distortion         | And Noise Performance                         | 1                                                                            |                   |      |                 | -      |

| HD2                | 2 <sup>nd</sup> Harmonic Distortion           | $V_O = 2V_{PP}$ , $f = 20MHz$                                                |                   | -53  |                 | dBc    |

| HD3                | 3 <sup>rd</sup> Harmonic Distortion           | $V_O = 2V_{PP}$ , $f = 20MHz$                                                |                   | -56  |                 | dBc    |

| THD                | Total Harmonic Distortion                     | $V_O = 2V_{PP}$ , $f = 20MHz$                                                |                   | -52  |                 | dBc    |

| e <sub>n</sub>     | Input-Referred Voltage Noise                  | f = 1MHz                                                                     |                   | 4.0  |                 | nV/√Hz |

| CP                 | 1dB Compression point                         | f = 10MHz                                                                    |                   | +7   |                 | dBm    |

| SNR                | Signal to Noise Ratio                         | f > 100kHz, BW = 5MHz,<br>V <sub>O</sub> = 350mVrms                          |                   | 92   |                 | dB     |

| Static, DC         | Performance                                   |                                                                              |                   |      |                 | 1      |

| A <sub>CL</sub>    | Small Signal Voltage Gain                     | $V_{O} = 100 \text{mV}_{PP}$<br>$R_{L} = 100 \Omega \text{ to V}^{+}/2$      | .97               | .996 |                 |        |

|                    |                                               | $V_O = 100 \text{mV}_{PP}$<br>$R_L = 2 \text{k} \Omega$ to V <sup>+</sup> /2 | .99               | .998 |                 | V/V    |

| V <sub>OS</sub>    | Input Offset Voltage                          |                                                                              |                   | 1.52 | 12<br><b>16</b> | mV     |

| TC V <sub>OS</sub> | Temperature Coefficient Input Offset Voltage  | See <sup>(4)</sup>                                                           |                   | 23   |                 | μV/°C  |

| I <sub>B</sub>     | Input Bias Current                            | See <sup>(5)</sup>                                                           | -5<br><b>-8</b>   | -2.7 |                 | μA     |

| TC I <sub>B</sub>  | Temperature Coefficient Input Bias<br>Current | See <sup>(4)</sup>                                                           | 1.6               |      |                 | nA/°C  |

| R <sub>OUT</sub>   | Output Resistance                             | $R_L = 100\Omega$ to V <sup>+</sup> /2, f = 100kHz                           |                   | 1.4  |                 | _      |

|                    |                                               | $R_L = 100\Omega$ to V <sup>+</sup> /2, f = 10MHz                            |                   | 1.6  |                 | Ω      |

| PSRR               | Power Supply Rejection Ratio                  | $V_S = +5V \text{ to } V_S = +5.5V,$<br>$V_{IN} = V_S/2$                     | 48<br><b>44</b>   | 68   |                 | dB     |

| Is                 | Supply Current                                | No Load                                                                      |                   | 4.7  | 7<br>8.5        | mA     |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(3)</sup> Slew rate is the average of the positive and negative slew rate.

<sup>(4)</sup> Average Temperature Coefficient is determined by dividing the change in a parameter at temperature extremes by the total temperature change

<sup>(5)</sup> Positive current corresponds to current flowing into the device.

#### 5V Electrical Characteristics (continued)

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_O = V_{CM} = V^+/2$  and  $R_L = 100\Omega$  to  $V^+/2$ . Boldface limits apply at the temperature extremes

| Symbol          | Parameter                    | Conditions                                | Min<br>(1)          | <b>Typ</b> (2) | Max<br>(1)          | Units |  |

|-----------------|------------------------------|-------------------------------------------|---------------------|----------------|---------------------|-------|--|

| Miscellane      | eous Performance             | 1                                         |                     |                | l                   | 1     |  |

| R <sub>IN</sub> | Input Resistance             |                                           |                     | 200            |                     | kΩ    |  |

| C <sub>IN</sub> | Input Capacitance            |                                           |                     | 2.0            |                     | pF    |  |

| V <sub>O</sub>  | Output Swing Positive        | $R_L = 100\Omega$ to $V^+/2$              | 3.80<br><b>3.75</b> | 3.88           |                     |       |  |

|                 |                              | $R_L = 2k\Omega$ to $V^+/2$               | 3.94<br><b>3.92</b> | 3.98           |                     | V     |  |

|                 | Output Swing Negative        | $R_L = 100\Omega$ to $V^+/2$              |                     | 1.12           | 1.20<br><b>1.25</b> | .,    |  |

|                 |                              | $R_L = 2k\Omega$ to $V^+/2$               |                     | 1.03           | 1.06<br><b>1.09</b> | V     |  |

| I <sub>sc</sub> | Output short circuit Current | Sourcing: $V_{IN} = +V_S$ , $V_O = V^+/2$ |                     | <b>-</b> 57    |                     | ^     |  |

|                 |                              | Sinking: $V_{IN} = -V_S$ , $V_O = V^+/2$  |                     | 26             |                     | mA    |  |

| Io              | Linear Output Current        | Sourcing: $V_{IN} - V_O = 0.5V^{(6)}$     | -50<br><b>-43</b>   | -64            |                     | A     |  |

|                 |                              | Sinking: $V_{IN} - V_{O} = -0.5V^{(6)}$   | 30<br><b>23</b>     | 42             |                     | mA    |  |

<sup>(6)</sup> Positive current corresponds to current flowing into the device.

#### **3V Electrical Characteristics**

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = 3V$ ,  $V^- = 0V$ ,  $V_O = V_{CM} = V^+/2$  and  $R_L = 100\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                           | Conditions                                 | <b>Min</b> (1)                                 | <b>Typ</b> (2) | Max<br>(1) | Units |

|----------------|-------------------------------------|--------------------------------------------|------------------------------------------------|----------------|------------|-------|

| Frequency      | Domain Response                     |                                            |                                                |                |            |       |

| SSBW           | Small Signal Bandwidth              | $V_O < 0.5V_{PP}$                          |                                                | 315            |            | MHz   |

| GFN            | Gain Flatness < 0.1dB               | $V_O < 0.5V_{PP}$                          |                                                | 44             |            | MHz   |

| FPBW           | Full Power Bandwidth (-3dB)         | $V_{O} = 1V_{PP} (+4.5 dBm)$               |                                                | 265            |            | MHZ   |

| Time Doma      | ain Response                        |                                            | <u>,                                      </u> |                | •          |       |

| t <sub>r</sub> | Rise Time                           | 1.0V Step (20-80%)                         |                                                | 0.8            |            | ns    |

| t <sub>f</sub> | Fall Time                           |                                            |                                                | 1.2            |            | ns    |

| t <sub>s</sub> | Settling Time to ±0.1%              | 1V Step                                    |                                                | 10             |            | ns    |

| os             | Overshoot                           | 0.5V Step                                  |                                                | 0              |            | %     |

| SR             | Slew Rate                           | See <sup>(3)</sup>                         |                                                | 770            |            | V/µs  |

| Distortion     | And Noise Performance               |                                            |                                                |                |            |       |

| HD2            | 2 <sup>nd</sup> Harmonic Distortion | $V_O = 2V_{PP}$ , $f = 20MHz$              |                                                | -74            |            | dBc   |

| HD3            | 3 <sup>rd</sup> Harmonic Distortion | $V_O = 2V_{PP}$ , $f = 20MHz$              |                                                | <b>-</b> 57    |            | dBc   |

| THD            | Total Harmonic Distortion           | $V_O = 2V_{PP}$ , $f = 20MHz$              |                                                | -56            |            | dBc   |

| e <sub>n</sub> | Input-Referred Voltage Noise        | f = 1MHz                                   |                                                | 3.9            |            | nV/Hz |

| СР             | 1dB Compression point               | f = 10MHz                                  |                                                | +4             |            | dBm   |

| SNR            | Signal to Noise Ratio               | f > 100kHz, BW = 5MHz,<br>$V_O = 350mVrms$ |                                                | 92             |            | dB    |

All limits are specified by testing or statistical analysis.

Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

(3) Slew rate is the average of the positive and negative slew rate.

## **3V Electrical Characteristics (continued)**

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = 3V$ ,  $V^- = 0V$ ,  $V_O = V_{CM} = V^+/2$  and  $R_L = 100\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                                     | Conditions                                                         | Min<br>(1)          | Typ  | Max<br>(1)           | Units |

|--------------------|-----------------------------------------------|--------------------------------------------------------------------|---------------------|------|----------------------|-------|

| Static, DC         | Performance                                   | 1                                                                  |                     |      |                      |       |

| A <sub>CL</sub>    | Small Signal Voltage Gain                     | $V_O = 100 \text{mV}_{PP}$ .s $R_L = 100 \Omega \text{ to V}^+/2$  |                     | .995 |                      | V/V   |

|                    |                                               | $V_{O} = 100 \text{mV}_{PP}$ $R_{L} = 2k\Omega \text{ to V}^{+}/2$ | .99                 | .998 |                      | V/V   |

| Vos                | Input Offset Voltage                          |                                                                    |                     | 1    | 7<br><b>9</b>        | mV    |

| TC V <sub>OS</sub> | Temperature Coefficient Input Offset Voltage  | See <sup>(4)</sup>                                                 |                     | 3.5  |                      | μV/°C |

| I <sub>B</sub>     | Input Bias Current                            | See <sup>(5)</sup>                                                 | −3<br><b>−3.5</b>   | -1.5 |                      | μA    |

| TC I <sub>B</sub>  | Temperature Coefficient Input Bias<br>Current | See <sup>(4)</sup>                                                 |                     | 0.46 |                      | nA/°C |

| R <sub>OUT</sub>   | Output Resistance                             | $R_L = 100\Omega$ to V <sup>+</sup> /2, f = 100kHz                 |                     | 1.8  |                      | 0     |

|                    |                                               | $R_L = 100\Omega$ to V <sup>+</sup> /2, f = 10MHz                  |                     | 2.3  |                      | Ω     |

| PSRR               | Power Supply Rejection Ratio                  | $V_S = +3V \text{ to } V_S = +3.5V,$<br>$V_{IN} = V^+/2$           | 48<br><b>46</b>     | 68   |                      | dB    |

| I <sub>S</sub>     | Supply Current                                | No Load                                                            |                     | 2.4  | 3.5<br><b>4.5</b>    | mA    |

| Miscellane         | ous Performance                               |                                                                    |                     |      | •                    |       |

| R <sub>IN</sub>    | Input Resistance                              |                                                                    |                     | 200  |                      | kΩ    |

| C <sub>IN</sub>    | Input Capacitance                             |                                                                    |                     | 2.3  |                      | pF    |

| Vo                 | Output Swing Positive                         | $R_L = 100\Omega$ to $V^+/2$                                       | 2.02<br><b>1.95</b> | 2.07 |                      | V     |

|                    |                                               | $R_L = 2k\Omega$ to $V^+/2$                                        | 2.12<br><b>2.02</b> | 2.17 |                      | V     |

|                    | Output Swing Negative                         | $R_L = 100\Omega$ to V <sup>+</sup> /2                             |                     | .930 | .970<br><b>1.050</b> | V     |

|                    |                                               | $R_L = 2k\Omega$ to V <sup>+</sup> /2                              |                     | .830 | .880<br><b>.980</b>  | V     |

| I <sub>SC</sub>    | Output Short Circuit Current                  | Sourcing: $V_{IN} = +V_S$ , $V_O = V^+/2$                          |                     | -32  |                      | mΛ    |

|                    |                                               | Sinking: $V_{IN} = -V_S$ , $V_O = V^+/2$                           |                     | 15   |                      | mA    |

| l <sub>O</sub>     | Linear Output Current                         | Sourcing: $V_{IN} - V_{O} = 0.5V^{(5)}$                            | -20<br><b>-13</b>   | -28  |                      | m ^   |

|                    |                                               | Sinking: $V_{IN} - V_{O} = -0.5V^{(5)}$                            | 12<br><b>8</b>      | 17   |                      | mA    |

<sup>(4)</sup> Average Temperature Coefficient is determined by dividing the change in a parameter at temperature extremes by the total temperature change.

<sup>(5)</sup> Positive current corresponds to current flowing into the device.

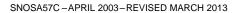

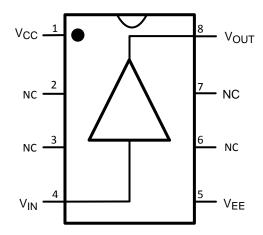

#### **CONNECTION DIAGRAMS**

Figure 2. 8-Pin SOIC (Top View) See Package Number D (R-PDSO-G8)

Figure 3. 5-Pin SOT-23 (Top View) See Package Number DBV (R-PDSO\_G5)

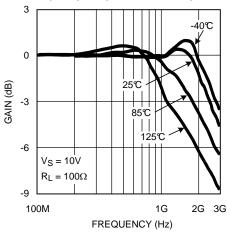

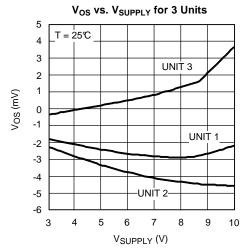

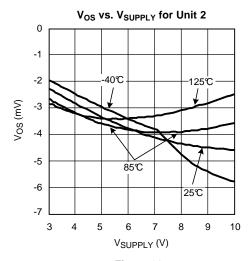

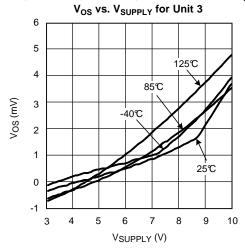

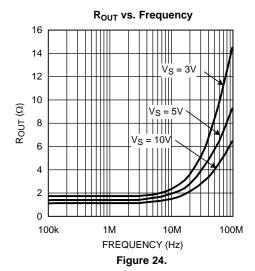

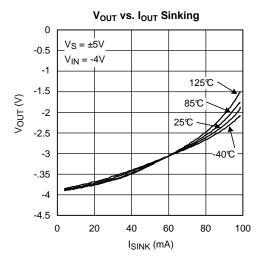

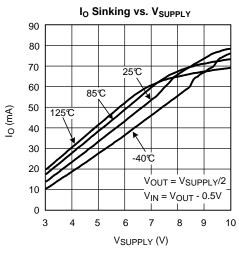

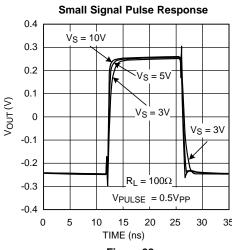

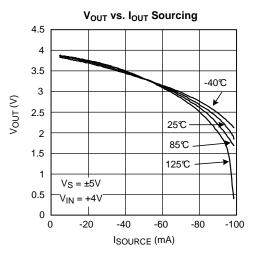

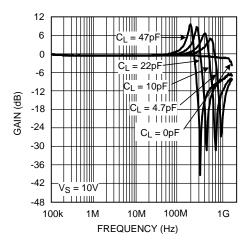

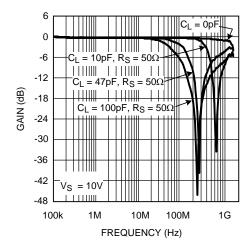

## **Typical Performance Charac teristics**

At  $T_J = 25^{\circ}C$ ;  $V^+ = +5V$ ;  $V^- = -5V$ ; Unless otherwise specified.

Figure 4.

Differential Gain and Phase

Frequency Response Over Temperature

Figure 5.

Figure 7.

DC OUTPUT VOLTAGE (mV)

At  $T_J = 25^{\circ}C$ ;  $V^+ = +5V$ ;  $V^- = -5V$ ; Unless otherwise specified.

Figure 10.

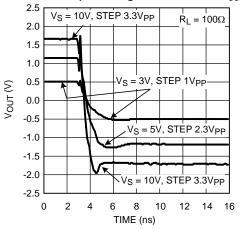

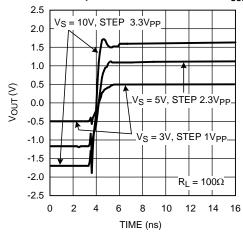

#### Transient Response Negative for Various V<sub>SUPPLY</sub>

Figure 12.

Figure 14.

### Transient Response Positive for Various V<sub>SUPPLY</sub>

Figure 11.

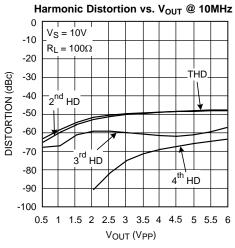

#### Harmonic Distortion vs. V<sub>OUT</sub> @ 5MHz

Figure 13.

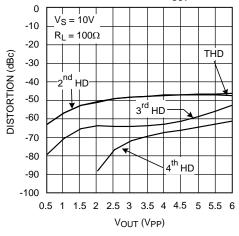

## Harmonic Distortion vs. V<sub>OUT</sub> @ 20MHz

Figure 15.

At  $T_J = 25^{\circ}C$ ;  $V^+ = +5V$ ;  $V^- = -5V$ ; Unless otherwise specified.

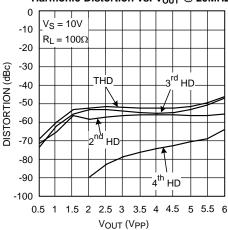

Figure 16.

Figure 18.

Figure 17.

Figure 19.

Figure 21.

Copyright © 2003–2013, Texas Instruments Incorporated

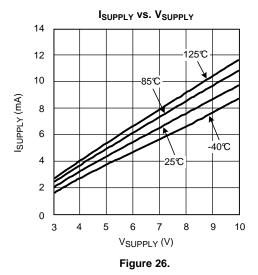

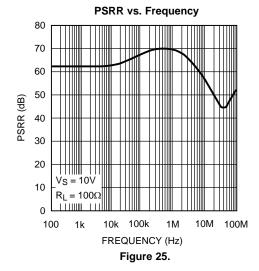

At  $T_J = 25^{\circ}C$ ;  $V^+ = +5V$ ;  $V^- = -5V$ ; Unless otherwise specified.

Figure 22.

Figure 23.

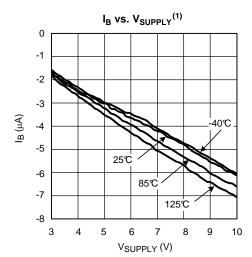

Positive current corresponds to current flowing into the device. (1)

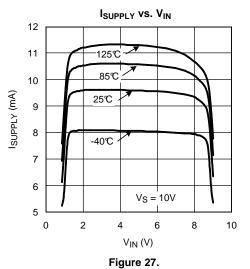

At  $T_J = 25^{\circ}C$ ;  $V^+ = +5V$ ;  $V^- = -5V$ ; Unless otherwise specified.

Figure 28.

Figure 30.

Figure 32.

Figure 29.

Figure 31.

At  $T_J = 25$ °C;  $V^+ = +5V$ ;  $V^- = -5V$ ; Unless otherwise specified.

Figure 35.

Submit Documentation Feedback

#### **APPLICATION NOTES**

#### **USING BUFFERS**

A buffer is an electronic device delivering current gain but no voltage gain. It is used in cases where low impedances need to be driven and more drive current is required. Buffers need a flat frequency response and small propagation delay. Furthermore, the buffer needs to be stable under resistive, capacitive and inductive loads. High frequency buffer applications require that the buffer be able to drive transmission lines and cables directly.

#### IN WHAT SITUATION WILL WE USE A BUFFER?

In case of a signal source not having a low output impedance one can increase the output drive capability by using a buffer. For example, an oscillator might stop working or have frequency shift which is unacceptably high when loaded heavily. A buffer should be used in that situation. Also in the case of feeding a signal to an A/D converter it is recommended that the signal source be isolated from the A/D converter. Using a buffer assures a low output impedance, the delivery of a stable signal to the converter, and accommodation of the complex and varying capacitive loads that the A/D converter presents to the OpAmp. Optimum value is often found by experimentation for the particular application.

The use of buffers is strongly recommended for the handling of high frequency signals, for the distribution of signals through transmission lines or on pcb's, or for the driving of external equipment. There are several driving options:

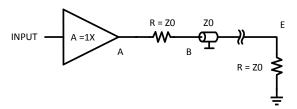

- Use one buffer to drive one transmission line (see Figure 36)

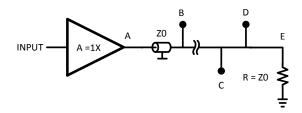

- Use one buffer to drive to multiple points on one transmission line (see Figure 37)

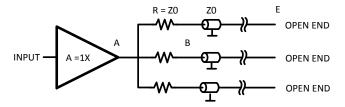

- Use one buffer to drive several transmission lines each driving a different receiver. (see Figure 38)

Figure 36.

Figure 37.

Figure 38.

In these three options it is seen that there is more than one preferred method to reach an (end) point on a transmission line. Until a certain point the designer can make his own choice but the designer should keep in mind never to break the rules about high frequency transport of signals. An explanation follows in the text below.

#### TRANSMISSION LINES

Introduction to transmission lines. The following is an overview of transmission line theory. Transmission lines can be used to send signals from DC to very high frequencies. At all points across the transmission line, Ohm's law must apply. For very high frequencies, parasitic behavior of the PCB or cables comes into play. The type of cable used must match the application. For example an audio cable looks like a coax cable but is unusable for radar frequencies at 10GHz. In this case one have to use special coax cables with lower attenuation and radiation characteristics.

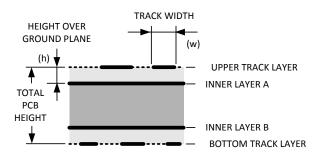

Normally a pcb trace is used to connect components on a pcb board together. An important considerations is the amount of current carried by these pcb traces. Wider pcb traces are required for higher current densities and for applications where very low series resistance is needed. When routed over a ground plane, pcb traces have a defined Characteristic Impedance. In many design situations characteristic impedance is not utilized. In the case of high frequency transmission, however it is necessary to match the load impedance to the line characteristic impedance (more on this later). Each trace is associated with a certain amount of series resistance and series inductance plus each trace exhibits parallel capacitance to the ground plane. The combination of these parameters defines the line's characteristic impedance. The formula with which we calculate this impedance is as follows:

$$Z_0 = \sqrt{(L/C)}$$

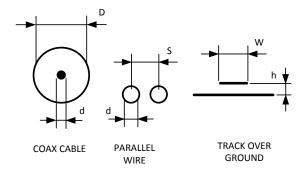

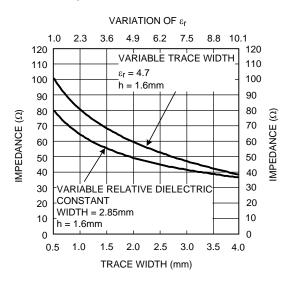

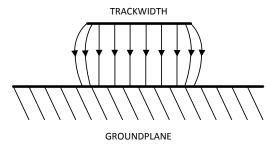

In this formula L and C are the value/unit length, and R is assumed to be zero. C and L are unknown in many cases so we have to follow other steps to calculate the  $Z_0$ . The characteristic impedance is a function of the geometry of the cross section of the line. In (Figure 39) we see three cross sections of commonly used transmission lines.

Figure 39.

$Z_0$  can be calculated by knowing some of the physical dimensions of the pcb line, such as pcb thickness, width of the trace and  $\varepsilon_r$ , relative dielectric constant. The formula given in transmission line theory for calculating  $Z_0$  is as follows:

$$Z = \frac{87}{\sqrt{(\varepsilon \, r + 1.41)}} \, x \ln \, \frac{(5.98 \, x \, h)}{(th + 0.8W)}$$

where

- ε<sub>r</sub>= relative dielectric constant

- h= pcb height

- W= trace width

- th= thickness of the copper

(1)

If we ignore the thickness of the copper in comparison to the width of the trace then we have the following equation:

Product Folder Links: LMH6559

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

$$Z = \frac{87}{\sqrt{(\varepsilon \, r + 1.41)}} \times \ln \frac{(5.98 \times h)}{(0.8W)}$$

(2)

With this formula it is possible to calculate the line impedance vs. the trace width. Figure 40 shows the impedance associated with a given line width. Using the same formula it is also possible to calculate what happens when  $\epsilon_r$  varies over a certain range of values. Varying the  $\epsilon_r$  over a range of 1 to 10 gives a variation for the Characteristic Impedance of about  $40\Omega$  from  $80\Omega$  to  $38\Omega$ . Most transmission lines are designed to have  $50\Omega$  or  $75\Omega$  impedance. The reason for that is that in many cases the pcb trace has to connect to a cable whose impedance is either  $50\Omega$  or  $75\Omega$ . As shown  $\epsilon_r$  and the line width influence this value.

Figure 40.

Next, there will be a discussion of some issues associated with the interaction of the transmission line at the source and at the load.

#### **Connecting A Load Using A Transmission Line**

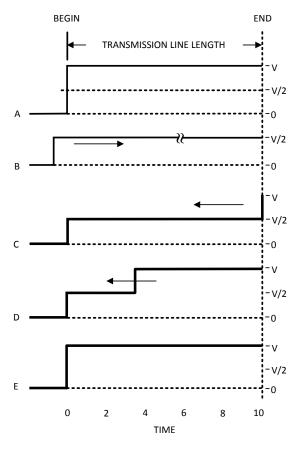

In most cases, it is unrealistic to think that we can place a driver or buffer so close to the load that we don't need a transmission line to transport the signal. The pcb trace length between a driver and the load may affect operation depending upon the operating frequency. Sometimes it is possible to do measurements by connecting the DUT directly to the analyzer. As frequencies become higher the short lines from the DUT to the analyzer become long lines. When this happens there is a need to use transmission lines. The next point to examine is what happens when the load is connected to the transmission line. When driving a load, it is important to match the line and load impedance, otherwise reflections will occur and this phenomena will distort the signal. If a transient is applied at T = 0 (Figure 41, trace A) the resultant waveform may be observed at the start point of the transmission line. At this point (begin) on the transmission line the voltage increases to (V) and the wave front travels along the transmission line and arrives at the load at T = 10. At any point across along the line  $I = V/Z_0$ , where  $Z_0$  is the impedance of the transmission line. For an applied transient of 2V with  $Z_0 = 50\Omega$  the current from the buffer output stage is 40mA. Many vintage opamps cannot deliver this level of current because of an output current limitation of about 20mA or even less. At T = 10 the wave front arrives at the load. Since the load is perfectly matched to the transmission line all of the current traveling across the line will be absorbed and there will be no reflections. In this case source and load voltages are exactly the same. When the load and the transmission line have unequal values of impedance a different situation results. Remember there is another basic which says that energy cannot be lost. The power in the transmission line is  $P = V^2/R$ . In our example the total power is  $2^2/50 = 80 \text{mW}$ . Assume a load of 75 $\Omega$ . In that case a power of 80mW arrives at the 75 $\Omega$  load and causes a voltage of the proper amplitude to maintain the incoming power.

$$V = \sqrt{(P \times R)} = \sqrt{(80 \times 10^{-3} \times 75)} = 2.45V$$

(3)

The voltage wavefront of 2.45V will now set about traveling back over the transmission line towards the source, thereby resulting in a reflection caused by the mismatch. On the other hand if the load is less then  $50\Omega$  the backwards traveling wavefront is subtracted from the incoming voltage of 2V. Assume the load is  $40\Omega$ . Then the voltage across the load is:

$$\sqrt{(80 \times 10^{-3} \times 40)} = 1.79 V \tag{4}$$

This voltage is now traveling backwards through the line toward the start point. In the case of a sinewave interferences develop between the incoming waveform and the backwards-going reflections, thus distorting the signal. If there is no load at all at the end point the complete transient of 2V is reflected and travels backwards to the beginning of the line. In this case the current at the endpoint is zero and the maximum voltage is reflected. In the case of a short at the end of the line the current is at maximum and the voltage is zero.

Figure 41.

#### **Using Serial And Parallel Termination**

Many applications, such as video, use a series resistance between the driver and the transmission line (see Figure 36). In this case the transmission line is terminated with the characteristic impedance at both ends of the line. See Figure 41 trace B. The voltage traveling through the transmission line is half the voltage seen at the output of the buffer, because the series resistor in combination with  $Z_0$  forms a two-to-one voltage divider. The result is a loss of 6dB. For video applications, amplifier gain is set to 2 in order to realize an overall gain of 1. Many operational amplifiers have a relatively flat frequency response when set to a gain of two compared to unity gain. In trace B it is seen that, if the voltage reaches the end of the transmission line, the line is perfectly matched and no reflections will occur. The end point voltage stays at half the output voltage of the opamp or buffer.

#### **Driving More Than One Input**

Another transmission line possibility is to route the trace via several points along a transmission line (Figure 37). This is only possible if care is taken to observe certain restrictions. Failure to do so will result in impedance discontinuities that will cause distortion of the signal. In the configuration of Figure 37 there is a transmission line connected to the buffer output and the end of the line is terminated with  $Z_0$ . We have seen in the Connecting A Load Using A Transmission Line section that for the condition above, the signal throughout the entire transmission line has the same value, that the value is the nominal value initiated by the opamp output, and no reflections occur at the end point. Because of the lack of reflections no interferences will occur. Consequently the signal has every where on the line the same amplitude. This allows the possibility of feeding this signal to the input port of any device which has high ohmic impedance and low input capacitance. In doing so keep in mind that the transient arrives at different times at the connected points in the transmission line. The speed of light in vacuum, which is about 3 \*  $10^8$  m/sec, reduces through a transmission line or a cable down to a value of about 2 \*  $10^8$  m/sec. The distance the signal will travel in 1ns is calculated by solving the following formula:

$S = V^*t$

#### where

- S = distance

- V = speed in the cable

This calculation gives the following result:  $s = 2*10^8 * 1*10^{-9} = 0.2m$

That is for each nanosecond the wave front shifts 20cm over the length of the transmission line. Keep in mind that in a distance of just 2cm the time displacement is already 100ps.

#### **Using Serial Termination To More Than One Transmission Line**

Another way to reach several points via a transmission line is to start several lines from one buffer output (see Figure 38). This is possible only if the output can deliver the needed current into the sum of all transmission lines. As can be seen in this figure there is a series termination used at the beginning of the transmission line and the end of the line has no termination. This means that only the signal at the endpoint is usable because at all other points the reflected signal will cause distortion over the line. Only at the endpoint will the measured signal be the same as at the startpoint. Referring to Figure 41 trace C, the signal at the beginning of the line has a value of V/2 and at T = 0 this voltage starts traveling towards the end of the transmission line. Once at the endpoint the line has no termination and 100% reflection will occur. At T = 10 the reflection causes the signal to jump to 2V and to start traveling back along the line to the buffer (see Figure 41 trace D). Once the wavefront reaches the series termination resistor, provided the termination value is Z<sub>0</sub>, the wavefront undergoes total absorption by the termination. This is only true if the output impedance of the buffer/driver is low in comparison to the characteristic impedance  $Z_0$ . At this moment the voltage in the whole transmission line has the nominal value of 2V (see Figure 41 trace E). If the three transmission lines each have a different length the particular point in time at which the voltage at the series termination resistor jumps to 2V is different for each case. However, this transient is not transferred to the other lines because the output of the buffer is low and this transient is highly attenuated by the combination of the termination resistor and the output impedance of the buffer. A simple calculation illustrates the point. Assume that the output impedance is  $5\Omega$ . For the frequency of interest the attenuation is  $V_B/V_A = 55/5 = 11$ , where A and B are the points in Figure 38. In this case the voltage caused by the reflection is 2/11 = 0.18V. This voltage is transferred to the remaining transmission lines in sequence and following the same rules as before this voltage is seen at the end points of those lines. The lower the output resistance the higher the decoupling between the different lines. Furthermore one can see that at the endpoint of these transmission lines there is a normal transient equal to the original transient at the beginning point. However at all other points of the transmission line there is a step voltage at different distances from the startpoint depending at what point this is measured (see trace D).

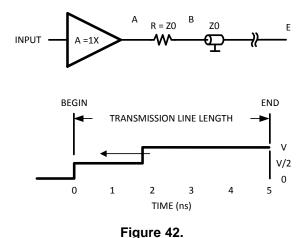

#### Measuring The Length Of A Transmission Line

An open transmission line can be used to measure the length of a particular transmission line. As can be seen in Figure 42 the line of interest has a certain length. A transient is applied at T = 0 and at that point in time the wavefront starts traveling with an amplitude of V/2 towards the end of the line where it is reflected back to the startpoint.

To calculate the length of the line it is necessary to measure immediately after the series termination resistor. The voltage at that point remains at half nominal voltage, thus V/2, until the reflection returns and the voltage jumps to V. During an interval of 5ns the signal travels to the end of the line where the wave front is reflected and returns to the measurement point. During the time interval when the wavefront is traveling to the end of the transmission line and back the voltage has a value of V/2. This interval is 10ns. The length can be calculated with the following formula: S = (V\*T)/2

$$S = \frac{(2 \times 10^8) \times (10 \times 10^{-9})}{2} = 1 \text{mtr}$$

(6)

As calculated before in the Driving More Than One Input section the signal travels 20cm/ns so in 5ns this distance indicated distance is 1m. So this example is easily verified.

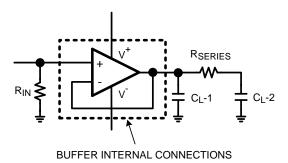

#### APPLYING A CAPACITIVE LOAD

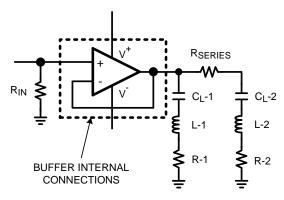

The assumption of pure resistance for the purpose of connecting the output stage of a buffer or opamp to a load is appropriate as a first approximation. Unfortunately that is only a part of the truth. Associated with this resistor is a capacitor in parallel and an inductor in series. Any capacitance such as  $C_L$ -1 which is connected directly to the output stage is active in the loop gain as seen in Figure 43. Output capacitance, present also at the minus input in the case of a buffer, causes an increasing phase shift leading to instability or even oscillation in the circuit.

Figure 43.

Unfortunately the leads of the output capacitor also contain series inductors which become more and more important at high frequencies. At a certain frequency this series capacitor and inductor forms an LC combination which becomes series resonant. At the resonant frequency the reactive component vanishes leaving only the ohmic resistance (R-1 or R-2) of the series L/C combination. (see Figure 44).

Figure 44.

Consider a frequency sweep over the entire spectrum for which the LMH6559 high frequency buffer is active. In the first instance peaking occurs due to the parasitic capacitance connected at the load whereas at higher frequencies the effects of the series combination of L and C become noticeable. This causes a distinctive dip in the output frequency sweep and this dip varies depending upon the particular capacitor as seen in Figure 45.

Figure 45.

To minimize peaking due to CL a series resistor for the purpose of isolation from the output stage should be used. A low valued resistor will minimize the influence of such a load capacitor. In a  $50\Omega$  system as is common in high frequency circuits a  $50\Omega$  series resistor is often used. Usage of the series resistor, as seen in Figure 46 eliminates the peaking but not the dip. The dip will vary with the particular capacitor. Using a resistor in series with a capacitor creates in a single pole situation a 6dB/oct rolloff. However, at high frequencies the internal inductance is appreciable and forms a series LC combination with the capacitor. Choice of a higher valued resistor, for example 500 to  $1k\Omega$ , and a capacitor of hundreds of pF's provides the expected response at lower frequencies.

Figure 46.

#### **USING GROUND PLANES**

The use of ground planes is recommended both for providing a low impedance path to ground (or to one of the other supply voltages) and also for forming effective controlled impedance transmission lines for the high frequency signal flow on the board. Multilayer boards often make use of inner conductive layers for routing supply voltages. These supply voltage layers form a complete plane rather than using discrete traces to connect the different points together for the specified supply. Signal traces on the other hand are routed on outside layers both top and bottom. This allows for easy access for measurement purposes. Fortunately, only very high density boards have signal layers in the middle of the board. In an earlier section, the formula for  $Z_0$  was derived as:

$$Z = \frac{87}{\sqrt{(\varepsilon r + 1.41)}} \times \ln \frac{(5.98 \times h)}{(0.8W)}$$

(7)

The width of a trace is determined by the thickness of the board. In the case of a multilayer board the thickness is the space between the trace and the first supply plane under this trace layer. By common practice, layers do not have to be evenly divided in the construction of a pcb. Refer to Figure 47. The design of a transmission line design over a pcb is based upon the thickness of the different internal layers and the  $\epsilon_r$  of the board material. The pcb manufacturer can supply information about important specifications. For example, a nominal 1.6mm thick pcb produces a  $50\Omega$  trace for a calculated width of 2.9mm. If this layer has a thickness of 0.35mm and for the same  $\epsilon_r$ , the trace width for  $50\Omega$  should be of 0.63mm, as calculated from Equation 8, a derivation from Equation 7.

$$w = \frac{5.98 \times h}{e^{A}}$$

where A =

$$\frac{\left[Z_{O} \times \sqrt{(\epsilon_{r} + 1.41)}\right]}{87}$$

(8)

Figure 47.

Using a trace over a ground plane has big advantages over the use of a standard single or double sided board. The main advantage is that the electric field generated by the signal transported over this trace is fixed between the trace and the ground plane e.g. there is almost no possibility of radiation (see Figure 48).

Figure 48.

This effect works to both sides because the circuit will not generate radiation but the circuit is also not sensible if exposed to a certain radiation level. The same is also noticeable when placing components flat on the printed circuit board. Standard through hole components when placed upright can act as an antenna causing an electric field which could be picked up by a nearby upright component. If placed directly at the surface of the pcb this influence is much lower.

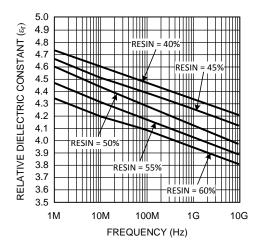

#### The Effect Of Variation For $\varepsilon_r$

When using pcb material the  $\varepsilon_r$  has a certain shift over the used frequency spectrum, so if necessary to work with very accurate trace impedances one must taken into account for which frequency region the design has to be functional. Figure 49 (Courtesy of Islola Corporation) gives an example what the drift in  $\varepsilon_r$  will be when using the pcb material produced by Isola. If working at frequencies of 100MHz then a 50 $\Omega$  trace has a width of 3.04mm for standard 1.6mm FR4 pcb material, and the same trace needs a width of 3.14mm. for frequencies around 10GHz.

Figure 49.

### **Routing Power Traces**

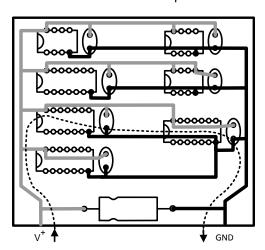

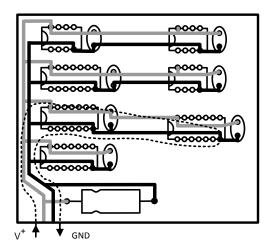

Power line traces routed over a pcb should be kept together for best practice. If not a ground loop will occur which may cause more sensitivity to radiation. Also additional ground trace length may lead to more ringing on digital signals. Careful attention to power line distribution leads to improved overall circuit performance. This is especially valid for analog circuits which are more sensitive to spurious noise and other unwanted signals.

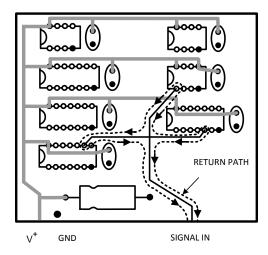

Figure 50.

As demonstrated in Figure 50 the power lines are routed from both sides on the pcb. In this case a current loop is created as indicated by the dotted line. This loop can act as an antenna for high frequency signals which makes the circuit sensitive to  $R_F$  radiation. A better way to route the power traces can be seen in the following setup. (see Figure 51)

Figure 51.

In this arrangement the power lines have been routed in order to avoid ground loops and to minimize sensitivity to noise etc. The same technique is valid when routing a high frequent signal over a board which has no ground plane. In that case is it good practice to route the high frequency signal alongside a ground trace. A still better way to create a pcb carrying high frequency signals is to use a pcb with a ground plane or planes.

#### **Discontinuities In A Ground Plane**

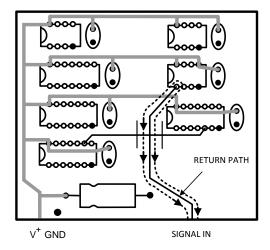

A ground plane with traces routed over this plane results in the build up of an electric field between the trace and the ground plane as seen in Figure 48. This field is build up over the entire routing of the trace. For the highest performance the ground plane should not be interrupted because to do so will cause the field lines to follow a roundabout path. In Figure 52 it was necessary to interrupt the ground plane with a crossing trace. This interruption causes the return current to follow a longer route than the signal path follows to overcome the discontinuity.

Figure 52.

If needed it is possible to bypass the interruption with traces that are parallel to the signal trace in order to reduce the negative effects of the discontinuity in the ground plane. In doing so, the current in the ground plane closely follows the signal trace on the return path as can be seen in Figure 53. Care must be taken not to place too many traces in the ground plane or the ground plane effectively vanishes such that even bypasses are unsuccessful in reducing negative effects.

Figure 53.

If the overall density becomes too high it is better to make a design which contains additional metal layers such that the ground planes actually function as ground planes. The costs for such a pcb are increased but the payoff is in overall effectiveness and ease of design.

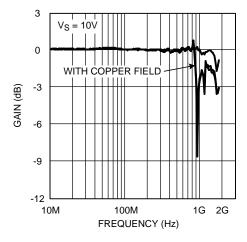

#### **Ground Planes At Top And Bottom Layer Of A PCB**

In addition to the bottom layer ground plane another useful practice is to leave as much copper as possible at the top layer. This is done to reduce the amount of copper to be removed from the top layer in the chemical process. This causes less pollution of the chemical baths allowing the manufacturer to make more pcb's with a certain amount of chemicals. Connecting this upper copper to ground provides additional shielding and signal performance is enhanced. For lower frequencies this is specifically true. However, at higher frequencies other effects become more and more important such that unwanted coupling may result in a reduction in the bandwidth of a circuit. In the design of a test circuit for the LMH6559 this effect was clearly noticeable and the useful bandwidth was reduced from 1500MHz to around 850MHz.

Figure 54.

As can be seen in Figure 54 the presence of a copper field close to the transmission line to and from the buffer causes unwanted coupling effects which can be seen in the dip at about 850MHz. This dip has a depth of about 5dB for the case when all of the unused space is filled with copper. In case of only one area being filled with copper this dip is about 9dB.

#### **PCB Board Layout And Component Selection**

Sound practice in the area of high frequency design requires that both active and passive components be used for the purposes for which they were designed. It is possible to amplify signals at frequencies of several hundreds of MHz using standard through hole resistors. Surface mount devices, however, are better suited for this purpose. Surface mount resistors and capacitors are smaller and therefore parasitics are of lower value and therefore have less influence on the properties of the amplifier. Another important issue is the pcb itself, which is no longer a simple carrier for all the parts and a medium to interconnect them. The pcb board becomes a real component itself and consequently contributes its own high frequency properties to the overall performance of the circuit. Sound practice dictates that a design have at least one ground plane on a pcb which provides a low impedance path for all decoupling capacitors and other ground connections. Care should be taken especially that on- board transmission lines have the same impedance as the cables to which they are connected -  $50\Omega$  for most applications and 75 $\Omega$  in case of video and cable TV applications. Such transmission lines usually require much wider traces on a standard double sided PCB board than needed for a 'normal' trace. Another important issue is that inputs and outputs must not 'see' each other. This occurs if inputs and outputs are routed together over the pcb with only a small amount of physical separation, particularly when there is a high differential in signal level between them. Furthermore components should be placed as flat and low as possible on the surface of the PCB. For higher frequencies a long lead can act as a coil, a capacitor or an antenna. A pair of leads can even form a transformer. Careful design of the pcb avoids oscillations or other unwanted behaviors. For ultra high frequency designs only surface mount components will give acceptable results. (for more information see OA-15 (Literature Number SNOA367).

TI suggests the following evaluation boards as a guide for high frequency layout and as an aid in device testing and characterization.

| Device     | Package | Evaluation Board Part Number |

|------------|---------|------------------------------|

| LMH6559MA  | SOIC    | CLC730245                    |

| LMH6559MAX | SOIC    | CLC730245                    |

| LMH6559MF  | SOT-23  | CLC730136                    |

| LMH6559MFX | SOT-23  | CLC730136                    |

These free evaluation boards are shipped when a device sample request is placed with Texas Instruments.

#### **POWER SEQUENCING OF THE LMH6559**

Caution should be exercised in applying power to the LMH6559. When the negative power supply pin is left floating it is recommended that other pins, such as positive supply and signal input should also be left unconnected. If the ground is floating while other pins are connected the input circuitry is effectively biased to ground, with a mostly low ohmic resistor, while the positive power supply is capable of delivering significant current through the circuit. This causes a high input bias current to flow which degrades the input junction. The result is an input bias current which is out of specification. When using inductive relays in an application care should be taken to connect first both power connections before connecting the bias resistor to the input.

## **REVISION HISTORY**

| CI | hanges from Revision B (March 2013) to Revision C  |  |   |  |  |

|----|----------------------------------------------------|--|---|--|--|

| •  | Changed layout of National Data Sheet to TI format |  | 2 |  |  |

Product Folder Links: LMH6559

1-Nov-2013

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|----------------------|---------|

| LMH6559MA        | NRND   | SOIC         | D                  | 8    | 95             | TBD                        | Call TI          | Call TI            | -40 to 85    | LMH65<br>59MA        |         |

| LMH6559MA/NOPB   | ACTIVE | SOIC         | D                  | 8    | 95             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LMH65<br>59MA        | Samples |

| LMH6559MAX/NOPB  | ACTIVE | SOIC         | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | LMH65<br>59MA        | Samples |

| LMH6559MF        | NRND   | SOT-23       | DBV                | 5    | 1000           | TBD                        | Call TI          | Call TI            | -40 to 85    | B05A                 |         |

| LMH6559MF/NOPB   | ACTIVE | SOT-23       | DBV                | 5    | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | B05A                 | Samples |

| LMH6559MFX/NOPB  | ACTIVE | SOT-23       | DBV                | 5    | 3000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | B05A                 | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

## PACKAGE OPTION ADDENDUM

1-Nov-2013

(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Mar-2013

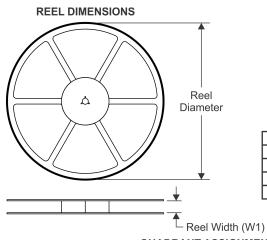

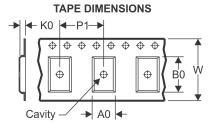

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

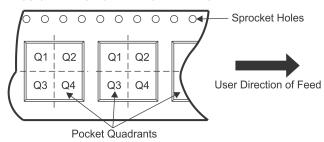

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LMH6559MAX/NOPB            | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LMH6559MF                  | SOT-23          | DBV                | 5 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMH6559MF/NOPB             | SOT-23          | DBV                | 5 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMH6559MFX/NOPB            | SOT-23          | DBV                | 5 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

www.ti.com 21-Mar-2013

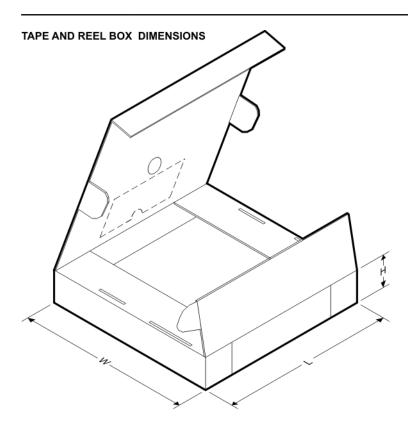

\*All dimensions are nominal

| 7 III GIITTOTOTOTO GIO TTOTTITTA |              |                 |      |      |             |            |             |

|----------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| LMH6559MAX/NOPB                  | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LMH6559MF                        | SOT-23       | DBV             | 5    | 1000 | 210.0       | 185.0      | 35.0        |

| LMH6559MF/NOPB                   | SOT-23       | DBV             | 5    | 1000 | 210.0       | 185.0      | 35.0        |

| LMH6559MFX/NOPB                  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

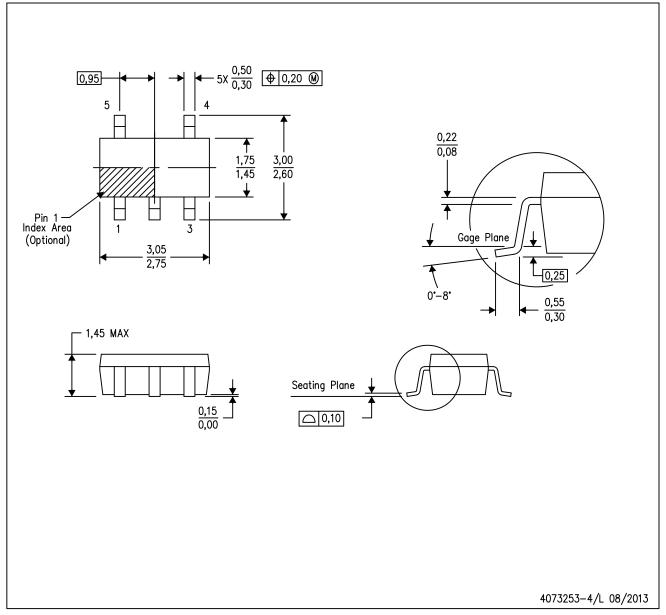

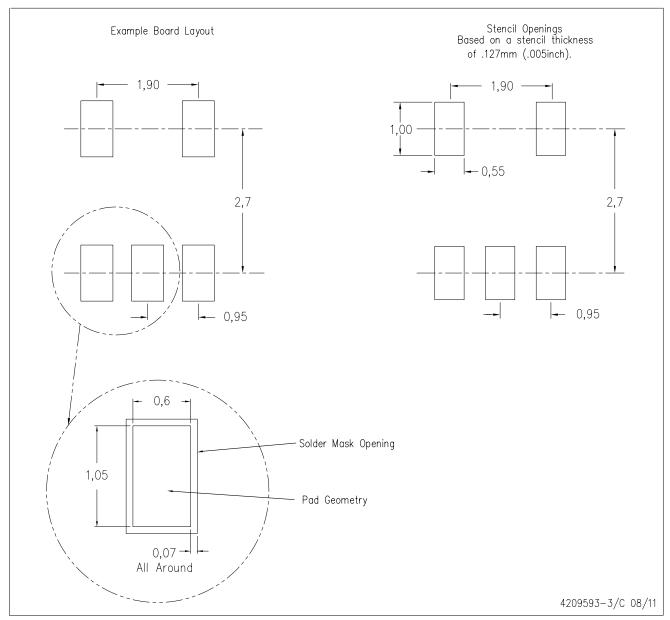

DBV (R-PDSO-G5)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-178 Variation AA.

# DBV (R-PDSO-G5)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

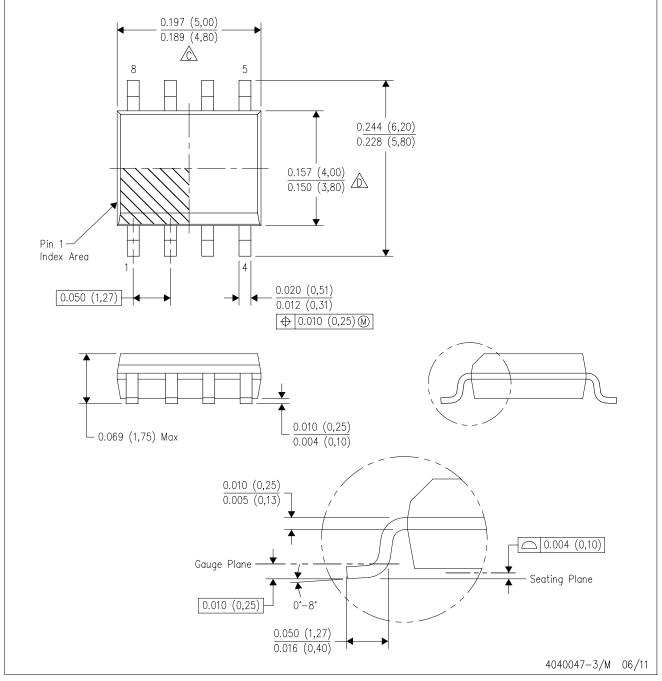

# D (R-PDSO-G8)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.