# LMH6518 900 MHz, Digitally Controlled, Variable Gain Amplifier

Check for Samples: LMH6518

# **FEATURES**

- Gain Range 40 dB

- Gain Step Size 2 dB

- Combined Gain Resolution with Gsample/Second ADC's 8.5 mdB

- Min Gain -1.16 dB

- Max Gain 38.8 dB

- -3 dB BW 900 MHz

- Rise/Fall Time <500 ps

- Recovery Time <5 ns</li>

- Propagation Delay Variation 100 ps

- HD2 @ 100 MHz -50 dBc

- HD3 @ 100 MHz -53 dBc

- Input-Referred Noise (Max Gain) 0.98 nV/√Hz

- Over-Voltage Clamps for Fast Recovery

- Power Consumption Auxiliary Turned Off 1.1W0.75W

# **APPLICATIONS**

- Oscilloscope Programmable Gain Amplifier

- Differential ADC Drivers

- High Frequency Single-Ended Input to Differential Conversion

- Precision Gain Control Applications

- Medical Applications

- **RF/IF Applications**

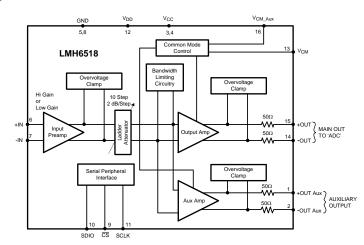

### **Functional Block Diagram**

# DESCRIPTION

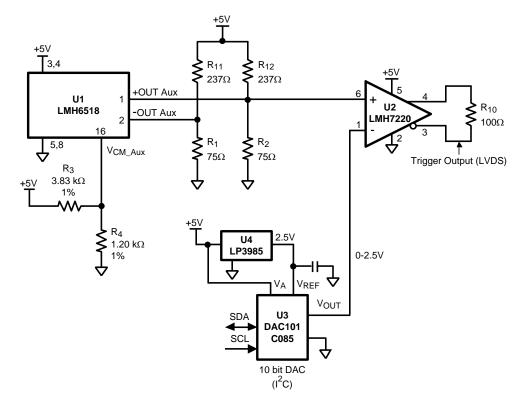

The LMH6518 is a digitally controlled variable gain amplifier whose total gain can be varied from -1.16 dB to 38.8 dB for a 40 dB range in 2 dB steps. The -3 dB bandwidth is 900 MHz at all gains. Gain accuracy at each setting is typically 0.1 dB. When used in conjunction with a Texas Instruments Gsample/second (Gsps) ADC with adjustable full scale (FS) range, the LMH6518 gain adjustment will accommodate full scale input signals from 6.8 mV<sub>PP</sub> to 920 mV<sub>PP</sub> to get 700 mV<sub>PP</sub> nominal at the ADC input. The Auxiliary output ("+OUT Aux" and "-OUT Aux") follows the Main output and is intended for use in Oscilloscope trigger function circuitry but may have other uses in other applications.

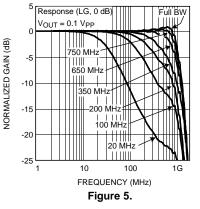

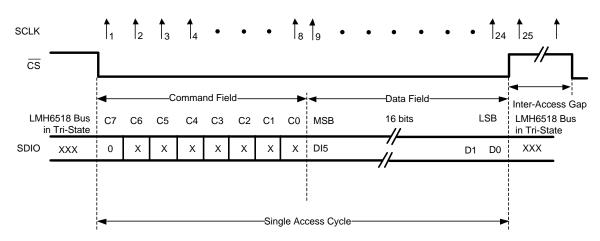

The LMH6518 gain is programmed via a SPI-1 compatible serial bus. A signal path combined gain resolution of 8.5 mdB can be achieved when the LMH6518's gain and the Gsps ADC's FS input are both manipulated. Inputs and outputs are DC-coupled. The outputs are differential with individual Common Mode (CM) voltage control (for Main and Auxiliary outputs) and have a selectable bandwidth limiting circuitry (common to both Main and Auxiliary) of 20, 100, 200, 350, 650, 750 MHz or full bandwidth.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

# LMH6518

#### SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

RUMENTS

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### Absolute Maximum Ratings (1)(2)

| ······································ |                |

|----------------------------------------|----------------|

| ESD Tolerance <sup>(3)</sup>           |                |

| Human Body Model                       | 2000V          |

| Machine Model                          | 200V           |

| Charge Device Model                    | 1000V          |

| Supply Voltage                         |                |

| V <sub>CC</sub> (5V nominal)           | 5.5V           |

| V <sub>DD</sub> (3.3V nominal)         | 3.6V           |

| Differential Input                     | ±1V            |

| Input Common Mode Voltage              | 1V to 4V       |

| $V_{CM}$ and $V_{CM_Aux}$              | 2V             |

| SPI Inputs                             | 3.6V           |

| Maximum Junction Temperature           | 150°C          |

| Storage Temperature Range              | -65°C to 150°C |

| Soldering Information                  |                |

| Infrared or Convection (20 sec.)       | 235°C          |

| Wave Soldering (10 sec.)               | 260°C          |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

### **Operating Ratings** <sup>(1)</sup>

| Supply Voltage    | $V_{CC} = 5V (\pm 5\%)$     |

|-------------------|-----------------------------|

|                   | $V_{DD} = 3.3V \ (\pm 5\%)$ |

| Temperature Range | -40°C to 85°C               |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

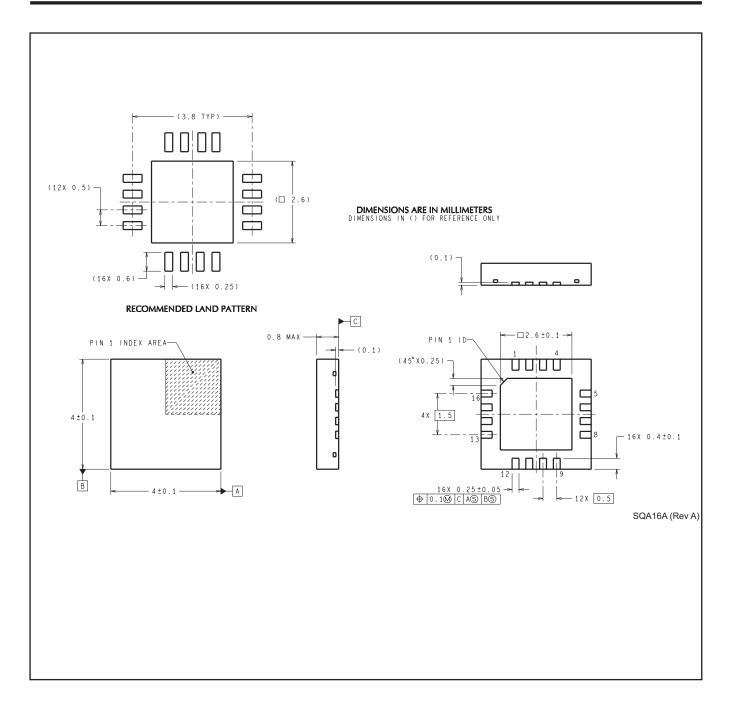

# **Thermal Properties**

| Temperature Range <sup>(1)</sup>                         | −40°C to 85°C |

|----------------------------------------------------------|---------------|

| Junction-to-Ambient                                      |               |

| Thermal Resistance ( $\theta J_A$ ), WQFN <sup>(1)</sup> | 40°C/W        |

(1) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for package soldered directly into a 2 layer PC board with zero air flow. Package should be soldered unto a 6.8 mm<sup>2</sup> copper area as shown in the "recommended land pattern" shown in the package drawing.

# Electrical Characteristics <sup>(1)</sup>

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}$ C, Input CM = 2.5V,  $V_{CM} = 1.2$ V,  $V_{CM_{Aux}} = 1.2$ V, Single-ended input drive,  $V_{CC} = 5$ V,  $V_{DD} = 3.3$ V,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7$   $V_{PP}$  differential (both Main & Auxiliary Outputs), both Main and Auxiliary Output Specifications, full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(2)</sup>. Electrical Characteristics Definition of Terms and Specifications for abbreviations used in the datasheet. **Boldface** limits apply at the temperature extremes.

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

(2) "Full Power" setting is with Auxiliary output turned on.

MH6518

www.ti.com

## Electrical Characteristics <sup>(1)</sup> (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}$ C, Input CM = 2.5V,  $V_{CM} = 1.2$ V,  $V_{CM_{Aux}} = 1.2$ V, Single-ended input drive,  $V_{CC} = 5$ V,  $V_{DD} = 3.3$ V,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7$   $V_{PP}$  differential (both Main & Auxiliary Outputs), both Main and Auxiliary Output Specifications, full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(2)</sup>. Electrical Characteristics Definition of Terms and Specifications for abbreviations used in the datasheet. **Boldface** limits apply at the temperature extremes.

| Symbol                  | Parameter                                                            | Condition                                                   | Min <sup>(3)</sup> | Тур <sup>(4)</sup> | Max <sup>(3)</sup> | Units           |

|-------------------------|----------------------------------------------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|-----------------|

| Dynamic Perfo           | rmance                                                               |                                                             |                    |                    |                    |                 |

| LSBW                    | -3 dB Bandwidth                                                      | All Gains                                                   |                    | 900                |                    | MHz             |

| Peaking                 | Peaking                                                              | All Gains                                                   |                    | 1                  |                    | dB              |

| GF_0.1 dB               | ±0.1 dB Gain Flatness                                                | All Gains                                                   |                    | 150                |                    | MHz             |

| GF_1 dB                 | ±1 dB Gain Flatness                                                  | All Gains                                                   |                    | 400                |                    | MHz             |

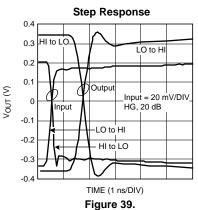

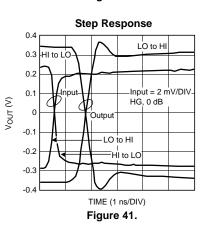

| TRS                     | Rise Time                                                            |                                                             |                    | 460                |                    | 20              |

| TRL                     | Fall Time                                                            |                                                             |                    | 450                |                    | ps              |

| OS                      | Overshoot                                                            | Main Output                                                 |                    | 9                  |                    | %               |

| t <sub>s_1</sub>        | Settling Time                                                        | Main Output, ±0.5%                                          |                    | 10                 |                    | ns              |

| t <sub>s_2</sub>        |                                                                      | Main Output, ±0.05%                                         |                    | 14                 |                    | 115             |

| t_recover               | Recovery Time <sup>(5)</sup>                                         | All Gains                                                   |                    | <5                 |                    | ns              |

| PD                      | Propagation Delay                                                    | $V_{OUT}$ = 0.7 $V_{PP}$ , All Gains                        |                    | 1.2                |                    | ns              |

| P <sub>D_VAR</sub>      | Propagation Delay Variation                                          | Gain Varied                                                 |                    | 100                |                    | ps              |

| Noise, Distortie        | on, and RF Specifications                                            |                                                             |                    |                    |                    |                 |

| e <sub>n_1</sub>        | Input Noise Spectral Density                                         | Max Gain, 10 MHz                                            |                    | 0.98               |                    | nV/√Hz          |

| e <sub>n_2</sub>        |                                                                      | Preamp LG and 0 dB Ladder, 10 MHz                           |                    | 4.1                |                    |                 |

| e <sub>no_1</sub>       | RMS Output Noise                                                     | Max Gain, 100 Hz to 400 MHz                                 |                    | 1.7                |                    | mV              |

| e <sub>no_2</sub>       | _                                                                    | Preamp LG, 0 dB Ladder, 100 Hz to 400 MHz                   |                    | 940                |                    | μV              |

| NF_1                    | Noise Figure                                                         | Max Gain, $R_S = 50\Omega$ each Input, 10 MHz               |                    | 3.8                |                    | -ID             |

| NF_2                    |                                                                      | Preamp LG, 0 dB Ladder, $R_S = 50\Omega$ each Input, 10 MHz |                    | 13.5               |                    | dB              |

| HD2/ HD3_1              | 2 <sup>nd</sup> / 3 <sup>rd</sup> Harmonic Distortion <sup>(6)</sup> | Main Output, 100 MHz, All Gains                             |                    | -50/ -53           |                    |                 |

| HD2/ HD3_2              |                                                                      | Auxiliary Output, 100 MHz, All Gains                        |                    | -48/ -50           |                    | dDa             |

| HD2/ HD3_3              |                                                                      | Main Output, 250 MHz, All Gains                             |                    | -44/ -50           |                    | dBc             |

| HD2/ HD3_4              |                                                                      | Auxiliary Output, 250 MHz, All Gains                        |                    | -42/ -42           |                    |                 |

| IMD3                    | Intermodulation Distortion (6)                                       | f = 250 MHz, Main output                                    |                    | -65                |                    | dBc             |

| OIP3_1                  | Intermodulation Intercept (6)                                        | Main Output, 250 MHz                                        |                    | 26                 |                    | dBm             |

| P_1dB_main              | -1 dB Compression                                                    | Main Output, 250 MHz, 0 dB Ladder                           |                    | 1.8                |                    |                 |

|                         |                                                                      | Main Output, 250 MHz, 20 dB Ladder                          |                    | 1.0                |                    |                 |

| P_1dB_aux               |                                                                      | Auxiliary Output, 250 MHz, 0 dB Ladder                      |                    | 1.65               |                    | V <sub>PP</sub> |

|                         |                                                                      | Auxiliary Output, 250 MHz, 20 dB Ladder                     |                    | 1.0                |                    |                 |

| Gain Paramete           | rs                                                                   |                                                             |                    |                    |                    |                 |

| A <sub>V_DIFF_MAX</sub> | Max Gain                                                             |                                                             | 38.1               | 38.8               | 39.5               | dB              |

| $A_{V\_DIFF\_MIN}$      | Min Gain                                                             |                                                             | -1.91              | -1.16              | -0.40              | dB              |

(3) Limits are 100% production tested at 25°C unless otherwise specified. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods.

(4) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

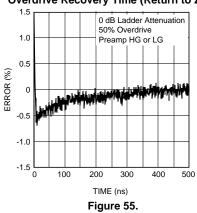

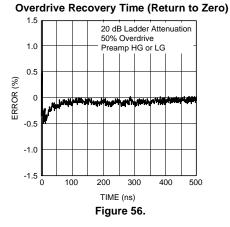

(5) Recovery time" is the slower of the Main and Auxiliary outputs. Output swing of 700 mV<sub>PP</sub> shifted up or down by 50% (0.35V) by introducing an offset. Measured values correspond to the time it takes to return to within ±1% of 0.7 V<sub>PP</sub> (±7 mV).

(6) Distortion data taken under single ended input condition.

#### SNOSB21C-MAY 2008-REVISED JULY 2013

# Electrical Characteristics <sup>(1)</sup> (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}$ C, Input CM = 2.5V,  $V_{CM} = 1.2$ V,  $V_{CM\_Aux} = 1.2$ V, Single-ended input drive,  $V_{CC} = 5$ V,  $V_{DD} = 3.3$ V,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7$   $V_{PP}$  differential (both Main & Auxiliary Outputs), both Main and Auxiliary Output Specifications, full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(2)</sup>. Electrical Characteristics Definition of Terms and Specifications for abbreviations used in the datasheet. **Boldface** limits apply at the temperature extremes.

| Symbol                                | Parameter                                              | Condition                                              | Min <sup>(3)</sup> | Тур <sup>(4)</sup> | Max <sup>(3)</sup> | Units            |  |

|---------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------|--------------------|--------------------|------------------|--|

| Gain_Step                             | Gain Step Size                                         | All Gains including Preamp Step                        | 1.8                | 2                  | 2.2                | dB               |  |

|                                       | Gain Step Size with ADC (See Applications Information) | ADC FS Adjusted                                        |                    | 8.5                |                    | mdB              |  |

| Gain_Range                            | Gain Range                                             |                                                        | 39                 | 40                 | 41                 | dB               |  |

| $TC_A_{V_DIFF}$                       | Gain Temp Coefficient (7)                              | All Gains                                              |                    | -0.8               |                    | mdB/°C           |  |

| Gain_A <sub>CC</sub>                  | Absolute Gain Accuracy                                 | Compared to theoretical from<br>Max Gain in 2 dB steps | 0.75               | _                  | +0.75              | dB               |  |

| Matching                              |                                                        |                                                        |                    |                    |                    |                  |  |

| Gain_match                            | Gain Matching Main/Auxiliary                           | All Gains                                              |                    | ±0.1               | ±0.2               | dB               |  |

| BW_match                              | -3 dB Bandwidth Matching<br>Main/Auxiliary             | All Gains                                              |                    | 5                  |                    | %                |  |

| RT_match                              | Rise Time Matching Main/ Auxiliary                     | All Gains                                              |                    | 5                  |                    | %                |  |

| PD_match                              | Propagation Delay Matching<br>Main/Auxiliary           | All Gains                                              |                    | 100                |                    | ps               |  |

| Analog I/O                            |                                                        | 1                                                      |                    |                    |                    |                  |  |

| CMRR_1                                | CM Rejection Ratio (see Table 1)                       | Preamp HG, 0 dB Ladder, 1.9V <<br>CMVR < 3.1V          | 45                 | 86                 |                    | dB               |  |

| CMRR_2                                |                                                        | Preamp LG, 0 dB Ladder, 1.9V <<br>CMVR < 3.1V          | 40                 | 55                 |                    | uв               |  |

| CMVR_1                                | Input Common Mode Voltage Range                        | Preamp HG, All Ladder Steps, CMRR<br>≥ 45 dB           | 1.9                | —                  | 3.1                | v                |  |

| CMVR_2                                | _                                                      | Preamp LG, All Ladder Steps, CMRR<br>≥ 40 dB           | 1.9                | _                  | 3.1                | v                |  |

| $ \Delta V_{O_{CM}} \Delta_{I_{CM}} $ |                                                        | All Gains, 2V < CMVR < 3V                              | -60                | -100               |                    | dB               |  |

| CMRR_CM                               | CM Rejection Ratio relative to VCM (see Table 1)       | Preamp LG, 0 dB                                        |                    | 101                |                    | dB               |  |

| Z <sub>in_diff</sub>                  | Differential Input Impedance                           | All Gains                                              |                    | 150  1.5           |                    |                  |  |

| Z <sub>in_CM</sub>                    | CM Input impedance                                     | Preamp HG                                              |                    | 420  1.7           |                    | KΩ   <br>pF      |  |

|                                       |                                                        | Preamp LG                                              |                    | 900  1.7           |                    | P.               |  |

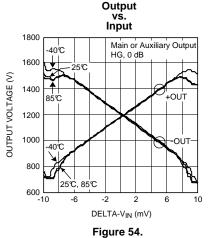

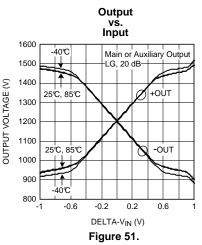

| FS <sub>OUT1</sub>                    | Full Scale Voltage Swing                               | Main Output, THD @ 100 MHz ≤<br>−40 dBc, All Gains     | 770 <sup>(8)</sup> | 800                |                    |                  |  |

| FS <sub>OUT2</sub>                    |                                                        | Main Output, Clamped, 0 dB Ladder                      |                    | 1800               | 1960               |                  |  |

| FS <sub>OUT3</sub>                    |                                                        | Auxiliary Output, THD @ 100 MHz ≤<br>−40 dBc All Gains | 770 <sup>(8)</sup> | 800                |                    | mV <sub>PP</sub> |  |

| FS <sub>OUT4</sub>                    |                                                        | Auxiliary Output, Clamped,0 dB Ladder                  |                    | 1600               | 1760               |                  |  |

| V <sub>OUT_MAX1</sub>                 | Voltage range at each output pin                       | Main Output, All gains, $V_{CM} = 1.2V$                | 0.5                |                    | 1.8                |                  |  |

| V <sub>OUT_MAX2</sub>                 | (clamped)                                              | Auxiliary Output, All Gains, $V_{CM} = 1.2V$           | 0.8                |                    | 2.2                |                  |  |

| V <sub>OUT_MAX3</sub>                 |                                                        | Main Output, All Gains, $V_{CM} = 1.45V$               |                    |                    | 2.05               | V                |  |

| V <sub>OUT_MAX4</sub>                 |                                                        | Auxiliary output, All gains,<br>$V_{CM} = 1.45V$       |                    |                    | 2.45               |                  |  |

| Z <sub>OUT_DIFF</sub>                 | Differential Output Impedance                          | All Gains                                              | 92                 | 100                | 108                | Ω                |  |

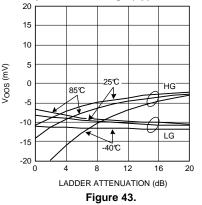

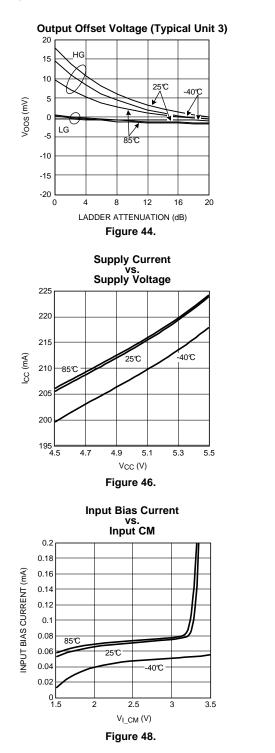

| V <sub>oos</sub>                      | Output Offset Voltage                                  | All Gains                                              |                    | ±15                | ±40                | mV               |  |

| V <sub>OOS_shift1</sub>               | Output Offset Voltage Shift                            | Preamp LG to Preamp HG                                 |                    | 13.7               |                    | m\/              |  |

| V <sub>OOS_shift2</sub>               |                                                        | All Gains, Excluding Preamp Step                       |                    | 12.7               |                    | mV               |  |

(7) Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.(8) Specified by design.

SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

# **Electrical Characteristics** <sup>(1)</sup> (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}$ C, Input CM = 2.5V,  $V_{CM} = 1.2$ V,  $V_{CM\_Aux} = 1.2$ V, Single-ended input drive,  $V_{CC} = 5$ V,  $V_{DD} = 3.3$ V,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7$   $V_{PP}$  differential (both Main & Auxiliary Outputs), both Main and Auxiliary Output Specifications, full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(2)</sup>. Electrical Characteristics Definition of Terms and Specifications for abbreviations used in the datasheet. **Boldface** limits apply at the temperature extremes.

| Symbol                | Parameter                                              | Condition                                     | Min <sup>(3)</sup> | Тур <sup>(4)</sup> | Max <sup>(3)</sup>  | Units |

|-----------------------|--------------------------------------------------------|-----------------------------------------------|--------------------|--------------------|---------------------|-------|

| TCV <sub>OOS</sub>    | Output Offset Voltage Drift <sup>(9)</sup>             | Preamp HG, 0 dB Ladder                        |                    | -24                |                     | µV/°C |

|                       |                                                        | Preamp LG, 0 dB Ladder                        |                    | -7                 |                     |       |

| I <sub>B</sub>        | Input Bias Current <sup>(10)</sup>                     |                                               |                    | +40                | +100<br><b>+140</b> | μA    |

| V <sub>OCM</sub>      | Output CM Voltage Range                                | All Gains                                     | 0.95               | 1.20               | 1.45                | V     |

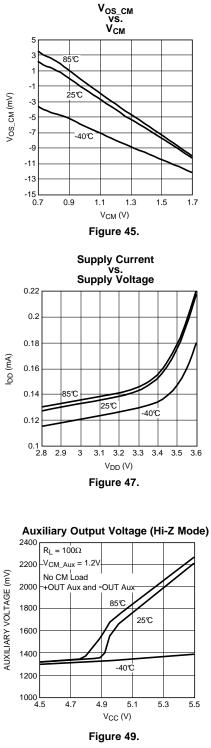

| V <sub>OS_CM</sub>    | Output CM Offset Voltage                               | All Gains                                     |                    | ±15                | ±30                 | mV    |

| TC_V <sub>OS_CM</sub> | CM Offset Voltage Temp Coefficient                     | All Gains                                     |                    | +55                |                     | µV/°C |

| BAL_Error_DC          | Output Gain Balance Error                              | DC, $\frac{\Delta V_{O\_CM}}{\Delta V_{OUT}}$ |                    | -78                |                     | dB    |

| BAL_Error_AC          |                                                        | 250 MHz, <u>Vo_cm</u><br>Vout                 |                    | -45                |                     | ub    |

| PB                    | Phase Balance Error (See Table 1)                      | 250 MHz                                       |                    | ±0.8               |                     | deg   |

| PSRR                  | Differential Power Supply Rejection(see                | Preamp HG, 0 dB Ladder                        | -60                | -87                |                     | JD    |

|                       | Table 1)                                               | Preamp LG, 0 dB Ladder                        | -50                | -70                |                     | dB    |

| PSRR_CM               | CM Power Supply Rejection(see Table 1)                 | Preamp LG, 0 dB                               | -55                | -71                |                     | dB    |

| V <sub>CM_I</sub>     | V <sub>CM</sub> Input Bias Current <sup>(11)</sup>     | All Gains                                     |                    | ±1                 | ±10<br><b>±20</b>   |       |

| V <sub>CM_AUX_I</sub> | V <sub>CM_AUX</sub> Input Bias Current <sup>(11)</sup> | All Gains                                     |                    | ±1                 | ±10<br><b>±20</b>   | nA    |

(9) Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

(10) Positive current is current flowing into the device.

(11) Positive current is current flowing into the device.

#### SNOSB21C-MAY 2008-REVISED JULY 2013

# Electrical Characteristics <sup>(1)</sup> (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}$ C, Input CM = 2.5V,  $V_{CM} = 1.2$ V,  $V_{CM\_Aux} = 1.2$ V, Single-ended input drive,  $V_{CC} = 5$ V,  $V_{DD} = 3.3$ V,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7$   $V_{PP}$  differential (both Main & Auxiliary Outputs), both Main and Auxiliary Output Specifications, full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(2)</sup>. Electrical Characteristics Definition of Terms and Specifications for abbreviations used in the datasheet. **Boldface** limits apply at the temperature extremes.

| Symbol               | Parameter                                    | Condition                                                   | Min <sup>(3)</sup>   | Typ <sup>(4)</sup> | Max <sup>(3)</sup> | Units                |  |

|----------------------|----------------------------------------------|-------------------------------------------------------------|----------------------|--------------------|--------------------|----------------------|--|

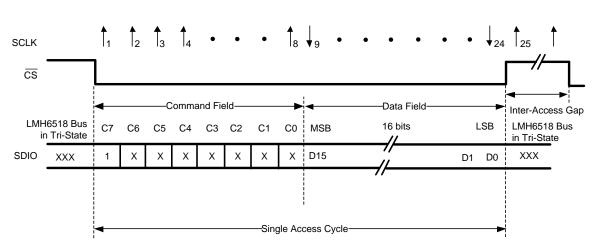

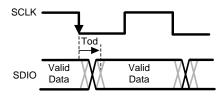

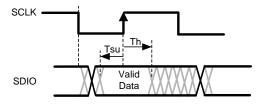

| Digital I/O & Ti     | iming                                        |                                                             |                      |                    |                    |                      |  |

| V <sub>IH</sub>      | Input Logic High                             |                                                             | V <sub>DD</sub> -0.6 |                    |                    | V                    |  |

| V <sub>IL</sub>      | Input Logic Low                              |                                                             |                      |                    | 0.5                | V                    |  |

| V <sub>OH</sub>      | Output Logic High                            |                                                             |                      | $V_{DD}$           |                    | V                    |  |

| V <sub>OL</sub>      | Output Logic Low                             |                                                             |                      | 0                  |                    | V                    |  |

| R <sub>Hi_Z</sub>    | Output Resistance                            | High Impedance Mode                                         |                      | 5                  |                    | MΩ                   |  |

| I_in                 | Input Bias Current                           |                                                             |                      | <1                 |                    | μA                   |  |

| F <sub>SCLK</sub>    | SCLK Rate                                    |                                                             |                      |                    | 10                 | MHz                  |  |

| F <sub>SCLK_DT</sub> | SCLK Duty Cyle                               |                                                             | 45                   | 50                 | 55                 | %                    |  |

| T <sub>S</sub>       | SDIO Setup Time                              |                                                             | 25                   |                    |                    | ns                   |  |

| Т <sub>Н</sub>       | SDIO Hold Time                               |                                                             | 25                   |                    |                    | ns                   |  |

| T <sub>CES</sub>     | CS Enable Setup Time                         | From $\overline{\text{CS}}$ asserted to rising edge of SCLK | 25                   |                    |                    | ns                   |  |

| t <sub>CDS</sub>     | CS Disable Setup Time                        | From CS de-asserted to rising edge of SCLK                  | 25                   |                    |                    | ns                   |  |

| T <sub>IAG</sub>     | Inter-Acess Gap                              |                                                             | 3                    |                    |                    | Cycles<br>of<br>SCLK |  |

| Power Require        | ements                                       |                                                             |                      |                    |                    |                      |  |

| I <sub>S1</sub>      | Supply Current                               | V <sub>CC</sub>                                             | 195                  | 210                | 225<br><b>230</b>  |                      |  |

| I <sub>S1_off</sub>  |                                              | V <sub>CC</sub> Aux off                                     |                      | 150                | 165<br><b>170</b>  | mA                   |  |

| I <sub>DD</sub>      |                                              | V <sub>DD</sub>                                             |                      | 180                | 350<br><b>400</b>  | μA                   |  |

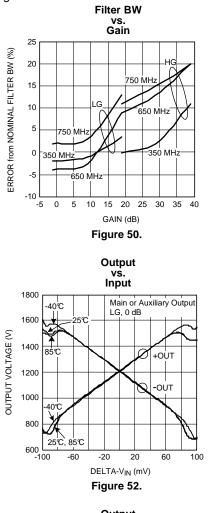

| Bandwidth Lin        | niting Filter Specifications                 |                                                             |                      |                    |                    |                      |  |

| Filter               | Parameter                                    | Condition                                                   | Min                  | Тур                | Max                | Units                |  |

| 20 MHz               | Pass Band Tolerance (All Gains)              | -3 dB Bandwidth                                             |                      | -0, +20            |                    | %                    |  |

| 100 MHz              | Pass Band Tolerance (All Gains)              | −3 dB Bandwidth                                             |                      | -0, +20            |                    | %                    |  |

| 200 MHz              | Pass Band Tolerance (All Gains)              | -3 dB Bandwidth                                             |                      | -0, +20            |                    | %                    |  |

| 350 MHz              | Pass Band Tolerance (Preamp LG, 0 dB Ladder) | −3 dB Bandwidth                                             |                      | ±10                |                    | %                    |  |

|                      | Pass Band Tolerance (All Gains)              |                                                             |                      | ±25                |                    |                      |  |

| 650 MHz              | Pass Band Tolerance (Preamp LG, 0 dB Ladder) | -3 dB Bandwidth                                             |                      | ±10                |                    | %                    |  |

|                      | Pass Band Tolerance (All Gains)              | 1                                                           |                      | ±25                |                    |                      |  |

| 750 MHz              | Pass Band Tolerance (Preamp LG, 0 dB Ladder) | −3 dB Bandwidth                                             |                      | ±10                |                    | %                    |  |

|                      | Pass Band Tolerance (All Gains)              | 1                                                           |                      | ±25                |                    |                      |  |

# LMH6518

SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

# Table 1. Definition of Terms and Specifications

| 1.  | A <sub>V_CM</sub> (dB)                    | Change in output offset voltage ( $\Delta V_{OOS}$ ) with respect to the change in input common mode                                                                                                                                                                                                                                                                                                   |

|-----|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   |                                           | voltage ( $\Delta V_{I_{CM}}$ )<br>Gain with 100 $\Omega$ differential load                                                                                                                                                                                                                                                                                                                            |

| 2.  | A <sub>V_DIFF</sub> (dB)                  |                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.  | CM                                        | Common Mode                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.  | CMRR (dB)                                 | Common Mode rejection defined as: $A_{V\_DIFF}$ (dB) - $A_{V\_CM}$ (dB)                                                                                                                                                                                                                                                                                                                                |

| 5.  | CMRR_CM                                   | Common Mode rejection relative to $V_{CM}$ defined as: $\Delta V_{OOS}/\!\Delta V_{CM}$                                                                                                                                                                                                                                                                                                                |

| 6.  | HG                                        | Preamp High Gain                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.  | Ladder                                    | Ladder Attenuator setting (0-20 dB)                                                                                                                                                                                                                                                                                                                                                                    |

| 8.  | LG                                        | Preamp Low Gain                                                                                                                                                                                                                                                                                                                                                                                        |

| 9.  | Max Gain                                  | Gain = 38.8 dB                                                                                                                                                                                                                                                                                                                                                                                         |

| 10. | Min Gain                                  | Gain = −1.16 dB                                                                                                                                                                                                                                                                                                                                                                                        |

| 11. | +Out                                      | Positive Main Output                                                                                                                                                                                                                                                                                                                                                                                   |

| 12. | -Out                                      | Negative Main Output                                                                                                                                                                                                                                                                                                                                                                                   |

| 13. | +Out Aux                                  | Positive Auxiliary Output                                                                                                                                                                                                                                                                                                                                                                              |

| 14. | -Out Aux                                  | Negative Auxiliary Output                                                                                                                                                                                                                                                                                                                                                                              |

| 15. | PB                                        | Phase Balance defined as the phase difference between the complimentary outputs relative to 180°                                                                                                                                                                                                                                                                                                       |

| 16. | PSRR                                      | Input referred V <sub>OOS</sub> shift divided by change in V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                             |

| 17. | PSRR_CM                                   | Output common mode voltage change ( $\Delta V_{O_CM}$ ) with respect to $V_{CC}$ voltage change ( $\Delta V_{CC}$ )                                                                                                                                                                                                                                                                                    |

| 18. | V <sub>CM</sub>                           | Input pin voltage that sets Main output CM                                                                                                                                                                                                                                                                                                                                                             |

| 19. | V <sub>CM_Aux</sub>                       | Input pin voltage that sets Auxiliary output CM                                                                                                                                                                                                                                                                                                                                                        |

| 20. | V <sub>I_CM</sub>                         | Input CM voltage (average of +IN and -IN)                                                                                                                                                                                                                                                                                                                                                              |

| 21. | $\Delta V_{IN}$ (V)                       | Differential voltage across device inputs                                                                                                                                                                                                                                                                                                                                                              |

| 22. | V <sub>OOS</sub>                          | DC offset voltage. Differential output voltage measured with inputs shorted together to $V_{CC}/2$                                                                                                                                                                                                                                                                                                     |

| 23. | V <sub>O_CM</sub>                         | Output common mode voltage (DC average of V <sub>+OUT</sub> and V <sub>-OUT</sub> )                                                                                                                                                                                                                                                                                                                    |

| 24. | V <sub>OS_CM</sub>                        | CM offset voltage: V <sub>O CM</sub> - V <sub>CM</sub>                                                                                                                                                                                                                                                                                                                                                 |

| 25. | $\Delta V_{O_{CM}}$                       | Variation in output common mode voltage (V <sub>O CM</sub> )                                                                                                                                                                                                                                                                                                                                           |

| 26. | $\frac{\Delta V_{O\_CM}}{\Delta V_{OUT}}$ | Balance Error. Measure of the output swing balance of "+OUT" and "-OUT", as reflected on the output common mode voltage ( $V_{O_{\rm C}CM}$ ), relative to the differential output swing ( $V_{OUT}$ ). Calculated as output common mode voltage change ( $\Delta V_{O_{\rm C}CM}$ ) divided by the output differential voltage change ( $\Delta V_{OUT}$ , which is nominally around 700 m $V_{PP}$ ) |

| 27. | ΔV <sub>OUT</sub>                         | Change in differential output voltage (Corrected for DC offset (V <sub>OOS</sub> ))                                                                                                                                                                                                                                                                                                                    |

|     |                                           |                                                                                                                                                                                                                                                                                                                                                                                                        |

SNOSB21C-MAY 2008-REVISED JULY 2013

www.ti.com

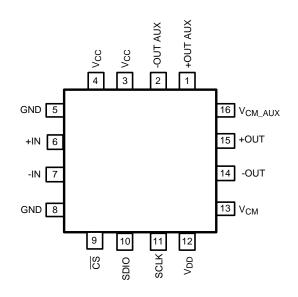

|                       | PIN OUT                                              |  |  |

|-----------------------|------------------------------------------------------|--|--|

| Pin Out Function      |                                                      |  |  |

| P1 = +OUT Aux         | Auxiliary positive output                            |  |  |

| P2 = -OUT Aux         | Auxiliary negative output                            |  |  |

| $P3 = V_{CC} (5V)$    | Analog power supply                                  |  |  |

| $P4 = V_{CC} (5V)$    | Analog power supply                                  |  |  |

| P5 = GND              | Ground, electrically connected to the WQFN heat sink |  |  |

| P6 = +IN              | Positive Input                                       |  |  |

| P7 = −IN              | Negative Input                                       |  |  |

| P8 = GND              | Ground, electrically connected to the WQFN heat sink |  |  |

| $P9 = \overline{CS}$  | SPI interface, Chip Select, Active low               |  |  |

| P10 = SDIO            | SPI interface, Serial Data Input/Output              |  |  |

| P11 = SCLK            | SPI interface, Clock                                 |  |  |

| $P12 = V_{DD} (3.3V)$ | Digital power supply                                 |  |  |

| $P13 = V_{CM}$        | Input from ADC to control main output CM             |  |  |

| P14 = −OUT            | Main negative output                                 |  |  |

| P15 = +OUT            | Main positive output                                 |  |  |

| $P16 = V_{CM_Aux}$    | Input to control auxiliary output CM                 |  |  |

# **Connection Diagram**

Figure 1. 16-Pin-Top View See Package Number RGH0016A

TEXAS INSTRUMENTS

www.ti.com

SNOSB21C - MAY 2008 - REVISED JULY 2013

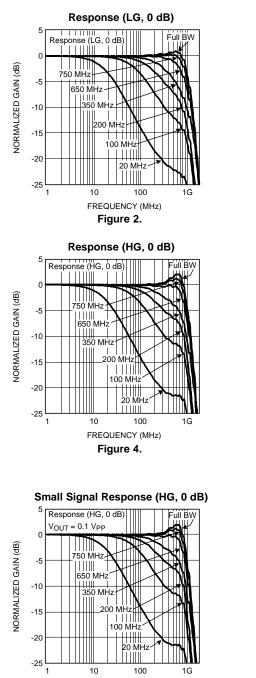

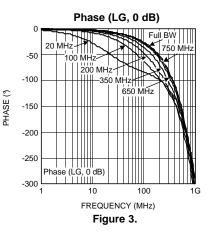

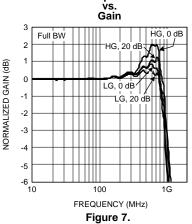

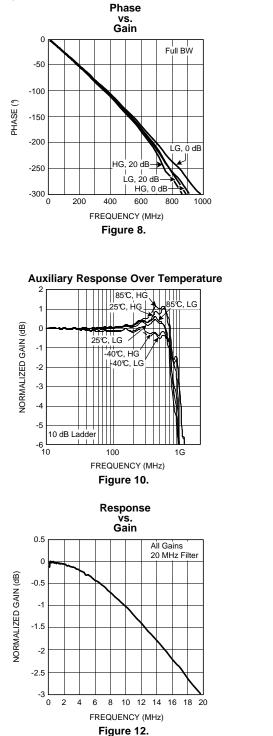

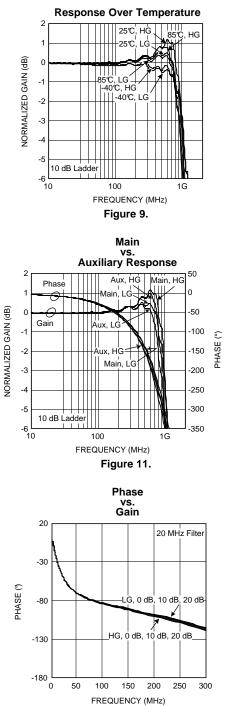

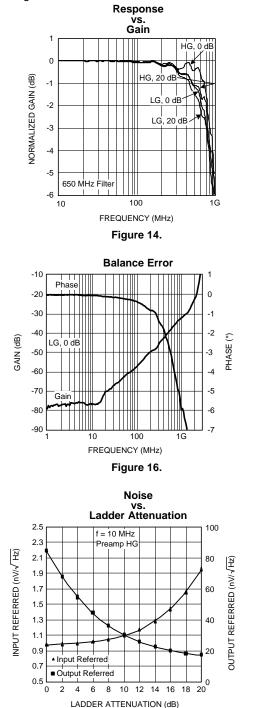

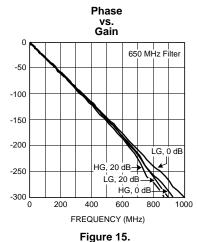

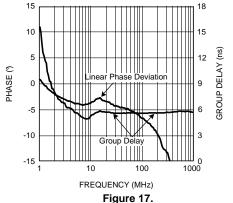

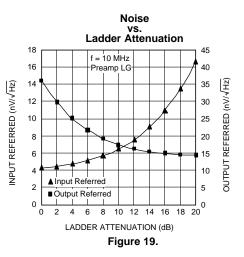

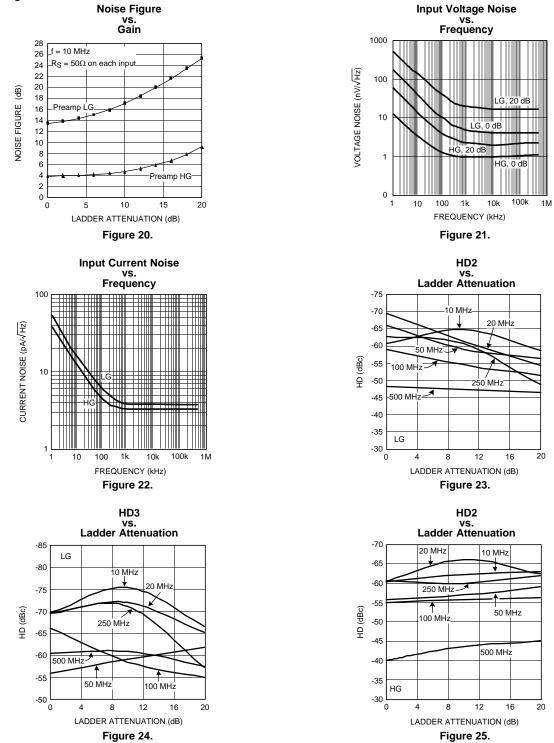

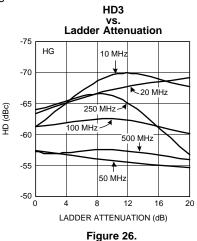

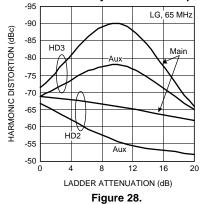

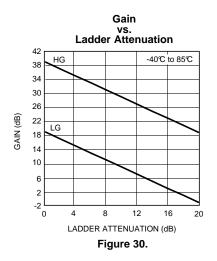

### **Typical Performance Characteristics**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

Small Signal Response (LG, 0 dB)

(1) "Full Power" setting is with Auxiliary output turned on.

FREQUENCY (MHz)

Figure 6.

LMH6518

SNOSB21C - MAY 2008 - REVISED JULY 2013

## **Typical Performance Characteristics (continued)**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

EXAS

ISTRUMENTS

www.ti.com

SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

## **Typical Performance Characteristics (continued)**

PHASE ()

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_{L} = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

Linear Phase Deviation and Group Delay

LMH6518

SNOSB21C - MAY 2008 - REVISED JULY 2013

## **Typical Performance Characteristics (continued)**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

www.ti.com

SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

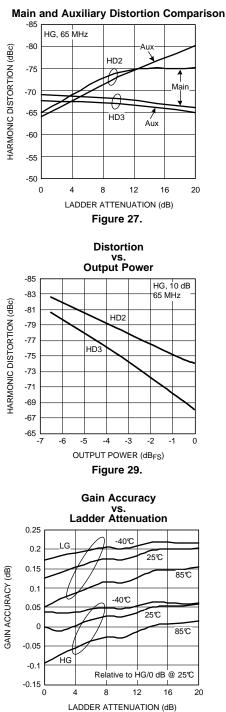

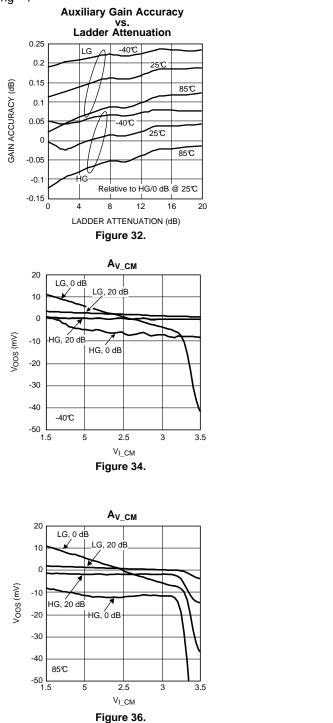

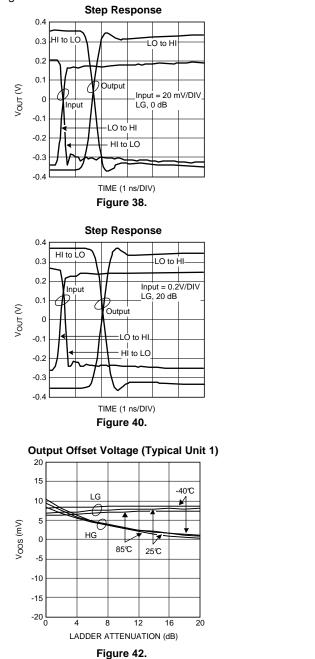

### **Typical Performance Characteristics (continued)**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_{L} = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

Main and Auxiliary Distortion Comparison

LMH6518

SNOSB21C - MAY 2008 - REVISED JULY 2013

# **Typical Performance Characteristics (continued)**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

www.ti.com

SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

## **Typical Performance Characteristics (continued)**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

#### Output Offset Voltage (Typical Unit 2)

LMH6518

SNOSB21C - MAY 2008 - REVISED JULY 2013

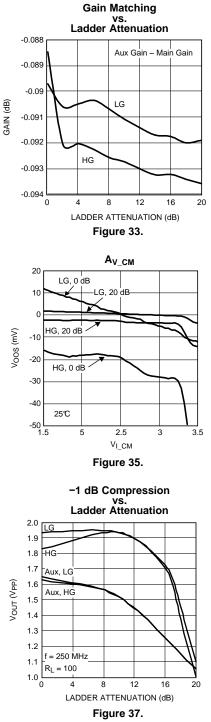

# **Typical Performance Characteristics (continued)**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

www.ti.com

STRUMENTS

EXAS

SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

### **Typical Performance Characteristics (continued)**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

**Overdrive Recovery Time (Return to Zero)**

LMH6518

# **Typical Performance Characteristics (continued)**

Unless otherwise specified, Input CM = 2.5V,  $V_{CM} = 1.2V$ ,  $V_{CM AUX} = 1.2V$ , Single-ended input drive,  $V_{CC} = 5V$ ,  $V_{DD} = 3.3V$ ,  $R_L = 100\Omega$  differential (both Main & Auxiliary Outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both Main and Auxiliary Outputs), Main output specification (Auxiliary is labeled "Auxiliary"), full bandwidth setting, gain = 18.8 dB (Preamp LG, 0 dB ladder attenuation), Full Power setting <sup>(1)</sup>.

XAS

STRUMENTS

www.ti.com

SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

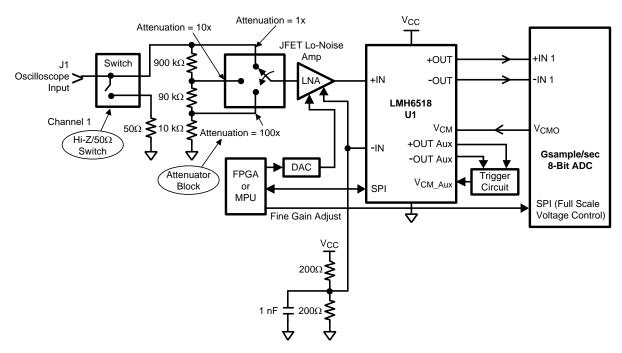

### **APPLICATIONS INFORMATION**

### FUNCTIONAL DESCRIPTION AND DYNAMIC RANGE IN OSCILLOSCOPE APPLICATIONS

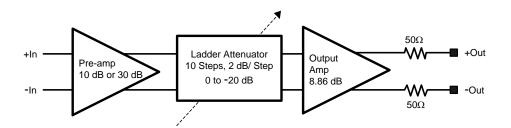

Here is a block diagram of the LMH6518's Main Output signal path:

Figure 57. LMH6518 Signal Path Block Diagram

The Auxiliary output (not shown) uses another but similar Output Amp that taps into the Ladder Attenuator output. In this document, Preamp gain of 30 dB is referred to as "Preamp HG" (High Gain) and Preamp gain of 10 dB as "Preamp LG" (Low Gain).

The LMH6518's 2 dB/step gain resolution and 40 dB adjustment range (from -1.16 dB to 38.8 dB) allows this device to be used with the TI GSample/second ADCs which have Full Scale, FS, adjustment (through their Extended Control Mode or ECM) to provide near-continuous variability (8.5 mdB resolution) to cover a 42.6 dB

$$(20 \text{ x } \log \frac{920 \text{ mV}_{\text{PP}}}{6.8 \text{ mV}_{\text{PP}}} = 42.6 \text{ dB})$$

(1)

FS input range. The Texas Instruments GSample/second ECM control allows the ADC FS to be set using the ADC SPI bus. The ADC FS voltage range is from 560 mV to 840 mV with 9 bits of FS voltage control.

The ADC ECM gain resolution can be calculated as follows:

Gain Resolution = 20 log

$$\frac{0.56 + \left(\frac{0.84 - 0.56}{2 \times 512}\right)}{0.56 - \left(\frac{0.84 - 0.56}{2 \times 512}\right)} = 8.5 \text{ mdB}$$

(2)

The recommended ADC FS operating range is, however, narrower and it is from 595 mV to 805 mV with 700 mV<sub>PP</sub> as the mid-point. Raising the value of ADC FS voltage is tantamount to reducing the signal path gain to accommodate a larger input and vice versa, thus providing a method of gain fine-adjust. The ADC ECM gain adjustment is -1.21 dB

(= 20 x log

$$\frac{700 \text{ mV}}{805 \text{ mV}}$$

) to +1.41 dB

$$(= 20 \times \log \frac{700 \text{ mV}}{595 \text{ mV}})$$

(3)

Because the ADC FS fine-adjust range of 2.62 dB (= 1.41 dB + 1.21 dB) is larger than the LMH6518's 2 dB/step resolution, there is always at least one LMH6518 gain setting to accommodate any FS signal from 6.8 mV<sub>PP</sub> to 920 mV<sub>PP</sub>, at the LMH6518 input, with 0.62 dB (= 2.62-2) overlap.

Copyright © 2008–2013, Texas Instruments Incorporated

Minimum LMH6518 FS Input =

SNOSB21C-MAY 2008-REVISED JULY 2013

path gain possible and vice versa:

Input =

$$\frac{0.1 \text{ VPP}}{\frac{(38.8 + 1.41) \text{ dB}}{20}}$$

= 6.8 mV<sub>PP</sub>

(or 8 mV\_{PP} with no ADC fine adjust)

Maximum LMH6518 FS Input =

$$\frac{0.7 \text{ V}_{PP}}{\frac{(-1.16 - 1.21) \text{ dB}}{20}} = 920 \text{ mV}_{PP}$$

(5)

Assuming a nominal 0.7V<sub>PP</sub> output, the LMH6518's minimum FS input swing is limited by the maximum signal

(or 800 mV  $_{\rm PP}$  with no ADC FS adjust)

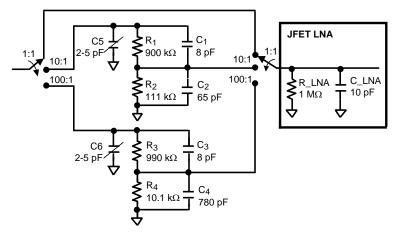

To accommodate a higher FS input, an additional attenuator is needed before the LMH6518. This front-end attenuator is shown in the Figure 62 with its details shown in Figure 71. The highest minimum attenuation level is determined by the largest FS input signal ( $FS_{max}$ ):

Attenuation (dB) = 20 x log

$$\frac{FS_{MAX} (V_{PP})}{800 \text{ mV}_{PP}}$$

So, to accommodate 80  $V_{PP}$ , 40 dB minimum attenuation is needed before the LMH6518.

$0.7 V_{PP}$

In a typical oscilloscope application, the voltage range encountered is from 1 mV/DIV to 10 V/DIV with 8 vertical divisions visible on the screen. One of the primary concerns in a digital oscilloscope is SNR which translates to display trace width/ thickness. Typically, oscilloscope manufacturers need the noise level to be low enough so that the "no-input" visible trace width is less than 1% of FS. Experience has shown that this corresponds to a minimum SNR of 52 dB.

The factors that influence SNR are:

- Scope front end noise (Front-end attenuator + scope probe Hi-Z buffer which is discussed later in this document and shown in Figure 62)

- LMH6518

- ADC

LMH6518 related SNR factors are:

- Bandwidth

- Preamp used (Preamp High Gain or Low Gain)

- Ladder Attenuation

- Signal level

SNR increases with the inverse square root of the bandwidth. So, reducing bandwidth from 450 MHz to 200 MHz, for example, improves SNR by 3.5 dB

$$(20 \text{ x} \log \frac{\sqrt{450 \text{ MHz}}}{\sqrt{200 \text{ MHz}}} = 3.5 \text{ dB})$$

(7)

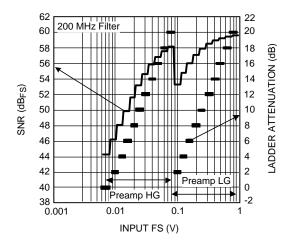

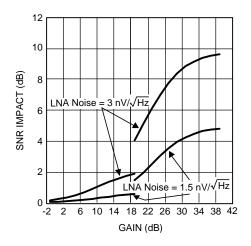

The other factors listed above, preamp and ladder attenuation, depend on the signal level and also impact SNR. The combined effect of these factors is summarized in Figure 58 where SNR is plotted as a function of the LMH6518 FS input voltage (assuming scope bandwidth of 200 MHz) and not including the ADC and the front end noise:

(4)

(6)

ISTRUMENTS

Figure 58. LMH6518 SNR & Ladder Attenuation used vs. Input

As can be seen from Figure 58, SNR of at least 52 dB is maintained for FS inputs above 24 mV<sub>PP</sub> (3 mV/DIV on a scope) assuming the LMH6518's internal 200 MHz filter is enabled. Most oscilloscope manufacturers relax the SNR specifications to 40 dB for the highest gain (lowest scope voltage setting). From Figure 58, LMH6518's minimum SNR is 43.5 dB, thereby meeting the relaxed SNR specification for the lower range of scope front panel voltages.

In Figure 58, the step-change in SNR near Input FS of 90 mV<sub>PP</sub> is the transition point from Preamp LG to Preamp HG with a subsequent 3 dB difference due to the Preamp HG/ 20 dB ladder attenuation's lower output noise compared to Preamp LG/ 2 dB ladder attenuation's noise. Judicious choice of front end attenuators can ensure that the 52 dB SNR specification is maintained for scope FS inputs  $\geq$  24 mV<sub>PP</sub> by confining the LMH6518 gain range to the lower 30.5 dB

$$(= 20 \text{ x} \log \frac{0.8 \text{ V}_{\text{PP}}}{24 \text{ mV}_{\text{PP}}})$$

from the total range of 40 dB (= 38.8 - (-1.16)) possible.

Here is an example:

To cover the range of 1 mV/DIV to 10 V/DIV (80 dB range), here is a configuration which affords good SNR:

| Row | Scope FS Input<br>(V <sub>PP</sub> ) | "S", Scope Vertical<br>Scale (V/DIV) | Preamp | Ladder Attenuation<br>Range (dB) | "A", Front-end<br>attenuation (V/V) | Minimum SNR (dB)<br>with 200 MHz filter |

|-----|--------------------------------------|--------------------------------------|--------|----------------------------------|-------------------------------------|-----------------------------------------|

| 1   | 8m-24m                               | 1m-3m                                | HG     | 0-10                             | 1                                   | 44                                      |

| 2   | 24m-80m                              | 3m-10m                               | HG     | 10-20                            | 1                                   | 52.0                                    |

| 3   | 80m-0.8                              | 10m-0.1                              | LG     | 0-20                             | 1                                   | 53.4                                    |

| 4   | 0.8-8                                | 0.1-1                                | LG     | 0-20                             | 10                                  | 53.4                                    |

| 5   | 8-80                                 | 1-10                                 | LG     | 0-20                             | 100                                 | 53.4                                    |

Table 2. Oscilloscope Example Including Front-End Attenuators

In Table 2, the highest FS input in Row 5, Column 2 (80  $V_{PP}$ ), and the LMH6518's highest FS input allowed (0.8  $V_{PP}$ ) set the

$$100x (= \frac{80 V_{PP}}{0.8 V_{PP}})$$

(9)

(8)

front-end attenuator value. The 100x attenuator will allow high SNR operation to 30.5 dB down, as explained earlier, or 2.4  $V_{PP}$  at scope input. In that same table, Rows 1-3 with no front-end attenuation (1x) cover the scope FS input range from 8 mV<sub>PP</sub>-800 mV<sub>PP</sub>. That leaves the scope FS input range of 0.8 V<sub>PP</sub>-2.4 V<sub>PP</sub>. If the 100x attenuator were used for the entire scope FS range of 0.8 V<sub>PP</sub>-80 V<sub>PP</sub>, SNR would dip below 52 dB for a portion of that range. Another attenuation level is thus required to maintain the SNR specification requirement of 52 dB.

SNOSB21C - MAY 2008 - REVISED JULY 2013

One possible attenuation partitioning is to select the additional attenuator value to cover a 20 dB range above 0.8  $V_{PP}$  FS (to 8  $V_{PP}$ ) with the 100x attenuator covering the remaining 20 dB range from 8  $V_{PP}$  to 80  $V_{PP}$ . Mapping 8  $V_{PP}$  FS scope input to 0.8  $V_{PP}$  at LMH6518 input means the additional attenuator is 10x, as shown in Table 2, Row 4. The remaining scope input range of 8  $V_{PP}$ -80  $V_{PP}$  would then be covered by the 100x front-end attenuator derived earlier. The entire scope input range is now covered with SNR maintained about 52 dB for scope FS input ≥ 24 m $V_{PP}$ , as shown in Table 2.

### SETTINGS AND ADC SPI CODE (ECM)

Covering the range from 1 mV/DIV to 10 V/DIV requires the following to be adjusted within the digital oscilloscope:

- Front-End Attenuator

- LMH6518 Preamp

Κ

- LMH6518 Ladder Attenuation

- ADC FS Value (ECM)

The LMH6518 Product Folder contains a spreadsheet which allows one to calculate the front-end attenuator, LMH6518 Preamp gain (HG or LG) and ladder attenuation, and ADC FS setting based on the scope vertical scale (S in V/DIV).

Here is the step by step procedure that explains the operations performed by the said spreadsheet based on the scope vertical scale setting (S in V/div) and front-end attenuation "A" (from Table 2). A numerical example is also worked out for more clarification:

1. Determine the required signal path gain, K:

$$= 20 \times \log \frac{\frac{0.95 \times 700 \text{ mV}_{PP}}{8 \times S(V/\text{div})}}{\frac{8 \times S(V/\text{div})}{A}} = -21.6 + 20 \times \log \frac{A}{S(V/\text{div})}$$

(10)

(11)

assuming the full scale signal occupies 95% of the 0.7  $V_{PP}$  FS (for 5% overhead) which occupies 8 vertical scope divisions).

Required condition:  $-2.37 \text{ dB} \le \text{K} \le 40.3 \text{ dB}$

Example: With S = 110 mV/DIV, Table 2 shows that A = 10 V/V:

$$\rightarrow$$

K = -21.6 + 20 x log  $\frac{10}{110 \text{ mV}}$  = 17.57 dB

- 2. Determine the LMH6518 gain, G:

- G is the closest LMH6518 gain, to the value of K where:

- G = (38.8 2n)dB; n = 0, 1, 2, ..., 20

- For this example, the closest G to K = 17.57 dB is 16.8 dB (with n = 11). The next LMH6518 gain, 18.8 dB (with n = 10) would be incorrect as 16.8 is closer. If 18.8 dB were mistakenly chosen, the ADC FS setting would be out of range.

- Therefore: G = 16.8 dB

- 3. Determine Preamp (HG or LG) & Ladder Attenuation:

- If G ≥ 18.8 dB  $\rightarrow$  Preamp is HG and Ladder Attenuation = 38.8 G

- If G < 18.8 dB  $\rightarrow$  Preamp is LG and Ladder Attenuation = 18.8 G

- For this example, with  $G = 16.8 \rightarrow Preamp \ LG$  and Ladder Attenuation = 2 dB (= 18.8-16.8).

- 4. Determine the required ADC FS voltage, FS<sub>E</sub>:

$$FS_{E} = \frac{S \times 8}{A} \times 1.05 \times 10^{\frac{3}{20}}$$

(12)

(13)

(14)

The "1.05" factor is to add 5% FS overhead margin to avoid ADC overdrive.

$$FS_{E} = \frac{S \times 8}{10} \times 1.05 \times 10^{\frac{16.8}{20}} = 639.3 \text{ mV}$$

Required condition:  $0.56V \le FS_E \le 0.84V$

Recommend condition:  $0.595V \le FS_E \le 0.805V$  for optimum ADC FS

5. Determine the ADC ECM code ratio:

$\text{ECM (ratio)} = \frac{\text{FS}_{\text{E}} - 0.56}{0.28}$

where

- 0.28V= (0.84-0.56)V

- 0.56V is the lower end of the ADC FS adjustability

- For this example:

ECM (ratio) =

$$\frac{0.6393 - 0.56}{0.28} = 0.283$$

- Required condition:  $0 \le ECM$  (ratio)  $\le 1$

- 6. Determine the ECM binary code to be sent on ADC SPI bus:

- Convert the ECM value represented by the ratio calculated above, to binary:

- ECM (binary) = DEC2BIN{ECM(ratio)\* 511, 9}

- Where "DEC2BIN" is a spreadsheet function which converts the decimal ECM ratio, from step 5 above, multiplied by 511 distinct levels, into binary 9 bits.

#### NOTE

The Web based spreadsheet computes ECM without the use of "DEC2BIN" function to ease usage by all spreadsheet users who may not have this function installed.

For this example: ECM (binary) = DEC2BIN(0.283\*511, 9) = 010010000. This would be the number to be sent to the ADC on the SPI bus to program the ADC to the proper FS voltage.

# INPUT/OUTPUT CONSIDERATIONS

The LMH6518's ideal Input/Output Conditions, considered individually, are listed below:

|                                               |                          |                                          | • •                                      |                            |                           |

|-----------------------------------------------|--------------------------|------------------------------------------|------------------------------------------|----------------------------|---------------------------|

| Impedance from<br>each input to<br>ground (Ω) | Common Mode<br>Input (V) | Differential Input<br>(V <sub>PP</sub> ) | Load Impedance (Ω)                       | Differential Output<br>(V) | Common Mode<br>Output (V) |

| ≤50                                           | 1.5 to 3.1               | <0.8                                     | 100 (differential)/ 50<br>(single ended) | <0.77                      | 0.95-1.45                 |

#### Table 3. LMH6518's Ideal Input/Output Conditions

In addition to the individual conditions listed in Table 3, the Input/Output terminal conditions should match differentially (i.e. +IN to -IN and +OUT to -OUT), as well, for best performance.

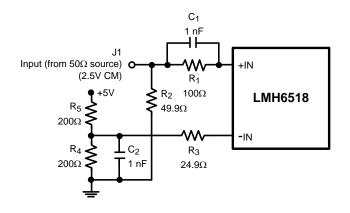

The input is differential but can be driven single-ended as long as the conditions of Table 3 are met and there is good matching between the driven and the undriven inputs from DC to the highest frequency of interest. If not, there could be a settling time impact among other possible performance degradations. The datasheet specifications are with single-ended input, unless specified. Here is the recommended bench-test schematic to drive one input and to bias the other input with good matching in mind:

SNOSB21C - MAY 2008 - REVISED JULY 2013

www.ti.com

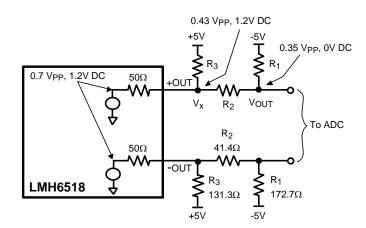

Figure 59. Recommended Single-Ended Bench-Test Input Drive from  $50\Omega$  Source

With the schematic of Figure 59, each LMH6518 input sees  $25\Omega$  to ground at the higher frequencies when the capacitors look like shorts. This impedance increases to  $125\Omega$  at DC for both inputs, thereby preserving the required matching at any frequency. This configuration, using properly selected R's and C's, allows four times less biasing power dissipation than when the undriven input is biased with an effective  $25\Omega$  from the LMH6518 input to ground.

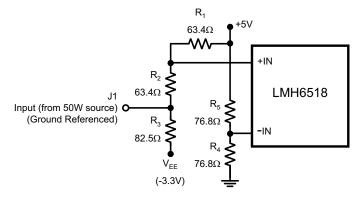

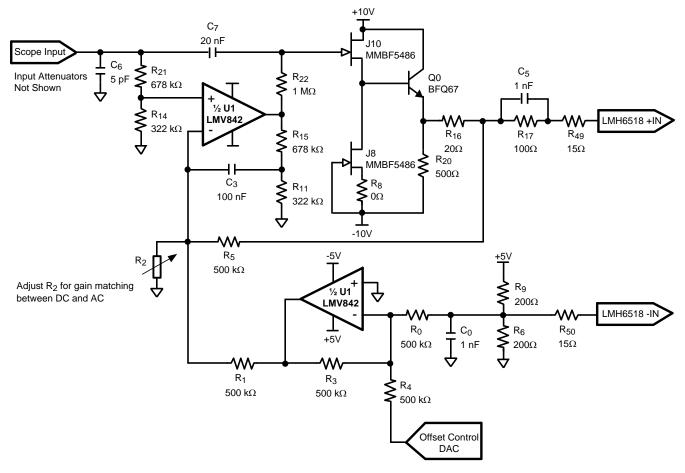

It is possible to drive the LMH6518 input from a ground referenced 50 $\Omega$  source by providing level shift circuitry on the driven input. Figure 60 shows a circuit where ½ the input signal reaches the LMH6518 input while the negative supply voltage (V<sub>EE</sub>) ensures that the 50 $\Omega$  source at J1 does not experience any biasing current while providing 50 $\Omega$  termination to the source. The driven input (+IN) is biased to 2.5V (V<sub>CC</sub>/2):

Figure 60. LMH6518 Driven by a Ground Referenced Source

In the schematic of Figure 60, the equivalent impedance from each LMH6518 input to ground is around  $38\Omega$ . This configuration's power consumption of ~0.5W (in R<sub>1</sub> - R<sub>5</sub>) is higher than that of Figure 59 because of additional power dissipated to perform the level shifting. Additional 50 $\Omega$  attenuators can be placed between J1 and R<sub>2</sub>/R<sub>3</sub> junction in Figure 60 in order to accommodate higher input voltages.

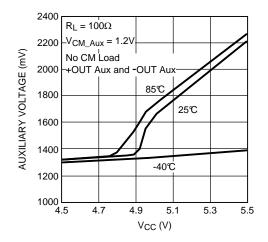

It is also possible to shift the LMH6518 *output* common mode level using a level shift approach similar to that of Figure 60. The circuit in Figure 61 shows an implementation where the LMH6518's nominal 1.2V CM output, set by a 1.2V on  $V_{CM}$  input from the Gsample/s ADC, is shifted lower for proper interface to different ADC's which require  $V_{CM} = 0V$  and have high input impedance:

SNOSB21C - MAY 2008 - REVISED JULY 2013

Figure 61. Output CM Shift Scheme

With the scheme of Figure 61, Vx is kept at 1.2V, by proper selection of external resistor values, so that the LMH6518 outputs are not CM-loaded. As was the case with input level shifting, this output level shifting also consumes additional power (0.58W).

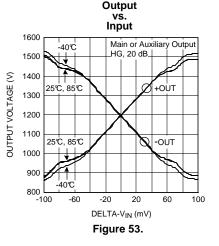

### Output Swing, Clamping, and Operation Beyond Full Scale

One of the major concerns in interfacing to low voltage ADC's (such as the Gsample/s ADC's that the LMH6518 is intended to drive) is ensuring that the ADC input is not violated with excessive drive. For this reason, plus the very important requirement of an oscilloscope to recover quickly and gracefully from an overdrive condition, the LMH6518 is fitted with three overvoltage clamps; one at the Preamp output and one at Main and Auxiliary outputs each. The Preamp clamp is responsible for preventing the Preamp from saturation (to minimize recovery time) with large ladder attenuation when Preamp output swing is at its highest. On the other hand, the output clamps, perform this function when the Ladder attenuation is lower and hence the output amplifier is closer to saturation, and prolonged recovery, if not properly clamped. The combination of these clamps results in Figure 51, Figure 52, Figure 53, and Figure 54 where it is possible to observe where output limiting starts due to the clamp action. LMH6518 owes its fast recovery time (< 5 ns) from 50% overdrive to the said clamps.