# LM96194 TruTherm™ Hardware Monitor with PI Fan Control for Workstation Management

Check for Samples: LM96194

## **FEATURES**

- ΣΔ ADC Architecture

- Monitors 9 Power Supplies

- Monitors 4 Remote Thermal Diodes and 2 LM60

- New TruTherm Technology Support for Precision Thermal Diode Measurements

- Internal Ambient Temperature Sensing

- Programmable Autonomous Fan Control Based on Temperature Readings with Fan Boost Support

- Fan Boost Support on Tachometer Limit Error Event

- Fan Control Based on 13-step Lookup Table or PI Control Loop or Combination of Both

- PI Fan Control Loop Supports Tcontrol

- Temperature Reading Digital Filters

- 0.5°C Digital Temperature Sensor Resolution

- 0.0625°C Filtered Temperature Resolution for Fan Control

- 2 PWM Fan Speed Control Outputs

- 4 Fan Tachometer Inputs

- Processor Thermal Throttling (PROCHOT)

Monitoring

- Dynamic VID Monitoring (6/7 VIDs per processor) Supports VRD10.2/11

- 8 General Purpose I/Os:

- 4 Can be Configured as Fan Tachometer Inputs

- 2 Can be Configured to Connect to Processor THERMTRIP

- 2 are Standard GPIOs that Could be Used to Monitor IERR Signal

- A General Purpose Inputs That can be Used to Monitor the 7th VID Signal for VRD11

- Limit Register Comparisons of all Monitored Values

- 2-wire Serial Digital Interface, SMBus 2.0 Compliant

- Supports Byte/block Read and Write

- Selectable Slave Address (Tri-level Pin Selects 1 of 3 Possible Addresses)

- ALERT Output Supports Interrupt or Comparator Modes

- WQFN-48 Package

- XOR-tree Test Mode

## **APPLICATIONS**

- Servers

- Workstations

- Processor based equipment

## **KEY SPECIFICATIONS**

- Voltage Measurement Accuracy: ±2% FS (max)

- Temperature Resolution: 9-bits, 0.5°C

- Temperature Sensor Accuracy: ±2.5 °C (max)

- Temperature Range:

- LM96194 Operational: -40°C to +85°C

- Remote Temp Accuracy: -40°C to +125°C

- Power Supply Voltage: +3.0V to +3.6V

- Power Supply Current: 1.6 mA

#### DESCRIPTION

The LM96194 hardware monitor has a two wire digital interface compatible with SMBus 2.0. Using a  $\Sigma\Delta$  ADC, the LM96194 measures the temperature of four remote diode connected transistors as well as its own die and 9 power supply voltages. The LM96194 has new TruTherm technology that supports precision thermal diode measurements of processors on submicron processes.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Pentium is a trademark of Intel Corporation. Intel is a registered trademark of Intel Corporation. I<sup>2</sup>C, I<sup>2</sup>C Block Write are trademarks of NXP.

All other trademarks are the property of their respective owners.

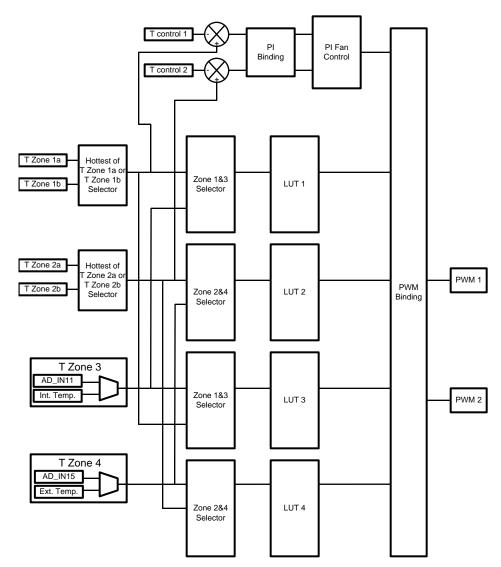

To set fan speed, the LM96194 has two PWM outputs that are each controlled by up to six temperature zones. The fan-control algorithm can be based on a lookup table, PI (proportional/integral) control loop, or a combination of both. The LM96194 includes digital filters that can be invoked to smooth temperature readings for better control of fan speed such that acoustical noise is minimized. The LM96194 has four tachometer inputs to measure fan speed. Limit and status registers for all measured values are included.

The LM96194 includes most of the features of the LM94, dual CPU motherboard serve<u>r management ASIC</u>, such as measurement and control support for dynamic Vccp monitoring for VRD10/11 and PROCHOT but is targeted for single processor systems.

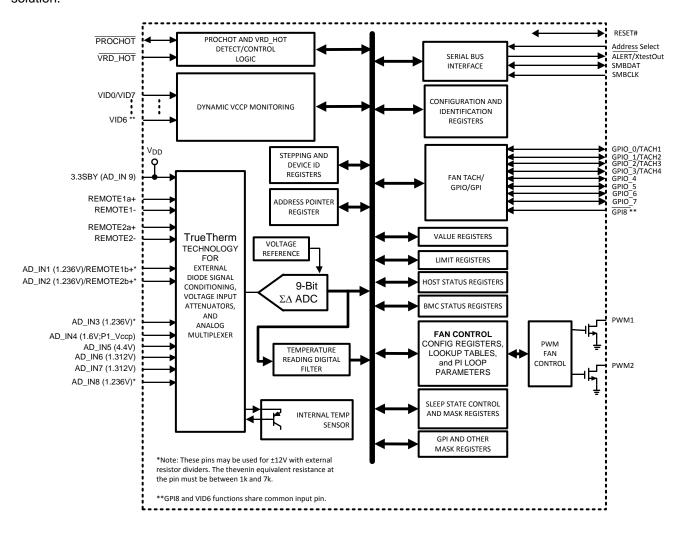

## **Block Diagram**

The block diagram of LM96194 hardware is illustrated below. The hardware implementation is a single chip ASIC solution.

## **Application**

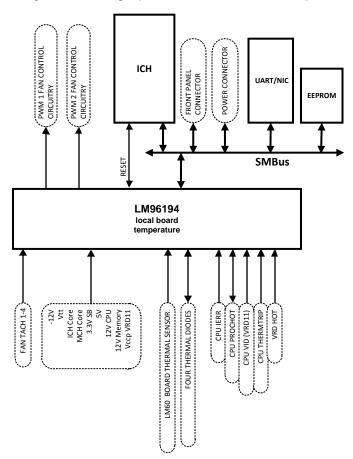

The system diagram show in Figure 1 is a single processor workstation example.

Figure 1. Workstation Management

Copyright © 2007–2013, Texas Instruments Incorporated

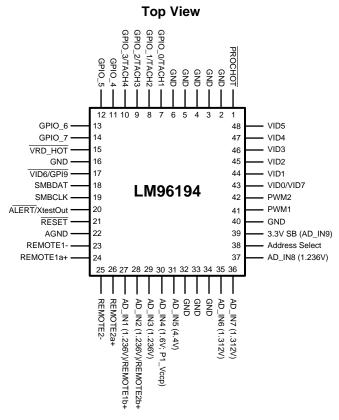

## **Connection Diagram**

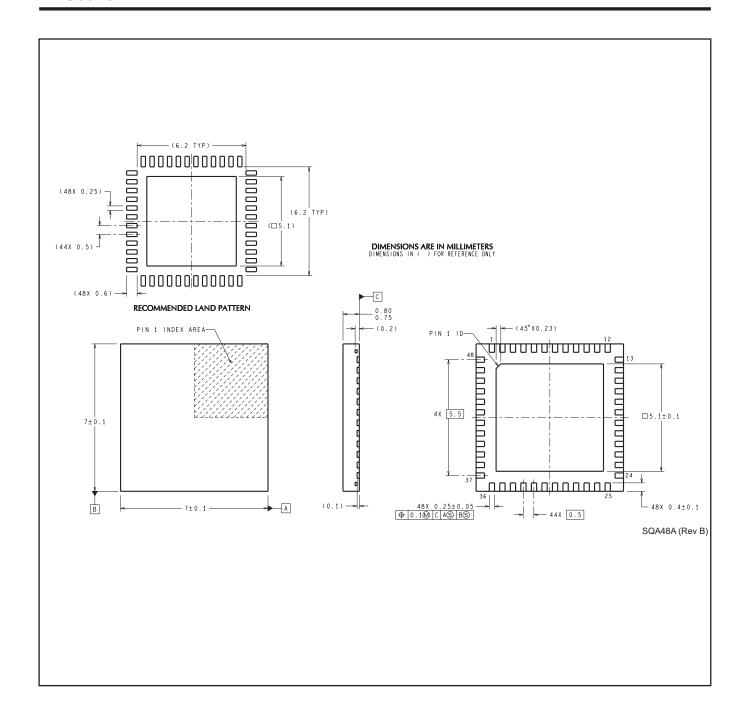

Figure 2. 48 Pin WQFN Package See Package Number RHS0048A

Table 1. Pin Descriptions<sup>(1)</sup>

| Name         | Pin No. | Туре                     | Function                                                                                                                                                        |

|--------------|---------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCHOT      | 1       | Digital I/O (Open-Drain) | Connected to CPU1 PROCHOT (processor hot) signal through a bidirectional level shifter. Supports TTL input logic levels and AGTL compatible input logic levels. |

| GND          | 2       | Ground                   | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.     |

| GND          | 3       | Ground                   | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.     |

| GND          | 4       | Ground                   | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.     |

| GND          | 5       | Ground                   | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.     |

| GND          | 6       | Ground                   | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.     |

| GPIO_0/TACH1 | 7       | Digital I/O (Open-Drain) | Can be configured as fan tach input or a general purpose open-drain digital I/O.                                                                                |

| GPIO_1/TACH2 | 8       | Digital I/O (Open-Drain) | Can be configured as fan tach input or a general purpose open-drain digital I/O.                                                                                |

(1) The over-score indicates the signal is active low ("Not").

## Table 1. Pin Descriptions<sup>(1)</sup> (continued)

| Name               | Pin No. | Туре                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|---------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_2/TACH3       | 9       | Digital I/O (Open-Drain)                          | Can be configured as fan tach input or a general purpose open-drain digital I/O.                                                                                                                                                                                                                                                                                                                                                 |

| GPIO_3/TACH4       | 10      | Digital I/O (Open-Drain)                          | Can be configured as fan tach input or a general purpose open-drain digital I/O                                                                                                                                                                                                                                                                                                                                                  |

| GPIO_4 / THERMTRIP | 11      | Digital I/O (Open-Drain)                          | A general purpose open-drain digital I/O. Can be configured to monitor a CPU's THERMTRIP signal to mask other errors. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                    |

| GPIO_5             | 12      | Digital I/O (Open-Drain)                          | A general purpose open-drain digital I/O. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                |

| GPIO_6             | 13      | Digital I/O (Open-Drain)                          | Can be used to detect the state of CPU's $\overline{\text{IERR}}$ or a general purpose opendrain digital I/O. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                            |

| GPIO_7             | 14      | Digital I/O (Open-Drain)                          | A general purpose open-drain digital I/O. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                |

| VRD1_HOT           | 15      | Digital Input                                     | CPU1 voltage regulator HOT. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                              |

| GND                | 16      | Ground Input                                      | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.                                                                                                                                                                                                                                                                      |

| VID6/GPI9          | 17      | Digital Input                                     | CPU VID6 input. Could also be used as a general purpose input to trigger an error event. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                 |

| SMBDAT             | 18      | Digital I/O (Open-Drain)                          | Bidirectional System Management Bus Data. Output configured as 5V tolerant open-drain. SMBus 2.0 compliant.                                                                                                                                                                                                                                                                                                                      |

| SMBCLK             | 19      | Digital Input                                     | System Management Bus Clock. Driven by an open-drain output, and is 5V tolerant. SMBus 2.0 Compliant.                                                                                                                                                                                                                                                                                                                            |

| ALERT/XtestOut     | 20      | Digital Output (Open-<br>Drain)                   | Open-drain ALERT output used in an interrupt driven system to signal that an error event has occurred. Masked error events do not activate the ALERT output. When in XOR tree test mode, functions as XOR Tree output.                                                                                                                                                                                                           |

| RESET              | 21      | Digital I/O (Open-Drain)                          | Open-drain reset output when power is first applied to the LM96194. Used as a reset for devices powered by 3.3V stand-by. After reset, this pin becomes a reset input. See RESET INPUT/OUTPUT for more information. If this pin is not used, connection to an external resistive pull-up is required to prevent LM96194 malfunction.                                                                                             |

| AGND               | 22      | GROUND Input                                      | Analog Ground. All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.                                                                                                                                                                                                                                                       |

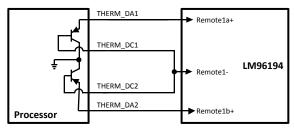

| REMOTE1-           | 23      | Remote Thermal<br>Diode_1- Input (CPU<br>THERMDC) | This is the negative input (current sink) from both of the CPU thermal diodes. Connected to THERMDC pin of Pentium processor or the emitter of a diode connected MMBT3904 NPN transistor. Serves as the negative input into the A/D for thermal diode voltage measurements. A 100 pF capacitor is optional and can be connected between REMOTE1- and REMOTE1+.                                                                   |

| REMOTE1a+          | 24      | Remote Thermal<br>Diode_1a+ I/O (CPU<br>THERMDA1) | This is a positive connection to the first CPU thermal diode. Serves as the positive input into the A/D for thermal diode voltage measurements. It also serves as a current source output that forward biases the thermal diode. Connected to THERMDA pin of Pentium processor or the base of a diode connected MMBT3904 NPN transistor. A 100 pF capacitor is optional and can be connected between REMOTE1- and each REMOTE1+. |

| REMOTE2-           | 25      | Remote Thermal<br>Diode_2 - Input                 | This is the negative input (current sink) from both of the CPU2 thermal diodes. Connected to THERMDC pins of Pentium processor or the emitter of a diode connected MMBT3904 NPN transistor. Serves as the negative input into the A/D for thermal diode voltage measurements. A 100 pF capacitor is optional and can be connected between REMOTE2- and each REMOTE2+.                                                            |

| REMOTE2a+          | 26      | Remote Thermal<br>Diode_2a + I/O                  | This is a positive connection to the third thermal diode. Serves as the positive input into the A/D for thermal diode voltage measurements. It also serves as a current source output that forward biases the thermal diode. Connected to THERMDA pin of Pentium processor or the base of a diode connected MMBT3904 NPN transistor. A 100 pF capacitor is optional and can be connected between REMOTE2- and REMOTE2+.          |

## Table 1. Pin Descriptions<sup>(1)</sup> (continued)

| Name             | Pin No. | Туре                                                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD_IN1/REMOTE1b+ | 27      | Analog Input (+12V1 or<br>CPU1 THERMDA2)            | Analog Input for +12V Rail 1 monitoring, for CPU1 voltage regulator. External attenuation resistors required such that 12V is attenuated to 0.927V for nominal ¾ scale reading. This pin may also serve as the second positive thermal diode input for the CPU.                                                                                                                                                                                                                                                        |

| AD_IN2/REMOTE2b+ | 28      | Analog Input or<br>Remote Thermal<br>Diode_2b + I/O | Analog Input for +12V Rail 2 monitoring. External attenuation resistors required such that 12V is attenuated to 0.927V for nominal ¾ scale reading. This pin may also serve as the fourth positive thermal diode input.                                                                                                                                                                                                                                                                                                |

| AD_IN3           | 29      | Analog Input (+12V3)                                | Analog Input for +12V Rail 3, for Memory/3GIO slots. External attenuation resistors required such that 12V is attenuated to 0.927V for nominal ¾ scale reading.                                                                                                                                                                                                                                                                                                                                                        |

| AD_IN4 (Vccp)    | 30      | Analog Input<br>(CPU1_Vccp)                         | Analog input for +Vccp (processor voltage) monitoring.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AD_IN5           | 31      | Analog Input (+3.3V)                                | Analog input for +3.3V monitoring, nominal ¾ scale reading                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND              | 32      | Ground                                              | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.                                                                                                                                                                                                                                                                                                                                                            |

| GND              | 33      | Ground                                              | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.                                                                                                                                                                                                                                                                                                                                                            |

| GND              | 34      | Ground                                              | All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.                                                                                                                                                                                                                                                                                                                                                            |

| AD_IN6           | 35      | Analog Input<br>(Mem_Vtt)                           | Analog input for +0.984V monitoring, nominal ¾ scale reading.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AD_IN7           | 36      | Analog Input (Gbit_Core)                            | Analog input for +0.984V S/B monitoring, nominal 3/4 scale reading.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AD_IN8           | 37      | Analog Input (-12V)                                 | Analog input for -12V monitoring. External resistors required to scale to positive level. Full scale reading at 1.236V, , nominal ¾ scale reading. This pin may also be used to monitor an analog temperature sensor such as the LM60, since readings from this input can be routed to the fan control logic.                                                                                                                                                                                                          |

| Address Select   | 38      | 3 level analog input                                | This input selects the lower two bits of the LM96194 SMBus slave address.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.3V SB (AD_IN8) | 39      | POWER (V <sub>DD</sub> ) +3.3V standby power        | $V_{DD}$ power input for LM96194. Generally this is connected to +3.3V standby power. The LM96194 can be powered by +3.3V if monitoring in low power states is not required, but power should be applied to this input before any other pins. This pin also serves as the analog input to monitor the 3.3V stand-by (SB) voltage. It is necessary to bypass this pin with a 0.1 μF in parallel with 100 pF. A bulk capacitance of 10 μF should be in the near vicinity. The 100 pF should be closest to the power pin. |

| GND              | 40      | Ground                                              | Digital Ground. All grounds need to be tied together at the chip then taken to a low noise system ground. A voltage difference between grounds may cause erroneous results.                                                                                                                                                                                                                                                                                                                                            |

| PWM1             | 41      | Digital Output (Open-<br>Drain)                     | Fan control output 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PWM2             | 42      | Digital Output (Open-<br>Drain)                     | Fan control output 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VID0/VID7        | 43      | Digital Input                                       | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                              |

| VID1             | 44      | Digital Input                                       | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                              |

| VID2             | 45      | Digital Input                                       | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                              |

| VID3             | 46      | Digital Input                                       | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                              |

| VID4             | 47      | Digital Input                                       | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                              |

| VID5             | 48      | Digital Input                                       | Voltage Identification signal from the processor. Supports TTL input logic levels and AGTL compatible input logic levels.                                                                                                                                                                                                                                                                                                                                                                                              |

Product Folder Links: LM96194

## **Server Terminology**

| A/D                            | Analog to Digital Converter                                                                            |

|--------------------------------|--------------------------------------------------------------------------------------------------------|

| ACPI                           | Advanced Configuration and Power Interface                                                             |

| ALERT                          | SMBus signal to bus master that an event occurred that has been flagged for attention.                 |

| ASF                            | Alert Standard Format                                                                                  |

| BMC                            | Baseboard Management Controller                                                                        |

| BW                             | Bandwidth                                                                                              |

| DIMM                           | Dual in line memory module                                                                             |

| DP                             | Dual-processor                                                                                         |

| ECC                            | Error checking and correcting                                                                          |

| FRU                            | Field replaceable unit                                                                                 |

| FSB                            | Front side bus                                                                                         |

| FW                             | Firmware                                                                                               |

| Gb                             | Gigabit                                                                                                |

| GB                             | Gigabyte                                                                                               |

| Gbe                            | Gigabit Ethernet                                                                                       |

| GPI                            | General purpose input                                                                                  |

| GPIO                           | General purpose I/O                                                                                    |

| HW                             | Hardware                                                                                               |

| I <sup>2</sup> C <sup>TM</sup> | Inter integrated circuit (bus)                                                                         |

| LAN                            | Local area network                                                                                     |

| LSb                            | Least Significant Bit                                                                                  |

| LSB                            | Least Significant Byte                                                                                 |

| LVDS                           | Low-Voltage Differential Signaling                                                                     |

| LUT                            | Look-Up Table                                                                                          |

| Mb                             | Megabit                                                                                                |

| MB                             | Megabyte                                                                                               |

| MP                             | Multi-processor                                                                                        |

| MSb                            | Most Significant Bit                                                                                   |

| MSB                            | Most Significant Byte                                                                                  |

| MTBF                           | Mean time between failures                                                                             |

| MTTR                           | Mean time to repair                                                                                    |

| NIC                            | Network Interface Card (Ethernet Card)                                                                 |

| OS                             | Operating system                                                                                       |

| P/S                            | Power Supply                                                                                           |

| PCI                            | PCI Local Bus                                                                                          |

| PDB                            | Power Distribution Board                                                                               |

| POR                            | Power On Reset                                                                                         |

| PS                             | Power Supply                                                                                           |

| SMBCLK and SMBDAT              | These signals comprise the SMBus interface (data and clock). See SMBus Interface for more information. |

| VRD                            | Voltage Regulator Down - regulates Vccp voltage for a CPU                                              |

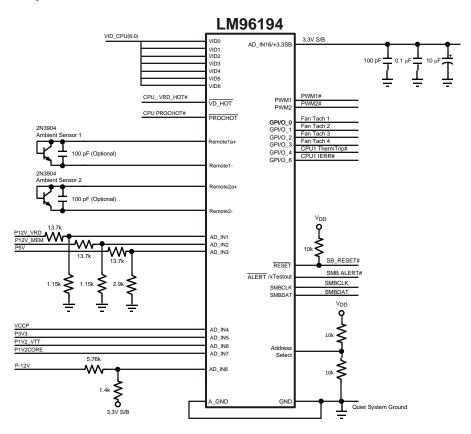

## **Recommended Implementation**

Figure 3. Recommended implementation without thermal diode connections

**Note:** 100 pF cap across each thermal diode is optional and should be placed close to the LM96194, if used. The maximum capacitance between thermal diode pins is 300 pF.

Figure 4. Thermal diode recommended implementation

## **Functional Description**

The LM96194 provides 9 channels of voltage monitoring, 4 remote thermal diode monitors, an internal/local ambient temperature sensor, a PROCHOT monitor, 4 fan tachometers, 8 GPIOs, THERMTRIP monitor for masking error events, 1 sets of 7 VID inputs, an ALERT output and all the associated limit registers on a single chip, and communicates to the rest of the baseboard over the System Management Bus (SMBus). The LM96194 also provides 2 PWM outputs and associated fan control logic for controlling the speed of system fans. There are two sets of fan control logic, a lookup table and a PI (proportional/integral) loop controller. The lookup table and PI controller are interactive, such that the fans run at the fastest required speed. Upon a temperature or fan tach error event, the PWM outputs may be programmed such that they automatically boost to 100% duty cycle. A timer is included that sets the minimum time that the fans are in the boost condition when activated by a fan tach error.

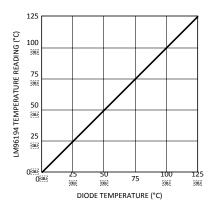

The LM96194 incorporates Texas Instrument's TruTherm technology for precision "Remote Diode" readings of processors on 90nm process geometry or smaller. Readings from the external thermal diodes and the internal temperature sensor are made available as an 9-bit two's-complement digital value with the LSb representing 0.5°C. Filtered temperature readings are available as a 12-bit two's-complement digital value with the LSb representing 0.0625°C.

All of the analog inputs include internal scaling resistors, exept for AD\_IN1, AD\_IN2, AD\_IN3 and AD\_IN8. External scaling resistors are required for measuring ±12V. The inputs are converted to 8-bit digital values such that a nominal voltage appears at ¾ scale for positive voltages and ¼ scale for negative voltages. The analog inputs are intended to be connected to both baseboard resident VRDs and to standard voltage rails supplied by a SSI compliant power supply.

The LM96194 has logic that ties a set of dynamically moving VID inputs to their associated Vccp analog input for real time window comparison fault determination. Voltage mapping for VRD10, VRD10 extended and VRD11are supported by the LM96194. When VRD10 mode is selected GPI8 and GPI9 can be used to detect external error flags whose state is reflected in the status registers.

Error events are captured in two sets of mirrored status registers (BMC Error Status Registers and Host Status Registers) allowing two controllers access to the status information without any interference.

The LM96194's ALERT output supports interrupt mode or comparator mode of operation. The comparator mode is only functional for thermal monitoring.

The LM96194 provides a number of internal registers, which are detailed in the Registers section of this document.

#### MONITORING CYCLE TIME

When the LM96194 is powered up, it cycles through each temperature measurement followed by the analog voltages in sequence, and it continuously loops through the sequence. The total monitoring cycle time is not less than 100 ms, as this is the time period that most external micro-controllers require to read the register values.

Each measured value is compared to values stored in the limit registers. When the measured value violates the programmed limit, a corresponding status bit in the B\_Error and H\_Error Status Registers is set.

The PROCHOT, tachometer and dynamic VID/Vccp monitoring is performed independently of the analog and temperature monitoring cycle.

## **ΣΔ A/D INHERENT AVERAGING**

The  $\Sigma\Delta$  A/D architecture filters the input signal. During one conversion many samples are taken of the input voltage and these samples are effectively averaged to give the final result. The output of the  $\Sigma\Delta$  A/D is the average value of the signal during the sampling interval. For a voltage measurement, the samples are accumulated for 1.5 ms. For a temperature measurement, the samples are accumulated for 8.4 ms.

## **TEMPERATURE MONITORING**

The LM96194 remote diode target is the embedded thermal diode found in a Xeon class processor in 90nm processes but can also work with any Intel<sup>®</sup> Corporation based processor in 90nm or 65nm. The LM96194 has an advanced thermal diode input stage using TI's TruTherm technology that reduces the spread in ideality found in sub-micron geometry thermal diodes. Internal analog filtering has been included in the thermal diode input stage thus minimizing the need for external thermal diode filter capacitors. In addition a digital filter has been included for the thermal diode temperature readings.

In some cases instead of using the embedded thermal diode, found on the Xeon processor, a diode connected 2N3904 transistor type can also be used. An example of this would be a MMBT3904 with its collector and base tied to the thermal diode REMOTE+ pin and the emitter tied to the thermal diode REMOTE- pin. Since the MMBT3904 is a surface mount device and has very small thermal mass, it measures the board temperature where it is mounted. The ideality and series resistance varies for different diodes. Therefore the LM96194 has register support to allow calibration selection between a 2N3904 or a Xeon processor. The LM96194 is optimized for typical Intel processors on 90nm or 65nm process or 2N3904 transistor. Other transistor types may be used but may have additional error that can be corrected for by programming the appropriate Zone Adjustment Offset register.

The LM96194 acquires temperature data from four different sources:

- 4 external diodes (embedded in a processor or discrete)

- 1 internal diode (internal to the LM96194)

- 1 analog temperature sensors, such as the LM60, that are connected to the AD\_15 pin

- a temperature value can be externally written into an LM96194 register from the SMBus.

All of these values, although not necessarily simultaneously, can be used to control fans, compared against limits, etc.

The temperature value registers are located at addresses 06h-09h, 50h-55h and 10h-23h. The temperature sources are referred to as "zones" for convenience:

| Zone    | Description                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------|

| Zone 1a | Processor 1 remote diode 1 (REMOTE1a+, REMOTE1-)                                                                       |

| Zone 1b | Processor 1 remote diode 2 (REMOTE1b+, REMOTE1-)                                                                       |

| Zone 2a | MMBT3904 remote diode 1 (REMOTE2a+, REMOTE2-)                                                                          |

| Zone 2b | MMBT2904 remote diode 2 (REMOTE2b+, REMOTE2-)                                                                          |

| Zone 3  | Internal LM96194 on-chip sensor; also accepts writes via SMBus                                                         |

| Zone 4  | External digital temperature value from SMBus write to register 53h or external LM60 analog sensor connected to AD_IN8 |

## "Remote Diode" TruTherm Mode

The processor "remote thermal diode" is more correctly described as a transistor. The LM93 treated the "remote diode" as a diode thus introducing inaccuracies. These inaccuracies have become more apparent as the geometry of processors is shrinking. The LM96194 can sense the "remote diode" using a new TruTherm technology that treats the remote device as a transistor. The TruTherm Mode is more accurate for processors on 90nm and smaller geometry. The LM96194 still supports the old diode method and is callibrated for 2N3904 transistor type.

## Temperature Data Format

Most of the temperature data for the LM96194 is represented in three formats:

8-bit, two's complement byte with the LSb equal to 1.0 °C; this applies to temperature measurements as well

as any temperature limit registers and some configuration registers.

| Temperature <sup>(1)</sup> | Binary    | Hex |

|----------------------------|-----------|-----|

| +125°C                     | 0111 1101 | 7Dh |

| +25°C                      | 0001 1001 | 19h |

| +1.0°C                     | 0000 0001 | 01h |

| 0°C                        | 0000 0000 | 00h |

| −1.0°C                     | 1111 1111 | FFh |

| −25°C                      | 1110 0111 | E7h |

| −55°C                      | 1100 1001 | C9h |

| −127°C                     | 1000 0001 | 81h |

<sup>(1)</sup> A value of 80h has a special meaning in the limit registers. It means that the temperature channel is masked. In addition, temperature readings of 80h indicate thermal diode faults.

Product Folder Links: *LM96194*

Copyright © 2007-2013, Texas Instruments Incorporated

9-bit two's complement word with the LSb equal to 0.5°C; this applies to unfiltered temperature measurement extended resolution value registers

| <b>T</b>    | Bin       |           |        |

|-------------|-----------|-----------|--------|

| Temperature | MSB       | LSB       | Hex    |

| +125.5°C    | 0111 1101 | 1000 0000 | 7D 80h |

| +25.5°C     | 0001 1001 | 1000 0000 | 19 80h |

| +0.5°C      | 0000 0000 | 1000 0000 | 00 80h |

| 0°C         | 0000 0000 | 0000 0000 | 00 00h |

| −0.5°C      | 1111 1111 | 1000 0000 | FF 80h |

| −25.5°C     | 1110 0111 | 1000 0000 | E7 80h |

| −55.5°C     | 1100 1001 | 1000 0000 | C9 80h |

| −127.5°C    | 1000 0001 | 1000 0000 | 81 80h |

12-bit two's complement word with the LSb equal to 0.0625°C; this applies to extended filtered temperature measurement extended resolution value registers

| <b>-</b>    | Bin       |           |        |

|-------------|-----------|-----------|--------|

| Temperature | MSB       | LSB       | Hex    |

| +125.0625°C | 0111 1101 | 0001 0000 | 7D 10h |

| +25.0625°C  | 0001 1001 | 0001 0000 | 19 10h |

| +1.0625°C   | 0000 0001 | 0001 0000 | 01 10h |

| 0°C         | 0000 0000 | 0000 0000 | 00 00h |

| −0.0625°C   | 1111 1111 | 1111 0000 | FF F0h |

| −25.0625°C  | 1110 0111 | 1111 0000 | E7 F0h |

| −55.0625°C  | 1100 1001 | 1111 0000 | C9 F0h |

| −127.0625°C | 1000 0000 | 1111 0000 | 80 F0h |

Some fan control configuration registers use four bits and have an unsigned binary format, please see the FAN CONTROL configuration register descriptions for further details on this 4-bit format.

## Thermal Diode Fault Status

The LM96194 provides for indications of a fault (open or short circuit) with the remote thermal diodes. Before a remote diode conversion is updated, the status of the remote diode is checked for an open or short circuit condition. If such a fault condition occurs, a status bit is set in the status register. A short circuit is defined as the diode pins connected to each other. When an open or short circuit is detected, the corresponding temperature register is set to 80h.

#### **EVENT ERRORS FOR FAN BOOST**

Copyright © 2007-2013, Texas Instruments Incorporated

Temperature boost error and tachometer error events can cause the fan control PWM output(s) to go to full on. A boost temperature error event will cause both PWM outputs to go to full on, while a tachometer event can be either bound to PWM1 or PWM2.

A fan boost temperature event occurs if any of the four temperature zones exceeds the temperature Fan Boost Limit for that zone. Once a temperature has exceed the boost limit, it must drop to a value equal to the boost limit minus the boost hysteresis before the boost condition is deactivated. The default setting for Zones 1 and 2 is 60°C and for Zones 3 and 4 it is 35°C.

The tachometer error boost function is enabled via the Tachometer Fan Boost Control register. Depending on the setting of the tachometer to PWM binding bits one or both of the PWM outputs will go to 100% duty cycle upon the detection of an unmasked Fan Tachometer Error Event. A Fan Tachometer Error event occurs when a tachometer reading exceeds the value set in it's FAN Tach Limit register. Once the error event ends the PWM output(s) will remain at 100% duty cycled for a time interval. Tach Boost Timeout, as programmed in the Tachometer Fan Boost Control register. If the tachometer error event returns during the middle of the timout interval the Tach Boost Timeout interval will be reset and restart once the error event ends.

## **VOLTAGE MONITORING**

The LM96194 contains inputs for monitoring voltages. Scaling is such that the correct value refers to approximately 3/4 scale or 192 decimal on all inputs, except for the  $\pm 12V$ . Scaling is accomplished by using internal resistor dividers, except for the  $\pm 12V$ . The typical input resistance of these inputs is 200 k ohms. Input voltages are converted by an 8-bit Delta-Sigma ( $\Delta\Sigma$ ) A/D. The Delta-Sigma A/D architecture provides inherent filtering and spike smoothing of the analog input signal.

The  $\pm 12V$  inputs must be scaled externally. A full scale reading is achieved when 1.236V is applied to these inputs. For optimum performance the  $\pm 12V$  should be scaled to provide a nominal  $\frac{3}{4}$  full scale reading, while the  $\pm 12V$  should be scaled to provide a nominal  $\frac{1}{4}$  scale reading. The thevenin resistance at the pin should be kept between 1 k $\Omega$  and 7 k $\Omega$ .

The -12V monitoring is particularly challenging. It is required that an external offset voltage and external resistors be used to bring the -12V rail into the positive input voltage region of the A/D input. It is suggested that the supply rail for the LM96194 device be used as the offset voltage. This voltage is usually derived from the P/S 5V stand-by voltage rail via a  $\pm 1\%$  accurate linear regulator. In this fashion we can always assume that the offset voltage is present when the -12V rail is present as the system cannot be turned on without the 3.3V stand-by voltage being present.

|        |               |                    |                                                 | _                  | _                                               | •                  | -                                               |                                    |

|--------|---------------|--------------------|-------------------------------------------------|--------------------|-------------------------------------------------|--------------------|-------------------------------------------------|------------------------------------|

| Pin    | Normal<br>Use | Nominal<br>Voltage | Register<br>Reading<br>at<br>Nominal<br>Voltage | Maximum<br>Voltage | Register<br>Reading<br>at<br>Maximum<br>Voltage | Minimum<br>Voltage | Register<br>Reading<br>at<br>Minimum<br>Voltage | Absolute<br>Maximum<br>Range       |

| AD_IN1 | +12V1         | 0.927V             | C0h                                             | 1.236V             | FFh                                             | 0V                 | 00h                                             | -0.3V to (V <sub>DD</sub> + 0.05V) |

| AD_IN2 | +12V2         | 0.927V             | C0h                                             | 1.236V             | FFh                                             | 0V                 | 00h                                             | $-0.3V$ to $(V_{DD} + 0.05V)$      |

| AD_IN3 | +12V3         | 0.927V             | C0h                                             | 1.236V             | FFh                                             | 0V                 | 00h                                             | -0.3V to (V <sub>DD</sub> + 0.05V) |

| AD_IN4 | Vccp1         | 1.20V              | C0h                                             | 1.60V              | FFh                                             | 0V                 | 00h                                             | -0.3V to +6.0V                     |

| AD_IN5 | +3.3V         | 3.30V              | C0h                                             | 4.40V              | FFh                                             | 0V                 | 00h                                             | -0.3V to +6.0V                     |

| AD_IN6 | Mem_Vtt       | 0.984V             | C0h                                             | 1.312V             | FFh                                             | 0V                 | 00h                                             | -0.3V to +6.0V                     |

| AD_IN7 | Gbit_Core     | 0.984V             | C0h                                             | 1.312V             | FFh                                             | 0V                 | 00h                                             | -0.3V to +6.0V                     |

| AD_IN8 | -12V          | 0.309V             | 40h                                             | 1.236V             | FFh                                             | 0V                 | 00h                                             | -0.3V to (V <sub>DD</sub> + 0.05V) |

| AD_IN9 | +3.3V S/B     | 3.3V               | C0h                                             | 3.6V               | D1h                                             | 3.0V               | AEh                                             | -0.3V to +6.0V                     |

Table 2. Voltage vs Register Reading

The nominal voltages listed in this table are only typical values. Voltage rails with different nominal voltages can be monitored, but the register reading at the nominal value is no longer C0h.

AD\_IN9 is also the power pin of the LM96194, therefore special limitations apply to this AD input. The specified operational voltage range for the LM96194 is 3.0V to 3.6V, therefore the voltage input to this pin is limited by this restriction. Care should also be taken not to apply more than 6V to this pin to prevent catastrophic damage.

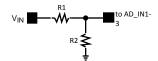

#### RECOMMENDED EXTERNAL SCALING RESISTORS FOR +12V POWER RAILS

The +12V inputs require external scaling resistors. The resistors need to scale 12V down to 0.927V.

Figure 5. Required External Scaling Resistors for +12V Power Input

To calculate the required ratio of R1 to R2 use this equation:

$$\frac{R1}{R2} = \frac{12}{0.927} - 1 = 11.04498 \tag{1}$$

It is recommended that the equivalent thevenin resistance of the divider be between 1k and 7k to minimize errors caused by leakage currents at extreme temperatures. The best values for the resistors are: R1=13.7 k $\Omega$  and R2=1.15 k $\Omega$ . This yields a ratio of 11.94498, which has a +0.27% deviation from the theoretical. It is also recommended that the resistors have ±1% tolerance or better.

Each LSB in the voltage value registers has a weight of 12V / 192 = 62.5 mV. To calculate the actual voltage of the +12V power input, use the following equation:

$$V_{IN} = (8-bit \ value \ register \ code) \ x \ (62.5 \ mV)$$

(2)

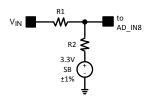

## RECOMMENDED EXTERNAL SCALING CIRCUIT FOR -12V POWER INPUT

The −12V input requires external resistors to level shift the nominal input voltage of −12V to +0.309V.

Figure 6. Required External Level Shifting Resistors for -12V Power Input

The  $\pm 3.3$ V standby voltage is used as a reference for the level shifting. Therefore, the tolerance of this voltage directly effects the accuracy of the  $\pm 12$ V reading. To minimize ratio errors, a tolerance of better than  $\pm 1\%$  should be used. It is recommended that the equivalent thevenin resistance of the divider is between 1k and 7k to minimize errors caused by leakage currents at extreme temperatures. To calculate the ratio of R1 to R2 use this equation:

$$\frac{R1}{R2} = \frac{(V_{IN} - V_{REF})}{(AD_{IN} - V_{REF})} - 1$$

(3)

where  $V_{IN}$  is the nominal input voltage of -12V,  $V_{REF}$  is the reference voltage of +3.3V and AD\_IN is the voltage required at the AD input for a  $\frac{1}{4}$  scale reading or 0.309V.

Therefore, for this case:

$$\frac{R1}{R2} = \frac{(-12 - 3.3)}{(0.309 - 3.3)} - 1 = 4.11535 \tag{4}$$

Using standard 1% resistor values for R1 of 5.76 k $\Omega$  and R2 of 1.4 k $\Omega$  yields an R1 to R2 ratio of 4.1143.

The input voltage V<sub>IN</sub> can be calculated using the value register reading (VR) using this equation:

$$V_{IN} = \frac{R1}{R2} = ( +1) \times [(1.236 V_{256}^{VR} ) - 3.3V] + 3.3V$$

$$= (24.69 \text{ mV} \times \text{VR}) - 13.5771V$$

(5)

The table below summarizes the theoretical voltage values for value register readings near -12V.

| Value Register | V <sub>IN</sub> | % Δ from −12V |

|----------------|-----------------|---------------|

| 15             | -13.2068        | -10.0563      |

| 16             | -13.1821        | -9.8505       |

| 17             | -13.1574        | -9.6448       |

| 18             | -13.1327        | -9.4390       |

| 19             | -13.1080        | -9.2332       |

| 20             | -13.0833        | -9.0275       |

| 21             | -13.0586        | -8.8217       |

| 22             | -13.0339        | -8.6159       |

| 23             | -13.0092        | -8.4101       |

| Value Register | V <sub>IN</sub>      | % ∆ from −12V      |

|----------------|----------------------|--------------------|

| 24             | -12.9845             | -8.2044            |

| 25             | -12.9598             | -7.9986            |

| 26             | -12.9351             | -7.7928            |

| 27             | -12.9104             | -7.5871            |

| 28             | -12.8858             | -7.3813            |

| 29             | -12.8611             | -7.1755            |

| 30             | -12.8364             | -6.9698            |

| 31             | -12.8117             | -6.7640            |

| 32             | -12.7870             | -6.5582            |

| 33             | -12.7623             | -6.3524            |

| 34             | -12.7376             | -6.1467            |

| 35             | -12.7129             | -5.9409            |

| 36             | -12.6882             | -5.7351            |

| 37             | -12.6635             | -5.5294            |

| 38             | -12.6388             | -5.3236            |

| 39             | -12.6366             | -5.3236<br>-5.1178 |

| 40             |                      |                    |

|                | -12.5894<br>12.5648  | -4.9121<br>4.7063  |

| 41 42          | -12.5648<br>-12.5401 | -4.7063<br>-4.5005 |

|                |                      |                    |

| 43             | -12.5154             | -4.2947            |

| 44             | -12.4907             | -4.0890            |

| 45             | -12.4660             | -3.8832            |

| 46             | -12.4413             | -3.6774            |

| 47             | -12.4166             | -3.4717            |

| 48             | -12.3919             | -3.2659            |

| 49             | -12.3672             | -3.0601            |

| 50             | -12.3425             | -2.8544            |

| 51             | -12.3178             | -2.6486            |

| 52             | -12.2931             | -2.4428            |

| 53             | -12.2684             | -2.2370            |

| 54             | -12.2438             | -2.0313            |

| 55             | -12.2191             | -1.8255            |

| 56             | -12.1944             | -1.6197            |

| 57             | -12.1697             | -1.4140            |

| 58             | -12.1450             | -1.2082            |

| 59             | -12.1203             | -1.0024            |

| 60             | -12.0956             | -0.7967            |

| 61             | -12.0709             | -0.5909            |

| 62             | -12.0462             | -0.3851            |

| 63             | -12.0215             | -0.1793            |

| 64             | -11.9968             | 0.0264             |

| 65             | -11.9721             | 0.2322             |

| 66             | -11.9474             | 0.4380             |

| 67             | -11.9228             | 0.6437             |

| 68             | -11.8981             | 0.8495             |

| 69             | -11.8734             | 1.0553             |

| 70             | -11.8487             | 1.2610             |

| 71             | -11.8240             | 1.4668             |

| 72             | -11.7993             | 1.6726             |

Submit Documentation Feedback

Copyright © 2007–2013, Texas Instruments Incorporated

| Value Register | V <sub>IN</sub> | % ∆ from −12V |

|----------------|-----------------|---------------|

| 73             | -11.7746        | 1.8784        |

| 74             | -11.7499        | 2.0841        |

| 75             | -11.7252        | 2.2899        |

| 76             | -11.7005        | 2.4957        |

| 77             | -11.6758        | 2.7014        |

| 78             | -11.6511        | 2.9072        |

| 79             | -11.6264        | 3.1130        |

| 80             | -11.6018        | 3.3188        |

| 81             | -11.5771        | 3.5245        |

| 82             | -11.5524        | 3.7303        |

| 83             | -11.5277        | 3.9361        |

| 84             | -11.5030        | 4.1418        |

| 85             | -11.4783        | 4.3476        |

| 86             | -11.4536        | 4.5534        |

| 87             | -11.4289        | 4.7591        |

| 88             | -11.4042        | 4.9649        |

| 89             | -11.3795        | 5.1707        |

| 90             | -11.3548        | 5.3765        |

| 91             | -11.3301        | 5.5822        |

| 92             | -11.3054        | 5.7880        |

| 93             | -11.2807        | 5.9938        |

| 94             | -11.2561        | 6.1995        |

| 95             | -11.2314        | 6.4053        |

| 96             | -11.2067        | 6.6111        |

| 97             | -11.1820        | 6.8168        |

| 98             | -11.1573        | 7.0226        |

| 99             | -11.1326        | 7.2284        |

| 100            | -11.1079        | 7.4342        |

| 101            | -11.0832        | 7.6399        |

| 102            | -11.0585        | 7.8457        |

| 103            | -11.0338        | 8.0515        |

| 104            | -11.0091        | 8.2572        |

| 105            | -10.9844        | 8.4630        |

| 106            | -10.9597        | 8.6688        |

| 107            | -10.9351        | 8.8745        |

| 108            | -10.9104        | 9.0803        |

| 109            | -10.8857        | 9.2861        |

| 110            | -10.8610        | 9.4919        |

| 111            | -10.8363        | 9.6976        |

| 112            | -10.8116        | 9.9034        |

| 113            | -10.7869        | 10.1092       |

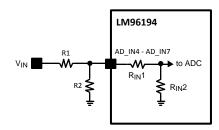

## ADDING EXTERNAL SCALING RESISTORS TO OTHER ANALOG INPUTS

All analog inputs, except AD\_IN1 through AD\_IN3 and AD\_IN8, include internal resistor dividers. Further scaling of AD\_IN4 through AD\_IN7 inputs with external scaling resistors is possible if the errors due to the internal dividers are accounted. The internal resistors,  $R_{IN}1 + R_{IN}2$  shown in Figure 7, will present to the external divider a minimum resistive load of 140 k $\Omega$ .

Figure 7. Internal Resistors, R<sub>IN</sub>1 + R<sub>IN</sub>2

## DYNAMIC Vccp MONITORING USING VID

The AD\_IN4 (CPU Vccp) input is dynamically monitored using the VIDx inputs to determine the limits. The dynamic comparisons operate independently of the static comparisons which use the statically programmed limits. The LM96194 supports 3 different specifications for the Voltage Regulator (VRM or VRD) used on motherboards with Intel CPUs with four different VID Modes of operation. The Voltage Regulator Specifications supported are the VRD10/VRM10, VRD10.2 Extended and VRD11/VRM11, and in this document they will be referred to as the VRD10, VRD10.2 and VRD11 specifications, respectively.

According to the VRD 10 specification when a VID signal is ramping to a new value, it steps by one LSB at a time, and one step occurs every 5  $\mu$ s. In worse case, up to 20 steps may occur at once over 100  $\mu$ s. The Vccp voltage from the VRD has to settle to the new value within 50  $\mu$ s of the last VID change. The LM96194 expects that the VID changes will not occur more frequently than every 5  $\mu$ s in the VRD10 mode. Similarly the LM96194 can support the timing requirements of the VRD10.2 and VRD11 specifications.

The VID signals can be changed by the processor under program control, by internal thermal events or by external control, like force PROCHOT.

The reference voltages selected by each value of the VID code can be found in the different VRM/VRD specifications. Transient VID values caused by line-to-line skew are ignored by the LM96194. See the VRM/VRD specifications for the worst case line-to-line skew.

The LM96194 averages the VID values over a sampling window to determine the average voltage that the VID input was indicating during the sampling window. At the completion of a voltage conversion cycle the LM96194 performs limit comparisons based on average VID values and not instantaneous values. The upper limit is determined by adding the upper limit offset to the average voltage indicated by VID. The lower limit is determined by subtracting the lower limit offset from average voltage indicated by VID. If the AD\_IN4 voltage falls outside the upper and lower limits, an error event is generated. Dynamic and static comparisons are performed once every 100 ms. The averaging time interval is 1.5 ms.

If at any time during the Vccp sampling window, the VID code indicates that the VRD/VRM should turn off its output, the dynamic Vccp checking is disabled for that sample.

The comparison accuracy is ±25 mV, therefore the comparison limits must be set to include this error. Since the Vccp voltage may be in the process of settling to a new value (due to a VID change), this settling should be taken into account when setting the upper and lower limit offsets.

The LM96194 has a limitation on the upper limit voltage for dynamic Vccp checking. The upper limit cannot exceed 1.5875V. If the sum of the voltage indicated by VID and the upper offset voltage exceed 1.5875, the upper limit checking is disabled.

Pin 17 has a dual purpose. When VRD10 mode is selected they can be used as general purpose inputs whose state is reflected the BMC and Host Error Status registers. In the other VRD modes they are used as a VID6 input.

#### MONITORING ANALOG TEMPERATURE SENSORS

The AD\_IN8 reading can be routed to the fan control logic to facilitate the use of external temperature sensors such as the LM60. When these inputs are used for temperature sensing the digital output returned is in signed format, that is the MSb is inverted.

The following table lists critical parameters necessary for converting the binary data to temperature.

| Input      | V NOM              | Full Scale 254.5<br>(code 256) V code V |        | mV<br>/LSb | LM60<br>deg<br>/LSb | LM50<br>deg<br>/LSb |  |

|------------|--------------------|-----------------------------------------|--------|------------|---------------------|---------------------|--|

| AD_<br>IN8 | 0.309<br>(¼ scale) | 1.2360                                  | 1.2288 | 4.8        | 0.7725              | 0.4828              |  |

The following table lists the equations to use for converting the AD\_IN8 Digital Value (DV) to a temperature value.

| Input  | LM60 Equation                    | LM50 Equation                        |  |  |  |  |

|--------|----------------------------------|--------------------------------------|--|--|--|--|

| AD_IN8 | $(DV + 40.18) \times 0.7725$ (6) | $(DV + 24.44) \times 0.4828 \tag{7}$ |  |  |  |  |

The following table lists the ideal values generated when using the LM60 at different temperatures.

|      | LM60          | AD_IN8 Reading    |               |  |  |  |  |

|------|---------------|-------------------|---------------|--|--|--|--|

| Temp | ldeal<br>Vout | Signed<br>Decimal | Signed<br>Hex |  |  |  |  |

| 0    | 0.424         | -40.18            | D8            |  |  |  |  |

| 25   | 0.5803        | -8                | F8            |  |  |  |  |

| 30   | 0.6115        | -1                | FF            |  |  |  |  |

| 35   | 0.6428        | 5                 | 5             |  |  |  |  |

| 40   | 0.6740        | 12                | С             |  |  |  |  |

| 45   | 0.7053        | 18                | 12            |  |  |  |  |

| 50   | 0.7365        | 25                | 19            |  |  |  |  |

| 55   | 0.7678        | 31                | 1F            |  |  |  |  |

| 60   | 0.7990        | 37                | 25            |  |  |  |  |

| 65   | 0.8303        | 44                | 2C            |  |  |  |  |

| 70   | 0.8615        | 50                | 32            |  |  |  |  |

| 75   | 0.8928        | 57                | 39            |  |  |  |  |

| 80   | 0.9240        | 63                | 3F            |  |  |  |  |

| 85   | 0.9553        | 70                | 46            |  |  |  |  |

| 90   | 0.9865        | 76                | 4C            |  |  |  |  |

| 95   | 1.0178        | 83                | 53            |  |  |  |  |

| 100  | 1.0490        | 89                | 59            |  |  |  |  |

| 105  | 1.0803        | 96                | 60            |  |  |  |  |

| 110  | 1.1115        | 102               | 66            |  |  |  |  |

| 115  | 1.1428        | 109               | 6D            |  |  |  |  |

| 120  | 1.1740        | 115               | 73            |  |  |  |  |

| 125  | 1.2053        | 122               | 7A            |  |  |  |  |

| 130  | 1.2365        | 127               | 7F            |  |  |  |  |

The following table lists the expected ideal digital values when using the LM50.

|      | LM50          | AD_IN8 Reading    |               |  |  |  |  |

|------|---------------|-------------------|---------------|--|--|--|--|

| Temp | Ideal<br>Vout | Signed<br>Decimal | Signed<br>Hex |  |  |  |  |

| 0    | 0.5           | -24.44            | E8            |  |  |  |  |

| 25   | 0.7500        | 27                | 1B            |  |  |  |  |

| 30   | 0.8000        | 38                | 26            |  |  |  |  |

| 35   | 0.8500        | 48                | 30            |  |  |  |  |

| 40   | 0.9000        | 58                | 3A            |  |  |  |  |

| 45   | 0.9500        | 69                | 45            |  |  |  |  |

| 50   | 1.0000        | 79                | 4F            |  |  |  |  |

|      | LM50          | AD_IN8 Reading    |               |  |  |  |  |  |

|------|---------------|-------------------|---------------|--|--|--|--|--|

| Temp | ldeal<br>Vout | Signed<br>Decimal | Signed<br>Hex |  |  |  |  |  |

| 55   | 1.0500        | 89                | 59            |  |  |  |  |  |

| 60   | 1.1000        | 100               | 64            |  |  |  |  |  |

| 65   | 1.1500        | 110               | 6E            |  |  |  |  |  |

| 70   | 1.2000        | 121               | 79            |  |  |  |  |  |

| 75   | 1.2500        | 127               | 7F            |  |  |  |  |  |

| 80   | 1.3000        | 127               | 7F            |  |  |  |  |  |

| 85   | 1.3500        | 127               | 7F            |  |  |  |  |  |

| 90   | 1.4000        | 127               | 7F            |  |  |  |  |  |

| 95   | 1.4500        | 127               | 7F            |  |  |  |  |  |

| 100  | 1.5000        | 127               | 7F            |  |  |  |  |  |

| 105  | 1.5500        | 127               | 7F            |  |  |  |  |  |

| 110  | 1.6000        | 127               | 7F            |  |  |  |  |  |

| 115  | 1.6500        | 127               | 7F            |  |  |  |  |  |

| 120  | 1.7000        | 127               | 7F            |  |  |  |  |  |

| 125  | 1.7500        | 127               | 7F            |  |  |  |  |  |

| 130  | 1.8000        | 127               | 7F            |  |  |  |  |  |

## PROCHOT BACKGROUND INFORMATION

PROCHOT is an output from a processor that indicates that the processor has reached a predetermined temperature trip point. At this trip point the processor can be programmed to lower its internal operating frequency and/or lower its supply voltage by changing the value of the 6 bit VID that it supplies to the VRD. The final VID setting and the rate at which it transitions to the new VID is programmable within the processor.

If PROCHOT is 100% throttled, it does not mean that the CPU is not executing, but it may mean that the CPU is about to encounter a thermal trip if the processor temperature continues to rise.

PROCHOT is also an input to some processors so that an external controller can force a thermal throttle based on external events.

PROCHOT is no longer asserted by the processor when the temperature drops below the predefined thermal trip point.

Oscillation around the trip point is avoided by the processor by requiring that the temperature be above/below the trip point for a predetermined period of time. A counter inside the processor is used to track this time and it has to be incremented to a max count for an above temperature trip and decremented to zero when below the trip temperature setting, to remove the trip.

The minimum time for  $\overline{PROCHOT}$  assertion is time dependant on the FSB frequency. The minimum time that the processor asserts  $\overline{PROCHOT}$  is estimated to be 187  $\mu$ s.

#### PROCHOT MONITORING

PROCHOT monitoring is meant to achieve two goals. One goal is to measure the percentage of time that PROCHOT is asserted over a programmable time period. The result of this measurement can be read from an 8-bit register where one LSB equals 1/256th of the PROCHOT Time Interval (0.39%). The second goal is to have a status register that indicates, as a coarse percentage, the amount of time a processor has been throttled. This second goal is required in order to communicate information over the NIC using ASF, i.e. status can be sent, not values.

To achieve the first goal, the PROCHOT input is monitored over a period of time as defined by the PROCHOT Time Interval Register. At the end of each time period, the 8-bit measurement is transferred to the Current PROCHOT register. Also at the end of each measurement period, the Current PROCHOT register value is moved to the Average PROCHOT register by adding the new value to the old value and dividing the result by 2. Note that the value that is averaged into the Average PROCHOT register is not the new measurement but rather the previous measurement. If the SMBus writes to the Current PROCHOT register, the capture cycle restarts. Also note, that a strict average of two 8-bit values may result in Average PROCHOT reflecting a value that is one LSB lower than the Current PROCHOT in steady state.

It should be noted that the 8-bit result has a positive bias of one half of an LSB. This is necessary because a value of 00h represents that PROCHOT was not asserted at all during the sampling window. Any amount of throttling results in a reading of 01h.

The following table demonstrates the mapping for the 8-bit result:

| 8-Bit Result | Percentage Thottled         |

|--------------|-----------------------------|

| 0            | Exactly 0%                  |

| 1            | Between 0% and 0.39%        |

| 2            | Between 0.39% and 0.78%     |

|              |                             |

| n            | Between (n-1)/256 and n/256 |

|              |                             |

| 253          | Between 98.4% and 98.8%     |

| 254          | Between 98.8% and 99.2%     |

| 255          | Greater than 99.2%          |

To achieve the second goal, the LM96194 has several comparators that compare the measured percentage reading against several fixed and 1 variable value. The variable value is user programmable.

The result of these comparisons generates several error status bits described in the following table:

| Status Description                               | Comparison Formula                                        |  |  |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| 100% Throttle                                    | PROCHOT was never de-asserted during monitoring interval. |  |  |  |  |  |

| Greater than or equal to 75% and less than 100%  | 193 ≤ measured value and not 100%                         |  |  |  |  |  |