SNVS718E - JUNE 2011 - REVISED FEBRUARY 2013

# LM5064 Negative Voltage System Power Management and Protection IC with PMBus

Check for Samples: LM5064

# **FEATURES**

- Input Voltage Range: -10V to -80V

- Programmable 26 mV or 50 mV Current Limit Threshold with Power Limiting (MOSFET Power Dissipation Limiting)

- Real Time Monitoring of  $V_{\text{IN}},\,V_{\text{OUT}},\,I_{\text{IN}},\,P_{\text{IN}},\,V_{\text{AUX}}$ • with 12-Bit Resolution and 1 kHz Sampling Rate

- **Configurable Circuit Breaker Protection for** Hard Shorts

- Configurable Under-Voltage and Over-Voltage Protection

- **Remote Temperature Sensing with Programmable Warning and Shutdown** Thresholds

- **Detection and Notification of Damaged MOSFET Condition**

- Power Measurement Accuracy: ±4.5% Over Temperature

- **True Input Power Averages Dynamic Power** Readings

- Averaging of  $V_{IN}$ ,  $I_{IN}$ ,  $P_{IN}$ , and  $V_{OUT}$  Over Programmable Interval Ranging from 0.001 to 4 Seconds

- **Programmable WARN and FAULT Thresholds** with SMBA Notification

- **Black Box Capture of Telemetry** Measurements and Device Status Triggered by WARN or FAULT Condition

- I<sup>2</sup>C/SMBus Interface and PMBus Compliant **Command Structure**

- **Full Featured Application Development** Software

- **HTSSOP-28** Package

# **APPLICATIONS**

- **Base Station Power Distribution Systems**

- Intelligent Solid State Circuit Breaker

- -24V/-48V Industrial Systems •

# DESCRIPTION

The LM5064 combines a high performance hot swap controller with a PMBus<sup>TM</sup> compliant SMBus/l<sup>2</sup>C interface to accurately measure, protect and control the electrical operating conditions of systems connected to a backplane power bus. The LM5064 continuously supplies real-time power, voltage, current, temperature and fault data to the system management host via the SMBus interface.

The LM5064 control block includes a unique hot swap architecture that provides current and power limiting to protect sensitive circuitry during insertion of boards into a live system backplane, or any other "hot" power source. A fast acting circuit breaker prevents damage in the event of a short circuit on the output. The input under-voltage and over-voltage levels and hysteresis are configurable, as well as the insertion delay time and fault detection time. A temperature monitoring block on the LM5064 interfaces with a low-cost external diode for monitoring the temperature of the external MOSFET or other thermally sensitive components. The PGD output provides a fast indicator when the input and/or output voltages are outside their programmed ranges.

The LM5064 monitoring circuit computes both the real-time and average values of subsystem operating parameters ( $V_{IN}$ ,  $I_{IN}$ ,  $P_{IN}$ ,  $V_{OUT}$ ) as well as the peak power. Accurate power averaging is accomplished by averaging the product of the input voltage and current. A black box (Telemetry/Fault Snapshot) function captures and stores telemetry data and device status in the event of a warning or a fault.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

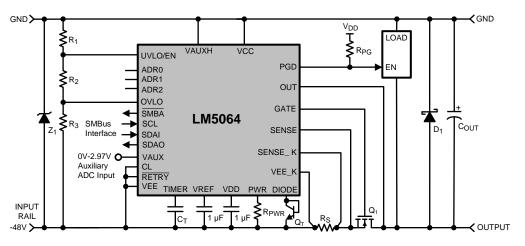

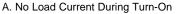

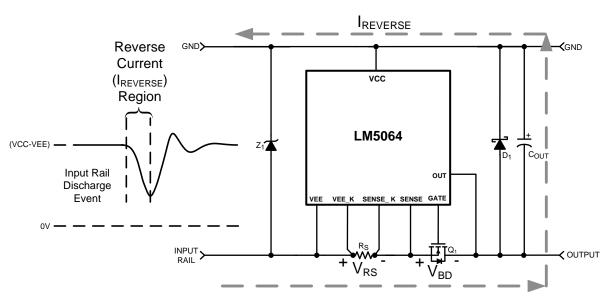

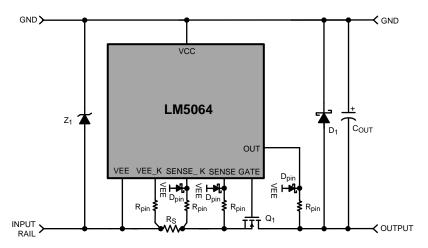

## **Typical Application Circuit**

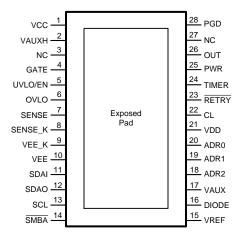

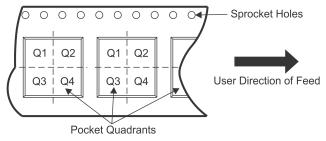

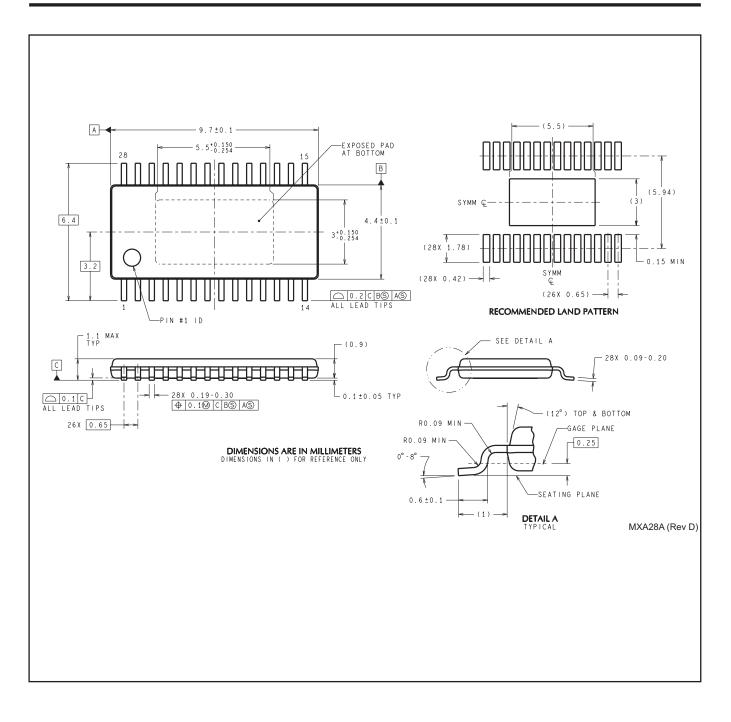

## **Connection Diagram**

#### Top View 28-Lead HTSSOP 9.7 mm × 4.4 mm × 0.9 mm PWP0028A Package

### **PIN DESCRIPTIONS**

| Pin# | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Positive supply input. Connect the VCC pin to the positive voltage rail.                                                                                                                                                                                                                                                                                                         |

| 2    | VAUXH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | High voltage auxiliary input. VCC with respect to VEE is measured by connecting the VAUXH pin to the VCC rail.                                                                                                                                                                                                                                                                   |

| 3    | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No connect. This pin is not internally connected and should not be connected to any signal or power rail.                                                                                                                                                                                                                                                                        |

| 4    | GATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MOSFET gate control signal for fault control of the output. The GATE pin is clamped to VEE through a 12.6V internal zener diode.                                                                                                                                                                                                                                                 |

| 5    | 5 UVLO/EN Under-voltage lockout threshold input. Connecting the UVLO pin to a resistor divider from VCC to VEE will se<br>under-voltage lockout threshold. After the UVLO pin voltage falls below 2.48V, an internal 20 μA current source<br>switched to provide a user settable hysteresis. The UVLO pin can be toggled directly to act as a precision ena<br>After the UVLO threshold voltage is exceeded, the output voltage will begin to transition to V <sub>VEE</sub> as the GATE<br>supplies 52 μA to turn on the MOSFET. |                                                                                                                                                                                                                                                                                                                                                                                  |

| 6    | OVLO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Over-voltage lockout threshold input. Connecting the OVLO pin to a resistor divider from VCC to VEE will set the over-voltage lockout threshold. After the OVLO pin voltage exceeds 2.47V, an internal 21 µA current source is switched to provide a user settable hysteresis. If the OVLO threshold is exceeded, the MOSFET will be immediately disabled to protect the output. |

### **PIN DESCRIPTIONS (continued)**

| Pin# | Name    | Description                                                                                                                                                                                                                                                                                                                                               |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | SENSE   | Current limit and power limit sense input. SENSE provides a direct connection to the MOSFET source and current sense resistor voltage to detect current limit and power limit events. This unfiltered signal will allow the LM5064 to quickly respond during over-current or over-power events.                                                           |

| 8    | SENSE_K | Current telemetry Kelvin sense positive input. SENSE_K is the positive input to a precision differential current sense amplifier. Connecting SENSE_K to the positive terminal of the current sense resistor will provide an accurate current telemetry signal.                                                                                            |

| 9    | VEE_K   | Current telemetry Kelvin sense negative input. The VEE_K pin is the negative input to a precision differential current sense amplifier. Connecting VEE_K to the negative terminal of the current sense resistor will provide an accurate current signal.                                                                                                  |

| 10   | VEE     | Negative supply input. Connect the VEE pin to the negative voltage supply rail. Use a small ceramic bypass capacitor (0.1 $\mu$ F) from the VEE pin to the VCC pin to suppress transient current spikes when the load switch is turned off. The operational voltage range for the VEE pin is -10V to -80V. The VEE pin absolute maximum voltage is -100V. |

| 11   | SDAI    | SMBus data input. The SDAI pin is designed to read PMBus commands using the SMBus communication protocol. SDAI can be connected to SDAO if desired.                                                                                                                                                                                                       |

| 12   | SDAO    | SMBus data output. The SDAO pin is designed to transmit PMBus commands using the SMBus communication protocol. SDAO can be connected to SDAI if desired.                                                                                                                                                                                                  |

| 13   | SCL     | SMBus clock input.                                                                                                                                                                                                                                                                                                                                        |

| 14   | SMBA    | SMBus alert. This pin is connected to an open drain MOSFET which pulls the pin to VEE if a fault is detected.                                                                                                                                                                                                                                             |

| 15   | VREF    | Internal ADC reference output. Connect a 1 $\mu$ F capacitor from the VREF pin to VEE to filter noise imposed on the internal reference output.                                                                                                                                                                                                           |

| 16   | DIODE   | Positive diode sense. The DIODE pin should be connected to the anode of a diode whose cathode is connected to VEE for temperature monitoring.                                                                                                                                                                                                             |

| 17   | VAUX    | Auxiliary pin allows voltage telemetry from an external source. Full scale input of 2.97V.                                                                                                                                                                                                                                                                |

| 18   | ADR2    | Address pin 2. The address pins can be connected to VDD, VEE, or left open to set the PMBus address of the LM5064.                                                                                                                                                                                                                                        |

| 19   | ADR1    | Address pin 1 The address pins can be connected to VDD, VEE, or left open to set the PMBus address of the LM5064.                                                                                                                                                                                                                                         |

| 20   | ADR0    | Address pin 0. The address pins can be connected to VDD, VEE, or left open to set the PMBus address of the LM5064.                                                                                                                                                                                                                                        |

| 21   | VDD     | Internal 4.9V sub-regulator output. VDD must be connected and closely coupled to VEE through a 1 µF ceramic bypass capacitor.                                                                                                                                                                                                                             |

| 22   | CL      | Current limit threshold input. The LM5064 detects current limit events by sensing the voltage across a series resistor. The current limit threshold is set to 26 mV by connecting CL to VDD and 50 mV when CL is connected to VEE.                                                                                                                        |

| 23   | RETRY   | Retry selction pin. Connecting $\overline{\text{RETRY}}$ to VDD sets the LM5064 to lockout after a fault condition is detected. Connecting $\overline{\text{RETRY}}$ to VEE sets the LM5064 to retry after a fault condition.                                                                                                                             |

| 24   | TIMER   | Timing input. Set the insertion time delay and the fault timeout period by connecting a capacitor from the TIMER pin to VEE. The restart time is also set through the TIMER pin when in restart mode.                                                                                                                                                     |

| 25   | PWR     | Power limit input. Connecting a resistor from PWR to VEE sets the maximum power dissipation allowed in the external MOSFET switch. Power is calculated using the current information through the current sense resistor and voltage sensed across the MOSFET.                                                                                             |

| 26   | OUT     | Output voltage sense input. The OUT pin is used to sense the output voltage and calculate the power across the MOSFET switch.                                                                                                                                                                                                                             |

| 27   | NC      | No connect. This pin is not internally connected and should not be connected to any signal or power rail.                                                                                                                                                                                                                                                 |

| 28   | PGD     | Power good monitor output. Open-drain output pulls low during over-current, UVLO, and OVLO. An external pull-up resistor to VDD or external rail is required.                                                                                                                                                                                             |

| EP   | EP      | Exposed pad. Connect to PCB VEE plane using multiple thermal vias.                                                                                                                                                                                                                                                                                        |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

# Absolute Maximum Ratings (1)

| -0.3V to 100V  |

|----------------|

| -0.3V to 16V   |

| -0.3V to 7V    |

| -0.3V to +0.3V |

| -0.3V to 6V    |

|                |

| 2 kV           |

| -65°C to 150°C |

| 150°C          |

|                |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which

operation of the device is intended to be functional. For specifications and test conditions, see the Electrical Characteristics. The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. 2 kV rating for all pins except GATE and PGD which are rated at 1.5 kV and 1 kV respectively. (2)

## **Operating Ratings**

| VCC supply voltage above VEE | 10V to +80V      |

|------------------------------|------------------|

| OUT voltage above VEE        | 0V to +80V       |

| PGD off voltage above VEE    | 0V to +80V       |

| Junction temperature         | -40°C to + 125°C |

### **Electrical Characteristics**

Limits in standard type are for  $T_J = 25^{\circ}$ C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply: VCC-VEE = 48V. See <sup>(1) (2)</sup>.

| Symbol                | Parameter                                  | Conditions                                     | Min   | Тур  | Max  | Units    |

|-----------------------|--------------------------------------------|------------------------------------------------|-------|------|------|----------|

| Input (VCC)           |                                            |                                                | · · · |      |      |          |

| I <sub>IN-EN</sub>    | Input current, enabled                     | VCC - VEE = 48V, UVLO/EN = 5V                  |       | 6    | 8    | mA       |

| POR <sub>IT</sub>     | Threshold voltage to start insertion timer | VCC - VEE increasing                           |       | 8    | 9.2  | V        |

| POR <sub>EN</sub>     | Threshold voltage to enable all functions  | VCC - VEE increasing                           |       | 8.7  | 9.9  | V        |

| POR <sub>EN-HYS</sub> | POR <sub>EN</sub> hysteresis               | VCC - VEE decreasing                           |       | 170  |      | mV       |

| Output (OUT)          |                                            |                                                |       |      |      |          |

| I <sub>OUT-EN</sub>   | OUT bias current, enabled                  | Enabled, OUT = VEE                             |       | -100 |      | nA       |

| I <sub>OUT-DIS</sub>  | OUT bias current, disabled <sup>(3)</sup>  | Disabled, OUT = VEE + 48V                      |       | 135  |      | μA       |

| OVLO/UVLO             |                                            | 1                                              |       |      | 1    | <u> </u> |

| UVLO <sub>TH</sub>    | UVLO/EN threshold                          | UVLO/EN Falling                                | 2.41  | 2.48 | 2.55 | V        |

| UVLO <sub>HYS</sub>   | UVLO/EN hysteresis current                 | UVLO/EN = VEE + 2V                             | 13    | 20   | 26   | μA       |

| UVLO <sub>DEL</sub>   | UVLO delay                                 | Delay to GATE high                             |       | 9    |      | μs       |

| 511                   |                                            | Delay to GATE low                              |       | 12   |      | μs       |

| UVLO <sub>BIAS</sub>  | UVLO/EN bias current                       | UVLO/EN = VEE + 5V                             |       |      | 1    | μA       |

| OVLO <sub>TH</sub>    | OVLO threshold                             |                                                | 2.39  | 2.47 | 2.53 | V        |

| OVLO <sub>HYS</sub>   | OVLO hysteresis current                    | OVLO = VEE + 2.8V                              | -26   | -21  | -13  | μA       |

| OVLO <sub>DEL</sub>   | OVLO delay                                 | Delay to GATE high                             |       | 10   |      | μs       |

| DEL                   |                                            | Delay to GATE low                              |       | 12   |      | μs       |

| OVLO <sub>BIAS</sub>  | OVLO bias current                          | OVLO = 2.3V                                    |       |      | 1    | μA       |

| Power Limit (PWF      | र)                                         |                                                |       |      |      |          |

| PWR <sub>LIM-1</sub>  | Power limit sense voltage<br>(OUT-SENSE)   | OUT – SENSE = 48V, RPWR = 145 k $\Omega$       | 19.5  | 24.5 | 29.5 | mV       |

| PWR <sub>LIM-2</sub>  |                                            | OUT - SENSE = 24V, RPWR = 75 k $\Omega$        |       | 24.7 |      | mV       |

| I <sub>PWR</sub>      | PWR pin current                            | V <sub>PWR</sub> = 2.5V                        |       | -18  |      | μA       |

| R <sub>SAT(PWR)</sub> | PWR pin impedance when disabled            | UVLO/EN = 2.0V                                 |       | 140  |      | Ω        |

| Gate Control (GA      | TE)                                        |                                                |       |      |      |          |

| I <sub>GATE</sub>     | Source current                             | Normal Operation                               | -72   | -52  | -32  | μA       |

|                       | Sink current                               | UVLO/EN < VEE+2V                               | 3.4   | 4.1  | 5.3  | mA       |

|                       |                                            | SENSE - VEE =150 mV, V <sub>GATE</sub> =VEE+5V | 50    | 111  | 180  | mA       |

| V <sub>GATE</sub>     | Gate output voltage in normal operation    | GATE-VEE Voltage                               |       | 12.6 |      | V        |

| Current Limit         |                                            |                                                | i     |      |      |          |

| V <sub>CL</sub>       | Current limit threshold voltage            | CL = VDD <sup>(4)</sup>                        | 23    | 26   | 30   | mV       |

| V <sub>CL</sub>       | Current limit threshold voltage            | CL = VEE or FLOAT <sup>(4)</sup>               | 47    | 50   | 53   | mV       |

| t <sub>CL</sub>       | Response time                              | SENSE-VEE stepped from 0 mV to 80 mV           |       | 54   |      | μs       |

| I <sub>SENSE</sub>    | SENSE input current                        | Enabled, OUT = VEE                             |       | -5   |      | μA       |

|                       |                                            | Disabled, OUT = VCC                            |       | -55  |      | μA       |

| I <sub>SENSE_K</sub>  | SENSE_K input current                      |                                                |       | -10  |      | μA       |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For specifications and test conditions, see the Electrical Characteristics.

(2) Current out of a pin is indicated as a negative value.

(3) OUT bias current (disabled) due to leakage current through an internal 1 MΩ resistance from SENSE to OUT.

(4) CL bit High or Low is set by either the CL pin on startup (if CL = VDD, then High, if CL = VEE or FLOAT, then Low) or by the current limit setting bit in the device setup register.

## **Electrical Characteristics (continued)**

Limits in standard type are for  $T_J = 25^{\circ}$ C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply: VCC-VEE = 48V. See <sup>(1) (2)</sup>.

| Symbol               | Parameter                                                      | Conditions                                                | Min  | Тур  | Max      | Units |

|----------------------|----------------------------------------------------------------|-----------------------------------------------------------|------|------|----------|-------|

| I <sub>VEE_K</sub>   | VEE_K input current                                            |                                                           |      | -10  |          | μA    |

| Circuit Breaker      |                                                                |                                                           |      |      |          |       |

| RT <sub>CB</sub>     | Circuit breaker to current limit                               | CB/CL ratio bit = 0, ILim = 50 mV                         | 1.45 | 1.9  | 2.22     |       |

|                      | ratio: (V <sub>SENSE</sub> -V <sub>VEE</sub> )/V <sub>CL</sub> | CB/CL ratio bit = 1, ILim = 50 mV                         | 2.8  | 3.7  | 4.9      |       |

|                      |                                                                | CB/CL ratio bit = 0, ILim = 26 mV                         |      | 1.8  |          |       |

|                      |                                                                | CB/CL ratio bit = 1, ILim = 26 mV                         |      | 3.6  |          |       |

| V <sub>CB</sub>      | Circuit breaker threshold                                      | CB/CL ratio bit = 0, ILim = 50 mV                         | 72   | 93   | 116      | mV    |

|                      | voltage: (V <sub>SENSE</sub> -V <sub>VEE</sub> )               | CB/CL ratio bit = 1, ILim = 50 mV                         | 144  | 187  | 230      | mV    |

|                      |                                                                | CB/CL ratio bit = 0, ILim = 26 mV                         | 37   | 49   | 59       | mV    |

|                      |                                                                | CB/CL ratio bit = 1, ILim = 26 mV                         | 72   | 93   | 116      | mV    |

| t <sub>CB</sub>      | Circuit breaker response time                                  | SENSE-VEE stepped from 0 mV to 150 mV, time to GATE = VEE |      | 800  |          | ns    |

| Timer (TIMER)        |                                                                |                                                           |      |      |          |       |

| V <sub>TMRH</sub>    | Upper threshold                                                |                                                           | 3.74 | 3.9  | 4.07     | V     |

| V <sub>TMRL</sub>    | Lower threshold                                                | Restart cycles                                            | 1.09 | 1.2  | 1.39     | V     |

|                      |                                                                | End of 8th cycle                                          |      | 0.3  |          | V     |

|                      |                                                                | Re-enable threshold                                       |      | 0.3  |          | V     |

| I <sub>TIMER</sub>   | Insertion time current                                         |                                                           | -5.9 | -4.8 | -3.3     | μA    |

|                      | Sink current, end of insertion time                            | TIMER pin = VEE+2V                                        | 1    | 1.5  | 2        | mA    |

|                      | Fault detection current                                        | SENSE-VEE=V <sub>CL</sub>                                 | -95  | -74  | -50      | μA    |

|                      | Fault sink current                                             |                                                           | 1.7  | 2.4  | 3.2      | μA    |

| DC <sub>FAULT</sub>  | Fault restart duty cycle                                       |                                                           |      | 0.5  |          | %     |

| t <sub>FAULT</sub>   | Fault to GATE = VEE delay                                      | TIMER pin reaches the upper threshold                     |      | 15   |          | μs    |

| Power Good (PG       | D)                                                             |                                                           |      |      |          |       |

| PGD <sub>TH</sub>    | Threshold measured at OUT -                                    | OUT – SENSE Decreasing                                    | 1.18 | 1.24 | 1.31     | V     |

|                      | SENSE                                                          | OUT – SENSE Increasing                                    | 2.44 | 2.5  | 2.56     | V     |

| PGD <sub>VOL</sub>   | Output low voltage                                             | I <sub>SINK</sub> = 2 mA                                  |      | 50   | 150      | mV    |

| PGD <sub>IOH</sub>   | Off leakage current                                            | V <sub>PGD</sub> = 80V                                    |      |      | 5        | μA    |

| ADC and MUX          |                                                                |                                                           |      |      |          |       |

|                      | Resolution                                                     |                                                           |      | 12   |          | Bits  |

| INL                  | Integral non-linearity                                         | ADC only                                                  |      | ±4   |          | LSB   |

| t <sub>ACQUIRE</sub> | Acquisition + conversion time                                  | Any Channel                                               |      | 100  |          | μs    |

| t <sub>RR</sub>      | Acquisition round robin time                                   | Cycle all channels                                        |      | 1    |          | ms    |

| Internal Referenc    | e                                                              |                                                           |      |      |          |       |

| V <sub>REF</sub>     | Reference voltage                                              |                                                           | 2.93 | 2.97 | 3.02     | V     |

| Telemetry Accura     | acy <sup>(5)</sup>                                             |                                                           |      |      |          |       |

| IIN <sub>FSR</sub>   | Current input full scale range                                 | CL= VEE <sup>(6)</sup>                                    |      | 74.9 |          | mV    |

|                      |                                                                | CL = VDD <sup>(6)</sup>                                   |      | 38.1 |          | mV    |

| IIN <sub>LSB</sub>   | Current input LSB                                              | CL= VEE <sup>(6)</sup>                                    |      | 18.3 |          | μV    |

|                      |                                                                | CL = VDD <sup>(6)</sup>                                   |      | 9.3  |          | μV    |

| VAUX <sub>FSR</sub>  | VAUX input full scale range                                    |                                                           |      | 2.96 | <u> </u> | V     |

(5) Full scale range depends on both the VREF value and the gain/attenuation of the current/voltage channel.

(6) CL bit High or Low is set by either the CL pin on startup (if CL = VDD, then High, if CL = VEE or FLOAT, then Low) or by the current limit setting bit in the device setup register.

### **Electrical Characteristics (continued)**

Limits in standard type are for  $T_J = 25^{\circ}$ C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply: VCC-VEE = 48V. See <sup>(1) (2)</sup>.

| Symbol                 | Parameter                                | Conditions                                          | Min  | Тур  | Max  | Units |

|------------------------|------------------------------------------|-----------------------------------------------------|------|------|------|-------|

| VAUX <sub>LSB</sub>    | VAUX input LSB                           |                                                     |      | 724  |      | μV    |

| VAUXH <sub>FSR</sub>   | VAUXH input full scale range             |                                                     |      | 88.9 |      | V     |

| VAUXH <sub>LSB</sub>   | VAUXH input LSB                          |                                                     |      | 21.7 |      | mV    |

| OUT <sub>LSB</sub>     | OUT pin LSB                              |                                                     |      | 21.7 |      | mV    |

| IIN <sub>ACC</sub>     | Input current accuracy                   | SENSE_K-VEE_K = 50 mV, CL = VEE (Note 6)            | -3.0 |      | 3.0  | %     |

| V <sub>ACC</sub>       | VAUX, VAUXH, OUT                         | VAUXH-VEE=48V,OUT - VEE= 48V, VAUX = 2.8V           | -2.7 |      | 2.7  | %     |

| PINACC                 | Input power accuracy                     | VCC-VEE = 48V, SENSE_K-VEE_K = 50 mV, CL<br>= VDD   | -4.5 |      | 4.5  | %     |

| Diode Temperatu        | re Sensor                                |                                                     |      |      |      |       |

| T <sub>ACC</sub>       | Temperature accuracy using local diode   | $T_A = 25^{\circ}C \text{ to } 85^{\circ}C$         |      | 2    |      | °C    |

|                        | Remote diode resolution                  |                                                     |      | 9    |      | bits  |

| IDIODE                 | External diode current source            | High Level                                          |      | 250  | 325  | μA    |

|                        |                                          | Low Level                                           |      | 9.4  |      | μA    |

|                        | Diode current ratio                      |                                                     |      | 25.9 |      |       |

| VAUX                   |                                          |                                                     |      |      |      |       |

| I <sub>IN</sub>        | Input current                            | VAUX = 3V                                           |      |      | 1    | μA    |

| VDD Regulation         |                                          |                                                     |      |      |      |       |

| VDD <sub>OUT</sub>     | VDD regulated output                     | IDD = 0 mA                                          | 4.6  | 4.9  | 5.15 | V     |

|                        |                                          | IDD = -10 mA                                        |      | 4.8  |      | V     |

| VDD <sub>ILIM</sub>    | VDD current limit                        | VDD = 0V                                            | -25  | -30  | -42  | mA    |

| VDD <sub>POR</sub>     | VDD voltage reset threshold              | VDD Rising                                          |      | 4.1  |      | V     |

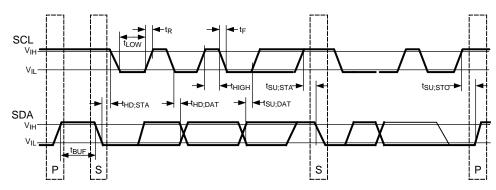

| PMBus Pin Thres        | holds (SCL, SDAI/O, SMBA) <sup>(7)</sup> |                                                     |      |      |      |       |

| V <sub>IL</sub>        | Data, clock input low voltage            | With respect to VEE                                 |      |      | 0.9  | V     |

| V <sub>IH</sub>        | Data, clock input high voltage           | With respect to VEE                                 | 2.1  |      | 5.5  | V     |

| V <sub>OL</sub>        | Data output low voltage                  | I <sub>SINK</sub> = 3 mA                            | 0    |      | 0.4  | μA    |

| I <sub>LEAK</sub>      | Input leakage current                    | SDAI, $\overline{\text{SMBA}}$ , SCL = 5V above VEE |      |      | 1    | μA    |

| Pin Strappable Th      | nresholds (CL, RETRY)                    |                                                     |      |      |      |       |

| V <sub>IH</sub>        | Input high voltage                       |                                                     | 3    |      |      | V     |

| I <sub>LEAK</sub>      | Input leakage current                    | CL, RETRY = 5V                                      |      | 5    |      | μA    |

| Thermal <sup>(8)</sup> |                                          | ·                                                   |      |      |      |       |

| θ <sub>JA</sub>        | Junction to ambient                      |                                                     |      | 30   |      | °C/W  |

| $\theta_{JC}$          | Junction to case                         |                                                     |      | 4    |      | °C/W  |

(7) PMBus communication clock rate at final test is 400 kHz.

(8) Junction to ambient thermal resistance is highly application and board layout dependent. Specified thermal resistance values for the package specified is based on a 4-layer, 4"x3", 2/1/1/2 oz. Cu board as per JEDEC standards is used. For detailed information on soldering plastic HTSSOP packages refer to the Packaging Data Book.

Texas **INSTRUMENTS**

SNVS718E -JUNE 2011-REVISED FEBRUARY 2013

www.ti.com

Submit Documentation Feedback

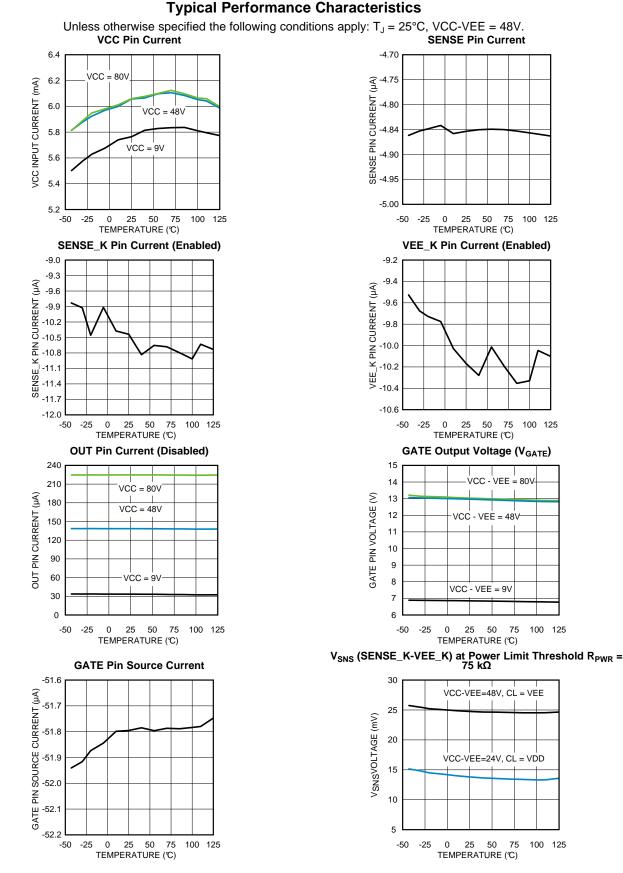

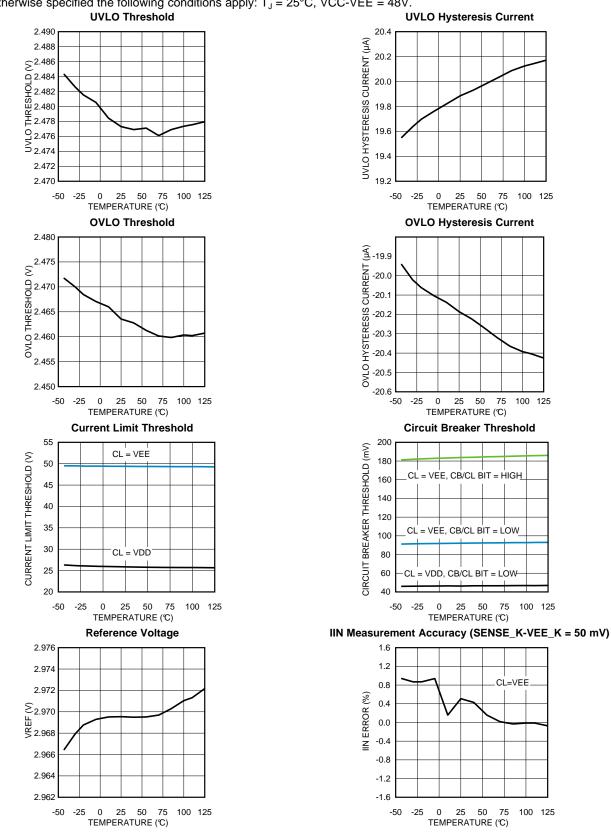

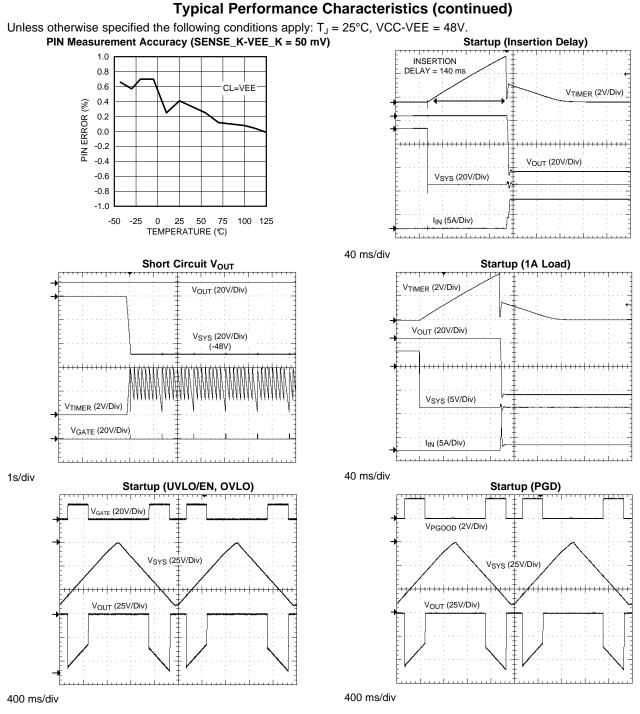

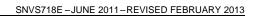

### **Typical Performance Characteristics (continued)**

Unless otherwise specified the following conditions apply:  $T_J = 25^{\circ}C$ , VCC-VEE = 48V.

Texas **ISTRUMENTS**

www.ti.com

SNVS718E -JUNE 2011-REVISED FEBRUARY 2013

TEXAS INSTRUMENTS

SNVS718E – JUNE 2011 – REVISED FEBRUARY 2013

www.ti.com

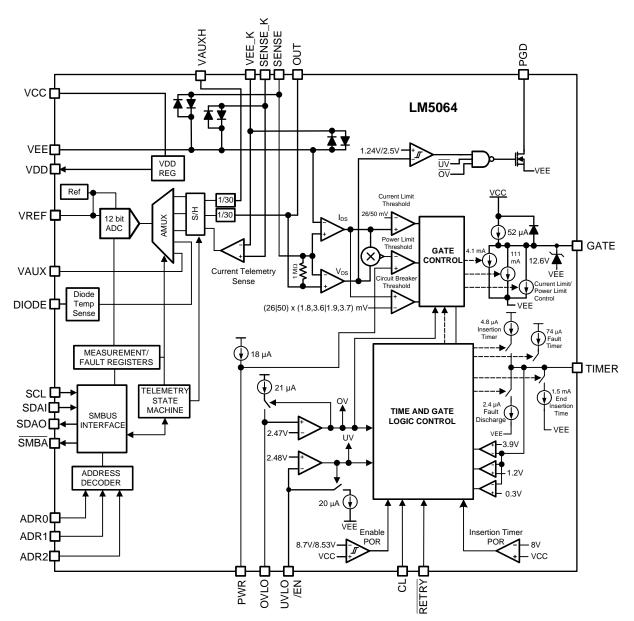

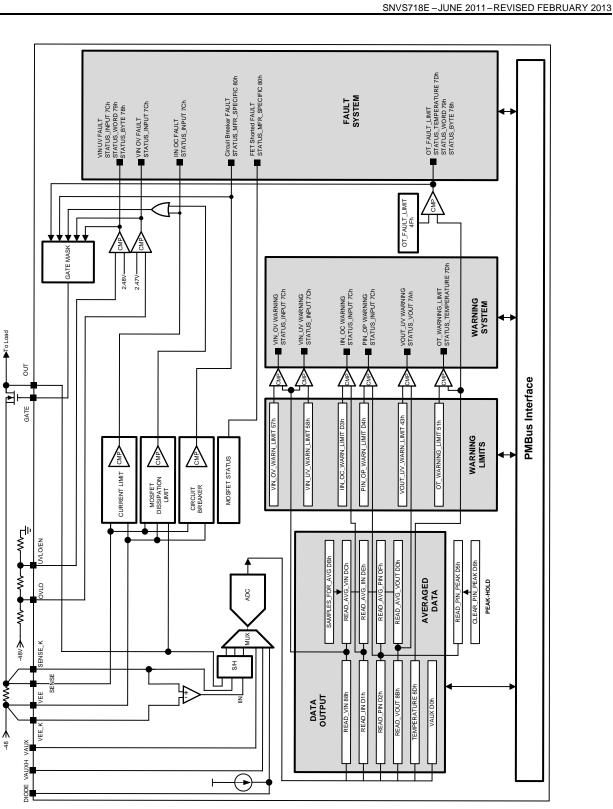

Figure 1. Block Diagram

## FUNCTIONAL DESCRIPTION

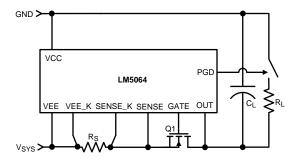

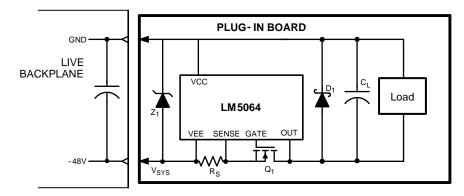

The LM5064 is designed to control the in-rush current to the load upon insertion of a circuit card into a live backplane or other "hot" power source, thereby limiting the voltage sag on the backplane's supply and the dv/dt of the voltage applied to the load. The effect from the insertion event on other circuits in the system is minimized, preventing possible unintended resets. A controlled shutdown when the circuit card is removed can also be implemented using the LM5064.

In addition to a programmable current limit, the LM5064 monitors and limits the maximum power dissipation in the series pass device ( $Q_1$ ) to maintain operation within the device's Safe Operating Area (SOA). Either current limiting or power limiting for an extended period of time (user defined) results in the shutdown of the series pass device. In this event, the LM5064 can latch off or repetitively retry based on the hardware setting of the RETRY pin. Once started, the number of retries can be set to 0, 1, 2, 4, 8, 16, or infinite. The circuit breaker function quickly switches off the series pass device upon detection of a severe over-current condition. Programmable under-voltage lockout (UVLO) and over-voltage lockout (OVLO) circuits shut down the LM5064 when the system input voltage ( $V_{SYS}$ ) is outside the desired operating range.

The telemetry capability of the LM5064 provides intelligent monitoring of the input voltage, output voltage, input current, input power, temperature, and an auxiliary input. The LM5064 also provides a peak capture of the input power and programmable hardware averaging of the input voltage, current, power, and output voltage. Warning thresholds which trigger the SMBA pin may be programmed for input and output voltage, current, power and temperature via the PMBus interface. Additionally, the LM5064 is capable of detecting damage to the external MOSFET,  $Q_1$ .

### **Operating Voltage**

The LM5064 operating voltage is the voltage supplied between VCC and VEE (VCC-VEE) which has an operating range of 10V to 80V with a 100V transient capability. All signals to the IC are referenced to the VEE voltage which acts as the effective return path for the IC.

### Power Up Sequence

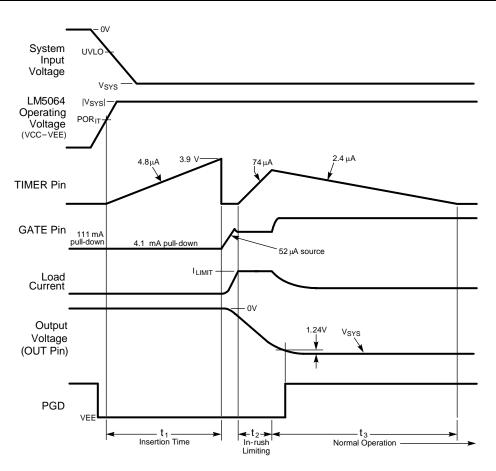

Referring to Figure 2, as the system voltage ( $V_{SYS}$ ) initially increases, the external N-channel MOSFET ( $Q_1$ ) is held off by an internal 111 mA pull-down current at the GATE pin. The strong pull-down current at the GATE pin prevents an inadvertent turn on as the MOSFET's gate-to-drain (Miller) capacitance is charged. Additionally, the TIMER pin is initially held at VEE. When the operating voltage of the LM5064 (VCC - VEE) reaches the POR<sub>IT</sub> threshold, the insertion time begins. During the insertion time, the capacitor at the TIMER pin ( $C_T$ ) is charged by a 4.8 µA current source, and  $Q_1$  is held off by a 4.1 mA pull-down current at the GATE pin regardless of the input voltage. The insertion time delay allows ringing and transients on  $V_{SYS}$  to settle before  $Q_1$  is enabled. The insertion time ends when the TIMER pin voltage reaches 3.9V.  $C_T$  is then quickly discharged by an internal 1.5 mA pull-down current. The GATE pin then switches on  $Q_1$  when the operating voltage exceeds the UVLO threshold. If the operating voltage is above the UVLO threshold at the end of the insertion time, ( $t_1$  in Figure 2) the GATE pin sources 52 µA to charge the gate capacitance of  $Q_1$ . The maximum voltage on GATE is limited by an internal 12.6V zener diode to VEE.

As the voltage at the OUT pin transitions to  $V_{SYS}$ , the LM5064 monitors the drain current and power dissipation of MOSFET Q<sub>1</sub>. In-rush current limiting and/or power limiting circuits actively control the current delivered to the load. During the in-rush limiting interval (t<sub>2</sub> in Figure 2), an internal 74 µA fault timer current source charges C<sub>T</sub>. If Q<sub>1</sub>'s power dissipation and the input current reduce below their respective limiting thresholds before the TIMER pin reaches 3.9V, the 74 µA current source is switched off, and C<sub>T</sub> is discharged by the internal 2.4 µA current sink (t<sub>3</sub> in Figure 2). The in-rush limiting will no longer engage unless a current-limit condition occurs.

If the TIMER pin voltage reaches 3.9V before in-rush current limiting or power limiting ceases during  $t_2$ , a fault is declared and  $Q_1$  is turned off. See the Fault Timer & Restart section for a complete description of the fault mode.

The LM5064 will assert the SMBA pin after the operating voltage has exceeded the POR threshold to indicate that the volatile memory and device settings are in their default state. The CONFIG\_PRESET bit within the MFR\_SPECIFIC\_17 register (E1h) indicates default configuration of warning thresholds and device operation and will remain high until a CLEAR\_FAULTS command is received.

www.ti.com

Figure 2. Power Up Sequence

## Gate Control

A current source provides the charge at the GATE pin to enhance the N-Channel MOSFET's gate ( $Q_1$ ). During normal operating conditions ( $t_3$  in Figure 2) the gate of  $Q_1$  is held charged by an internal 52 µA current source. The GATE pin peak voltage is roughly 12.6V, which will force a  $V_{GS}$  across  $Q_1$  of 12.6V under normal operation. When the system voltage is initially applied, the GATE pin is held low by a 111 mA pull-down current. This helps prevent an inadvertent turn on of  $Q_1$  through its drain-gate capacitance as the applied system voltage increases.

During the insertion time ( $t_1$  in Figure 2), the GATE pin is held low by a 4.1 mA pull-down current. This maintains  $Q_1$  in the off-state until the end of  $t_1$ , regardless of the voltage on  $V_{SYS}$  or UVLO/EN. Following the insertion time, during  $t_2$  in Figure 2, the gate voltage of  $Q_1$  is modulated to keep the current or power dissipation level from exceeding the programmed levels. While in the current or power limiting mode, the TIMER pin capacitor is charging. If the current and power limiting cease before the TIMER pin reaches 3.9V, the TIMER pin capacitor then discharges, and the circuit begins normal operation. If the in-rush limiting condition persists such that the TIMER pin reached 3.9V during  $t_2$ , the GATE pin is then pulled low by the 4.1 mA pull-down current. The GATE pin is then held low until either a power up sequence is initiated (RETRY pin to VDD), an automatic retry is attempted (RETRY pin to VEE or floating), or a PMBus ON/OFF command is initiated. See the Fault Timer & Restart section. If the operating voltage falls below the UVLO threshold, or rises above the OVLO threshold, the GATE pin is pulled low by the 4.1 mA pull-down current to switch off  $Q_1$ .

## **Current Limit**

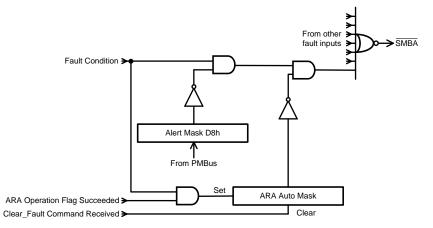

The current limit threshold is reached when the voltage across the sense resistor  $R_S$  (SENSE to VEE) exceeds the internal voltage limit of 26 mV or 50 mV depending on whether the CL pin is connected to VDD or VEE, respectively. In the current limiting condition, the GATE voltage is controlled to limit the current in MOSFET Q<sub>1</sub>. While the current limit circuit is active, the fault timer is active as described in the Fault Timer & Restart section. If the load current falls below the current limit threshold before the end of the Fault Timeout Period, the LM5064 resumes normal operation. If the current limit condition persists for longer than the Fault Timeout Period set by C<sub>T</sub>, the IIN OC Fault bit in the STATUS\_INPUT (7Ch) register, the INPUT bit in the STATUS\_WORD (79h) register, and IIN\_OC/PFET\_OP\_FAULT bit in the DIAGNOSTIC\_WORD (E1h) register will be toggled high and SMBA pin will be asserted. SMBA toggling can be disabled using the ALERT\_MASK (D8h) register. For proper operation, the R<sub>S</sub> resistor value should be no higher than 200 m $\Omega$ . Higher values may create instability in the current limit control loop. The current limit threshold pin value may be overridden by setting appropriate bits in the DEVICE\_SETUP register (D9h).

### Circuit Breaker

If the load current increases rapidly (e.g., the load is short circuited), the current in the sense resistor ( $R_S$ ) may exceed the current limit threshold before the current limit control loop is able to respond. If the current exceeds 1.9x or 3.7x (CL = VEE) the current limit threshold,  $Q_1$  is quickly switched off by the 111 mA pull-down current at the GATE pin, and a Fault Timeout Period begins. When the voltage across  $R_S$  falls below the circuit breaker (CB) threshold, the 111 mA pull-down current at the GATE pin is switched off, and the gate voltage of  $Q_1$  is then determined by the current limit or the power limit functions. If the TIMER pin reaches 3.9V before the current limiting or power limiting condition ceases,  $Q_1$  is switched off by the 4.1 mA pull-down current at the GATE pin as described in the Fault Timer & Restart section. A circuit breaker event will cause the CIRCUIT\_BREAKER\_FAULT bit in the STATUS\_MFR\_SPECIFIC (80h) and DIAGNOSTIC\_WORD (E1h) registers to be toggled high, and SMBA pin will be asserted unless this feature is disabled using the ALERT\_MASK (D8h) register. The circuit breaker pin configuration may be overridden by setting appropriate bits in the DEVICE\_SETUP (D9h) register.

### Power Limit

An important feature of the LM5064 is the MOSFET power limiting. The power limit function can be used to maintain the maximum power dissipation of MOSFET  $Q_1$  within the device SOA rating. The LM5064 determines the power dissipation in  $Q_1$  by monitoring its drain-source voltage (OUT to SENSE), and the drain current through the  $R_S$  (SENSE to VEE). The product of the current and voltage is compared to the power limit threshold programmed by the resistor at the PWR pin. If the power dissipation reaches the limiting threshold, the GATE voltage is modulated to regulate the current in  $Q_1$ . While the power limit condition persists for longer than the Fault Timeout Period set by the timer capacitor,  $C_T$ , the IIN OC Fault bit in the STATUS\_INPUT (7Ch) register, the INPUT bit in the STATUS\_WORD (79h) register, and the IIN\_OC/PFET\_OP\_FAULT bit in the DIAGNOSTIC\_WORD (E1h) register will be toggled high and SMBA pin will be asserted unless this feature is disabled using the ALERT\_MASK (D8h) register.

### Fault Timer & Restart

When the current limit or power limit threshold is reached during turn-on, or as a result of a fault condition, the gate-to-source voltage of  $Q_1$  is modulated to regulate the load current and power dissipation in  $Q_1$ . When either limiting function is active, a 74 µA fault timer current source charges the external capacitor ( $C_T$ ) at the TIMER pin as shown in Figure 2(Fault Timeout Period). If the fault condition subsides during the Fault Timeout Period before the TIMER pin reaches 3.9V, the LM5064 returns to the normal operating mode and  $C_T$  is discharged by the 1.5 mA current sink. If the TIMER pin reaches 3.9V during the Fault Timeout Period,  $Q_1$  is switched off by a 4.1 mA pull-down current at the GATE pin. The subsequent restart procedure then depends on the selected retry configuration.

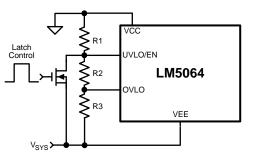

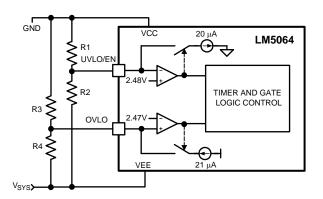

If the RETRY pin is high (VDD), the LM5064 latches the GATE pin low at the end of the Fault Timeout Period.  $C_T$  is then discharged to VEE by the 2.4  $\mu$ A fault current sink. The GATE pin is held low by the 4.1 mA pull-down current until a power up sequence is externally initiated by cycling the operating voltage (VCC-VEE), or momentarily pulling the UVLO/EN pin below its threshold with an open-collector or open-drain device as shown in Figure 3. The voltage at the TIMER pin must be <0.3V for the restart procedure to be effective. The TIMER\_LATCHED\_OFF bit in the DIAGNOSTIC\_WORD (E1h) register will remain high while the latched off condition persists.

Figure 3. Latched Fault Restart Control

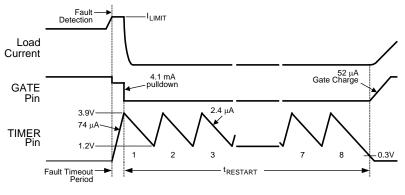

The LM5064 provides an automatic restart sequence which consists of the TIMER pin cycling between 3.9V and 1.2V eight times after the Fault Timeout Period, as shown in Figure 4. The period of each cycle is determined by the 74  $\mu$ A charging current, and the 2.4  $\mu$ A discharge current, and the value of the capacitor C<sub>T</sub>. When the TIMER pin reaches 0.3V during the eighth high-to-low ramp, the 52  $\mu$ A current source at the GATE pin turns on Q<sub>1</sub>. If the fault condition is still present, the Fault Timeout Period and the restart sequence repeat. The RETRY pin allows selecting no retries or infinite retries. Finer control of the retry behavior can be achieved through the DEVICE\_SETUP (D9h) register. Retry counts of 0, 1, 2, 4, 8, 16 or infinite may be selected by setting the appropriate bits in the DEVICE\_SETUP (D9h) register.

Figure 4. Restart Sequence

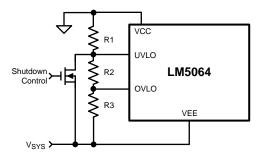

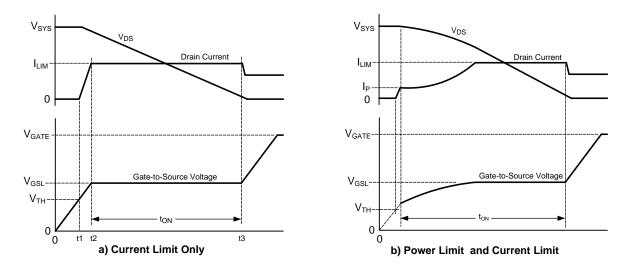

### Under-Voltage Lockout (UVLO)

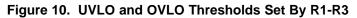

The series pass MOSFET (Q<sub>1</sub>) is enabled when the input supply voltage (V<sub>SYS</sub>) is within the operating range defined by the programmable under-voltage lockout (UVLO) and over-voltage lockout (OVLO) levels. Typically, the UVLO level at V<sub>SYS</sub> is set with a resistor divider (R1-R3) as shown in Figure 5. Referring to the Block Diagram when V<sub>SYS</sub> is below the UVLO level, the internal 20  $\mu$ A current source at UVLO/EN is enabled, the current source at OVLO is off, and Q<sub>1</sub> is held off by the 4.1 mA pull-down current at the GATE pin. As V<sub>SYS</sub> is increased, raising the voltage at UVLO/EN above its threshold with respect to VEE, the 20  $\mu$ A current source at UVLO/EN is written source at UVLO/EN is switched off, increasing the voltage at UVLO/EN, providing hysteresis for this threshold. With the UVLO/EN pin above its threshold, Q<sub>1</sub> is switched on by the 52  $\mu$ A current source at the GATE pin if the insertion time delay has expired.

See the Application Information section for a procedure to calculate the values of the threshold setting resistors (R1-R3). The minimum possible UVLO level at  $V_{SYS}$  can be set by connecting the UVLO/EN pin to VCC. In this case Q<sub>1</sub> is enabled after the insertion time when the operating voltage (VCC-VEE) reaches the POR threshold. After power up an UVLO condition will cause the INPUT bit in the STATUS\_WORD (79h) register, the VIN\_UV\_FAULT bit in the STATUS\_INPUT (7Ch) register, and the VIN\_UNDERVOLTAGE\_FAULT bit in the DIAGNOSTIC\_WORD (E1h) registers to be toggled high and SMBA pin will be pulled low unless this feature is disabled using the ALERT\_MASK (D8h) register.

M5064

#### www.ti.com

#### Over-Voltage Lockout (OVLO)

The series pass MOSFET (Q<sub>1</sub>) is enabled when the input supply voltage (V<sub>SYS</sub>) is within the operating range defined by the programmable under-voltage lockout (UVLO) and over-voltage lockout (OVLO) levels. If V<sub>SYS</sub> raises the OVLO pin voltage above its threshold (2.47V above VEE), Q<sub>1</sub> is switched off by the 4.1 mA pull-down current at the GATE pin, denying power to the load. When the OVLO pin is above its threshold, the internal 21  $\mu$ A current source at OVLO is switched on, raising the voltage at OVLO to provide threshold hysteresis. When V<sub>SYS</sub> is reduced below the OVLO level Q<sub>1</sub> is re-enabled. An OVLO condition will toggle the VIN\_OV\_FAULT bit in the STATUS\_INPUT (7Ch) register, the INPUT bit in the STATUS\_WORD (79h) register and the VIN\_OVERVOLTAGE\_FAULT bit in the DIAGNOSTIC\_WORD (E1h) register. The SMBA pin will be pulled low unless this feature is disabled using the ALERT\_MASK (D8h) register.

#### Shutdown Control

The load current can be remotely switched off by taking the UVLO/EN pin below its threshold with an open collector or open drain device, as shown in Figure 5. Upon releasing the UVLO/EN pin the LM5064 switches on the load current with in-rush current and power limiting.

Figure 5. Shutdown Control

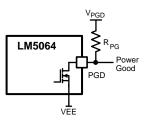

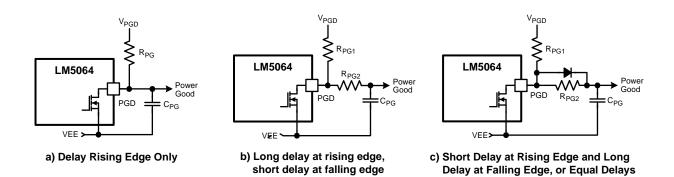

#### Power Good Pin

The Power Good output indicator pin (PGD) is connected to the drain of an internal N-channel MOSFET. An external pull-up resistor is required at PGD to an appropriate voltage to indicate the status to downstream circuitry. The off-state voltage at the PGD pin must be more positive than VEE, and can be up to 80V above VEE with transient capability to 100V. PGD is switched high at the end of the turn-on sequence when the voltage from OUT to SENSE (the external MOSFET's V<sub>DS</sub>) decreases below 1.24V. PGD switches low if the MOSFET's V<sub>DS</sub> increases passed 2.5V, if the system input voltage goes below the UVLO threshold or above the OVLO threshold, or if a fault is detected. However, the PGD output cannot stay low when the operating voltage (VCC-VEE) is less than 2V.

#### **VDD Sub-Regulator**

The LM5064 contains an internal linear sub-regulator which steps down the VCC voltage to generate a 4.9V rail (above VEE) used for powering low voltage circuitry. The VDD sub-regulator should be used as the pull-up supply for the CL, RETRY, ADR2, ADR1, ADR0 pins if they are to be tied high. It may also be used as the pull-up supply for the PGD and the SMBus signals (SDA, SCL, SMBA). The VDD sub-regulator is not designed to drive high currents. Careful consideration of internal power dissipation should be practiced when VDD is loaded with other integrated circuits. The VDD pin is current limited to 30 mA in order to protect the LM5064 in the event of a short. The sub-regulator requires a ceramic bypass capacitance (terminated to VEE) having a value of 1 µF or greater to be placed as close to the VDD pin as the PCB layout allows.

www.ti.com

### **Remote Temperature Sensing**

The LM5064 is designed to measure temperature remotely using an MMBT3904 NPN transistor. The base and collector of the MMBT3904 should be connected to the DIODE pin and the emitter to VEE. Place the MMBT3904 near the device that requires temperature sensing. If the temperature of the hot swap pass MOSFET,  $Q_1$ , is to be measured, the MMBT3904 should be placed as close to  $Q_1$  as the layout allows. The temperature is measured by means of a change in the diode voltage in response to a step in current supplied by the DIODE pin. The DIODE pin sources a constant 9.4 µA but pulses 250 µA once every millisecond in order to measure the diode temperature. Care must be taken in the PCB layout to keep the parasitic resistance between the DIODE pin and the MMBT3904 low so as not to degrade the measurement. Additionally, a small 1000 pF bypass capacitor should be placed in parallel with the MMBT3904 (collector to emitter) to reduce the effects of noise. The temperature can be read using the READ\_TEMPERATURE\_1 PMBus command (8Dh). The default limits of the LM5064 will cause SMBA pin to be pulled low if the measured temperature exceeds 125°C and will disable  $Q_1$  if the temperature exceeds 150°C. These thresholds can be reprogrammed via the PMBus interface using the OT\_WARN\_LIMIT (51h) and OT\_FAULT\_LIMIT (4Fh) commands. If the temperature measurement and protection capability of the LM5064 are not used, the DIODE pin should be connected to VEE.

Erroneous temperature measurements may result when the device input voltage is below the minimum operating voltage (10V) due to VREF dropping out below the nominal voltage (2.97V). At higher ambient temperatures, this measurement could read a value higher than the OT\_FAULT\_LIMIT, and will trigger a fault, disabling  $Q_1$ . In this case, the faults should be removed and the device reset by writing a 0h, followed by an 80h to the OPERATION (01h) register.

### Damaged MOSFET Detection

The LM5064 is able to detect whether the external MOSFET,  $Q_1$ , is damaged under certain conditions. If the voltage across the sense resistor exceeds 4 mV while the GATE voltage is low or the internal logic indicates that the GATE should be low, the EXT\_MOSFET\_SHORTED bit in the STATUS\_MFR\_SPECIFIC (80h) and DIAGNOSTIC\_WORD (E1h) registers will be toggled high and the SMBA pin will be asserted unless this feature is disabled using the ALERT\_MASK register (D8h). This method effectively determines whether  $Q_1$  is shorted because of damage present between the drain and gate and/or drain and source.

### **Enabling/Disabling and Resetting**

The output can be disabled at any time during normal operation by either pulling the UVLO/EN pin to below its threshold or the OVLO pin above its threshold, causing the GATE voltage to be forced low with a pull-down strength of 4.1 mA. Toggling the UVLO/EN pin will also reset the LM5064 from a latched-off state due to an over-current or over-power limit condition which has caused the maximum allowed number of retries to be exceeded. While the UVLO/EN or OVLO pins can be used to disable the output they have no effect on the volatile memory or address location of the LM5064. User stored values for address, device operation, and warning and fault levels programmed via the SMBus are preserved while the LM5064 is powered regardless of the state of the UVLO/EN and OVLO pins.The output may also be enabled or disabled by writing 80h or 0h to the OPERATION (01h) register. To re-enable after a fault, the fault condition should be cleared and the OPERATION (01h) register should be written with a 0h and then 80h.

The SMBus address of the LM5064 is captured based on the states (VEE, NC, VDD) of the ADR0, ADR1, and ADR2 pins during turn-on and is latched into a volatile register once VDD has exceeded its POR threshold of 4.1V. Reassigning or postponing the address capture is accomplished by holding the VREF pin to VEE. Pulling the VREF pin low will also reset the logic and erase the volatile memory of the LM5064. Once released, the VREF pin will charge up to its final value and the address will be latched into a volatile register once the voltage at the VREF exceeds 2.55V.

### **APPLICATION INFORMATION**

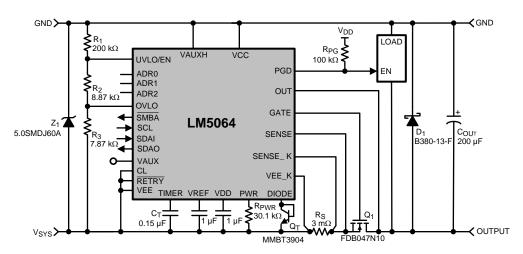

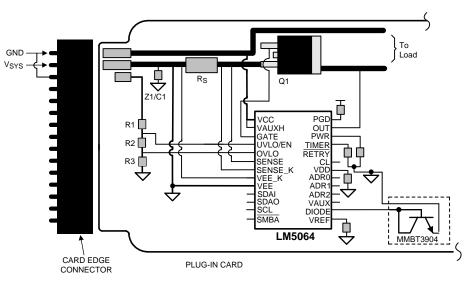

Figure 6. Typical Application Circuit

#### **DESIGN-IN PROCEDURE**

Refer to Figure 6 for a Typical Application Circuit. The following is a step-by-step procedure for hardware design of the LM5064. This procedure refers to section numbers that provide detailed information on the following design steps. The recommended design-in procedure is as follows:

**MOSFET Selection:** Determine the MOSFET based on breakdown voltage, current and power ratings.

**Current Limit,**  $R_s$ : Determine the current limit threshold (I<sub>LIM</sub>). This threshold must be higher than the normal maximum load current, allowing for tolerances in the current sense resistor value and the LM5064 Current Limit threshold voltage. Use Equation 1 to determine the value for  $R_s$ .

**Power Limit Threshold:** Determine the maximum allowable power dissipation for the series pass MOSFET ( $Q_1$ ), using the device's SOA information. Use Equation 2 to determine the value for  $R_{PWR}$ . Note that many MOSFET manufacturers do not accurately specify the device SOA so it is usually beneficial to choose a conservative value when selecting  $R_{PWR}$ .

**Turn-on Time and TIMER Capacitor, C<sub>T</sub>:** Determine the value for the timing capacitor at the TIMER pin (C<sub>T</sub>) using Equation 7 and Equation 8. The fault timeout period  $(t_{FAULT})$  **MUST** be longer than the circuit's turn-on time. The turn-on time can be estimated using the equations in the TURN-ON TIME section, but should be verified experimentally. Review the resulting insertion time and the restart timing if retry is enabled.

**UVLO, OVLO:** Choose option A, B, C, or D from the UVLO, OVLO section to set the UVLO and OVLO thresholds and hysteresis. Use the procedure for the appropriate option to determine the resistor values at the UVLO/EN and OVLO pins.

### MOSFET SELECTION

It is recommended that the external MOSFET  $(Q_1)$  selection is based on the following criteria:

- The BV<sub>DSS</sub> rating should be greater than the maximum system voltage (V<sub>SYS</sub>), plus ringing and transients which can occur when the circuit card, or adjacent cards, are inserted or removed.

- The maximum continuous current rating should be based on the current limit threshold (for example, 26 mV/R<sub>S</sub> for CL = VDD), not the maximum load current, since the circuit can operate near the current limit threshold continuously.

- The Pulsed Drain Current spec ( $I_{DM}$ ) must be greater than the current threshold for the circuit breaker function (49/93/187 mV/R<sub>S</sub>, depending on CL and CB configuration).

www.ti.com

- The SOA (Safe Operating Area) chart of the device, and the thermal properties, should be used to determine the maximum power dissipation threshold set by the R<sub>PWR</sub> resistor. The programmed maximum power dissipation should have a reasonable margin from the maximum power defined by the MOSFET's SOA curve. If the device is set to infinitely retry, the MOSFET will be repeatedly stressed during fault restart cycles. The MOSFET manufacturer should be consulted for guidelines.

-  $R_{DS(on)}$  should be sufficiently low such that the power dissipation at maximum load current ( $I_{LIM}^2 \times R_{DS(on)}$ ) does not raise its junction temperature above the manufacturer's recommendation.

- The gate-to-source voltage provided by the LM5064 can be as high as 12.6V. Q<sub>1</sub> must be able to tolerate this voltage for its V<sub>GS</sub> rating. An additional zener diode can be added from GATE to VEE to lower this voltage and limit the peak V<sub>GS</sub>.

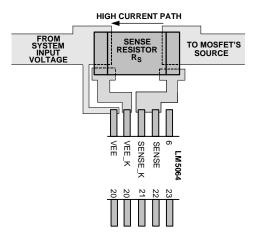

### CURRENT LIMIT (R<sub>s</sub>)

The LM5064 monitors the current in the external MOSFET  $Q_1$  by measuring the voltage across the sense resistor ( $R_S$ ), connected from SENSE to VEE. The required resistor value is calculated from:

$$R_s = \frac{V_{CL}}{I_{LIM}}$$

(1)

where  $I_{LIM}$  is the desired current limit threshold. If the voltage across  $R_S$  reaches  $V_{CL}$ , the current limit circuit modulates the gate of  $Q_1$  to regulate the current at  $I_{LIM}$ . While the current limiting circuit is active, the fault timer is active as described in the Fault Timer & Restart section. For proper operation,  $R_S$  must be less than 200 m $\Omega$ .

$V_{CL}$  can be set to either 26 mV or 50 mV via hardware and/or software. This setting defaults to use of CL pin which, when connected to VDD is 26 mV, or VEE is 50 mV. The value, when powered, can be set via the PMBus with the DEVICE\_SETUP (D9h) command, which defaults to the 26 mV setting.

Once the desired setting is known, calculate the shunt based on that input voltage and maximum current. While the maximum load current in normal operation can be used to determine the required power rating for resistor  $R_S$ , basing it on the current limit value provides a more reliable design since the circuit can operate near the current limit threshold continuously. The resistor's surge capability must also be considered since the circuit breaker threshold is 1.9 or 3.7 times the current limit threshold.

Connections from  $R_S$  to the LM5064 should be made using Kelvin techniques. In the suggested layout of Figure 7 the small pads at the lower corners of the sense resistor connect only to the sense resistor terminals, and not to the traces carrying the high current. With this technique, only the voltage across the sense resistor is applied to SENSE\_K, SENSE, and VEE\_K, eliminating the voltage drop across the high current solder connections.

Figure 7. Sense Resistor Connections

#### POWER LIMIT THRESHOLD

(2)

The LM5064 determines the power dissipation in the external MOSFET ( $Q_1$ ) by monitoring the drain current (the current in  $R_S$ ) and the  $V_{DS}$  of  $Q_1$  (OUT to SENSE pins). The resistor at the PWR pin ( $R_{PWR}$ ) sets the maximum power dissipation for  $Q_1$ , and is calculated from the following equation:

$$R_{PWR} = 1.25 \times 10^5 \times R_S \times P_{MOSEET(IIM)}$$

where  $P_{MOSFET(LIM)}$  is the desired power limit threshold for  $Q_1$ , and  $R_S$  is the current sense resistor described in the CURRENT LIMIT ( $R_S$ ) section. For example, if  $R_S$  is 3 m $\Omega$ ,  $V_{IN}$  = 48V, and the desired power limit threshold is 80W,  $R_{PWR}$  calculates to 30.1 k $\Omega$  (standard 1% value). If  $Q_1$ 's power dissipation reaches the threshold  $Q_1$ 's gate is modulated to regulate the load current, keeping  $Q_1$ 's power from exceeding the threshold. For proper operation of the power limiting feature,  $R_{PWR}$  must be  $\leq 150 \text{ k}\Omega$ . While the power limit is reached during startup, or if the output voltage falls due to a severe over-load or short circuit. The programmed maximum power dissipation should have a reasonable margin from the maximum power defined by the SOA chart, especially if retry is enabled, because the MOSFET will be repeatedly stressed during fault restart cycles. The MOSFET manufacturer should be consulted for guidelines. If the application does not require use of the power limit function the PWR pin can be left open. The accuracy of the power limit function at turn-on may degrade if a very low power dissipation limit is set. The reason for this caution is that the voltage across the sense resistor, which is monitored and regulated by the power limit circuit, is lowest at turn-on when the regulated current is at a minimum. The voltage across the sense resistor during power limit can be expressed as follows:

$$V_{\text{SENSE}} = I_{\text{LIM}} x R_{\text{S}} = \frac{R_{\text{S}} x P_{\text{MOSFET(LIM)}}}{V_{\text{DS}}}$$

(3)

where  $I_{LIM}$  is the current in  $R_S$ , and  $V_{DS}$  is the voltage across  $Q_1$ . For example, if the power limit is set at 80W with  $R_S = 3 \text{ m}\Omega$ , and  $V_{DS} = 48V$  the sense resistor voltage calculates to 5.0 mV, which is comfortably regulated by the LM5064. However, if the power limit is set lower (e.g., 25W), the sense resistor voltage calculates to 1.6 mV. At this low level noise and offsets within the LM5064 may degrade the power limit accuracy. To maintain accuracy, the sense resistor voltage should not be less than 3 mV.

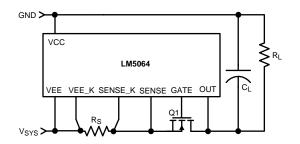

#### **TURN-ON TIME**

The output turn-on time depends on whether the LM5064 operates in current limit, or in both power limit and current limit, during turn-on.

**A)** Turn-on with current limit only: The current limit threshold ( $I_{LIM}$ ) is determined by the current sense resistor ( $R_S$ ). If the current limit threshold is less than the current defined by the power limit threshold at maximum  $V_{DS}$  the circuit operates only at the current limit threshold during turn-on. Referring to Figure 8(A), as the load current reaches  $I_{LIM}$ , the gate-to-source voltage is controlled at GATE to maintain the current at  $I_{LIM}$ . As the output voltage reaches its final value ( $V_{DS} \cong 0V$ ) the drain current reduces to its normal operating value. The time for the OUT pin voltage to transition from zero volts to  $V_{SYS}$  is equal to:

$$t_{on} = \frac{|V_{SYS}| C_L}{I_{LIM}}$$

(4)

where  $C_L$  is the load capacitance. For example, if  $V_{SYS} = -48V$ ,  $C_L = 200 \ \mu$ F, and  $I_{LIM} = 8.7A$ ,  $t_{ON}$  calculates to 1.1 ms. The maximum instantaneous power dissipated in the MOSFET is 418W. This calculation assumes the time from  $t_1$  to  $t_2$  in Figure 9 (A) is small compared to  $t_{ON}$ , the load does not draw any current until after the output voltage has reached its final value, and PGD switches high (Figure 8 (A)). The Fault Timeout Period must be set longer than  $t_{ON}$  to prevent a fault shut-down before the turn-on sequence is complete.

If the load draws current during the turn-on sequence (Figure 8 (B)), the turn-on time is longer than the above calculation, and is approximately equal to:

$$t_{ON} = -(R_L \times C_L) \times \ln \left[ \frac{(I_{L|M} \times R_L) - |V_{SYS}|}{(I_{L|M} \times R_L)} \right]$$

(5)

where  $R_L$  is the load resistance. The Fault Timeout Period must be set longer than  $t_{ON}$  to prevent a fault shutdown before the turn-on sequence is complete.

B. Load Draws Current During Turn-On

#### Figure 8. Current During Turn-On

**B)** Turn-On with Power Limit and Current Limit: The maximum allowed power dissipation in  $Q_1$  ( $P_{MOSFET(LIM)}$ ) is defined by the resistor at the PWR pin, and the current sense resistor  $R_S$ . See the POWER LIMIT THRESHOLD section. If the current limit threshold ( $I_{LIM}$ ) is higher than the current defined by the power limit threshold at maximum  $V_{DS}$  ( $P_{MOSFET(LIM)}/|V_{SYS}|$ ) the circuit operates initially in the power limit mode when the  $V_{DS}$  of  $Q_1$  is high, and then transitions to current limit mode as the current increases to  $I_{LIM}$  and  $V_{DS}$  decreases. Assuming the load ( $R_L$ ) is not connected during turn-on, the time for the output voltage to reach its final value is approximately equal to:

$$t_{\text{ON}} = \frac{C_{\text{L}} x V_{\text{SYS}}^2}{2 x P_{\text{MOSFET(LIM)}}} + \frac{C_{\text{L}} x P_{\text{MOSFET(LIM)}}}{2 x I_{\text{LIM}}^2}$$

(6)

For example, if  $V_{SYS} = -48V$ ,  $C_L = 200 \ \mu\text{F}$ ,  $I_{LIM} = 8.7\text{A}$ , and  $P_{MOSFET(LIM)} = 80W$ ,  $t_{ON}$  calculates to  $\approx 3.0 \text{ ms}$ , and the initial current level ( $I_P$ ) is approximately 1.67A. The Fault Timeout Period must be set longer than  $t_{ON}$ .

### TIMER CAPACITOR, C<sub>T</sub>

(8)

The TIMER pin capacitor ( $C_T$ ) sets the timing for the insertion time delay, fault timeout period, and the restart timing of the LM5064.

**A) Insertion Delay -**Upon applying the system voltage ( $V_{SYS}$ ) to the circuit, the external MOSFET ( $Q_1$ ) is held off during the insertion time ( $t_1$  in Figure 2) to allow ringing and transients at  $V_{SYS}$  to settle. Since each backplane's response to a circuit card plug-in is unique, the worst case settling time must be determined for each application. The insertion time starts when  $V_{SYS}$  reaches the POR threshold, at which time the internal 4.8 µA current source charges  $C_T$  from 0V to 3.9V. The required capacitor value is calculated from:

$$C_{\rm T} = \frac{t_1 x \, 4.8 \,\mu A}{3.9 \,\rm V} = t_1 x \, 1.2 \, x \, 10^{-6} \tag{7}$$

For example, if the desired insertion delay is 125 ms,  $C_T$  calculates to 0.15  $\mu$ F. At the end of the insertion delay,  $C_T$  is quickly discharged by a 1.5 mA current sink.

**B)** Fault Timeout Period -During in-rush current limiting or upon detection of a fault condition where the current limit and/or power limit circuits regulate the current through  $Q_1$ , the fault timer current source (74  $\mu$ A) is switched on to charge  $C_T$ . The Fault Timeout Period is the time required for the TIMER pin voltage to reach 3.9V, at which time  $Q_1$  is switched off. The required capacitor value for the desired Fault Timeout Period t<sub>FAULT</sub> is calculated from:

$$C_{T} = \frac{t_{FAULT} \times 74 \mu A}{3.9 V} = t_{FAULT} \times 1.9 \times 10^{-5}$$