SNVS151F - NOVEMBER 2000 - REVISED APRIL 2013

## LM3712 Microprocessor Supervisory Circuits with Separate Watchdog Timer Output, Power Fail Input and Manual Reset

Check for Samples: LM3712

#### **FEATURES**

- Standard Reset Threshold Voltage: 3.08V

- Custom Reset Threshold Voltages: For Other Voltages between 2.2V and 5.0V in 10mV Increments. Contact TI.

- No External Components Required

- Manual-Reset Input

- RESET Output

- Precision Supply Voltage Monitor

- Factory Programmable Reset and Watchdog Timeout Delays

- Separate Watchdog Output

- Separate Power Fail Comparator

- Available in DSBGA Package for Minimum Footprint

- ±0.5% Reset Threshold Accuracy at Room Temperature

- ±2% Reset Threshold Accuracy Over Temperature Extremes

- Reset Assertion Down to 1V V<sub>CC</sub>

- 28 μA V<sub>CC</sub> Supply Current

#### **APPLICATIONS**

- Embedded Controllers and Processors

- Intelligent Instruments

- Automotive Systems

- Critical µP Power Monitoring

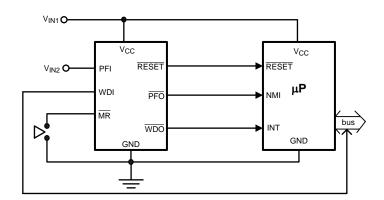

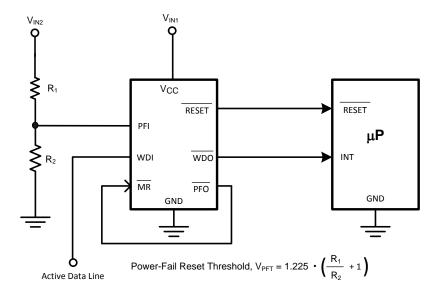

#### **Typical Application**

## DESCRIPTION

The LM3712 series of microprocessor supervisory circuits provide the maximum flexibility for monitoring power supplies and battery controlled functions in systems without backup batteries. The LM3712 series are available in a 9-bump DSBGA package.

Built-in features include the following:

Reset: Reset is asserted during power-up, power-down, and brownout conditions. RESET is specified down to  $V_{CC}$  of 1.0V.

Manual Reset Input: An input that asserts reset when pulled low.

Power-Fail Input: A 1.225V threshold detector for power fail warning, or to monitor a power supply other than  $V_{\rm CC}$ .

Watchdog Timer: The WDI (Watchdog Input) monitors one of the  $\mu$ P's output lines for activity. If no output transition occurs during the watchdog timeout period, the watchdog output (WDO) pulls low.

ATA.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

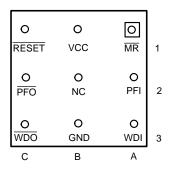

## **Connection Diagram**

Figure 1. Top View (looking from the coating side) DSBGA 9 Bump Package BPA09

## **PIN DESCRIPTIONS**

| Bump No. | Name     | Function                                                                                                                                                                                                                                                                                                                               |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1       | MR       | Manual-Reset input. When $\overline{\text{MR}}$ is less than $V_{\text{MRT}}$ (Manual Reset Threshold) $\overline{\text{RESET}}$ is engaged.                                                                                                                                                                                           |

| B1       | $V_{CC}$ | Power Supply input.                                                                                                                                                                                                                                                                                                                    |

| C1       | RESET    | Reset Logic Output. Pulses low for $t_{RP}$ (Reset Timeout Period) when triggered, and stays low whenever $V_{CC}$ is below the reset threshold or when $\overline{MR}$ is below $V_{MRT}$ . It remains low for $t_{RP}$ after either $V_{CC}$ rises above the reset threshold, or after $\overline{MR}$ input rises above $V_{MRT}$ . |

| C2       | PFO      | Power-Fail Logic Output. When PFI is below V <sub>PFT</sub> PFO goes low; otherwise, PFO remains high.                                                                                                                                                                                                                                 |

| C3       | WDO      | Watchdog Output. If no digital activity is detected on WDI (Watchdog Input) for a period exceeding $t_{\text{WD}}$ , this output pulls low.                                                                                                                                                                                            |

| В3       | GND      | Ground reference for all signals.                                                                                                                                                                                                                                                                                                      |

| А3       | WDI      | Watchdog Input Transition Monitor: If no transition activity occurs for a period exceeding $t_{WD}$ (Watchdog Timeout Period), reset is engaged.                                                                                                                                                                                       |

| A2       | PFI      | Power-Fail Comparator Input. When PFI is less than V <sub>PFT</sub> (Power-Fail Reset Threshold), the PFO goes low; otherwise, PFO remains high.                                                                                                                                                                                       |

| B2       | NC       | No Connect. Test input used at factory only. Leave floating.                                                                                                                                                                                                                                                                           |

Product Folder Links: LM3712

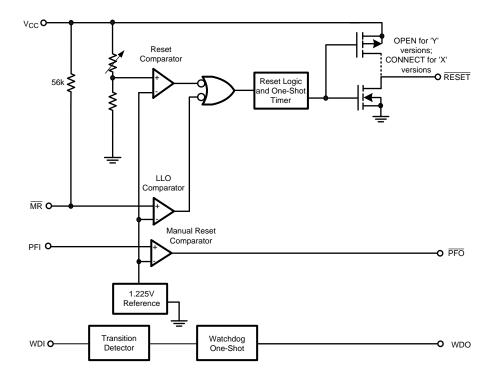

#### **Block Diagram**

Table 1. Table Of Functions

| Part Number | Active Low<br>Reset | Active<br>High Reset | Output<br>(X = totem-pole)<br>(Y = open-drain) | Reset Timeout<br>Period | Watchdog<br>Timeout Period | Manual<br>Reset | Power Fail<br>Comparator |

|-------------|---------------------|----------------------|------------------------------------------------|-------------------------|----------------------------|-----------------|--------------------------|

| LM3712      | x                   |                      | X, Y <sup>(1)</sup>                            | Customized              | Customized                 | x               | x                        |

(1) = available upon request. Contact TI

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ABSOLUTE MAXIMUM RATINGS(1)(2)

| Supply Voltage (V <sub>CC</sub> ) |                            | -0.3V to 6.0V |

|-----------------------------------|----------------------------|---------------|

| All Other Inputs                  | $-0.3V$ to $V_{CC} + 0.3V$ |               |

| ESD Ratings <sup>(3)</sup>        | Human Body Model           | 1.5kV         |

|                                   | Machine Model              | 150V          |

| Power Dissipation                 | See <sup>(4)</sup>         |               |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed conditions.

- (2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

- (3) The Human Body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.

- (4) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance, θ<sub>J-A</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperture is calculated using:

P (MAX) = T<sub>J</sub>(MAX) T<sub>A</sub>

$\theta_{1-\lambda}$

Where the value of  $\theta_{\text{J-A}}$  for the DSBGA package is 220°C/W.

Copyright © 2000–2013, Texas Instruments Incorporated

SNVS151F - NOVEMBER 2000-REVISED APRIL 2013

## **OPERATING RATINGS**(1)

Temperature Range −40°C ≤ T<sub>J</sub> ≤ 85°C

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed conditions.

#### **ELECTRICAL CHARACTERISTICS**

Limits in the standard typeface are for  $T_J = 25$ °C and limits in **boldface type** apply over full operating range. Unless otherwise specified:  $V_{CC} = +2.2V$  to 5.5V.

| Symbol                                   | Parameter                                   | Conditions                                                                                                                                                   | Min                        | Тур                         | Max                         | Units                                 |

|------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|-----------------------------|---------------------------------------|

| POWER SI                                 | JPPLY                                       |                                                                                                                                                              | -                          | *                           |                             | *                                     |

| V <sub>CC</sub>                          | Operating Voltage<br>Range: V <sub>CC</sub> |                                                                                                                                                              | 1.0                        |                             | 5.5                         | V                                     |

| I <sub>CC</sub>                          | V <sub>CC</sub> Supply Current              | All inputs = V <sub>CC</sub> ; all outputs floating                                                                                                          |                            | 28                          | 50                          | μΑ                                    |

| RESET TH                                 | RESHOLD                                     |                                                                                                                                                              |                            |                             |                             |                                       |

| V <sub>RST</sub>                         | Reset Threshold                             | V <sub>CC</sub> falling                                                                                                                                      | -0.5<br><b>-2</b>          | V <sub>RST</sub>            | +0.5<br>+2                  | %                                     |

|                                          |                                             | V <sub>CC</sub> falling: T <sub>A</sub> = 0°C to 70°C                                                                                                        | -1.5                       |                             | +1.5                        |                                       |

| $V_{RSTH}$                               | Reset Threshold<br>Hysteresis               |                                                                                                                                                              |                            | 0.0032•V <sub>RST</sub>     |                             | mV                                    |

| t <sub>RP</sub>                          | Reset Timeout Period                        | Reset Timeout Period = E, J, N, S<br>Reset Timeout Period = F, K, P, T<br>Reset Timeout Period = G, L, Q, U<br>Reset Timeout Period = H, M, R, V             | 1<br>20<br>140<br>1120     | 1.4<br>28<br>200<br>1600    | 2<br>40<br>280<br>2240      | ms                                    |

| $t_{RD}$                                 | V <sub>CC</sub> to Reset Delay              | V <sub>CC</sub> falling at 1mV/μs                                                                                                                            |                            | 20                          |                             | μs                                    |

| RESET                                    | _                                           |                                                                                                                                                              |                            |                             |                             |                                       |

| $V_{OL}$                                 | RESET                                       | $V_{CC} > 1.0V$ , $I_{SINK} = 50\mu A$                                                                                                                       |                            |                             | 0.3                         |                                       |

|                                          |                                             | $V_{CC} > 1.2V$ , $I_{SINK} = 100 \mu A$                                                                                                                     |                            |                             | 0.3                         |                                       |

|                                          |                                             | $V_{CC} > 2.25V$ , $I_{SINK} = 900\mu A$                                                                                                                     |                            |                             | 0.3                         |                                       |

|                                          |                                             | $V_{CC} > 2.7V$ , $I_{SINK} = 1.2mA$                                                                                                                         |                            |                             | 0.3                         | V                                     |

|                                          |                                             | $V_{CC} > 4.5V$ , $I_{SINK} = 3.2mA$                                                                                                                         |                            |                             | 0.4                         | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| $V_{OH}$                                 | RESET                                       | $V_{CC} > 2.25V$ , $I_{SOURCE} = 300\mu A$                                                                                                                   | 0.8 V <sub>CC</sub>        |                             |                             |                                       |

|                                          |                                             | $V_{CC} > 2.7V$ , $I_{SOURCE} = 500\mu A$                                                                                                                    | 0.8 V <sub>CC</sub>        |                             |                             |                                       |

|                                          |                                             | $V_{CC} > 4.5V$ , $I_{SOURCE} = 800\mu A$                                                                                                                    | V <sub>CC</sub> - 1.5V     |                             |                             |                                       |

| WDI                                      |                                             |                                                                                                                                                              |                            |                             |                             |                                       |

| WDI                                      | Watchdog Input Current                      |                                                                                                                                                              | -1                         |                             | +1                          | μA                                    |

| $WDI_T$                                  | Watchdog Input<br>Threshold                 |                                                                                                                                                              | 0.2•V <sub>CC</sub>        | 1.225                       | 0.8•V <sub>CC</sub>         | V                                     |

| t <sub>WD</sub>                          | Watchdog Timeout<br>Period                  | Watchdog Timeout Period = E, F, G, H<br>Watchdog Timeout Period = J, K, L, M<br>Watchdog Timeout Period = N, P, Q, R<br>Watchdog Timeout Period = S, T, U, V | 4.3<br>71<br>1120<br>17900 | 6.2<br>102<br>1600<br>25600 | 9.3<br>153<br>2400<br>38400 | ms                                    |

| PFI/MR                                   |                                             |                                                                                                                                                              |                            |                             |                             |                                       |

| $V_{PFT}$                                | PFI Input Threshold                         |                                                                                                                                                              | 1.200                      | 1.225                       | 1.250                       | V                                     |

| V <sub>MRT</sub>                         | MR Input Threshold                          | MR, Low                                                                                                                                                      |                            |                             | 0.8                         | .,                                    |

|                                          |                                             | MR, High                                                                                                                                                     | 2.0                        |                             |                             | V                                     |

| V <sub>PFTH</sub> /<br>V <sub>MRTH</sub> | PFI/MR Threshold<br>Hysteresis              | $PFI/\overline{MR}$ falling: $V_{CC} = V_{RST MAX}$ to 5.5V                                                                                                  |                            | 0.0032•V <sub>RST</sub>     |                             | mV                                    |

| I <sub>PFI</sub>                         | Input Current (PFI only)                    |                                                                                                                                                              | -75                        |                             | 75                          | nA                                    |

| $R_{MR}$                                 | MR Pull-up Resistance                       |                                                                                                                                                              | 35                         | 56                          | 75                          | kΩ                                    |

| t <sub>MD</sub>                          | MR to Reset Delay                           |                                                                                                                                                              |                            | 12                          |                             | μS                                    |

| t <sub>MR</sub>                          | MR Pulse Width                              |                                                                                                                                                              | 25                         |                             |                             | μS                                    |

Submit Documentation Feedback

Copyright © 2000–2013, Texas Instruments Incorporated

SNVS151F - NOVEMBER 2000 - REVISED APRIL 2013

## **ELECTRICAL CHARACTERISTICS (continued)**

Limits in the standard typeface are for  $T_J$  = 25°C and limits in **boldface type** apply over full operating range. Unless otherwise specified:  $V_{CC}$  = +2.2V to 5.5V.

| Symbol            | Parameter                                                                            | Conditions                                 | Min                    | Тур                     | Max                   | Units |

|-------------------|--------------------------------------------------------------------------------------|--------------------------------------------|------------------------|-------------------------|-----------------------|-------|

| PFO, WDO          |                                                                                      |                                            |                        |                         |                       |       |

| V <sub>OL</sub>   | PFO, WDO Output<br>Voltage                                                           | $V_{CC} > 2.25V$ , $I_{SINK} = 900\mu A$   |                        |                         | 0.3                   | V     |

|                   |                                                                                      | $V_{CC} > 2.7V$ , $I_{SINK} = 1.2mA$       |                        |                         | 0.3                   |       |

|                   |                                                                                      | $V_{CC} > 4.5V$ , $I_{SINK} = 3.2mA$       |                        |                         | 0.4                   |       |

| V <sub>OH</sub>   |                                                                                      | $V_{CC} > 2.25V$ , $I_{SOURCE} = 300\mu A$ | 0.8 V <sub>CC</sub>    |                         |                       |       |

|                   |                                                                                      | $V_{CC} > 2.7V$ , $I_{SOURCE} = 500\mu A$  | 0.8 V <sub>CC</sub>    |                         |                       |       |

|                   |                                                                                      | $V_{CC} > 4.5V$ , $I_{SOURCE} = 800\mu A$  | V <sub>CC</sub> - 1.5V |                         |                       |       |

| LLO OUTP          | UT                                                                                   |                                            |                        |                         |                       |       |

| V <sub>LLOT</sub> | LLO Output Threshold (V <sub>LLO</sub> – V <sub>RST</sub> , V <sub>CC</sub> falling) |                                            | 1.01•V <sub>RST</sub>  | 1.02•V <sub>RST</sub>   | 1.03•V <sub>RST</sub> | V     |

| $V_{LLOTH}$       | Low-Line Comparator<br>Hysteresis                                                    |                                            |                        | 0.0032•V <sub>RST</sub> |                       | mV    |

| t <sub>CD</sub>   | Low-Line Comparator<br>Delay                                                         | V <sub>CC</sub> falling at 1mV/μs          |                        | 20                      |                       | μs    |

Product Folder Links: LM3712

Copyright © 2000–2013, Texas Instruments Incorporated

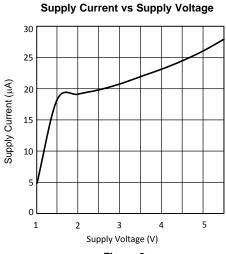

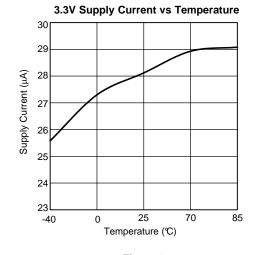

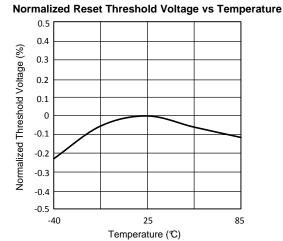

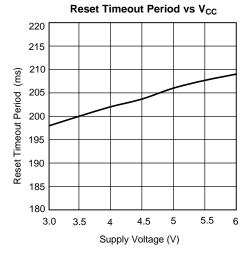

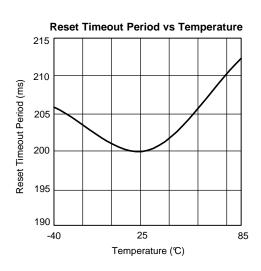

## TYPICAL PERFORMANCE CHARACTERISTICS

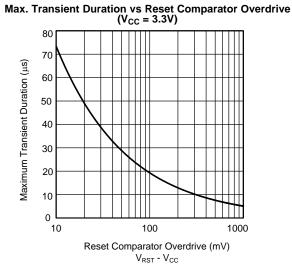

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

Figure 7.

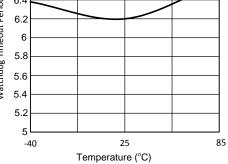

# TYPICAL PERFORMANCE CHARACTERISTICS (continued) Watchdog Timeout Period vs Temperature (two programmed as 6.2ms)

## 6.8 6.6 Watchdog Timeout Period (ms) 6.4 6.2

Figure 8.

#### CIRCUIT INFORMATION

#### **RESET OUTPUT**

The Reset input of a  $\mu P$  initializes the device into a known state. The LM3712 microprocessor supervisory circuits assert a forced reset output to prevent code execution errors during power-up, power-down, and brownout conditions.

RESET is ensured valid for  $V_{CC} > 1V$ . Once  $V_{CC}$  exceeds the reset threshold, an internal timer maintains the output for the reset timeout period. After this interval, reset goes high. The LM3712 offers an active-low RESET.

Any time  $V_{CC}$  drops below the reset threshold (such as during a brownout), the reset activates. When  $V_{CC}$  again rises above the reset threshold, the internal timer starts. Reset holds until  $V_{CC}$  exceeds the reset threshold for longer than the reset timeout period. After this time, reset releases.

The Manual Reset input (MR) will initiate a forced reset also. See the MANUAL RESET INPUT (MR) section.

#### RESET THRESHOLD

The LM3712 family is available with a reset voltage of 3.08V. Other reset thresholds in the 2.20V to 5.0V range, in steps of 10 mV, are available; contact TI for details.

## MANUAL RESET INPUT (MR)

Many  $\mu P$ -based products require a manual reset capability, allowing the operator to initiate a reset. The  $\overline{MR}$  input is fully debounced and provides an internal 56 k $\Omega$  pull-up. When the  $\overline{MR}$  input is pulled below  $V_{\underline{MRT}}$  (1.225V) for more than 25  $\mu s$ , reset is asserted after a typical delay of 12  $\mu s$ . Reset remains active as long as  $\overline{MR}$  is held low, and releases after the reset timeout period expires after  $\overline{MR}$  rises above  $V_{\underline{MRT}}$ . Use  $\overline{MR}$  with digital logic to assert or to daisy chain supervisory circuits. It may be used as another low-line comparator by adding a buffer.

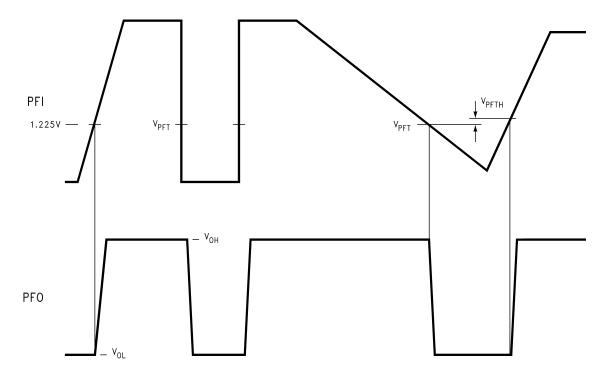

## POWER-FAIL COMPARATOR (PFI/PFO)

The PFI is compared to a 1.225V internal reference,  $V_{PFT}$ . If PFI is less than  $V_{PFT}$ , the Power Fail Output  $\overline{PFO}$  drops low. The power-fail comparator signals a falling power supply, and is driven typically by an external voltage divider that senses either the unregulated supply or another system supply voltage. The voltage divider generally is chosen so the voltage at PFI drops below  $V_{PFT}$  several milliseconds before the main supply voltage drops below the reset threshold, providing advanced warning of a brownout.

The voltage threshold is set by R<sub>1</sub> and R<sub>2</sub> and is calculated as follows:

$$V_{PFT} = \left(\frac{R1 + R2}{R2}\right) \times 1.225V \tag{1}$$

Note this comparator is completely separate from the rest of the circuitry, and may be employed for other functions as needed.

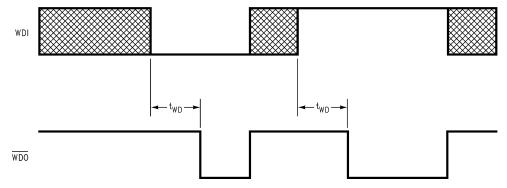

## **WATCHDOG TIMER INPUT (WDI)**

The watchdog timer input monitors one of the microprocessor's output lines for activity. Each time a transition occurs on this monitored line, the watchdog counter is reset. However, if no transition occurs and the timeout period is reached, the LM3712 assumes that the microprocessor has locked up and the watchdog output WDO, is activated.

WDI is a high impedance input. WDO is an active-low totem pole output.

#### SPECIAL PRECAUTIONS FOR THE DSBGA PACKAGE

As with most integrated circuits, the LM3712 is sensitive to exposure from visible and infrared (IR) light radiation. Unlike a plastic encapsulated IC, the DSBGA package has very limited shielding from light, and some sensitivity to light reflected from the surface of the PC board or long wavelength IR entering the die from the side may be experienced. This light could have an unpredictable affect on the electrical performance of the IC. Care should be taken to shield the device from direct exposure to bright visible or IR light during operation.

Product Folder Links: LM3712

#### **DSBGA MOUNTING**

The DSBGA package requires specific mounting techniques which are detailed in TI Application Note AN-1112. Referring to the section *Surface Mount Technology (SMT) Assembly Considerations*, it should be noted that the pad style which must be used with the 9-pin package is the NSMD (non-solder mask defined) type.

For best results during assembly, alignment ordinals on the PC board may be used to facilitate placement of the DSBGA device.

## **Timing Diagrams**

Figure 9. LM3712 Reset Time with  $\overline{\text{MR}}$

Figure 10. PFI Comparator Timing Diagram

Copyright © 2000–2013, Texas Instruments Incorporated

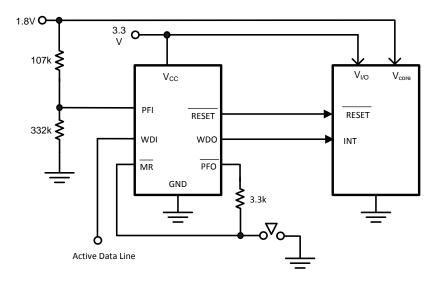

## **Typical Application Circuits**

Figure 11. Monitoring Two Critical Supplies Plus Dataline

Figure 12. Monitoring Two Supplies plus Manual Reset And Dataline

| SNVS151F – NOVEMBER | 2000 - F | REVISED | APRIL | 2013 |

|---------------------|----------|---------|-------|------|

|---------------------|----------|---------|-------|------|

## **REVISION HISTORY**

| CI | Changes from Revision E (April 2013) to Revision F |   |    |  |  |  |

|----|----------------------------------------------------|---|----|--|--|--|

| •  | Changed layout of National Data Sheet to TI format | 1 | 10 |  |  |  |

Product Folder Links: LM3712

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>