SNVS059C - FEBRUARY 2000 - REVISED APRIL 2013

# LM2639 5-Bit Programmable, High Frequency Multi-phase PWM Controller

Check for Samples: LM2639

#### **FEATURES**

- Ultra Fast Load Transient Response

- Enables all Surface-Mount-Design

- Selectable 2, 3, 4 Phase Operation

- Clock Frequency from 40 kHz to 10 MHz

- · Precision Load Current Sharing

- 5-bit Programmable from 3.5V to 1.3V

- VID Code Compatible to VRM 8.X Specification

- Output Voltage is 2.0V for VID Code 11111

- Selectable Internal or External Clock

- Digital 16-Step Soft Start

- Input Under-Voltage Lock-Out, Over-Current Protection

### **APPLICATIONS**

- Servers and Workstations

- High Current, Ultra-Fast Transient Microprocessors

#### DESCRIPTION

The LM2639 provides an attractive solution for power supplies of high power microprocessors (such as Pentium II<sup>TM</sup>, M II<sup>TM</sup>, K6<sup>TM</sup>-2, K6<sup>TM</sup>-3, etc.) exhibiting ultra fast load transients. Compared to a conventional single-phase supply, an LM2639 based multi-phase supply distributes the thermal and electrical loading among components in multiple phases and greatly reduces the corresponding stress in each component. The LM2639 can be programmed to control either a 3-phase converter or a 4-phase converter. Phase shift among the phases is 120° in the case of three phase and 90° with four-phase. Because the power channels are out of phase, there can be significant ripple cancellation for both the input and output current, resulting in reduced input and output capacitor size. Due to the nominal operating frequency of 2 MHz per phase, the size of the output inductors can be greatly reduced which results in a much faster load transient response and a dramatically shrunk output capacitor bank. Microprocessor power supplies with all surface mount components can be easily built.

The internal high speed transconductance amplifier specifies good dynamic performance. The output drive voltages can be adjusted through a resistor divider to control switching loss in the external FETs.

The internal master clock frequency of up to 8 MHz is set by an external reference resistor. An external clock of 10 MHz can also be used to drive the chip to achieve frequency control and multi-chip operation.

The LM2639 also provides input under-voltage lockout with hysteresis and input over-current protection.

lack

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

M II is a trademark of Cyrix Corporation. Pentium II is a trademark of Intel Corporation.

All other trademarks are the property of their respective owners.

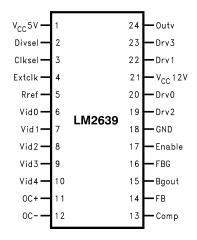

#### **Pin Configuration**

24-Pin Plastic SOIC (Top View) See Package Number DW0024B

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings (1)(2)

| , we end to maximum ratinge |                 |

|-----------------------------|-----------------|

| V <sub>CC</sub> 5V          | 7V              |

| V <sub>CC</sub> 12V         | 20V             |

| Junction Temperature        | 125°C           |

| Power Dissipation (3)       | 1.6W            |

| Storage Temperature         | −65°C to +150°C |

| ESD Susceptibility (4)      | 2 kV            |

| Soldering Time, Temperature | 10 sec., 300°C  |

- (1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating ratings do not imply specified performance limits.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office / Distributors for availability and specifications.

- (3) Maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>JMAX</sub>, the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is calculated using: P<sub>MAX</sub> = (T<sub>JMAX</sub> ¬ T<sub>A</sub>)/θ<sub>JA</sub>. The junction-to-ambient thermal resistance, θ<sub>JA</sub>, for LM2639 is 78°C/W. For a T<sub>JMAX</sub> of 150°C and T<sub>A</sub> of 25°C, the maximum allowable power dissipation is 1.6W.

- (4) ESD ratings for pins DRV0, DRV1, DRV2 and DRV3 is 1kV. ESD rating for all other pins is 2kV.

### Operating Ratings (1)

| - p                        |                |

|----------------------------|----------------|

| V <sub>CC</sub>            | 4.75V to 5.25V |

| Junction Temperature Range | 0°C to 70°C    |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating ratings do not imply specified performance limits.

Submit Documentation Feedback

#### **Electrical Characteristics**

$V_{CC}5V = 5V$ ,  $V_{CC}12V = 12V$  unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A = T_J = +25$ °C. Limits appearing in **boldface** type apply over the entire operating temperature range.

| Symbol              | Parameter                                         | Conditions                                                               | Min            | Тур      | Max             | Units |

|---------------------|---------------------------------------------------|--------------------------------------------------------------------------|----------------|----------|-----------------|-------|

| Vcc5V               | V <sub>CC</sub> 5V Pin Voltage                    |                                                                          | 4.5            | 5.0      | 5.5             | V     |

| Vcc12V              | V <sub>CC</sub> 12V Pin Voltage                   |                                                                          | 10.0           | 12.0     | 18.0            | V     |

| V <sub>DACOUT</sub> | 5-bit DAC Output Voltage                          | See <sup>(1)</sup>                                                       | <i>N</i> −1%   | N        | <i>N</i> +1%    |       |

|                     |                                                   |                                                                          | <b>N</b> −1.5% | N        | <b>N</b> +1.5%  | V     |

| I <sub>CC</sub> 12V | Quiescent V <sub>CC</sub> 12V Current             | Enable = 5V, VID = 00001, DRV<br>Outputs Floating                        |                | 1.3      | 3               | mA    |

| I <sub>CC</sub> 5V  | Operating V <sub>CC</sub> 5V Current              | V <sub>OUT</sub> = 2.00V                                                 |                | 4.3      | 8               | mA    |

| V <sub>REF</sub>    | Rref Pin Voltage                                  |                                                                          |                | 1.225    |                 | V     |

| V <sub>INL</sub>    | Vid0:4, Clksel, Divsel, and Enable                | Logic Low (2)                                                            |                | 1.8      | 1.5             | V     |

| V <sub>INH</sub>    | Pins Logic Threshold                              | Logic High (3)                                                           | 3.5            | 2.8      |                 | V     |

| 1                   | Vid0:4 and Enable Pins Internal<br>Pullup Current | The Corresponding Dia OV                                                 | 60             | 100      | 140             |       |

| I <sub>INL</sub>    | Clksel, Divsel Pins Internal Pullup<br>Current    | The Corresponding Pin = 0V                                               | -10            | 0        | 10              | μA    |

|                     | Gate Driver Resistance When Sinking Current       | $I_{SINK} = 50 \mu A, V_{CC}12V = 14V$                                   |                | 12       |                 | Ω     |

| $V_{DRV}$           | DRV0:3 Output Voltage                             | I <sub>DRV</sub> = 10 mA, V <sub>CC</sub> 12V = 14V, OutV<br>= 12V or 5V | OutV -<br>0.3V | OutV     | OutV + 0.<br>3V | V     |

| t <sub>fall</sub>   | DRV0:3 Fall Time                                  | See (4)                                                                  |                | 7        |                 | ns    |

| I <sub>SRC</sub>    | DRV0:3 Source Current                             | DRV0:3 = 0V, V <sub>CC</sub> 12V = 14V, OutV<br>= 5V                     | 40             | 60       |                 | mA    |

| I <sub>SINK</sub>   | DRV0:3 Sink Current                               | DRV0:3 = 5V, V <sub>CC</sub> 12V = 14V, OutV = 5V                        | 90             | 160      | 250             | mA    |

|                     | B <sub>gOUT</sub> Voltage                         | Current Limit Not Activated                                              |                | 4        |                 | V     |

|                     |                                                   | Current Limit Activated                                                  |                | 0        |                 | V     |

| I <sub>FB</sub>     | FB Pin Bias Current                               | FB = 2V                                                                  |                | 30       |                 | nA    |

|                     | B <sub>gOUT</sub> Sink Current                    | $B_{gOUT} = 1V$                                                          | 1.0            | 2.4      | 5               | mA    |

| Fosc                | Oscillator Frequency                              | 8.02kΩ from Rref Pin to Ground                                           | 7.0            | 8.0      | 8.7             | MHz   |

| $\Delta_{D}$        | DRV0:3 Duty Cycle Match                           | Duty Cycle = 50%                                                         | -1             |          | +1              | %     |

| $\Delta_{ph}$       | DRV0:3 Phase Accuracy                             | Duty Cycle = 50%, F <sub>clock</sub> = 8 MHz                             | -1             |          | +1              | Deg   |

| T <sub>off</sub>    | DIMM Off time                                     | Divide by 4                                                              |                | 22       |                 | 0/    |

| $T_{off}$           | PWM Off time                                      | Divide by 3                                                              |                | 22       |                 | %     |

| OutV                | Drive Voltage Range                               | Output Freq.= 2MHz, V <sub>O</sub> = 2.00V                               | 0              | 12       | Vcc12           | V     |

| V <sub>OCC_CM</sub> | Over-current Comparator Common Mode Range         |                                                                          | 3              |          | 12              | V     |

| IB_OC+              | OC+ Input Bias Current                            | V <sub>IN</sub> = 5V, OC+ = 5V, OC- = 4V                                 | 100            | 145      | 200             | μΑ    |

| IB_OC-              | OC- Input Bias Current                            | V <sub>IN</sub> = 5V, OC+ = 6V, OC- = 5V                                 | 85             | 125      | 165             | μΑ    |

| V <sub>OS_OCC</sub> | Over-current Comparator Input Offset Voltage      | $V_{IN} = 5V$ $V_{IN} = 12V$                                             | 2              | 16<br>21 | 42              | mV    |

| D <sub>MAX</sub>    | Maximun Duty Cycle                                | FB = 0V                                                                  |                | 78       |                 | %     |

| gm                  | Error Amplifier Transconductance                  |                                                                          |                | 1.36     |                 | mmho  |

| V <sub>ramp</sub>   | Ramp Signal Peak-to-Peak Amplitude                |                                                                          |                | 2        |                 | V     |

| I <sub>comp</sub>   | COMP Pin Source Current                           |                                                                          | 250            | 400      | 550             | μA    |

Submit Documentation Feedback

<sup>(1)</sup> The letter *N* stands for the typical output voltages appearing in *italic boldface* type in 5-Bit DAC Output Voltage Table.

(2) Max value of logic low means any voltage below this value is specified to be taken as logic low whereas a voltage higher than this value is not specified to be taken as a logic low.

Min value of logic high means any voltage above this value is specified to be taken as logic high whereas a voltage lower than this value is not specified to be taken as a logic high.

When driving bipolar FET drivers in the typical application circuit.

SNVS059C - FEBRUARY 2000-REVISED APRIL 2013

www.ti.com

### **Electrical Characteristics (continued)**

$V_{CC}5V = 5V$ ,  $V_{CC}12V = 12V$  unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A = T_J = +25$ °C. Limits appearing in **boldface** type apply over the entire operating temperature range.

| Symbol               | Parameter                      | Conditions                | Min | Тур  | Max | Units |  |

|----------------------|--------------------------------|---------------------------|-----|------|-----|-------|--|

| I <sub>comp</sub>    | COMP Pin Sink Current          |                           | 160 | 280  | 400 | μA    |  |

| V <sub>comp_hi</sub> | COMP Pin High Clamp            |                           |     | 2.9  |     | V     |  |

| V <sub>comp_lo</sub> | COMP Pin Low Clamp             |                           |     | 0.19 |     | V     |  |

| V <sub>POR</sub>     | Power On Reset Trip Point      | Vcc5V Pin Voltage Rising  |     | 4.0  |     | \/    |  |

|                      |                                | Vcc5V Pin Voltage Falling |     | 3.6  |     | V     |  |

|                      | Vcc12V Minimum Working Voltage | See (5)                   |     | 3.8  |     | V     |  |

| t <sub>SS</sub>      | Soft Start Delay               | F <sub>OSC</sub> = 8MHz   |     | 1.6  |     | ms    |  |

<sup>(5)</sup> When Vcc12V pin goes below this voltage, all DRV pins go to 0V.

Submit Documentation Feedback

Copyright © 2000–2013, Texas Instruments Incorporated

# **5-BIT DAC OUTPUT VOLTAGE TABLE**

| Symbol              | Parameter                                         | Conditions     | Typical | Units |

|---------------------|---------------------------------------------------|----------------|---------|-------|

| V <sub>DACOUT</sub> | 5-Bit DAC Output Voltages for Different VID Codes | VID4:0 = 01111 | 1.30    | V     |

|                     |                                                   | VID4:0 = 01110 | 1.35    |       |

|                     |                                                   | VID4:0 = 01101 | 1.40    |       |

|                     |                                                   | VID4:0 = 01100 | 1.45    |       |

|                     |                                                   | VID4:0 = 01011 | 1.50    |       |

|                     |                                                   | VID4:0 = 01010 | 1.55    |       |

|                     |                                                   | VID4:0 = 01001 | 1.60    |       |

|                     |                                                   | VID4:0 = 01000 | 1.65    |       |

|                     |                                                   | VID4:0 = 00111 | 1.70    |       |

|                     |                                                   | VID4:0 = 00110 | 1.75    |       |

|                     |                                                   | VID4:0 = 00101 | 1.80    |       |

|                     |                                                   | VID4:0 = 00100 | 1.85    |       |

|                     |                                                   | VID4:0 = 00011 | 1.90    |       |

|                     |                                                   | VID4:0 = 00010 | 1.95    |       |

|                     |                                                   | VID4:0 = 00001 | 2.00    |       |

|                     |                                                   | VID4:0 = 00000 | 2.05    |       |

|                     |                                                   | VID4:0 = 11111 | 2.0     |       |

|                     |                                                   | VID4:0 = 11110 | 2.1     |       |

|                     |                                                   | VID4:0 = 11101 | 2.2     |       |

|                     |                                                   | VID4:0 = 11100 | 2.3     |       |

|                     |                                                   | VID4:0 = 11011 | 2.4     |       |

|                     |                                                   | VID4:0 = 11010 | 2.5     |       |

|                     |                                                   | VID4:0 = 11001 | 2.6     |       |

|                     |                                                   | VID4:0 = 11000 | 2.7     |       |

|                     |                                                   | VID4:0 = 10111 | 2.8     |       |

|                     |                                                   | VID4:0 = 10110 | 2.9     |       |

|                     |                                                   | VID4:0 = 10101 | 3.0     |       |

|                     |                                                   | VID4:0 = 10100 | 3.1     |       |

|                     |                                                   | VID4:0 = 10011 | 3.2     |       |

|                     |                                                   | VID4:0 = 10010 | 3.3     | 1     |

|                     |                                                   | VID4:0 = 10001 | 3.4     | 1     |

|                     |                                                   | VID4:0 = 10000 | 3.5     | 1     |

Pin Description

www.ti.com

| Pin | Pin Name | Pin Function                                                                                                                                                        |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Vcc5V    | Supply Voltage Input (5V nominal)                                                                                                                                   |

| 2   | Divsel   | Selects Phase Mode. Logic low selects 4 phase. Logic high selects 3 phase. 2 phase operation is achieved by using 2 outputs in 4 phase mode.                        |

| 3   | Clksel   | Clock Select: Logic high selects internal clock. Logic low selects external clock.                                                                                  |

| 4   | Extclk   | External Clock Input. Output frequency = Clock Input / No. of Phases. Connect to Vcc5V to select internal clock.                                                    |

| 5   | Rref     | Connects to external reference resistor. Sets the operating frequency of the internal clock and the ramp time for the PWM. Reference voltage at this pin is 1.26V.  |

| 6   | Vid0     | 5-Bit DAC Input (LSB).                                                                                                                                              |

| 7   | Vid1     | 5-Bit DAC Input.                                                                                                                                                    |

| 8   | Vid2     | 5-Bit DAC Input.                                                                                                                                                    |

| 9   | Vid3     | 5-Bit DAC Input.                                                                                                                                                    |

| 10  | Vid4     | 5-Bit DAC Input (MSB)                                                                                                                                               |

| 11  | OC+      | Over-current Comparator. Non-inverting input.                                                                                                                       |

| 12  | OC-      | Over-current Comparator. Inverting input.                                                                                                                           |

| 13  | COMP     | Compensation Pin. This is the output of the internal transconductance amplifier. Compensation network should be connected between this pin and feedback ground FBG. |

| 14  | FB       | Feedback Input. Normally Kelvin connected to supply output.                                                                                                         |

| 15  | Bgout    | Current Limit Flag. Goes to logic low when current limit is activated. When over-current condition is removed, this pin is weakly pulled up to Vcc5V.               |

| 16  | FBG      | Feedback Ground. This pin should be connected to the ground at the supply output.                                                                                   |

| 17  | ENABLE   | Output Enable Pin. Tie to logic high to enable and logic low to disable.                                                                                            |

| 18  | GND      | Power Ground Pin.                                                                                                                                                   |

| 19  | DRV2     | Phase 2 Output.                                                                                                                                                     |

| 20  | DRV0     | Phase 0 Output.                                                                                                                                                     |

| 21  | Vcc12V   | Supply Voltage for FET Drivers DRV0:3.                                                                                                                              |

| 22  | DRV1     | Phase 1 Output.                                                                                                                                                     |

| 23  | DRV3     | Phase 3 Output.                                                                                                                                                     |

| 24  | OutV     | Sets the maximum DRV0:3 drive voltage to reduce switching loss in external FET's.                                                                                   |

Submit Documentation Feedback

Copyright © 2000–2013, Texas Instruments Incorporated

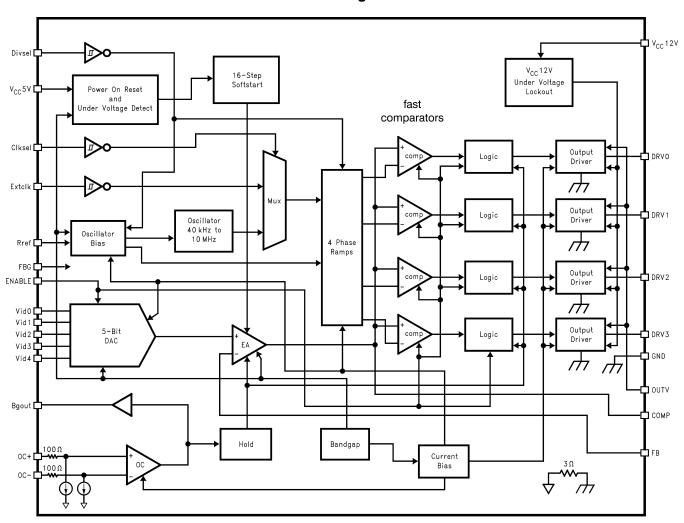

# **Block Diagram**

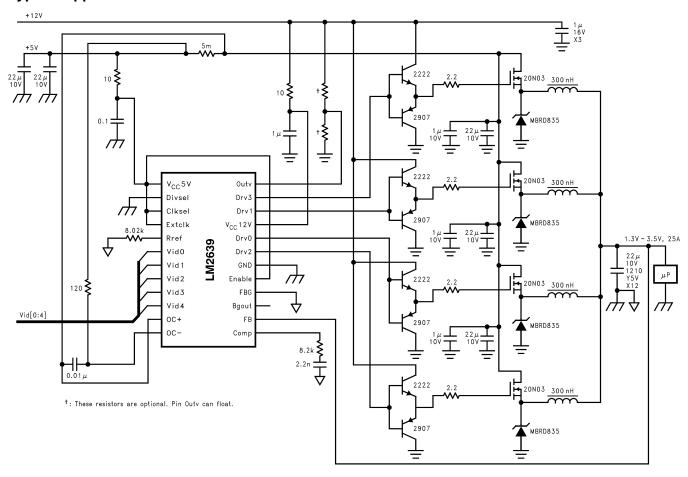

# **Typical Application**

| SNVS059C - | -FEBRUARY | 2000- | -REVISED | APRIL | 2013 |

|------------|-----------|-------|----------|-------|------|

|            |           |       |          |       |      |

# **REVISION HISTORY**

| Changes from Revision B (April 2013) to Revision C |                                                    |   |  |  |  |

|----------------------------------------------------|----------------------------------------------------|---|--|--|--|

| •                                                  | Changed layout of National Data Sheet to TI format | 8 |  |  |  |

Copyright © 2000–2013, Texas Instruments Incorporated Product Folder Links: LM2639

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>