# LM12L458 12-Bit + Sign Data Acquisition System with Self-Calibration

Check for Samples: LM12L458

## **FEATURES**

- Three Operating Modes: 12-Bit + Sign, 8-Bit + Sign, and "Watchdog"

- Single-Ended or Differential Inputs

- Built-In Sample-and-Hold

- Instruction RAM and Event Sequencer

- 8-Channel Multiplexer

- 32-Word Conversion FIFO

- Programmable Acquisition Times and Conversion Rates

- · Self-Calibration and Diagnostic Mode

- 8- or 16-Bit Wide Data Bus Microprocessor or DSP Interface

- CMOS Compatible I/O

#### **APPLICATIONS**

- Data Logging

- Process Control

- Energy Management

- Medical Instrumentation

#### **KEY SPECIFICATIONS**

- (f<sub>CLK</sub> = 6 MHz)

- Resolution: 12-Bit + Sign or 8-Bit + Sign

- Single Supply: +3 to +5.5 V

13-bit Conversion Time: 7.3 μs

9-bit Conversion Time: 3.5 μs

- 13-bit Through-Put Rate: 106 k Samples/s

- (Min)

- Comparison Time ("Watchdog" Mode): 1.8 μs (Max)

- ILE: ±1 LSB (Max)

- Power Consumption: 15 mW (max)

- Stand-By Mode: 5 μW (typ)

### DESCRIPTION

The LM12L458 is a highly integrated 3.3V Data Acquisition System. It combines a fully-differential self-calibrating (correcting linearity and zero errors) 13-bit (12-bit + sign) analog-to-digital converter (ADC) and sample-and-hold (S/H) with extensive analog functions and digital functionality. Up to 32 consecutive conversions, using two's complement format, can be stored in an internal 32-word (16-bit wide) FIFO data buffer. An internal 8-word RAM can store the conversion sequence for up to eight acquisitions through the LM12L458's eight-input multiplexer. The LM12L458 can also operate with 8bit + sign resolution and in a supervisory "watchdog" mode that compares an input signal against two programmable limits. Programmable acquisition times and conversion rates are possible through the use of internal clock-driven timers.

All registers, RAM, and FIFO are directly addressable through the high speed microprocessor interface to either an 8-bit or 16-bit data bus. The LM12L458 includes a direct memory access (DMA) interface for high-speed conversion data transfer.

Additional applications information can be found in applications notes AN-906 (JAJA265), AN-947 (SNAA012), and AN-949 (SNAA013).

₩.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

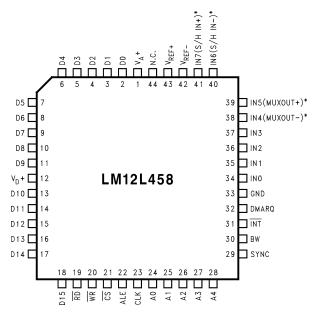

# **Connection Diagram**

\*Pin names in ( ) apply to the obsolete LM12L454, shown for reference only.

Figure 1. Connection Diagram

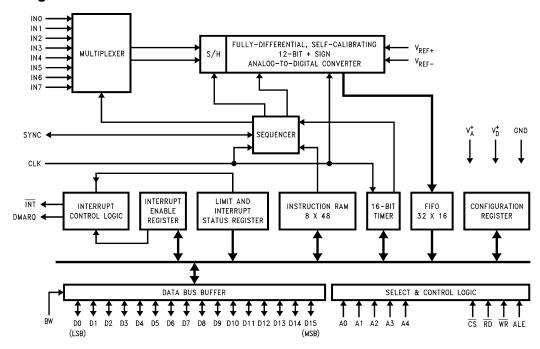

# **Functional Diagram**

Figure 2. LM12L458

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)

| Supply Voltage (V <sub>A</sub> + and V <sub>D</sub> +) | 6.0V                             |

|--------------------------------------------------------|----------------------------------|

| Voltage at Input and Output Pins, except analog inputs | -0.3V to (V <sup>+</sup> + 0.3V) |

| Voltage at Analog Inputs                               | - 5V to (V <sup>+</sup> + 5V)    |

| $ (V_A+)-(V_D+) $                                      | 300 mV                           |

| Input Current at Any Pin (3)                           | ±5 mA                            |

| Package Input Current <sup>(3)</sup>                   | ±20 mA                           |

| Power Consumption $(T_A = 25^{\circ}C)^{(4)}$          | 875 mW                           |

| Storage Temperature                                    | −65°C to +150°C                  |

| Lead Temperature, Infrared, 15 sec.                    | +300°C                           |

| ESD Susceptibility <sup>(5)</sup>                      | 1.5 kV                           |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (2) All voltages are measured with respect to GND, unless otherwise specified.

- (3) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supply rails (V<sub>IN</sub> < GND or V<sub>IN</sub> > (V<sub>A</sub>+ or V<sub>D</sub>+)), the current at that pin should be limited to 5 mA. The 20 mA maximum package input current rating allows the voltage at any four pins, with an input current of 5 mA, to simultaneously exceed the power supply voltages.

- (4) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>Jmax</sub> (maximum junction temperature), ?<sub>JA</sub> (package junction to ambient thermal resistance), and T<sub>A</sub> (ambient temperature). The maximum allowable power dissipation at any temperature is PD<sub>max</sub> = (T<sub>Jmax</sub> T<sub>A</sub>)/?<sub>JA</sub> or the number given in the Absolute Maximum Ratings, whichever is lower.

- (5) Human body model, 100 pF discharged through a 1.5 kO resistor.

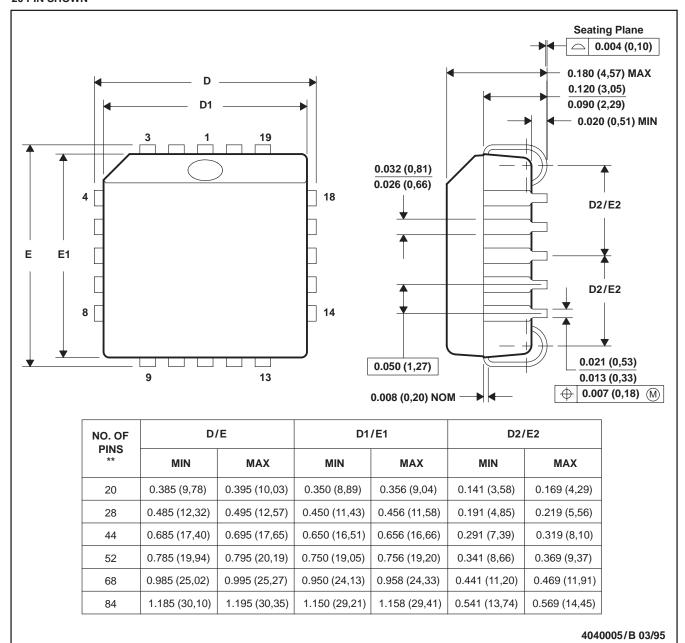

#### **Package Thermal Resistances**

| Package      | $\theta_{JA}$ |

|--------------|---------------|

| 44-Lead PLCC | 50°C / W      |

# Operating Ratings(1)(2)

| Temperature Range                                   | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$   |

|-----------------------------------------------------|------------------------------------------------------------------------|

| Supply Voltage - V <sub>A</sub> +, V <sub>D</sub> + | +3.0V to +5.5V                                                         |

| $ V_A + - V_D + $                                   | ≤100 mV                                                                |

| V <sub>IN+</sub> Input Range                        | $GND \leq V_{IN+} \leq V_{A} +$                                        |

| V <sub>IN</sub> - Input Range                       | $GND \leq V_{IN^{-}} \leq V_{A} +$                                     |

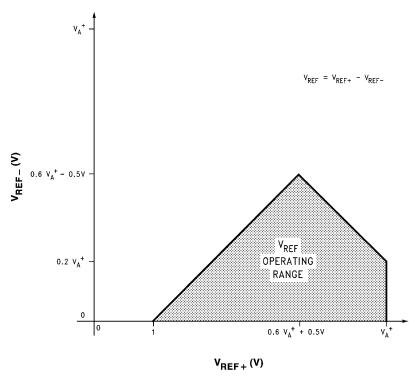

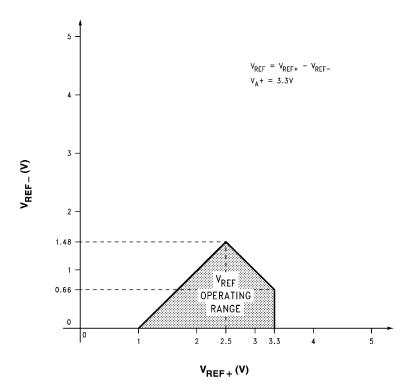

| V <sub>REF+</sub> Input Voltage                     | $1V \le V_{REF+} \le V_A +$                                            |

| V <sub>REF</sub> - Input Voltage                    | $0V \le V_{REF-} \le V_{REF+} - 1V$                                    |

| V <sub>REF+</sub> - V <sub>REF-</sub>               | $1V \le V_{REF} \le V_A +$                                             |

| V <sub>REF</sub> Common Mode Range <sup>(3)</sup>   | $0.1 \text{ V}_{A}^{+} \le \text{V}_{REFCM} \le 0.6 \text{ V}_{A}^{+}$ |

| $T_{J}(MAX)$                                        | 150°C                                                                  |

- (1) All voltages are measured with respect to GND, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (3)  $V_{REFCM}$  (Reference Voltage Common Mode Range) is defined as  $(V_{REF+} + V_{REF-})/2$ .

# Table 1. Reliability Information - Transistor Count

| Device                                         | Number |

|------------------------------------------------|--------|

| P-Chan MOS Transistor                          | 12,232 |

| N-Chan MOS Transistor                          | 15,457 |

| Parasitic Vertical Bipolar Junction Transistor | 4      |

| Parasitic Lateral Bipolar Junction Transistor  | 2      |

| TOTAL Transistors                              | 27,695 |

#### **Converter Characteristics**

The following specifications apply for  $V_A$ + =  $V_D$ + = +3.3V,  $V_{REF+}$  = +2.5V,  $V_{REF-}$  = 0V, 12-bit + sign conversion mode,  $f_{CLK}$  = 6.0 MHz,  $R_S = 25\Omega$ , source impedance for  $V_{REF+}$  and  $V_{REF-} \le 25\Omega$ , fully-differential input with fixed 1.25V common-mode voltage, and minimum acquisition time unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C^{(1)(2)(3)(4)}$

| Symbol                                | Parameter                                                            | Conditions                        | Typical <sup>(5)</sup> | Limits <sup>(6)</sup> | Units      |

|---------------------------------------|----------------------------------------------------------------------|-----------------------------------|------------------------|-----------------------|------------|

| ILE                                   | Integral Linearity Error                                             | After Auto-Cal <sup>(7)(8)</sup>  | ±1/2                   | ±1                    | LSB (max)  |

| TUE                                   | Total Unadjusted Error                                               | After Auto-Cal <sup>(7)</sup>     | ±1                     |                       | LSB        |

|                                       | Resolution with No Missing Codes                                     | After Auto-Cal <sup>(7)</sup>     |                        | 13                    | Bits (max) |

| DNL                                   | Differential Non-Linearity                                           | After Auto-Cal                    |                        | ±1                    | LSB (max)  |

|                                       | Zero Error                                                           | After Auto-Cal <sup>(9)</sup> (8) | ±1/4                   | ±1                    | LSB (max)  |

|                                       | Positive Full-Scale Error                                            | After Auto-Cal (7)(8)             | ±1/2                   | ±3                    | LSB (max)  |

|                                       | Negative Full-Scale Error                                            | After Auto-Cal (7)(8)             | ±1/2                   | ±3                    | LSB (max)  |

|                                       | DC Common Mode Error                                                 | See <sup>(10)</sup>               | ±2                     | ±4                    | LSB (max)  |

| ILE                                   | 8-Bit + Sign and "Watchdog" Mode Integral Linearity Error            | See <sup>(7)</sup>                |                        | ±1/2                  | LSB (max)  |

| TUE                                   | 8-Bit + Sign and "Watchdog" Mode Total<br>Unadjusted Error           | After Auto-Zero                   | ±1/2                   | ±3/4                  | LSB (max)  |

|                                       | 8-Bit + Sign and "Watchdog" Mode<br>Resolution with No Missing Codes |                                   |                        | 9                     | Bits (max) |

| DNL                                   | 8-Bit + Sign and "Watchdog" Mode Differential Non-Linearity          |                                   |                        | ±1                    | LSB (max)  |

|                                       | 8-Bit + Sign and "Watchdog" Mode Zero Error                          | After Auto-Zero                   |                        | ±1/2                  | LSB (max)  |

|                                       | 8-Bit + Sign and "Watchdog" Full-Scale Error                         |                                   |                        | ±1/2                  | LSB (max)  |

|                                       | 8-Bit + Sign and "Watchdog" Mode DC Common Mode Error                |                                   | ±1/8                   |                       | LSB        |

|                                       | Multiplexer Channel-to-Channel Matching                              |                                   | ±0.05                  |                       | LSB        |

| V                                     | Non Investing Input Dance                                            |                                   |                        | GND                   | V (min)    |

| $V_{IN+}$                             | Non-Inverting Input Range                                            |                                   |                        | V <sub>A</sub> +      | V (max)    |

| V                                     | Investing Input Dance                                                |                                   |                        | GND                   | V (min)    |

| V <sub>IN</sub> -                     | Inverting Input Range                                                |                                   |                        | V <sub>A</sub> +      | V (max)    |

| · · · · · · · · · · · · · · · · · · · | Differential Input Voltage Renge                                     |                                   |                        | -V <sub>A</sub> +     | V (min)    |

| $V_{IN+} - V_{IN-}$                   | Differential Input Voltage Range                                     |                                   |                        | V <sub>A</sub> +      | V (max)    |

| $\frac{V_{IN+}-V_{IN-}}{2}$           | Common Mode Input Voltage Bosse                                      |                                   |                        | GND                   | V (min)    |

| 2                                     | Common Mode Input Voltage Range                                      |                                   |                        | V <sub>A</sub> +      | V (max)    |

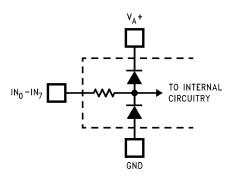

- (1) Two on-chip diodes are tied to each analog input through a series resistor, as shown below. Input voltage magnitude up to 5V above V<sub>A</sub>+ or 5V below GND will not damage the LM12L458. However, errors in the A/D conversion can occur if these diodes are forward biased by more than 100 mV. As an example, if V<sub>A</sub>+ is 3.0 V<sub>DC</sub>, full-scale input voltage must be =3.1 V<sub>DC</sub> to ensure accurate conversions. See Figure 3

- (2)  $V_A$ + and  $V_D$ + must be connected together to the same power supply voltage and bypassed with separate capacitors at each  $V^+$  pin to assure conversion/comparison accuracy.

- Accuracy is ensured when operating at  $f_{CLK} = 6$  MHz.

- With the test condition for  $V_{REF} = V_{REF}$  eiven as +2.5V, the 12-bit LSB is 305  $\mu$ V and the 8-bit/"Watchdog" LSB is 4.88 mV.

- Typical figures are at  $T_A = 25^{\circ}$ C and represent most likely parametric norm.

- Limits are specified to AOQL (Average Output Quality Level).

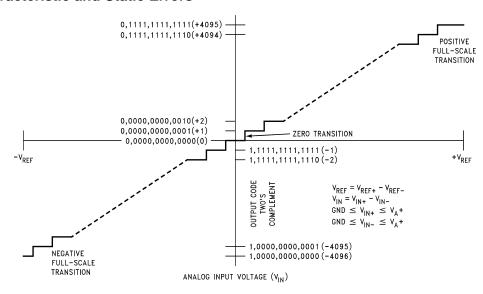

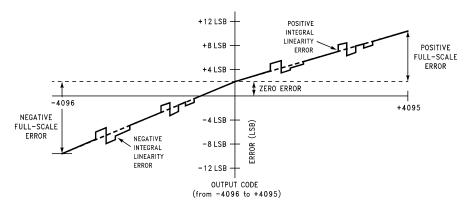

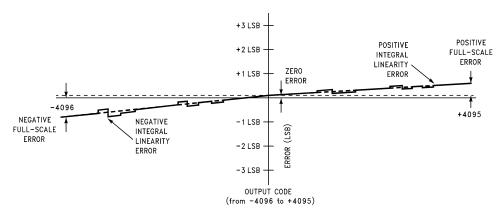

- Positive integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive full-scale and zero. For negative integral linearity error the straight line passes through negative full-scale and zero. (See Figure 10 and Figure 11).

- The LM12L458's self-calibration technique ensures linearity and offset errors as specified, but noise inherent in the self-calibration process will result in a repeatability uncertainty of ±0.10 LSB.

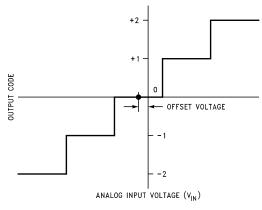

- Zero error is a measure of the deviation from the mid-scale voltage (a code of zero), expressed in LSB. It is the worst-case value of the code transitions between -1 to 0 and 0 to +1 (see Figure 12).

Product Folder Links: LM12L458

(10) The DC common-mode error is measured with both inputs shorted together and driven from 0V to +2.5V. The measured value is referred to the resulting output value when the inputs are driven with a 1.25V signal.

# **Converter Characteristics (continued)**

The following specifications apply for  $V_A + = V_D + = +3.3V$ ,  $V_{REF+} = +2.5V$ ,  $V_{REF-} = 0V$ , 12-bit + sign conversion mode,  $f_{CLK} = 6.0$  MHz,  $R_S = 25\Omega$ , source impedance for  $V_{REF+}$  and  $V_{REF-} \le 25\Omega$ , fully-differential input with fixed 1.25V common-mode voltage, and minimum acquisition time unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX}**; all other limits  $T_A = T_J = 25^{\circ}C^{(1)(2)(3)(4)}$

| Symbol           | P                                                       | arameter          | Conditions                           | Typical <sup>(5)</sup> | Limits <sup>(6)</sup> | Units     |

|------------------|---------------------------------------------------------|-------------------|--------------------------------------|------------------------|-----------------------|-----------|

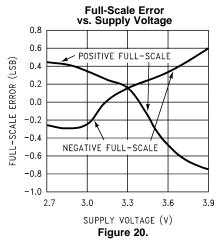

|                  |                                                         | Zero Error        | $V_A$ + = $V_D$ + = +3.3 $V$ ±10%    | ±0.2                   | ±1.75                 | LSB (max) |

| PSS              | Power Supply Sensitivity (11)                           | Full-Scale Error  | $V_{REF+} = 2.5V$ , $V_{REF-} = GND$ | ±0.4                   | ±2                    | LSB (max) |

|                  | Constantly                                              | Linearity Error   |                                      | ±0.2                   |                       | LSB       |

| C <sub>REF</sub> | V <sub>REF+</sub> /V <sub>REF</sub> - Input Capacitance |                   |                                      | 85                     |                       | pF        |

| C <sub>IN</sub>  | Selected Multiplex<br>Capacitance                       | ker Channel Input |                                      | 75                     |                       | pF        |

<sup>(11)</sup> Power Supply Sensitivity is measured after Auto-Zero and/or Auto-Calibration cycle has been completed with V<sub>A</sub>+ and V<sub>D</sub>+ at the specified extremes.

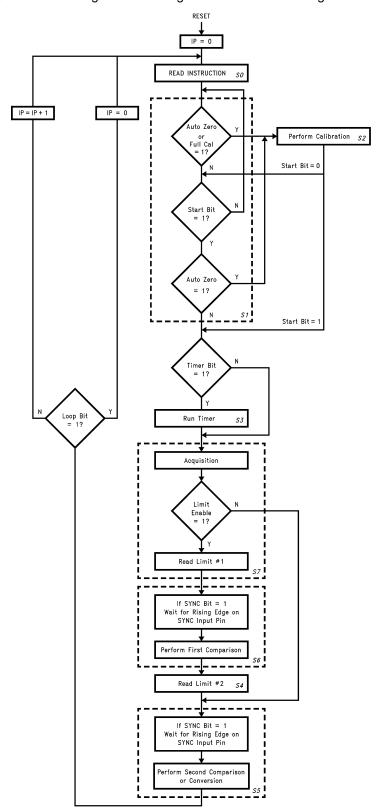

#### **Converter AC Characteristics**

The following specifications apply for  $V_A+=V_D+=+3.3V$ ,  $V_{REF+}=+2.5V$ ,  $V_{REF-}=0V$ , 12-bit + sign conversion mode,  $f_{CLK}=6.0$  MHz,  $R_S=25\Omega$ , source impedance for  $V_{REF+}$  and  $V_{REF-}\leq 25\Omega$ , fully-differential input with fixed +1.25V common-mode voltage, and minimum acquisition time unless otherwise specified. **Boldface limits apply for T\_A=T\_J=T\_{MIN} to T\_{MAX}**; all other limits  $T_A=T_J=25^{\circ}C$ . (1)(2)(3) (4)

| Symbol           | Parameter                       | Conditions                                                     | Typical <sup>(5)</sup>   | Limits <sup>(6)</sup>            | Units     |

|------------------|---------------------------------|----------------------------------------------------------------|--------------------------|----------------------------------|-----------|

|                  | Clark Data Carls                |                                                                | 50                       | 40                               | % (min)   |

|                  | Clock Duty Cycle                |                                                                | 50                       | 60                               | % (max)   |

|                  | Conversion Time                 | 13-Bit Resolution, Sequencer State<br>S5 (Figure 31)           | 44 (t <sub>CLK</sub> )   | 44 (t <sub>CLK</sub> ) + 50 ns   | (max)     |

| t <sub>C</sub>   | Conversion Time                 | 9-Bit Resolution, Sequencer State S5 (Figure 31)               | 21 (t <sub>CLK</sub> )   | 21 (t <sub>CLK</sub> ) + 50 ns   | (max)     |

|                  | Association Time                | Sequencer State S7 (Figure 31)<br>Built-in minimum for 13-Bits | 9 (t <sub>CLK</sub> )    | 9 (t <sub>CLK</sub> ) + 50 ns    | (max)     |

| t <sub>A</sub>   | Acquisition Time                | Built-in minimum for 9-Bits and "Watchdog" mode                | 2 (t <sub>CLK</sub> )    | 2 (t <sub>CLK</sub> ) + 50 ns    | (max)     |

| t <sub>Z</sub>   | Auto-Zero Time                  | Sequencer State S2 (Figure 31)                                 | 76 (t <sub>CLK</sub> )   | 76 (t <sub>CLK</sub> ) + 50 ns   | (max)     |

| t <sub>CAL</sub> | Full Calibration Time           | Sequencer State S2 (Figure 31)                                 | 4944 (t <sub>CLK</sub> ) | 4944 (t <sub>CLK</sub> ) + 50 ns | (max)     |

|                  | Throughput Rate <sup>(7)</sup>  |                                                                | 107                      | 106                              | kHz (min) |

| $t_{WD}$         | "Watchdog" Mode Comparison Time | Sequencer States S6, S4, and S5 (Figure 31)                    | 11 (t <sub>CLK</sub> )   | 11 (t <sub>CLK</sub> ) + 50 ns   | (max)     |

| t <sub>PU</sub>  | Power-Up Time                   |                                                                | 10                       |                                  | ms        |

| t <sub>WU</sub>  | Wake-Up Time                    |                                                                | 10                       |                                  | ms        |

- (1) Two on-chip diodes are tied to each analog input through a series resistor, as shown below. Input voltage magnitude up to 5V above V<sub>A</sub>+ or 5V below GND will not damage the LM12L458. However, errors in the A/D conversion can occur if these diodes are forward biased by more than 100 mV. As an example, if V<sub>A</sub>+ is 3.0 V<sub>DC</sub>, full-scale input voltage must be =3.1 V<sub>DC</sub> to ensure accurate conversions. See Figure 3

- (2) V<sub>A</sub>+ and V<sub>D</sub>+ must be connected together to the same power supply voltage and bypassed with separate capacitors at each V<sup>+</sup> pin to assure conversion/comparison accuracy.

- (3) Accuracy is ensured when operating at  $f_{CLK} = 6$  MHz.

- (4) With the test condition for V<sub>REF</sub> = V<sub>REF+</sub> V<sub>REF</sub> given as +2.5V, the 12-bit LSB is 305 μV and the 8-bit/"Watchdog" LSB is 4.88 mV.

- (5) Typical figures are at  $T_A = 25^{\circ}$ C and represent most likely parametric norm.

- (6) Limits are specified to AOQL (Average Output Quality Level).

- (7) The Throughput Rate is for a single instruction repeated continuously. Sequencer states 0 (1 clock cycle), 1 (1 clock cycle), 7 (9 clock cycles) and 5 (44 clock cycles) are used (see Figure 31). One additional clock cycle is used to read the conversion result stored in the FIFO, for a total of 56 clock cycles per conversion. The Throughput Rate is f<sub>CLK</sub> (MHz)/N, where N is the number of clock cycles/conversion.

#### **DC Characteristics**

The following specifications apply for  $V_A+=V_D+=+3.3V$ ,  $V_{REF+}=+2.5V$ ,  $V_{REF-}=0V$ ,  $f_{CLK}=6.0$  MHz and minimum acquisition time unless otherwise specified. **Boldface limits apply for T\_A=T\_J=T\_{MIN} to T\_{MAX}**; all other limits  $T_A=T_J=25^{\circ}C$ . (1) (2) (3)

| Symbol           | Parameter                                  | 1                        | Conditions                                                           | Typical <sup>(4)</sup>   | Limits <sup>(5)</sup> | Units                             |          |          |     |

|------------------|--------------------------------------------|--------------------------|----------------------------------------------------------------------|--------------------------|-----------------------|-----------------------------------|----------|----------|-----|

| I <sub>D</sub> + | V <sub>D</sub> + Supply Current            | <del>CS</del> = "1"      |                                                                      | 0.4                      | 1.0                   | mA (max)                          |          |          |     |

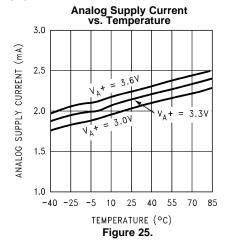

| I <sub>A</sub> + | V <sub>A</sub> + Supply Current            | <del>CS</del> = "1"      |                                                                      | 2.25                     | 3.5                   | mA (max)                          |          |          |     |

|                  | Stand-By Supply Current                    | Power-Down               | Clock Stopped                                                        | 1.5                      | 4.5                   | μA (max)                          |          |          |     |

| I <sub>ST</sub>  | $(I_D + + I_A +)$                          | Mode Selected            | 6 MHz Clock                                                          | 30                       |                       | μA (max)                          |          |          |     |

|                  |                                            |                          | ON-Channel = 3.6V                                                    | 0.1                      | 0.3                   | ( ( ( ( ) ( ) ( ) ( ) ( ) ( ) ( ) |          |          |     |

|                  | Multiplexer ON-Channel Leakage             | \\ \                     | OFF-Channel = 0V                                                     | 0.1                      | 0.3                   | μA (max)                          |          |          |     |

|                  | Current                                    | $V_A$ + = +3.6 $V$       | ON-Channel = 0V                                                      | 0.4                      | 0.2                   | ()                                |          |          |     |

|                  |                                            |                          | OFF-Channel = 3.6V                                                   | 0.1                      | 0.3                   | μA (max)                          |          |          |     |

|                  |                                            |                          | ON-Channel = 3.6V                                                    | 0.4                      | 0.0                   | ()                                |          |          |     |

|                  | Multiplexer OFF-Channel<br>Leakage Current |                          | .,                                                                   | V <sub>A</sub> + = +3.6V | OFF-Channel = 0V      | 0.1                               | 0.3      | μA (max) |     |

|                  |                                            |                          | Leakage Current $V_A = +3.6V$ ON-Channel = $0V$ OFF-Channel = $3.6V$ |                          | $V_A + = +3.6V$       | ON-Channel = 0V                   | 0.4      |          | ( ) |

|                  |                                            |                          |                                                                      |                          | 0.1                   | 0.3                               | μA (max) |          |     |

|                  |                                            | V <sub>IN</sub> = +3.3V  |                                                                      | 850                      | 1500                  | Ω                                 |          |          |     |

| R <sub>ON</sub>  | Multiplexer ON-Resistance                  | V <sub>IN</sub> = +1.65V |                                                                      | 1300                     | 2000                  | Ω                                 |          |          |     |

|                  |                                            | V <sub>IN</sub> = 0V     |                                                                      | 830                      | 1500                  | Ω                                 |          |          |     |

|                  | Multiplexer $V_{IN} = +3.3V$               |                          |                                                                      | ±1.0%                    | ±3.0%                 | Ω                                 |          |          |     |

|                  | Channel-to-Channel                         | V <sub>IN</sub> = +1.65V |                                                                      | ±1.0%                    | ±3.0%                 | Ω                                 |          |          |     |

|                  | R <sub>ON</sub> matching                   | $V_{IN} = 0V$            |                                                                      | ±1.0%                    | ±3.0%                 | Ω                                 |          |          |     |

<sup>(1)</sup> Two on-chip diodes are tied to each analog input through a series resistor, as shown below. Input voltage magnitude up to 5V above V<sub>A</sub>+ or 5V below GND will not damage the LM12L458. However, errors in the A/D conversion can occur if these diodes are forward biased by more than 100 mV. As an example, if V<sub>A</sub>+ is 3.0 V<sub>DC</sub>, full-scale input voltage must be =3.1 V<sub>DC</sub> to ensure accurate conversions. See Figure 3

(5) Limits are specified to AOQL (Average Output Quality Level).

<sup>(2)</sup> V<sub>A</sub>+ and V<sub>D</sub>+ must be connected together to the same power supply voltage and bypassed with separate capacitors at each V<sup>+</sup> pin to assure conversion/comparison accuracy.

<sup>(3)</sup> Accuracy is ensured when operating at  $f_{CLK} = 6$  MHz.

<sup>(4)</sup> Typical figures are at  $T_A = 25^{\circ}$ C and represent most likely parametric norm.

## **Digital Characteristics**

The following specifications apply for  $V_A+=V_D+=+3.3V$ , unless otherwise specified. **Boldface limits apply for T\_A=T\_J=T\_{MIN} to T\_{MAX}**; all other limits  $T_A=T_J=25^{\circ}C$ . (1)(2)(3)

| Symbol              | Parameter                          | Conditions                                     | Typical <sup>(4)</sup> | Limits <sup>(5)</sup> | Units                |

|---------------------|------------------------------------|------------------------------------------------|------------------------|-----------------------|----------------------|

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage          | $V_A + = V_D + = +3.6V$                        |                        | 2.0                   | V (min)              |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage          | $V_A + = V_D + = +3.0V \text{ ALE},$<br>Pin 22 |                        | 0.7<br>0.6            | V (max)              |

| I <sub>IN(1)</sub>  | Logical "1" Input Current          | V <sub>IN</sub> = +3.3V                        | 0.005                  | 1.0<br>2.0            | μΑ (max)<br>μΑ (max) |

| I <sub>IN(0)</sub>  | Logical "0" Input Current          | V <sub>IN</sub> = 0V                           | -0.005                 | -1.0<br>-2.0          | μA (max)             |

| C <sub>IN</sub>     | D0-D15 Input Capacitance           |                                                | 6                      |                       | pF                   |

|                     |                                    | $V_A + = V_D + = 3.0V$                         |                        |                       |                      |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage         | I <sub>OUT</sub> = -360 μA                     |                        | 2.4                   | V (min)              |

|                     |                                    | I <sub>OUT</sub> = −10 μA                      |                        | 2.85                  | V (min)              |

|                     |                                    | $V_A + = V_D + = +3.0V$                        |                        |                       |                      |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage         | I <sub>OUT</sub> = 1.6 mA                      |                        | 0.4                   | V (max)              |

|                     |                                    | I <sub>OUT</sub> = 10 μA                       |                        | 0.1                   | V (max)              |

|                     | TDI CTATE Output I calcage Compart | V <sub>OUT</sub> = 0V                          | -0.01                  | -3.0                  | μA (max)             |

| I <sub>OUT</sub>    | TRI-STATE Output Leakage Current   | $V_{OUT} = +3.3V$                              | 0.01                   | 3.0                   | μA (max)             |

- (1) Two on-chip diodes are tied to each analog input through a series resistor, as shown below. Input voltage magnitude up to 5V above V<sub>A</sub>+ or 5V below GND will not damage the LM12L458. However, errors in the A/D conversion can occur if these diodes are forward biased by more than 100 mV. As an example, if V<sub>A</sub>+ is 3.0 V<sub>DC</sub>, full-scale input voltage must be =3.1 V<sub>DC</sub> to ensure accurate conversions. See Figure 3

- (2) V<sub>A</sub>+ and V<sub>D</sub>+ must be connected together to the same power supply voltage and bypassed with separate capacitors at each V<sup>+</sup> pin to assure conversion/comparison accuracy.

- (3) Accuracy is ensured when operating at  $f_{CLK} = 6$  MHz.

- (4) Typical figures are at  $T_A = 25^{\circ}$ C and represent most likely parametric norm.

- (5) Limits are specified to AOQL (Average Output Quality Level).

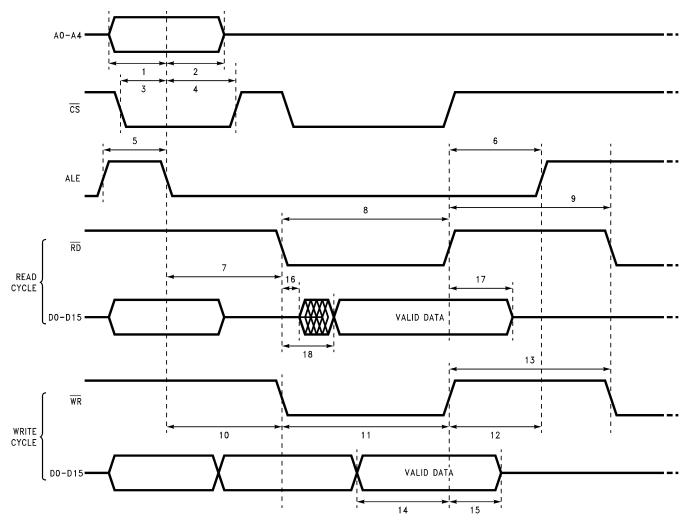

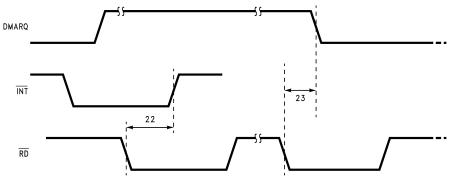

# **Digital Timing Characteristics**

The following specifications apply for  $V_A + = V_D + = +3.3V$ ,  $t_r = t_f = 3$  ns, and  $C_L = 100$  pF on data I/O,  $\overline{\text{INT}}$  and DMARQ lines unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C. (1)(2)(3)

| Symbol (See<br>Figure 28 Figure 29<br>Figure 30) | Parameter                                  | Conditions | Typical <sup>(4)</sup> | Limits <sup>(5)</sup> | Units    |

|--------------------------------------------------|--------------------------------------------|------------|------------------------|-----------------------|----------|

| 1, 3                                             | CS or Address Valid to ALE Low Set-Up Time |            |                        | 40                    | ns (min) |

| 2, 4                                             | CS or Address Valid to ALE Low Hold Time   |            |                        | 20                    | ns (min) |

| 5                                                | ALE Pulse Width                            |            |                        | 45                    | ns (min) |

| 6                                                | RD High to Next ALE High                   |            |                        | 35                    | ns (min) |

| 7                                                | ALE Low to RD Low                          |            |                        | 20                    | ns (min) |

| 8                                                | RD Pulse Width                             |            |                        | 100                   | ns (min) |

| 9                                                | RD High to Next RD or WR Low               |            |                        | 100                   | ns (min) |

| 10                                               | ALE Low to WR Low                          |            |                        | 20                    | ns (min) |

| 11                                               | WR Pulse Width                             |            |                        | 60                    | ns (min) |

| 12                                               | WR High to Next ALE High                   |            |                        | 75                    | ns (min) |

| 13                                               | WR High to Next RD or WR Low               |            |                        | 140                   | ns (min) |

<sup>(1)</sup> Two on-chip diodes are tied to each analog input through a series resistor, as shown below. Input voltage magnitude up to 5V above V<sub>A</sub>+ or 5V below GND will not damage the LM12L458. However, errors in the A/D conversion can occur if these diodes are forward biased by more than 100 mV. As an example, if V<sub>A</sub>+ is 3.0 V<sub>DC</sub>, full-scale input voltage must be =3.1 V<sub>DC</sub> to ensure accurate conversions. See Figure 3

<sup>(2)</sup> V<sub>A</sub>+ and V<sub>D</sub>+ must be connected together to the same power supply voltage and bypassed with separate capacitors at each V<sup>+</sup> pin to assure conversion/comparison accuracy.

<sup>(3)</sup> Accuracy is ensured when operating at  $f_{CLK} = 6$  MHz.

<sup>(4)</sup> Typical figures are at  $T_A = 25^{\circ}$ C and represent most likely parametric norm.

<sup>(5)</sup> Limits are specified to AOQL (Average Output Quality Level).

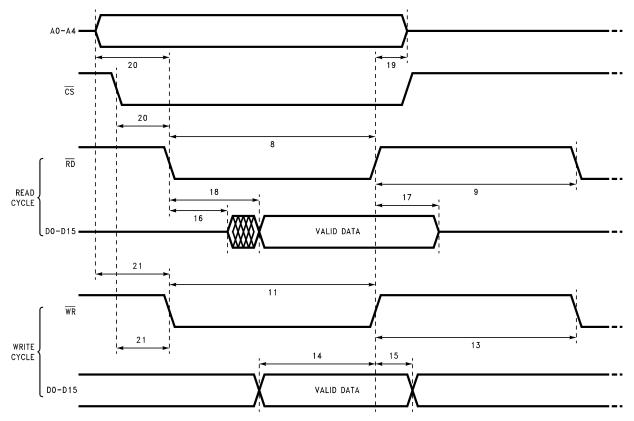

# **Digital Timing Characteristics (continued)**

The following specifications apply for  $V_A+=V_D+=+3.3V$ ,  $t_r=t_f=3$  ns, and  $C_L=100$  pF on data I/O,  $\overline{INT}$  and DMARQ lines unless otherwise specified. **Boldface limits apply for T**<sub>A</sub> = **T**<sub>J</sub> = **T**<sub>MIN</sub> **to T**<sub>MAX</sub>; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C. (1)(2)(3)

| Symbol (See<br>Figure 28 Figure 29<br>Figure 30) | Parameter                             | Conditions            | Typical <sup>(4)</sup> | Limits <sup>(5)</sup> | Units    |

|--------------------------------------------------|---------------------------------------|-----------------------|------------------------|-----------------------|----------|

| 14                                               | Data Valid to WR High Set-Up Time     |                       |                        | 40                    | ns (min) |

| 15                                               | Data Valid to WR High Hold Time       |                       |                        | 30                    | ns (min) |

| 40                                               | DD Louis to Data Due Out of TDL CTATE |                       | 20                     | 10                    | ns (min) |

| 16                                               | RD Low to Data Bus Out of TRI-STATE   |                       | 30                     | 70                    | ns (max) |

| 17                                               | RD High to TRI-STATE                  | R <sub>L</sub> = 1 kΩ | 30                     | 10                    | ns (min) |

| 17                                               |                                       |                       | 30                     | 110                   | ns (max) |

| 18                                               | DD Low to Data Valid (Access Time)    |                       | 30                     | 10                    | ns (min) |

| 10                                               | RD Low to Data Valid (Access Time)    |                       | 30                     | 95                    | ns (max) |

| 20                                               | Address Valid or CS Low to RD Low     |                       |                        | 20                    | ns (min) |

| 21                                               | Address Valid or CS Low to WR Low     |                       |                        | 20                    | ns (min) |

| 19                                               | Address Invalid from RD or WR High    |                       |                        | 10                    | ns (min) |

| 22                                               | INT High from DD Low                  |                       | 20                     | 10                    | ns (min) |

| 22                                               | INT High from RD Low                  |                       | 30                     | 60                    | ns (max) |

| 23                                               | DMARQ Low from RD Low                 |                       | 00                     | 10                    | ns (min) |

| ۷۵                                               | DIVIARQ LOW HOLLI RD LOW              |                       | 30                     | 60                    | ns (max) |

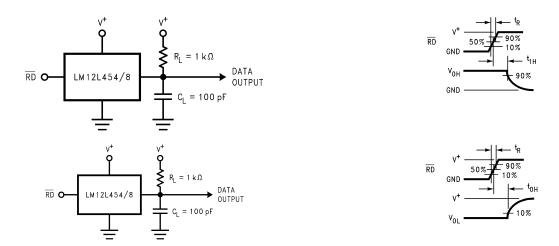

**Test Circuits and Waveforms**

Figure 3.

Figure 4. TRI-STATE Test Circuits and Waveforms

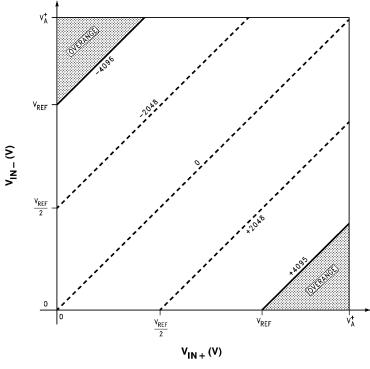

# Input and Reference Range

$$\begin{split} &V_{REF} = V_{REF+} - V_{REF-} \\ &V_{IN} = V_{IN+} - V_{IN-} \\ &GND \leq V_{IN+} \leq V_A + \\ &GND \leq V_{IN-} \leq V_A + \end{split}$$

Figure 5. The General Case of Output Digital Code vs. the Operating Input Voltage Range

Figure 6. Specific Case of Output Digital Code vs. the Operating Input Voltage Range for  $V_{REF} = 2.5V$

Figure 7. The General Case of the  $V_{\text{REF}}$  Operating Range

Submit Documentation Feedback

Copyright © 1999–2013, Texas Instruments Incorporated

Figure 8. The Specific Case of the  $V_{REF}$  Operating Range for  $V_{A}$ + = 3.3V

# **Transfer Characteristic and Static Errors**

Figure 9. Transfer Characteristic

Copyright © 1999–2013, Texas Instruments Incorporated

Figure 10. Simplified Error Curve vs. Output Code without Auto-Calibration or Auto-Zero Cycles

Figure 11. Simplified Error Curve vs. Output Code after Auto-Calibration Cycle

Figure 12. Offset or Zero Error Voltage

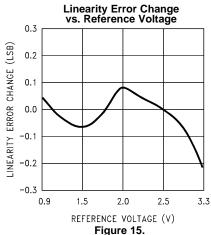

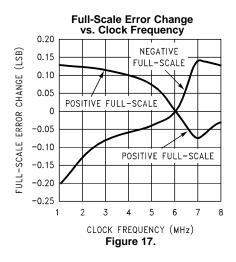

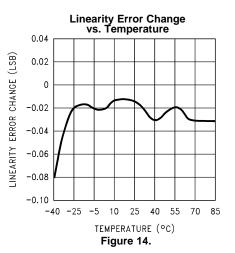

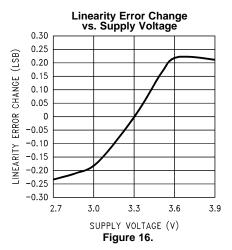

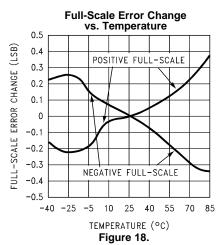

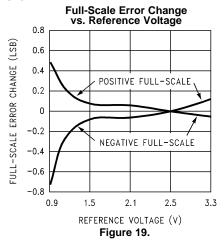

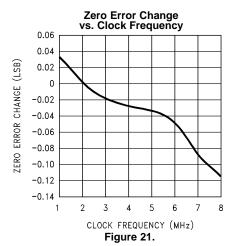

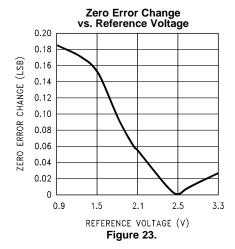

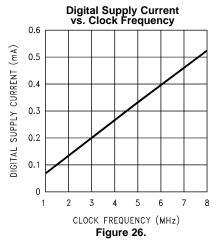

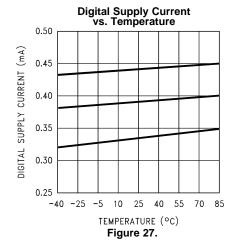

## **Typical Performance Characteristics**

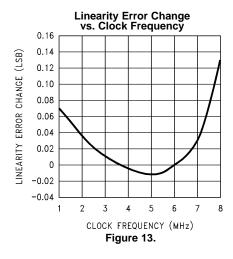

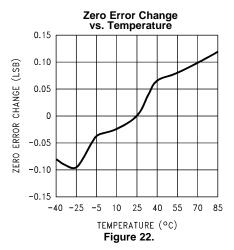

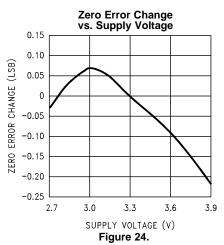

The following curves apply for 12-bit + sign mode after auto-calibration with  $V_A$ + =  $V_D$ + = +3.3V,  $V_{REF+}$  = +2.5V,  $V_{REF-}$  = 0V,  $V_A$  = 25°C, and  $V_{CLK}$  = 6 MHz unless otherwise specified. The performance for 8-bit + sign and "watchdog" modes is equal to or better than shown. (1)

(1) With the test condition for  $V_{REF} = V_{REF+} - V_{REF-}$  given as +2.5V, the 12-bit LSB is 305  $\mu$ V and the 8-bit/"Watchdog" LSB is 4.88 mV.

# **Typical Performance Characteristics (continued)**

The following curves apply for 12-bit + sign mode after auto-calibration with  $V_A$ + =  $V_D$ + = +3.3V,  $V_{REF+}$  = +2.5V,  $V_{REF-}$  = 0V,  $V_A$  = 25°C, and  $V_{CLK}$  = 6 MHz unless otherwise specified. The performance for 8-bit + sign and "watchdog" modes is equal to or better than shown. (1)

# **Typical Performance Characteristics (continued)**

The following curves apply for 12-bit + sign mode after auto-calibration with  $V_A$ + =  $V_D$ + = +3.3V,  $V_{REF+}$  = +2.5V,  $V_{REF-}$  = 0V,  $T_A$  = 25°C, and  $f_{CLK}$  = 6 MHz unless otherwise specified. The performance for 8-bit + sign and "watchdog" modes is equal to or better than shown. (1)

SNAS085B -JULY 1999-REVISED MARCH 2013

# **Timing Diagrams**

$V_{A}\text{+} = V_{D}\text{+} = \text{+}3.3\text{V}, \, t_{R} = t_{F} = 3 \,\, \text{ns, } C_{L} = 100 \,\, \text{pF for the } \overline{\text{INT}}, \, \text{DMARQ, D0-D15 outputs.}$

Figure 28. Multiplexed Data Bus

| 1, 3: CS or Address valid to ALE low set-up time. | 11: WR pulse width                      |

|---------------------------------------------------|-----------------------------------------|

| 2, 4: CS or Address valid to ALE low hold time.   | 12: WR high to next ALE high            |

| 5: ALE pulse width                                | 13: WR high to next WR or RD low        |

| 6: RD high to next ALE high                       | 14: Data valid to WR high set-up time   |

| 7: ALE low to RD low                              | 15: Data valid to WR high hold time     |

| 8: RD pulse width                                 | 16: RD low to data bus out of TRI-STATE |

| 9: RD high to next RD or WR low                   | 17: RD high to TRI-STATE                |

| 10: ALE low to WR low                             | 18: RD low to data valid (access time)  |

Figure 29. Non-Multiplexed Data Bus (ALE = 1)

| 8: RD pulse width                                                                                                 | 16: RD low to data bus out of TRI-STATE                                      |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| 9: RD high to next RD or WR low                                                                                   | 17: RD high to TRI-STATE                                                     |  |  |  |  |  |

| 11: WR pulse width                                                                                                | 18: RD low to data valid (access time)                                       |  |  |  |  |  |

| 13: WR high to next WR or RD low                                                                                  | 19: Address invalid from $\overline{RD}$ or $\overline{WR}$ high (hold time) |  |  |  |  |  |

| 14: Data valid to WR high set-up time                                                                             | 20: CS low or address valid to RD low                                        |  |  |  |  |  |

| 15: Data valid to WR high hold time                                                                               | 21: CS low or address valid to WR low                                        |  |  |  |  |  |

| $V_A$ + = $V_D$ + = +3.3V, $t_R$ = $t_F$ = 3 ns, $C_L$ = 100 pF for the $\overline{INT}$ , DMARQ, D0–D15 outputs. |                                                                              |  |  |  |  |  |

Figure 30. Interrupt and DMARQ

| 22: INT high from RD low | 23: DMARQ low from RD low |

|--------------------------|---------------------------|

|--------------------------|---------------------------|

Product Folder Links: LM12L458

#### **PIN DESCRIPTIONS**

- $V_A$ +,  $V_D$ + Analog and digital supply voltage pins. The LM12L458's supply voltage operating range is +3.0V to +5.5V. Accuracy is ensured only if  $V_A$ + and  $V_D$ + are connected to the same power supply. Each pin should have a parallel combination of 10  $\mu$ F (electrolytic or tantalum) and 0.1  $\mu$ F (ceramic) bypass capacitors connected between it and ground.

- **D0–D15** The internal data input/output TRI-STATE buffers are connected to these pins. These buffers are designed to drive capacitive loads of 100 pF or less. External buffers are necessary for driving higher load capacitances. These pins allows the user a means of instruction input and data output. With a logic **high** applied to the **BW** pin, data lines D8–D15 are placed in a high impedance state and data lines D0–D7 are used for instruction input and data output when the LM12L458 is connected to an 8-bit wide data bus. A logic **low** on the **BW** pin allows the LM12L458 to exchange information over a 16-bit wide data bus.

- Input for the active low READ bus control signal. The data input/output TRI-STATE buffers, as selected by the logic signal applied to the **BW** pin, are enabled when RD and CS are both low. This allows the LM12L458 to transmit information onto the data bus.

- WR Input for the active low WRITE bus control signal. The data input/output TRI-STATE buffers, as selected by the logic signal applied to the **BW** pin, are enabled when WR and CS are both low. This allows the LM12L458 to receive information from the data bus.

- Input for the active low Chip Select control signal. A logic low should be applied to this pin only during a READ or WRITE access to the LM12L458. The internal clocking is halted and conversion stops while Chip Select is low. Conversion resumes when the Chip Select input signal returns high.

- ALE Address Latch Enable input. It is used in systems containing a multiplexed data bus. When ALE is asserted **high**, the LM12L458 accepts information on the data bus as a valid address. A high-to-low transition will latch the address data on A0–A4 and the logic state on the CS input. Any changes on A0–A4 and CS while ALE is low will not affect the LM12L458. See Figure 28. When a non-multiplexed bus is used, ALE is continuously asserted **high**. See Figure 29.

- **CLK** External clock input pin. The LM12L458 operates with an input clock frequency in the range of 0.05 MHz to 8 MHz.

- **A0–A4** The LM12L458's address lines. They are used to access all internal registers, Conversion FIFO, and Instruction **RAM**.

- SYNC Synchronization input/output. When used as an output, it is designed to drive capacitive loads of 100 pF or less. External buffers are necessary for driving higher load capacitances. SYNC is an **input** if the Configuration register's "I/O Select" bit is **low**. A rising edge on this pin causes the internal S/H to hold the input signal. The next rising clock edge either starts a conversion or makes a comparison to a programmable limit depending on which function is requested by a programming instruction. This pin will be an **output** if "I/O Select" is set **high**. The SYNC output goes high when a conversion or a comparison is started and low when completed. (See CONFIGURATION REGISTER). An internal reset after power is first applied to the LM12L458 automatically sets this pin as an input.

- **BW** Bus Width input pin. This input allows the LM12L458 to interface directly with either an 8- or 16-bit data bus. A logic high sets the width to 8 bits and places D8–D15 in a high impedance state. A logic low sets the width to 16 bits.

- INT Active low interrupt output. This output is designed to drive capacitive loads of 100 pF or less. External buffers are necessary for driving higher load capacitances. An interrupt signal is generated any time a non-masked interrupt condition takes place. There are eight different conditions that can cause an interrupt. Any interrupt is reset by reading the Interrupt Status register. (See INTERRUPTS)

- **DMARQ** Active high Direct Memory Access Request output. This output is designed to drive capacitive loads of 100 pF or less. External buffers are necessary for driving higher load capacitances. It goes high whenever the number of conversion results in the conversion FIFO equals a programmable value stored in the Interrupt Enable register. It returns to a logic low when the FIFO is empty.

- **GND** Ground connection. It should be connected to a low resistance and inductance analog ground return that connects directly to the system power supply ground.

- **IN0–IN7** These are the eight analog inputs. A given channel is selected through the instruction RAM. Any of the channels can be configured as an independent single-ended input. Any pair of channels, whether adjacent

www.ti.com

or non-adjacent, can operate as a fully differential pair.

- $V_{REF-}$  This is the negative reference input. The LM12L458 operates with 0V ≤  $V_{REF-}$  ≤  $V_{REF+}$ . This pin should be bypassed to ground with a parallel combination of 10 μF and 0.1 μF (ceramic) capacitors.

- $V_{REF+}$  Positive reference input. The LM12L458 operate with 0V ≤  $V_{REF+}$  ≤  $V_A$ +. This pin should be bypassed to ground with a parallel combination of 10 μF and 0.1 μF (ceramic) capacitors.

- **N.C.** This is a no connect pin.

### **FUNCTIONAL DESCRIPTION**

The LM12L458 is a multi-functional Data Acquisition System that includes a fully differential 12-bit-plus-sign self-calibrating analog-to-digital converter (ADC) with a two's-complement output format, an 8-channel analog multiplexer, a first-in-first-out (FIFO) register that can store 32 conversion results, and an Instruction RAM that can store as many as eight instructions to be sequentially executed. All of this circuitry operates on only a single +3.3V power supply.

The LM12L458 has three modes of operation:

- 1. 12-bit + sign with correction

- 2. 8-bit + sign without correction

- 3. 8-bit + sign comparison mode ("watchdog" mode)

The fully differential 12-bit-plus-sign ADC uses a charge redistribution topology that includes calibration capabilities. Charge re-distribution ADCs use a capacitor ladder in place of a resistor ladder to form an internal DAC. The DAC is used by a successive approximation register to generate intermediate voltages between the voltages applied to  $V_{REF-}$  and  $V_{REF+}$ . These intermediate voltages are compared against the sampled analog input voltage as each bit is generated. The number of intermediate voltages and comparisons equals the ADC's resolution. The correction of each bit's accuracy is accomplished by calibrating the capacitor ladder used in the ADC.

Two different calibration modes are available; one compensates for offset voltage, or zero error, while the other corrects both offset error and the ADC's linearity error.

When correcting offset only, the offset error is measured once and a correction coefficient is created. During the full calibration, the offset error is measured eight times, averaged, and a correction coefficient is created. After completion of either calibration mode, the offset correction coefficient is stored in an internal offset correction register.

The LM12L458's overall linearity correction is achieved by correcting the internal DAC's capacitor mismatch. Each capacitor is compared eight times against all remaining smaller value capacitors and any errors are averaged. A correction coefficient is then created and stored in one of the thirteen internal linearity correction registers. An internal state machine, using patterns stored in an internal 16 x 8-bit ROM, executes each calibration algorithm.

Once calibrated, an internal arithmetic logic unit (ALU) uses the offset correction coefficient and the 13 linearity correction coefficients to reduce the conversion's offset error and linearity error, in the background, during the 12-bit + sign conversion. The 8-bit + sign conversion and comparison modes use only the offset coefficient. The 8-bit + sign mode performs a conversion in less than half the time used by the 12-bit + sign conversion mode.

The LM12L458's "watchdog" mode is used to monitor a single-ended or differential signal's amplitude. Each sampled signal has two limits. An interrupt can be generated if the input signal is above or below either of the two limits. This allows interrupts to be generated when analog voltage inputs are "inside the window" or, alternatively, "outside the window". After a "watchdog" mode interrupt, the processor can then request a conversion on the input signal and read the signal's magnitude.

The analog input multiplexer can be configured for any combination of single-ended or fully differential operation. Each input is referenced to ground when a multiplexer channel operates in the single-ended mode. Fully differential analog input channels are formed by pairing any two channels together.

The LM12L458's internal S/H is designed to operate at its minimum acquisition time (1.5  $\mu$ s, 12 bits) when the source impedance, R<sub>S</sub>, is  $\leq 80\Omega$  (f<sub>CLK</sub>  $\leq 6$  MHz). When  $80\Omega < R_S \leq 5.56$  k $\Omega$ , the internal S/H's acquisition time can be increased to a maximum of 6.5  $\mu$ s (12 bits, f<sub>CLK</sub> = 6 MHz). See INSTRUCTION RAM (Instruction RAM "00") Bits 12–15 for more information.

Microprocessor overhead is reduced through the use of the internal conversion FIFO. Thirty-two consecutive conversions can be completed and stored in the FIFO without any microprocessor intervention. The microprocessor can, at any time, interrogate the FIFO and retrieve its contents. It can also wait for the LM12L458 to issue an interrupt when the FIFO is full or after any number (≤32) of conversions have been stored.

Conversion sequencing, internal timer interval, multiplexer configuration, and many other operations are programmed and set in the Instruction RAM.

A diagnostic mode is available that allows verification of the LM12L458's operation. This mode internally connects the voltages present at the  $V_{REF+}$ ,  $V_{REF-}$ , and GND pins to the internal  $V_{IN+}$  and  $V_{IN-}$  S/H inputs. This mode is activated by setting the Diagnostic bit (Bit 11) in the Configuration register to a "1". More information concerning this mode of operation can be found in CONFIGURATION REGISTER.

## Internal User-Programmable Registers

#### **INSTRUCTION RAM**

The instruction RAM holds up to eight sequentially executable instructions. Each 48-bit long instruction is divided into three 16-bit sections. READ and WRITE operations can be issued to each 16-bit section using the instruction's address and the 2-bit "RAM pointer" in the Configuration register. The eight instructions are located at addresses 0000 through 0111 (A4–A1, BW = 0) when using a 16-bit wide data bus or at addresses 00000 through 01111 (A4–A0, BW = 1) when using an 8-bit wide data bus. They can be accessed and programmed in random order.

Any Instruction RAM READ or WRITE can affect the sequencer's operation:

The Sequencer should be stopped by setting the RESET bit to a "1" or by resetting the START bit in the Configuration Register and waiting for the current instruction to finish execution before any Instruction RAM READ or WRITE is initiated. Bit 0 of the Configuration Register indicates the Sequencer Status. See CONFIGURATION REGISTER for information on the Configuration Register.

A soft RESET should be issued by writing a "1" to the Configuration Register's RESET bit after any READ or WRITE to the Instruction RAM.

The three sections in the Instruction RAM are selected by the Configuration Register's 2-bit "RAM Pointer", bits D8 and D9. The first 16-bit Instruction RAM section is selected with the RAM Pointer equal to "00". This section provides multiplexer channel selection, as well as resolution, acquisition time, etc. The second 16-bit section holds "watchdog" limit #1, its sign, and an indicator that shows that an interrupt can be generated if the input signal is greater or less than the programmed limit. The third 16-bit section holds "watchdog" limit #2, its sign, and an indicator that shows that an interrupt can be generated if the input signal is greater or less than the programmed limit.

#### Instruction RAM "00"

**Bit 0** is the LOOP bit. It indicates the last instruction to be executed in any instruction sequence when it is set to a "1". The next instruction to be executed will be instruction 0.

**Bit 1** is the PAUSE bit. This controls the Sequencer's operation. When the PAUSE bit is set ("1"), the Sequencer will stop after reading the current instruction, but before executing it and the start bit, in the Configuration register, is automatically reset to a "0". Setting the PAUSE also causes an interrupt to be issued. The Sequencer is restarted by placing a "1" in the Configuration register's Bit 0 (Start bit).

After the Instruction RAM has been programmed and the RESET bit is set to "1", the Sequencer retrieves Instruction 000, decodes it, and waits for a "1" to be placed in the Configuration's START bit. The START bit value of "0" "overrides" the action of Instruction 000's PAUSE bit when the Sequencer is started. Once started, the Sequencer executes Instruction 000 and retrieves, decodes, and executes each of the remaining instructions. No PAUSE Interrupt (INT 5) is generated the first time the Sequencer executes Instruction 000 having a PAUSE bit set to "1". When the Sequencer encounters a LOOP bit or completes all eight instructions, Instruction 000 is retrieved and decoded. A set PAUSE bit in Instruction 000 now halts the Sequencer before the instruction is executed.

**Bits 2–4** select which of the eight input channels ("000" to "111" for IN0–IN7) will be configured as non-inverting inputs to the LM12L458's ADC. (See Table 4.)

**Bits 5–7** select which of the seven input channels ("001" to "111" for IN1 to IN7) will be configured as inverting inputs to the LM12L458's ADC. (See Table 4.) Fully differential operation is created by selecting two multiplexer channels, one operating in the non-inverting mode and the other operating in the inverting mode. A code of "000" selects ground as the inverting input for single ended operation.

Bit 8 is the SYNC bit. Setting Bit 8 to "1" causes the Sequencer to suspend operation at the end of the internal S/H's acquisition cycle and to wait until a rising edge appears at the SYNC pin. When a rising edge appears, the S/H acquires the input signal magnitude and the ADC performs a conversion on the clock's next rising edge. When the SYNC pin is used as an input, the Configuration register's "I/O Select" bit (Bit 7) must be set to a "0". With SYNC configured as an input, it is possible to synchronize the start of a conversion to an external event. This is useful in applications such as digital signal processing (DSP) where the exact timing of conversions is important.

When the LM12L458 is used in the "watchdog" mode with external synchronization, two rising edges on the SYNC input are required to initiate two comparisons. The first rising edge initiates the comparison of the selected analog input signal with Limit #1 (found in Instruction RAM "01") and the second rising edge initiates the comparison of the same analog input signal with Limit #2 (found in Instruction RAM "10").

**Bit 9** is the TIMER bit. When Bit 9 is set to "1", the Sequencer will halt until the internal 16-bit Timer counts down to zero. During this time interval, no "watchdog" comparisons or analog-to-digital conversions will be performed.

Bit 10 selects the ADC conversion resolution. Setting Bit 10 to "1" selects 8-bit + sign and when reset to "0" selects 12-bit + sign.

**Bit 11** is the "watchdog" comparison mode enable bit. When operating in the "watchdog" comparison mode, the selected analog input signal is compared with the programmable values stored in Limit #1 and Limit #2 (see Instruction RAM "01" and Instruction RAM "10"). Setting Bit 11 to "1" causes two comparisons of the selected analog input signal with the two stored limits. When Bit 11 is reset to "0", an 8-bit + sign or 12-bit + sign (depending on the state of Bit 10 of Instruction RAM "00") conversion of the input signal can take place.

# Table 2. LM12L458 Memory Map for 16-Bit Wide Data Bus<sup>(1)</sup>

| A4 | А3 | A2      | A1 | Purpose                               | Туре | D15                                                    | D14                                                       | D13      | D12        | D11                             | D10                          | D9                      | D8                    | D7       | D6                         | D5                                      | D4        | D3       | D2            | D1    | D0    |

|----|----|---------|----|---------------------------------------|------|--------------------------------------------------------|-----------------------------------------------------------|----------|------------|---------------------------------|------------------------------|-------------------------|-----------------------|----------|----------------------------|-----------------------------------------|-----------|----------|---------------|-------|-------|

| 0  | 0  | 0<br>to | 0  | Instruction RAM (RAM<br>Pointer = 00) | R/W  |                                                        | Acquisition Time                                          |          |            | Acquisition Time Watch- dog 8/7 |                              | 8/12                    | Timer                 | Sync     |                            | $V_{\text{IN-}}$ $V_{\text{IN+}}$ Pause |           |          | Loop          |       |       |

|    | 1  | 1       | 1  |                                       |      |                                                        |                                                           |          |            |                                 |                              |                         |                       |          |                            |                                         |           |          |               |       |       |

|    | 0  | 0       | 0  | In admiration DAM (DAM                |      |                                                        |                                                           |          |            |                                 |                              |                         |                       |          |                            |                                         |           |          |               |       |       |

| 0  |    | to      |    | Instruction RAM (RAM<br>Pointer = 01) | R/W  | Don't Care                                             |                                                           |          |            |                                 | >/< Sign                     |                         |                       |          | Limit #1                   |                                         |           |          |               |       |       |

|    | 1  | 1       | 1  |                                       |      |                                                        |                                                           |          |            |                                 |                              |                         |                       |          |                            |                                         |           |          |               |       |       |

|    | 0  | 0       | 0  |                                       |      |                                                        |                                                           |          |            |                                 |                              |                         |                       |          |                            |                                         |           |          |               |       |       |

| 0  |    | to      |    | Instruction RAM (RAM<br>Pointer = 10) | R/W  |                                                        |                                                           | I        | Don't Care |                                 |                              | >/<                     | Sign                  | Limit #2 |                            |                                         |           |          |               |       |       |

|    | 1  | 1       | 1  | ,                                     |      |                                                        |                                                           |          |            |                                 |                              |                         |                       |          |                            |                                         |           |          |               |       |       |

| 1  | 0  | 0       | 0  | Configuration Register                | R/W  |                                                        | Do                                                        | n't Care |            | DIAG                            | Test = 0                     | RAM                     | Pointer               | I/O Sel  | Auto<br>Zero <sub>ec</sub> | Chan<br>Mask                            | Stand- by | Full CAL | Auto-<br>Zero | Reset | Start |

| 1  | 0  | 0       | 1  | Interrupt Enable Register             | R/W  | Num                                                    | Number of Conversions in Conversion FIFO to Generate INT2 |          |            |                                 |                              | encer Add<br>enerate IN |                       | INT7     | Don't<br>Care              | INT6                                    | INT4      | INT3     | INT2          | INT1  | INT0  |

| 1  | 0  | 1       | 0  | Interrupt Status Register             | R    | Actual Number of Conversion Results in Conversion FIFO |                                                           |          |            |                                 | ess of Sequent<br>on Being I |                         | INST7                 | "0"      | INST5                      | INST4                                   | INST3     | INST2    | INST1         | INST0 |       |

| 1  | 0  | 1       | 1  | Timer Register                        | R/W  | Timer Preset High Byte                                 |                                                           |          |            |                                 |                              | Timer Preset Low Byte   |                       |          |                            |                                         |           |          |               |       |       |

| 1  | 1  | 0       | 0  | Conversion FIFO                       | R    | Add                                                    | Address or Sign Sign Conversion Data: MSBs                |          |            |                                 |                              |                         | Conversion Data: LSBs |          |                            |                                         |           |          |               |       |       |

| 1  | 1  | 0       | 1  | Limit Status Register                 | R    |                                                        | Limit #2: Status                                          |          |            |                                 |                              | ·                       | Limit #1: Status      |          |                            |                                         |           |          |               |       |       |

<sup>(1) (</sup>BW = "0", Test Bit = "0" and A0 = Don't Care)

# Table 3. LM12L458 Memory Map for 8-Bit Wide Data Bus<sup>(1)</sup>

|    |    | •• |    |    |                              | _                  |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

|----|----|----|----|----|------------------------------|--------------------|-------------------------|--------------------------------------------------------------------|-----------------|-----------------|-----------|---------------|---------------------------------------|---------|--|--|

| A4 | А3 | A2 | A1 | A0 | Purpose                      | Type               | D7                      | D6                                                                 | D5              | D4              | D3        | D2            | D1                                    | D0      |  |  |

|    | 0  | 0  | 0  |    |                              |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

| 0  |    | to |    | 0  |                              | R/W                |                         | $V_{IN-}$                                                          |                 |                 | $V_{IN+}$ |               | Pause                                 | Loop    |  |  |

|    | 1  | 1  | 1  |    | Instruction RAM              |                    |                         |                                                                    |                 |                 | ı         | 1             |                                       |         |  |  |

|    | 0  | 0  | 0  |    | (RAM Pointer = 00)           |                    |                         | W-1-1-                                                             |                 |                 |           |               |                                       |         |  |  |

| 0  |    | to |    | 1  |                              | R/W                |                         | Acquisition Time Watch-dog 8/12                                    |                 |                 |           |               |                                       |         |  |  |

|    | 1  | 1  | 1  |    |                              |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

|    | 0  | 0  | 0  |    |                              |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

| 0  |    | to |    | 0  |                              | R/W                |                         |                                                                    |                 | Comparison      | Limit #1  |               |                                       |         |  |  |

|    | 1  | 1  | 1  |    | Instruction RAM              |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

|    | 0  | 0  | 0  |    | (RAM Pointer = 01)           |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

| 0  |    | to |    | 1  |                              | R/W                |                         |                                                                    | Don             | t Care          |           |               | >/<                                   | Sign    |  |  |

|    | 1  | 1  | 1  |    |                              |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

|    | 0  | 0  | 0  |    |                              |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

| 0  |    | to |    | 0  |                              | R/W                | R/W Comparison Limit #2 |                                                                    |                 |                 |           |               |                                       |         |  |  |

|    | 1  | 1  | 1  |    | Instruction RAM              |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

|    | 0  | 0  | 0  |    | (RAM Pointer = 10)           | (RAM Pointer = 10) |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

| 0  |    | to |    | 1  |                              | R/W                |                         | Don't Care                                                         |                 |                 |           |               |                                       | Sign    |  |  |

|    | 1  | 1  | 1  |    |                              |                    |                         |                                                                    |                 |                 |           |               |                                       |         |  |  |

| 1  | 0  | 0  | 0  | 0  | Configuration                | R/W                | I/O Sel                 | Auto Zero <sub>ec</sub>                                            | Chan Mask       | Stand- by       | Full Cal  | Auto- Zero    | Reset                                 | Start   |  |  |

| 1  | 0  | 0  | 0  | 1  | Configuration<br>Register    | R/W                |                         | Don'                                                               | t Care          |                 | DIAG      | Test<br>= 0   | RAM I                                 | Pointer |  |  |

| 1  | 0  | 0  | 1  | 0  |                              | R/W                | INT7                    | Don't Care                                                         | INT5            | INT4            | INT3      | INT2          | INT1                                  | INT0    |  |  |

| 1  | 0  | 0  | 1  | 1  | Interrupt Enable<br>Register | R/W                | Numbe                   | er of Conversior                                                   | ns in Conversio | n FIFO to Gener | ate INT2  | Sequence      | er Address to Generat                 |         |  |  |

| 1  | 0  | 1  | 0  | 0  |                              | R                  | INST7                   | "0"                                                                | INST5           | INST4           | INST3     | INST2         | INST1                                 | INST0   |  |  |