## FPD87310

FPD87310 Universal Interface XGA Panel Timing Controller with RSDS (Reduced Swing Differential Signaling) and FPD-Link

Literature Number: SNOS466

## FPD87310

# Universal Interface XGA Panel Timing Controller with RSDS™ (Reduced Swing Differential Signaling) and FPD-Link

## **General Description**

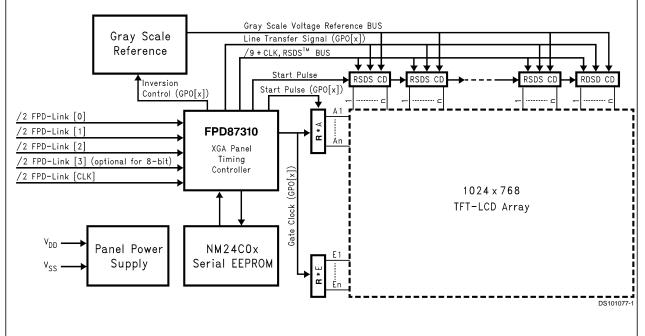

The FPD87310 Panel Timing Controller is an integrated FPD-Link + RSDS + TFT-LCD Timing Controller. It resides on the Flat Panel Display and provides the interface signal routing and Timing Control between Graphics or Video Controllers and a TFT-LCD system. FPD-Link, a low power, low EMI (ElectroMagnetic Interference) interface is used between this Controller and the Host system.

A RSDS (Reduced Swing Differential Signaling) Column Driver interface is used between the Timing Controller and the Column Drivers.

Programmable, General Purpose Outputs provide Row and Column Driver control. The FPD87310 is configured via metal mask initialization value or an optional external serial EEPROM. Reserved space in the EEPROM is available for display identification information. The system can access the EEPROM to read the display identification data or program initialization values used by the FPD87310.

This single 9-bit+CLK differential bus conveys the 18 bits color data for XGA panels at 130 Mb/s when using VESA 60 Hz standard timing.

### **Features**

- RSDS (Reduced Swing Differential Signaling) Column Driver bus for low power and reduced EMI

- Drives RSDS Column Drivers at 130 Mb/s with a 65 MHz clock

- 6- or 8-bit LVDS Video System Interface (FPD-Link)

- 10 General Purpose Outputs for Column/Row Drivers

- Optional EEPROM programming allows fine tuning in development and production environments

- Selectable dual initialization value sets to share parts for the different model panel module

- Ability to drive XGA/SVGA TFT-LCD Systems

- Narrow 9-bit+CLK differential Column Driver Bus minimizes width of Source PCB

- CMOS circuitry operates from a 3.3V supply

- Supports Graphics Controllers with spread spectrum interface featurefor lower EMI

## System Diagram

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{DD}$ ) 4V DC Input Voltage ( $V_{IN}$ ) -0.3V to 4.0V DC Output Voltage ( $V_{OUT}$ ) -0.3V to  $V_{DD}$  +0.3V Storage Temperature Range ( $T_{STG}$ ) -65°C to +150°C

ESD Rating:  $\begin{array}{ll} \text{HBM} & \geq 2 \text{kV} \\ \text{MM} & \geq 200 \text{V} \end{array}$

## **Operating Conditions**

|                                         | win | wax | Units |

|-----------------------------------------|-----|-----|-------|

| Supply Voltage (V <sub>DD</sub> )       | 3.0 | 3.6 | V     |

| Operating Temp Range (T <sub>A</sub> )  | 0   | 70  | °C    |

| Operating Frequency (f <sub>CLK</sub> ) |     | 67  | MHz   |

#### **Electrical Characteristics**

DC ELECTRICAL CHARACTERISTICS  $V_{DD} = 3.3V \pm 0.3V$ ,  $V_{SS} = 0.0V$  (Unless otherwise specified).

| Symbol          | Parameter                         | Conditions                                                   | Min | Тур | Max | Units |

|-----------------|-----------------------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| V <sub>OH</sub> | Minimum High Level Output Voltage | $V_{DD} = 3.3V, I_{OH} = 8 \text{ mA}$                       | 2.2 |     |     | V     |

| V <sub>OL</sub> | Maximum Low Level Output Voltage  | $V_{DD} = 3.3V$ , $I_{OL} = 8$ mA                            |     |     | 0.8 | V     |

| V <sub>IH</sub> | Minimum High Level Input Voltage  |                                                              | 2.0 |     |     | V     |

| V <sub>IL</sub> | Maximum Low Level Input Voltage   |                                                              |     |     | 0.8 | V     |

| I <sub>IN</sub> | Input Current                     | $V_{IN} = V_{SS}$ to $V_{DD}$                                | -10 |     | 10  | μA    |

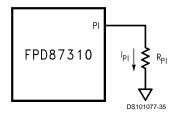

| I <sub>DD</sub> | Supply Current                    | $f_{CLK} = 65 \text{ MHz}, R_{Pl} = 13k\Omega, See$ Figure 1 |     |     | 140 | mA    |

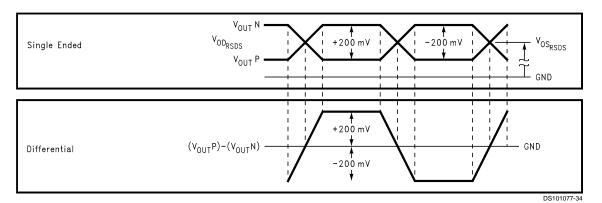

#### FPD-Link (LVDS) RECEIVER INPUT (RxCLK+/-, RxIN[y]+/-; y = 0, 1, 2, 3)

| Symbol              | Parameter                               | Conditions                                      | Min  | Тур  | Max  | Units |

|---------------------|-----------------------------------------|-------------------------------------------------|------|------|------|-------|

| $V_{IH_{LVDS}}$     | LVDS Input High Level Threshold Voltage | $V_{CM_{LVDS}} = +1.2V$ (Note 2)                |      |      | +100 | mV    |

| V <sub>ILLVDS</sub> | LVDS Input Low Level Threshold Voltage  | $V_{CM_{LVDS}} = +1.2V$ (Note 2)                | -100 |      |      | mV    |

| V <sub>CMLVDS</sub> | LVDS Input Common Mode Voltage Range    | $V_{DIFF_{LVDS}} = \pm 100 \text{ mV (Note 2)}$ |      | 1.25 |      | V     |

| I <sub>IN</sub>     | LVDS Input Current                      | $V_{IN} = +2.4V, V_{CC} = 3.6V$                 |      |      | ±10  | μA    |

|                     |                                         | $V_{IN} = 0V, V_{CC} = 3.6V$                    |      |      | ±10  | μA    |

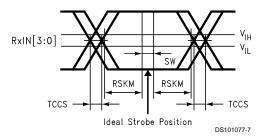

#### **RSDS TRANSMITTER OUTPUT** (RSCKP/N, RSx[y]P/N; x = R, G, B y = 0, 1, 2)

| Symbol              | Parameter                                | Conditions                                      | Min  | Тур  | Max  | Units |

|---------------------|------------------------------------------|-------------------------------------------------|------|------|------|-------|

| V <sub>OHRSDS</sub> | RSDS High Differential Output<br>Voltage | $V_{CM_{RSDS}} = +1.3V \pm 5\%$ (Note 3)        | +150 | +200 |      | mV    |

| V <sub>OLRSDS</sub> | RSDS Low Differential Output<br>Voltage  | $V_{CM_{RSDS}} = +1.3V \pm 5\%$ (Note 3)        |      | -200 | -150 | mV    |

| V <sub>CMRSDS</sub> | RSDS Common Mode Output<br>Voltage       | $V_{DIFF_{RSDS}} = \pm 200 \text{ mV (Note 3)}$ |      | 1.3  |      | V     |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

$\textbf{Note 2:} \ \ V_{CM_{LVDS}} = (V_{RxCLK+} + V_{RxCLK-})/2 \ \text{or} \ \ V_{CM_{LVDS}} = (V_{RxIN[y]+} + V_{RxIN[y]-})/2; \ y = 0, \ 1, \ 2, \ 3.$

$V_{DIFF_{LVDS}} = V_{RxCLK+} - V_{RxCLK-} \text{ or } V_{DIFF_{LVDS}} = V_{RxIN[y]+} - V_{RxIN[y]-; \ y \ = \ 0, \ 1, \ 2, \ 3}$

Note 3:  $V_{CMRSDS} = (V_{RSCKP} + V_{RSCKN})/2$  or  $V_{CMRSDS} = (V_{RSx[y]P} + V_{RSx[y]N})/2$ ; x = R, G, B, y = 0, 1, 2

The Termination Resister for differential line between positive and negative output is  $100\Omega$ .

Pin "PI" is connected to ground by 13.0 k $\Omega$ . This parameter is Guaranteed by Design.

### **AC Electrical Characteristics**

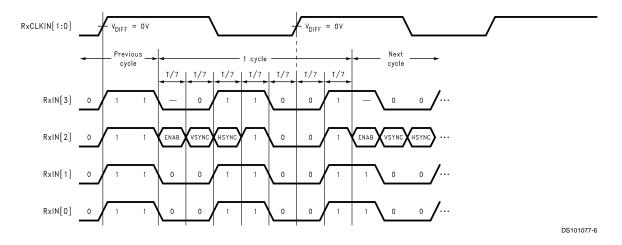

FPD-Link INPUT TIMING  $V_{DD} = 3.3V \pm 0.3V$ ,  $V_{SS} = 0.0V$  (Unless otherwise specified).

| Symbol | Parameter                                         | Conditions                           | Min | Тур | Max | Units |

|--------|---------------------------------------------------|--------------------------------------|-----|-----|-----|-------|

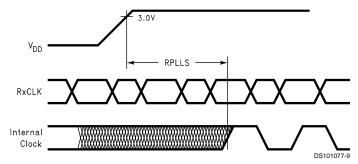

| RPLLS  | FPD-Link Receiver Phase Lock<br>Loop Wake-up Time |                                      |     |     | 10  | ms    |

| RSKM   | RxIN Skew Margin (Note 4)                         | $V_{DD} = 3.3V, T_{A} = 25^{\circ}C$ | 400 |     |     | ps    |

Note 4: Receiver Skew Margin is defined as the valid data sampling region at the receiver inputs.

This margin takes into account transmitter output skew (TCCS) and the setup and hold time (internal data sampling window) allowing for FPD-Link LVDS cable skew dependent on type/length of cable, and source clock (FPD-Link Transmitter TxCLK IN) jitter.

RSKM ≤ cable skew (type, length) + source clock jitter (cycle to cycle). The specified RSKM minimum assumes a TPPOSmax limit of 200ps (65MHz). This parameter is Guaranteed by Design.

FIGURE 1. FPD87310 Input  $I_{\rm DD}$  Test Pattern

SW Setup and Hold Time (internal data sampling window)

TCCS Transmitter Output Skew

RSKM ≥ Cable Skew (type, length) + Source Clock Jitter (cycle to cycle)

Cable Skew Typically 10 ps - 40 ps per foot.

FIGURE 2. FPD87310 (FPD-Link Receiver) Input Skew Margin

FIGURE 3. RSDS Waveform - Single Ended and Differential

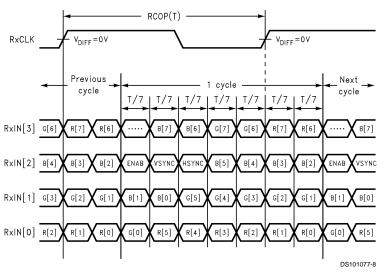

FIGURE 4. FPD87310 (FPD-Link Receiver) Input Data Mapping

Note: R/G/B [7] are the MSBs and R/G/B [0] are LSBs. This mapping is specific to this device only. Transmitters must be able to support this mapping for inter-operability.

FIGURE 5. FPD87310 (FPD-Link Receiver)

Phase Lock Loop Wake-up Time

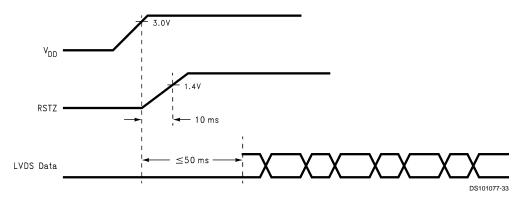

FIGURE 6. FPD87310 Power Up Sequence

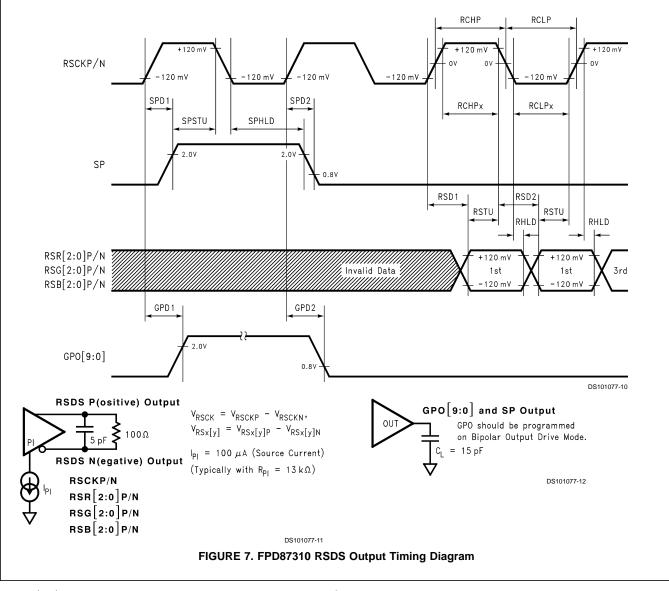

RSDS (Reduced Swing Differential Signalling) Output Timing, these parameters are Guaranteed by Design.

| Symbol | Parameter                                                                               | Conditions                                                                      | Min | Тур | Max | Units |

|--------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|-------|

| SPD1   | SP Rising from RSCK Rising                                                              | C <sub>L</sub> = 15 pF                                                          | 0   |     | 3.0 | ns    |

| SPD2   | SP Falling from RSCK Rising                                                             | C <sub>L</sub> = 15 pF                                                          | 0   |     | 3.0 | ns    |

| GPD1   | GPO[9:0] Rising from RSCK Rising                                                        | C <sub>L</sub> = 15 pF                                                          | 0   |     | 14  | ns    |

| GPD2   | GPO[9:0] Falling from RSCK Rising                                                       | C <sub>L</sub> = 15 pF                                                          | 0   |     | 14  | ns    |

| RCHP   | RSDS Clock (RSCK) High Period                                                           | $R_T = 100\Omega$ , $C_T = 5 pF$<br>$I_{PI} = 100 \mu A$ ,<br>f=65MHz           | 7.0 |     |     | ns    |

| RCLP   | RSDS Clock (RSCK) Low Period                                                            | $R_T = 100\Omega, C_T = 5 \text{ pF}$<br>$I_{PI} = 100 \mu\text{A},$<br>f=65MHz | 7.0 |     |     | ns    |

| RSTU   | RSR,G,B Setup to Falling or Rising Edge of RSCK, Register Output Format Control = 0010  | $R_T = 100\Omega$ , $C_T = 5 pF$<br>$I_{PI} = 100 \mu A$ ,<br>f=65MHz,          | 3.8 |     |     | ns    |

| RHLD   | RSR,G,B Hold from Falling or Rising Edge of RSCK, Register Output Format Control = 0010 | $R_T = 100\Omega, C_T = 5 \text{ pF}$<br>$I_{PI} = 100 \mu\text{A},$<br>f=65MHz | 0.2 |     |     | ns    |

#### **AC Electrical Characteristics** (Continued) RCHP RCLP RSCKP/N (differential RSP<sub>3</sub> Signal) RSTU RSTU SPD1 SPD2 — RHLD RHLD SP +120 mV R[1] RSR[0]P/N R[0] R[1] R[1] R[0] R[0] RSR[1]P/N R[2] R[3] R[3] RSR[2]P/N R[4] R[5] R[5] R[5] R[4] R[4] RSG[0]P/N G[0] G[1] G[0]G[1] G[0] G[1] RSG[1]P/N G[2] G[3] G[2] G[3] G[2] G[3] G[4] G[5] G[5] G[5]

Note: RSCKP/N, RSR[2:0]P/N, RSG[2:0]P/N and RSB[2:0]P/N are differential outputs, SP is single ended output.

RSB[0]P/N

RSB[1]P/N

FIGURE 8. FPD87310 RSDS Output Data Mapping

B[0]

B[2]

B[4]

B[1]

B[3]

B[5]

B[0]

B[2]

B[4]

B[1]

B[3]

B[5]

B[0]

B[2]

B[4]

— 3rd Data

B[1]

B[3]

B[5]

DS101077-13

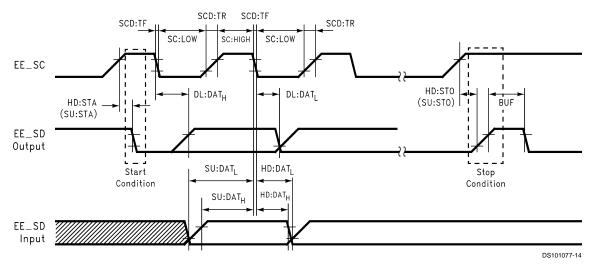

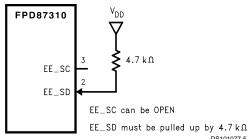

**EEPROM INTERFACE TIMING**This table is provided for reference only.

| Symbol              | Parameter                       | Conditions                                           | Min | Тур | Max | Units |

|---------------------|---------------------------------|------------------------------------------------------|-----|-----|-----|-------|

| f <sub>SC</sub>     | EE_SC Clock Frequency           |                                                      |     | 100 |     | kHz   |

| SC:LOW              | Clock Low Period                | $R_P = 4.7 \text{ k}\Omega, C_L = 50 \text{ pF}$     | 4.7 |     |     | μs    |

| SC:HIGH             | Clock High Period               | $R_{P} = 4.7 \text{ k}\Omega, C_{L} = 50 \text{ pF}$ | 4.0 |     |     | μs    |

| SCD:TR              | EE_SC and EE_SD Rise Time       | $R_{P} = 4.7 \text{ k}\Omega, C_{L} = 50 \text{ pF}$ |     |     | 1.0 | μs    |

| SCD:TF              | EE_SC and EE_SD Fall Time       | $R_{P} = 4.7 \text{ k}\Omega, C_{L} = 50 \text{ pF}$ |     |     | 0.3 | μs    |

| HD:STA              | Start Condition Hold Time       | $R_{P} = 4.7 \text{ k}\Omega, C_{L} = 50 \text{ pF}$ | 4.0 |     |     | μs    |

| HD:STO              | Stop Condition Hold Time        | $R_{P} = 4.7 \text{ k}\Omega, C_{L} = 50 \text{ pF}$ | 0.6 |     |     | μs    |

| DL:DAT <sub>H</sub> | Clock Falling Edge to Data High | $R_{P} = 4.7 \text{ k}\Omega, C_{L} = 50 \text{ pF}$ |     |     | 400 | ns    |

| DL:DAT <sub>L</sub> | Clock Falling Edge to Data Low  | $R_P = 4.7 \text{ k}\Omega, C_L = 50 \text{ pF}$     |     |     | 400 | ns    |

| SU:DAT              | Data Latch Setup Time           | $R_P = 4.7 \text{ k}\Omega, C_L = 50 \text{ pF}$     | 250 |     |     | ns    |

| HD:DAT              | Data Latch Hold Time            | $R_{P} = 4.7 \text{ k}\Omega, C_{L} = 50 \text{ pF}$ | 5   |     |     | μs    |

| BUF                 | Bus Free Time                   | $R_{P} = 4.7 \text{ k}\Omega, C_{L} = 50 \text{ pF}$ | 4.7 |     |     | μs    |

FIGURE 9. EEPROM Interface Bus Timing

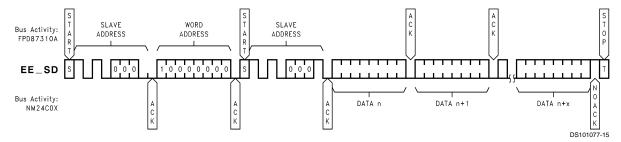

FIGURE 10. EEPROM Sequential Read

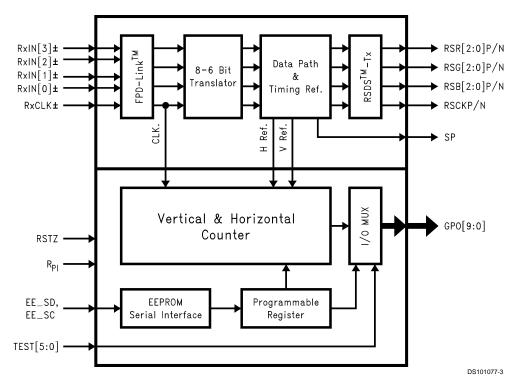

## **Block Diagram**

## **Functional Description**

#### **FPD-Link RECEIVER**

The LVDS based FPD-Link Receiver inputs video data and control timing. 4-LVDS channels plus clock provide 24 bits color. 3-LVDS channels can be used for 18 bits color. The video data is regenerated to a parallel data stream and routed to the 8-6 bit translator.

The GPOs (General Purpose Outputs) continue outputting the programmed control sequence at a reduced frame rate. RSTZ initialized the chip with the default register values.

#### SPREAD SPECTRUM SUPPORT

The FPD-Link receiver supports graphics controllers with Spread Spectrum interfaces for reducing EMI. The Spread Spectrum method supported is Center Spread. A maximum of 2% Center Spread is supported at a frequency modulation of 200kHz maximum.

#### **8-6 BIT TRANSLATOR**

8-bit data is reduced to a 6-bit data path via a time multiplexed dithering technique or simple truncation of the LSBs. This function is enabled via the Input Control Register bits [4,3]. Care should be taken in providing the correct input color mapping (see *Figure 4*)

#### DATAPATH BLOCK AND RSDS TRANSMITTER

6-bit video data (RGB) is input to the Datapath Block at a 65 MHz rate.

The data is delayed to align the Column Driver Start Pulse (SP) with the Column Driver data. The data (RSR[2:0]P/N, RSG[2:0]P/N, RSB[2:0]P/N) is output at a 130 MHz rate on 9 differential output channels (9 pairs of outputs).

The clock is output on the RSCKP/N differential pair.

The RSDS Column Drivers latch data on both positive and negative edges of the clock.

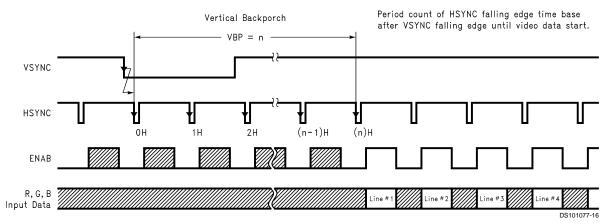

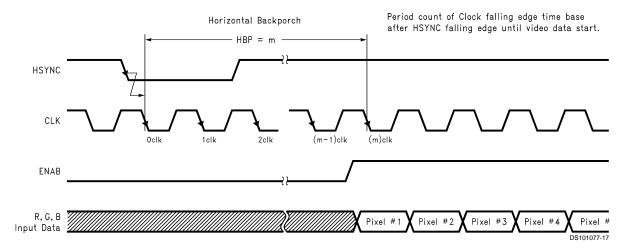

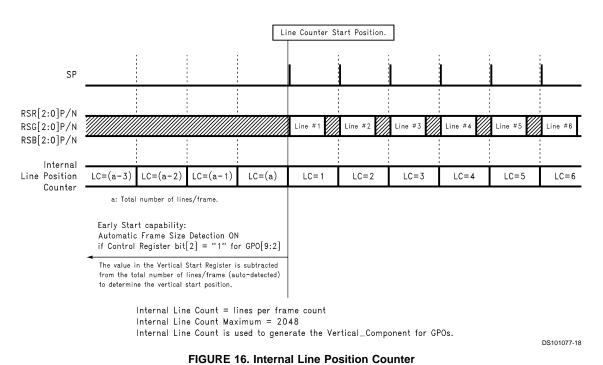

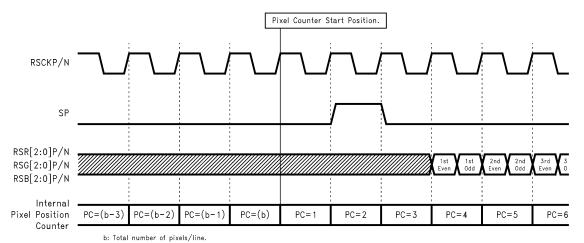

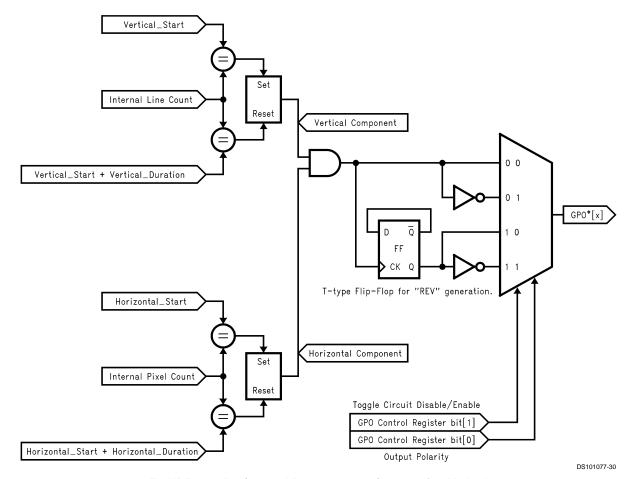

#### **VERTICAL AND HORIZONTAL COUNTER**

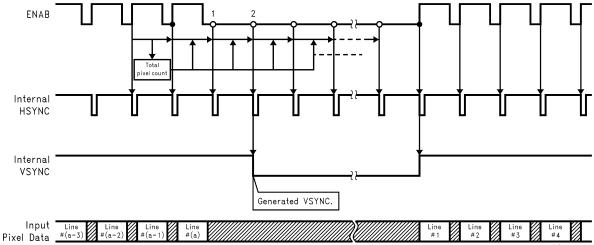

The counter block provides control to the Column Drivers, Row Drivers, and power supply as GPOs (General Purpose Outputs). Several video input formats are supported; Video timing which is fixed vertically, and horizontally (ENAB is ignored); Video timing which is fixed vertically, but uses ENAB for horizontal positioning; ENAB Only Mode which uses ENAB to position both vertically and horizontally. The FIX\_VERT and FIX\_HORIZ along with internal ENAB detection circuitry; control the operational mode. The fixed vertical and horizontal position points are programmable.

#### **TIMING CONTROL**

The Timing Control function generates control to Column Drivers, Row Drivers, and power supply. The programmable GPOs (General Purpose Outputs) provide for CD latch pulse, REV, and Row Driver control generation.

The General Purpose Outputs allow the user to generate control anywhere within the frame data. Standard Row Driver interface or Custom Row Driver interfaces can be implemented with the 10 GPOs (General Purpose Outputs). Note that GPO[9] must be used for output blanking control.

#### THE GENERAL PURPOSE OUTPUTS

Five registers provide the timing definition for each GPO.

- The Horizontal Start Register defines the output pixel number for which the GPO output goes active.

- The Horizontal Duration Register determines how many clocks the output will remain active during the line.

- The Vertical Start Register defines at what line# the output become active.

- The Vertical Duration Register defines how many lines the output remains active.

## Functional Description (Continued)

Each output has a Control Register (bit [0]) which defines the GPO polarity (active high or low). Another bit in the Control Register (bit [1] enables the "toggle" mode. This mode is useful in REV generation when alternating polarity is required from line to line. Frame to Frame polarity changes are made by programming an odd # in the vertical duration register when in "toggle" mode.

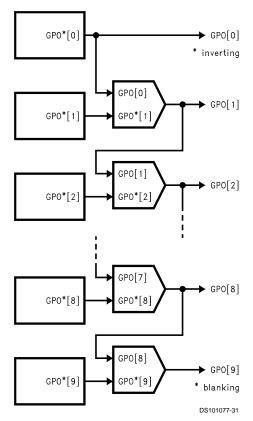

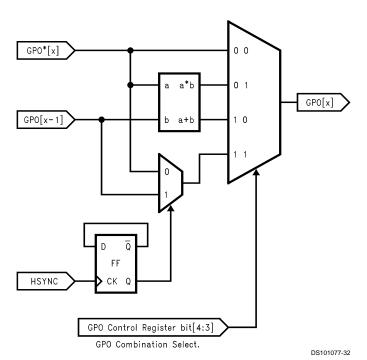

Two of the General Purpose Outputs have additional capabilities.

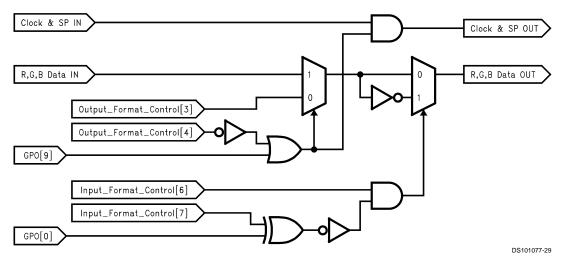

GPO[0] is capable of performing line inversion on the output data. Bits [4,3] of the Output Format Control Register provides control for this function.

GPO[9] controls output blanking and must be used for this purpose. If output blanking is not desired, this register must be programmed to always be active.

Black or White Data Generation (all "0" or "1" data) at the end of each frame is generated when Input Format Control Register bits [7,6] is set "10" or "11". When those bits are set, Black or White data is output after line #768 if GPO[9] is active.

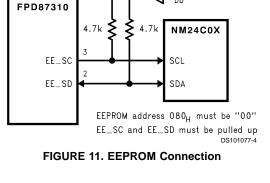

#### SERIAL EEPROM INTERFACE

The Serial EEPROM Interface controls the FPD87310 initialization. If the first byte word read from the EEPROM is not "00", the internal default values are used to initialize all programmable function of the FPD87310.

At power-up, the FPD87310 configures the internal programmable registers with data from the EEPROM. After the FPD87310 is initialized, the EEPROM can be accessed by the system in which display configuration and manufacturing information can be obtained. The EEPROM can be programmed "in system" providing quick evaluation of different display timing. External access to the EEPROM must be preceded by pin TEST[2] = "1" in order to interrupt the FPD87310 download. Continuous initialization with EEPROM is also selectable by pin TEST[2] = "0".

The FPD87310 initialization data begins at EEPROM address  $080_{\rm H}$ . The first 128 bytes  $(00_{\rm H}-07F_{\rm H})$  are reserved for display identification data.

FIGURE 12. Without EEPROM

#### RSDS OUTPUT VOLTAGE CONTROL

The RSDS output voltage swing is controlled through an external load resistor connected to the  $R_{\text{Pl}}$  pin. Typical value for the  $R_{\text{Pl}}$  is  $13 k\Omega$  for most applications. However, this is dependent on overall LCD module design characteristics such as trace impedance, termination, etc. The RSDS output voltage is inversely related to the  $R_{\text{Pl}}$  value. Lower  $R_{\text{Pl}}$  values will increase the RSDS output voltage swing and consequently overall power consumption will also increase. See .Figure 13

FIGURE 13. R<sub>PI</sub> Connection Diagram

## **Programmable Registers**

At power-up, data is read from an external EEPROM. If anything other than 00H is read back on the first EEPROM access (indicating EEPROM not present), the internal default values are used.

Pull-Up must be used on EE\_SD pin if external EEPROM is not used.

The following parameters are initialized at power up.

TABLE 1. FPD87310 Programmable Register Definition

| Control                              | EEPROM                              |         | The CONTROL REGISTER provide more setting information to the      |

|--------------------------------------|-------------------------------------|---------|-------------------------------------------------------------------|

| Registers                            | Address                             |         | input and output interfaces.                                      |

| Output Format<br>Control             | 082 <sub>H</sub> , 081 <sub>H</sub> | [2:0]   | Reserved                                                          |

| (16 bits)                            |                                     | [3]     | Output Data Inversion                                             |

| (10 bits)                            |                                     |         | "0" - Data inversion is Disabled                                  |

|                                      |                                     |         | "1" - Data inversion is Enabled                                   |

|                                      |                                     | [4]     | Output Data Inversion/Polarity                                    |

|                                      |                                     |         | "0" - Data Inversion when GPO[0] is "0"                           |

|                                      |                                     |         | "1" - Data inversion when GPO[0] is "1"                           |

|                                      |                                     | [7:5]   | Reserved                                                          |

|                                      |                                     | [11:8]  | RSDS output setup/hold time control                               |

|                                      |                                     | [13:12] | Unused Pixels                                                     |

|                                      |                                     |         | "00" - no unconnected pixels at beginning of first CD             |

|                                      |                                     |         | "01" - 1 unconnected pixels at beginning of first CD              |

|                                      |                                     |         | "10" - 2 unconnected pixels at beginning of first CD              |

|                                      |                                     |         | "11" - 3 unconnected pixels at beginning of first CD              |

|                                      |                                     | [15:14] | Reserved                                                          |

| Input Format                         | 085 <sub>H</sub>                    | [1:0]   | Reserved                                                          |

| Control                              |                                     | [2]     | Reserved                                                          |

| (8 bits)                             |                                     | [3]     | Frame Rate Control (8 bits only)                                  |

|                                      |                                     |         | "0" - Enable Frame Rate Control                                   |

|                                      |                                     |         | "1" - Disable Frame Rate Control (Truncate LSBs)                  |

|                                      |                                     | [4]     | 8/6 Bits Video                                                    |

|                                      |                                     |         | "0" - 6 Bits Video                                                |

|                                      |                                     |         | "1" - 8 Bits Video                                                |

|                                      |                                     | [5]     | Reserved                                                          |

|                                      |                                     | [7:6]   | Black or White data Generation                                    |

|                                      |                                     |         | "00" - No data manipulation is performed                          |

|                                      |                                     |         | "10" - Data goes to "0" when GPO[9] is "0"                        |

|                                      |                                     |         | "11" - Data goes to "1" when GPO[9] is "0"                        |

|                                      |                                     |         | Black data "0" or White data "1" will be output on lines > 768.   |

|                                      |                                     |         | GPO[9] must be programmed to > 768 lines for data to be output.   |

| Horizontal<br>Backporch<br>(11 bits) | 087 <sub>H</sub> , 086 <sub>H</sub> | # of 65 | MHz clocks after the falling edge of HYSYNC until start of video. |

| Vertical<br>Backporch<br>(11 bits)   | 089 <sub>H</sub> , 088 <sub>H</sub> | # of HS | SYNC from VSYNC falling edge until start of video.                |

## Programmable Registers (Continued)

TABLE 1. FPD87310 Programmable Register Definition (Continued)

| l                                                       | IABEL                                                                                                                                                                                                                                                                   | 1. 11 Do7 310 1 Togrammable Register Deminion (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control                                                 | EEPROM                                                                                                                                                                                                                                                                  | The CONTROL REGISTER provide more setting information to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Registers                                               | Address                                                                                                                                                                                                                                                                 | input and output interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| General<br>Purpose Output<br>GPO Registers<br>(10 sets) | See Table 2 EEPROM Memory Map GPO[0]:a=08B <sub>H</sub> GPO[1]:a=094 <sub>H</sub> GPO[2]:a=09D <sub>H</sub> GPO[3]:a=0A6 <sub>H</sub> GPO[4]:a=0AF <sub>H</sub> GPO[5]:a=0B8 <sub>H</sub> GPO[6]:a=0C1 <sub>H</sub> GPO[7]:a=0CA <sub>H</sub> GPO[8]:a=0D3 <sub>H</sub> | The GPO registers provide complete control over placement of control edges/strobes within the data frame.  The GPO timing registers (Vertical Start, Vertical Duration, Horizontal Start, and Horizontal Duration) define the control timing relative to the Internal line and pixel counters.  The line counter corresponds to the line being displayed. The pixel counter corresponds to the pixel output each line. The Control Register provides polarity selection and/or generation of a line to line frame to frame alternating signal (REV). Each General Purpose Output can be uniquely configured.  See the GPO programming examples for details.  - GPO[0]: provides for the data inverting function enabled by bit [3] of the Output Format Control Register. |

| Horizontal Start (11 bits)                              | GPO[9]:a=0DC <sub>H</sub> (a+1), (a)                                                                                                                                                                                                                                    | Internal count (pixel counter) at which GPO[x] goes active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Horizontal Duration (11 bits)                           | (a+3), (a+2)                                                                                                                                                                                                                                                            | # Pixel Clocks GPO[x] is active after Horizontal Start (if "0", Horizontal component is always on)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vertical Start<br>(11 bits)                             | (a+5), (a+4)                                                                                                                                                                                                                                                            | Line# at which GPO[x] control generation begins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Vertical Duration (11 bits)                             | (a+7), (a+6)                                                                                                                                                                                                                                                            | # Lines GPO[x] control generation continues (if "0", Vertical component is always on)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## Programmable Registers (Continued)

TABLE 1. FPD87310 Programmable Register Definition (Continued)

| Control<br>Registers | EEPROM<br>Address |       | The CONTROL REGISTER provide more setting information to the input and output interfaces.                                                              |

|----------------------|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Register     | (a+8)             | [0]   | Output polarity - defines active high or active low output                                                                                             |

| (8 bits)             |                   |       | "0" - Normal output (active high)                                                                                                                      |

|                      |                   |       | "1" - Inverted output (active low)                                                                                                                     |

|                      |                   | [1]   | Toggle circuit Enable/Disable                                                                                                                          |

|                      |                   |       | "0" - Toggle circuitry Disabled; Normal GPO output                                                                                                     |

|                      |                   |       | "1" - Toggle circuitry Enabled                                                                                                                         |

|                      |                   | [2]   | Automatic Frame Size Detection                                                                                                                         |

|                      |                   |       | GPO[1:0].                                                                                                                                              |

|                      |                   |       | "0" - Normal Operation.                                                                                                                                |

|                      |                   |       | "1" - Used with Toggle circuitry to create a "continuous" REV signal. The value of the Vertical Duration Register is overwritten.                      |

|                      |                   |       | GPO[9:2].                                                                                                                                              |

|                      |                   |       | "0" - Normal Operation.                                                                                                                                |

|                      |                   |       | "1" - Early Start capability.                                                                                                                          |

|                      |                   |       | The value in the Vertical Start Register is subtracted from the total number of lines/frames (auto-detected) to determine the vertical start position. |

|                      |                   | [4:3] | GPO[9:1] Combination Select.                                                                                                                           |

|                      |                   |       | "00" - Select GPO[x] as programmed. (No combination function).                                                                                         |

|                      |                   |       | "01" - Select GPO[x] "ANDed" with GPO[x-1].                                                                                                            |

|                      |                   |       | "10" - Select GPO[x] "ORed" with GPO[x-1].                                                                                                             |

|                      |                   |       | "11" - Select GPO[x] and GPO[x-1] on alternating frames.                                                                                               |

|                      |                   | [6:5] | Power-up sequence delay.                                                                                                                               |

|                      |                   |       | "00" - Outputs active after 1st VSYNC after EEPROM download.                                                                                           |

|                      |                   |       | "01" - Outputs active after 2nd VSYNC after EEPROM download.                                                                                           |

|                      |                   |       | "10" - Outputs active after 3rd VSYNC after EEPROM download.                                                                                           |

|                      |                   |       | "11" - Outputs actve after 4th VSYNC after EEPROM download.                                                                                            |

|                      |                   | [7]   | Open Drain Output Control                                                                                                                              |

|                      |                   |       | "0" - Outputs are Normal Operation. (sink/source drive current)                                                                                        |

|                      |                   |       | "1" - Outputs are Open Drain. (sink current only)                                                                                                      |

TABLE 2. Internal Default Register Values and EEPROM Memory Map

| No | Add | ress | Bits | Control Register         | Register Name   |     | De  | fault   | Valu | ses    |

|----|-----|------|------|--------------------------|-----------------|-----|-----|---------|------|--------|

|    | FF- | -EF  |      | not used/not loaded      |                 | Ini | t#1 | #1 Init |      | Init#3 |

| 56 | E4  |      | 8    | GPO9 Control Register    | reg_gpo9_cont   | 30  |     | 09      |      |        |

| 55 | E3  | E2   | 11   | GPO9 Vertical Duration   | reg_gpo9_Icount | 00  | 00  | 00      | 00   |        |

| 54 | E1  | E0   | 11   | GPO9 Vertical Start      | reg_gpo9_Istart | 00  | 01  | 00      | 01   |        |

| 53 | DF  | DE   | 11   | GPO9 Horizontal Duration | reg_gpo9_pcount | 00  | 40  | 00      | 40   |        |

| 52 | DC  | DD   | 11   | GPO9 Horizontal Start    | reg_gpo9_pstart | 03  | 86  | 03      | 86   |        |

| 51 | DB  |      | 8    | GPO8 Control Register    | reg_gpo8_cont   | 21  |     | 09      |      |        |

| 50 | DA  | D9   | 11   | GPO8 Vertical Duration   | reg_gpo8_Icount | 00  | 00  | 00      | 01   |        |

| 49 | D8  | D7   | 11   | GPO8 Vertical Start      | reg_gpo8_lstart | 00  | 01  | 00      | 01   |        |

| 48 | D6  | D5   | 11   | GPO8 Horizontal Duration | reg_gpo8_pcount | 00  | 00  | 00      | 40   |        |

| 47 | D4  | D3   | 11   | GPO8 Horizontal Start    | reg_gpo8_pstart | 00  | 01  | 01      | C2   |        |

| 46 | D2  |      | 8    | GPO7 Control Register    | reg_gpo7_cont   | 00  |     | 09      |      |        |

| 45 | D1  | D0   | 11   | GPO7 Vertical Duration   | reg_gpo7_lcount | 00  | 00  | 00      | 01   |        |

| 44 | CF  | CE   | 11   | GPO7 Vertical Start      | reg_gpo7_lstart | 00  | 00  | 00      | 01   |        |

| 43 | CD  | CC   | 11   | GPO7 Horizontal Duration | reg_gpo7_pcount | 00  | 00  | 00      | 40   |        |

## Programmable Registers (Continued)

TABLE 2. Internal Default Register Values and EEPROM Memory Map (Continued)

| No | Add | ress | Bits | Control Register               | Register Name     | e Default Valu |     | ues |     |          |                                                  |

|----|-----|------|------|--------------------------------|-------------------|----------------|-----|-----|-----|----------|--------------------------------------------------|

| 42 | СВ  | CA   | 11   | GPO7 Horizontal Start          | reg_gpo7_pstart   | 00             | 00  | 01  | 42  |          |                                                  |

| 41 | C9  |      | 8    | GPO6 Control Register          | reg_gpo6_cont     | 00             |     | 09  | -   |          | $\vdash$                                         |

| 40 | C8  | C7   | 11   | GPO6 Vertical Duration         | reg_gpo6_lcount   | 00             | 00  | 00  | 01  |          | $\vdash$                                         |

| 39 | C6  | C5   | 11   | GPO6 Vertical Start            | reg_gpo6_lstart   | 00             | 00  | 00  | 01  |          | $\vdash$                                         |

| 38 | C4  | C3   | 11   | GPO6 Horizontal Duration       | reg_gpo6_pcount   | 00             | 00  | 00  | 40  |          | $\vdash$                                         |

| 37 | C2  | C1   | 11   | GPO6 Horizontal Start          | reg_gpo6_pstart   | 00             | 00  | 00  | C2  |          | $\vdash$                                         |

| 36 | C0  |      | 8    | GPO5 Control Register          | reg_gpo5_cont     | 00             | 00  | 01  | -   |          | $\vdash$                                         |

| 35 | BF  | BE   | 11   | GPO5 Vertical Duration         | reg_gpo5_lcount   | 00             | 00  | 00  | 01  |          | <del> </del>                                     |

| 34 | BD  | BC   | 11   | GPO5 Vertical Start            | reg_gpo5_lstart   | 00             | 00  | 00  | 01  |          | <u> </u>                                         |

| 33 | BB  | BA   | 11   | GPO5 Horizontal Duration       | reg_gpo5_pcount   | 00             | 00  | 00  | 40  |          | <del>                                     </del> |

| 32 | B9  | B8   | 11   | GPO5 Horizontal Start          | reg_gpo5_pstart   | 00             | 00  | 00  | 42  |          | $\vdash$                                         |

| 31 | B7  |      | 8    | GPO4 Control Register          | reg_gpo4_cont     | 00             |     | 00  | 12  |          | $\vdash$                                         |

| 30 | B6  | B5   | 11   | GPO4 Vertical Duration         | reg_gpo4_lcount   | 00             | 00  | 00  | 00  |          | $\vdash$                                         |

| 29 | B4  | B3   | 11   | GPO4 Vertical Start            | reg_gpo4_lstart   | 00             | 01  | 00  | 01  |          | <del> </del>                                     |

| 28 | B2  | B1   | 11   | GPO4 Horizontal Duration       | reg_gpo4_istart   | 00             | 50  | 00  | 50  |          | <del> </del>                                     |

| 27 | B0  | AF   | 11   | GPO4 Horizontal Start          | reg_gpo4_pcount   | 03             | FA  | 03  | FA  | $\vdash$ | $\vdash$                                         |

| 26 | AE  | AF   | 8    | GPO3 Control Register          |                   | 00             | FA  | 20  | FA  |          | <del> </del>                                     |

| 25 | AD  | AC   | 11   | GPO3 Vertical Duration         | reg_gpo3_cont     | 00             | 00  | 00  | 00  |          | -                                                |

| 23 | AB  |      | 11   |                                | reg_gpo3_lcount   | 00             | 01  | 00  | 01  |          | <del></del>                                      |

|    |     | AA   |      | GPO3 Vertical Start            | reg_gpo3_lstart   |                | -   |     | -   |          | <del>                                     </del> |

| 23 | A9  | A8   | 11   | GPO3 Horizontal Duration       | reg_gpo3_pcount   | 02             | A0  | 00  | 00  |          | ₩                                                |

| 22 | A7  | A6   | 11   | GPO3 Horizontal Start          | reg_gpo3_pstart   | 03             | 86  | 00  | 02  |          | ₩                                                |

| 21 | A5  | 10   | 8    | GPO2 Control Register          | reg_gpo2_cont     | 00             | 0.4 | 01  | 0.4 |          | <u> </u>                                         |

| 20 | A4  | A3   | 11   | GPO2 Vertical Duration         | reg_gpo2_lcount   | 00             | 01  | 00  | 01  |          | <u> </u>                                         |

| 19 | A2  | A1   | 11   | GPO2 Vertical Start            | reg_gpo2_lstart   | 00             | 01  | 00  | 01  |          | <u> </u>                                         |

| 18 | A0  | 9F   | 11   | GPO2 Horizontal Duration       | reg_gpo2_pcount   | 05             | 46  | 00  | A0  |          | <u> </u>                                         |

| 17 | 9E  | 9D   | 11   | GPO2 Horizontal Start          | reg_gpo2_pstart   | 00             | 02  | 00  | 02  | <u> </u> | <u> </u>                                         |

| 16 | 9C  |      | 8    | GPO1 Control Register          | reg_gpo1_cont     | 07             |     | 07  |     | <u> </u> | <u> </u>                                         |

| 15 | 9B  | 9A   | 11   | GPO1 Vertical Duration         | reg_gpo1_lcount   | 00             | 01  | 00  | 01  |          | <u> </u>                                         |

| 14 | 99  | 98   | 11   | GPO1 Vertical Start            | reg_gpo1_lstart   | 00             | 01  | 00  | 01  |          | <u> </u>                                         |

| 13 | 97  | 96   | 11   | GPO1 Horizontal Duration       | reg_gpo1_pcount   | 04             | 00  | 04  | 00  | <u> </u> | <u> </u>                                         |

| 12 | 95  | 94   | 11   | GPO1 Horizontal Start          | reg_gpo1_pstart   | 03             | FA  | 03  | FA  |          | <u> </u>                                         |

| 11 | 93  |      | 8    | GPO0 Control Register          | reg_gpo0_cont     | 06             |     | 06  |     |          | <u> </u>                                         |

| 10 | 92  | 91   | 11   | GPO0 Vertical Duration         | reg_gpo0_lcount   |                | _   | 00  |     |          | <u> </u>                                         |

| 9  | 90  | 8F   | 11   | GPO0 Vertical Start            | reg_gpo0_lstart   | 00             | -   | 00  |     |          | <u> </u>                                         |

| 8  | 8E  | 8D   | 11   | GPO0 Horizontal Duration       | reg_gpo0_pcount   | 04             | 00  | 04  | 00  |          | <u> </u>                                         |

| 7  | 8C  | 8B   | 11   | GPO0 Horizontal Start          | reg_gpo0_pstart   | 03             | FA  | 03  | FA  |          | <u> </u>                                         |

| 6  | 8A  |      | 8    | (Reserved)                     |                   |                |     |     |     |          |                                                  |

| 5  | 89  | 88   | 11   | Vertical Backporch             | reg_vbp           | 00             | 23  | 00  | 23  |          |                                                  |

| 4  | 87  | 86   | 11   | Horizontal Backporch           | reg_hbp           | 01             | 28  | 01  | 28  |          |                                                  |

| 3  | 85  |      | 8    | Input Format Control           | reg_input_format  | 00             |     | 00  |     | 00       |                                                  |

| 2  | 84  |      | 8    | (Reserved)                     |                   |                |     |     |     |          |                                                  |

| 1  | 83  |      | 8    | (Reserved)                     |                   |                |     |     |     |          |                                                  |

| 0  | 82  | 81   | 16   | Output Format Control          | reg_output_format | 02             | 00  | 02  | 00  | 02       | 00                                               |

|    | 80  |      | 8    | (Programmed to "00H" for EEPRO | M auto detect)    | 00             |     | 00  |     | 00       |                                                  |

|    | 7F- | -00  |      | DDC VESA DATA                  |                   |                |     |     |     |          |                                                  |

## **Timing Definition**

FIGURE 14. Vertical Backporch Definition

Note: Horizontal Position determined by ENAB if FIX\_VERT = "0" and ENAB is active.

FIGURE 15. Horizontal Backporch Definition

## Timing Definition (Continued)

Internal Pixel Count Final value = pixels per line

Internal Pixel Count Maximum = 2048 (65 MHz Clocks)

$Internal\ Pixel\ Count\ is\ used\ to\ generate\ the\ Horizontal\_Component\ for\ GPOs.$

DS101077-19

FIGURE 17. Internal Pixel Position Counter

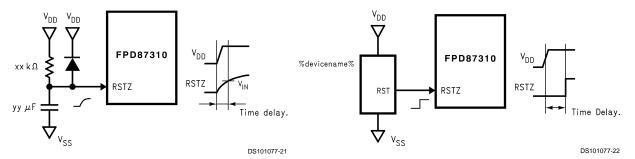

EEPROM download occurs at first detected Vertical Blanking Period after "RSTZ" signal rising up.

When in "ENAB Only Mode", VSYNC timing is generated internally when ENAB remains "Low" (No Toggle) for more then 2 line times.

Outputs activation depends on GPO\_Control\_Register bits [6:5].

EEPROM download occur every 5 frames when TEST[2] = "0".

When FPD87310 detected no EEPROM connection, the default value will be used for timing generation.

If set Early Start Capability, Outputs might be delayed activate position.

FIGURE 18. Power-Up Sequence and EEPROM Downloading

## Timing Definition (Continued)

If RSTZ is required long time constant delay or start slow ramping up supply ( $V_{DD}$ ), NOT recommended to use this reset circuit.

FIGURE 19. Suggested Power-Up Resetting Circuit

## **Timing Modes**

The FPD87310 has Three Input Timing Operation Mode.

- Fixed Vertical/Fixed Horizontal Mode. (FIX\_VERT/FIX\_HORIZ)

- Fixed Vertical/ENAB Horizontal Mode. (FIX\_VERT/ENAB\_HORIZ/FIX\_HORIZ)

- 3. ENAB Only Mode.

Input Timing Operation Mode can be programmed by input pin "FIX\_VERT", and "FIX\_HORIZ"

| FIX_<br>VERT | FIX_<br>HORIZ | ENAB<br>Tog-<br>gling | Operation Mode          |

|--------------|---------------|-----------------------|-------------------------|

| 0            | 0             | Yes                   | ENAB ONLY               |

| 1            | 0             | Yes                   | FIX_VERT/FIX_HORIZ/ENAB |

| 1            | 1             | Х                     | FIX_VERT/FIX_HORIZ      |

#### **ENAB ONLY MODE**

FIX\_VERT="0", FIX\_HORIZ="0", ENAB is Toggling

When in ENAB Only Mode, VSYNC timing is generated internally when ENAB remains "Low" (No Toggle) for more than 2 line times.

FIGURE 20. ENAB ONLY MODE and Internally Generated Timing

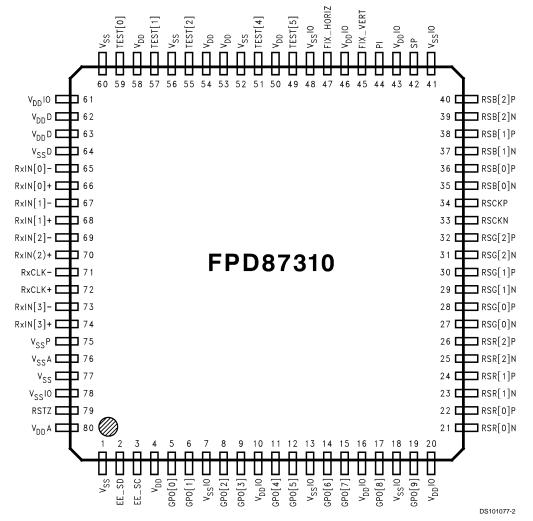

## **Connection Diagram**

Thin Quad Flatpak (TQFP80)

## **Pin Description**

#### SYSTEM INTERFACE

| Symbol     | Pin Count | Туре  | Function                                                                   |  |

|------------|-----------|-------|----------------------------------------------------------------------------|--|

| RxIN[0]+/- | 2         | LVDSI | FPD-Link Data Differential Pair 0 Input                                    |  |

| RxIN[1]+/- | 2         | LVDSI | FPD-Link Data Differential Pair 1 Input                                    |  |

| RxIN[2]+/- | 2         | LVDSI | FPD-Link Data Differential Pair 2 Input                                    |  |

| RxIN[3]+/- | 2         | LVDSI | FPD-Link Data Differential Pair 3 Input (Used in 8 Bits Video Application) |  |

| RxCLK+/-   | 2         | LVDSI | FPD-Link Clock Differential Pair Input                                     |  |

| RSTZ       | 1         | STI   | Reset Input, Active Low                                                    |  |

#### **COLUMN DRIVER INTERFACE**

| Pin Count                                                         | Type  | Function                                                   |

|-------------------------------------------------------------------|-------|------------------------------------------------------------|

| 6                                                                 | RSDSO | Red Reduced Swing Differential Outputs to Column Drivers   |

| 6                                                                 | RSDSO | Green Reduced Swing Differential Outputs to Column Drivers |

| 6                                                                 | RSDSO | Blue Reduced Swing Differential Outputs to Column Drivers  |

| RSCKP/N 2 RSDSO Clock Reduced Swing Differential Outputs to Colur |       | Clock Reduced Swing Differential Outputs to Column Drivers |

| 1 TO Start Pulse Output to Column Driver                          |       | Start Pulse Output to Column Driver                        |

|                                                                   | 6     | 6 RSDSO 6 RSDSO 6 RSDSO 2 RSDSO                            |

## Pin Description (Continued)

| Symbol | Pin Count | Туре | Function                                         |  |

|--------|-----------|------|--------------------------------------------------|--|

| PI     | 1         | I    | Reference for Reduced Swing Differential Outputs |  |

#### **GENERAL PURPOSE OUTPUTS**

| Symbol   | Pin Count | Туре  | Function                               |  |

|----------|-----------|-------|----------------------------------------|--|

| GPO[9:0] | 10        | TO/OD | General Purpose Outputs (Programmable) |  |

#### **EEPROM INTERFACE**

| Symbol | Pin Count | Туре | Function           |  |

|--------|-----------|------|--------------------|--|

| EE_SD  | 1         | I/OD | EEPROM Serial Data |  |

| EE_SC  | 1         | OD   | EEPROM Clock       |  |

#### **POWER SUPPLY**

| Symbol             | Pin Count | Type | Function                       |  |  |  |

|--------------------|-----------|------|--------------------------------|--|--|--|

| $V_{DD}A$          | 1         | Р    | FPD-Link PLL and Bandgap Power |  |  |  |

| $V_{DD}D$          | 2         | Р    | FPD-Link Receiver Power        |  |  |  |

| $V_{DD}$           | 5         | Р    | Digital Power                  |  |  |  |

| $V_{DD}IO$         | 6         | Р    | Digital I/O Power              |  |  |  |

| V <sub>SS</sub> P  | 1         | G    | FPD-Link PLL Ground            |  |  |  |

| V <sub>SS</sub> A  | 1         | G    | FPD-Link Bandgap Ground        |  |  |  |

| V <sub>SS</sub> D  | 1         | G    | FPD-Link Receiver Ground       |  |  |  |

| V <sub>SS</sub>    | 5         | G    | Digital Ground                 |  |  |  |

| V <sub>SS</sub> IO | 6         | G    | Digital I/O Ground             |  |  |  |

#### **TEST/CONFIGURATION**

| Symbol          | Pin Count | Туре | Function                                                                                                   |  |  |  |

|-----------------|-----------|------|------------------------------------------------------------------------------------------------------------|--|--|--|

| FIX_VERT        | 1         | I    | Selects VSYNC or ENAB for Vertical Timing                                                                  |  |  |  |

|                 |           |      | "0" = ENAB Vertical Timing "1" = VSYNC Vertical Timing                                                     |  |  |  |

| FIX_HORIZ       | 1         | I    | Selects HSYNC or ENAB for Horizontal Timing  "0" = ENAB Horizontal Timing  "1" = HYNC Horizontal Timing    |  |  |  |

| TEST[0,1,2,4,5] | 5         | I    | Test/Configuration Pins TEST[0]-Must be "0" TEST[1]-Must be "0" TEST[2] EEPROM Init Value Download Control |  |  |  |

|                 |           |      | "0" - Downloaded every 5 frames "1" - Downloaded once at Power-Up TEST[4]-Must be "0" TEST[5]-Must be "0"  |  |  |  |

### Pin Type Legend

I TTL Input

STI Schmitt Trigger TTL Input

I/TO TTL Input/TRI-STATE® Output

TO TRI-STATE Output

OD Open Drain Output

LVDSI Low Voltage Differential Signal Input

RSDSO Reduced Swing Differential Sgnal Output

P Power

G Ground

# Appendix A: GPO (General Purpose Output) Programming Examples

The GPO control generation is based on the internal line count and pixel count shown in *Figures 16, 17.* Two programmable registers (Vertical Start and Vertical Duration) control the vertical component of the control signal. This establishes at what line and for how many lines the control signal.

## Appendix A: GPO (General Purpose Output) Programming Examples (Continued)

nal will be active. Likewise, two programmable registers (Horizontal Start and Horizontal Duration) control the horizontal component of the control signal. The Horizontal register values determine at what pixel count the signal goes active and for how many pixel counts the signal stays active during each line. The Vertical Component enables the signal for however many lines programmed for and the Horizontal Component generates pulses within that vertical time period.

Generally the following types of signals are generated:

- 1. DC (either "1" or "0")

- 2. A pulse every line.

- 3. A pulse once a frame (either in pixels or lines)

Pulsed during active video (pulses are blanked during vertical blanking period of frame).

Table 3 describes the programming requirements for general types of pulses generated.

The GPO's also have a "toggle mode". This provides the capability to generate a "REVERSAL" signal used in most LCD applications. Bit[1] of the Central register is set to a "1" to enable toggle mode operation. The GPO is programmed so that a rising edge is produced when the control signal is required to toggle. This generally occurs once each line. Also, the # of edges generated per frame is programmed to be an odd #. This ensures that the control signal will alternate polarity from frame to frame.

Examples of GPO programming to produce specific control signals are included in the following pages.

**TABLE 3. GPO Pulse Generation**

| Туре | Vertical<br>Start | Vertical<br>Duration | Horizontal<br>Start | Horizontal<br>Duration | GPO Output                                                                                                                    |  |

|------|-------------------|----------------------|---------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | =0                | =0                   | =0                  | =0                     | Stuck 0 (When Output Polarity = "0") Stuck 1 (When Output Polarity = "1") Polarity control is in GPO Control Register bit [0] |  |

| 2    | =0                | =0                   | #C                  | #D                     | Pulse is generated every line beginning at #C pixel clocks from start of output line and lasting for #D pixel clocks.         |  |

| 3    | #A                | #B                   | #C                  | =0                     | Pulse begins at line #A, pixel #C and continues to line #(A+B), pixel #C (multi-line pulse)                                   |  |

| 4    | #A                | #B                   | #C                  | #D                     | Pulse generation begins at line #A and continue for #B lines.  Each pulse begins at pixel #C and lasts for #D pixel counts    |  |

Note 5: GPO[0]: provides for the data inverting function enabled by bit[3] of the Output Format Control Register.

GPO[9]: provides programmable output RGB data, Clock and SP blanking function enabled by bit[6] of the Input Format Control Register (RSR[2:0]P/N, RSG[2:0]P/N, RSB[2:0]P/N, RSCKP/N and SP).

DS101077-25

## Appendix A: GPO (General Purpose Output) Programming Examples

(Continued)

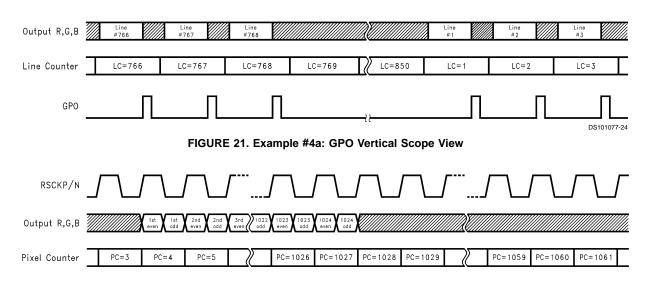

#### **GPO Programming Example #4a:**

Generate a control signal which transitions high at end of each line, has a pulse width of 0.5  $\mu$ s, and remains low during the vertical blanking period.

This control signal is used for latch pulse to the Column Drivers.

Based on 65 MHz XGA video, 1024 pixel/line, 768 lines/frame.

Horizontal time (clocks/line) = 1300 dot clocks Vertical period (lines/frame) = 850 lines

FIGURE 22. Example #4a: GPO Horizontal Scope View

Vertical control is active beginning at line #1 and remains active for line #768.

**GPO Vertical Start Register = 1** (0001<sub>H</sub>)

GPO

GPO Vertical Duration Register = 768  $(0300_{H})$

Positive pulse goes high each line at 1024 output clocks after last pixel are outputted on R, G, B.

Pulse remains high for 32 output clocks (0.5  $\mu$ s/15.38 ns = 32.5).

Note: 4 pixel counts are added to the output data start # because the GPO pixel count begins 4 clocks prior to the output data. Shown as Figure 17 "Internal Pixel Position Counter".

GPO Horizontal Start Register = 1028 (0404<sub>H</sub>)

**GPO** Horizontal Duration Register = 32 (0020<sub>H</sub>)

The controlled pulses are positive (bit[0] = "0") and the toggle circuitry is disabled (bit[1] = "0").

**GPO Control Register = 0**  $(00_{h})$   $(00000000_{R})$

## Appendix A: GPO (General Purpose Output) Programming Examples (Continued)

• ` ` ′

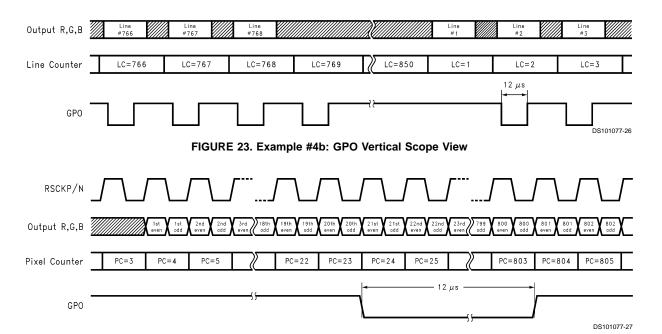

#### **GPO Programming Example #4b:**

Generate a control signal which transitions low 20 output clocks after the beginning of each output line, has a pulsewidth (low) of 12  $\mu$ s, and goes high during horizontal blanking.

This control signal is used as an output enable for the Row Drivers.

Based on 65 MHz XGA video, 1024 pixel/line,

768 lines/frame.

Horizontal time (clocks/line) = 1300 dot clocks.

Vertical period (lines/frame) = 850 lines.

FIGURE 24. Example #4b: GPO Horizontal Scope View

Vertical control is active beginning at line #2 and remains active for line #768.

GPO Vertical Start Register = 2 (0002<sub>H</sub>)

GPO Vertical Duration Register = 768 (0300<sub>H</sub>)

Negative pulse goes low each line at 20 output clocks after first pixel data are outputted on R, G, B. Pulse remains low for 780 output clocks (12  $\mu$ s/15.38 ns = 780).

Note: 4 pixel counts are added to the output data start # because the GPO pixel count begins 4 clocks prior to output data. (Shown as "Figure 17 Internal Pixel Position Counter".

GPO Horizontal Start Register = 24 (0018<sub>H</sub>)

**GPO** Horizontal Duration Register = 780 (030c<sub>H</sub>)

The controlled pulses are negative (bit[0] = "1") and the toggle circuitry is disabled (bit[1] = "0").

**GPO Control Register = 1**  $(01_{H})$   $(00000001_{B})$

## Appendix A: GPO (General **Purpose Output) Programming Examples** (Continued)

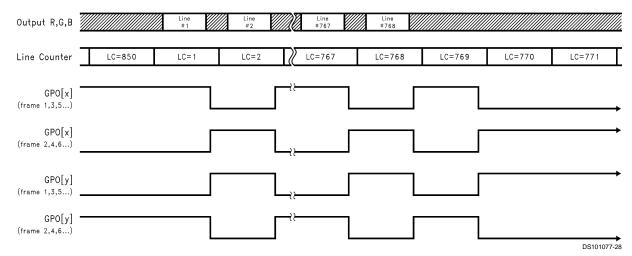

#### **GPO Programming Example #4c:**

Generate a control signal which toggles at 20 output clocks after end of each output line during horizontal blanking and alternates polarity each frame.

This control signal is used as the reversal signal. Based on 65 MHz XGA video, 1024 pixel/line, 768 lines/frame.

Horizontal time (clocks/line) = 1300 dot clocks Vertical period (lines/frame) = 850 lines

FIGURE 25. Example #4c: GPO Vertical Scope View

Control is active beginning at line #1 and remains active for

(Odd number programmed in Vertical Duration Register causes control signal to alternate polarity each frame)

GPO Vertical Start Register = 1 (0001<sub>H</sub>)

GPO Vertical Duration Register = 769 (0301<sub>H</sub>)

Positive going pulse causes output to toggle.

Edge occurs 20 output clocks after end of each line (1024 + 20 = 1044). Pulse duration is not critical since the output will be in toggle mode, but it cannot be "0".

Note: 4 pixel counts are added to the output data start # because the GPO pixel count begins 4 clocks prior to the output data. Shown as "Figure 17 Internal Pixel Position Counter."

GPO Horizontal Start Register = 1048 (0418<sub>H</sub>) [1044+4=1048]

**GPO** Horizontal Duration Register = 16 (0010<sub>H</sub>)

The controlled pulses are positive (bit[0] = "0") and the toggle circuitry is enabled (bit[1] = "1").

**GPO Control Register = 2**  $(02_{H})$   $(00000010_{B})$

(For a second control signal of opposite polarity, (GPO[y]) program another GPO Control Register with same count values, signal are negative. (bit[0] = "1").

**GPO Control Register = 3**  $(03_{H})$   $(00000011_{R})$

## Appendix A: GPO (General Purpose Output) Programming Examples (Continued)

### **Special Function GPOs**

FPD87310 has been provided two special purpose GPOs for manipulating the Output RGB Data, also the Clock and SP output can be controlled by GPO[9].

- 1. GPO[0] Output Data Inverting. Output \_Format\_Control\_Register bits[4:3]

- 2. GPO[9] Output Data Blanking. Input\_Format\_Control\_Register bits[7:6]

## Appendix A: GPO (General Purpose Output) Programming Examples

(Continued)

TABLE 4. GPO[0] Inverting and GPO[9] Blanking Logical Function

| _      | Output Format<br>Control Register |        | Output Format<br>Control Register |           | GPO[9]=0  |           | GPO[9]=1  |  |

|--------|-----------------------------------|--------|-----------------------------------|-----------|-----------|-----------|-----------|--|

| bit[7] | bit[6]                            | bit[4] | bit[3]                            | GPO[0]=0  | GPO[0]=1  | GPO[0]=0  | GPO[0]=1  |  |

|        |                                   | х      | 0                                 | -         | -         | -         | -         |  |

| 0      | x                                 | 0      | 1                                 | inv(data) | -         | inv(data) | -         |  |

|        |                                   | 1      | 1                                 | -         | inv(data) | -         | inv(data) |  |

|        |                                   | х      | 0                                 | 0         | 0         | -         | -         |  |

| 1      | 0                                 | 0      | 1                                 | 1         | 0         | inv(data) | -         |  |

|        |                                   | 1      | 1                                 | 0         | 1         | -         | inv(data) |  |

|        |                                   | х      | 0                                 | 1         | 1         | -         | -         |  |

| 1      | 1                                 | 0      | 1                                 | 0         | 1         | inv(data) | -         |  |

|        |                                   | 1      | 1                                 | 1         | 0         | -         | inv(data) |  |

#### Legends:

- output data is unchanged inv(data) output data is inverted 0 output data is all "0" 1 output data is all "1"

### TABLE 5. GPO[9] Blanking for Clock and SP

| Output Format<br>Control Register |        | GPO[9]=0        | GPO[9]=1        |  |  |

|-----------------------------------|--------|-----------------|-----------------|--|--|

| bit[7]                            | bit[6] |                 |                 |  |  |

| 0                                 | х      | Output CLK & SP | Output CLK & SP |  |  |

| 1                                 | х      | No Output ("0") | Output CLK & SP |  |  |

FIGURE 26. GPO[0] Inverting and GPO[9] Blanking Method

## Appendix A: GPO (General Purpose Output) Programming Examples (Continued)

FIGURE 27. GPO (General Purpose Output) Generation Method

## Appendix A: GPO (General Purpose Output) Programming Examples

(Continued)

FIGURE 28. GPO Nesting

FIGURE 29. GPO Combination Selector

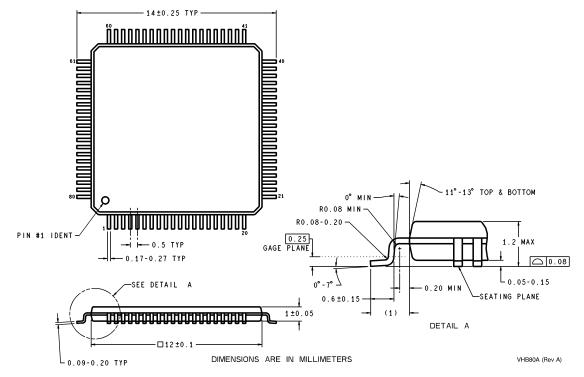

## Physical Dimensions inches (millimeters) unless otherwise noted

Thin Plastic Quad Flatpak (TQFP)

Dimensions are in Millimeters

NS Package Number VHB80A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com www.national.com National Semiconductor Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.