## **sPMIC for Micro-Converter Bias and Drivers**

#### **ISL1801**

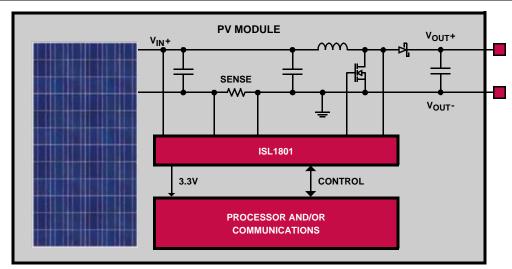

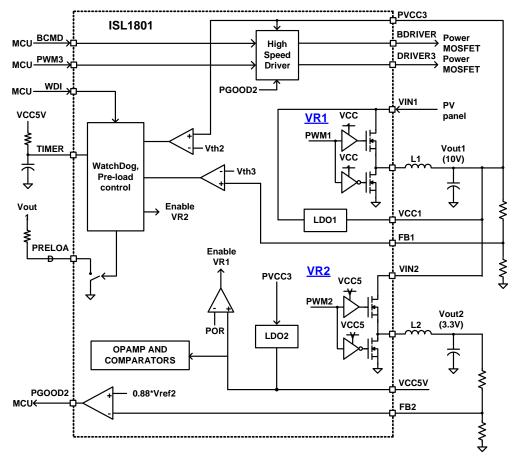

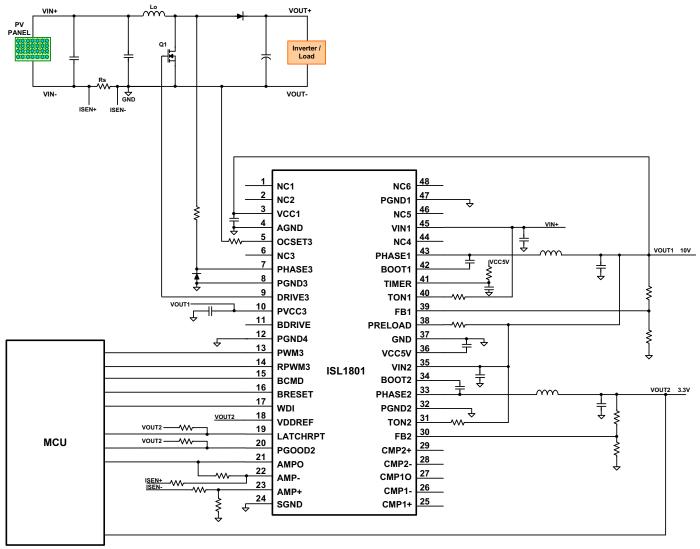

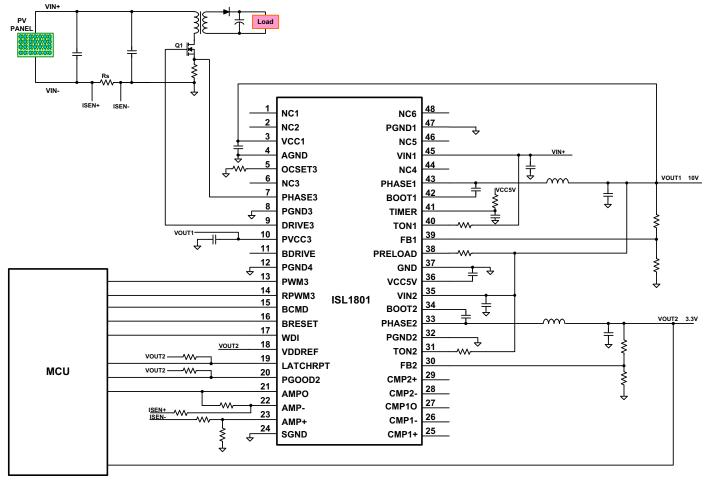

The ISL1801 is a power management IC (PMIC) optimized for solar array micro-converters and other systems operating from a high voltage DC supply. The ISL1801 can be used in buck, boost or buck-boost micro-converter topologies in order to maximize the energy harvest from a solar array. In addition to the power stage and main controller, the ISL1801 includes the bias regulators, gate drivers, current sense amplifier and comparators needed for micro-converters.

The ISL1801 integrates two switching regulators that can be used to generate the driver and the micro-controller (MCU) power supplies. In addition, it has a low offset, low drift amplifier for current sensing, two comparators for overvoltage and overcurrent protection plus a watch-dog timer to reset the MCU if necessary. This single IC solution offers high integration and dramatically reduces the total number of components in the micro-converter system improving the system reliability and reducing cost.

The first regulator takes input voltages ranging from 9V to 90V from the solar panel and outputs a regulated supply for drivers and the secondary regulator. The secondary regulator converts the output of the first regulator to a programmable micro-controller supply, typically 3.3V. A high voltage start-up LDO provides the necessary bias voltage until the switching regulator is operating.

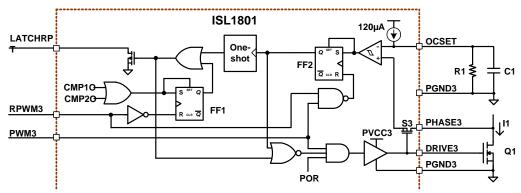

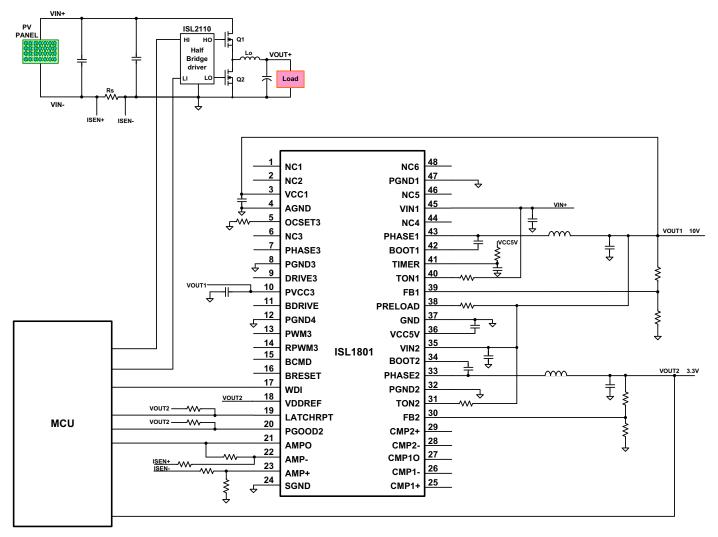

The ISL1801 integrates two high speed MOSFET drivers for Buck, Flyback or Boost converters configured as shown in the application schematics. The Drive3 also has the integrated peak current limiting capabilities.

The ISL1801 includes comprehensive start-up, shutdown and fault logic to ensure reliable operation of micro-converters in solar applications.

#### **Features**

- . 90V Input Buck Switching Regulator

- 120mA (minimum) Output with OCP, OVP, OTP

- Integrated Upper and Lower MOSFETs

- 90V On-Chip Start-Up 6.7V LDO

- Low Voltage Buck Switching Regulator

- 200mA (minimum) Output with OCP, OVP

- Integrated Upper and Lower MOSFETs

- PGOOD Output

- · Low Voltage Bias LDO

- Input Voltage Range from 6V to 14V

- Regulated 5V Output up to 10mA

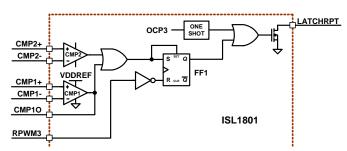

- · Dual High-Speed Gate Driver

- 14V Voltage Rating

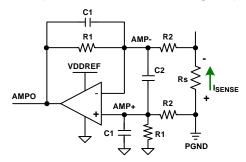

- 2A Peak Sourcing and 5A Peak Sinking Current

- Peak Current Limit for DRIVE3

- Dedicated Amplifier for Accurate Current Sense

- Two Comparators for General Purpose Protection

- · Integrated Watch-dog Timer

## Applications

- Solar Power Optimizer

- Solar Power Micro-Inverter

- Solar Charge Controller

- · Telecom Power Supply

### **Related Literature**

• ISL1801 Product Folder

FIGURE 1. TYPICAL APPLICATION

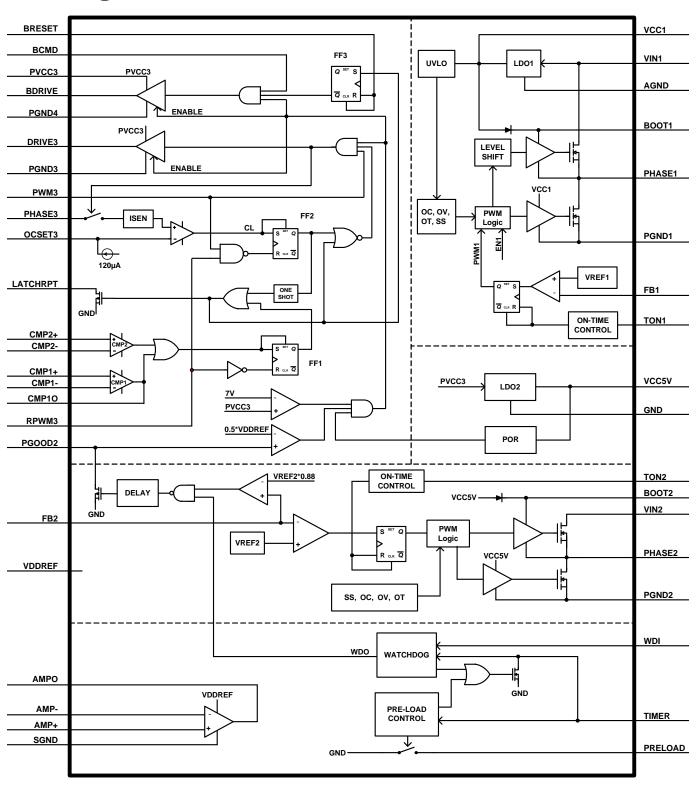

# **Block Diagram**

FIGURE 2. ISL1801 BLOCK DIAGRAM

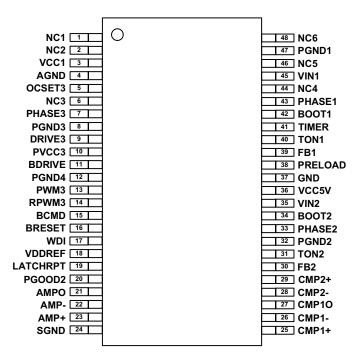

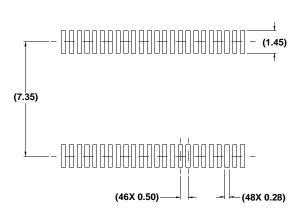

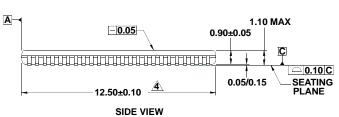

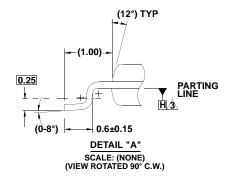

## **Pin Configuration**

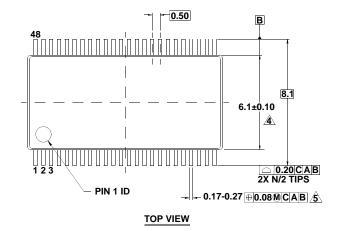

ISL1801 (48 LD TSSOP) TOP VIEW

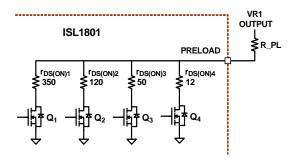

## **Pin Descriptions**

| TSSOP | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | NC1    | NC pin.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2     | NC2    | NC pin.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3     | VCC1   | High voltage start-up LD01 output and also the pin providing bias to the HV circuitry on the ISL1801. Place a 1µF ceramic capacitor from this pin to ground as decoupling cap. Connect this pin to the output of the high voltage regulator. When the output of the switching regulator is stable, the start-up LD0 is disabled and the chip bias is supplied by the more efficient switching regulator. |

| 4     | AGND   | Analog ground pin for VCC1.                                                                                                                                                                                                                                                                                                                                                                              |

| 5     | OCSET3 | A resistor between this pin and ground set the peak current limit threshold for the power stage MOSFET at Phase3. A $0.01\mu F$ capacitor can be used at this pin to filter any switching noise.                                                                                                                                                                                                         |

| 6     | NC3    | NC pin.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7     | PHASE3 | The phase node pin of the power stage controlled by DRIVE3. This pin should be connected to the drain of the power MOSFET through one resistor and diode which prevent the voltage at Phase3 pin from dropping below -0.6V. Refer to the typical application schematics starting on page 23, for correct connections.                                                                                    |

| 8     | PGND3  | The ground pin for the high speed driver DRIVE3.                                                                                                                                                                                                                                                                                                                                                         |

| 9     | DRIVE3 | The output of the high speed driver.                                                                                                                                                                                                                                                                                                                                                                     |

| 10    | PVCC3  | The bias input pin for both the high speed driver and the low speed driver. It is normally connected to V <sub>OUT1</sub> . PVCC3 also powers LDO2 which provides the bias supply for all internal control circuits.                                                                                                                                                                                     |

| 11    | BDRIVE | The output of the high speed driver controlled by the BCMD signal.                                                                                                                                                                                                                                                                                                                                       |

| 12    | PGND4  | The ground pin for BDRIVE.                                                                                                                                                                                                                                                                                                                                                                               |

| 13    | PWM3   | The PWM input signal for DRIVE3.                                                                                                                                                                                                                                                                                                                                                                         |

# Pin Descriptions (Continued)

| TSSOP | SYMBOL   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14    | RPWM3    | The reset signal for both flip-flops in the LATCHRPT circuit and overcurrent-protection circuit of DRIVE3/PHASE3. RPWM3=0 will reset both flip-flops. Avoid running PWM3=1 with RPWM3=0 for a long time or at very high frequency, since it may result in very high switching frequency at DRIVE3 in the overcurrent protection condition.                        |

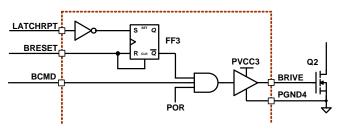

| 15    | BCMD     | Logic input to control BDRIVE.                                                                                                                                                                                                                                                                                                                                    |

| 16    | BRESET   | Logic input to reset the LATCHRPT flip-flop in the BDRIVE control circuit.                                                                                                                                                                                                                                                                                        |

| 17    | WDI      | Watch-dog circuit clock input signal.                                                                                                                                                                                                                                                                                                                             |

| 18    | VDDREF   | Reference signal for output signals to the MCU. Connect this pin to V <sub>OUT2</sub> , which provides a clamp voltage for all the output pins (CMP10, AMP0) interfacing with the MCU.                                                                                                                                                                            |

| 19    | LATCHRPT | Open drain output signal. When either comparator or Phase3 overcurrent protection is triggered, this pin is pulled LOW to inform the MCU. The two internal flip-flops used to latch these faults can be reset by setting RWPM3=0.                                                                                                                                 |

| 20    | PGOOD2   | Open drain output pin indicating power good for the low voltage regulator. A logic low signal at the watch-dog output will also pull this pin LOW allowing it to reset the MCU in either fault condition.                                                                                                                                                         |

| 21    | AMPO     | Integrated amplifier output.                                                                                                                                                                                                                                                                                                                                      |

| 22    | AMP-     | Integrated amplifier inverting input.                                                                                                                                                                                                                                                                                                                             |

| 23    | AMP+     | Integrated amplifier non-inverting input.                                                                                                                                                                                                                                                                                                                         |

| 24    | SGND     | The ground pin of the sensitive control circuits biased by VCC5V. Connect this pin to a ground plane with minimum noise.                                                                                                                                                                                                                                          |

| 25    | CMP1+    | Comparator 1 non-inverting input.                                                                                                                                                                                                                                                                                                                                 |

| 26    | CMP1-    | Comparator 1 inverting input.                                                                                                                                                                                                                                                                                                                                     |

| 27    | CMP10    | Comparator 1 output. This signal also triggers the flip-flop for the LATCHRPT signal.                                                                                                                                                                                                                                                                             |

| 28    | CMP2-    | Comparator 2 inverting input.                                                                                                                                                                                                                                                                                                                                     |

| 29    | CMP2+    | Comparator 2 non-inverting input.                                                                                                                                                                                                                                                                                                                                 |

| 30    | FB2      | The feedback sense pin for the low voltage switching regulator. The output voltage is programmable by a resistor divider feeding back the output voltage.                                                                                                                                                                                                         |

| 31    | TON2     | On-time adjustment for the secondary (low voltage) switching regulator. Connect a resistor from this pin to the input voltage of the low voltage regulator to adjust the ON-time and switching frequency.                                                                                                                                                         |

| 32    | PGND2    | The ground pin of the low voltage switching regulator's power stage. There are switching power current pulses coming out of this pin. Place the ground pad of the input power stage decoupling cap as close to this pin as possible.                                                                                                                              |

| 33    | PHASE2   | The phase node of the low voltage switching regulator. This pin should be connected to the output inductor.                                                                                                                                                                                                                                                       |

| 34    | B00T2    | The boot pin of the low voltage switching regulator. An external bootstrap capacitor is required. This pin provides bias voltage to the high-side MOSFET driver. A bootstrap circuit is used to create a voltage suitable to drive the internal N-channel MOSFET. The boot diode is included within the IC.                                                       |

| 35    | VIN2     | Input of the low voltage switching regulator. This pin is connected to the drain of the internal high side MOSFET.                                                                                                                                                                                                                                                |

| 36    | VCC5V    | The output of the internal 5V LDO providing the bias supply for the IC. A $1\mu F$ ceramic decoupling capacitor should be placed from this pin to ground.                                                                                                                                                                                                         |

| 37    | GND      | The analog ground pin.                                                                                                                                                                                                                                                                                                                                            |

| 38    | PRELOAD  | Place a resistor from this pin to V <sub>OUT1</sub> to provide the loading for the high voltage switching regulator. When this load can be successfully driven the low voltage switching regulator will be enabled. If the PV module output power is insufficient, the low voltage switching regulator will not start.                                            |

| 39    | FB1      | The feedback sense pin for the high voltage switching regulator. The output voltage is programmable by a resistor divider feeding back the output voltage.                                                                                                                                                                                                        |

| 40    | TON1     | On-time adjustment for the high voltage switching regulator. Connect a resistor from this pin to the input voltage of the high voltage regulator to adjust the ON-time and switching frequency.                                                                                                                                                                   |

| 41    | TIMER    | Tie a resistor from VCC5V to this pin and a cap from this pin to ground. The RC time constant sets the time needed for both start-up and watch-dog timing. A minimum of $0.01\mu\text{F}$ should be connected to this pin to filter the switching noise from BOOT1. The pull-up resistor should not be more than $200\text{k}\Omega$ to assure correct operation. |

## Pin Descriptions (Continued)

| TSSOP | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                  |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42    | B00T1  | The boot pin of the high voltage switching regulator. An external bootstrap capacitor is required. This pin provides bias voltage to the high-side MOSFET driver. A bootstrap circuit is used to create a voltage suitable to drive the internal N-channel MOSFET. The boot diode is included within the IC. |

| 43    | PHASE1 | The phase node of the high voltage switching regulator, VR1. This pin should be connected to the output inductor.                                                                                                                                                                                            |

| 44    | NC4    | NC pin.                                                                                                                                                                                                                                                                                                      |

| 45    | VIN1   | Input to both the high voltage switching regulator and the high voltage start-up LDO1. This pin connects the high voltage supply to the drain of the internal high side MOSFET.                                                                                                                              |

| 46    | NC5    | NC pin.                                                                                                                                                                                                                                                                                                      |

| 47    | PGND1  | The ground pin of the high voltage switching regulator's power stage. There are switching power current pulses coming out of this pin. Place the VIN1 decoupling capacitor as close as possible to this pin.                                                                                                 |

| 48    | NC6    | NC pin.                                                                                                                                                                                                                                                                                                      |

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | V <sub>IN1</sub> RANGE<br>(V) | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|--------------------------------|-----------------|-------------------------------|--------------------|----------------------|----------------|

| ISL1801IVZ                     | ISL1801 IVZ     | 9 to 90                       | -40 to +85         | 48 Ld TSSOP          | M48.240        |

| ISL1801EVAL1ZA                 | Evaluation Boar | d                             |                    |                      |                |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL1801. For more information on MSL please see tech brief TB363.

## **ISL1801**

# **Table of Contents**

| Absolute Maximum Ratings                                                           | 7    |

|------------------------------------------------------------------------------------|------|

| Thermal Information                                                                | 7    |

| Recommended Operating Conditions                                                   | 7    |

| High Voltage 10V Bias Regulator VR1 Electrical Specifications                      | 7    |

| Low Voltage 3.3V Bias Regulator VR2 Electrical Specifications                      | 8    |

| Driver Electrical Specifications                                                   | 9    |

| Watch-Dog Timer Electrical Specifications                                          | . 10 |

| Current Sense Opamp Electrical Specifications                                      | . 10 |

| Dual High Speed Comparator Electrical Specifications                               | . 11 |

| Preload Electrical Specifications                                                  | . 11 |

| Typical Performance Curves                                                         | . 12 |

| Test Waveforms                                                                     | . 13 |

| Summary of Operation                                                               | . 15 |

| Detailed Operation                                                                 |      |

| Dual Synchronous Buck Switching Regulators With Constant On-Time Control           |      |

| Dual LDO Bias Supplies                                                             |      |

| Dual Low Side MOSFET Drivers                                                       |      |

| Dual High Speed Comparator                                                         |      |

| Precision Amplifier                                                                |      |

| Preload Operation                                                                  |      |

| Watch-Dog Timer                                                                    |      |

| Power-Up Sequence.                                                                 |      |

| Power-Down Sequence                                                                |      |

| Overvoltage Protection                                                             |      |

| -                                                                                  |      |

| Applications Information                                                           |      |

| Application Circuit 1, Boost Regulator                                             |      |

| Application Circuit 2, Flyback Regulator                                           |      |

| Application Circuit 3, Synchronous Buck Regulator with External Half Bridge Driver |      |

| Application Circuit 4, Buck-Boost Regulator with External Half Bridge Drivers      | 26   |

| PC Board Layout Guidelines                                                         | . 26 |

| Layout Procedure                                                                   | 27   |

| Revision History                                                                   | . 28 |

| Products                                                                           | . 28 |

| Package Outline Drawing                                                            | . 29 |

### **Absolute Maximum Ratings**

| Supply Voltage, VCC1, VBOOT1-VPHASE1             | 0.3V to 16V        |

|--------------------------------------------------|--------------------|

| Voltage on VIN1                                  | 0.3V to 100V       |

| Voltage on BOOT1                                 | 0.3V to 116V       |

| Voltage on PHASE1, PHASE3                        | 0.3V to 100V       |

| Voltage on VIN2, PRELOAD                         | 0.3V to 16V        |

| Voltage on PHASE2                                | 0.3V to 16V        |

| Voltage on BOOT2                                 | 0.3V to 22.5V      |

| BDRIVE, DRIVE3 Voltages                          | 0.3V to VCC1+0.3V  |

| Supply Voltage, VCC5V                            | 0.3V to 6.5V       |

| Voltage on All Other Pins                        | 0.3V to VCC5V+0.3V |

| LDO(VCC5V) Current (Continuous)                  | 10mA               |

| LDO(VCC1) Current (Continuous)                   | 10mA               |

| ESD Rating                                       |                    |

| Human Body Model (Tested per JESD22-A114E        | i)2kV              |

| Machine Model (Tested per JESD22-A115-A)         | 200V               |

| Latch Up (Tested per JESD-78B; Class 2, Level A) | 100mA              |

|                                                  |                    |

#### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}(^{\circ}C/W)$ | $\theta_{JC}$ (°C/W) |

|-------------------------------------------|----------------------------|----------------------|

| 48 Ld TSSOP Package (Notes 4, 5)          | 58                         | 16                   |

| Maximum Junction Temperature (Plastic Pac | kage)                      | +150°C               |

| Storage Temperature Range                 | 6                          | 5°C to +150°C        |

| Pb-Free Reflow Profile                    |                            | . see link below     |

| http://www.intersil.com/pbfree/Pb-FreeRe  | eflow.asp                  |                      |

## **Recommended Operating Conditions**

| Temperature Range     | 40°C to +85°C |

|-----------------------|---------------|

| Supply Voltage, VCC1  | 6V to 14V     |

| Voltage on VIN1 Pin   | 9V to 90V     |

| Voltage on BOOT1 Pin  | 15V to 104V   |

| Voltage on VIN2 Pin   | 6V to 14V     |

| Voltage on BOOT2 Pin  |               |

| Supply Voltage, VCC5V | 4.5V to 5.5V  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

- 5. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

# **High Voltage 10V Bias Regulator VR1 Electrical Specifications** $T_A = +25$ °C, VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40°C to +85°C.

| SYMBOL                 | PARAMETER                  | TEST CONDITIONS                                                                                                                                                                | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |

|------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-------|

| V <sub>IN1</sub> SUPPI | <u>.</u> Y                 |                                                                                                                                                                                |                 |                 |                 |       |

| V <sub>IN1</sub>       | Input Voltage Range        |                                                                                                                                                                                | 9               |                 | 90              | V     |

|                        | Shut-Down Current          | V <sub>IN1</sub> = 5V                                                                                                                                                          |                 | 500             |                 | μΑ    |

|                        | Operating Current          | V <sub>IN1</sub> = 40V, PVCC3 = 0V, all inner circuits of the low voltage section are disabled, and only LDO1 and some inner circuits of the high voltage section are running. |                 | 1.3             | 2               | mA    |

| VCC1 SUPP              | PLY                        |                                                                                                                                                                                |                 |                 |                 |       |

|                        | VCC1 LDO Regulator Output  |                                                                                                                                                                                |                 | 6.8             |                 | V     |

|                        | Rising UV Threshold        |                                                                                                                                                                                | 5.2             | 5.9             | 6.6             | V     |

|                        | UV Threshold Hysteresis    |                                                                                                                                                                                |                 | 1               |                 | V     |

| REFERENC               | E AND SOFT-START           |                                                                                                                                                                                |                 |                 |                 |       |

| V <sub>REF1</sub>      | Internal Reference Voltage |                                                                                                                                                                                | 1.98            | 2               | 2.02            | V     |

| POWER MO               | OSFETS                     |                                                                                                                                                                                |                 |                 |                 | •     |

| r <sub>DS(ON)</sub>    | Upper Switch ON-Resistance | I <sub>OUT</sub> = 50mA, BOOT1-PHASE1 = 6V, test at wafer sort                                                                                                                 |                 | 2.3             | 3.2             | Ω     |

| r <sub>DS(ON)</sub>    | Lower Switch ON-Resistance | I <sub>OUT</sub> = 50mA, VCC1 = 10V, test at wafer sort                                                                                                                        |                 | 1.2             | 2               | Ω     |

| ON TIME GI             | ENERATOR                   |                                                                                                                                                                                |                 |                 |                 |       |

|                        | t <sub>ON</sub>            | V <sub>IN1</sub> = 10V, R <sub>ON</sub> = 1M                                                                                                                                   | 2.75            | 3               | 3.25            | μs    |

|                        | t <sub>ON</sub>            | V <sub>IN1</sub> = 90V, R <sub>ON</sub> = 1M                                                                                                                                   |                 | 0.3             |                 | μs    |

| MINIMUM (              | OFF TIME                   |                                                                                                                                                                                |                 |                 |                 |       |

|                        | T <sub>MINOFF</sub>        |                                                                                                                                                                                |                 | 0.3             |                 | μs    |

| MINIMUM (              | ON TIME                    |                                                                                                                                                                                |                 |                 |                 |       |

|                        | T <sub>MINON</sub>         |                                                                                                                                                                                |                 | 0.3             |                 | μs    |

# **High Voltage 10V Bias Regulator VR1 Electrical Specifications** $T_A = +25 \,^{\circ}\text{C}$ , VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40 $\,^{\circ}\text{C}$ to +85 $\,^{\circ}\text{C}$ . (Continued)

| SYMBOL    | PARAMETER                        | TEST CONDITIONS                                                                                                                | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |

|-----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-------|

| REGULATIO | N AND RIPPLE                     |                                                                                                                                |                 |                 |                 |       |

|           | System Accuracy                  |                                                                                                                                |                 | ±3              |                 | %     |

|           | Output Voltage Ripple            | V <sub>IN1</sub> = 40V, V <sub>OUT</sub> = 10V, F <sub>SW</sub> = 100kHz,<br>L <sub>OUT</sub> = 470µH, C <sub>OUT</sub> = 22µF |                 | 100             |                 | mV    |

| OVERCURR  | ENT PROTECTION                   |                                                                                                                                |                 |                 |                 |       |

|           | Overcurrent Protection Threshold | Test on Wafer Sort                                                                                                             | 120             | 185             | 230             | mA    |

| OVERVOLTA | AGE PROTECTION                   |                                                                                                                                |                 |                 |                 |       |

|           | FB1 OVP Threshold                |                                                                                                                                |                 | 2.4             |                 | ٧     |

| THERMAL S | SHUTDOWN                         |                                                                                                                                |                 |                 |                 |       |

|           | Thermal Shut-down Temperature    | Rising Threshold                                                                                                               |                 | 150             |                 | °C    |

|           | Thermal Shut-down Hysteresis     |                                                                                                                                |                 | 30              |                 | °C    |

# Low Voltage 3.3V Bias Regulator VR2 Electrical Specifications $T_A = +25$ °C, VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40°C to +85°C.

| SYMBOL                 | PARAMETER                        | TEST CONDITIONS                                                                                             | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |

|------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-------|

| V <sub>IN2</sub> SUPPL | Y                                |                                                                                                             |                 | I I             |                 |       |

|                        | Input Voltage Range              |                                                                                                             |                 |                 | 14              | ٧     |

| VCC5 SUPP              | LY                               |                                                                                                             | 1               | 1               |                 |       |

|                        | VCC5 LDO Output                  |                                                                                                             |                 | 5               |                 | ٧     |

|                        | Rising UV Threshold              |                                                                                                             | 4.3             | 4.5             | 4.7             | V     |

|                        | Hysteresis                       |                                                                                                             |                 | 165             |                 | m۷    |

| REFERENCI              | E AND SOFT-START                 |                                                                                                             |                 |                 |                 |       |

| V <sub>REF</sub>       | Internal Reference Voltage       |                                                                                                             |                 | 0.7             |                 | V     |

|                        | Soft-Start Interval              | Current Limiting Threshold of VR2<br>Ramps from 25% to 100%                                                 |                 | 1.5             |                 | ms    |

| POWER MO               | SFETs                            |                                                                                                             |                 |                 |                 |       |

| r <sub>DS(ON)</sub>    | Upper Switch ON-Resistance       | I <sub>OUT</sub> = 200mA                                                                                    |                 | 1               | 2               | Ω     |

| r <sub>DS(ON)</sub>    | Lower Switch ON-Resistance       | I <sub>OUT</sub> = 200mA                                                                                    |                 | 1               | 2               | Ω     |

| ON TIME GE             | ENERATOR (4 trim options)        |                                                                                                             |                 |                 |                 |       |

|                        | ton                              | V <sub>IN2</sub> = 10V, R <sub>ON</sub> = 1M                                                                | 950             | 1100            | 1250            | ns    |

|                        | t <sub>ON</sub>                  | V <sub>IN2</sub> = 12V, R <sub>ON</sub> = 1M                                                                |                 | 800             |                 | ns    |

| мінімим с              | ON TIME                          |                                                                                                             |                 |                 |                 |       |

|                        | T <sub>MINON</sub>               |                                                                                                             |                 | 150             |                 | ns    |

| мінімим с              | OFF TIME                         |                                                                                                             | •               | 1               |                 |       |

|                        | T <sub>MINOFF</sub>              |                                                                                                             |                 | 150             |                 | ns    |

| REGULATIO              | N AND RIPPLE                     |                                                                                                             | •               | 1               |                 |       |

|                        | System Accuracy                  |                                                                                                             |                 | ±2              |                 | %     |

|                        | Output Voltage Ripple            | $V_{IN2}$ = 10V, $V_{OUT2}$ = 3.3V,<br>$F_{SW}$ = 300kHz,<br>$L_{OUT}$ = 47 $\mu$ H, $C_{OUT}$ = 22 $\mu$ F |                 | 30              |                 | mV    |

| OVERCURR               | ENT PROTECTION                   | '                                                                                                           | 1               | 1               |                 | 1     |

|                        | Overcurrent Protection Threshold |                                                                                                             | 200             | 245             | 290             | mA    |

### **ISL1801**

# Low Voltage 3.3V Bias Regulator VR2 Electrical Specifications $T_A = +25$ °C, VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40°C to +85°C. (Continued)

| SYMBOL    | PARAMETER                  | TEST CONDITIONS                                           | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |  |  |  |

|-----------|----------------------------|-----------------------------------------------------------|-----------------|-----------------|-----------------|-------|--|--|--|

| OVERVOLTA | OVERVOLTAGE PROTECTION     |                                                           |                 |                 |                 |       |  |  |  |

|           | FB2 OVP Threshold          |                                                           |                 | 0.775           |                 | V     |  |  |  |

| PG00D2 (0 | PEN DRAIN OUTPUT)          |                                                           |                 |                 | II.             |       |  |  |  |

|           | Power-Good Lower Threshold | Fraction of V <sub>OUT2</sub> set point; 3µs noise filter | 83              | 90              | 95              | %     |  |  |  |

|           | PGOOD2 Leakage Current     | V <sub>PULLUP</sub> = 3.3V                                |                 |                 | 1               | μΑ    |  |  |  |

|           | PGOOD2 Voltage Low         | I <sub>PGOOD2</sub> = 4mA                                 |                 |                 | 0.5             | V     |  |  |  |

# **Driver Electrical Specifications** $T_A = +25 \,^{\circ}\text{C}$ , VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40 $^{\circ}\text{C}$ to +85 $^{\circ}\text{C}$ .

| SYMBOL           | PARAMETER                                 | TEST CONDITIONS                                          | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |

|------------------|-------------------------------------------|----------------------------------------------------------|-----------------|-----------------|-----------------|-------|

| PVCC3 SUF        | PPLY                                      |                                                          |                 |                 |                 |       |

|                  | Shut-down Current                         | PVCC3 = 3V                                               |                 | 0.85            | 1               | mA    |

|                  | Operating Current                         | PVCC3 = 10V, Drive3 = Bdrive = 1, or 0                   |                 | 1.75            | 3.2             | mA    |

|                  | Operating Current                         | PVCC3 = 10V, F <sub>S</sub> = 50kHz, 10nF load on Drive3 |                 | 3.5             |                 | mA    |

| LOGIC INP        | JT PINS                                   |                                                          |                 | 1               |                 |       |

|                  | Low Level Voltage Threshold               | PWM3, RPWM3, BCMD, BRESET,<br>VDDRFE = 3.3V              |                 |                 | 0.7             | V     |

|                  | High Level Voltage Threshold              | PWM3, RPWM3, BCMD, BRESET,<br>VDDRFE = 3.3V              | 2.4             |                 |                 | V     |

|                  | Input Pull-Down Current                   |                                                          |                 | 500             |                 | nA    |

| DRIVE3 AN        | D BDRIVE GATE DRIVER                      |                                                          |                 |                 |                 |       |

|                  | Low Level Output Voltage                  | I <sub>DRIVE</sub> = 100mA                               |                 | 50              | 250             | mV    |

|                  | High Level Output Voltage                 | I <sub>DRIVE</sub> = -100mA                              | 9.25            | 9.8             |                 | V     |

|                  | Peak Pull-Down Current                    | V <sub>DRIVE</sub> = 0V                                  |                 | 5               |                 | Α     |

|                  | Peak Pull-Up Current                      | V <sub>DRIVE</sub> = 10V                                 |                 | 2               |                 | Α     |

|                  | Active Pull-Down Resistance before POR    | VCC1 = 10V                                               |                 | 270             | 600             | Ω     |

| OVERCURF         | RENT PROTECTION OCSET3                    |                                                          |                 |                 |                 |       |

|                  | OC Threshold Current                      | Current from OCSET3 Pin                                  | 110             | 120             | 130             | μΑ    |

|                  | OC Comparator Input Offset                |                                                          |                 | 3               |                 | mV    |

| DRIVE3 AN        | D BDRIVE SWITCHING CHARACTERISTICS        | •                                                        |                 |                 |                 |       |

| t <sub>PHL</sub> | Turn-Off Propagation Delay                | PWM Falling to DRIVE Falling                             |                 | 200             | 300             | ns    |

| t <sub>PLH</sub> | Turn-On Propagation Delay                 | PWM Rising to DRIVE Rising                               | 150 300         |                 | 300             | ns    |

| t <sub>RC</sub>  | Output Rise Time (10% to 90%)             | C <sub>L</sub> = 10nF                                    |                 | 90              |                 | ns    |

| t <sub>FC</sub>  | Output Fall Time (90% to 10%)             | C <sub>L</sub> = 10nF                                    |                 | 50              |                 | ns    |

| t <sub>PW</sub>  | Input Pulse Width that Changes the Output |                                                          | 300             |                 |                 | ns    |

## **ISL1801**

# Watch-Dog Timer Electrical Specifications $T_A = +25 \,^{\circ}\text{C}$ , VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40 $^{\circ}\text{C}$ to +85 $^{\circ}\text{C}$ .

| SYMBOL     | PARAMETER                            | TEST CONDITIONS               | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |

|------------|--------------------------------------|-------------------------------|-----------------|-----------------|-----------------|-------|

| INPUT PIN  |                                      |                               |                 |                 |                 |       |

|            | Low Level Input Voltage Threshold    | WDI, VDDRFE = 3.3V, VCC5 = 5V |                 |                 | 0.7             | V     |

|            | High Level Input Voltage Threshold   | WDI, VDDRFE = 3.3V, VCC5 = 5V | 2.4             |                 |                 | V     |

|            | Disable Mode Input Voltage Threshold | WDI, VDDRFE = 3.3V, VCC5 = 5V |                 | 4.5             |                 | V     |

|            | Inner Pull-up Resistor               | Pull up to VCC5               |                 | 50              |                 | kΩ    |

|            | Minimum Pulse Width                  | WDI, VDDRFE = 3.3V, VCC5 = 5V |                 | 300             |                 | ns    |

| TIME-OUT ( | CHARACTERISTICS                      |                               |                 |                 |                 |       |

|            | Timer Rising Threshold               | VCC5 = 5V                     |                 | 4.5             |                 | V     |

| SWITCHING  | CHARACTERISTICS                      |                               |                 |                 |                 |       |

|            | Timer Reset Pulse Width              |                               |                 | 1.5             |                 | ms    |

|            | Timer Leakage Current                | Timer = 5V                    |                 |                 | 1.2             | μΑ    |

|            | Timer Voltage Low                    | I <sub>Timer</sub> = 4mA      |                 |                 | 0.5             | V     |

|            | PG00D2 Reset Pulse Width             |                               |                 | 1               |                 | ms    |

# Current Sense Opamp Electrical Specifications $T_A = +25 \,^{\circ}\text{C}$ , VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40 $^{\circ}\text{C}$ to +85 $^{\circ}\text{C}$ .

| SYMBOL                                          | PARAMETER                           | TEST CONDITIONS                                                                 | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS              |

|-------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------|-----------------|-----------------|-----------------|--------------------|

|                                                 | Input Offset Voltage                |                                                                                 | -600            | 0               | 600             | μV                 |

|                                                 | Input Offset Voltage Drift          |                                                                                 |                 | ±0.6            |                 | μV/°C              |

|                                                 | Input Bias Current                  |                                                                                 |                 | 3               |                 | nA                 |

|                                                 | Input Offset Current                |                                                                                 |                 | ±1              |                 | nA                 |

| V <sub>CM_min</sub> Minimum Common-Mode Voltage |                                     |                                                                                 |                 | -0.1            |                 | V                  |

| V <sub>CM_max</sub>                             | Maximum Common-Mode Voltage         |                                                                                 |                 | 2               |                 | V                  |

| CMRR                                            | Common-Mode Rejection Ratio         | V <sub>CM</sub> = -0.1V to 2V                                                   |                 | 100             |                 | dB                 |

| PSRR                                            | Power Supply Rejection Ratio        | V <sub>CC</sub> = 3.3V to 5.5V, V <sub>OUT2</sub> = 3.3V                        |                 | 100             |                 | dB                 |

|                                                 | Large Signal Voltage Gain           |                                                                                 |                 | 220             |                 | V/mV               |

|                                                 | Maximum Output Voltage Swing        | Output low, $R_L = 100k\Omega$ to $V_{CM}$                                      |                 | 5.3             |                 | mV                 |

|                                                 |                                     | Output high, $R_L = 100k\Omega$ to $V_{CM}$ ;<br>VDDREF Tied to 3.3V $V_{OUT2}$ |                 | 3.0             |                 | V                  |

|                                                 | Short-Circuit Output Source Current | $R_L = 10\Omega$ to $V_{CM}$                                                    |                 | 30              |                 | mA                 |

| C SPECIFI                                       | CATIONS                             |                                                                                 |                 | +               |                 | +                  |

|                                                 | Gain Bandwidth Product              | $R_L = 10k\Omega$ to $V_{CM}$                                                   |                 | 130             |                 | kHz                |

|                                                 | Input Noise Voltage Peak-to-Peak    | F = 0.1Hz to 10Hz                                                               |                 | 1.4             |                 | μV <sub>P-P</sub>  |

|                                                 | Input Noise Voltage Density         | f <sub>O</sub> = 1kHz                                                           |                 | 64              |                 | nV/√ <del>Hz</del> |

|                                                 | Input Noise Current Density         | f <sub>O</sub> = 10kHz                                                          |                 | 0.19            |                 | pA/√ <del>Hz</del> |

|                                                 | Slew Rate                           |                                                                                 |                 | 100             |                 | V/ms               |

#### Dual High Speed Comparator Electrical Specifications TA = +25°C, VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40°C to +85°C.

| SYMBOL              | PARAMETER                          | TEST CONDITIONS                                                                                   | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |

|---------------------|------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-------|

|                     | Input Offset Voltage               |                                                                                                   | -5              | 0               | 5               | mV    |

|                     | Input Offset Voltage Drift         |                                                                                                   |                 | ±12             |                 | μV/°C |

|                     | Input Bias Current                 |                                                                                                   |                 | ±1              |                 | pA    |

|                     | Input Offset Current               |                                                                                                   |                 | ±1              |                 | pA    |

| V <sub>CM_min</sub> | Minimum Common-Mode Voltage        |                                                                                                   |                 | -0.2            |                 | V     |

| V <sub>CM_max</sub> | Maximum Common-Mode Voltage        |                                                                                                   |                 | 3.3             |                 | V     |

| CMRR                | Common-Mode Rejection Ratio        | V <sub>CM</sub> = -0.2V to V <sub>OUT2</sub>                                                      |                 | 62              |                 | dB    |

|                     | Input Common-Mode Capacitance      |                                                                                                   |                 | 2               |                 | pF    |

|                     | Input Differential Capacitance     |                                                                                                   |                 | 4               |                 | pF    |

|                     | Output High Voltage                | I <sub>OUT</sub> = -0.3mA; VDDREF Tied to 3.3V<br>V <sub>OUT2</sub>                               | 2.7             | 3               |                 | V     |

|                     | Output Low Voltage                 | I <sub>OUT</sub> = 0.3mA                                                                          |                 | 175             | 300             | mV    |

|                     | Short Circuit Current              |                                                                                                   |                 | 1               |                 | mA    |

| SWITCHING           | SPECIFICATIONS                     |                                                                                                   | *               | -               |                 |       |

|                     | Low-to-High Propagation Delay Time | Input overdrive = 100mV                                                                           |                 |                 | 0.4             | μs    |

|                     | High-to-low Propagation Delay Time | Input overdrive = 100mV                                                                           |                 |                 | 0.2             | μs    |

|                     | Rise Time                          | C <sub>L</sub> = 10pF                                                                             |                 | 100             |                 | ns    |

|                     | Fall Time                          | C <sub>L</sub> = 10pF                                                                             |                 | 100             |                 | ns    |

| LATCHRPT            | (OPEN DRAIN OUTPUT)                |                                                                                                   |                 | 1               |                 | 1     |

|                     | LATCHRPT One-Shot Pulse Width      | Under pulse by pulse OC condition,<br>LATCHRPT pulled low for one-shot<br>period of each OC cycle |                 | 1               |                 | μs    |

|                     | LATCHRPT Leakage Current           | V <sub>PULLUP</sub> = 3.3V                                                                        |                 |                 | 1               | μA    |

|                     | LATCHRPT Voltage Low               | I <sub>LATCHRPT</sub> = 4mA                                                                       |                 |                 | 0.5             | V     |

#### Preload Electrical Specifications $T_A = +25 \,^{\circ}$ C, VR1 = 10V, VR2 = 3.3V. Boldface limits apply over the operating temperature range, -40°C to +85°C.

| SYMBOL              | PARAMETER                 | TEST CONDITIONS                                    | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |

|---------------------|---------------------------|----------------------------------------------------|-----------------|-----------------|-----------------|-------|

| POWER MO            | OSFET                     |                                                    | '               |                 |                 | ı     |

| r <sub>DS(ON)</sub> | Switch 1 ON ON-Resistance | Pull up to VCC1 = 10V through $100\Omega$ resistor |                 | 350             |                 | Ω     |

| r <sub>DS(ON)</sub> | Switch 2 ON ON-Resistance | Pull up to VCC1 = 10V through $100\Omega$ resistor |                 | 120             |                 | Ω     |

| r <sub>DS(ON)</sub> | Switch 3 ON ON-Resistance | Pull up to VCC1 = 10V through $100\Omega$ resistor |                 | 50              |                 | Ω     |

| r <sub>DS(ON)</sub> | Switch 4 ON ON-Resistance | Pull up to VCC1 = 10V through $100\Omega$ resistor |                 | 12              |                 | Ω     |

#### NOTES:

- 6. Compliance to datasheet values is assured by one or more methods: production test, characterization and/or design.

- 7. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

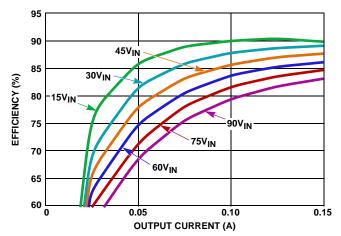

## **Typical Performance Curves**

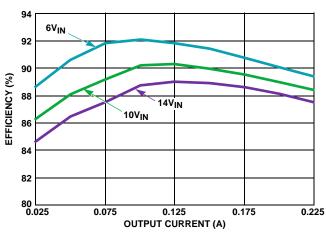

FIGURE 3. VR1 EFFICIENCY vs LOAD CURRENT WITH V<sub>OUT1</sub> = 10V @ F<sub>SW1</sub> = 170kHz

FIGURE 4. VR2 EFFICIENCY vs LOAD CURRENT WITH  $V_{OUT2} = 2.5V @ F_{SW2} = 210kHz$

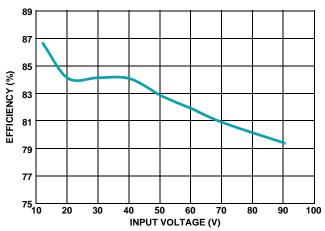

FIGURE 5. VR1 + VR2 EFFICIENCY vs INPUT VOLTAGE WITH  $V_{OUT1} = 10V, I_{OUT1} = 100 \text{mA} \circledast F_{SW1} = 170 \text{kHz}, \\ V_{OUT2} = 2.5V, I_{OUT2} = 200 \text{mA}, F_{SW2} = 210 \text{kHz}$

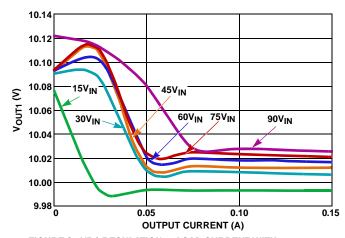

FIGURE 6. VR1 REGULATION vs LOAD CURRENT WITH  $\rm V_{OUT1}$  = 10V @  $\rm F_{SW1}$  = 170kHz

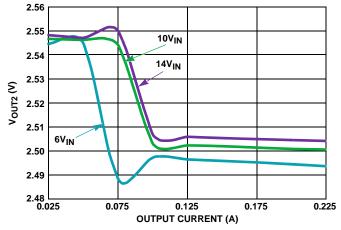

FIGURE 7. VR2 REGULATION vs LOAD CURRENT WITH  $V_{OUT2} = 2.5 V \ @ \ F_{SW2} = 210 \text{kHz}$

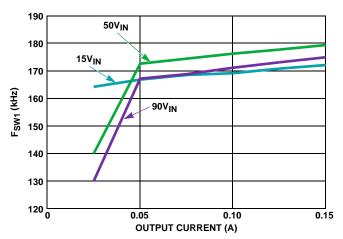

FIGURE 8. VR1 SWITCHING FREQUENCY vs LOAD CURRENT WITH  $V_{OUT1} = 10V$

## Typical Performance Curves (Continued)

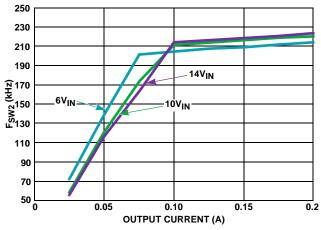

FIGURE 9. VR2 SWITCHING FREQUENCY vs LOAD CURRENT WITH  $V_{OUT2} = 2.5V$

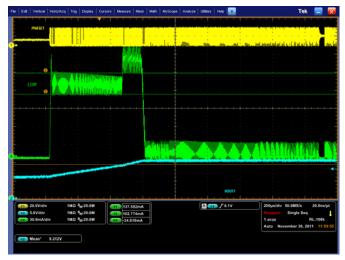

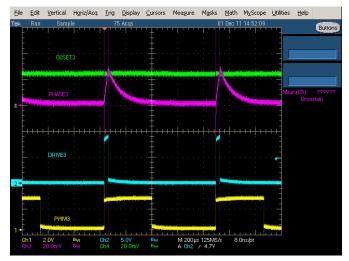

## **Test Waveforms**

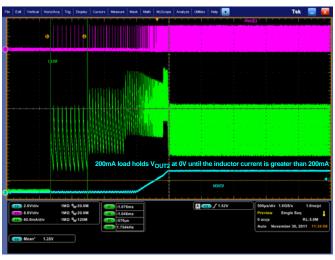

FIGURE 10. VR1 SOFT-START (FROM TOP TO BOTTOM: PHASE1, I\_L1,  $V_{OUT1}$ )

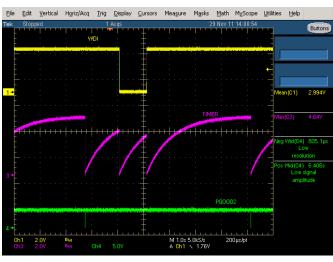

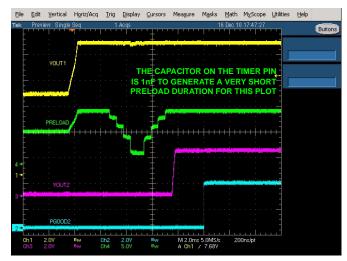

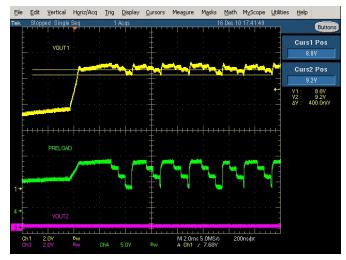

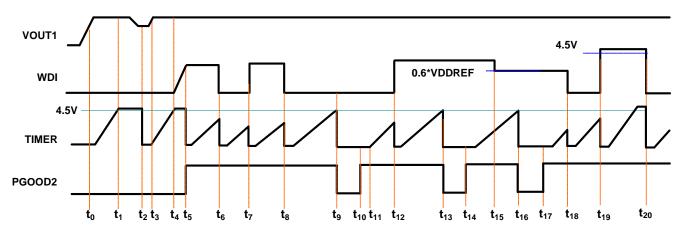

FIGURE 12. WATCH-DOG OPERATION

FIGURE 11. VR2 SOFT-START WITH 200mA LOAD (FROM TOP TO BOTTOM: PHASE2, I\_L2,  $V_{OUT2}$ )

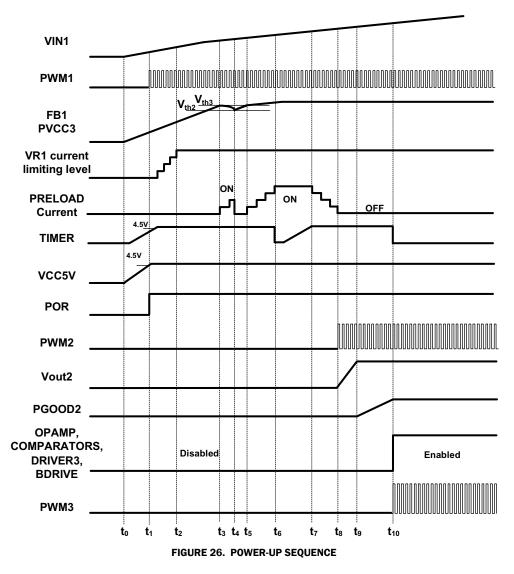

FIGURE 13. NORMAL POWER-UP SEQUENCE

## Test Waveforms (Continued)

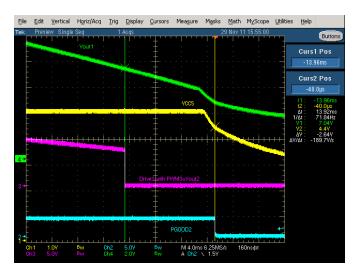

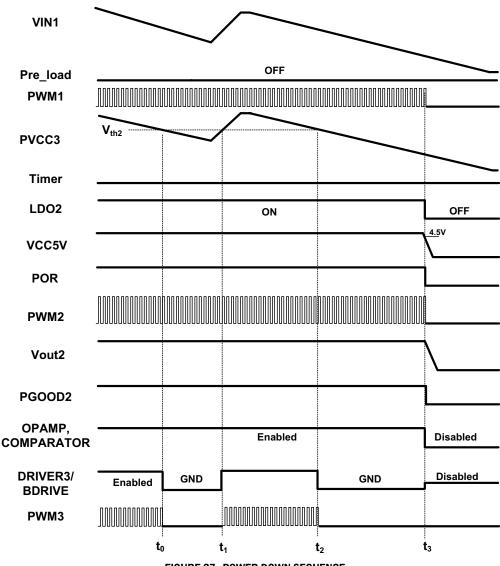

FIGURE 15. NORMAL POWER-DOWN SEQUENCE

FIGURE 16. OCSET3 THRESHOLD CROSSING TRIGGERS OCP

## **Summary of Operation**

The ISL1801 is a versatile Solar Power Management IC (sPMIC). It has two switching regulators, two LDOs, two general purpose comparators, two power MOSFET drivers, a current sense OPAMP and other logic functions. Figure 17 shows the main blocks in the ISL1801.

The high voltage LDO1 can be directly connected to a high voltage input power source up to 90V. Its output can be used to start up the high voltage switching regulator VR1. Once VR1's output is greater than 6.7V, LDO1 is disabled to save power. The second low voltage regulator, LDO2, can be connected to the output of VR1 to generate the 5V supply required for the internal control circuits including those that operate VR1 and VR2.

The first switching regulator, VR1, can be directly connected to an input voltage up to 90V. VR1 provides a regulated voltage for the second switching regulator, VR2, and the two integrated MOSFET drivers. The low voltage switching regulator, VR2, can be used to generate the regulated voltage for an MCU or other external circuitry. The PGOOD2 signal is used to indicate that VR2 output voltage is within the regulation window. The output voltage of both VR1 and VR2 can be set through resistor dividers at the FB1 and FB2 pins respectively. The switching frequencies of VR1 and VR2 are determined by the resistors at the TON1 and TON2 pins respectively.

There are two low-side drivers for the external power MOSFETs. Both drivers are powered by the PVCC3 pin, which is normally connected to the output of VR1.

The integrated amplifier has low offset and drift so the MCU can accurately sense the amplified module current.

Overcurrent and overvoltage conditions can be monitored by the two general purpose high speed comparators. Any detected fault condition can be used to trigger an MCU interrupt.

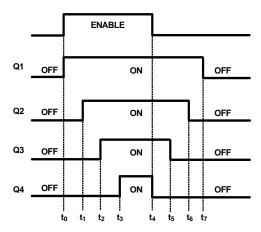

The preload function is specially designed for solar applications. It applies a resistive load to the input power source to verify that it is sufficient for device operation. VR2, the MCU supply, will not be enabled until the input power source has enough power. This function can significantly reduce the power cycling of the MCU at system start-up and shutdown.

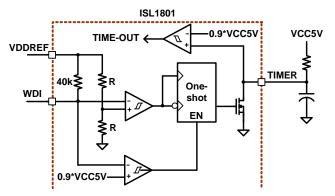

The ISL1801 also includes a watch-dog circuit to prevent the software in the MCU from hanging in an unknown state. The MCU can use the watch-dog input (WDI) pin to periodically restart the timer. The watch-dog time out is set by a resistor to VCC5V and a capacitor to ground, both connected to the TIMER pin. If the RC timer expires before an MCU reset on the WDI pin the PGOOD2 pin will be pulled low to reset the MCU.

FIGURE 17. ISL1801 SIMPLIFIED BLOCK DIAGRAM

## **Detailed Operation**

# **Dual Synchronous Buck Switching Regulators With Constant On-Time Control**

There are two synchronous Buck switching regulators in the ISL1801. The high voltage switching regulator, VR1, can be connected to a power source up to 90V. The low voltage switching regulator, VR2, supports input voltages up to 14V. Typically, VR2 is connected to the output of VR1. Both switching regulators include integrated MOSFETs.

Both VR1 and VR2 employ a constant on-time PWM control architecture with input voltage feed-forward. The constant on-time PWM control architecture relies on the output ripple voltage to provide the PWM ramp signal; thus the output filter capacitor's ESR acts as a current-feedback resistor. For some applications with ceramic capacitors, the output voltage ripple is small due to very low ESR. In order to achieve the stable operation for very low voltage ripple applications, one internal ramp is generated and add to the FB signal to emulate the output voltage ripple. The high-side switch ON time is determined by a one-shot whose period is inversely proportional to input voltage and directly proportional to output voltage. Another oneshot sets a minimum OFF time (300ns typical for VR1 and 150ns typical for VR2). The ON time one-shot triggers when the following conditions are met: the error comparator's output is high, the synchronous rectifier current is below the current-limit threshold, and the minimum OFF time one-shot has timed out. The controller utilizes the valley point of the output ripple to regulate and determine the OFF time.

#### **SWITCHING FREQUENCY OF VR1 AND VR2**

Each PWM core includes a one-shot that sets the ON time for the high-side switch of each voltage regulator. Each fast, low-jitter, adjustable one-shot includes circuitry that varies the ON time in response to the input voltage and output voltage. This algorithm results in a nearly constant switching frequency despite the lack of a fixed-frequency clock generator.

The high-side switch ON time is inversely proportional to the input voltage as measured by the TON1 and TON2 pins for VR1 and VR2 respectively. Both TON1 and TON2 pins are tied to an internal voltage reference and the current flowing into these pins is monitored to generate the ON time one shot.

For high voltage VR1 the TON1 pin is tied to an internal 1V reference and the width of the ON-time one shot is:

$$t_{ON1} = \frac{2.7e^{-11} \cdot R_{ON1}}{V_{IN1} - 1}$$

(EQ. 1)

$V_{IN1}$  is the input voltage for high voltage VR1, while  $R_{ON1}$  is the resistor from  $V_{IN1}$  to the TON1 pin.

The switching frequency of VR1 is:

$$F_{SW1} = \frac{V_{OUT1} \cdot (V_{IN1} - 1)}{2.7e^{-11} \cdot R_{ON1} \cdot V_{IN1}}$$

(EQ. 2)

When  $V_{IN1}$  is much larger than 1V, the switching frequency of VR1 is almost independent of its input voltage:

$$F_{SW1} \approx \frac{V_{OUT1}}{2.7e^{-11} \cdot R_{ON1}}$$

(EQ. 3)

For a 10V output the switching frequency of VR1 is about 370kHz with  $R_{ON1}$  = 1M $\Omega$ .

For low voltage VR2, the TON2 pin is tied to an internal 0.5V reference and the width of the ON-time one shot is:

$$t_{ON2} = \frac{1.05e^{-11} \cdot R_{ON2}}{V_{IN2} - 0.5} \tag{EQ. 4}$$

$V_{IN2}$  is the input voltage for VR2, while  $R_{ON2}$  is the resistor from  $V_{IN2}$  to the TON2 pin.

The switching frequency of VR2 is:

$$F_{SW2} = \frac{V_{OUT2} \cdot (V_{IN2} - 0.5)}{1.05e^{-11} \cdot R_{ON2} \cdot V_{IN2}}$$

(EQ. 5)

When  $V_{IN2}$  is much larger than 0.5V, the switching frequency of VR2 is almost independent of its input voltage:

$$F_{SW2} \approx \frac{V_{OUT2}}{1.05e^{-11} \cdot R_{ON2}}$$

(EQ. 6)

For a 3.3V output the switching frequency of VR2 is about 314kHz with  $R_{ON2}$  = 1M $\Omega$ .

#### **CURRENT LIMITING OF VR1 AND VR2**

To prevent the output current from becoming too high a new ON-time pulse can start only when the current through the synchronous MOSFET is below the current limiting threshold. This limits the valley of the output inductor current to a fixed value, typically 140mA for VR1 and 200mA for VR2.

The maximum peak current through the output inductor is the sum of the current limiting threshold and the current ripple determined by the ON-time, inductor value and the input/output voltage.

#### **DIODE EMULATION OPERATION**

To improve the efficiency for light loads, the synchronous MOSFET is turned off when its current drops to 0. This prevents negative current through the output inductor emulating diode operation.

With diode emulation operation under light load conditions the output voltage may drop slowly after the synchronous MOSFET turns OFF. It may take a long time for the output voltage to drop below the reference voltage to start a new switching cycle. This will have the effect of reducing the switching frequency under light load conditions.

#### **OVERVOLTAGE PROTECTION**

The feedback voltage for VR1 and VR2 is continuously monitored to prevent the output voltage from going too high.

When the VR1 output voltage feedback FB1 is higher than 120% of VREF1, the Overvoltage Protection (OVP) is triggered. When this condition occurs, the lower side MOSFET of VR1 is turned on

immediately. At the same time, the PRELOAD current will be applied to VOUT1 to discharge the output. When the current through the lower side MOSFET drops to 0, turn off this MOSFET to prevent the negative inductor current. the OVP is reset when FB1 voltage drops to VREF1.

For low voltage VR2, OVP is triggered when the FB2 voltage is above 0.775V. When this condition occurs the lower synchronous MOSFET of VR2 is turned on immediately. It is held on until the FB2 voltage drops below 0.73V.

#### **POWER-GOOD SIGNAL (PGOOD2)**