# 5:1 Intermediate Bus Converter Module: Up to 500 W Output

# **Applications**

- Enterprise networks

- Optical access networks

- Storage networks

- Automated test equipment

#### **Features**

• Input: 38 – 55 Vdc

• Output: 9.6 Vdc at 48 Vin

• Output current up to 48 A

• Output power: up to 500 W [A]

• 1,500 Vdc isolation

98% peak efficiency

• Low profile: 0.38" height above board

• Industry standard 1/8 Brick pinout

• Sine Amplitude Converter

Low noise 1 MHz ZVS/ZCS

[A] For lower power applications see 300 W model IB048E096T40N1-00

#### **Product Overview**

The Intermediate Bus Converter (IBC) Module is a very efficient, low profile, isolated, fixed ratio converter for power system applications in enterprise and optical access networks.

Rated at up to 360 W from 38 Vin and up to 500 W from 54 to 55 Vin, the IBC conforms to an industry standard eighth brick footprint while supplying the power of a quarter brick. Its leading efficiency enables full load operation at 55°C with only 200 LFM airflow. Its small cross section facilitates unimpeded airflow — above and below its thin body — to minimize the temperature rise of downstream components.

| Absolute Maximum Ratio                    | ngs   |      |               |                       |

|-------------------------------------------|-------|------|---------------|-----------------------|

|                                           | Min   | Max  | Unit          | Notes                 |

| Input voltage (+In to –In)                |       |      |               |                       |

| Operating                                 | 36    | 60   | Vdc           |                       |

| Non-operating                             |       | 75   | Vdc           | <100 mS               |

| Input voltage slew rate                   |       | 5    | V/ <b>µ</b> s |                       |

| EN to -IN                                 | -0.5  | 20   | Vdc           |                       |

| Output voltage (+Out to –Out)             | -0.5  | 13.8 | Vdc           |                       |

| Output current                            |       | 48   | А             | Pout ≤ 500 W          |

| Dielectric withstand<br>(input to output) | 1,500 |      | Vdc           | 1 min.                |

| Temperature                               |       |      |               |                       |

| Operating junction                        | -40   | 125  | °C            | Hottest Semiconductor |

| Storage                                   | -55   | 125  | °C            |                       |

# **SPECIFICATIONS**

All specifications valid at 48  $V_{IN}$ , 100% rated load and 25°C ambient, unless otherwise indicated.

| Attribute                                                             | Symbol | Conditions / Notes                                                                       | Min   | Тур   | Max    | Unit  |

|-----------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------|-------|-------|--------|-------|

|                                                                       |        |                                                                                          |       |       |        |       |

| INPUT (Operating from DC input source)                                |        |                                                                                          |       |       |        |       |

| Operating input voltage                                               |        |                                                                                          | 38    | 48    | 55     | Vdc   |

| Non-operating input surge withstand                                   |        | <100 mS                                                                                  |       |       | 75     | Vdc   |

| Operating input dV/dt                                                 |        |                                                                                          | 0.003 |       | 5      | V/us  |

| Undervoltage protection                                               |        |                                                                                          |       |       |        |       |

| Turn-on                                                               |        |                                                                                          | 31    |       | 36     | Vdc   |

| Turn-off                                                              |        |                                                                                          | 29    |       | 34     | Vdc   |

| Turn-on/Turn-off hysteresis                                           |        |                                                                                          | 2     |       |        | Vdc   |

| Time constant                                                         |        |                                                                                          |       |       | 7      | μs    |

| Undervoltage blanking time UV blanking time is enabled after start up |        | 50                                                                                       | 100   | 200   | μs     |       |

| Overvoltage protection                                                |        |                                                                                          |       |       |        |       |

| Turn-off                                                              |        |                                                                                          | 60    |       | 64     | Vdc   |

| Turn-on                                                               |        |                                                                                          | 55    |       | 64     | Vdc   |

| Time constant                                                         |        |                                                                                          |       |       | 4      | μs    |

| Turn ON delay                                                         |        |                                                                                          |       |       |        |       |

| Start up inhibit                                                      |        | V <sub>IN</sub> reaching turn-on voltage<br>to enable function operational, see Figure 6 | 20    | 25    | 30     | ms    |

| Turn-on delay                                                         |        | Enable to 90% $V_{OUT}$ ; pre-applied $V_{IN}$ , see Figure 7, 0 load capacitance        |       |       | 50     | μs    |

| Output voltage rise time                                              |        | From 10% to 90% Vout, 10% load,<br>0 load capacitance.                                   |       |       | 50     | μs    |

| Restart turn-on delay                                                 |        | See page 10 for resart after EN pin disable                                              |       |       | 250    | ms    |

| No Load power dissipation                                             |        | page 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1                                               |       |       |        |       |

| Enabled                                                               |        |                                                                                          |       | 1.9   | 2.5    | W     |

| Disabled                                                              |        |                                                                                          |       | 0.18  | 0.21   | W     |

| Input current                                                         |        | Low line, full load                                                                      |       |       | 9.8    | А     |

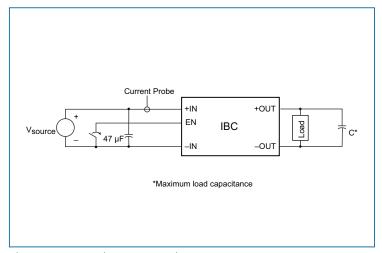

| Inrush current overshoot                                              |        | Using test circuit in Figure 21                                                          |       |       | 9.8    | Α     |

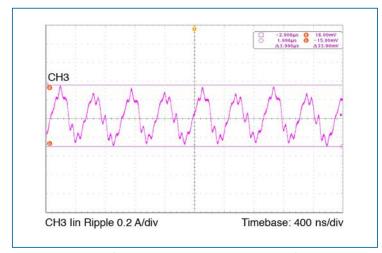

| Input reflected ripple current                                        |        | At max power; Using test circuit in Figure 22                                            |       |       | 500    | mArms |

| Peak short circuit input current                                      |        | osing test enear in rigare 22                                                            |       |       | 40     | А     |

| Repetitive short circuit peak current                                 |        |                                                                                          |       |       | 25     | A     |

| Internal input capacitance                                            |        |                                                                                          |       | 8.8   | 23     | μF    |

| Internal input inductance                                             |        |                                                                                          |       | 5     |        | nH    |

| Recommended external                                                  |        |                                                                                          |       |       |        |       |

| input capacitance                                                     |        | 200 nH maximum source inductance                                                         | 47    |       | 470    | μF    |

| OUTPUT                                                                |        |                                                                                          |       |       |        |       |

| DC Output voltage band                                                |        | No load, over Vin range                                                                  | 7.6   | 9.6   | 11.0   | V     |

| Output power [a]                                                      |        |                                                                                          |       |       |        |       |

| 38-55 V <sub>IN</sub>                                                 |        |                                                                                          | 0     |       | 360    | W     |

| 48-55 V <sub>IN</sub>                                                 |        |                                                                                          | 0     |       | 450    | W     |

| 54-55 V <sub>IN</sub>                                                 |        |                                                                                          | 0     |       | 500    | W     |

| Output current                                                        |        | P ≤ 500 W                                                                                |       |       | 48     | А     |

| Output start up load                                                  |        | of lout max, maximum output capacitance                                                  |       |       | 15     | %     |

| Effective output resistance                                           |        |                                                                                          |       | 4.2   |        | mΩ    |

| Line regulation (K factor)                                            |        | V <sub>OUT</sub> = K • V <sub>IN</sub> @ no load                                         | 0.198 | 0.200 | 0.2020 |       |

Does not exceed IPC-9592 derating guidelines. At 70°C ambient, full power operation may exceed IPC-9592 guidelines, but does not exceed component ratings, does not activate OTP and does not compromise reliability.

All specifications valid at 48  $V_{\rm IN}$ , 100% rated load and 25°C ambient, unless otherwise indicated.

| Attribute                             | Symbol | Conditions / Notes                                                                                        | Min  | Тур  | Max  | Unit  |

|---------------------------------------|--------|-----------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                                       | -      |                                                                                                           |      |      |      |       |

| OUTPUT (Continued)                    |        |                                                                                                           |      |      |      |       |

| Current share accuracy                |        | Full power operation; See Parallel Operation on page 11; up to 3 units                                    |      |      | 10   | %     |

| Efficiency                            |        |                                                                                                           |      |      |      |       |

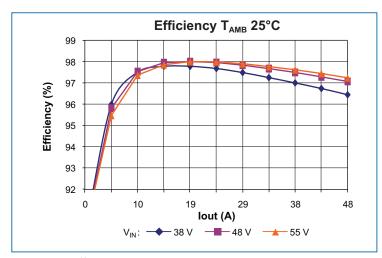

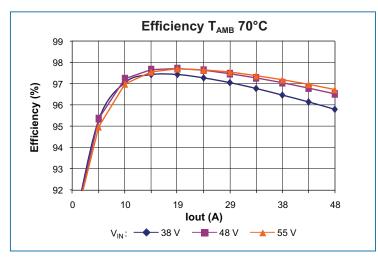

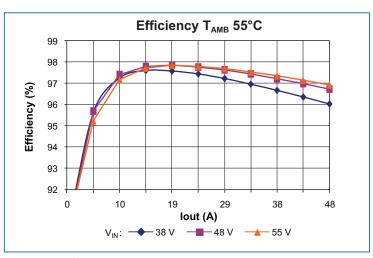

| 50% load                              |        | See Figure 1,2 and 3                                                                                      | 97.5 | 98.0 |      | %     |

| Full load                             |        | See Figure 1,2 and 3                                                                                      | 96.9 | 97.1 |      | %     |

| Internal output inductance            |        |                                                                                                           |      | 1.6  |      | nH    |

| Internal output capacitance           |        |                                                                                                           |      | 55   |      | μF    |

| Load capacitance                      |        | Nominal load                                                                                              | 0    |      | 4500 | μF    |

| Output OVP set point                  |        | Module will shutdown                                                                                      | 12.0 |      | 12.8 | Vdc   |

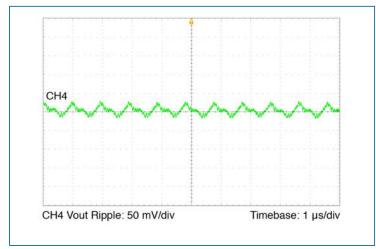

| Output voltage ripple                 |        | 20 MHz bandwidth, using test circuit in Figure 23                                                         |      | 60   | 150  | mVp-p |

| Output Overload protection threshold  |        | Of lout max., will not shutdown when started into max Cout and 15% load Auto restart with duty cycle <10% | 105  |      | 150  | %     |

| Over current protection time constant |        |                                                                                                           |      |      | 5    | ms    |

| Short circuit current response time   |        |                                                                                                           |      |      | 1.5  | μs    |

| Switching frequency                   |        |                                                                                                           |      | 1.0  |      | MHz   |

| Transient Response                    |        |                                                                                                           |      |      |      |       |

| Voltage overshoot                     |        | 25% load step; See Figures 11 - 14<br>using test set up in Figure 24                                      |      |      | 100  | mV    |

| Response time                         |        | See Figures 11 - 14 using test set up in Figure 24                                                        |      | 1    |      | μs    |

| V <sub>IN</sub> step                  |        | 5 V step in 1 μs within Vin operating range                                                               |      |      | 1.25 | V     |

| Pre-bias voltage                      |        | Unit will start up into pre-bias voltage on output                                                        | 0    |      | 12   | Vdc   |

| Attribute                    | Symbol | Conditions / Notes                                                               |       | Тур         | Max    | Unit   |

|------------------------------|--------|----------------------------------------------------------------------------------|-------|-------------|--------|--------|

|                              | , ,    |                                                                                  |       | 71          |        |        |

| MTBF                         |        | Calculated per Telcordia SR-332, 40°C                                            | 1.0   |             |        | Mhrs   |

| Service life                 |        | Calculated at 30°C                                                               | 7     |             |        | Years  |

| Over temperature shut down   |        | T <sub>J</sub> ; Converter will reset when over temperature condition is removed | 125   | 130         | 135    | °C     |

| Dielectric withstand         |        | Input to output                                                                  | 1,500 |             |        | Vdc    |

| Insulation resistance        |        | Input to output                                                                  |       | 30          |        | ΜΩ     |

| Mechanical                   |        |                                                                                  |       |             |        |        |

| Weight                       |        |                                                                                  |       | 0.71 / 20.3 |        | oz/g   |

| Length                       |        |                                                                                  |       | 2.30/58.4   |        | in/mm  |

| Width                        |        |                                                                                  |       | 0.9/22.9    |        | in/mm  |

| Height above customer board  |        |                                                                                  |       | 0.38/9.5    |        | in/mm  |

| Pin Solderability            |        | Storage life for normal solderability                                            |       |             | 1      | Years  |

| Moisture Sensitivity Level   | MSL    | Not applicable, for wave soldering only                                          | N/A   |             |        |        |

| Clearance to customer board  |        | From lowest component on IBC                                                     |       | 0.12/3.0    |        | in/mm  |

| Agency approvals             |        | UL/cUL 60950-1, EN 60950-1, IEC 60950-1                                          |       |             |        | cTUVus |

| Agency approvais             |        | Low voltage directive (CE Mark)                                                  |       |             |        | CE     |

| Altitude, operating          |        | Derate operating temp 1°C per 1,000 feet above sea level                         | -500  |             | 10,000 | Feet   |

| Relative humidity, Operating |        | Non condensing                                                                   | 10    |             | 90     | %      |

| RoHS compliance              |        | Compatible with RoHS directive 2002/95/EC                                        |       |             |        |        |

| Attribute                       | Symbol | Conditions / Notes                            | Min | Тур | Max  | Unit |

|---------------------------------|--------|-----------------------------------------------|-----|-----|------|------|

|                                 |        |                                               |     |     |      |      |

| Enable (negative logic)*        |        | Referenced to –IN                             |     |     |      |      |

| Module enable threshold         |        |                                               | 8.0 |     |      | Vdc  |

| Module enable current           |        | $V_{EN} = 0.8 \text{ V}$                      |     | 130 | 200  | μΑ   |

| Module disable threshold        |        |                                               |     |     | 2.4  | Vdc  |

| Module disable current          |        | V <sub>EN</sub> = 2.4 V                       |     |     | 10   | μΑ   |

| Disable hysteresis              |        |                                               |     | 500 |      | mV   |

| Enable pin open circuit voltage |        |                                               |     | 2.5 | 3.0  | Vdc  |

| EN to -IN resistance            |        | Open circuit, 10 V applied between EN and -IN |     | 35  |      | kΩ   |

| Enable (positive logic)*        |        | Referenced to –IN                             |     |     |      |      |

| Module enable threshold         |        |                                               | 2.0 | 2.5 | 3.0  | Vdc  |

| Module disable threshold        |        |                                               |     |     | 1.45 | Vdc  |

| EN source current (operating)   |        | $V_{EN} = 5 \text{ V}$                        |     |     | 2    | mA   |

| EN voltage (operating)          |        |                                               | 4.7 | 5   | 5.3  | Vdc  |

<sup>\*</sup>See part numbering on page 11

IPC-9592A, Based on Class II Category 2 the following detail is applicable. – Pre-conditioning required

| <b>Environmental Qualification</b>           |                                                                                                                                                                                                   |                 |  |  |  |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Test Description                             | Test Detail                                                                                                                                                                                       | Quantity Tested |  |  |  |  |

|                                              | Low Temp                                                                                                                                                                                          | 3               |  |  |  |  |

|                                              | High Temp                                                                                                                                                                                         | 3               |  |  |  |  |

|                                              | Rapid Thermal Cycling                                                                                                                                                                             | 3               |  |  |  |  |

| 5.2.3 HALT (Highly Accelerated Life testing) | 6 DOF Random Vibration Test                                                                                                                                                                       | 3               |  |  |  |  |

|                                              | Input Voltage Test                                                                                                                                                                                | 3               |  |  |  |  |

|                                              | Output Load Test                                                                                                                                                                                  | 3               |  |  |  |  |

|                                              | Combined Stresses Test                                                                                                                                                                            | 3               |  |  |  |  |

| 5.2.4 THB (Temp. Humidity Bias)              | (72 hr presoak required) 1000 hrs – Continuous Bias                                                                                                                                               | 30              |  |  |  |  |

| 5.2.5 HTOB (High Temp. Operating Bias)       | Power cycle - On 42 minutes Off 1 minute, On 1 minute, Off 1 minute, Off 1 minute, On 1 minute, Off 1 minute, On 1 minutes. Alternating between maximum and minimum operating Voltage every hour. | 30              |  |  |  |  |

| 5.2.6 TC (Temp. Cycling)                     | 700 cycles , 30 minute dwell at each extreme – 20C minimum ramp rate.                                                                                                                             | 30              |  |  |  |  |

| 5.2.7 Power Cycling                          | Reference IPC-9592A                                                                                                                                                                               | 3               |  |  |  |  |

|                                              | Random Vibration – Operating IEC 60068-2-64 (normal operation vibration)                                                                                                                          | 3               |  |  |  |  |

|                                              | Random Vibration Non-operating (transportation) IEC 60068-2-64                                                                                                                                    | 3               |  |  |  |  |

| 5.2.8 – 5.2.13 Shock and Vibration           | Shock Operating - normal operation shock IEC 60068-2-27                                                                                                                                           | 3               |  |  |  |  |

|                                              | Free fall - IEC 60068-2-32                                                                                                                                                                        | 3               |  |  |  |  |

|                                              | Drop Test 1 full shipping container (box)                                                                                                                                                         | 12              |  |  |  |  |

|                                              | 5.2.14.1 Corrosion Resistance – Not required                                                                                                                                                      | N/A             |  |  |  |  |

|                                              | 5.2.14.2 Dust Resistance – Unpotted class II GR-1274-CORE                                                                                                                                         | 3               |  |  |  |  |

| 5.2.14 Other Environmental Tests             | 5.2.14.3 SMT Attachment Reliability IPC-9701 - J-STD-002                                                                                                                                          | 3               |  |  |  |  |

|                                              | 5.2.14.4 Through Hole solderability – J-STD-002                                                                                                                                                   | 5               |  |  |  |  |

| ESD Classification Testing                   | Sample size assumes CDM testing                                                                                                                                                                   | 12              |  |  |  |  |

| Total Quantity                               |                                                                                                                                                                                                   | 161             |  |  |  |  |

#### **WAVEFORMS**

Figure 1 — Efficiency vs. output current, 25°C ambient

Figure 3 — Efficiency vs. output current, 70°C ambient

Figure 5 — Input reflected ripple current at nominal line, full load

Figure 2 — Efficiency vs. output current, 55°C ambient

Figure 4 — Inrush current at high line 15% load

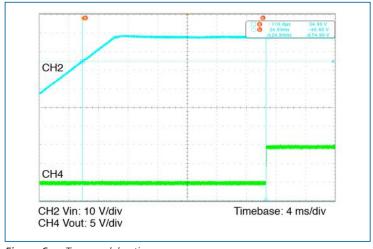

Figure 6 — Turn on delay time;  $V_{IN}$  turn on delay at nominal line, 15% load; start up inhibit time

#### **WAVEFORMS (CONT.)**

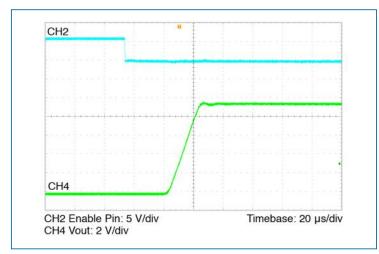

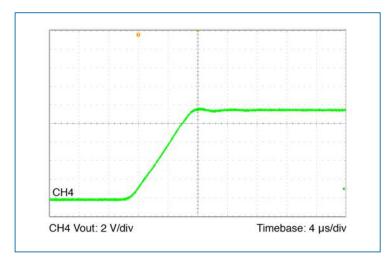

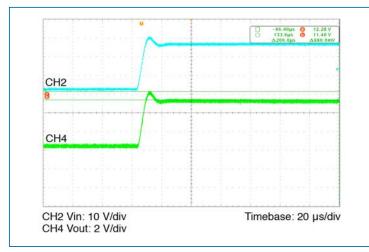

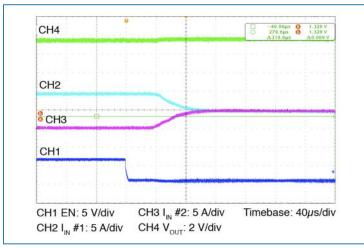

Figure 7 — Turn on delay time; Enable turn on delay at nominal line, 15% load

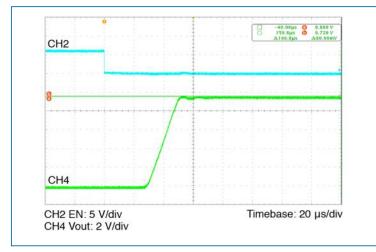

Figure 9 — Overshoot at turn on at nominal line, 15% load

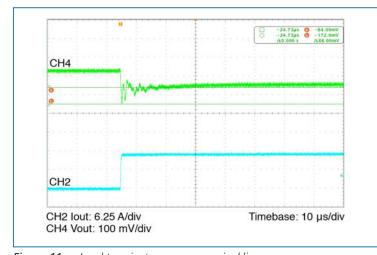

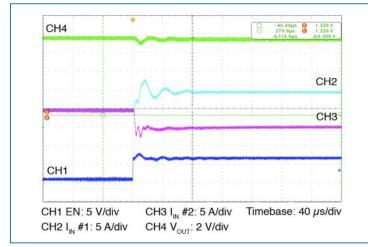

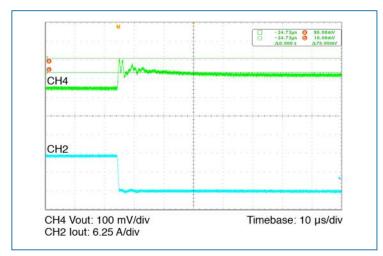

Figure 11 — Load transient response; nominal line Load step 75–100%

Figure 8 — Output voltage rise time at nominal line, 10% load

Figure 10 — Undershoot at turn off at nominal line, 15% load

Figure 12 — Load transient response; Full load to 75%; nominal line

#### **WAVEFORMS (CONT.)**

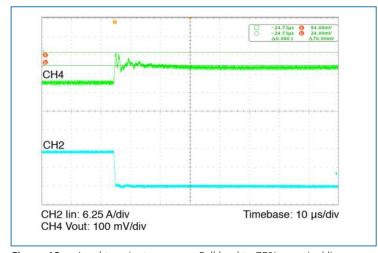

Figure 13 — Load transient response; nominal line Load step 0-25%

Figure 15 — Input transient response; Vin step low line to high line at full load

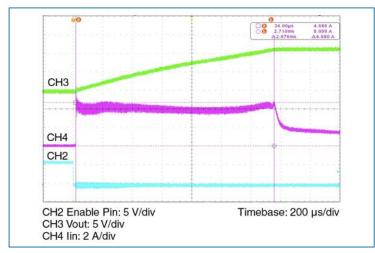

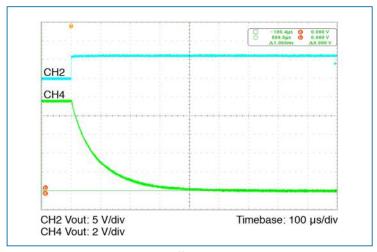

Figure 17 — Two modules parallel array test. Vout and lin change when one module is disabled. Nominal Vin, lout = 48A

Figure 14 — Load transient response; 25–0%; nominal line

Figure 16 — Output ripple; Nominal line, full load

Figure 18 — Two modules parallel array test. Vout and lin change when one module is enabled. Nominal Vin, lout = 48A

#### **SPECIFICATIONS**

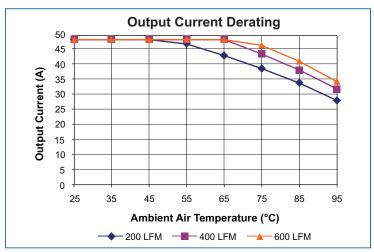

Figure 19 — Maximum output power derating vs ambient air temperature.

Transverse airflow, Board and junction temperatures <125°C

tested with IBC evaluation board IB048E096T48N1-CB

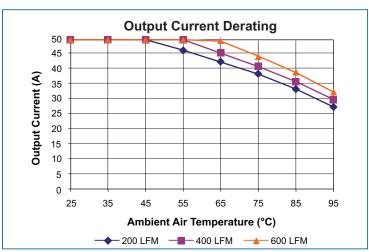

Figure 20 — Maximum output power derating vs ambient air temperature.

Longitudinal airflow, Board and junction temperatures <125°C tested with IBC evaluation board IB048E096T48N1-CB

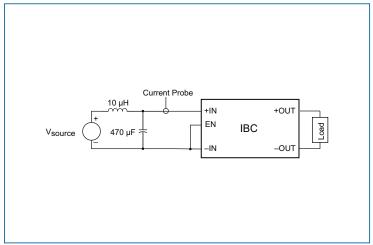

Figure 21 — Inrush current overshoot

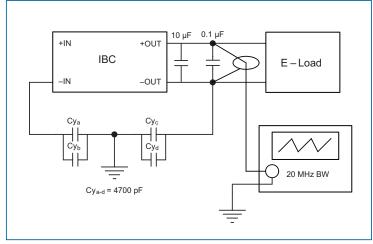

Figure 22 — Input reflected ripple current

Figure 23 — Test circuit; output voltage ripple

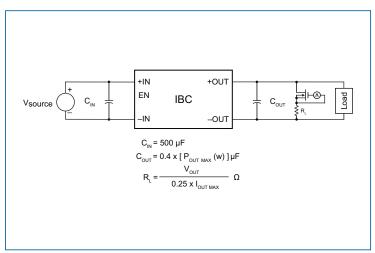

Figure 24 — Load transient response

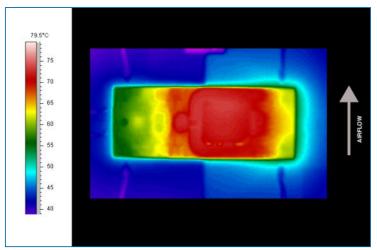

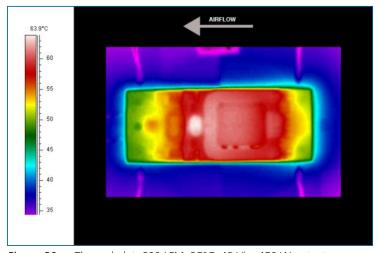

# THERMAL DATA

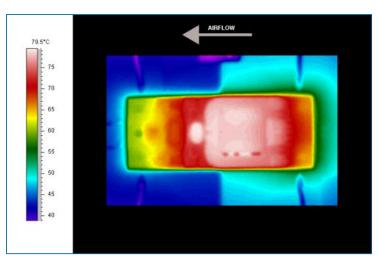

Figure 25 — Thermal plot, 200 LFM, 25°C, 48 Vin, 450 W output power

Figure 26 — Thermal plot, 200 LFM, 25°C, 48 Vin, 450 W output power

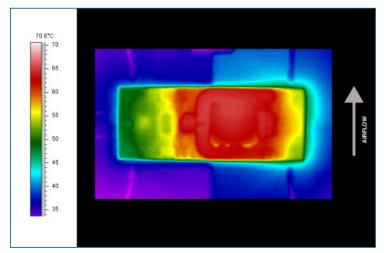

Figure 27 — Thermal plot, 400 LFM, 25°C, 48 Vin, 450 W output power

Figure 28 — Thermal plot, 400 LFM, 25°C, 48 Vin, 450 W output power

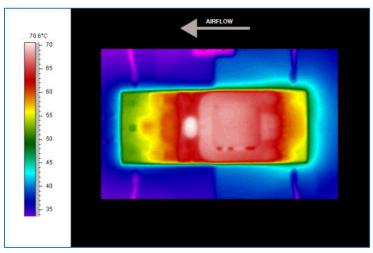

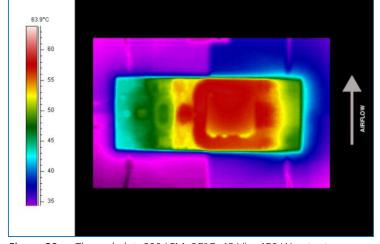

Figure 29 — Thermal plot, 600 LFM, 25°C, 48 Vin, 450 W output power

Figure 30 — Thermal plot, 600 LFM, 25°C, 48 Vin, 450 W output power

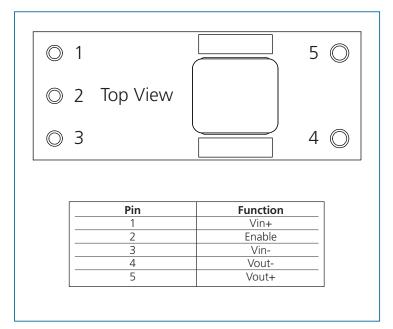

#### PIN / CONTROL FUNCTIONS

#### +In / -In – DC Voltage Input Pins

The IBC input voltage range should not be exceeded. An internal undervoltage/overvoltage lockout function prevents operation outside of the normal operating input range. The IBC turns on within an input voltage window bounded by the "Input under-voltage turn-on" and "Input over-voltage turn-off" levels, as specified. The IBC may be protected against accidental application of a reverse input voltage by the addition of a rectifier in series with the positive input, or a reverse rectifier in shunt with the positive input located on the load side of the input fuse.

The connection of the IBC to its power source should be implemented with minimal distribution inductance. If the interconnect inductance exceeds 100 nH, the input should be bypassed with a RC damper to retain low source impedance and stable operation. With an interconnect inductance of 200 nH, the RC damper may be 47  $\mu F$  in series with 0.3  $\Omega.$  A single electrolytic or equivalent low-Q capacitor may be used in place of the series RC bypass.

#### **EN - Enable/Disable**

### **Negative Logic Option**

If the EN port is left floating, the IBC output is disabled. Once this port ispulled lower than 0.8 Vdc with respect to –In, the output is enabled. The EN port can be driven by a relay, opto-coupler, or open collector transistor. Refer to Figures 6 and 7 for the typical enable / disable characteristics. This port should not be toggled at a rate higher than 1 Hz. The EN port should also not be driven by or pulled up to an external voltage source.

#### **Positive Logic Option**

If the EN port is left floating, the IBC output is enabled. Once this port is pulled lower than 1.4 Vdc with respect to –In, the output is disabled. This action can be realized by employing a relay, opto-coupler, or open collector transistor. This port should not be toggled at a rate higher than 1 Hz.

The EN port should also not be driven by or pulled up to an external voltage source. The EN port can source up to 2 mA at 5 Vdc. The EN port should never be used to sink current.

If the IBC is disabled using the EN pin, the module will attempt to restart approximately every 250ms. Once the module has been disabled for at least 250ms, the turn on delay after the EN pin is enabled will be as shown in Figure 7.

## +Out / -Out – DC Voltage Output Pins

Total load capacitance at the output of the IBC should not exceed the specified maximum. Owing to the wide bandwidth and low output impedance of the IBC, low frequency bypass capacitance and significant energy storage may be more densely and efficiently provided by adding capacitance at the input of the IBC.

Figure 31 — IBC Pin Designations

#### **APPLICATIONS NOTE**

#### **Parallel Operation**

The IBC will inherently current share when operated in an array. Arrays may be used for higher power or redundancy in an application. Current sharing accuracy is maximized when the source and load impedance presented to each IBC within an array are equal. The recommended method to achieve matched impedances is to dedicate common copper planes within the PCB to deliver and return the current to the array, rather than rely upon traces of varying lengths. In typical applications the current being delivered to the load is larger than that sourced from the input, allowing narrower traces to be utilized on the input side if necessary. The use of dedicated power planes is, however, preferable.

One or more IBCs in an array may be disabled without adversely affecting operation or reliability as long as the load does not exceed the rated power of the enabled IBCs

The IBC power train and control architecture allow bi-directional power transfer, including reverse power processing from the IBC output to its input. The IBC's ability to process power in reverse improves the IBC transient response to an output load dump.

#### Thermal Considerations

The temperature distribution of the VI Brick can vary significantly with its input/output operating conditions, thermal management and environmental conditions. Although the PCB is UL rated to 130°C, it is recommended that PCB temperatures be maintained at or below 125°C. For maximum long term reliability, lower PCB temperatures are recommended for continuous operation, however, short periods of operation at 125°C will not negatively impact performance or reliability.

WARNING: Thermal and voltage hazards. The IBC can operate with surface temperatures and operating voltages that may be hazardous to personnel. Ensure that adequate protection is in place to avoid inadvertent contact.

#### **Input Impedance Recommendations**

To take full advantage of the IBC capabilities, the impedance presented to its input terminals must be low from DC to approximately 5 MHz. The source should exhibit low inductance and should have a critically damped response. If the interconnect inductance is excessive, the IBC input pins should be bypassed with an RC damper (e.g., 47  $\mu F$  in series with 0.3  $\Omega$ ) to retain low source impedance and proper operation. Given the wide bandwidth of the IBC, the source response is generally the limiting factor in the overall system response.

Anomalies in the response of the source will appear at the output of the IBC multiplied by its K factor. The DC resistance of the source should be kept as low as possible to minimize voltage deviations. This is especially important if the IBC is operated near low or high line as the overvoltage/undervoltage detection circuitry could be activated.

#### **Input Fuse Recommendations**

The IBC is not internally fused in order to provide flexibility in configuring power systems. However, input line fusing of VI Bricks must always be incorporated within the power system. A fast acting fuse should be placed in series with the +In port. See safety agency approvals.

## **Application Notes**

For IBC and VI Brick application notes on soldering, thermal management, board layout, and system design visit vicorpower.com.

#### PART NUMBERING

| Product<br>Family | Input<br>Voltage | Package | Nominal<br>Output Voltage | Temperature<br>Grade | Output<br>Current | Enable<br>Logic | Pin<br>Length | Options          |

|-------------------|------------------|---------|---------------------------|----------------------|-------------------|-----------------|---------------|------------------|

| IB                | 048 = 38-55 Vdc  | Е       | 096                       | T                    | 48                | N = Negative    | 1 = 0.145     | -00 = Open frame |

|                   |                  |         |                           |                      |                   | P = Positive    | 2 = 0.210     |                  |

|                   |                  |         |                           |                      |                   |                 | 3 = 0.180     |                  |

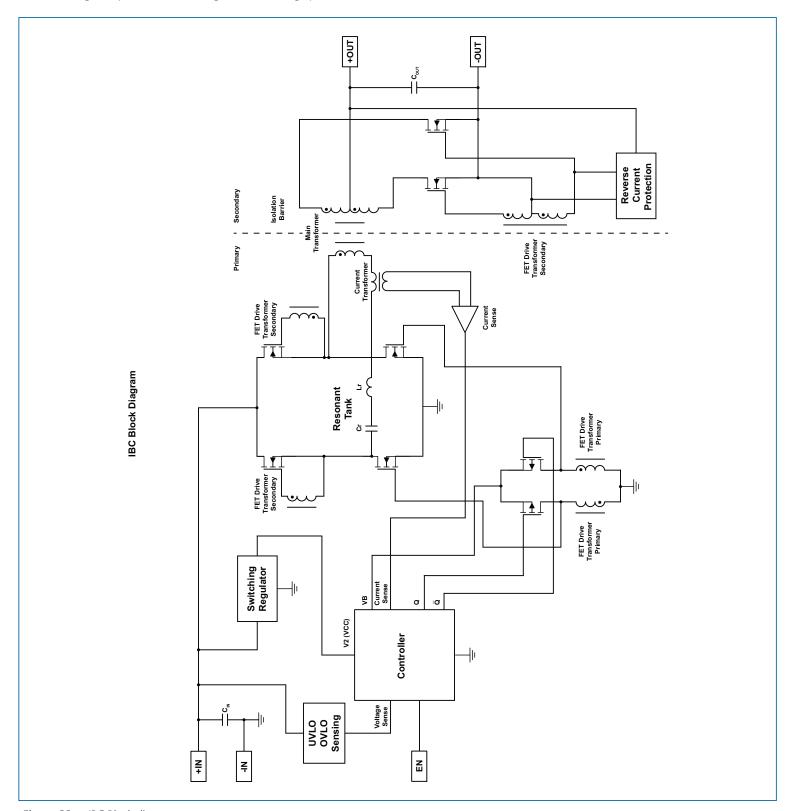

# **IBC BLOCK DIAGRAM**

The Sine Amplitude Converter<sup> $\mathbb{M}$ </sup> (SAC<sup> $\mathbb{M}$ </sup>) uses a high frequency resonant tank to transfer energy from input to output. The resonant tank is formed by Cr and leakage inductance from the main transformer, Lr, as shown in the block diagram. The controller regulates switching frequency of the FET drivers, monitors current sensing, and provides undervoltage and overvoltage protection.

Figure 32 — IBC Block diagram

**IBC MODULE**

Page 12 of 14

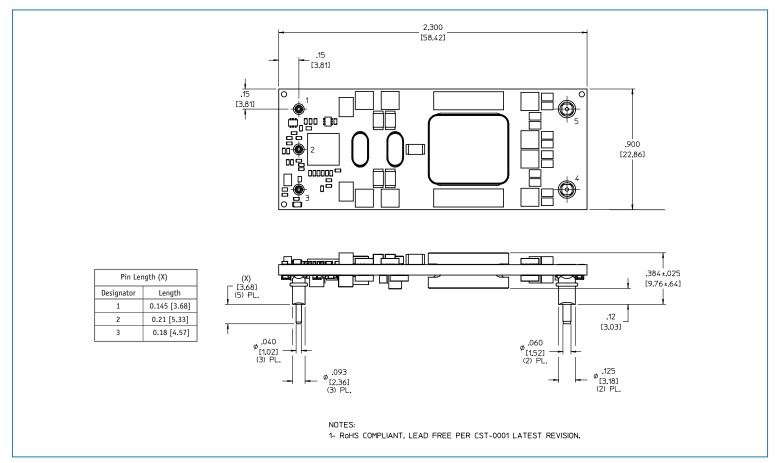

# **MECHANICAL DRAWINGS**

Figure 33 — IBC outline drawing

Figure 34 — IBC PCB recommended hole pattern

# Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication. Vicor reserves the right to make changes to any products, specifications, and product descriptions at any time without notice. Information published by Vicor has been checked and is believed to be accurate at the time it was printed; however, Vicor assumes no responsibility for inaccuracies. Testing and other quality controls are used to the extent Vicor deems necessary to support Vicor's product warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

Specifications are subject to change without notice.

#### **Vicor's Standard Terms and Conditions**

All sales are subject to Vicor's Standard Terms and Conditions of Sale, which are available on Vicor's webpage or upon request.

#### **Product Warranty**

In Vicor's standard terms and conditions of sale, Vicor warrants that its products are free from non-conformity to its Standard Specifications (the "Express Limited Warranty"). This warranty is extended only to the original Buyer for the period expiring two (2) years after the date of shipment and is not transferable.

UNLESS OTHERWISE EXPRESSLY STATED IN A WRITTEN SALES AGREEMENT SIGNED BY A DULY AUTHORIZED VICOR SIGNATORY, VICOR DISCLAIMS ALL REPRESENTATIONS, LIABILITIES, AND WARRANTIES OF ANY KIND (WHETHER ARISING BY IMPLICATION OR BY OPERATION OF LAW) WITH RESPECT TO THE PRODUCTS, INCLUDING, WITHOUT LIMITATION, ANY WARRANTIES OR REPRESENTATIONS AS TO MERCHANTABILITY, FITNESS FOR PARTICULAR PURPOSE, INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT, OR ANY OTHER MATTER.

This warranty does not extend to products subjected to misuse, accident, or improper application, maintenance, or storage. Vicor shall not be liable for collateral or consequential damage. Vicor disclaims any and all liability arising out of the application or use of any product or circuit and assumes no liability for applications assistance or buyer product design. Buyers are responsible for their products and applications using Vicor products and components. Prior to using or distributing any products that include Vicor components, buyers should provide adequate design, testing and operating safeguards.

Vicor will repair or replace defective products in accordance with its own best judgment. For service under this warranty, the buyer must contact Vicor to obtain a Return Material Authorization (RMA) number and shipping instructions. Products returned without prior authorization will be returned to the buyer. The buyer will pay all charges incurred in returning the product to the factory. Vicor will pay all reshipment charges if the product was defective within the terms of this warranty.

#### **Life Support Policy**

VICOR'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF VICOR CORPORATION. As used herein, life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness. Per Vicor Terms and Conditions of Sale, the user of Vicor products and components in life support applications assumes all risks of such use and indemnifies Vicor against all liability and damages.

#### **Intellectual Property Notice**

Vicor and its subsidiaries own Intellectual Property (including issued U.S. and Foreign Patents and pending patent applications) relating to the products described in this data sheet. No license, whether express, implied, or arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Interested parties should contact Vicor's Intellectual Property Department.

The products described on this data sheet are protected by the following U.S. Patents Numbers: 5,945,130; 6,403,009; 6,710,257; 6,911,848; 6,930,893; 6,934,166; 6,940,013; 6,969,909; 7,038,917; 7,166,898; 7,187,263; 7,361,844; D496,906; D505,114; D506,438; D509,472; and for use under 6,975,098 and 6,984,965.

## **Vicor Corporation**

25 Frontage Road Andover, MA, USA 01810 Tel: 800-735-6200 Fax: 978-475-6715

#### email

Customer Service: <u>custserv@vicorpower.com</u> Technical Support: <u>apps@vicorpower.com</u>