# DAC707 DAC708 DAC709

# Microprocessor-Compatible 16-BIT DIGITAL-TO-ANALOG CONVERTERS

## **FEATURES**

- TWO-CHIP CONSTRUCTION

- HIGH-SPEED 16-BIT PARALLEL, 8-BIT (BYTE) PARALLEL, AND SERIAL INPUT MODES

- DOUBLE-BUFFERED INPUT REGISTER CONFIGURATION

- V<sub>OUT</sub> AND I<sub>OUT</sub> MODELS

## DESCRIPTION

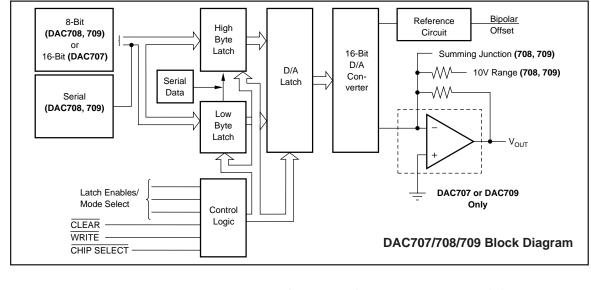

The DAC708 and DAC709 are 16-bit converters designed to interface to an 8-bit microprocessor bus. 16bit data is loaded in two successive 8-bit bytes into parallel 8-bit latches before being transferred into the D/A latch. The DAC708 and DAC709 are current and voltage output models respectively and are in 24-pin hermetic DIPs. Input coding is Binary Two's Complement (bipolar) or Unipolar Straight Binary (unipolar, when an external logic inverter is used to invert the MSB). In addition, the DAC708/709 can be loaded serially (MSB first).

The DAC707 is designed to interface to a 16-bit bus.

- HIGH ACCURACY: Linearity Error ±0.003% of FSR max

Differential Linearity Error ±0.006% of FSR max

- MONOTONIC (TO 14 BITS) OVER SPECIFIED TEMPERATURE RANGE

- HERMETICALLY SEALED

- LOW COST PLASTIC VERSIONS AVAILABLE (DAC707JP/KP)

Data is written into a 16-bit latch and subsequently the D/A latch. The DAC707 has bipolar voltage output and input coding is Binary Two's Complement (BTC).

All models have Write and Clear control lines as well as input latch enable lines. In addition, DAC708 and DAC709 have Chip Select control lines. In the bipolar mode, the Clear input sets the D/A latch to give zero voltage or current output. They are all 14-bit accurate and are complete with reference, and for the DAC707, and DAC709, a voltage output amplifier. All models are available with an optional burn-in screening.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

## ELECTRICAL

At  $T_A = +25^{\circ}C$ ,  $V_{CC} = \pm 15V$ ,  $V_{DD} = +5V$ , and after a 10-minute warm-up, unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                                                                | DAC707JP     |                                                                                                            |                                                                                                        |                | C707/708/7<br>DAC707KF                |                                                                                          | DAC707/708/<br>709BH, SH |                                 |                                          |                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------|---------------------------------------|------------------------------------------------------------------------------------------|--------------------------|---------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRODUCT                                                                                                                                                                                                                                                                                                                                                        | MIN          | ТҮР                                                                                                        | MAX                                                                                                    | MIN            | TYP                                   | MAX                                                                                      | MIN                      | TYP                             | MAX                                      | UNITS                                                                                                                         |

| INPUT                                                                                                                                                                                                                                                                                                                                                          |              |                                                                                                            |                                                                                                        |                |                                       |                                                                                          |                          |                                 |                                          |                                                                                                                               |

| DIGITAL INPUT<br>Resolution<br>Bipolar Input Code (all models)                                                                                                                                                                                                                                                                                                 | Bina         | ry Two's Co                                                                                                | 16                                                                                                     |                | *                                     | *                                                                                        |                          | *                               | *                                        | Bits                                                                                                                          |

| $ \begin{array}{c} \text{Dipolar input Code}(\text{cli}) (DAC708/709 \text{ only}) \\ \text{Logic Levels}^{(2)}: \text{V}_{\text{IH}} \\ & \text{V}_{\text{IL}} \\ & \text{I}_{\text{IH}} (\text{V}_{\text{I}} = +2.7\text{V}) \\ & \text{I}_{\text{IL}} (\text{V}_{\text{I}} = +0.4\text{V}) \end{array} $                                                    | +2.0<br>-1.0 |                                                                                                            | +5.5<br>+0.8<br>1                                                                                      | Uniţ<br>*<br>* | bolar Straig                          | ht Binary<br>*<br>*<br>*                                                                 | *                        | *                               | *<br>*<br>*                              | V<br>V<br>μΑ<br>μΑ                                                                                                            |

| TRANSFER CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                       |              |                                                                                                            |                                                                                                        |                |                                       |                                                                                          |                          |                                 |                                          |                                                                                                                               |

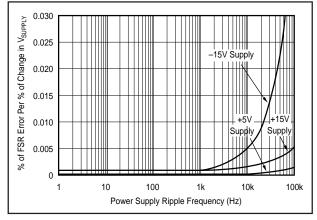

| ACCURACY <sup>(3)</sup><br>Linearity Error<br>Differential Linearity Error <sup>(5)</sup><br>at Bipolar Zero <sup>(5, 6)</sup><br>Gain Error <sup>(7)</sup><br>Zero Error <sup>(7)</sup><br>Monotonicity Over Spec Temp Range<br>Power Supply Sensitivity: +V <sub>CC</sub> , -V <sub>CC</sub><br>V <sub>DD</sub>                                              | 13           | $\begin{array}{c} \pm 0.003 \\ \pm 0.0045 \\ \pm 0.07 \\ \pm 0.05 \\ \pm 0.0015 \\ \pm 0.0001 \end{array}$ | $\begin{array}{c} \pm 0.006 \\ \pm 0.012 \\ \pm 0.30 \\ \pm 0.1 \\ \pm 0.006 \\ \pm 0.001 \end{array}$ | 14             | ±0.0015<br>±0.003<br>±0.003<br>*<br>* | ±0.003<br>±0.006<br>±0.006<br>±0.15<br>*<br>*                                            | 14                       | *<br>±0.0015<br>±0.05<br>*<br>* | *<br>±0.003<br>±0.10<br>*<br>±0.003<br>* | % of FSR <sup>(4)</sup><br>% of FSR<br>% of FSR<br>% of FSR<br>Bits<br>% of FSR/%V <sub>CC</sub><br>% of FSR/%V <sub>DD</sub> |

| DRIFT (Over Spec Temp Range <sup>(3)</sup> )<br>Total Error Over Temp Range <sup>(8)</sup><br>Total Full Scale Drift<br>Gain Drift<br>Zero Drift: Unipolar (DAC708/709 only)<br>Bipolar (all models)<br>Differential Linearity Over Temp <sup>(5)</sup><br>Linearity Error Over Temp <sup>(5)</sup>                                                            |              | ±0.08<br>±10<br>±10<br>±5                                                                                  | ±30<br>±15<br>±0.012<br>±0.012                                                                         |                | *<br>*<br><u>+</u> 2.5<br>*           | $\pm 0.15$<br>$\pm 25$<br>$\pm 25$<br>$\pm 12$<br>$\pm 0.009$ ,<br>-0.006<br>$\pm 0.006$ |                          | *<br>±7<br>±1.5<br>±4           | ±0.10<br>±15<br>±15<br>±3<br>±10<br>*    | % of FSR<br>ppm of FSR/°C<br>ppm of FSR/°C<br>ppm of FSR/°C<br>% of FSR<br>% of FSR                                           |

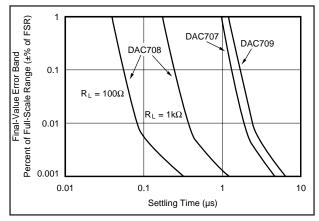

| $\begin{array}{l} \textbf{SETTLING TIME (to \pm 0.003\% \text{ of FSR})^{(9)}}\\ \textbf{Voltage Output Models}\\ \textbf{Full Scale Step (2k\Omega load)}\\ \textbf{1LSB Step at Worst Case Code^{(10)}}\\ \textbf{Slew Rate}\\ \textbf{Current Output Models}\\ \textbf{Full Scale Step (2mA): 10 to 100\Omega Load}\\ \textbf{1k\Omega Load}\\ \end{array}$ |              | 4<br>2.5<br>10                                                                                             |                                                                                                        |                | *<br>*<br>*<br>350<br>1               | 8 4                                                                                      |                          | * * *                           | 8<br>4                                   | μs<br>μs<br>V/μs<br>ns<br>μs                                                                                                  |

| OUTPUT                                                                                                                                                                                                                                                                                                                                                         |              |                                                                                                            |                                                                                                        |                |                                       |                                                                                          |                          |                                 |                                          |                                                                                                                               |

| VOLTAGE OUTPUT MODELS<br>Output Voltage Range<br>DAC709: Unipolar (USB Code)<br>Bipolar (BTC Code)<br>DAC707 Bipolar (BTC Code)<br>Output Current<br>Output Current<br>Output Impedance<br>Short Circuit to Common Duration                                                                                                                                    | ±5           | ±10<br>0.15<br>Indefinite                                                                                  |                                                                                                        | *              | 0 to +10<br>±5, ±10<br>*              |                                                                                          | *                        | *<br>*<br>*                     |                                          | V<br>V<br>mA<br>Ω                                                                                                             |

| CURRENT OUTPUT MODELS<br>Output Current Range (±30% typ)<br>DAC708: Unipolar (USB Code)<br>Bipolar (BTC Code)<br>Unipolar Output Impedance (±30% typ)<br>Bipolar Output Impedance (±30% typ)<br>Compliance Voltage                                                                                                                                             |              |                                                                                                            |                                                                                                        |                | 0 to -2<br>±1<br>4.0<br>2.45<br>±2.5  |                                                                                          |                          | *<br>*<br>*                     |                                          | mA<br>mA<br>kΩ<br>V                                                                                                           |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

## **ELECTRICAL (CONT)**

At  $T_A = +25^{\circ}$ C,  $V_{CC} = \pm 15$ V,  $V_{DD} = +5$ V, and after a 10-minute warm-up, unless otherwise noted.

|                                                            |       | DAC707JP |       |     | DAC707/708/709KH,<br>DAC707KP |      | DAC707/708/<br>709BH, SH |     |      |       |

|------------------------------------------------------------|-------|----------|-------|-----|-------------------------------|------|--------------------------|-----|------|-------|

| PRODUCT                                                    | MIN   | TYP      | MAX   | MIN | TYP                           | MAX  | MIN                      | TYP | MAX  | UNITS |

| POWER SUPPLY REQUIREMENTS                                  |       |          |       |     |                               |      |                          |     |      |       |

| Voltage (all models): +V <sub>CC</sub>                     | +13.5 | +15      | +16.5 | *   | *                             | *    | *                        | *   | *    | V     |

| -V <sub>CC</sub>                                           | -13.5 | -15      | -16.5 | *   | *                             | *    | *                        | *   | *    | V     |

| V <sub>DD</sub><br>Current (No Load, +15V Supplies)        | +4.5  | +5       | +5.5  | *   | *                             | *    | *                        | *   | *    | V     |

| Current Output Models: +V <sub>CC</sub>                    |       |          |       |     | +10                           | +25  |                          | *   | *    | mA    |

| -V <sub>CC</sub>                                           |       |          |       |     | -13                           | -25  |                          | *   | *    | mA    |

| V <sub>DD</sub>                                            |       |          |       |     | +5                            | +10  |                          | *   | *    | mA    |

| Voltage Output Models: +V <sub>CC</sub>                    |       | +16      | +30   |     | *                             | *    |                          | *   | *    | mA    |

| -V <sub>CC</sub>                                           |       | -18      | -30   |     | *                             | *    |                          | *   | *    | mA    |

| V <sub>DD</sub>                                            |       | +5       | +10   |     | *                             | *    |                          | *   | *    | mA    |

| Power Dissipation (±15V supplies)<br>Current Output Models |       |          |       |     | 370                           | 800  |                          | *   | *    | mW    |

| Voltage Output Models                                      |       | 535      |       |     | *                             | 950  |                          | *   | *    | mW    |

| TEMPERATURE RANGE                                          |       |          |       |     |                               |      |                          |     |      |       |

| Specification: BH Grades                                   |       |          |       |     |                               |      | -25                      |     | +85  | °C    |

| JP, KP, KH Grades                                          | 0     |          | +70   | *   |                               | *    |                          |     |      | °C    |

| SH Grades                                                  |       |          |       |     |                               |      | -55                      |     | +125 | °C    |

| Storage: Ceramic                                           |       |          |       | -65 |                               | +150 | -65                      |     | +150 | °C    |

| Plastic                                                    | -60   |          | +100  | *   |                               | *    |                          |     |      | °C    |

\*Specification same as for models in column to the left.

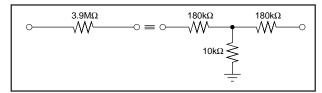

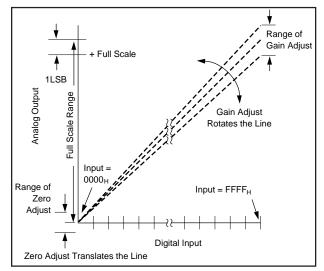

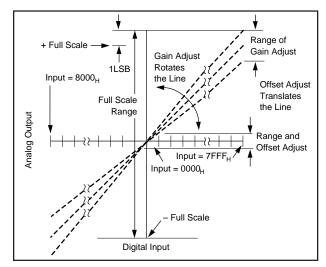

NOTES: (1) MSB must be inverted externally prior to DAC708/709 input. (2) Digital inputs are TTL, LSTTL, 54/74C, 54/74HC and 54/74HTC compatible over the specified temperature range. (3) DAC708 (current-output models) are specified and tested with an external output operational amplifier connected using the internal feedback resistor in all tests. (4) FSR means Full Scale Range. For example, for  $\pm$ 10V output, FSR = 20V. (5)  $\pm$ 0.0015% of Full Scale Range is equal to 1 LSB in 16-bit resolution,  $\pm$ 0.003% of Full Scale Range is equal to 1 LSB in 16-bit resolution.  $\pm$ 0.006% of Full Scale Range is equal to 1 LSB in 16-bit resolution. (6) Error at input code 0000<sub>H</sub>. (For unipolar connection on DAC708/709, the MSB must be inverted externally prior to D/A input.) (7) Adjustable to zero with external trim potentiometer. Adjusting the gain potentiometer rotates the transfer function around the bipolar zero point. (8) With gain and zero errors adjusted to zero at +25°C. (9) Maximum represents the 3σ limit. Not 100% tested for this parameter. (10) The bipolar worst-case code change is FFFF<sub>H</sub> to 0000<sub>H</sub> and 0000<sub>H</sub> to FFFF<sub>H</sub>. For unipolar (DAC708/709 only) it is 7FFF<sub>H</sub> to 8000<sub>H</sub> and 8000<sub>H</sub> to 7FFF<sub>H</sub>.

#### **PACKAGE INFORMATION**

| PRODUCT  | PACKAGE                          | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|----------------------------------|------------------------------------------|

| DAC707JP | 28-Pin Plastic DBL Wide DIP      | 215                                      |

| DAC707KP | 28-Pin Plastic DBL Wide DIP      | 215                                      |

| DAC707BH | 28LD Side Brazed<br>Hermetic Dip | 149                                      |

| DAC707KH | 28LD Side Brazed<br>Hermetic DIP | 149                                      |

| DAC707SH | 28LD Side Brazed<br>Hermetic DIP | 149                                      |

| DAC708BH | 24LD Side Brazed<br>Hermetic DIP | 165                                      |

| DAC708KH | 24LD Side Brazed<br>Hermetic DIP | 165                                      |

| DAC708SH | 24LD Side Brazed<br>Hermetic DIP | 165                                      |

| DAC709BH | 24LD Side Brazed<br>Hermetic DIP | 165                                      |

| DAC709KH | 24LD Side Brazed<br>Hermetic DIP | 165                                      |

| DAC709SH | 24LD Side Brazed<br>Hermetic DIP | 165                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

#### **ABSOLUTE MAXIMUM RATINGS**

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability. |

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

DAC707/708/709

#### **ORDERING INFORMATION**

| PRODUCT                                                                                                                                                                                      | TEMPERATURE                                                                                                                                         | INPUT                                                                                                                                              | OUTPUT                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                              | RANGE                                                                                                                                               | CONFIGURATION                                                                                                                                      | CONFIGURATION                                                                                                                                                               |

| DAC707JP<br>DAC707JP-BI <sup>(1)</sup><br>DAC707KP<br>DAC707KP-BI <sup>(1)</sup><br>DAC707KH<br>DAC707KH-BI <sup>(1)</sup><br>DAC707BH<br>DAC707BH<br>DAC707BH-BI <sup>(1)</sup><br>DAC707SH | 0°C to +70°C<br>0°C to +70°C<br>0°C to +70°C<br>0°C to +70°C<br>0°C to +70°C<br>0°C to +70°C<br>-25°C to +85°C<br>-25°C to +85°C<br>-55°C to +125°C | 16-bit port<br>16-bit port<br>16-bit port<br>16-bit port<br>16-bit port<br>16-bit port<br>16-bit port<br>16-bit port<br>16-bit port<br>16-bit port | ±10V output     ±10V output |

| DAC707SH-BI <sup>(1)</sup>                                                                                                                                                                   | -55°C to +125°C                                                                                                                                     | 16-bit port                                                                                                                                        | ±10V output                                                                                                                                                                 |

| DAC708KH                                                                                                                                                                                     | 0°C to +70°C                                                                                                                                        | 8-bit port                                                                                                                                         | ±1mA output                                                                                                                                                                 |

| DAC708BH                                                                                                                                                                                     | −25°C to +85°C                                                                                                                                      | 8-bit port                                                                                                                                         | ±1mA output                                                                                                                                                                 |

| DAC708SH                                                                                                                                                                                     | −55°C to +125°C                                                                                                                                     | 8-bit port                                                                                                                                         | ±1mA output                                                                                                                                                                 |

| DAC709KH                                                                                                                                                                                     | 0°C to +70°C                                                                                                                                        | 8-bit port                                                                                                                                         | ±10V output                                                                                                                                                                 |

| DAC709BH                                                                                                                                                                                     | −25°C to +85°C                                                                                                                                      | 8-bit port                                                                                                                                         | ±10V output                                                                                                                                                                 |

| DAC709SH                                                                                                                                                                                     | −55°C to +125°C                                                                                                                                     | 8-bit port                                                                                                                                         | ±10V output                                                                                                                                                                 |

NOTE: (1) 25 piece minimum order.

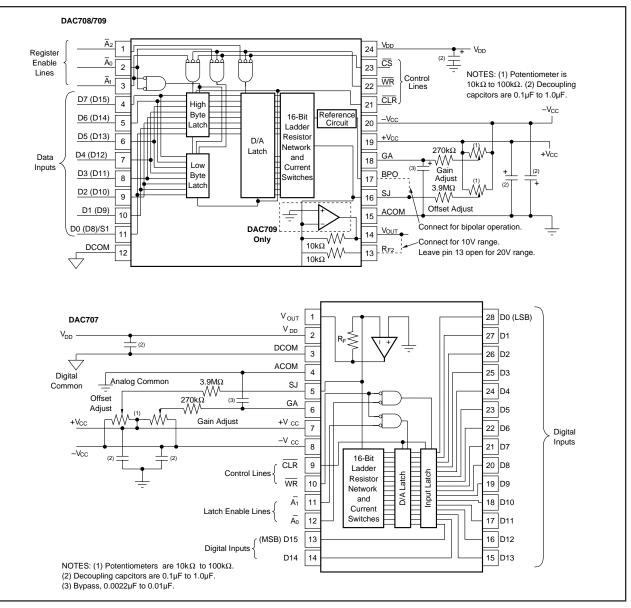

#### **CONNECTION DIAGRAMS**

## **DESCRIPTION OF PIN FUNCTIONS**

| NonLogic supply (+5V)2 $A_0$ $E_0$ DCOMDigital common3 $A_1$ $E_0$ ACOMAnalog common4D7 (D15)InSJSumming junction of the internal output op amp for the<br>bagram.5D6 (D14)InGAGain adjust pinction of the output amplifier. Refer to Block<br>Diagram.5D6 (D14)DGAGain adjust pinction of the output amplifier. Refer to Block<br>Diagram.7D4 (D12)D-V_{CC}Positive supply voltage (+15V)7D4 (D12)D-V_{CC}Negative supply voltage (-15V)8D3 (D11)DCLRClear line. Sets the input latch to zero and sets the D/A<br>latch to the input code that gives bipolar zero on the<br>D/A output (Active low)10D1 (D9)DWRWrite control line (Active low)11D0 (D8)/SIDD15 (MSB)Data bit 15 (Most Significant Bit)13R <sub>F2</sub> $F_0$ D13Data bit 12Data bit 12InfNGC/CO80)ND14Data bit 1315ACOMAD15Data bit 1414Your<br>NGC/CO708)SI<br>DO<br>DI<br>DI<br>DI<br>DI<br>DI<br>DIBAGAGAD14Data bit 16C22WIRVD15Data bit 16CCCRD14Data bit 16C22WIRVD15Data bit 623CGCCD16Data bit 623DGCC<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DAC708/709                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD<br>DD<br>LOGIC SUPPLY (+5V)LOGIC SUPPLY (+5V) <thlogic (+5v)<="" supply="" th=""><thlogic (+5v)<<="" supply="" th=""><th>DESCRIPTION</th></thlogic></thlogic>                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                        |

| VDD<br>DDLogic supply (+5V)2Ao<br>aLogic supply (+5V)DCOMDigital common3A,Logic supply (-5V)ACOMAnalog common4D7 (D15)In<br>to the summing junction of the internal output op amp for the<br>DDAC707. Offset adjust circuit is connected to the<br>summing junction of the output amplifier. Refer to Block<br>Diagram.5D6 (D14)In<br>erGAGain adjust pin. Refer to Connection Diagram for gain<br>adjust circuit.6D5 (D13)D-VocPositive supply voltage (+15V)7D4 (D12)D-VocNegative supply voltage (+15V)7D4 (D12)D-VocNegative supply voltage (-15V)7D4 (D12)DCIRClear line. Sets the input latch to zero and sets the D/A<br>latch to the input code that gives bipolar zero on the<br>D/A output (Active low)10D (D9)DMRWrite control line (Active low)11D (D08)/SIDDA1Enable for Input latch (Active low)11D (D08)/SIDD13Data bit 1315ACOMAD14Data bit 1315ACOMAD15Data bit 1018GAGD9Data bit 1019VocPD1Data bit 316SJ (DAC709)DD1Data bit 320-VocPD13Data bit 1018GAGD9Data bit 320-VocPD1Data bit 620-Voc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Latch enable for D/A latch (Active low)                                                                                                                                                                                                            |

| ACOMAnalog common4D7 (D15)In<br>dat<br>dat<br>datSJSumming junction of the internal output op amp for the<br>DAC707. Offset adjust circuit is connected to the<br>summing junction of the output amplifier. Refer to Block<br>Diagram.5D6 (D14)In<br>datGAGain adjust pin. Refer to Connection Diagram for gain<br>adjust circuit.6D5 (D13)D1+V_{CC}Positive supply voltage (+15V)7D4 (D12)D1-V_{CC}Negative supply voltage (-15V)8B3 (D11)D2CIRClear line. Sets the input latch to zero and sets the D/A<br>tatch to the input code that gives bipolar zero on the<br>D/A output (Active low)10D1 (D9)D2WRWrite control line (Active low)10D1 (D9)D2D3Af_0Enable for input latch (Active low)11D0 (D8)/SID6D15 (MSB)Data bit 15 (Most Significant Bit)13RF2F6D14Data bit 1315ACOMArD12Data bit 1111BPOBiD13Data bit 1111BPOBiD14Data bit 1018GAGAD15MSBData bit 320 $-V_{CC}$ PCD16Data bit 622 $\overline{WR}$ $\overline{WR}$ D17Data bit 623 $\overline{CS}$ $\overline{CS}$ D18Data bit 623 $\overline{CS}$ $\overline{CS}$ D19Data bit 623 $\overline{CS}$ $\overline{CS}$ D10Data bit 624 $\sqrt{DO}$ $\sqrt{DO}$ <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Latch enable for "low byte" input (Active low). When both $A_0$ and $A_1$ are logic "0", the serial input mode is selected and the serial input is enabled.                                                                                        |

| SJSumming junction of the internal output op amp for the<br>DAC707. Offset adjust circuit is connected to the<br>summing junction of the output amplifier. Refer to Block<br>Diagram.5D6 (D14)In<br>erGAGain adjust pin. Refer to Connection Diagram for gain<br>adjust circuit.6D5 (D13)D-V_{CC}Positive supply voltage (+15V)7D4 (D12)D-V_{CC}Negative supply voltage (-15V)8D3 (D11)DCLRClear line. Sets the input tatch to zero and sets the D/A<br>latch to the input code that gives bipolar zero on the<br>D/A output (Active low)10D1 (D9)DWRWrite control line (Active low)11D0 (D8)/SID $\overline{A}_1$ Enable for D/A converter latch (Active low)11D0 (D8)/SIDD15 (MSB)Data bit 15 (Most Significant Bit)13 $R_{r2}$ $R_{r2}$ D14Data bit 12DDDDD15MBBData bit 1315ACOMAD12Data bit 1117BPOBitD14Data bit 1315ACOMAD12Data bit 1018GAGD13Data bit 1018GAGD14Data bit 1117BPOBitD10Data bit 320-V_{CC}PD11Data bit 1018GAGD2Data bit 620-V_{CC}PD3Data bit 622WRVD4Data bit 5Data bit 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Latch enable for "high byte" input (Active low). When both $A_0$ and $A_1$ are logic "0", the serial input mode is selected and the serial input is enabled.                                                                                       |

| DAC707. Offset adjust circuit is connected to the<br>summing junction of the output amplifier. Refer to Block<br>Diagram.erGAGain adjust pin. Refer to Connection Diagram for gain<br>adjust circuit.6D5 (D13)Di+V <sub>CC</sub> Positive supply voltage (+15V)7D4 (D12)Di-V <sub>CC</sub> Negative supply voltage (-15V)7D4 (D12)Di-V <sub>CC</sub> Negative supply voltage (-15V)8D3 (D11)DiCLRClear line. Sets the input latch to zero and sets the D/A<br>latch to the input code that gives bipolar zero on the<br>D/A output (Active low)10D1 (D9)Di $\overline{A_1}$ Enable for input latch (Active low)10D1 (D9)DiSet $\overline{A_0}$ Enable for input latch (Active low)12DCOMSetD15 (MSB)Data bit 15 (Most Significant Bit)13R <sub>F2</sub> F6<br>ar<br>ar<br>ar<br>arSetD14Data bit 13D1414V <sub>OUT</sub><br>N <sub>CT</sub><br>R <sub>F1</sub> (DAC708)Vie<br>St<br>(DAC708)SetD13Data bit 11D1D1SetACOMAr<br>Ad<br>St<br>(DAC708)SetD14Data bit 1018GAGD15MSBData bit 1018GAGD16Data bit 1019+V <sub>CC</sub> P1D17Data bit 320-V <sub>CC</sub> P1D18Data bit 420-V <sub>CC</sub> P1D19Data bit 5CSCSCSD10Data bit 621CLRCID6Data bit 5 <td>Input for data bit 7 if enabling low byte (LB) latch or data bit 15 if enabling the high byte (HB) latch.</td>                                                                                                                                                                                                                                                                                                                                                                               | Input for data bit 7 if enabling low byte (LB) latch or data bit 15 if enabling the high byte (HB) latch.                                                                                                                                          |

| adjust circuit.CCCCC+V_{CC}Positive supply voltage (+15V)7D4 (D12)D2-V_{CC}Negative supply voltage (-15V)8D3 (D11)D2CLRClear line. Sets the input latch to zero and sets the D/A<br>latch to the input code that gives bipolar zero on the<br>D/A output (Active low)10D1 (D9)WRWrite control line (Active low)10D1 (D9)D2 $\overline{A}_1$ Enable for D/A converter latch (Active low)11D0 (D8)/SID5 $\overline{A}_0$ Enable for input latch (Active low)12DCOMD1D15 (MSB)Data bit 15 (Most Significant Bit)13R <sub>F2</sub> F6D14Data bit 1414V <sub>OUT</sub><br>R <sub>F1</sub> (DAC708)WD12Data bit 1216SJ (DAC709)<br>Iour (DAC708)D1D14Data bit 1117BPOBit<br>Bit<br>BitD14Data bit 1117BPOBit<br>Bit<br>BitD15MSBData bit 1018GAGD16Data bit 1018GAGGD7Data bit 721CLRCLCLD6Data bit 622WRWKD6Data bit 5Data bit 325No pinKD2Data bit 325No pinCKD3Data bit 326No pinCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input for data bit 6 if enabling LB latch or data bit 14 if enabling the HB latch.                                                                                                                                                                 |

| $-V_{CC}$<br>CLRNegative supply voltage (-15V)8<br>clear line. Sets the input latch to zero and sets the D/A<br>latch to the input code that gives bipolar zero on the<br>D/A output (Active low)9<br>clear line. Sets the input latch to zero and sets the D/A<br>latch to the input code that gives bipolar zero on the<br>D/A output (Active low)9<br>clear line. Sets the input latch to zero and sets the D/A<br>latch to the input code that gives bipolar zero on the<br>D/A output (Active low)9<br>clear line. Sets the input latch (Active low)10D 1 (D9)D0<br>D $\overline{A}_{1}$ Enable for D/A converter latch (Active low)11D0 (D8)/SID<br>SetD15 (MSB)Data bit 15 (Most Significant Bit)13R <sub>F2</sub> Fa<br>registrationD14Data bit 1414 $V_{OUT}$<br>R <sub>F1</sub> (DAC708)Via<br>R<br>R<br>registrationVia<br>R<br>R<br>registrationD13Data bit 13Data bit 1216SJ (DAC709)<br>R<br>R<br>registrationSi (DAC709)<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R<br>R | Data bit 5 (LB) or data bit 13 (HB)                                                                                                                                                                                                                |

| $\overline{\text{CLR}}$ Clear line. Sets the input latch to zero and sets the D/A<br>D/A output (Active low)9D2 (D10)D2 $\overline{\text{WR}}$ Write control line (Active low)10D1 (D9)D1D1 $\overline{\text{A}}_1$ Enable for D/A converter latch (Active low)11D0 (D8)/SID5 $\overline{\text{A}}_0$ Enable for input latch (Active low)12DCOMD1D15 (MSB)Data bit 15 (Most Significant Bit)13R <sub>F2</sub> FragretD14Data bit 14Vourt<br>RF1 (DAC708)Vourt<br>RF1Vourt<br>RF1 (DAC708)Vourt<br>RF1D13Data bit 1216SJ (DAC709)<br>RO10SI<br>D10 (DAC708)SI<br>D10D14Data bit 1117BPOBi<br>Bi<br>D10SI<br>RO10SI<br>RO10D11Data bit 1117BPOBi<br>Bi<br>D10SI<br>RO10SI<br>RO10SI<br>RO10D14Data bit 1117BPOBi<br>Bi<br>D10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10SI<br>RO10 <td>Data bit 4 (LB) or data bit 12 (HB)</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Data bit 4 (LB) or data bit 12 (HB)                                                                                                                                                                                                                |

| Iatch to the input code that gives bipolar zero on the<br>D/A output (Active Iow)I0D1 (D9)D2 $\overline{MR}$ Write control line (Active Iow)10D1 (D9)D2 $\overline{A}_1$ Enable for D/A converter latch (Active Iow)11D0 (D8)/SID2 $\overline{A}_0$ Enable for input latch (Active Iow)12DCOMD1D15 (MSB)Data bit 15 (Most Significant Bit)13 $R_{F2}$ $F_{e1}$ D14Data bit 1414 $V_{OUT}$<br>$R_{F1} (DAC708)R_{F2}R_{F1}D13Data bit 1215ACOMAdD12Data bit 1216SJ (DAC709)I_{OUT} (DAC708)SJD11Data bit 1117BPOBibijD10Data bit 1018GAGD9Data bit 320-V_{CC}PiCOD7Data bit 321CIRCICIRD6Data bit 523\overline{CS}CICIRD6Data bit 523\overline{CS}CICIRD3Data bit 325No pinTD2Data bit 325No pinT$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Data bit 3 (LB) or data bit 11 (HB)                                                                                                                                                                                                                |

| $\overline{A}_1$ Enable for D/A converter latch (Active low)11D0 (D8)/SID0 $\overline{A}_0$ Enable for input latch (Active low)12DCOMD1D15 (MSB)Data bit 15 (Most Significant Bit)13 $R_{F2}$ $F_{ar}$ D14Data bit 1414 $V_{OUT}$<br>$R_{F1} (DAC708)VoutR_{F1} (DAC708)VoutR_{F1} (DAC708)D13Data bit 1315ACOMArD12Data bit 1216SJ (DAC709)Iour (DAC708)D1D11Data bit 1117BPOBitD10Data bit 1018GAGD9Data bit 721\overline{CLR}CID7Data bit 523\overline{CS}CID6Data bit 523\overline{CS}CID6Data bit 523\overline{CS}CID3Data bit 325No pinTD2Data bit 325No pinT$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Data bit 2 (LB) or data bit 10 (HB)                                                                                                                                                                                                                |

| $\overline{A}_0$ Enable for input latch (Active low)       12       DCOM       Dist         D15 (MSB)       Data bit 15 (Most Significant Bit)       13 $R_{F2}$ $Fa$ D14       Data bit 14       14 $V_{OUT}$ $R_{F1}$ (DAC708) $V_{R1}$ D13       Data bit 13       15       ACOM       Ar         D12       Data bit 12       16 $SJ$ (DAC709) $SL$ D11       Data bit 11       17       BPO       Bit         D11       Data bit 11       17       BPO       Bit         D10       Data bit 19       19 $+V_{CC}$ Proce         D8       Data bit 3       20 $-V_{CC}$ Proce       Proce         D7       Data bit 6       20 $-V_{CC}$ Proce       Proce       Proce         D6       Data bit 7       21 $\overline{CLR}$ $\overline{CLR}$ $\overline{CLR}$ $\overline{CLR}$ $\overline{CLR}$ $\overline{CLR}$ $\overline{CLR}$ D10       Data bit 6       22 $\overline{VR}$ 23 $\overline{CLR}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Data bit 1 (LB) or data bit 9 (HB)                                                                                                                                                                                                                 |

| D15 (MSB)       Data bit 15 (Most Significant Bit)       13       R <sub>F2</sub> Fairs         D14       Data bit 14       14       Vout       R <sub>F1</sub> (DAC708)       Vout         D13       Data bit 13       15       ACOM       A         D14       Data bit 13       15       ACOM       A         D12       Data bit 12       16       SJ (DAC709)       Su (DAC709)                                                                                                                                                                                                                                                                                                                                    | Data bit 0 (LB) or data bit 8 (HB). Serial input when serial mode is selected.                                                                                                                                                                     |

| D14       Data bit 14       14 $V_{OUT}$<br>$R_{F1}$ (DAC708) $V_{US}$<br>$R_{R1}$ D13       Data bit 13       15       ACOM       Ar         D12       Data bit 12       16       SJ (DAC709)<br>$I_{OUT}$ (DAC708)       SI         D11       Data bit 12       16       SJ (DAC709)<br>$I_{OUT}$ (DAC708)       SI         D11       Data bit 11       17       BPO       Bit         D10       Data bit 9       19 $+V_{CC}$ Po         D8       Data bit 7       21       CLR       CI         D7       Data bit 5       23       CS       CI         D6       Data bit 5       23       CS       CI         D6       Data bit 3       25       No pin       To         D6       Data bit 3       25       No pin       To         D6       Data bit 3       25       No pin       To         D4       Data bit 3       25       No pin       CI         D7       Data bit 3       25       No pin       CI         D6       Data bit 3       25       No pin       CI         D7       Data bit 3       25       No pin       CI <td>Digital common</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Digital common                                                                                                                                                                                                                                     |

| D13       Data bit 13       15       ACOM       Ar         D12       Data bit 12       16       SJ (DAC709)       Su         D11       Data bit 11       17       BPO       Bit         D10       Data bit 10       18       GA       Ga         D10       Data bit 9       19 $+V_{CC}$ Pe         D8       Data bit 7       20 $-V_{CC}$ Nu         D7       Data bit 7       21       CLR       CL         D6       Data bit 6       22       WR       W         D7       Data bit 6       23       CS       CL         D6       Data bit 6       24 $V_{DD}$ La         D4       Data bit 3       24       V_D       La         D6       Data bit 6       23       CS       CL         D4       Data bit 3       24       V_D       La         D4       Data bit 3       25       No pin       CL         D3       Data bit 3       25       No pin       CL         D2       Data bit 2       26       No pin       CL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Feedback resistor for internal or external operational<br>amplifier. Connect to pin 14 when a 10V output range<br>is desired. Leave open for a 20V output range.                                                                                   |

| D12Data bit 1216SJ (DAC709)<br>IouT (DAC708)Su<br>AD11Data bit 1117BPOBiD10Data bit 1018GAGD9Data bit 919+V <sub>CC</sub> PdD8Data bit 820-V <sub>CC</sub> PdD7Data bit 7Data bit 7CIRCIRD6Data bit 523CSCID4Data bit 523CSCID4Data bit 324V <sub>DD</sub> LID3Data bit 325No pinTD2Data bit 2CICICI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Voltage output for DAC709 or feedback resistor for<br>use with an external output op amp for the DAC708.<br>Refer to Connection Diagram for connection of<br>external op amp to DAC708.                                                            |

| D11Data bit 1117BPOBit<br>bitD10Data bit 1018GAGD9Data bit 919+V <sub>CC</sub> PoD8Data bit 820-V <sub>CC</sub> NoD7Data bit 721CLRCLD6Data bit 622WRWD5Data bit 523CSCLD4Data bit 324V <sub>DD</sub> LCD3Data bit 325No pinT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Analog common                                                                                                                                                                                                                                      |

| D10Data bit 1018GAGiD9Data bit 919+V <sub>CC</sub> PdD8Data bit 820-V <sub>CC</sub> NdD7Data bit 721CLRCLD6Data bit 622WRWD5Data bit 523CSCLD4Data bit 324V <sub>DD</sub> LCD3Data bit 325No pinTD2Data bit 2VPdCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Summing junction of the internal output op amp for the DAC709, or the current output for the DAC708. Refer to Connection Diagram for connection of external op amp to DAC708.                                                                      |

| D9Data bit 919+V <sub>CC</sub> PdD8Data bit 820-V <sub>CC</sub> NuD7Data bit 721CLRCLD6Data bit 622WRWD5Data bit 523CSCLD4Data bit 324V <sub>DD</sub> LCD3Data bit 20ata bit 3CFNo pinD2Data bit 2CCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bipolar offset. Connect to pin 16 when operating in the bipolar mode. Leave open for unipolar mode.                                                                                                                                                |

| D8Data bit 820-V_{CC}NuD7Data bit 72121-V_{CC}NuD6Data bit 622WRWD5Data bit 523CSCID4Data bit 424V_{DD}LCD3Data bit 325No pinTD2Data bit 2CCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Gain adjust pin                                                                                                                                                                                                                                    |

| D7Data bit 721CLRCLD6Data bit 622WRWD5Data bit 523CSCLD4Data bit 424VDDLCD3Data bit 325No pinTD2Data bit 2CNo pinT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Positive supply voltage (+15V)                                                                                                                                                                                                                     |

| D6Data bit 622WRWD5Data bit 523CSCID4Data bit 424V <sub>DD</sub> LoD3Data bit 325No pin1D2Data bit 2(T1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Negative supply voltage (-15V)                                                                                                                                                                                                                     |

| D5Data bit 523CSCID4Data bit 424VVLoD3Data bit 325No pinLoD2Data bit 20No pinCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Clear line. Sets the high and low byte input registers<br>to zero and, for bipolar operation, sets the D/A register<br>to the input code that gives bipolar zero on the D/A<br>output. (In the unipolar mode, invert the MSB prior to<br>the D/A.) |

| D4Data bit 424VDDLaD3Data bit 325No pin1D2Data bit 226No pin1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Write control line                                                                                                                                                                                                                                 |

| D3Data bit 325No pinD2Data bit 226No pin(T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Chip select control line                                                                                                                                                                                                                           |

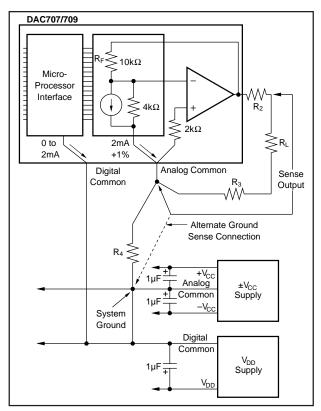

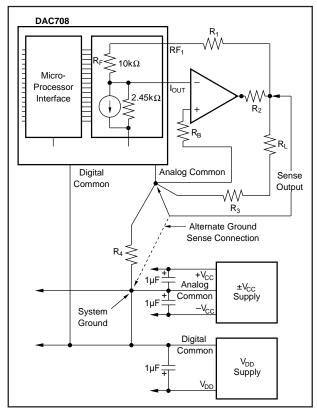

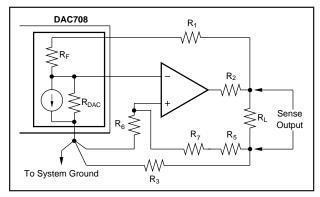

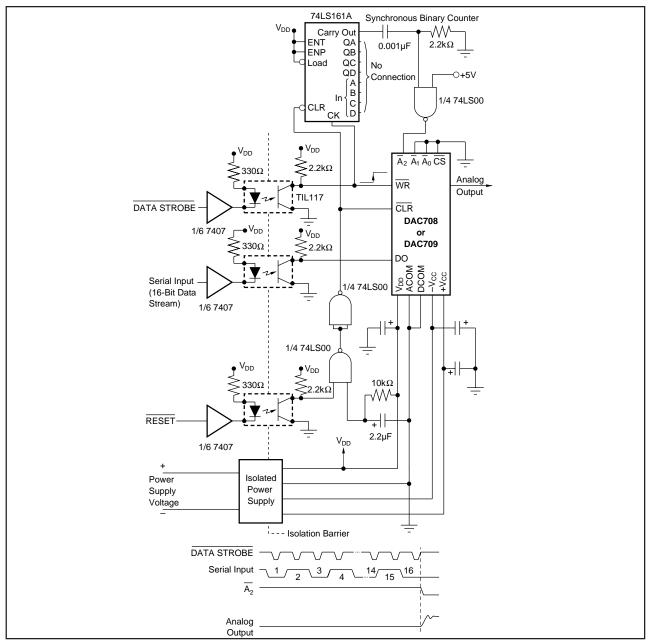

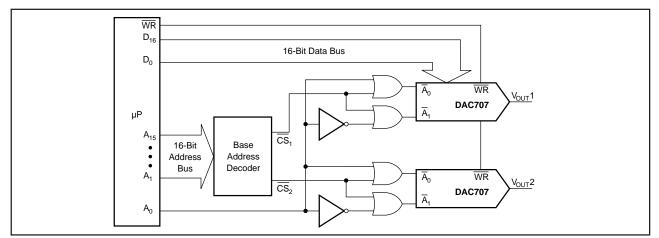

| D2 Data bit 2 26 No pin (T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Logic supply (+5V)                                                                                                                                                                                                                                 |