# 2.4 GHz IEEE 802.15.4 / ZigBee-ready RF Transceiver

## Applications

- 2.4 GHz IEEE 802.15.4 systems

- ZigBee systems

- Home/building automation

- Industrial Control

#### **Product Description**

The **CC2420** is a true single-chip 2.4 GHz IEEE 802.15.4 compliant RF transceiver designed for low power and low voltage wireless applications. **CC2420** includes a digital direct sequence spread spectrum baseband modem providing a spreading gain of 9 dB and an effective data rate of 250 kbps.

The **CC2420** is a low-cost, highly integrated solution for robust wireless communication in the 2.4 GHz unlicensed ISM band. It complies with worldwide regulations covered by ETSI EN 300 328 and EN 300 440 class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan).

The **CC2420** provides extensive hardware support for packet handling, data buffering, burst transmissions, data encryption, data authentication, clear channel assessment, link quality indication and packet timing information. These

## **Key Features**

- True single-chip 2.4 GHz IEEE 802.15.4 compliant RF transceiver with baseband modem and MAC support

- DSSS baseband modem with 2 MChips/s and 250 kbps effective data rate.

- Suitable for both RFD and FFD operation

- Low current consumption (RX: 18.8 mA, TX: 17.4 mA)

- Low supply voltage (2.1 3.6 V) with integrated voltage regulator

- Low supply voltage (1.6 2.0 V) with external voltage regulator

- Wireless sensor networks

- PC peripherals

- Consumer Electronics

features reduce the load on the host controller and allow *CC2420* to interface low-cost microcontrollers.

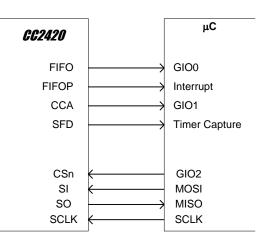

The configuration interface and transmit / receive FIFOs of *CC2420* are accessed via an SPI interface. In a typical application *CC2420* will be used together with a microcontroller and a few external passive components.

*CC2420* is based on Chipcon's SmartRF<sup>®</sup>-03 technology in 0.18  $\mu$ m CMOS.

- Programmable output power

- No external RF switch / filter needed

- I/Q low-IF receiver

- I/Q direct upconversion transmitter

- Very few external components

- 128(RX) + 128(TX) byte data buffering

- Digital RSSI / LQI support

- Hardware MAC encryption (AES-128)

- Battery monitor

- QLP-48 package, 7x7 mm

- Complies with ETSI EN 300 328, EN 300 440 class 2, FCC CFR-47 part 15 and ARIB STD-T66

- Powerful and flexible development tools available

# Table of contents

| 1  | Α                | bbreviations                                                        | 5  |

|----|------------------|---------------------------------------------------------------------|----|

| 2  | R                | eferences                                                           | 6  |

| 3  | Fe               | eatures                                                             | 7  |

| 4  |                  | bsolute Maximum Ratings                                             | 8  |

| 5  | 0                | perating Conditions                                                 | 8  |

| 6  |                  | lectrical Specifications                                            |    |

| Ŭ  | 6.1              | Overall                                                             |    |

|    | 6.2              | Transmit Section                                                    | 9  |

|    | 6.3              | Receive Section                                                     | 10 |

|    | 6.4              | RSSI / Carrier Sense                                                | 11 |

|    | 6.5              | IF Section                                                          |    |

|    | 6.6              | Frequency Synthesizer Section                                       | 11 |

|    | 6.7              | Digital Inputs/Outputs                                              | 12 |

|    | 6.8              | Voltage Regulator                                                   | 13 |

|    | 6.9              | Battery Monitor                                                     | 13 |

|    | 6.10             | Power Supply                                                        | 13 |

| 7  | Pi               | in Assignment                                                       | 15 |

| 8  |                  | ircuit Description                                                  |    |

| 9  |                  | pplication Circuit                                                  |    |

| 1  | 9.1              | Input / output matching                                             | 19 |

|    | 9.2              | Bias resistor                                                       |    |

|    | 9.3              | Crystal                                                             |    |

|    | 9.4              | Voltage regulator                                                   |    |

|    | 9.5              | Power supply decoupling and filtering                               |    |

| 1  |                  | IEEE 802.15.4 Modulation Format                                     |    |

| 1  | 1                | Configuration Overview                                              |    |

| 12 | 2                | Evaluation Software                                                 |    |

| 1. | _                |                                                                     |    |

| 1, | <b>5</b><br>13.1 | 4-wire Serial Configuration and Data Interface<br>Pin configuration |    |

|    | 13.1             |                                                                     |    |

|    | 13.2             | 6                                                                   |    |

|    | 13.4             | Command strobes                                                     | 20 |

|    | 13.5             |                                                                     |    |

|    | 13.6             |                                                                     |    |

|    | 13.7             | Multiple SPI access                                                 | 31 |

| 14 | 4                | Microcontroller Interface and Pin Description                       | 32 |

|    | 14.1             |                                                                     |    |

|    | 14.2             | -                                                                   |    |

|    | 14.3             | RXFIFO overflow                                                     | 33 |

|    | 14.4             |                                                                     | 34 |

|    | 14.5             | General control and status pins                                     | 35 |

| 1  | 5                | Demodulator, Symbol Synchroniser and Data Decision                  | 35 |

| 1  | 6                | Frame Format                                                        |    |

|    | 16.1             |                                                                     | 36 |

|    | 16.2             | Length field                                                        | 37 |

|    | 16.3             | L                                                                   |    |

|    | 16.4             | Frame check sequence                                                | 38 |

#### Chipcon Products from Texas Instruments

| 17           | RF Data Buffering                                       | 39                           |

|--------------|---------------------------------------------------------|------------------------------|

| 17.1         |                                                         | 39                           |

| 17.2         | Buffered receive mode                                   | 39                           |

| 17.3         | Unbuffered, serial mode                                 | 40                           |

| 18           | Address Recognition                                     | 41                           |

| 19           | Acknowledge Frames                                      | 41                           |

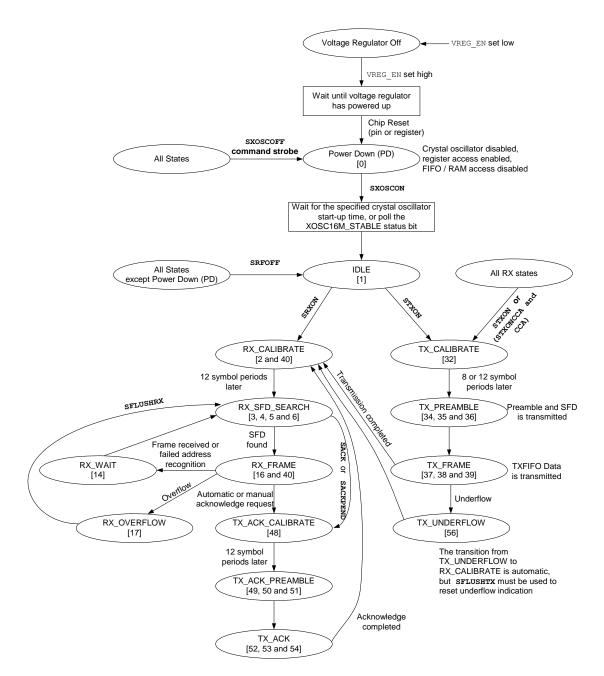

| 20           | Radio control state machine                             | 43                           |

| 21           | MAC Security Operations (Encryption and Authentication) | 45                           |

| 21.1         |                                                         |                              |

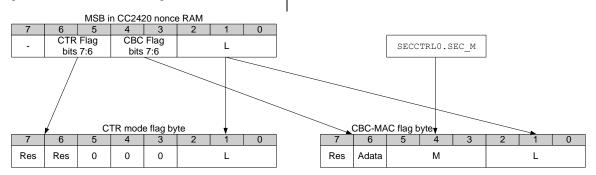

| 21.2         | Nonce / counter                                         | 45                           |

| 21.3         | 71                                                      | 46                           |

| 21.4         | J I                                                     | 46                           |

| 21.5<br>21.6 |                                                         | 47<br>47                     |

| 21.0         |                                                         | 47                           |

| 21.7         |                                                         | 47                           |

| 21.0         | Linear IF and AGC Settings                              |                              |

| 22           |                                                         |                              |

| -            | RSSI / Energy Detection                                 |                              |

| 24           | Link Quality Indication                                 |                              |

| 25           | Clear Channel Assessment                                |                              |

| 26           | Frequency and Channel Programming                       | 50                           |

| 27           | VCO and PLL Self-Calibration                            |                              |

| 27.1         |                                                         |                              |

| 27.2         | PLL self-calibration                                    | 51                           |

| 28           | Output Power Programming                                | 51                           |

| 29           | Voltage Regulator                                       | 51                           |

| 30           | Battery Monitor                                         | 52                           |

| 31           | Crystal Oscillator                                      | 53                           |

| 32           | Input / Output Matching                                 | 54                           |

| 33           | Transmitter Test Modes                                  | 55                           |

| 33.1         | Unmodulated carrier                                     |                              |

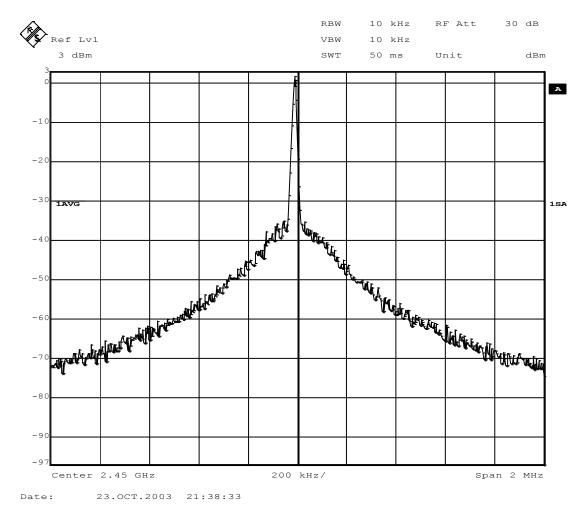

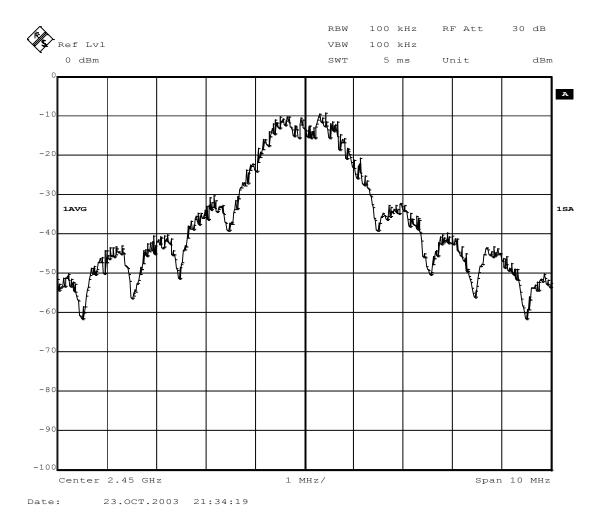

| 33.2         | Modulated spectrum                                      | 56                           |

| 34           | System Considerations and Guidelines                    | 57                           |

| 34.1         | Frequency hopping and multi-channel systems             | 57                           |

| 34.2         |                                                         |                              |

| 34.3         | J J                                                     |                              |

| 34.4         |                                                         |                              |

| 34.5         | · · · · · · · · · · · · · · · · · · ·                   |                              |

| 34.6<br>34.7 | · · · · · · · · · · · · · · · · · · ·                   |                              |

| 34.8         |                                                         |                              |

| 35           | PCB Layout Recommendations                              |                              |

| 36           | Antenna Considerations                                  |                              |

| 30<br>37     |                                                         |                              |

| -            | Configuration Registers                                 |                              |

| 38           | Test Output Signals                                     |                              |

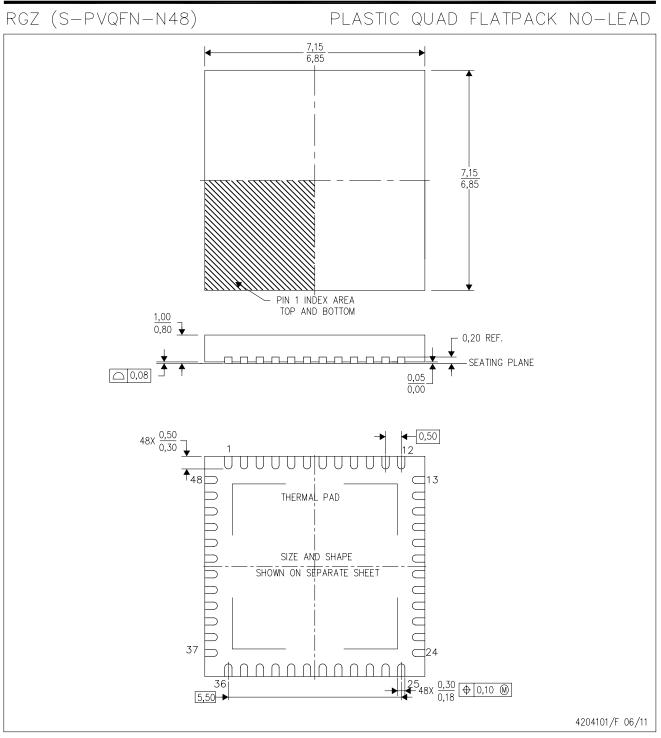

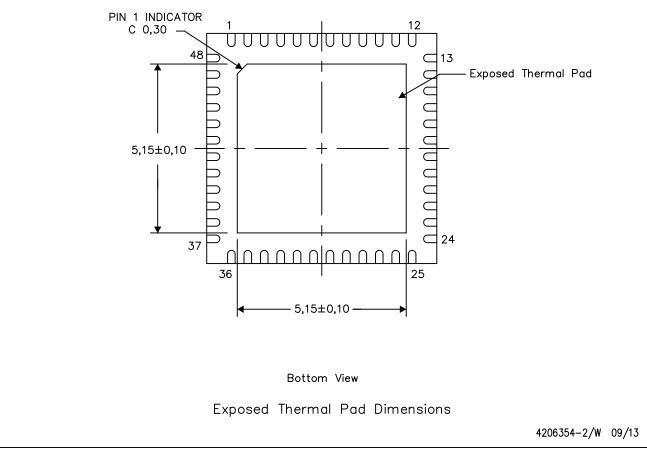

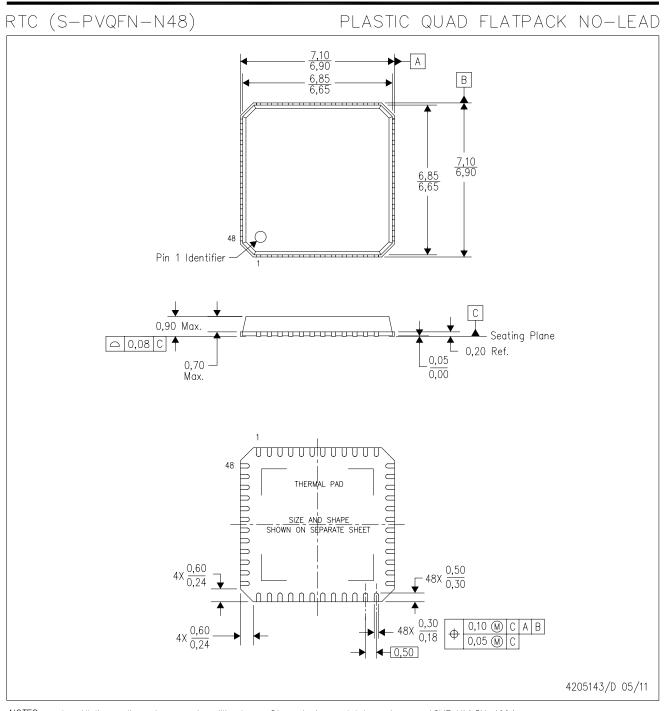

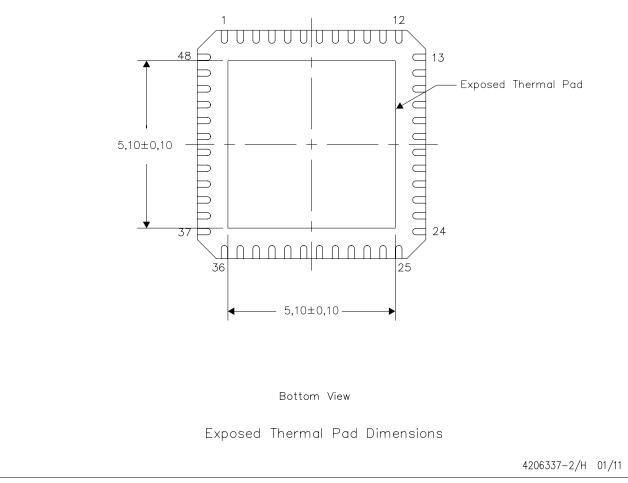

| 39           | Package Description (QLP 48)                            |                              |

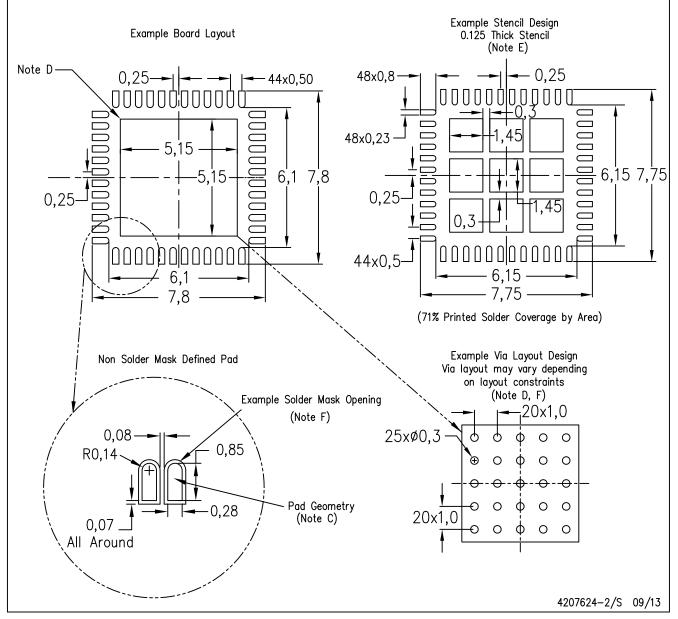

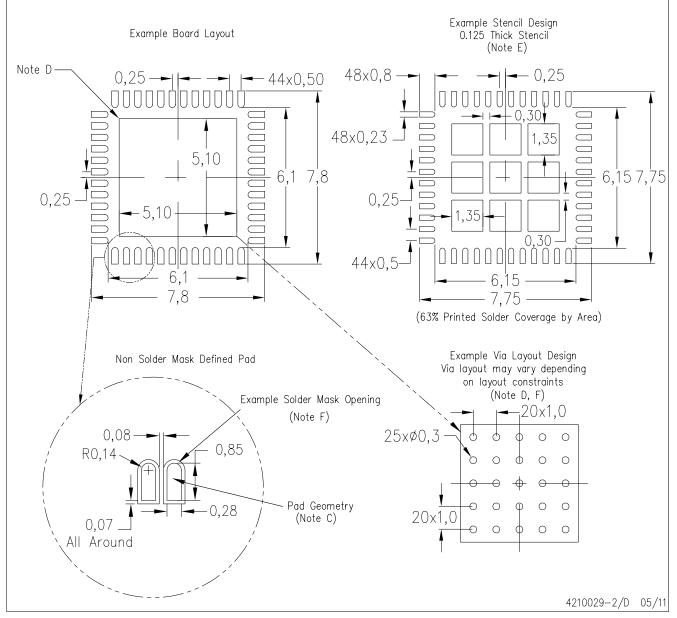

| 40           | Recommended layout for package (QLP 48)                 | Error! Bookmark not defined. |

#### Chipcon Products from Texas Instruments

| 40.1   | Package thermal properties          | Error! Bookmark not defined. |

|--------|-------------------------------------|------------------------------|

| 40.2   | Soldering information               | 83                           |

| 40.3   | Plastic tube specification          |                              |

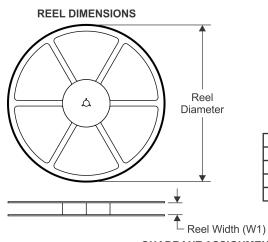

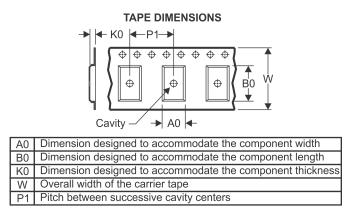

| 40.4   | Carrier tape and reel specification | Error! Bookmark not defined. |

| 41     | Ordering Information                | Error! Bookmark not defined. |

|        | General Information                 |                              |

| 42.1   | Document History                    |                              |

|        | Product Status Definitions          |                              |

| 43     | Address Information                 | Error! Bookmark not defined. |

| 44 '   | TI Worldwide Technical Support      | Error! Bookmark not defined. |

| Import | ant Notice                          | Error! Bookmark not defined. |

## 1 Abbreviations

|         |   | Angles to Disital Convertor                               |

|---------|---|-----------------------------------------------------------|

| ADC     | - | Analog to Digital Converter                               |

| AES     | - | Advanced Encryption Standard                              |

| AGC     | - | Automatic Gain Control                                    |

| ARIB    | - | Association of Radio Industries and Businesses            |

| BER     | - | Bit Error Rate                                            |

| CBC-MAC | - | Cipher Block Chaining Message Authentication Code         |

| CCA     | - | Clear Channel Assessment                                  |

| CCM     | - | Counter mode + CBC-MAC                                    |

| CFR     | - | Code of Federal Regulations                               |

| CSMA-CA | - | Carrier Sense Multiple Access with Collision Avoidance    |

| CTR     | - | Counter mode (encryption)                                 |

| CW      | - | Continuous Wave                                           |

| DAC     | - | Digital to Analog Converter                               |

| DSSS    | - | Direct Sequence Spread Spectrum                           |

| ESD     | - | Electro Static Discharge                                  |

| ESR     | - | Equivalent Series Resistance                              |

| EVM     | - | Error Vector Magnitude                                    |

| FCC     | - | Federal Communications Commission                         |

| FCF     | - | Frame Control Field                                       |

| FIFO    | - | First In First Out                                        |

| FFCTRL  | - | FIFO and Frame Control                                    |

| HSSD    | - | High Speed Serial Debug                                   |

| IEEE    | - | Institute of Electrical and Electronics Engineers         |

| IF      | - | Intermediate Frequency                                    |

| ISM     | - | Industrial, Scientific and Medical                        |

| ITU-T   | - | International Telecommunication Union – Telecommunication |

|         |   | Standardization Sector                                    |

| I/O     | _ | Input / Output                                            |

| I/Q     | _ | In-phase / Quadrature-phase                               |

| kbps    | _ | kilo bits per second                                      |

| LNA     | _ | Low-Noise Amplifier                                       |

| LO      | _ | Local Oscillator                                          |

| LQI     | - | Link Quality Indication                                   |

| LSB     | - | Least Significant Bit / Byte                              |

| MAC     | - | Medium Access Control                                     |

| MAC     | - | MAC Footer                                                |

|         | - |                                                           |

| MHR     | - | MAC Header                                                |

| MIC     | - | Message Integrity Code                                    |

| MPDU    | - | MAC Protocol Data Unit                                    |

| MSDU    | - | MAC Service Data Unit                                     |

| NA      | - | Not Available                                             |

| NC      | - | Not Connected                                             |

| O-QPSK  | - | Offset - Quadrature Phase Shift Keying                    |

| PA      | - | Power Amplifier                                           |

| PCB     | - | Printed Circuit Board                                     |

| PER     | - | Packet Error Rate                                         |

| PHY     | - | Physical Layer                                            |

| PHR     | - | PHY Header                                                |

| PLL     | - | Phase Locked Loop                                         |

| PSDU    | - | PHY Service Data Unit                                     |

| QLP     | - | Quad Leadless Package                                     |

| RAM     | - | Random Access Memory                                      |

| RBW     | - | Resolution BandWidth                                      |

| RF      | - | Radio Frequency                                           |

| RSSI    | - | Receive Signal Strength Indicator                         |

|         |   |                                                           |

#### Chipcon Products from Texas Instruments

| RX  | - | Receive                       |

|-----|---|-------------------------------|

| SHR | - | Synchronisation Header        |

| SPI | - | Serial Peripheral Interface   |

| TBD | - | To Be Decided / To Be Defined |

| T/R | - | Transmit / Receive            |

| ТХ  | - | Transmit                      |

| VCO | - | Voltage Controlled Oscillator |

| VGA | - | Variable Gain Amplifier       |

### 2 References

[1] IEEE std. 802.15.4 - 2003: Wireless Medium Access Control (MAC) and Physical Layer (PHY) specifications for Low Rate Wireless Personal Area Networks (LR-WPANs)

http://standards.ieee.org/getieee802/download/802.15.4-2003.pdf

[2] NIST FIPS Pub 197: Advanced Encryption Standard (AES), Federal Information Processing Standards Publication 197, US Department of Commerce/N.I.S.T., November 26, 2001. Available from the NIST website.

http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf

[3] R. Housley, D. Whiting, N. Ferguson, Counter with CBC-MAC (CCM), submitted to NIST, June 3, 2002. Available from the NIST website.

http://csrc.nist.gov/CryptoToolkit/modes/proposedmodes/ProposedModesPag e.html

## 3 Features

- 2400 2483.5 MHz RF Transceiver

- Direct Sequence Spread Spectrum (DSSS) transceiver

- 250 kbps data rate, 2 MChip/s chip rate

- O-QPSK with half sine pulse shaping modulation

- Very low current consumption (RX: 18.8 mA, TX: 17.4 mA)

- High sensitivity (-95 dBm)

- High adjacent channel rejection (30/45 dB)

- High alternate channel rejection (53/54 dB)

- On-chip VCO, LNA and PA

- Low supply voltage (2.1 3.6 V) with on-chip voltage regulator

- Programmable output power

- I/Q low-IF soft decision receiver

- I/Q direct up-conversion transmitter

- Separate transmit and receive FIFOs

- 128 byte transmit data FIFO

- 128 byte receive data FIFO

- Very few external components

- Only reference crystal and a minimised number of passives

- No external filters needed

- Easy configuration interface

- 4-wire SPI interface

- Serial clock up to 10 MHz

- 802.15.4 MAC hardware support:

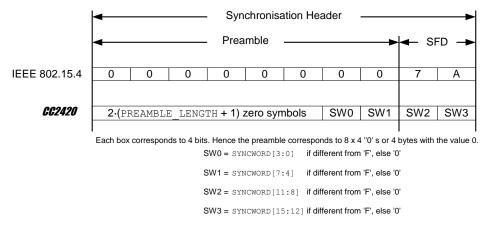

- Automatic preamble generator

- Synchronisation word insertion/detection

- CRC-16 computation and checking over the MAC payload

- Clear Channel Assessment

- Energy detection / digital RSSI

- Link Quality Indication

- Full automatic MAC security (CTR, CBC-MAC, CCM)

- 802.15.4 MAC hardware security:

- Automated security operations within the receive and transmit FIFOs.

- CTR mode encryption / decryption

- CBC-MAC authentication

- CCM encryption / decryption and authentication

- Stand-alone AES encryption

- Development tools available

- Fully equipped development kit

- Demonstration board reference design with microcontroller code

- Easy-to-use software for generating the **CC2420** configuration data

- Small size QLP-48 package, 7 x 7 mm

- Complies with EN 300 328, EN 300 440 class 2, FCC CFR47 part 15 and ARIB STD-T66

## 4 Absolute Maximum Ratings

| Parameter                                                                                                               | Min. | Max.               | Units | Condition |

|-------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------|

| Supply voltage for on-chip voltage regulator,<br>VREG_IN pin 43.                                                        | -0.3 | 3.6                | V     |           |

| Supply voltage (VDDIO) for digital I/Os, DVDD3.3, pin 25.                                                               | -0.3 | 3.6                | V     |           |

| Supply voltage (VDD) on AVDD_VCO, DVDD1.8,<br>etc (pin no 1, 2, 3, 4, 10, 14, 15, 17, 18, 20, 26, 35,<br>37, 44 and 48) | -0.3 | 2.0                | V     |           |

| Voltage on any digital I/O pin, (pin no. 21, 27-34 and 41)                                                              | -0.3 | VDDIO+0.3, max 3.6 | V     |           |

| Voltage on any other pin, (pin no. 6, 7, 8, 11, 12, 13, 16, 36, 38, 39, 40, 45, 46 and 47)                              | -0.3 | VDD+0.3, max 2.0   | V     |           |

| Input RF level                                                                                                          |      | 10                 | dBm   |           |

| Storage temperature range                                                                                               | -50  | 150                | °C    |           |

| Reflow solder temperature                                                                                               |      | 260                | °C    | T = 10 s  |

The absolute maximum ratings given above should under no circumstances be violated. Stress exceeding one or more of the limiting values may cause permanent damage to the device.

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

# 5 Operating Conditions

| Parameter                                                                                                               | Min. | Тур. | Max. | Units | Condition                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------|

| Supply voltage for on-chip voltage regulator,<br>VREG_IN pin 43.                                                        | 2.1  |      | 3.6  | V     |                                                                                                                 |

| Supply voltage (VDDIO) for digital I/Os, DVDD3.3, pin 25.                                                               | 1.6  |      | 3.6  | V     | The digital I/O voltage (DVDD3.3 pin)<br>must match the external interfacing<br>circuit (e.g. microcontroller). |

| Supply voltage (VDD) on AVDD_VCO, DVDD1.8,<br>etc (pin no 1, 2, 3, 4, 10, 14, 15, 17, 18, 20, 26, 35,<br>37, 44 and 48) | 1.6  | 1.8  | 2.0  | V     | The typical application uses regulated<br>1.8 V supply generated by the on-chip<br>voltage regulator.           |

| Operating ambient temperature range, T <sub>A</sub>                                                                     | -40  |      | 85   | °C    |                                                                                                                 |

# 6 Electrical Specifications

Measured on **CC2420** EM with transmission line balun,  $T_A = 25$  °C, DVDD3.3 and VREG\_IN = 3.3 V, internal voltage regulator used if nothing else stated.

#### 6.1 Overall

| Parameter          | Min. | Тур. | Max.   | Unit | Condition / Note                                                       |

|--------------------|------|------|--------|------|------------------------------------------------------------------------|

| RF Frequency Range | 2400 |      | 2483.5 | MHz  | Programmable in 1 MHz steps, 5<br>MHz steps for compliance with<br>[1] |

#### 6.2 Transmit Section

| Parameter                                                                             | Min. | Тур.                     | Max. | Unit                     | Condition / Note                                                                                                                                                             |

|---------------------------------------------------------------------------------------|------|--------------------------|------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit bit rate                                                                     | 250  |                          | 250  | kbps                     | As defined by [1]                                                                                                                                                            |

| Transmit chip rate                                                                    | 2000 |                          | 2000 | kChips/s                 | As defined by [1]                                                                                                                                                            |

| Nominal output power                                                                  | -3   | 0                        |      | dBm                      | Delivered to a single ended 50 $\Omega$<br>load through a balun.<br>[1] requires minimum –3 dBm                                                                              |

| Programmable output power range                                                       |      | 24                       |      | dB                       | The output power is<br>programmable in 8 steps from<br>approximately –24 to 0 dBm.                                                                                           |

| Harmonics<br>2 <sup>nd</sup> harmonic<br>3 <sup>rd</sup> harmonic                     |      | -44<br>-64               |      | dBm<br>dBm               | Measured conducted with 1 MHz resolution bandwidth on spectrum analyser. At max output power delivered to a single ended 50 $\Omega$ load through a balun. See page 54.      |

| Spurious emission<br>30 - 1000 MHz<br>1– 12.75 GHz<br>1.8 – 1.9 GHz<br>5.15 – 5.3 GHz |      | -56<br>-44<br>-56<br>-51 |      | dBm<br>dBm<br>dBm<br>dBm | Maximum output power.<br>Complies with EN 300 328, EN<br>300 440, FCC CFR47 Part 15<br>and ARIB STD-T-66                                                                     |

| Error Vector Magnitude (EVM)                                                          |      | 11                       |      | %                        | Measured as defined by [1]<br>[1] requires max. 35 %                                                                                                                         |

| Optimum load impedance                                                                |      | 95<br>+ j187             |      | Ω                        | Differential impedance as seen<br>from the RF-port (RF_P and<br>RF_N) towards the antenna. For<br>matching details see the Input /<br>Output Matching section on page<br>54. |

#### 6.3 Receive Section

| Parameter                                                                                                       | Min. | Тур.                     | Max. | Unit                     | Condition / Note                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------|------|--------------------------|------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver Sensitivity                                                                                            |      |                          |      |                          |                                                                                                                                                                                |

|                                                                                                                 | -90  | -95                      |      | dBm                      | PER = 1%, as specified by [1]                                                                                                                                                  |

|                                                                                                                 |      |                          |      |                          | Measured in a $50\Omega$ single-ended load through a balun.                                                                                                                    |

|                                                                                                                 |      |                          |      |                          | [1] requires –85 dBm                                                                                                                                                           |

| Saturation (maximum input level)                                                                                | 0    | 10                       |      | dBm                      | PER = 1%, as specified by [1]                                                                                                                                                  |

|                                                                                                                 |      |                          |      |                          | Measured in a $50\Omega$ single–ended load through a balun.                                                                                                                    |

|                                                                                                                 |      |                          |      |                          | [1] requires –20 dBm                                                                                                                                                           |

| Adjacent channel rejection<br>+ 5 MHz channel spacing                                                           |      | 45                       |      | dB                       | Wanted signal @ -82 dBm,<br>adjacent modulated channel at<br>+5 MHz, PER = 1 %, as specified<br>by [1].                                                                        |

|                                                                                                                 |      |                          |      |                          | [1] requires 0 dB                                                                                                                                                              |

| Adjacent channel rejection<br>- 5 MHz channel spacing                                                           |      | 30                       |      | dB                       | Wanted signal @ -82 dBm,<br>adjacent modulated channel at<br>-5 MHz, PER = 1 %, as specified<br>by [1].                                                                        |

|                                                                                                                 |      |                          |      |                          | [1] requires 0 dB                                                                                                                                                              |

| Alternate channel rejection<br>+ 10 MHz channel spacing                                                         |      | 54                       |      | dB                       | Wanted signal @ -82 dBm,<br>adjacent modulated channel at<br>+10 MHz, PER = 1 %, as<br>specified by [1]                                                                        |

|                                                                                                                 |      |                          |      |                          | [1] requires 30 dB                                                                                                                                                             |

| Alternate channel rejection - 10 MHz channel spacing                                                            |      | 53                       |      | dB                       | Wanted signal @ -82 dBm,<br>adjacent modulated channel at<br>-10 MHz, PER = 1 %, as<br>specified by [1]                                                                        |

|                                                                                                                 |      |                          |      |                          | [1] requires 30 dB                                                                                                                                                             |

| Channel rejection<br>≥ + 15 MHz<br>≤ - 15 MHz                                                                   |      | 62<br>62                 |      | dB<br>dB                 | Wanted signal @ -82 dBm.<br>Undesired signal is an IEEE<br>802.15.4 modulated channel,<br>stepped through all channels<br>from 2405 to 2480 MHz. Signal<br>level for PER = 1%. |

| Co-channel rejection                                                                                            |      | -3                       |      | dB                       | Wanted signal @ -82 dBm.<br>Undesired signal is an IEEE<br>802.15.4 modulated at the same<br>frequency as the desired signal.<br>Signal level for PER = 1%.                    |

| Blocking / Desensitisation                                                                                      |      |                          |      |                          |                                                                                                                                                                                |

| +/- 5 MHz from band edge<br>+/- 20 MHz from band edge<br>+/- 30 MHz from band edge<br>+/- 50 MHz from band edge |      | -28<br>-28<br>-27<br>-28 |      | dBm<br>dBm<br>dBm<br>dBm | Wanted signal 3 dB above the<br>sensitivity level, CW jammer,<br>PER = 1%. Complies with EN<br>300 440 class 2.                                                                |

| Spurious emission                                                                                               |      | 1                        |      |                          |                                                                                                                                                                                |

| 30 – 1000 MHz<br>1 – 12.75 GHz                                                                                  |      | -73<br>-58               |      | dBm<br>dBm               | Conducted measurement in a 50 $\Omega$ single ended load. Measured according to EN 300 328, EN 300 440 class 2, FCC CFR47, Part 15 and ARIB STD-T-66                           |

| Parameter                   | Min. | Тур. | Max. | Unit | Condition / Note                                                                                                                                                                        |

|-----------------------------|------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency error tolerance   | -300 |      | 300  | kHz  | Difference between centre<br>frequency of the received RF<br>signal and local oscillator<br>frequency<br>[1] requires 200 kHz                                                           |

| Symbol rate error tolerance |      |      | 120  | ppm  | Difference between incoming<br>symbol rate and the internally<br>generated symbol rate<br>[1] requires 80 ppm                                                                           |

| Data latency                |      | 3    |      | μs   | Processing delay in receiver.<br>Time from complete transmission<br>of SFD until complete reception<br>of SFD, i.e. from SFD goes<br>active on transmitter until active<br>on receiver. |

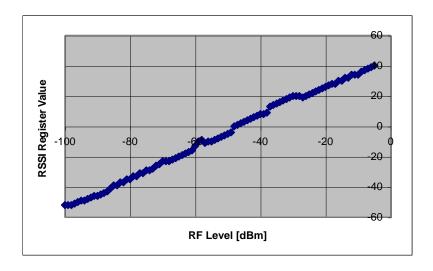

#### 6.4 RSSI / Carrier Sense

| Parameter           | Min. | Тур.    | Max. | Unit | Condition / Note                                     |

|---------------------|------|---------|------|------|------------------------------------------------------|

| Carrier sense level |      | - 77    |      | dBm  | Programmable in<br>RSSI.CCA_THR                      |

| RSSI dynamic range  |      | 100     |      | dB   | The range is approximately from<br>–100 dBm to 0 dBm |

| RSSI accuracy       |      | ± 6     |      | dB   | See page 48 for details                              |

| RSSI linearity      |      | $\pm 3$ |      | dB   |                                                      |

| RSSI average time   |      | 128     |      | μs   | 8 symbol periods, as specified by [1]                |

#### 6.5 IF Section

| Parameter                   | Min. | Тур. | Max. | Unit | Condition / Note |

|-----------------------------|------|------|------|------|------------------|

| Intermediate frequency (IF) |      | 2    |      | MHz  |                  |

|                             |      |      |      |      |                  |

#### 6.6 Frequency Synthesizer Section

| Parameter                              | Min. | Тур.     | Max. | Unit | Condition / Note                                                |

|----------------------------------------|------|----------|------|------|-----------------------------------------------------------------|

| Crystal oscillator frequency           |      | 16       |      | MHz  | See page 53 for details.                                        |

| Crystal frequency accuracy requirement | - 40 |          | 40   | ppm  | Including aging and temperature dependency, as specified by [1] |

| Crystal operation                      |      | Parallel |      |      | C381 and C391 are loading capacitors, see page 53               |

| Parameter                        | Min. | Тур.                         | Max. | Unit                                 | Condition / Note                                                                                                                                        |

|----------------------------------|------|------------------------------|------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal load capacitance         | 12   | 16                           | 20   | pF                                   | 16 pF recommended                                                                                                                                       |

| Crystal ESR                      |      |                              | 60   | Ω                                    |                                                                                                                                                         |

| Crystal oscillator start-up time |      | 1.0                          |      | ms                                   | 16 pF load                                                                                                                                              |

| Phase noise                      |      | -109<br>-117<br>-117<br>-117 |      | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz | Unmodulated carrier<br>At ±1 MHz offset from carrier<br>At ±2 MHz offset from carrier<br>At ±3 MHz offset from carrier<br>At ±5 MHz offset from carrier |

| PLL loop bandwidth               |      | 100                          |      | kHz                                  |                                                                                                                                                         |

| PLL lock time                    |      |                              | 192  | μs                                   | The startup time from the crystal oscillator is running and RX / TX turnaround time                                                                     |

## 6.7 Digital Inputs/Outputs

| Parameter                                                            | Min.         | Тур. | Max.         | Unit | Condition / Note                                                                          |

|----------------------------------------------------------------------|--------------|------|--------------|------|-------------------------------------------------------------------------------------------|

| General                                                              |              |      |              |      | Signal levels are referred to the voltage level at pin DVDD3.3                            |

| Logic "0" input voltage                                              | 0            |      | 0.3*<br>DVDD | V    |                                                                                           |

| Logic "1" input voltage                                              | 0.7*<br>DVDD |      | DVDD         | V    |                                                                                           |

| Logic "0" output voltage                                             | 0            |      | 0.4          | V    | Output current -8 mA,<br>3.3 V supply voltage                                             |

| Logic "1" output voltage                                             | 2.5          |      | VDD          | V    | Output current 8 mA,<br>3.3 V supply voltage                                              |

| Logic "0" input current                                              | NA           |      | -1           | μΑ   | Input signal equals GND                                                                   |

| Logic "1" input current                                              | NA           |      | 1            | μA   | Input signal equals VDD                                                                   |

| FIFO setup time                                                      | 20           |      |              | ns   | TX unbuffered mode, minimum time FIFO must be ready before the positive edge of FIFOP     |

| FIFO hold time                                                       | 10           |      |              | ns   | TX unbuffered mode, minimum<br>time FIFO must be held after the<br>positive edge of FIFOP |

| Serial interface pins (SCLK, SI, SO<br>and CSn) timing specification |              |      |              |      | See Table 4 on page 28                                                                    |

## 6.8 Voltage Regulator

| Parameter         | Min. | Тур. | Max. | Unit | Condition / Note                                                                                             |  |

|-------------------|------|------|------|------|--------------------------------------------------------------------------------------------------------------|--|

| General           |      |      |      |      | Note that the internal voltage regulator can only supply CC2420 and no external circuitry.                   |  |

| Input Voltage     | 2.1  | 3.0  | 3.6  | V    | On the VREG_IN pin                                                                                           |  |

| Output Voltage    | 1.7  | 1.8  | 1.9  | V    | On the VREG_OUT pin                                                                                          |  |

| Quiescent current | 13   | 20   | 29   | μΑ   | No current drawn from the<br>VREG_OUT pin. Min and max<br>numbers include 2.1 through 3.6<br>V input voltage |  |

| Start-up time     |      | 0.3  | 0.6  | ms   |                                                                                                              |  |

## 6.9 Battery Monitor

| Parameter           | Min. | Тур. | Max. | Unit | Condition / Note                                       |

|---------------------|------|------|------|------|--------------------------------------------------------|

| Current consumption | 6    | 30   | 90   | μA   | When enabled                                           |

| Start-up time       |      |      | 100  | μs   | Voltage regulator already enabled                      |

| Settling time       |      |      | 2    | μs   | New toggle voltage programmed                          |

| Step size           |      |      | 50   | mV   |                                                        |

| Hysteresis          |      |      | 10   | mV   |                                                        |

| Absolute accuracy   | -80  |      | 80   | mV   | May be software calibrated for known reference voltage |

| Relative accuracy   | -50  |      | 50   | mV   |                                                        |

#### 6.10 Power Supply

| Parameter                                                               | Min. | Тур.              | Max. | Unit           | Condition / Note                                                                                       |

|-------------------------------------------------------------------------|------|-------------------|------|----------------|--------------------------------------------------------------------------------------------------------|

| Current consumption in different modes (see Figure 25, page 44)         |      |                   |      |                | Current drawn from VREG_IN, through voltage regulator                                                  |

| Voltage regulator off (OFF)<br>Power Down mode (PD)<br>Idle mode (IDLE) |      | 0.02<br>20<br>426 | 1    | μΑ<br>μΑ<br>μΑ | Voltage regulator off<br>Voltage regulator on<br>Including crystal oscillator and<br>voltage regulator |

| Current Consumption, receive mode                                       |      | 18.8              |      | mA             |                                                                                                        |

| Parameter                                                            | Min. | Тур.                           | Max. | Unit                 | Condition / Note                                                                                                    |

|----------------------------------------------------------------------|------|--------------------------------|------|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Current Consumption, transmit mode:                                  |      |                                |      |                      |                                                                                                                     |

| P = -25 dBm<br>P = -15 dBm<br>P = -10 dBm<br>P = -5 dBm<br>P = 0 dBm |      | 8.5<br>9.9<br>11<br>14<br>17.4 |      | mA<br>mA<br>mA<br>mA | The output power is delivered differentially to a 50 $\Omega$ singled ended load through a balun, see also page 54. |

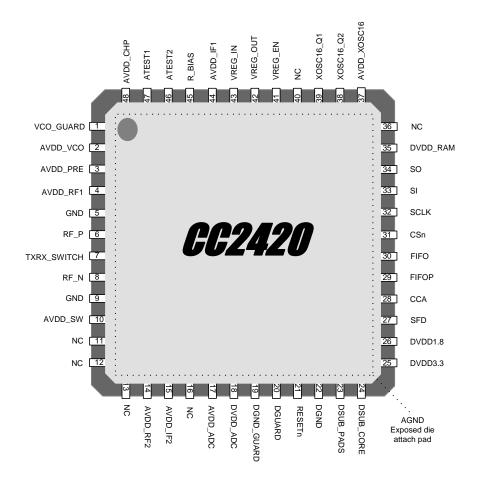

## 7 Pin Assignment

| Figure 1. | CC2420 | Pinout - | Тор | View |

|-----------|--------|----------|-----|------|

|-----------|--------|----------|-----|------|

| Pin | Pin Name    | Pin type        | Pin Description                                                                                                             |

|-----|-------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

| -   | AGND        | Ground (analog) | Exposed die attach pad. Must be connected to solid ground<br>plane                                                          |

| 1   | VCO_GUARD   | Power (analog)  | Connection of guard ring for VCO (to AVDD) shielding                                                                        |

| 2   | AVDD_VCO    | Power (analog)  | 1.8 V Power supply for VCO                                                                                                  |

| 3   | AVDD_PRE    | Power (analog)  | 1.8 V Power supply for Prescaler                                                                                            |

| 4   | AVDD_RF1    | Power (analog)  | 1.8 V Power supply for RF front-end                                                                                         |

| 5   | GND         | Ground (analog) | Grounded pin for RF shielding                                                                                               |

| 6   | RF_P        | RF I/O          | Positive RF input/output signal to LNA/from PA in<br>receive/transmit mode                                                  |

| 7   | TXRX_SWITCH | Power (analog)  | Common supply connection for integrated RF front-end. Must<br>be connected to RF_P and RF_N externally through a DC<br>path |

| 8   | RF_N        | RF I/O          | Negative RF input/output signal to LNA/from PA in<br>receive/transmit mode                                                  |

| 9   | GND         | Ground (analog) | Grounded pin for RF shielding                                                                                               |

| 10  | AVDD_SW     | Power (analog)  | 1.8 V Power supply for LNA / PA switch                                                                                      |

| 11  | NC          | -               | Not Connected                                                                                                               |

| 12  | NC          | -               | Not Connected                                                                                                               |

| 13  | NC          | -               | Not Connected                                                                                                               |

| 14  | AVDD_RF2    | Power (analog)  | 1.8 V Power supply for receive and transmit mixers                                                                          |

| Pin | Pin Name    | Pin type         | Pin Description                                                                                                                             |

|-----|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | AVDD_IF2    | Power (analog)   | 1.8 V Power supply for transmit / receive IF chain                                                                                          |

| 16  | NC          | -                | Not Connected                                                                                                                               |

| 17  | AVDD_ADC    | Power (analog)   | 1.8 V Power supply for analog parts of ADCs and DACs                                                                                        |

| 18  | DVDD_ADC    | Power (digital)  | 1.8 V Power supply for digital parts of receive ADCs                                                                                        |

| 19  | DGND_GUARD  | Ground (digital) | Ground connection for digital noise isolation                                                                                               |

| 20  | DGUARD      | Power (digital)  | 1.8 V Power supply connection for digital noise isolation                                                                                   |

| 21  | RESETn      | Digital Input    | Asynchronous, active low digital reset                                                                                                      |

| 22  | DGND        | Ground (digital) | Ground connection for digital core and pads                                                                                                 |

| 23  | DSUB_PADS   | Ground (digital) | Substrate connection for digital pads                                                                                                       |

| 24  | DSUB_CORE   | Ground (digital) | Substrate connection for digital modules                                                                                                    |

| 25  | DVDD3.3     | Power (digital)  | 3.3 V Power supply for digital I/Os                                                                                                         |

| 26  | DVDD1.8     | Power (digital)  | 1.8 V Power supply for digital core                                                                                                         |

| 27  | SFD         | Digital output   | SFD (Start of Frame Delimiter) / digital mux output                                                                                         |

| 28  | CCA         | Digital output   | CCA (Clear Channel Assessment) / digital mux output                                                                                         |

| 29  | FIFOP       | Digital output   | Active when number of bytes in FIFO exceeds threshold / serial RF clock output in test mode                                                 |

| 30  | FIFO        | Digital I/O      | Active when data in FIFO /<br>serial RF data input / output in test mode                                                                    |

| 31  | CSn         | Digital input    | SPI Chip select, active low                                                                                                                 |

| 32  | SCLK        | Digital input    | SPI Clock input, up to 10 MHz                                                                                                               |

| 33  | SI          | Digital input    | SPI Slave Input. Sampled on the positive edge of SCLK                                                                                       |

| 34  | SO          | Digital output   | SPI Slave Output. Updated on the negative edge of SCLK.                                                                                     |

|     |             | (tristate)       | Tristate when CSn high.                                                                                                                     |

| 35  | DVDD_RAM    | Power (digital)  | 1.8 V Power supply for digital RAM                                                                                                          |

| 36  | NC          | -                | Not Connected                                                                                                                               |

| 37  | AVDD_XOSC16 | Power (analog)   | 1.8 V crystal oscillator power supply                                                                                                       |

| 38  | XOSC16_Q2   | Analog I/O       | 16 MHz Crystal oscillator pin 2                                                                                                             |

| 39  | XOSC16_Q1   | Analog I/O       | 16 MHz Crystal oscillator pin 1 or external clock input                                                                                     |

| 40  | NC          | -                | Not Connected                                                                                                                               |

| 41  | VREG_EN     | Digital input    | Voltage regulator enable, active high, held at VREG_IN<br>voltage level when active. Note that VREG_EN is relative<br>VREG_IN, not DVDD3.3. |

| 42  | VREG_OUT    | Power output     | Voltage regulator 1.8 V power supply output                                                                                                 |

| 43  | VREG_IN     | Power (analog)   | Voltage regulator 2.1 to 3.6 V power supply input                                                                                           |

| 44  | AVDD_IF1    | Power (analog)   | 1.8 V Power supply for transmit / receive IF chain                                                                                          |

| 45  | R_BIAS      | Analog output    | External precision resistor, 43 k $\Omega$ , ± 1 %                                                                                          |

| 46  | ATEST2      | Analog I/O       | Analog test I/O for prototype and production testing                                                                                        |

| 47  | ATEST1      | Analog I/O       | Analog test I/O for prototype and production testing                                                                                        |

| 48  | AVDD_CHP    | Power (analog)   | 1.8 V Power supply for phase detector and charge pump                                                                                       |

#### NOTES:

The exposed die attach pad **must** be connected to a solid ground plane as this is the main ground connection for the chip.

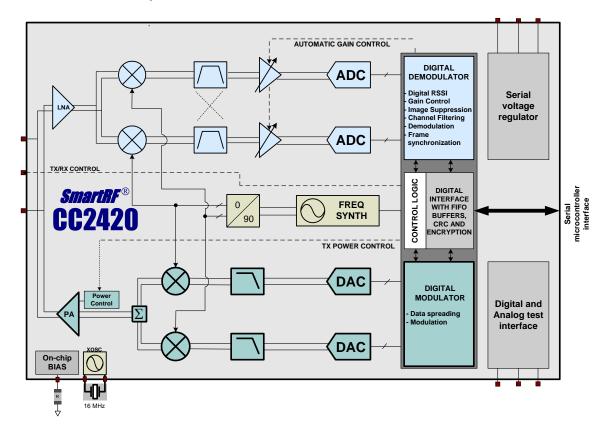

## 8 Circuit Description

Figure 2. CC2420 simplified block diagram

A simplified block diagram of **CC2420** is shown in Figure 2.

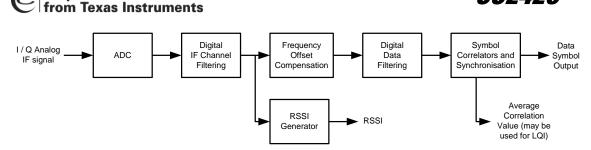

**CC2420** features a low-IF receiver. The received RF signal is amplified by the low-noise amplifier (LNA) and down-converted in quadrature (I and Q) to the intermediate frequency (IF). At IF (2 MHz), the complex I/Q signal is filtered and amplified, and then digitized by the ADCs. Automatic gain control, final channel filtering, despreading, symbol correlation and byte synchronisation are performed digitally.

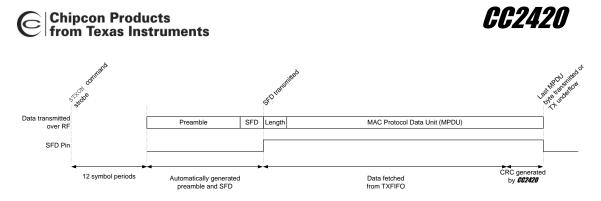

When the SFD pin goes active, this indicates that a start of frame delimiter has been detected. **CC2420** buffers the received data in a 128 byte receive FIFO. The user may read the FIFO through an SPI interface. CRC is verified in hardware. RSSI and correlation values are appended to the frame. CCA is available on a pin in receive mode. Serial (unbuffered) data modes are also available for test purposes.

The **CC2420** transmitter is based on direct up-conversion. The data is buffered in a 128 byte transmit FIFO (separate from the receive FIFO). The preamble and start of frame delimiter are generated by hardware. Each symbol (4 bits) is spread using the IEEE 802.15.4 spreading sequence to 32 chips and output to the digital-to-analog converters (DACs).

An analog low pass filter passes the signal to the quadrature (I and Q) upconversion mixers. The RF signal is amplified in the power amplifier (PA) and fed to the antenna.

The internal T/R switch circuitry makes the antenna interface and matching easy. The RF connection is differential. A balun may be used for single-ended antennas. The biasing of the PA and LNA is done by connecting TXRX\_SWITCH to RF\_P and RF\_N through an external DC path.

The frequency synthesizer includes a completely on-chip LC VCO and a 90

degrees phase splitter for generating the I and Q LO signals to the down-conversion mixers in receive mode and up-conversion mixers in transmit mode. The VCO operates in the frequency range 4800 – 4966 MHz, and the frequency is divided by two when split in I and Q.

A crystal must be connected to  $XOSC16_Q1$  and  $XOSC16_Q2$  and provides the reference frequency for the synthesizer. A digital lock signal is available from the PLL.

The digital baseband includes support for frame handling, address recognition, data buffering and MAC security.

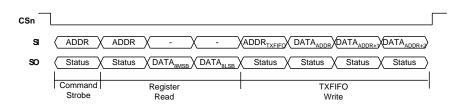

The 4-wire SPI serial interface is used for configuration and data buffering.

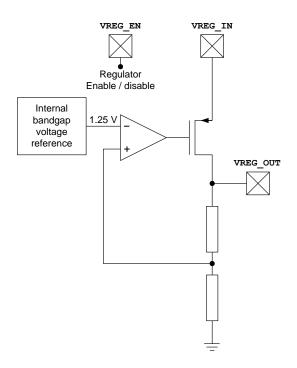

An on-chip voltage regulator delivers the regulated 1.8 V supply voltage. The voltage regulator may be enabled / disabled through a separate pin.

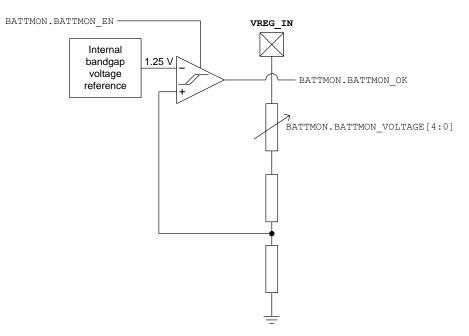

A battery monitor may optionally be used to monitor the unregulated power supply voltage. The battery monitor is configurable through the SPI interface.

## 9 Application Circuit

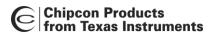

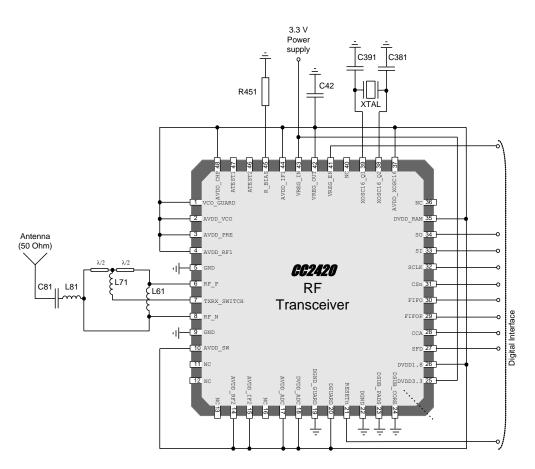

Few external components are required for the operation of **CC2420**. A typical application circuit is shown in Figure 4. The external components shown are described in Table 1 and typical values are given in Table 2. Note that most decoupling capacitors are not shown on the application circuits. For the complete reference design please refer to Texas Instrument's web site: http://www.ti.com.

#### 9.1 Input / output matching

The RF input/output is high impedance and differential. The optimum differential load for the RF port is  $95+j187 \Omega$ .

When using an unbalanced antenna such as a monopole, a balun should be used in order to optimise performance. The balun can be implemented using low-cost discrete inductors and capacitors only or in combination with transmission lines.

Figure 3 shows the balun implemented in a two-layer reference design. It consists of a half wave transmission line, C81, L61, L71 and L81. The circuit will present the optimum RF termination to **CC2420** with a 50  $\Omega$  load on the antenna connection. This circuit has improved EVM performance, sensitivity and harmonic suppression compared to the design in Figure 4. Please refer to the input/output matching section on page 54 for more details.

The balun in Figure 4 consists of C61, C62, C71, C81, L61, L62 and L81, and will present the optimum RF termination to **CC2420** with a 50  $\Omega$  load on the antenna connection. A low pass filter may be added to add margin to the FCC requirement on second harmonic level.

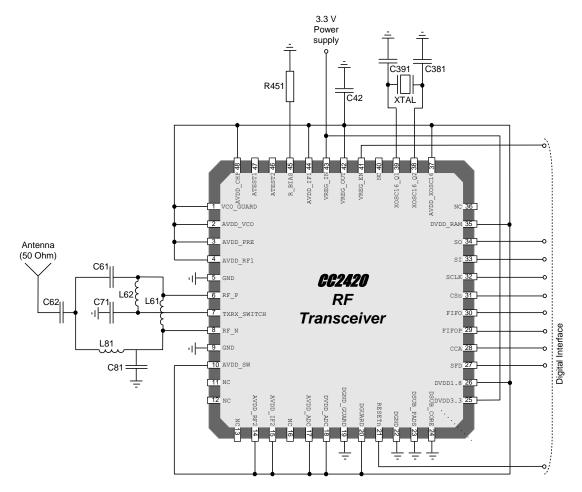

If a balanced antenna such as a folded dipole is used, the balun can be omitted. If the antenna also provides a DC path from the TXRX\_SWITCH pin to the RF pins, inductors are not needed for DC bias.

Figure 5 shows a suggested application circuit using a differential antenna. The antenna type is a standard folded dipole. The dipole has a virtual ground point; hence bias is provided without degradation in antenna performance.

#### 9.2 Bias resistor

The bias resistor R451 is used to set an accurate bias current.

#### 9.3 Crystal

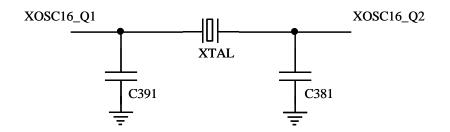

An external crystal with two loading capacitors (C381 and C391) is used for the crystal oscillator. See page 53 for details.

#### 9.4 Voltage regulator

The on chip voltage regulator supplies all 1.8 V power supply inputs. C42 is required for stability of the regulator. A series resistor may be used to comply with the ESR requirement.

# 9.5 Power supply decoupling and filtering

Proper power supply decoupling must be used for optimum performance. The placement and size of the decoupling capacitors and the power supply filtering are very important to achieve the best performance in an application. Texas Instruments provides a compact reference design that should be followed very closely..

#### Chipcon Products from Texas Instruments

| Ref  | Description                                        |

|------|----------------------------------------------------|

| C42  | Voltage regulator load capacitance                 |

| C61  | Balun and match                                    |

| C62  | DC block to antenna and match                      |

| C71  | Front-end bias decoupling and match                |

| C81  | Balun and match                                    |

| C381 | 16MHz crystal load capacitor, see page 53          |

| C391 | 16MHz crystal load capacitor, see page 53          |

| L61  | DC bias and match                                  |

| L62  | DC bias and match                                  |

| L71  | DC bias and match                                  |

| L81  | Balun and match                                    |

| R451 | Precision resistor for current reference generator |

| XTAL | 16MHz crystal, see page 53                         |

Figure 3. Typical application circuit with transmission line balun for single-ended operation

*CC2420*

Figure 4. Typical application circuit with discrete balun for single-ended operation

Figure 5. Suggested application circuit with differential antenna (folded dipole)

| ltem | Single ended output, transmission line balun               | Single ended output, discrete balun                        | Differential antenna                                            |  |  |  |  |

|------|------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| C42  | 10 μF, 0.5Ω < ESR < 5Ω                                     | 10 μF, 0.5Ω < ESR < 5Ω                                     | 10 μF, 0.5Ω < ESR < 5Ω                                          |  |  |  |  |

| C61  | Not used                                                   | 0.5 pF, +/- 0.25pF, NP0, 0402                              | Not used                                                        |  |  |  |  |

| C62  | Not used                                                   | 5.6 pF, +/- 0.25pF, NP0, 0402                              | Not used                                                        |  |  |  |  |

| C71  | Not used                                                   | 5.6 pF, 10%, X5R, 0402                                     | Not used                                                        |  |  |  |  |

| C81  | 5.6 pF, +/- 0.25pF, NP0, 0402                              | 0.5 pF, +/- 0.25pF, NP0, 0402                              | Not used                                                        |  |  |  |  |

| C381 | 27 pF, 5%, NP0, 0402                                       | 27 pF, 5%, NP0, 0402                                       | 27 pF, 5%, NP0, 0402                                            |  |  |  |  |

| C391 | 27 pF, 5%, NP0, 0402                                       | 27 pF, 5%, NP0, 0402                                       | 27 pF, 5%, NP0, 0402                                            |  |  |  |  |

| L61  | 8.2 nH, 5%,<br>Monolithic/multilayer, 0402                 | 7.5 nH, 5%,<br>Monolithic/multilayer, 0402                 | 27 nH, 5%, Monolithic/multilayer, 0402                          |  |  |  |  |

| L62  | Not used                                                   | 5.6 nH, 5%,<br>Monolithic/multilayer, 0402                 | Not used                                                        |  |  |  |  |

| L71  | 22 nH, 5%,<br>Monolithic/multilayer, 0402                  | Not used                                                   | 12 nH, 5%, Monolithic/multilayer,<br>0402                       |  |  |  |  |

| L81  | 1.8 nH, +/- 0.3nH,<br>Monolithic/multilayer, 0402          | 7.5 nH, 5%,<br>Monolithic/multilayer, 0402                 | Not used                                                        |  |  |  |  |

| R451 | 43 kΩ, 1%, 0402                                            | 43 kΩ, 1%, 0402                                            | 43 kΩ, 1%, 0402                                                 |  |  |  |  |

| XTAL | 16 MHz crystal, 16 pF load ( $C_L$ ),<br>ESR < 60 $\Omega$ | 16 MHz crystal, 16 pF load ( $C_L$ ),<br>ESR < 60 $\Omega$ | 16 MHz crystal, 16 pF load (C <sub>L</sub> ), ESR < 60 $\Omega$ |  |  |  |  |

Table 2. Bill of materials for the application circuits

### 10 IEEE 802.15.4 Modulation Format

This section is meant as an introduction to the 2.4 GHz direct sequence spread spectrum (DSSS) RF modulation format defined in IEEE 802.15.4. For a complete description, please refer to [1].

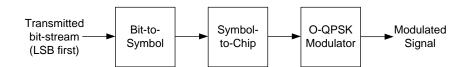

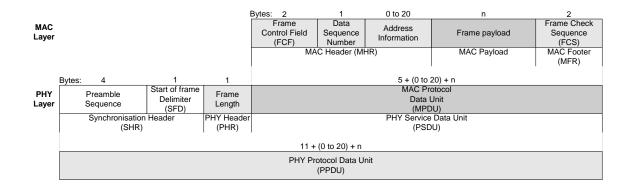

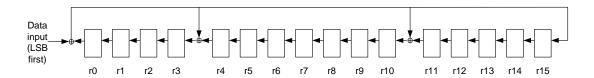

The modulation and spreading functions are illustrated at block level in Figure 6 [1]. Each byte is divided into two symbols, 4 bits each. The least significant symbol is transmitted first. For multi-byte fields, the

least significant byte is transmitted first, except for security related fields where the most significant byte it transmitted first.

Each symbol is mapped to one out of 16 pseudo-random sequences, 32 chips each. The symbol to chip mapping is shown in Table 3. The chip sequence is then transmitted at 2 MChips/s, with the least significant chip (C<sub>0</sub>) transmitted first for each symbol.

Figure 6. Modulation and spreading functions [1]

| Symbol | Chip sequence (C <sub>0</sub> , C <sub>1</sub> , C <sub>2</sub> , , C <sub>31</sub> ) |

|--------|---------------------------------------------------------------------------------------|

| 0      | 11011001110000110101001000101110                                                      |

| 1      | 11101101100111000011010100100010                                                      |

| 2      | 00101110110110011100001101010010                                                      |

| 3      | 00100010111011011001110000110101                                                      |

| 4      | 01010010001011101101100111000011                                                      |

| 5      | 00110101001000101110110110011100                                                      |

| 6      | 11000011010100100010111011011001                                                      |

| 7      | 10011100001101010010001011101101                                                      |

| 8      | 1000110010010110000001110111011                                                       |

| 9      | 10111000110010010110000001110111                                                      |

| 10     | 01111011100011001001011000000111                                                      |

| 11     | 0111011110111000110010010100000                                                       |

| 12     | 00000111011110111000110010010110                                                      |

| 13     | 0110000011101111011100011001001                                                       |

| 14     | 10010110000001110111101110001100                                                      |

| 15     | 11001001011000000111011110111000                                                      |

| Ta     | ble 3. IEEE 802.15.4 symbol-to-chip mapping [1]                                       |

Table 3. IEEE 802.15.4 symbol-to-chip mapping [1]

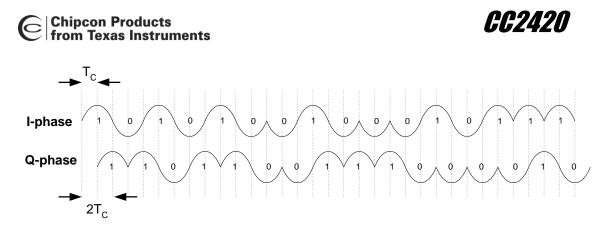

The modulation format is Offset -Quadrature Phase Shift Keying (O-QPSK) with half-sine chip shaping. This is equivalent to MSK modulation. Each chip

is shaped as a half-sine, transmitted alternately in the I and Q channels with one half chip period offset. This is illustrated for the zero-symbol in Figure 7.

Figure 7. I / Q Phases when transmitting a zero-symbol chip sequence,  $T_c = 0.5 \ \mu s$

## **11 Configuration Overview**

**CC2420** can be configured to achieve the best performance for different applications. Through the programmable configuration registers the following key parameters can be programmed:

- Receive / transmit mode

- RF channel selection

- RF output power

- Power-down / power-up mode

- Crystal oscillator power-up / power down

- Clear Channel Assessment mode

- Packet handling hardware support

- Encryption / Authentication modes

## **12 Evaluation Software**

Texas Instruments (TI) provides users of **CC2420** with a software program, SmartRF<sup>®</sup> Studio (Windows interface) which may be used for radio performance and functionality evaluation. SmartRF®

Studio can be downloaded from TI's web page: <u>http://www.ti.com</u>. Figure 8 shows the user interface of the **CC2420** configuration software.

| Calculation Window - CC2420 - Smart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | tRF Studio                                                                          | _ 8 ×    |