SBOS277F - JUNE 2004 - REVISED DECEMBER 2007

# 18-V SUPPLY MULTI-CHANNEL GAMMA CORRECTION BUFFER

### **FEATURES**

Wide Supply Range: 4.5 V to 18 V

• Gamma Correction Channels: 10, 6, and 4

Integrated V<sub>COM</sub> Buffer

Excellent Output Current Drive:

- Gamma Channels:

> 30 mA at 0.5 V Swing to Rails(1)

- V<sub>COM</sub>:

> 100 mA typ at 2 V Swing to Rails(1)

Large Capacitive Load Drive Capability

Rail-to-Rail Output

■ PowerPAD™ Package

• Low-Power/Channel: < 500 μA

High ESD Rating: 8 kV HBM, 2 kV CDM, 300 V MM

Specified for -25°C to +85°C

(1) See Typical Characteristic curves for details.

#### DESCRIPTION

The BUFxx704 are a series of multi-channel buffers targeted towards gamma correction in high-resolution LCD panels. They are pin-compatible with the existing BUFxx702 and BUFxx703 families and operate at higher supply voltages up to 18 V (19 V absolute max). The higher supply voltage enables faster response times and brighter images in large-screen LCD panels. This is especially important in LCD TV applications.

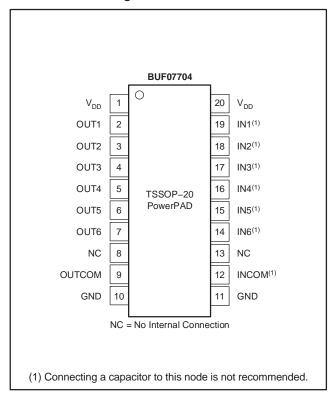

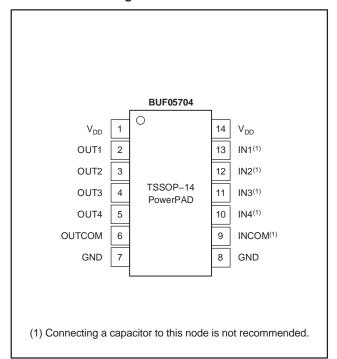

The number of gamma correction channels required depends on a variety of factors and differs greatly from design to design. Therefore, 10, 6, and 4 channel options are offered. For additional space and cost savings, a V<sub>COM</sub> channel with > 100mA drive capability is integrated into the BUF11704, BUF07704, and BUF05704.

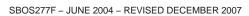

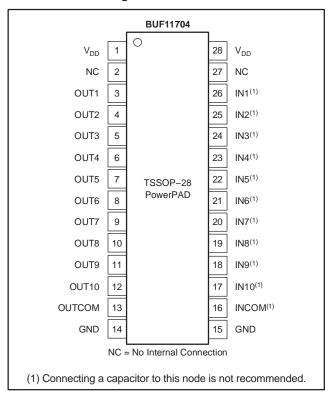

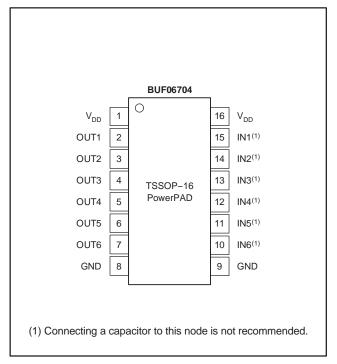

The BUF11704, BUF07704, BUF06704, and BUF05704 are available in the TSSOP-28, TSSOP-20, TSSOP-16, and TSSOP-14 PowerPAD packages for dramatically increased power dissipation capability. This way, a large number of channels can be handled safely in one package.

A flow-through pinout has been adopted to allow simple PCB routing and maintain the cost-effectiveness of this solution. All inputs and outputs of the BUFxx704 incorporate internal ESD protection circuits that prevent functional failures at voltages up to 8 kV (HBM), 2 kV (CDM), and 300 V (MM).

| MODEL    | GAMMA<br>CHANNELS | V <sub>COM</sub> CHANNELS |

|----------|-------------------|---------------------------|

| BUF11704 | 10                | 1                         |

| BUF07704 | 6                 | 1                         |

| BUF06704 | 6                 | 0                         |

| BUF05704 | 4                 | 1                         |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated. All other trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS(1)**

Over operating free-air temperature range unless otherwise noted

| PARAMETERS                                           | BUFxx704         | UNIT         |

|------------------------------------------------------|------------------|--------------|

| Supply Voltage, V <sub>DD</sub> (2)                  | 19               | V            |

| Input Voltage Range, V <sub>I</sub>                  | ±V <sub>DD</sub> |              |

| Continuous Total Power Dissipation                   | See Dissipation  | Rating Table |

| Operating Free-Air Temperature Range, TA             | -25 to 85        | °C           |

| Maximum Junction Temperature, T <sub>J</sub>         | 125              | °C           |

| Storage Temperature Range, T <sub>STG</sub>          | -65 to 150       | °C           |

| Lead Temperature 1.6mm (1/16 inch) from Case for 10s | 260              | °C           |

| ESD Rating:                                          |                  |              |

| Human Body Model (HBM)                               | 8                | kV           |

| Charged-Device Model (CDM)                           | 2                | kV           |

| Machine Model (MM)                                   | 300              | V            |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### ORDERING INFORMATION(1)

| PRODUCT  | PACKAGE-LEAD | PACKAGE MARKING |

|----------|--------------|-----------------|

| BUF05704 | TSSOP-14     | BUF05704        |

| BUF06704 | TSSOP-16     | BUF06704        |

| BUF07704 | TSSOP-20     | BUF07704        |

| BUF11704 | TSSOP-28     | BUF11704        |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

#### **DISSIPATION RATING TABLE**

| PACKAGE TYPE | PACKAGE<br>DESIGNATOR | θJC <sup>(1)</sup><br>(°C/W) | <sub>∂JA</sub> (1)<br>(°C/W) | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING |

|--------------|-----------------------|------------------------------|------------------------------|----------------------------------------------------------------------------|

| TSSOP-28     | PWP (28)              | 0.72                         | 27.9                         | 3.58 W                                                                     |

| TSSOP-20     | PWP (20)              | 1.40                         | 32.63                        | 3.06 W                                                                     |

| TSSOP-16     | PWP (16)              | 2.07                         | 36.51                        | 2.74                                                                       |

| TSSOP-14     | PWP (14)              | 2.07                         | 37.47                        | 2.67                                                                       |

<sup>(1)</sup> PowerPAD attached to PCB, 0 lfm airflow, and 76mm x 76mm copper area.

#### **RECOMMENDED OPERATING CONDITIONS**

|                                                | MIN | NOM MAX | UNIT |

|------------------------------------------------|-----|---------|------|

| Supply Voltage, V <sub>DD</sub>                | 7   | 18      | V    |

| Operating Free-Air Temperature, T <sub>A</sub> | -25 | +85     | °C   |

<sup>(2)</sup> All voltage values are with respect to GND.

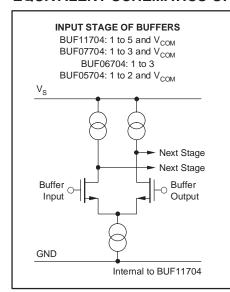

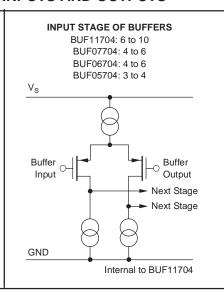

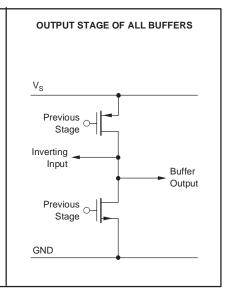

#### **EQUIVALENT SCHEMATICS OF INPUTS AND OUTPUTS**

#### **ELECTRICAL CHARACTERISTICS: BUFxx704**

Over operating free-air temperature range,  $V_{DD} = 18 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

|        | PARAMETEI                | २                            | TEST CONDITIONS                                                       | TA                        | MIN | TYP        | MAX | UNIT |  |

|--------|--------------------------|------------------------------|-----------------------------------------------------------------------|---------------------------|-----|------------|-----|------|--|

|        |                          | 0                            |                                                                       | 25°C                      |     | -1         | 20  |      |  |

| .,     | land offertual term      | Gamma buffers                | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                 | Full range(1)             |     |            | 20  | \/   |  |

| VIO    | Input offset voltage     | V                            | V <sub>I</sub> = 9V                                                   | 25°C                      |     | -1         | 30  | mV   |  |

|        |                          | VCOM                         |                                                                       | Full range(1)             |     |            | 30  |      |  |

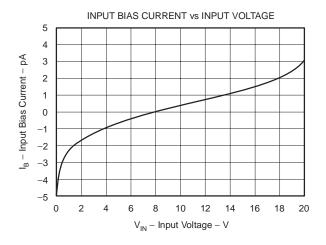

|        | Leaved billion assume at |                              | V V /0                                                                | 25°C                      |     | 1          |     | 4    |  |

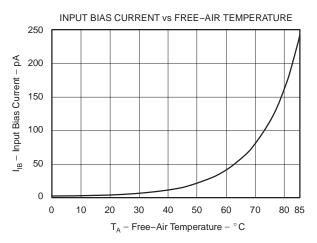

| IB     | Input bias current       |                              | $V_I = V_{DD}/2$                                                      | Full range <sup>(1)</sup> |     | 200        |     | pΑ   |  |

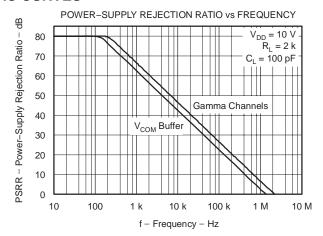

| B000   |                          |                              | V 45V4 40V4                                                           | 25°C                      | 62  | 80         |     | j    |  |

| PSRR   | Power-Supply Reject      | ion Ratio                    | $V_{DD} = 4.5 \text{ V to } 19 \text{ V}$                             | Full range(1)             | 60  |            |     | dB   |  |

|        | Buffer gain              |                              | V <sub>I</sub> = 5 V                                                  | 25°C                      |     | 0.9995     |     | V/V  |  |

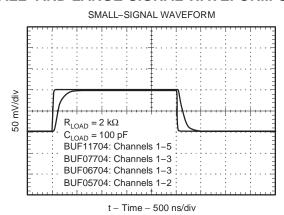

| BW_3dB | 3dB bandwidth            | Gamma buffers<br>VCOM buffer | $C_L = 100 \text{ pF}, R_L = 2 \text{ k}\Omega$                       | 25°C                      |     | 1<br>0.6   |     | MHz  |  |

| SR     | Slew rate                | Gamma buffers<br>VCOM buffer | $C_L$ = 100 pF, $R_L$ = 2 k $\Omega$<br>V <sub>IN</sub> = 2 V to 16 V | 25°C                      |     | 1.6<br>4.6 |     | V/µs |  |

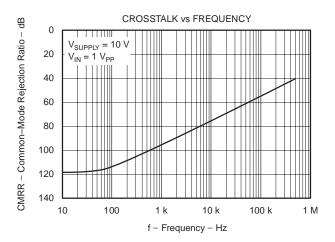

|        | Crosstalk                | _                            | $V_{IP-P} = 6 \text{ V, } f = 1 \text{ kHz}$                          | 25°C                      |     | 85         |     | dB   |  |

<sup>(1)</sup> Full range is -25°C to 85°C.

|          | PARAME                    | TER                                        | TEST CONDITIONS                                      | T <sub>A</sub> (1) | MIN   | TYP  | MAX                 | UNIT      |

|----------|---------------------------|--------------------------------------------|------------------------------------------------------|--------------------|-------|------|---------------------|-----------|

| Inn      | Supply current            | ALL                                        | $V_O = V_{DD}/2$                                     | 25°C               |       | 5    | 9.0                 | mA        |

| lDD      | Supply current            | ALL                                        | No Load                                              |                    |       |      | 9.0                 | ША        |

|          |                           | Buffers 1-5                                |                                                      |                    | 1     |      | $V_{DD}$            |           |

| Common-m | node input range          | Buffers 6-10                               |                                                      | 25°C               | GND   | \    | / <sub>DD</sub> – 1 | V         |

|          |                           | V <sub>COM</sub> buffer                    |                                                      |                    | 1     |      | $V_{DD}$            |           |

|          |                           | V <sub>COM</sub> buffer sinking            | $I_O = 1 \text{ mA to } 100 \text{ mA},$             | 25°C               |       | 1    | 5                   |           |

|          |                           | VCOM paner sinking                         | V <sub>IN</sub> = 2 V                                | Full range         |       |      | 5                   |           |

|          |                           | VCOM buffer sourcing                       | $I_O = -1$ mA to $-100$ mA                           | 25°C               |       | 1    | 5                   |           |

|          | Load regulation           | VCOM panel sourcing                        | V <sub>IN</sub> = 16 V                               | Full range         |       |      | 5                   | mV/mA     |

|          | Load regulation           | Buffers 1-10 sinking                       | $I_O = 1 \text{ mA to } 10 \text{ mA}$               | 25°C               |       | 1    | 5                   | IIIV/IIIA |

|          |                           | Dullers 1-10 siriking                      | V <sub>IN</sub> = 1 V                                | Full range         |       |      | 5                   |           |

|          | Buffers 1-10 sourcing     | $I_{O} = -1 \text{ mA to } -10 \text{ mA}$ | 25°C                                                 |                    | 1     | 5    |                     |           |

|          |                           | Bullers 1-10 sourcing                      | V <sub>IN</sub> = 17 V                               |                    |       |      | 5                   |           |

| VOH1-5   |                           | Buffers 1-5                                | V <sub>IN</sub> = 18 V<br>ISOURCE = 10 mA            | 25°C               | 17.85 | 17.9 |                     | V         |

| Vaus     | High-level output voltage | Buffers 6-10                               | V <sub>IN</sub> = 17 V<br>I <sub>SINK</sub> = 10 mA  | – 25°C             |       | 17   | 17.15               | V         |

| VOH6-10  |                           | Bullers 6-10                               | V <sub>IN</sub> = 17 V<br>ISOURCE = 10 mA            | 25°C               | 16.85 | 17   |                     | '         |

| V        |                           |                                            | V <sub>IN</sub> = 1 V<br>I <sub>SINK</sub> = 10 mA   | - 25°C             |       | 1.0  | 1.15                | V         |

| VOL1-5   | Low-level output voltage  | Buffers 1-5                                | V <sub>IN</sub> = 1 V<br>ISOURCE = 10 mA             | 25*0               | 0.85  | 1.0  |                     |           |

| VOL6-10  |                           | Buffers 6-10                               | V <sub>IN</sub> = 0 V<br>I <sub>SINK</sub> = 10 mA   | 25°C               |       | 0    | 0.15                | V         |

| V        | High-level output         | Va a s a buffar                            | V <sub>IN</sub> = 16 V<br>I <sub>SINK</sub> = 100 mA | 25°C               |       | 16   | 16.15               | V         |

| VOHCOM   | voltage                   | V <sub>COM</sub> buffer                    | V <sub>IN</sub> = 16 V<br>ISOURCE = 100 mA           | 25.0               | 15.85 | 16   |                     |           |

| .,       | Low-level output          | \                                          | V <sub>IN</sub> = 2 V<br>I <sub>SINK</sub> = 100 mA  | 0500               |       | 2    | 2.15                |           |

| VOLCOM   | voltage                   | V <sub>COM</sub> buffer                    | V <sub>IN</sub> = 2 V<br>ISOURCE = 100 mA            | 25°C               | 1.85  | 2    | _                   | V         |

<sup>(1)</sup> Full range is -25°C to 85°C.

|                    | PARAME                    | TER                                      | TEST CONDITIONS                                      | T <sub>A</sub> (1) | MIN   | TYP  | MAX                 | UNIT      |

|--------------------|---------------------------|------------------------------------------|------------------------------------------------------|--------------------|-------|------|---------------------|-----------|

| laa                | Supply current            | ALL                                      | $V_O = V_{DD}/2$                                     | 25°C               |       | 5    | 7.5                 | mA        |

| IDD                | Supply current            | ALL                                      | No Load                                              | Full range         |       |      | 7.5                 | IIIA      |

|                    |                           | Buffers 1-3                              |                                                      |                    | 1     |      | $V_{DD}$            |           |

| Common-m           | node input range          | Buffers 4-6                              |                                                      | 25°C               | GND   | ١    | / <sub>DD</sub> – 1 | V         |

|                    |                           | V <sub>COM</sub> buffer                  |                                                      |                    | 1     |      | $V_{DD}$            |           |

|                    |                           | VCOM buffer sinking                      | $I_O = 1 \text{ mA to } 100 \text{ mA}$              | 25°C               |       | 1    | 5                   |           |

|                    |                           | ACOM panel surking                       | V <sub>IN</sub> = 2 V                                | Full range         |       |      | 5                   |           |

|                    |                           | V <sub>COM</sub> buffer sourcing         | $I_{O} = -1 \text{ mA to } -100 \text{ mA}$          | 25°C               |       | 1    | 5                   |           |

|                    | Load regulation           | VCOM panel sourcing                      | V <sub>IN</sub> = 16 V                               | Full range         |       |      | 5                   | mV/mA     |

|                    | Load regulation           | Buffers 1-6 sinking                      | $I_O = 1 \text{ mA to } 10 \text{ mA}$               | 25°C               |       | 1    | 5                   | 1110/111/ |

|                    |                           | Dullers 1-0 sirking                      | V <sub>IN</sub> = 1 V                                | Full range         |       |      | 5                   |           |

|                    | Buffers 1-6 sourcing      | $I_O = -1 \text{ mA to } -10 \text{ mA}$ | 25°C                                                 |                    | 1     | 5    |                     |           |

|                    |                           | Bullers 1-0 Sourcing                     | V <sub>IN</sub> = 17 V                               | Full range         |       |      | 5                   |           |

| VOH1-3             |                           | Buffers 1-3                              | V <sub>IN</sub> = 18 V<br>ISOURCE = 10 mA            | 25°C               | 17.85 | 17.9 |                     | V         |

| Vauva              | High-level output voltage | Buffers 4-6                              | V <sub>IN</sub> = 17 V<br>I <sub>SINK</sub> = 10 mA  | 25°C               |       | 17   | 17.15               | V         |

| VOH4-6             |                           | bullets 4-0                              | V <sub>IN</sub> = 17 V<br>ISOURCE = 10 mA            | 25 C               | 16.85 | 17   |                     | V         |

| \/a                |                           | Buffers 1-3                              | V <sub>IN</sub> = 1 V<br>I <sub>SINK</sub> = 10 mA   | 2500               |       | 1.0  | 1.15                | V         |

| VOL1-3             | Low-level output voltage  | bullers 1-3                              | V <sub>IN</sub> = 1 V<br>ISOURCE = 10 mA             | — 25°C             | 0.85  | 1.0  |                     |           |

| V <sub>OL4-6</sub> |                           | Buffers 4-6                              | V <sub>IN</sub> = 0 V<br>I <sub>SINK</sub> = 10 mA   | 25°C               |       | 0    | 0.15                | V         |

| V                  | High-level output         | Va a s huffar                            | V <sub>IN</sub> = 16 V<br>I <sub>SINK</sub> = 100 mA | 25°C               |       | 16   | 16.15               | V         |

| VOHCOM             | voltage                   | V <sub>COM</sub> buffer                  | V <sub>IN</sub> = 16 V<br>ISOURCE = 100 mA           | 25.0               | 15.85 | 16   |                     |           |

|                    | Low-level output          | V <sub>IN</sub> =                        |                                                      | 0500               |       | 2    | 2.15                |           |

| VOLCOM             | voltage                   | VCOM buffer                              | V <sub>IN</sub> = 2 V<br>ISOURCE = 100 mA            | 25°C               | 1.85  | 2    |                     | V         |

<sup>(1)</sup> Full range is -25°C to 85°C.

|                    | PARAME                    | TER                                        | TEST CONDITIONS                                    | T <sub>A</sub> (1) | MIN   | TYP   | MAX                 | UNIT  |

|--------------------|---------------------------|--------------------------------------------|----------------------------------------------------|--------------------|-------|-------|---------------------|-------|

| Inn                | Supply current            | ALL                                        | $V_O = V_{DD}/2$                                   | 25°C               |       | 5     | 7.5                 | mA    |

| IDD                | Зарріу сапені             | No Load                                    |                                                    | Full range         |       |       | 7.5                 | ША    |

| Common             | mada innut ranga          | Buffers 1-3                                |                                                    | 25°C               | 1     |       | $V_{DD}$            | V     |

| Common-i           | mode input range          | Buffers 4-6                                |                                                    | 25 C               | GND   | \     | / <sub>DD</sub> – 1 | V     |

|                    |                           | Duffero 1 6 einking                        | I <sub>O</sub> = 1 mA to 10 mA                     | 25°C               |       | 1     | 5                   |       |

|                    | Load regulation           | Buffers 1-6 sinking                        | V <sub>IN</sub> = 1 V                              | Full range         |       |       | 5                   | mV/mA |

| Load regulation    | Buffers 1-6 sourcing      | $I_{O} = -1 \text{ mA to } -10 \text{ mA}$ | 25°C                                               |                    | 1     | 5     | IIIV/IIIA           |       |

|                    |                           | Bullers 1-0 Sourcing                       | V <sub>IN</sub> = 17 V                             | Full range         |       |       | 5                   |       |

| VOH1-3             |                           | Buffers 1-3                                | V <sub>IN</sub> = 18 V<br>ISOURCE = 10 mA          | 25°C               | 17.85 | 17.9  |                     | V     |

|                    | High-level output voltage | D. #                                       | V <sub>IN</sub> = 17 V<br> SINK = 10 mA            |                    | 17    | 17.15 | .,,                 |       |

| V <sub>OH4-6</sub> |                           | Buffers 4-6                                | V <sub>IN</sub> = 17 V<br>ISOURCE = 10 mA          | 25°C               | 16.85 | 17    |                     | V     |

| Value              |                           | Buffers 1-3                                | V <sub>IN</sub> = 1 V<br>I <sub>SINK</sub> = 10 mA | 25°C               |       | 1.0   | 1.15                | · V   |

| V <sub>OL1-3</sub> | Low-level output voltage  | Dullers 1-3                                | V <sub>IN</sub> = 1 V<br>ISOURCE = 10 mA           | 25 C               | 0.85  | 1.0   |                     |       |

| VOL4-6             |                           | Buffers 4-6                                | V <sub>IN</sub> = 0 V<br>I <sub>SINK</sub> = 10 mA | 25°C               |       | 0     | 0.15                | V     |

<sup>(1)</sup> Full range is –25°C to 85°C.

|                    | PARAME                    | TER                              | TEST CONDITIONS                                      | T <sub>A</sub> (1) | MIN   | TYP  | MAX                 | UNIT      |

|--------------------|---------------------------|----------------------------------|------------------------------------------------------|--------------------|-------|------|---------------------|-----------|

| Inn                | Supply current            | ALL                              | $V_O = V_{DD}/2$                                     | 25°C               |       | 5    | 7.5                 | mA        |

| lDD                | Supply current            | ALL                              | No Load                                              | Full range         |       |      | 7.5                 | IIIA      |

|                    |                           | Buffers 1-2                      |                                                      |                    | 1     |      | $V_{DD}$            |           |

| Common-m           | node input range          | Buffers 3-4                      |                                                      | 25°C               | GND   | ١    | / <sub>DD</sub> – 1 | V         |

|                    |                           | V <sub>COM</sub> buffer          |                                                      |                    | 1     |      | $V_{DD}$            |           |

|                    |                           | VCOM buffer sinking              | $I_O = 1 \text{ mA to } 100 \text{ mA}$              | 25°C               |       | 1    | 5                   |           |

|                    |                           | ACOM panel surking               | V <sub>IN</sub> = 2 V                                | Full range         |       |      | 5                   |           |

|                    |                           | V <sub>COM</sub> buffer sourcing | $I_{O} = -1 \text{ mA to } -100 \text{ mA}$          | 25°C               |       | 1    | 5                   |           |

|                    | Load regulation           | VCOM panel sourcing              | V <sub>IN</sub> = 16 V                               | Full range         |       |      | 5                   | mV/mA     |

|                    | Load regulation           | Buffers 1-4 sinking              | $I_O = 1 \text{ mA to } 10 \text{ mA}$               | 25°C               |       | 1    | 5                   | 1110/111/ |

|                    |                           | Dullers 1-4 Siriking             | V <sub>IN</sub> = 1 V                                | Full range         |       |      | 5                   |           |

|                    |                           | Buffers 1-4 sourcing             | $I_O = -1 \text{ mA to } -10 \text{ mA}$             | 25°C               |       | 1    | 5                   |           |

|                    |                           | Bullers 1-4 Sourcing             | V <sub>IN</sub> = 17 V                               | Full range         |       |      | 5                   |           |

| V <sub>OH1-3</sub> |                           | Buffers 1-2                      | V <sub>IN</sub> = 18 V<br>ISOURCE = 10 mA            | 25°C               | 17.85 | 17.9 |                     | V         |

| V                  | High-level output voltage | Buffers 3-4                      | V <sub>IN</sub> = 17 V<br>I <sub>SINK</sub> = 10 mA  | 25°C               |       | 17   | 17.15               | V         |

| VOH4-6             |                           | bullets 3-4                      | V <sub>IN</sub> = 17 V<br>ISOURCE = 10 mA            | 25 C               | 16.85 | 17   |                     | V         |

| \/a                |                           | Buffers 1-2                      | V <sub>IN</sub> = 1 V<br>I <sub>SINK</sub> = 10 mA   | 2500               |       | 1.0  | 1.15                | V         |

| VOL1-3             | Low-level output voltage  | bullers 1-2                      | V <sub>IN</sub> = 1 V<br>ISOURCE = 10 mA             | — 25°C             | 0.85  | 1.0  |                     |           |

| V <sub>OL4-6</sub> |                           | Buffers 3-4                      | V <sub>IN</sub> = 0 V<br>I <sub>SINK</sub> = 10 mA   | 25°C               |       | 0    | 0.15                | V         |

| V                  | High-level output         | Va a s huffar                    | V <sub>IN</sub> = 16 V<br>I <sub>SINK</sub> = 100 mA | 25°C               |       | 16   | 16.15               | V         |

| VOHCOM             | voltage                   | V <sub>COM</sub> buffer          | V <sub>IN</sub> = 16 V<br>ISOURCE = 100 mA           | 25.0               | 15.85 | 16   |                     |           |

| \/                 | Low-level output          | \\ \h.#6                         | V <sub>IN</sub> = 2 V<br>I <sub>SINK</sub> = 100 mA  | 0500               |       | 2    | 2.15                |           |

| VOLCOM             | voltage                   | VCOM buffer                      | V <sub>IN</sub> = 2 V<br>ISOURCE = 100 mA            | 25°C               | 1.85  | 2    |                     | V         |

<sup>(1)</sup> Full range is -25°C to 85°C.

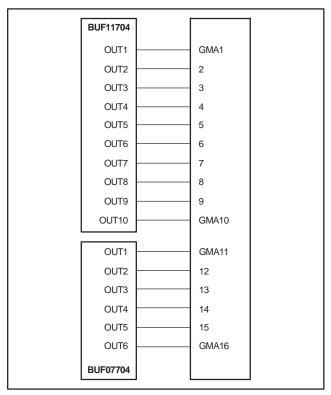

#### **BUF11704 Pin Configuration**

#### **BUF06704 Pin Configuration**

#### **BUF07704 Pin Configuration**

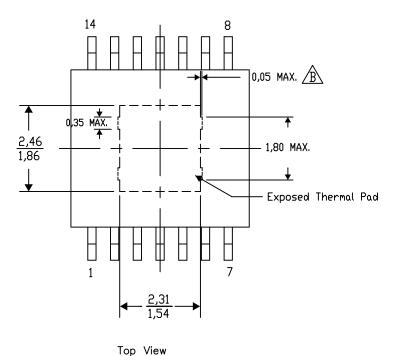

#### **BUF05704 Pin Configuration**

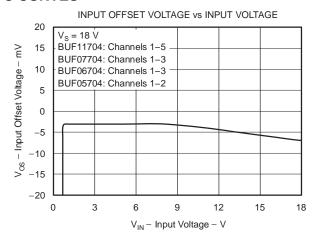

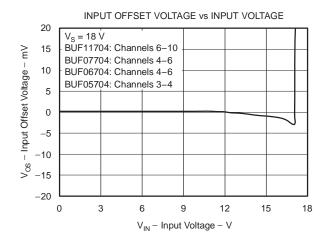

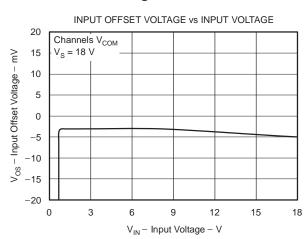

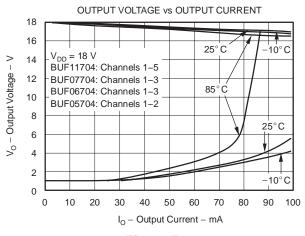

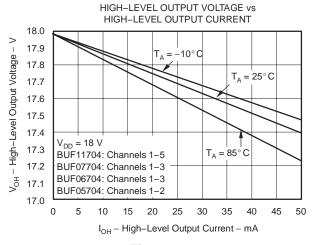

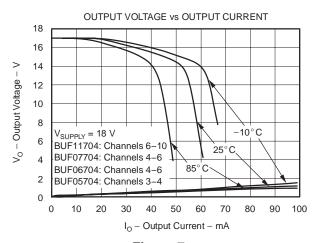

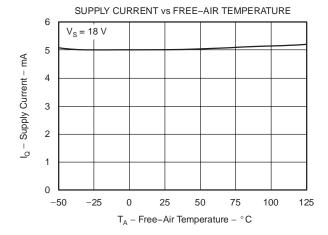

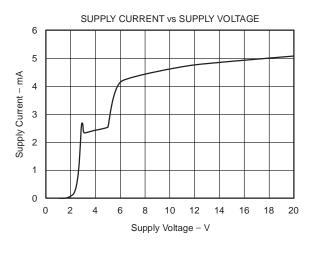

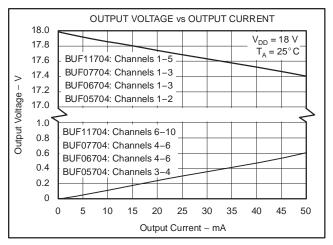

#### **DC CURVES**

Figure 1

Figure 2

Figure 3

Figure 4

Figure 5

Figure 6

#### **DC CURVES (continued)**

Figure 7

Figure 9

Figure 11

Figure 8

Figure 10

Figure 12

#### **AC CURVES**

Figure 13 Figure 14

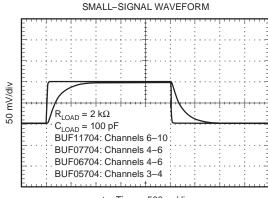

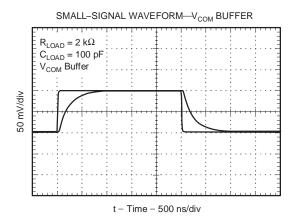

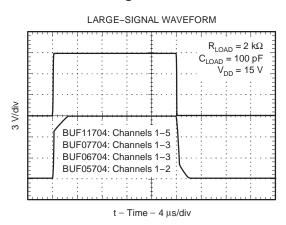

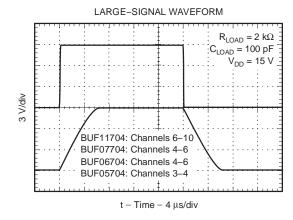

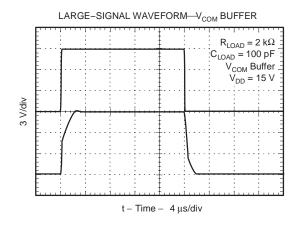

#### **SMALL- AND LARGE-SIGNAL WAVEFORM CURVES**

t - Time - 500 ns/div

Figure 15

Figure 16

Figure 17

Figure 18

Figure 19 Figure 20

#### **APPLICATION INFORMATION**

The requirements on the number of gamma correction channels vary greatly from panel to panel. Therefore, the BUFxx704 series of gamma correction buffers offer different channel combinations. The BUF11704 offers 10 gamma channels plus one  $V_{COM}$  channel, whereas the BUF07704 provides six gamma channels plus one  $V_{COM}$ . The  $V_{COM}$  channel on both models can be used to drive the  $V_{COM}$  node on the LCD panel.

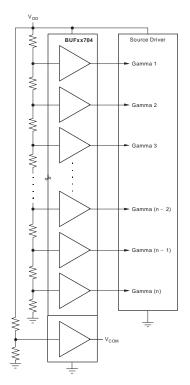

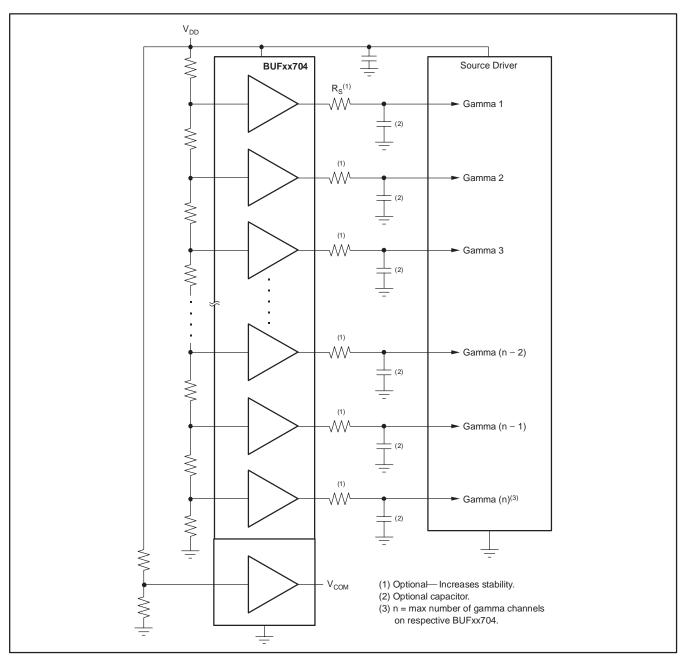

Gamma correction voltages are often generated using a simple resistor ladder, as shown in Figure 21. The BUFxx704 buffers the various nodes on the gamma correction resistor ladder. The low output impedance of the BUFxx704 forces the external gamma correction voltage on the respective reference node of the LCD source driver. Figure 21 shows an example of the BUFxx704 in a typical block diagram driving an LCD source driver with 10- or 6-channel gamma correction reference inputs.

Figure 21. LCD Source Driver Typical Block Diagram

#### **ESD RATINGS**

The BUFxx704 has excellent ESD performance: 8 kV HBM; 2 kV CDM; and 300 V MM. These ESD ratings allow for increased manufacturability, fewer production failures, and higher reliability.

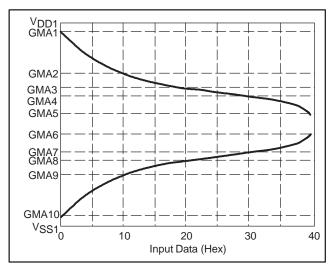

#### INPUT VOLTAGE RANGE GAMMA BUFFERS

Figure 22 shows a typical gamma correction curve with 10 gamma correction reference points (GMA1 through GMA10). As can be seen from this curve, the voltage requirements for each buffer vary greatly. The swing capability of the input stages of the various buffers is carefully matched to the application. Using the example of the BUF11704 with 10 gamma correction channels, buffers 1 to 5 have input stages that include  $V_{DD}$ , but will only swing within 1 V to GND. Buffers 1 through 5 have only a single NMOS input stage. Buffers 6 through 10 have only a single PMOS input stage. The input range of the PMOS input stage includes GND.

Figure 22. Gamma Correction Curve

#### **OUTPUT VOLTAGE SWING GAMMA BUFFERS**

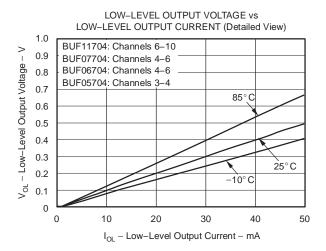

The output stages have been designed to match the characteristic of the input stage. Once again, using the example of the BUF11704, this means that the output stage of buffers 1 to 5 swing very close to  $V_{DD}$ , typically  $V_{CC}$  – 100 mV at 10 mA; its ability to swing to GND is limited. Buffers 6 through 10 swing closer to GND than  $V_{DD}$ . Buffers 6 to 10 are designed to swing very close to GND; typically, GND + 100 mV at a 10 mA load current. See the *Typical Characteristics* for more details. This approach significantly reduces the silicon area and cost of the whole solution. However, due to

this architecture, the correct buffer needs to be connected to the correct gamma correction voltage. Connect buffer 1 to the gamma voltage closest to  $V_{DD}$ , and buffers 2 through 5 to the following voltages. Buffer 10 should be connected to the gamma correction voltage closest to GND (or the negative rail), and buffers 9 through 6 to the following higher voltages.

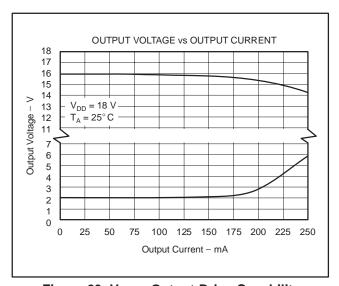

### COMMON BUFFER (V<sub>COM</sub>)

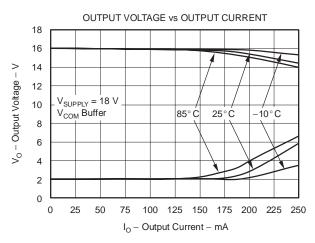

The common buffer output of the BUFxx704 has a greater output drive capability than the gamma buffers to meet the heavier current demands of driving the common node of the LCD panel. The common buffer output was also designed to drive heavier capacitive loads. Excellent output swing is possible with high currents ( > 100 mA), as shown in Figure 23.

Figure 23. V<sub>COM</sub> Output Drive Capability

#### **CAPACITIVE LOAD DRIVE**

The BUFxx704 has been designed to be able to sink/source large dc currents. Its output stage has been designed to deliver output current transients with little disturbance of the output voltage. However, there are times when very fast current pulses are required. Therefore, in LCD source driver buffer applications, it is quite normal for capacitors to be placed at the outputs of the reference buffers. These capacitors improve the transient load regulation and will typically vary from 100 pF and more. The BUFxx704 gamma buffers were designed to drive capacitances in excess of 100 pF. The output is able to swing within 150 mV of the rails on 10 mA of output current; see Figure 24.

Figure 24. Gamma Buffer Drive Capability

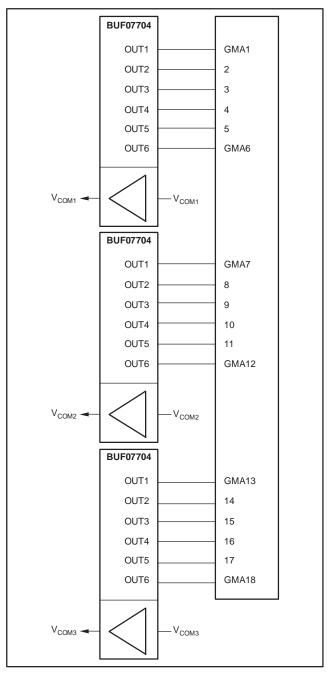

#### **APPLICATIONS WITH >10 GAMMA CHANNELS**

When a greater number of gamma correction channels are required, two or more BUFxx704 devices can be used in parallel, as shown in Figure 25. This capability provides a cost-effective way of creating more reference voltages over the use of quad-channel op amps or buffers. The suggested configuration in Figure 25 simplifies layout. The various different channel versions provide a high degree of flexibility and also minimize total cost and space.

Figure 25. Creating > 10 Gamma Voltage Channels

#### MULTIPLE V<sub>COM</sub> CHANNELS

In some LCD panels, more than one  $V_{COM}$  driver is required for best panel performance. Figure 26 uses three BUF07704s to create a total of 18 gamma-correction and three  $V_{COM}$  channels. This solution saves considerable space and cost over the more conventional approach of using five or six quad-channel buffers or op amps.

Figure 26. 18-Channel Application with Three Integrated V<sub>COM</sub> Channels

Table 1. How to Combine for > 10 Channels

|                         | BUF05704 | BUF06704 | BUF07704 | BUF11704 |

|-------------------------|----------|----------|----------|----------|

| 12ch                    |          | 2        | _        | _        |

| 12ch + V <sub>COM</sub> | _        | 1        | 1        | _        |

| 14ch + V <sub>COM</sub> | 1        | _        | _        | 1        |

| 16ch + V <sub>COM</sub> | _        | 1        | _        | 1        |

| 18ch + V <sub>COM</sub> | _        | _        | _        | 2        |

| 20ch + V <sub>COM</sub> | _        | _        | _        | 2        |

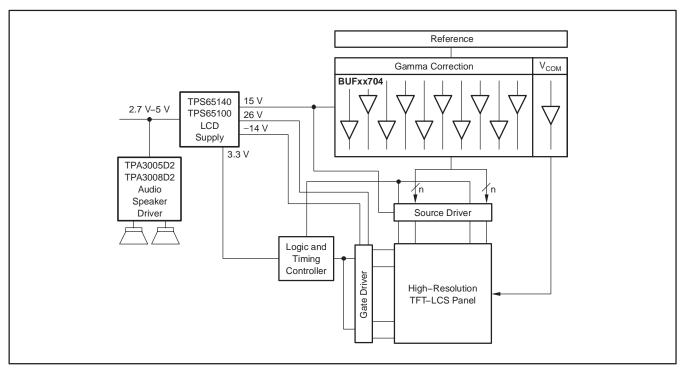

#### COMPLETE LCD SOLUTION FROM TI

In addition to the BUFxx704 line of gamma correction buffers, TI offers a complete set of ICs for the LCD panel market, including source and gate drivers, timing controllers, various power-supply solutions, and audio power solutions. Figure 27 shows the total IC solution from TI.

# AUDIO POWER AMPLIFIER FOR TV SPEAKERS

The TPA3005D2 is a 6 W (per channel) stereo audio amplifier specifically targeted towards LCD monitors and TVs. It offers highly efficient, filter-free Class-D operation for driving bridge-tied stereo speakers. The TPA3005D2 is designed to drive stereo speakers as low as 8  $\Omega$  without an output filter. The high efficiency of the TPA3005D2 eliminates the need for external heatsinks when playing music. The TPA3008D2 is similar to the

TPA3005D2, but is capable of 8 W of output power. Texas Instruments offers a full line of linear and switch-mode audio power amplifiers. For more information, visit www.ti.com. For excellent audio performance, TI recommends the OPA364 (SBOS259) or OPA353 (SBOS103) as headphone drivers.

# INTEGRATED DC/DC CONVERTERS FOR LCD PANELS: TPS65100 and TPS65140

The TPS65100 and TPS65140 offer a very compact and small power supply solution to provide all three power-supply voltages required by TFT (thin film transistor) LCD displays. Additionally the devices have an integrated V<sub>COM</sub> buffer. The auxiliary linear regulator controller can be used to generate the 3.3 V logic power rail for systems powered by a 5 V supply rail only. The main output can power the LCD source drivers as well as the BUFxx704. An integrated adjustable charge pump doubler/tripler provides the positive LCD gate drive voltage. An externally adjustable negative charge pump provides the negative gate drive voltage. The TPS65100 has an integrated V<sub>COM</sub> buffer to power the LCD backplane. A version of the BUFxx704 without the integrated V<sub>COM</sub> buffer could be used for minimum redundancy and lowest cost. For LCD panels powered by 5 V only, the TPS65100 has a linear regulator controller that uses an external transistor to provide a regulated 3.3 V output for the digital circuits. Contact the local sales office for more information.

Figure 27. TI LCD Solution

# GENERAL PowerPAD DESIGN CONSIDERATIONS

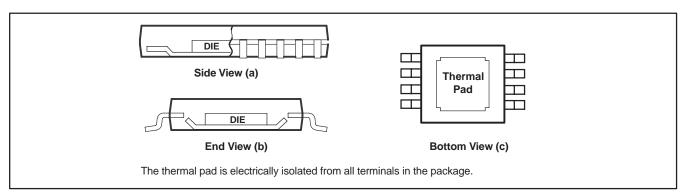

The BUFxx704 is available in the thermally-enhanced PowerPAD family of packages. These packages are constructed using a downset leadframe upon which the die is mounted, as shown in Figure 28(a) and (b). This arrangement results in the lead frame being exposed as a thermal pad on the underside of the package; see Figure 28(c). Due to this thermal pad having direct thermal contact with the die, excellent thermal performance is achieved by providing a good thermal path away from the thermal pad.

The PowerPAD package allows for both assembly and thermal management in one manufacturing operation. During the surface-mount solder operation (when the leads are being soldered), the thermal pad must be soldered to a copper area underneath the package. Through the use of thermal paths within this copper area, heat can be conducted away from the package into either a ground plane or other heat-dissipating device. Soldering the PowerPAD to the PCB is always required, even with applications that have low power dissipation. This provides the necessary thermal and mechanical connection between the lead frame die pad and the PCB.

The PowerPAD must be connected to the device's most negative supply voltage.

- 1. Prepare the PCB with a top-side etch pattern. There should be etching for the leads as well as etch for the thermal pad.

- 2. Place recommended holes in the area of the thermal pad. Ideal thermal land size and thermal via patterns (2x3 for BUF05704 PWP-14 and BUF06704 PWP-16; 2x4 for BUF07704 PWP-20; and 2x5 for BUF11704 PWP-28) can be seen in the technical brief, PowerPAD Thermally-Enhanced Package (SLMA002), available for download at www.ti.com. These holes should be 13 mils (0.33 mm) in diameter. Keep them small, so that solder wicking through the holes is not a problem during reflow.

- 3. Additional vias may be placed anywhere along the thermal plane outside of the thermal pad area. This helps dissipate the heat generated by the BUFxx704 IC. These additional vias may be larger than the 13-mil diameter vias directly under the thermal pad. They can be larger because they are not in the thermal pad area to be soldered; thus, wicking is not a problem.

- 4. Connect all holes to the internal ground plane.

- 5. When connecting these holes to the ground plane, do not use the typical web or spoke via connection methodology. Web connections have a high thermal resistance connection that is useful for slowing the heat transfer during soldering operations. This makes the soldering of vias that have plane connections easier. In this application, however, low thermal resistance is desired for the most efficient heat transfer. Therefore, the holes under the BUFxx704 PowerPAD package should make their connection to the internal ground plane with a complete connection around the circumference of the plated-through hole.

- 6. The top-side solder mask should leave the terminals of the package and the thermal pad area with its six holes (BUF05704 and BUF06704), eight holes (BUF07704) or ten holes (BUF11704) exposed. The bottom-side solder mask should cover the holes of the thermal pad area. This prevents solder from being pulled away from the thermal pad area during the reflow process.

- 7. Apply solder paste to the exposed thermal pad area and all of the IC terminals.

- With these preparatory steps in place, the BUFxx704 IC is simply placed in position and run through the solder reflow operation as any standard surface-mount component. This preparation results in a properly installed part.

Figure 28. Views of Thermally-Enhanced DGN Package

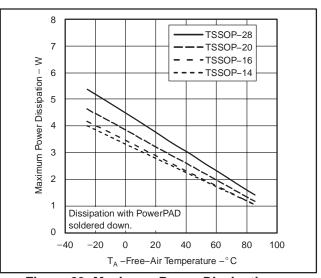

For a given  $\theta_{JA}$ , the maximum power dissipation is shown in Figure 29, and is calculated by the following formula:

$$\mathsf{P}_{\mathsf{D}} = \left( \frac{\mathsf{T}_{\mathsf{MAX}} - \mathsf{T}_{\mathsf{A}}}{\theta_{\mathsf{JA}}} \right)$$

Where:

P<sub>D</sub> = maximum power dissipation (W)

$T_{MAX}$  = absolute maximum junction temperature (125°C)

$T_A$  = free-ambient air temperature (°C)

$\theta_{JA} = \theta_{JC} + \theta_{CA}$

$\theta_{JC}$  = thermal coefficient from junction to case (°C/W)

$\theta_{CA}$  = thermal coefficient from case-to-ambient air (°C/W)

Figure 29. Maximum Power Dissipation vs Free-Air Temperature

11-Apr-2013

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

| BUF05704AIPWP    | NRND   | HTSSOP       | PWP                | 14   | 90             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |              | BUF5704           |         |

| BUF05704AIPWPG4  | NRND   | HTSSOP       | PWP                | 14   | 90             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |              | BUF5704           |         |

| BUF05704AIPWPR   | NRND   | HTSSOP       | PWP                | 14   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |              | BUF5704           |         |

| BUF05704AIPWPRG4 | NRND   | HTSSOP       | PWP                | 14   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |              | BUF5704           |         |

| BUF06704AIPWP    | NRND   | HTSSOP       | PWP                | 16   | 90             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |              | BUF6704           |         |

| BUF06704AIPWPG4  | NRND   | HTSSOP       | PWP                | 16   | 90             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR |              | BUF6704           |         |

| BUF07704AIPWP    | NRND   | HTSSOP       | PWP                | 20   | 70             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | BUF07704          |         |

| BUF07704AIPWPG4  | NRND   | HTSSOP       | PWP                | 20   | 70             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | BUF07704          |         |

| BUF07704AIPWPR   | NRND   | HTSSOP       | PWP                | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | BUF07704          |         |

| BUF07704AIPWPRG4 | NRND   | HTSSOP       | PWP                | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | BUF07704          |         |

| BUF11704AIPWP    | NRND   | HTSSOP       | PWP                | 28   | 50             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | BUF11704          |         |

| BUF11704AIPWPG4  | NRND   | HTSSOP       | PWP                | 28   | 50             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | BUF11704          |         |

| BUF11704AIPWPR   | NRND   | HTSSOP       | PWP                | 28   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | BUF11704          |         |

| BUF11704AIPWPRG4 | NRND   | HTSSOP       | PWP                | 28   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -25 to 85    | BUF11704          |         |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

#### PACKAGE OPTION ADDENDUM

11-Apr-2013

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

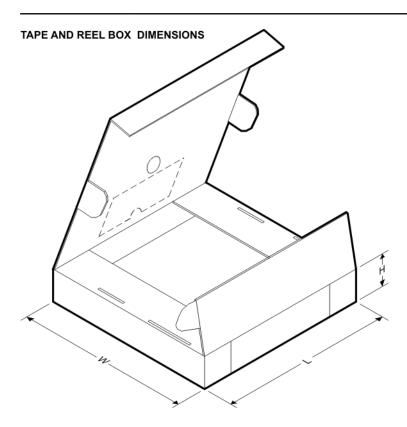

### PACKAGE MATERIALS INFORMATION

www.ti.com 23-Nov-2013

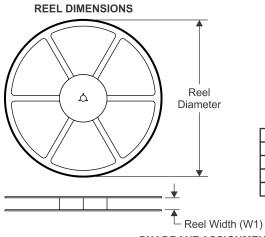

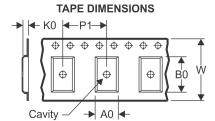

#### TAPE AND REEL INFORMATION

| _ | _  |                                                           |

|---|----|-----------------------------------------------------------|

|   |    | 3                                                         |

|   | B0 | Dimension designed to accommodate the component length    |

|   | K0 | Dimension designed to accommodate the component thickness |

|   | W  | Overall width of the carrier tape                         |

|   | P1 | Pitch between successive cavity centers                   |

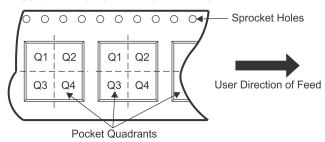

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device Device |               | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| В             | UF05704AIPWPR | HTSSOP          | PWP                | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| В             | UF07704AIPWPR | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| В             | UF11704AIPWPR | HTSSOP          | PWP                | 28 | 2000 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

www.ti.com 23-Nov-2013

\*All dimensions are nominal

|                |              |                 |      |      | 1           |            |             |  |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

| BUF05704AIPWPR | HTSSOP       | PWP             | 14   | 2000 | 367.0       | 367.0      | 35.0        |  |

| BUF07704AIPWPR | HTSSOP       | PWP             | 20   | 2000 | 367.0       | 367.0      | 38.0        |  |

| BUF11704AIPWPR | HTSSOP       | PWP             | 28   | 2000 | 367.0       | 367.0      | 38.0        |  |

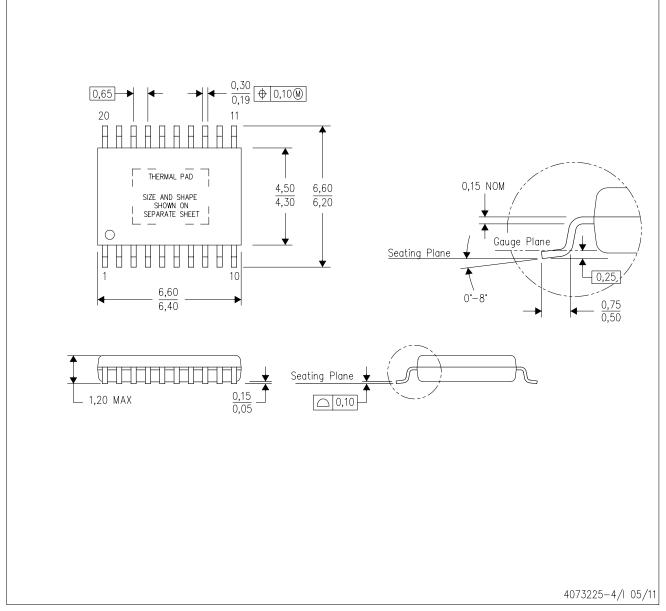

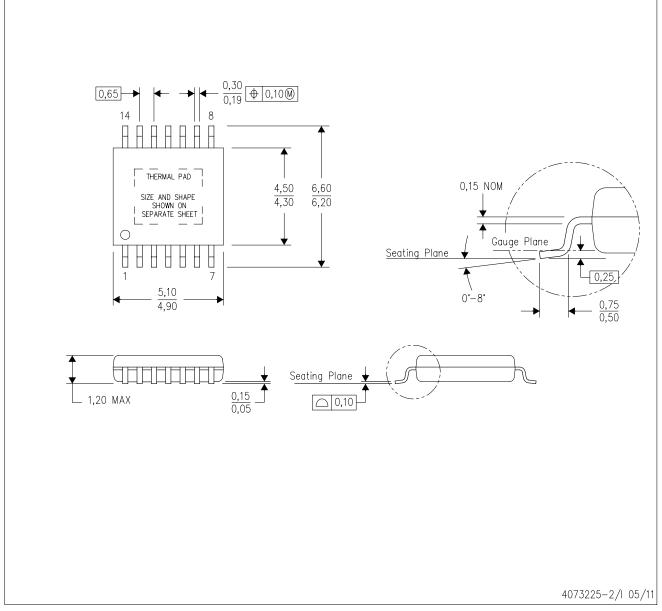

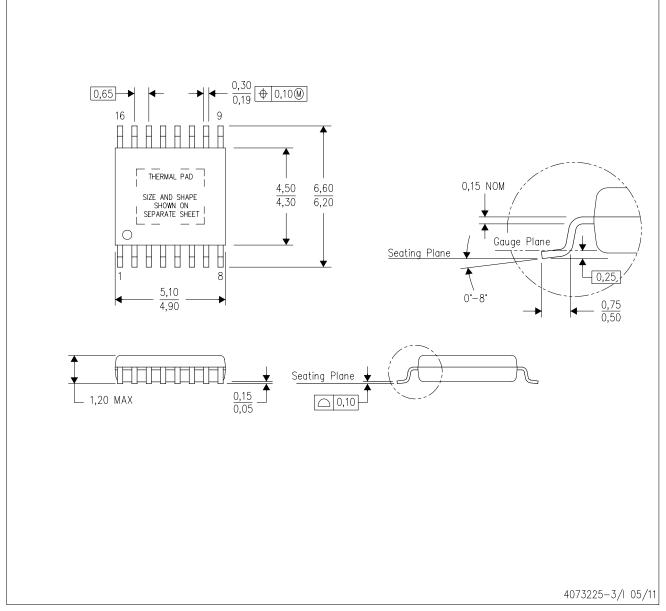

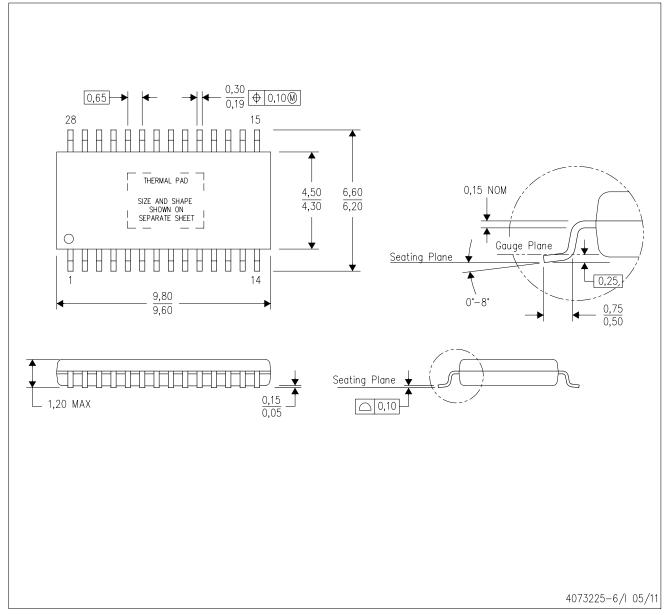

PWP (R-PDSO-G20)

### PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G20) PowerPAD™ SMALL PLASTIC OUTLINE

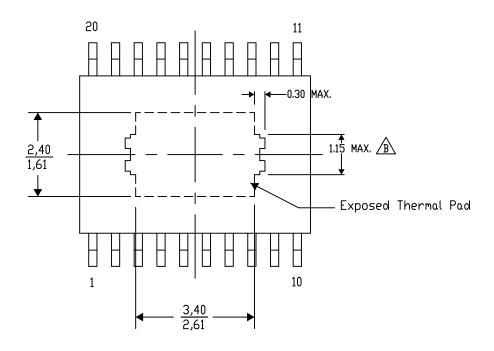

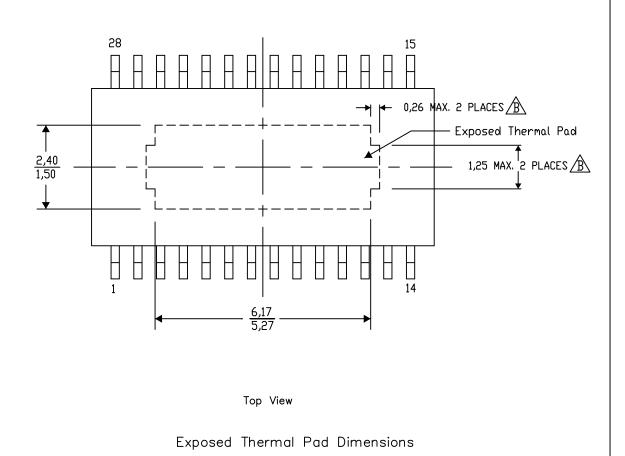

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-15/AG 08/13

NOTE: A. All linear dimensions are in millimeters

Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

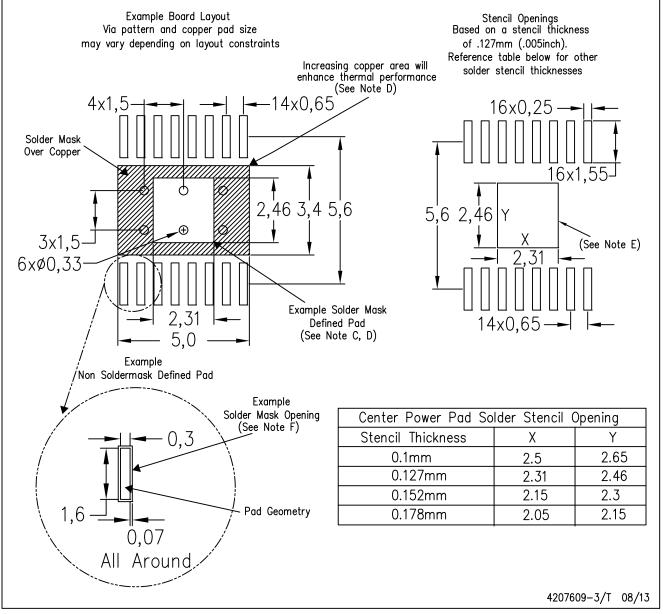

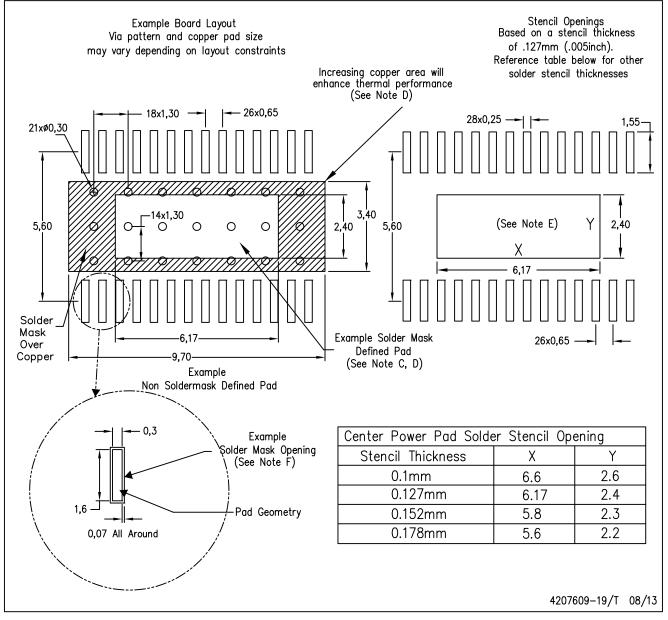

# PWP (R-PDSO-G20)

# PowerPAD™ PLASTIC SMALL OUTLINE

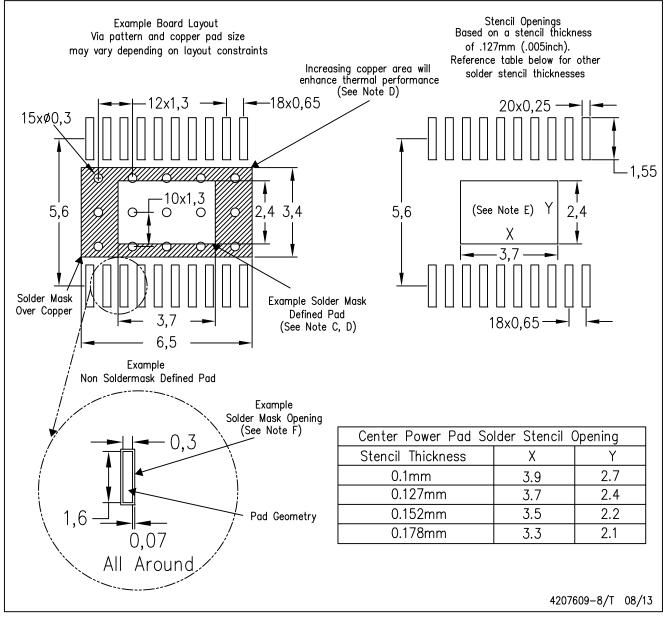

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PWP (R-PDSO-G14)

### PowerPAD ™ PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

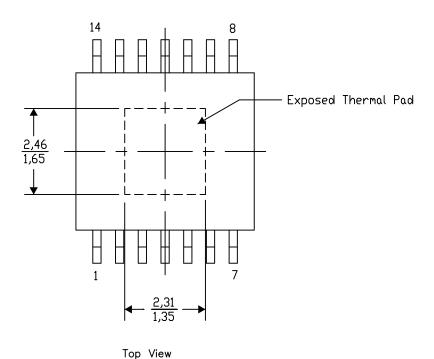

# PWP (R-PDSO-G14) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

4206332-2/AG 08/13

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

# PWP (R-PDSO-G14)

# PowerPAD™ PLASTIC SMALL OUTLINE

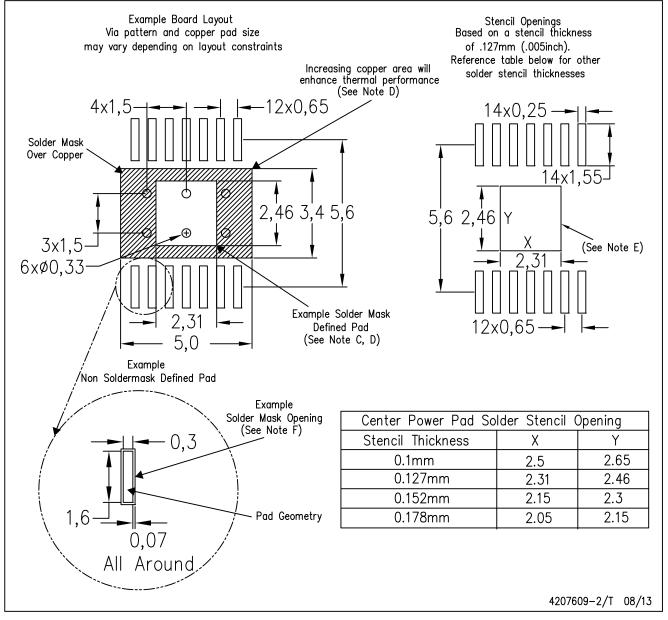

#### NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

# PWP (R-PDSO-G14) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

4206332-44/AG 08/13

NOTE: A. All linear dimensions are in millimeters

🛕 Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

PWP (R-PDSO-G16)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

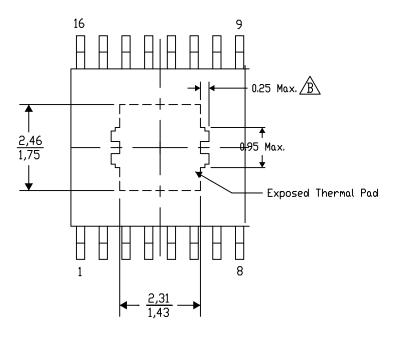

# PWP (R-PDSO-G16) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-6/AG 08/13

NOTE: A. All linear dimensions are in millimeters

🛕 Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

# PWP (R-PDSO-G16)

# PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PWP (R-PDSO-G28)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

4206332-33/AG 08/13

# PWP (R-PDSO-G28) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

B Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

# PWP (R-PDSO-G28)

# PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets.

- E. For specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>