# Ultra Low Power Boost Converter with Battery Management for Energy Harvester Applications

Check for Samples: bq25504

## FEATURES

- Ultra Low Power With High Efficiency DC/DC Boost Converter/Charger

- Continuous Energy Harvesting From Low Input Sources: V<sub>IN</sub> ≥ 80 mV(Typical)

- Ultra Low Quiescent Current: I<sub>Q</sub> < 330 nA (Typical)

- Cold-Start Voltage: V<sub>IN</sub> ≥ 330 mV (Typical)

- Programmable Dynamic Maximum Power Point Tracking (MPPT)

- Integrated Dynamic Maximum Power Point Tracking for Optimal Energy Extraction From a Variety of Energy Generation Sources

- Input Voltage Regulation Prevents Collapsing Input Source

- Energy Storage

- Energy can be Stored to Re-Chargeable Liion Batteries, Thin-film Batteries, Super-Capacitors, or Conventional Capacitors

- Battery Charging and Protection

- User Programmable Undervoltage and Overvoltage Levels

- On-Chip Temperature Sensor with

Programmable Overtemperature Shutoff

- Battery Status Output

- Battery Good Output Pin

- Programmable Threshold and Hysteresis

- Warn Attached Microcontrollers of Pending Loss of Power

- Can be Used to Enable/Disable System Loads

## APPLICATIONS

- Energy Harvesting

- Solar Charger

- Thermal Electric Generator (TEG) Harvesting

- Wireless Sensor Networks (WSN)

- Industrial Monitoring

- Environmental Monitoring

- Bridge and Structural Health Monitoring (SHM)

- Smart Building Controls

- Portable and Wearable Health Devices

- Entertainment System Remote Controls

## DESCRIPTION

The bq25504 is the first of a new family of intelligent integrated energy harvesting Nano-Power management solutions that are well suited for meeting the special needs of ultra low power applications. The product is specifically designed to efficiently acquire and manage the microwatts ( $\mu$ W) to miliwatts (mW) of power generated from a variety of DC sources like photovoltaic (solar) or thermal electric generators. The bq25504 is the first device of its kind to implement a highly efficient boost converter/charger targeted toward products and systems, such as wireless sensor networks (WSN) which have stringent power and operational demands. The design of the bq25504 starts with a DCDC boost converter/charger that requires only microwatts of power to begin operating.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **bq25504** SLUSAH0A-OCTOBER 2011-REVISED SEPTEMBER 2012

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION CONTINUED**

Once started, the boost converter/charger can effectively extract power from low voltage output harvesters such as thermoelectric generators (TEGs) or single or dual cell solar panels. The boost converter can be started with VIN as low as 330 mV, and once started, can continue to harvest energy down to  $V_{IN}$  = 80 mV.

The bq25504 also implements a programmable maximum power point tracking sampling network to optimize the transfer of power into the device. Sampling the VIN\_DC open circuit voltage is programmed using external resistors, and held with an external capacitor (CREF).

For example solar cells that operate at maximum power point (MPP) of 80% of their open circuit voltage, the resistor divider can be set to 80% of the VIN\_DC voltage and the network will control the VIN\_DC to operate near that sampled reference voltage. Alternatively, an external reference voltage can be provide by a MCU to produce a more complex MPPT algorithm.

The bq25504 was designed with the flexibility to support a variety of energy storage elements. The availability of the sources from which harvesters extract their energy can often be sporadic or time-varying. Systems will typically need some type of energy storage element, such as a re-chargeable battery, super capacitor, or conventional capacitor. The storage element will make certain constant power is available when needed for the systems. The storage element also allows the system to handle any peak currents that can not directly come from the input source.

To prevent damage to a customer's storage element, both maximum and minimum voltages are monitored against the user programmed undervoltage (UV) and overvoltage (OV) levels.

To further assist users in the strict management of their energy budgets, the bq25504 toggles the battery good flag to signal an attached microprocessor when the voltage on an energy storage battery or capacitor has dropped below a pre-set critical level. This should trigger the shedding of load currents to prevent the system from entering an undervoltage condition. The OV, UV and battery good thresholds are programmed independently.

All the capabilities of bq25504 are packed into a small foot-print 16-lead 3 mm x 3 mm QFN package.

# PART NO. PACKAGE ORDERING NUMBER (TAPE AND REEL)<sup>(1)</sup> PACKAGE MARKING QUANTITY bq25504 QFN 16 pin 3 mm x 3 mm BQ25504RGTR B5504 3000 BQ25504RGTT B5504 250

#### ORDERING INFORMATION

(1) The RGW package is available in tape on reel. Add R suffix to order quantities of 3000 parts per reel, T suffix for 250 parts per reel.

## **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

over operating free-air temperature range (unless otherwise noted)

|                              |                                                                                                                                                                                 | VAL  | UE   |   |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---|--|

|                              |                                                                                                                                                                                 | MIN  | UNIT |   |  |

| Input voltage                | VIN_DC, VOC_SAMP, VREF_SAMP, VBAT_OV, VBAT_UV, VRDIV,                                                                                                                           | -0.3 | 5.5  | V |  |

| Peak Input Power, PIN_PK     | Dut voltage         VIN_DC, VOC_SAMP, VREF_SAMP, VBAT_OV, VBAT_UV, VRDIV,           eak Input Power, PIN_PK         OK_HYST, OK_PROG, VBAT_OK, VBAT, VSTOR, LBST <sup>(2)</sup> |      |      |   |  |

| Operating junction temperatu | -40                                                                                                                                                                             | 125  | °C   |   |  |

| Storage temperature range,   | -65                                                                                                                                                                             | 150  | °C   |   |  |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to  $V_{SS}$ /ground terminal.

#### THERMAL INFORMATION

|                         | THERMAL METRIC <sup>(1)(2)</sup>             | bq25504       |       |

|-------------------------|----------------------------------------------|---------------|-------|

|                         |                                              | RGT (16 PINS) | UNITS |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 48.5          |       |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 63.9          |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 22            | °C/W  |

| Ψιτ                     | Junction-to-top characterization parameter   | 1.8           | C/W   |

| Ψјв                     | Junction-to-board characterization parameter | 22            |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 6.5           |       |

For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

For thermal estimates of this device based on PCB copper area, see the TI PCB Thermal Calculator.

#### **RECOMMENDED OPERATING CONDITIONS**

|                                     |                                                        | MIN  | NOM | MAX  | UNIT |

|-------------------------------------|--------------------------------------------------------|------|-----|------|------|

| V <sub>IN (DC)</sub>                | DC input voltage into VIN_DC <sup>(1)</sup>            | 0.13 |     | 3    | V    |

| VBAT                                | Battery voltage range <sup>(2)</sup>                   | 2.5  |     | 5.25 | V    |

| C <sub>HVR</sub>                    | Input capacitance                                      | 4.23 | 4.7 | 5.17 | μF   |

| C <sub>STOR</sub>                   | Storage capacitance                                    | 4.23 | 4.7 | 5.17 | μF   |

| C <sub>BAT</sub>                    | Battery pin capacitance or equivalent battery capacity | 100  |     |      | μF   |

| C <sub>REF</sub>                    | Sampled reference storage capacitance                  | 9    | 10  | 11   | nF   |

| R <sub>OC1</sub> + R <sub>OC2</sub> | Total resistance for setting for MPPT reference.       | 18   | 20  | 22   | MΩ   |

| $R_{OK}1 + R_{OK}2 + R_{OK3}$       | Total resistance for setting reference voltage.        | 9    | 10  | 11   | MΩ   |

| R <sub>UV1</sub> + R <sub>UV2</sub> | Total resistance for setting reference voltage.        | 9    | 10  | 11   | MΩ   |

| R <sub>OV1</sub> + R <sub>OV2</sub> | Total resistance for setting reference voltage.        | 9    | 10  | 11   | MΩ   |

| L <sub>BST</sub>                    | Input inductance                                       | 19.8 | 22  | 24.2 | μH   |

| T <sub>A</sub>                      | Operating free air ambient temperature                 | -40  |     | 85   | °C   |

| TJ                                  | Operating junction temperature                         | -40  |     | 105  | °C   |

(1) Maximum input power ≤ 300 mW. Cold start has been completed

(2) VBAT\_OV setting must be higher than VIN\_DC

## **ELECTRICAL CHARACTERISTICS**

Over recommended temperature range, typical values are at T<sub>A</sub> = 25°C. Unless otherwise noted, specifications apply for conditions of VIN\_DC = 1.2V, VBAT = VSTOR = 3V. External components  $L_{BST} = 22 \mu$ H,  $C_{HVR} = 4.7 \mu$ F  $C_{STOR} = 4.7 \mu$ F.

|                         | PARAMETER                                                                              | TEST CONDITIONS                                                                          | MIN  | TYP  | MAX  | UNIT |

|-------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| BOOST CONVERT           | TER \ CHARGER STAGE                                                                    |                                                                                          |      |      |      |      |

| V <sub>IN(DC)</sub>     | DC input voltage into VIN_DC                                                           | Cold-start completed                                                                     | 130  |      | 3000 | mV   |

| I <sub>IN(DC)</sub>     | Peak Current flowing from V <sub>IN</sub> into VIN_DC input                            | 0.5V < V <sub>IN</sub> < 3 V; VSTOR = 4.2 V                                              |      | 200  | 300  | mA   |

| P <sub>IN</sub>         | Input power range for normal charging                                                  | VBAT > VIN_DC; VIN_DC = 0.5 V                                                            | 0.01 |      | 300  | mW   |

| V <sub>IN(CS)</sub>     | Cold-start Voltage. Input voltage that will start<br>charging of VSTOR                 | $\label{eq:VBAT_VBAT_UV; VSTOR = 0 V;} \\ 0^{\circ}C < T_A < 85^{\circ}C \\ \end{array}$ |      | 330  | 450  | mV   |

| P <sub>IN(CS)</sub>     | Minimum cold-start input power to start normal<br>charging                             | VBAT < VBAT_UV; VSTOR = 0 V; Input source impedance 0 $\Omega$                           |      | 10   | 50   | μW   |

| V <sub>STOR_CHGEN</sub> | Voltage on VSTOR when cold start operation ends<br>and normal charger operation begins |                                                                                          | 1.6  | 1.77 | 1.95 | V    |

| R <sub>BAT(on)</sub>    | Resistance of switch between VBAT and VSTOR when turned on.                            | VBAT = 4.2 V; VSTOR load = 50 mA                                                         |      |      | 2    | Ω    |

|                         | Observed Law Dide switch ON secietarias                                                | VBAT = 2.1 V                                                                             |      |      | 2    | 0    |

|                         | Charger Low Side switch ON resistance                                                  | VBAT = 4.2 V                                                                             |      |      | 2    | Ω    |

| R <sub>DS(on)</sub>     | Observe and the Ulick Olida and the Obligation                                         | VBAT = 2.1 V                                                                             |      |      | 5    | 0    |

|                         | Charger rectifier High Side switch ON resistance                                       | VBAT = 4.2 V                                                                             |      |      | 5    | Ω    |

| f <sub>SW_BST</sub>     | Boost converter mode switching frequency                                               |                                                                                          |      |      | 1    | MHz  |

SLUSAH0A-OCTOBER 2011-REVISED SEPTEMBER 2012

#### Texas Instruments

www.ti.com

## **ELECTRICAL CHARACTERISTICS (continued)**

Over recommended temperature range, typical values are at  $T_A = 25^{\circ}$ C. Unless otherwise noted, specifications apply for conditions of VIN\_DC = 1.2V, VBAT = VSTOR = 3V. External components  $L_{BST} = 22 \mu$ H,  $C_{HVR} = 4.7 \mu$ F  $C_{STOR} = 4.7 \mu$ F.

|                           | PARAMETER                                                                                                                     | TEST CONDITIONS                                                              | MIN            | TYP  | MAX                 | UNIT |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------|------|---------------------|------|

| BATTERY MANAGE            | MENT                                                                                                                          |                                                                              |                |      |                     |      |

| 1                         | Leakage on VBAT pin                                                                                                           | VBAT = 2.1 V; VBAT_UV = 2.3 V, $T_J = 25^{\circ}C$<br>VSTOR = 0 V            |                | 1    | 5                   | nA   |

| I <sub>VBAT</sub>         | Leakage on VBAT pin                                                                                                           | VBAT = 2.1 V; VBAT_UV = 2.3 V,<br>-40°C < T <sub>J</sub> < 65°C, VSTOR = 0 V |                |      | 80                  | nA   |

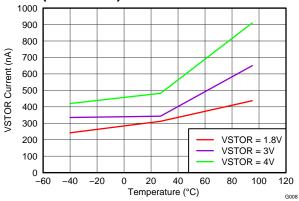

|                           | VSTOR Quiescent current Charger Shutdown in UV Condition                                                                      | VIN_DC = 0V;<br>VBAT < VBAT_UV = 2.4V;<br>VSTOR = 2.2V, No load on VBAT      |                | 330  | 750                 | nA   |

| IVSTOR                    | VSTOR Quiescent current Charger Shutdown in OV Condition                                                                      | VIN_DC = 0V,<br>VBAT > VBAT_OV, VSTOR = 4.25,<br>No load on VBAT             |                | 570  | 1400                | nA   |

| V <sub>BAT_OV</sub>       | Programmable voltage range for overvoltage threshold (Battery voltage is rising)                                              | VBAT increasing                                                              | 2.5            |      | 5.25                | V    |

| V <sub>BAT_OV_HYST</sub>  | Battery voltage overvoltage hysteresis threshold<br>(Battery voltage is falling), internal threshold                          | VBAT decreasing                                                              | 18             | 35   | 89                  | mV   |

| V <sub>BAT_UV</sub>       | Programmable voltage range for under voltage threshold (Battery voltage is falling)                                           | VBAT decreasing; VBAT_UV > V <sub>Bias</sub>                                 | 2.2            |      | VBAT_OV             | V    |

| V <sub>BAT_UV_HYST</sub>  | Battery under voltage threshold hysteresis, internal thershold                                                                | VBAT increasing                                                              | 40             | 80   | 125                 | mV   |

| V <sub>BAT_OK</sub>       | Programmable voltage range for threshold voltage<br>for high to low transition of digital signal indicating<br>battery is OK, | VBAT decreasing                                                              | VBAT_UV        |      | VBAT_OV             | V    |

| V <sub>BAT_OK_HYST</sub>  | Programmable voltage range for threshold voltage<br>for low to high transition of digital signal indicating<br>battery is OK, | VBAT increasing                                                              | 50             |      | VBAT_OV-<br>VBAT_UV | mV   |

| V <sub>BAT_ACCURACY</sub> | Overall Accuracy for threshold values, UV, OV, VBAT_OK                                                                        | Selected resistors are 0.1% tolerance                                        | -5%            |      | 5%                  |      |

| V <sub>BAT_OKH</sub>      | VBAT OK (High) threshold voltage                                                                                              | Load = 10 µA                                                                 |                |      | VSTOR-<br>200mV     | V    |

| V <sub>BAT_OKL</sub>      | VBAT OK (Low) threshold voltage                                                                                               | Load = 10 µA                                                                 |                |      | 100                 | mV   |

| TSD_PROTL                 | The temperature at which the boost converter is                                                                               | OT_Prog = LO                                                                 |                | 65   |                     | °C   |

| TSD_PROTH                 | disabled and the switch between VBAT and VSTOR is disconnected to protect the battery                                         | OT_Prog = HI                                                                 |                | 120  |                     |      |

| OT Days                   | Voltage for OT_PROG High setting                                                                                              |                                                                              | 2              |      |                     | V    |

| OT_Prog                   | Voltage for OT_PROG Low setting                                                                                               |                                                                              |                |      | 0.3                 | V    |

| BIAS and MPPT CO          | NTROL STAGE                                                                                                                   |                                                                              | -              |      |                     |      |

| VOC_sample                | Sampling period of VIN_DC open circuit voltage                                                                                |                                                                              |                | 16   |                     | s    |

| VOC_Settling              | Sampling period of VIN_DC open circuit voltage                                                                                |                                                                              |                | 256  |                     | ms   |

| VIN_Reg                   | Regulation of VIN_DC during charging                                                                                          | 0.5 V <v<sub>IN &lt; 3 V; I<sub>IN</sub> (DC) = 10 mA</v<sub>                | -10%           |      | 10%                 |      |

| VIN_shutoff               | DC input voltage into VIN_DC when charger is<br>turned off                                                                    |                                                                              | 40             | 80   | 130                 | mV   |

| MPPT_Disable              | Threshold on VOC_SAMP to disable MPPT<br>functionality                                                                        |                                                                              | VSTOR-15<br>mV |      |                     | V    |

| VBIAS                     | Voltage node which is used as reference for the<br>programmable voltage thresholds                                            | VIN_DC ≥ 0.5V; VSTOR ≥ 1.8 V                                                 | 1.21           | 1.25 | 1.27                | V    |

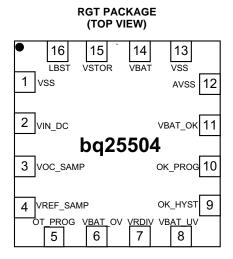

## **DEVICE INFORMATION**

#### PIN FUNCTIONS

|     | PIN       | I/O TYPE | DESCRIPTION                                                                                                                                                                                                            |

|-----|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME      |          | DESCRIPTION                                                                                                                                                                                                            |

| 1   | VSS       | Input    | General ground connection for the device                                                                                                                                                                               |

| 2   | VIN_DC    | Input    | DC voltage input from energy harvesters                                                                                                                                                                                |

| 3   | VOC_SAMP  | Input    | Sampling pin for MPPT network. To disable MPPT, connect to VSTOR                                                                                                                                                       |

| 4   | VREF_SAMP | Input    | Switched node for holding the reference set by resistors on VOC_SAMP for MPPT. When MPPT is disabled, VREF_SAMP should not be left floating but either either be tied to an external reference voltage or tied to GND. |

| 5   | OT_PROG   | Input    | Digital Programming input for overtemperature threshold                                                                                                                                                                |

| 6   | VBAT_OV   | Input    | Resistor divider input for over voltage threshold                                                                                                                                                                      |

| 7   | VRDIV     | Output   | Resistor divider biasing voltage.                                                                                                                                                                                      |

| 8   | VBAT_UV   | Input    | Resistor divider input for under voltage threshold                                                                                                                                                                     |

| 9   | OK_HYST   | Input    | Resistor divider input for VBAT_OK hysteresis threshold                                                                                                                                                                |

| 10  | OK_PROG   | Input    | Resistor divider input for VBAT_OK threshold                                                                                                                                                                           |

| 11  | VBAT_OK   | Output   | Digital battery good indicator referenced to VSTOR pin                                                                                                                                                                 |

| 12  | AVSS      | Supply   | Signal ground connection for the device                                                                                                                                                                                |

| 13  | VSS       | Supply   | General ground connection for the device                                                                                                                                                                               |

| 14  | VBAT      | I/O      | Connection for storage elements                                                                                                                                                                                        |

| 15  | VSTOR     | Output   | Connection for the system load, output of the boost converter                                                                                                                                                          |

| 16  | LBST      | Input    | Inductor connection for the boost converter switching node                                                                                                                                                             |

SLUSAH0A-OCTOBER 2011-REVISED SEPTEMBER 2012

www.ti.com

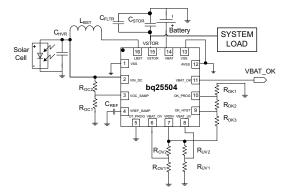

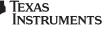

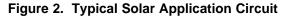

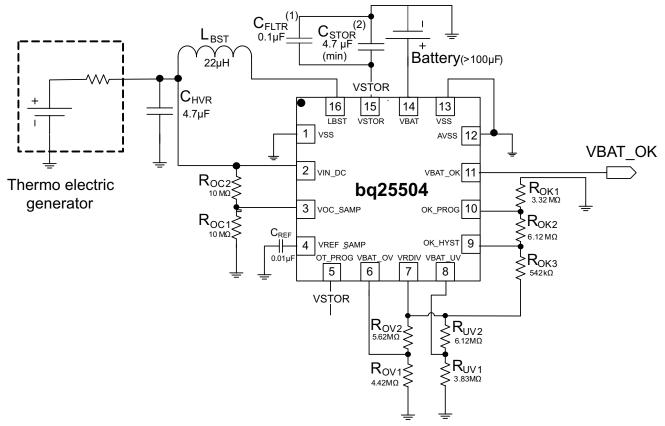

## **TYPICAL APPLICATION CIRCUITS**

$\begin{array}{l} \text{VIN\_DC} = 1.2 \text{ V, } C_{\text{STOR}} = 4.7 \ \mu\text{F}, \ L_{\text{BST}} = 22 \ \mu\text{H}, \ C_{\text{HVR}} = 4.7 \ \mu\text{F}, \ C_{\text{REF}} = 10 \ \text{nF}, \ \text{TSD\_PROTL} \ (65^{\circ}\text{C}), \\ \text{MPPT} \ (\text{V}_{\text{OC}}) = 80\% \ \text{VBAT\_OV} = 3.1 \ \text{V}, \ \text{VBAT\_UV} = 2.2 \ \text{V}, \ \text{VBAT\_OK} = 2.4 \ \text{V}, \ \text{VBAT\_OK\_HYST} = 2.8 \ \text{V}, \\ \text{R}_{\text{OK1}} = 4.42 \ \text{M}\Omega, \ \text{R}_{\text{OK2}} = 4.22 \ \text{M}\Omega, \ \text{R}_{\text{OK3}} = 1.43 \ \text{M}\Omega, \ \text{R}_{\text{OV1}} = 5.9 \ \text{M}\Omega, \ \text{R}_{\text{OV2}} = 4.02 \ \text{M}\Omega, \\ \end{array}$

$R_{UV1}$ = 5.6 M $\Omega$ ,  $R_{UV2}$  = 4.42 M $\Omega$ ,  $R_{OC1}$ = 15.62 M $\Omega$ ,  $R_{OC2}$  = 4.42 M $\Omega$

- (1) Place close as possible to IC pin 15 (VSTOR) and pin 13 (VSS)

- (2) See the Capacitor Selection section for guidance on sizing  $C_{\mbox{STOR}}$

$\begin{array}{l} \text{VIN}\_\text{DC} = 0.5 \text{ V}, \ \text{C}_{\text{STOR}} = 4.7 \ \mu\text{F}, \ \text{L}_{\text{BST}} = 22 \ \mu\text{H}, \ \text{C}_{\text{HVR}} = 4.7 \ \mu\text{F}, \ \text{C}_{\text{REF}} = 10 \ \text{nF}, \ \text{TSD}\_\text{PROTH} \ (120^\circ\text{C}), \\ \text{MPPT} \ (\text{V}_{\text{OC}}) = 50\% \ \text{VBAT}\_\text{OV} = 4.2 \ \text{V}, \ \text{VBAT}\_\text{UV} = 3.2 \ \text{V}, \ \text{VBAT}\_\text{OK} = 3.5 \ \text{V}, \ \text{VBAT}\_\text{OK}\_\text{HYST} = 3.7 \ \text{V}, \\ \text{R}_{\text{OK1}} = 3.32 \ \text{M}\Omega, \ \text{R}_{\text{OK2}} = 6.12 \ \text{M}\Omega, \ \text{R}_{\text{OK3}} = 0.542 \ \text{M}\Omega, \ \text{R}_{\text{OV1}} = 4.42 \ \text{M}\Omega, \ \text{R}_{\text{OV2}} = 5.62 \ \text{M}\Omega, \\ \text{R}_{\text{UV1}} = 3.83 \ \text{M}\Omega, \ \text{R}_{\text{UV2}} = 6.12 \ \text{M}\Omega, \ \text{R}_{\text{OC1}} = 10 \ \text{M}\Omega, \ \text{R}_{\text{OC2}} = 10 \ \text{M}\Omega \end{array}$

- (1) Place close as possible to IC pin 15 (VSTOR) and pin 13 (VSS)

- (2) See the Capacitor Selection section for guidance on sizing  $C_{\mbox{\scriptsize STOR}}$

Figure 3. Typical TEG Application Circuit

## bq25504

SLUSAH0A-OCTOBER 2011-REVISED SEPTEMBER 2012

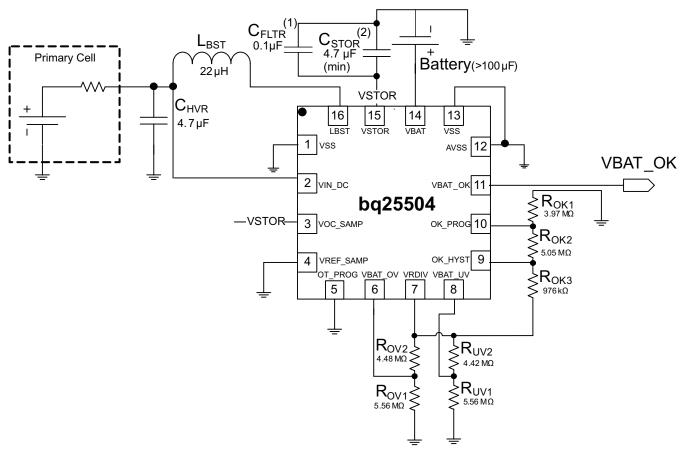

$$\begin{split} \text{VIN}_\text{DC} &= 1.2 \text{ V}, \text{ } \text{C}_{\text{STOR}} = 4.7 \text{ } \mu\text{F}, \text{ } \text{L}_{\text{BST}} = 22 \text{ } \mu\text{H}, \text{ } \text{C}_{\text{HVR}} = 4.7 \text{ } \mu\text{F}, \text{ } \text{TSD}_\text{PROTL} \text{ (65°C)}, \\ \text{MPPT} (\text{V}_{\text{OC}}) &= \text{Disabled VBAT}_\text{OV} = 3.3 \text{ V}, \text{ } \text{VBAT}_\text{UV} = 2.2 \text{ V}, \text{ } \text{VBAT}_\text{OK} = 2.8 \text{ V}, \text{ } \text{VBAT}_\text{OK}_\text{HYST} = 3.1 \text{ V}, \\ \text{R}_{\text{OK1}} = 3.97 \text{ } \text{M}\Omega, \text{ } \text{R}_{\text{OK2}} = 5.05 \text{ } \text{M}\Omega, \text{ } \text{R}_{\text{OK3}} = 0.976 \text{ } \text{M}\Omega, \text{ } \text{R}_{\text{OV1}} = 5.56 \text{ } \text{M}\Omega, \\ \text{R}_{\text{OV2}} = 4.48 \text{ } \text{M}\Omega, \text{ } \text{R}_{\text{UV1}} = 5.56 \text{ } \text{M}\Omega, \text{ } \text{R}_{\text{UV2}} = 4.42 \text{ } \text{M}\Omega \end{split}$$

- (1) Place close as possible to IC pin 15 (VSTOR) and pin 13 (VSS)

- (2) See the Capacitor Selection section for guidance on sizing  $C_{\mbox{STOR}}$

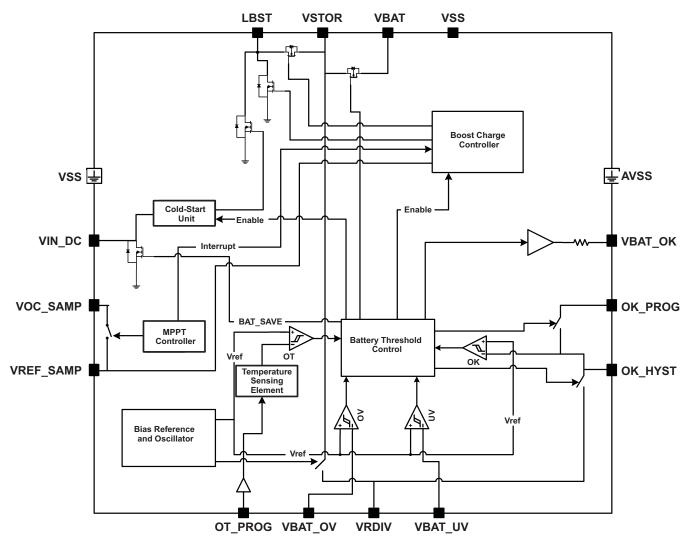

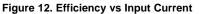

HIGH-LEVEL FUNCTIONAL BLOCK DIAGRAM

Figure 5. High-level Functional Diagram

TEXAS INSTRUMENTS

www.ti.com

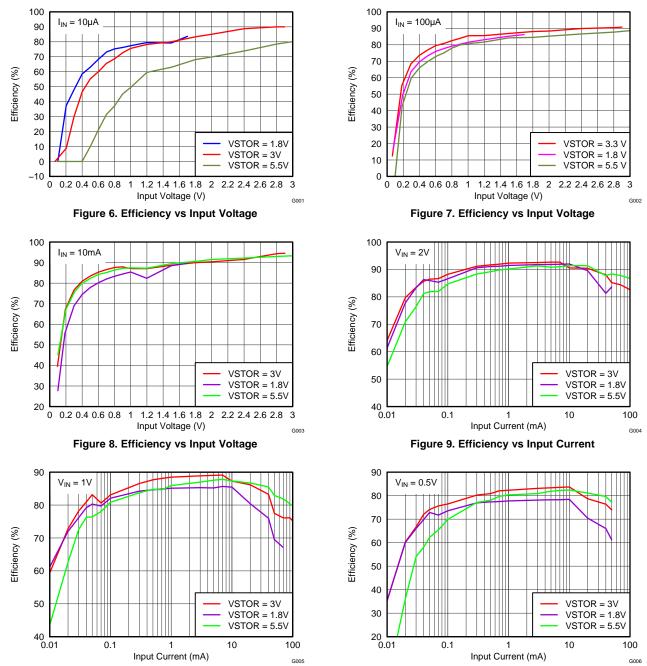

## **TYPICAL CHARACTERISTICS**

Figure 10. Efficiency vs Input Current

Figure 11. Efficiency vs Input Current

bq25504 SLUSAH0A – OCTOBER 2011 – REVISED SEPTEMBER 2012

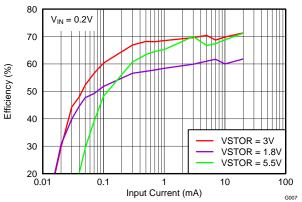

**TYPICAL CHARACTERISTICS (continued)**

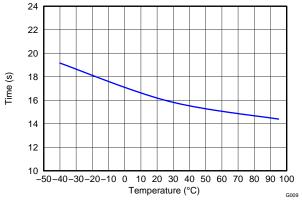

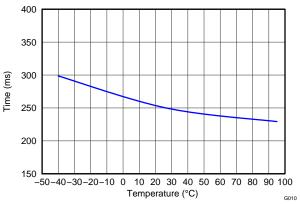

Figure 14. Sample Period vs Temperature

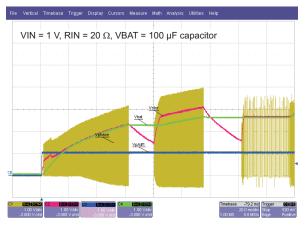

Figure 16. Example of Startup with no Battery and 10 K\Omega Load

Figure 15. Settling Period vs Temperature

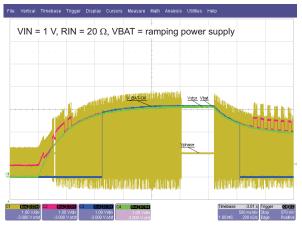

#### Figure 17. Example of VBAT\_OK Operation, Ramping Battery From 0 V to 3.1 V

# bq25504

SLUSAH0A-OCTOBER 2011-REVISED SEPTEMBER 2012

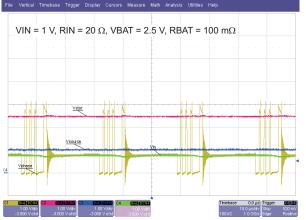

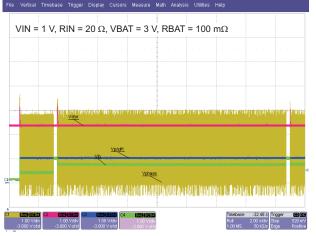

Figure 18. Example of PFM Switching Converter Waveform

Figure 19. Example of Output Ripple Voltage During Operation at O V Setting

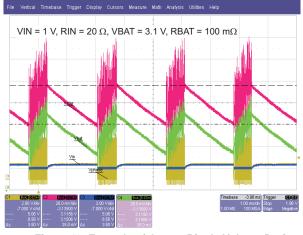

Figure 20. Example of Startup When VBAT is Held Below UV Setting

Figure 21. Example of Sampling Time for MPPT Operation

**TYPICAL CHARACTERISTICS (continued)**

www.ti.com

Texas

## DETAILED PRINCIPLE OF OPERATION

### OVERVIEW

The bq25504 is an ultra low quiescent current, efficient synchronous boost converter/charger. The boost converter is based on a switching regulator architecture which maximizes efficiency while minimizing start-up and operation power. The bq25504 uses pulse frequency modulation (PFM) to maintain efficiency, even under light load conditions. In addition, bq25504 also implements battery protection features so that either rechargeable batteries or capacitors can be used as energy storage elements. Figure 5 is a high-level functional block diagram which highlights most of the major functional blocks inside the bq25504.

#### Intended Operation

The bq25504's priority is to charge up the VSTOR capacitor, CSTOR, then power additional internal circuitry from VSTOR. When a storage element is attached (i.e. hot-plugged), the bq25504 will first attempt to charge up CSTOR from the storage element by turning on the internal PFET between the VSTOR and VBAT pins for approximately 45ms. See Storage Element section for guidance on selecting the storage element. If a system load tied to VSTOR prevent the storage element from charging VSTOR within 45 ms typical, it is recommended to add an external PFET between the system load and VSTOR. An inverted VBAT\_OK signal can be used to drive the gate of the PFET. Once the VSTOR pin voltage reaches the user set under voltage threshold (VBAT\_UV), the internal PFET stays on and the boost converter / charger begins to charge the storage element if there is sufficient power available at the VIN\_DC pin, as explained below.If VSTOR does not reach VBAT\_UV within 45 ms typical, then the PFET turns off and the Cold-Start subsystem turns on, also as explained below.

When no input source is attached, the VSTOR node should be discharged to ground before attaching a storage element. Hot-plugging a storage element that is charged (e.g., the battery protector is closed) and with VSTOR above ground results in the PFET between VSTOR and VBAT remaining off until a input source is attached and charging resumes. In addition, if a system load attached to VSTOR has fast transients that could pull VSTOR below VBAT\_UV, the internal PFET switch will turn off in order to recharge the CSTOR capacitor. See the application section for guidance on sizing the VSTOR and/or VBAT capacitance to account for transients. If the voltage applied at VIN\_DC is greater than VSTOR or VBAT then current may flow until the voltage at the input is reduced or the voltage at VSTOR and VBAT rise. This is considered an abnormal condition and the boost converter/charger does not operate.

#### Cold -Start Operation (VSTOR < V<sub>STOR\_CHGN</sub> and VIN\_DC > V<sub>IN(CS)</sub>)

When the voltage at pin VIN\_DC exceeds the minimum input voltage with sufficient power, the cold-start subsystem turns on. The cold-start subsystem is essentially an unregulated boost converter. When the storage capacitor, CSTOR, voltage reaches  $V_{\text{STOR_CHGEN}}$  (1.8V typical), the main boost regulator starts up. The VSTOR voltage from the main boost regulator is now compared against battery undervoltage threshold (VBAT\_UV). When the VBAT\_UV threshold is reached, the PMOS switch between VSTOR and VBAT is turned on, which allows the energy storage element attached to VBAT to charge up. Cold start is not as efficient as the main boost regulator. If there is not sufficient power available it is possible that the cold start continuously runs and the VSTOR output does not increase to 1.8 V and start the main boost regulator.

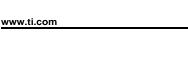

Figure 22 shows the key threshold voltages. The battery management thresholds are explained later is this section.

## Boost Converter, Charger Operation (VSTOR > $V_{STOR_{CHGN}}$ and VIN\_DC > $V_{IN(DC)-MIN}$ )

The boost converter in bq25504 is used to charge the storage element attached at VBAT with the energy available from the DC input source. For the first 32 ms (typical) after the main converter is turned ON, the charger is disabled to let the input go up to its open-circuit voltage. This is needed to get the reference voltage which will be used for the remainder of the charger operation till the next MPPT sampling cycle turns ON. The boost converter employs pulse frequency modulation (PFM) mode of control to regulate the input voltage (VIN\_DC) close to the desired reference voltage regulation is obtained by transferring charge from the input to VSTOR only when the input voltage is higher than the voltage on pin VREF\_SAMP. The current through the inductor is controlled through internal current sense circuitry. The peak current in the inductor is dithered internally to set levels to maintain high efficiency of the converter across a wide input current range. The converter nominally transfers up to a average of 100 mA of input current. The boost converter is disabled when the voltage on VSTOR reaches the OV condition to protect the battery connected at VBAT from overcharging.

## bq25504

SLUSAH0A-OCTOBER 2011-REVISED SEPTEMBER 2012

(1)

#### **Maximum Power Point Tracking**

Maximum power point tracking (MPPT) is implemented in bq25504 in order to maximize the power extracted from an energy harvester source. MPPT is performed by periodically sampling a ratio of the open-circuit voltage of the energy harvester and using that as the reference voltage (VREF\_SAMP) to the boost converter. The sampling ratio can be externally programmed using the resistors  $R_{OC1}$  and  $R_{OC2}$ . For solar harvesters, the resistive division ratio can be typically set between 0.7-0.8 and for thermoelectric harvesters; a resistive division ratio of 0.5 is typically used. The exact ratio for MPPT can be optimized to meet the needs of the input source being used.

Internally, the boost converter modulates the effective impedance of the energy transfer circuitry to regulate the input voltage (VIN\_DC) to the sampled reference voltage (VREF\_SAMP). A new reference voltage is obtained every 16s by periodically disabling the charger for 256ms and sampling a ratio of the open-circuit voltage. The reference voltage is set by the following expression:

VREF\_SAMP = VIN\_DC(OpenCircuit)

$$\left(\frac{R_{OC1}}{R_{OC1} + R_{OC2}}\right)$$

The internal MPPT circuitry and the periodic sampling of VIN\_DC can be disabled by tying the VOC\_SAMP pin to VSTOR. When disabled an external reference voltage can be fed to the VREF\_SAMP pin. The boost converter will then regulate VIN\_DC to the externally provided reference. If input regulation is not desired, VREF\_SAMP can be tied to GND.

#### Storage Element

When operating as a charger, the main storage elements must be connected to VBAT pin. Many types of elements can be used, such as capacitors, super capacitors or various battery chemistries. A storage element with 100uF equivalent capacitance is required to filter the pulse currents of the PFM switching converter. The equivalent capacitance of a battery can be computed as computed as  $C_{EQ} = 2 \times \text{mAHr}_{\text{BAT}(CHRGD)} \times 3600 \text{ s/Hr} / V_{\text{BAT}(CHRGD)}$ . In order for the storage element to be able to charge VSTOR capacitor (CSTOR) with in the 45ms window at hot-plug; therefore preventing the IC from entering cold start. The time constant created by he storage element's series resistance (plus the resistance of the internal PFET switch) and equivalent capacitance must be less than 45 ms (typical). For example, a battery's resistance can be computed as  $R_{BAT} = V_{BAT} / I_{BAT(CONTIUOUS)}$  from the battery specifications. To take full advantage of the battery management, the load is normally tied to the VSTOR pin and not the VBAT pin. Also, if there are large load transients or the storage element has significant impedance then it may be necessary to increase the CSTOR capacitor from the 4.7uF minimum or add additional capacitance to VBAT in order to prevent a droop in the VSTOR voltage. See Capacitor Selection section in Application Information section for guidance on sizing the capacitor.

#### **Battery Management**

In this section the battery management functionality of the bq25504 integrated circuit (IC) is presented. The IC has internal circuitry to manage the voltage across the storage element and to optimize the charging of the storage element. For successfully extracting energy from the source, three different threshold voltages must be programmed using external resistors, namely the under voltage (UV) threshold, battery good threshold (VBAT\_OK) and over voltage (OV) threshold. The three threshold voltages determine the region of operation of the IC. Figure 22 shows a plot of the voltage at the VSTOR pin and the various threshold voltages. For the best operation of the system, the VBAT\_OK should be used to determine when a load can be applied or removed. A detailed description of the three voltage thresholds and the procedure for designing the external resistors for setting the three voltage thresholds are described next.

**NSTRUMENTS**

Figure 22. Figure Shows the Relative Position of Various Threshold Voltages (Threshold Voltages are From Typical Solar Application Circuit in Figure 2)

## Battery Undervoltage Protection

To prevent rechargeable batteries from being deeply discharged and damaged, and to prevent completely depleting charge from a capacitive storage element, the undervoltage (VBAT\_UV) threshold must be set using external resistors. The VBAT\_UV threshold voltage when the battery voltage is decreasing is given by Equation 2:

$$VBAT_UV = VBIAS \left(1 + \frac{R_{UV2}}{R_{UV1}}\right)$$

(2)

The sum of the resistors should be approximately, 10 M $\Omega$  that is,  $R_{UV1} + R_{UV2} = 10 M\Omega$ . The undervoltage threshold when battery voltage is increasing is given by UV\_HYST. It is internal set to the under voltage threshold plus an internal hysteresis voltage denoted by VBAT\_UV\_HYST. For proper functioning of the IC and the overall system, the load must be connected to the VSTOR pin while the storage element must be connected to the VBAT pin. Once the VSTOR pin voltage goes above the UV\_HYST threshold, the VSTOR pin and the VBAT pins are shorted. The switch remains closed until the VSTOR pin voltage falls below the under voltage threshold. The VBAT\_UV threshold should be considered a fail safe to the system and the system load should be removed or reduced based on the VBAT\_OK signal.

## Battery Overvoltage Protection

To prevent rechargeable batteries from being exposed to excessive charging voltages and to prevent over charging a capacitive storage element, the over-voltage (VBAT\_OV) threshold level must be set using external resistors. This is also the voltage value to which the charger will regulate the VSTOR/VBAT pin when the input has sufficient power. The VBAT\_OV threshold when the battery voltage is rising is given by Equation 3:

$$VBAT_OV = \frac{3}{2}VBIAS \left(1 + \frac{R_{OV2}}{R_{OV1}}\right)$$

(3)

bq25504 SLUSAH0A-OCTOBER 2011-REVISED SEPTEMBER 2012

www.ti.com

The sum of the resistors should be approximately 10 M $\Omega$  that is,  $R_{OV1} + R_{OV2} = 10 M\Omega$ . The overvoltage threshold when battery voltage is decreasing is given by OV\_HYST. It is internal set to the over voltage threshold minus an internal hysteresis voltage denoted by VBAT\_OV\_HYST. Once the voltage at the battery exceeds VBAT\_OV threshold, the boost converter is disabled. The charger will start again once the battery voltage falls below the VBAT\_OV\_HYST level. When there is excessive input energy, the VBAT pin voltage will ripple between the VBAT\_OV and the VBAT\_OV\_HYST levels.

#### CAUTION

If VIN\_DC is higher than VSTOR and VSTOR is higher than VBAT\_OV, the input VIN\_DC is pulled to ground through a small resistance to stop further charging of the attached battery or capacitor. It is critical that if this case is expected, the impedance of the source attached to VIN\_DC be higher than 20  $\Omega$  and not a low impedance source.

#### Battery Voltage in Operating Range (VBAT\_OK Output)

The IC allows the user to set a programmable voltage independent of the overvoltage and undervoltage settings to indicate whether the VSTOR voltage (and therefore the VBAT voltage when the PFET between the two pins is turned on) is at an acceptable level. When the battery voltage is decreasing the threshold is set by Equation 4

$$VBAT_OK_PROG = VBIAS \left(1 + \frac{R_{OK2}}{R_{OK1}}\right)$$

(4)

When the battery voltage is increasing, the threshold is set by Equation 5

$$VBAT_OK_HYST = VBIAS\left(1 + \frac{R_{OK2} + R_{OK3}}{R_{OK1}}\right)$$

(5)

The sum of the resistors should be approximately 10 M $\Omega$  i.e.,  $R_{OK1} + R_{OK2} + R_{OK3} = 10 M\Omega$ . The logic high level of this signal is equal to the VSTOR voltage and the logic low level is ground. The logic high level has ~20 K $\Omega$  internally in series to limit the available current to prevent MCU damage until it is fully powered. The VBAT\_OK\_PROG threshold must be greater than or equal to the UV threshold. For the best operation of the system, the VBAT\_OK should be setup to drive an external PFET between VSTOR and the system load in order to determine when the load can be applied or removed to optimize the storage element capacity.

#### Thermal Shutdown

Rechargeable Li-ion batteries need protection from damage due to operation at elevated temperatures. The application should provide this battery protection and ensure that the ambient temperature is never elevated greater than the expected operational range of 85°C.

The bq25504 uses an integrated temperature sensor to monitor the junction temperature of the device. If the OT\_PROG pin is tied low, then the temperature threshold for thermal protection is set to TSD\_ProtL which is 65°C typically. If the OT\_PROG is tied high, then the temperature is set to TSD\_ProtH which is 120°C typically. Once the temperature threshold is exceeded, the boost converter/charger is disabled and charging ceases. Once the temperature of the device drops below this threshold, the boost converter and or charger can resume operation. To avoid unstable operation near the overtemp threshold, a built-in hysteresis of approximately 5°C has been implemented. Care should be taken to not over discharge the battery in this condition since the boost converter/charger is disabled. However, if the supply voltage drops to the VBAT\_UV setting, then the switch between VBAT and VSTOR will open and protect the battery even if the device is in thermal shutdown.

## **APPLICATION INFORMATION**

#### INDUCTOR SELECTION

For the bq25504 to operate properly, an inductor of appropriate value must be connected between Pin 16 (LBST) and Pin 2 (VIN\_DC) for the boost converter.

For the boost converter and or charger, the inductor must have an inductance =  $22 \mu$ H and have a peak current capability of  $\geq 250$  mA with the minimum series resistance to keep high efficiency.

## CAPACITOR SELECTION

In general, all the capacitors need to be low leakage. Any leakage the capacitors have will reduce efficiency, increase the quiescent current and diminish the effectiveness of the IC for energy harvesting.

#### VREF\_SAMP Capacitance:

The MPPT operation depends on the sampled value of the open circuit voltage and the input regulation follows the voltage stored on the CREF capacitor. This capacitor is sensitive to leakage since the holding period is around 16 seconds. As the capacitor voltage drops due to any leakage, the input regulation voltage also drops preventing proper operation from extraction the maximum power from the input source. Therefore, it is recommended that the leakage be less than 2 nA at 3 V bias.

#### VIN\_DC Capacitance:

Energy from the energy harvester input source is initially stored on a capacitor CHVR tied to Pin 2 (VIN\_DC) and ground (VSS, Pin 1). For energy harvesters which have a source impedance which is dominated by a capacitive behavior, the value of the harvester capacitor should scaled according to the value of the output capacitance of the energy source, but an initial value of 4.7  $\mu$ F is recommended.

#### :VSTOR Capacitance

Operation of the BQ25504 requires a two capacitors to be connected between Pin 15 (VSTOR) and ground. A high frequency bypass capacitor of at 0.01  $\mu$ F should be placed as close as possible between VSTOR and GND. In addition, a bulk capacitor of at least 4.7  $\mu$ F should be connected between Pin 15 and ground to assure stability of the boost converter, especially when the battery is fully charged and the converter in output voltage limiting mode.

#### Additional Capacitance on VSTOR or VBAT:

If there are large, fast system load transients and, or the storage element has high resistance, then the CSTOR capacitors may momentarily discharge below the VBAT\_UV threshold in response to the transient. This causes the bq25504 to turn off the PFET switch between VSTOR and VBAT and turn on the boost converter. Of, the CSTOR capacitors may further discharge below the VSTOR\_CHGEN threshold and cause the bq25504 to enter Cold Start. For instance, some Li-ion batteries or thin-film batteries may not have the current capacity to meet the surge current requirements of an attached low power radio. To prevent VSTOR from drooping, either increase the CSTOR capacitance or add additional capacitance in parallel with the storage element is recommended. For example, if the bq25504 is configured to charge the storage element to 4.2 V and a 500 mA load transient of 50  $\mu$ s duration infrequently occurs, then, solving I = C x dv/dt for CSTOR gives :

CSTOR ≥ 500 mA x 50 µs/(4.2 V − 1.8 V) = 10.5 µF

(6)

Note that increasing CSTOR is the recommended solution but will cause the bq25504 to operate in the less efficient Cold Start mode for a longer period at startup compared to using CSTOR = 4.7  $\mu$ F. If longer Cold Start run times are not desired, then place the additional capacitance in parallel with the storage element.

For a recommended list of standard components, see the EVM User's guide (SLUU654).

## bq25504

SLUSAH0A-OCTOBER 2011-REVISED SEPTEMBER 2012

www.ti.com

Page

## LAYOUT CONSIDERATIONS

As for all switching power supplies, the layout is an important step in the design, especially at high peak currents and high switching frequencies. If the layout is not carefully done, the boost converter/charger could show stability problems as well as EMI problems. Therefore, use wide and short traces for the main current path and for the power ground paths. The input and output capacitor, as well as the inductor should be placed as close as possible to the IC.

The resistors that program the thresholds should be placed as close as possible to the input pins of the IC to minimize parasitic capacitance to less than 2 pF.

To layout the ground, it is recommended to use short traces as well, separated from the power ground traces. This avoids ground shift problems, which can occur due to superimposition of power ground current and control ground current. Assure that the ground traces are connected close to the device GND pin.

## THERMAL CONSIDERATIONS

Implementation of integrated circuits in low-profile and fine-pitch surface-mount packages typically requires special attention to power dissipation. Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power-dissipation limits of a given component.

Three basic approaches for enhancing thermal performance are listed below.

- Improving the power-dissipation capability of the PCB design

- Improving the thermal coupling of the component to the PCB

- Introducing airflow in the system

For more details on how to use the thermal parameters in the Thermal Table, check the Thermal Characteristics Application Note (SZZA017) and the IC Package Thermal Metrics Application Note (SPRA953).

## **REVISION HISTORY**

#### Changes from Original (October 2011) to Revision A

Added C<sub>FLTR</sub> and Notes 1 and 2 to Figure 2

6

Added C<sub>FLTR</sub> and Notes 1 and 2 to Figure 3

7

Added C<sub>FLTR</sub> and Notes 1 and 2 to Figure 4

8

Added the INTENDED OPERATION section

13

Changed the Cold -Start Operation section

13

Changed the Boost Converter, Charger Operation section

13

Changed the Storage Element section

14

Changed the CAPACITOR SELECTION section

17

11-Apr-2013

## **PACKAGING INFORMATION**

| Orderable Device |        | Package Type | •       | Pins | •    |                            | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        |                  | (3)                 |              | (4)               |         |

| BQ25504RGTR      | ACTIVE | QFN          | RGT     | 16   | 3000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | B5504             | Samples |

| BQ25504RGTT      | ACTIVE | QFN          | RGT     | 16   | 250  | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | B5504             | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

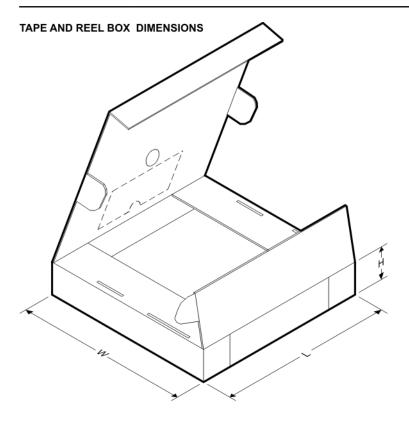

# PACKAGE MATERIALS INFORMATION

www.ti.com

## TAPE AND REEL INFORMATION

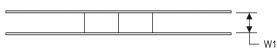

#### REEL DIMENSIONS

Texas Instruments

TAPE AND REEL INFORMATION

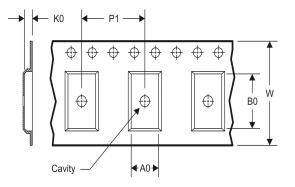

#### TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| BQ25504RGTR                 | QFN             | RGT                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| BQ25504RGTT                 | QFN             | RGT                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

28-Aug-2012

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ25504RGTR | QFN          | RGT             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| BQ25504RGTT | QFN          | RGT             | 16   | 250  | 210.0       | 185.0      | 35.0        |

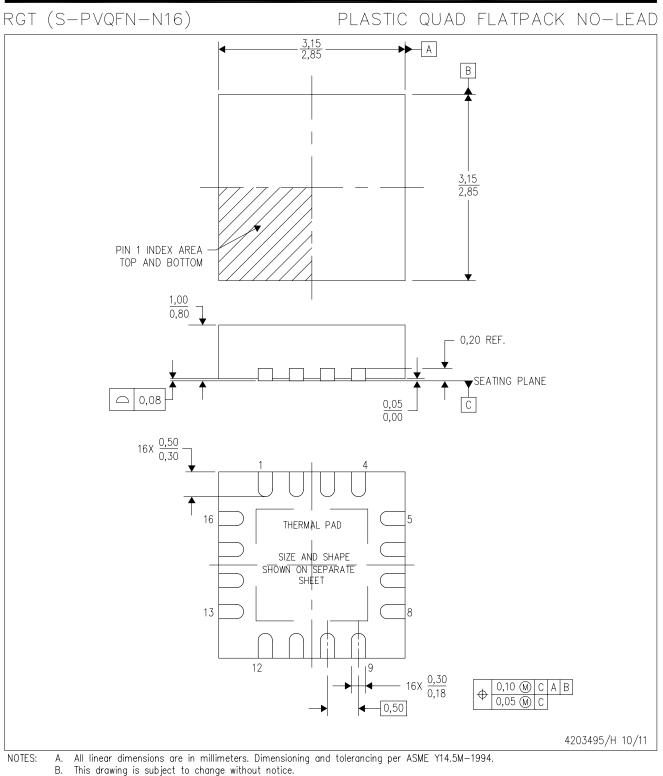

# **MECHANICAL DATA**

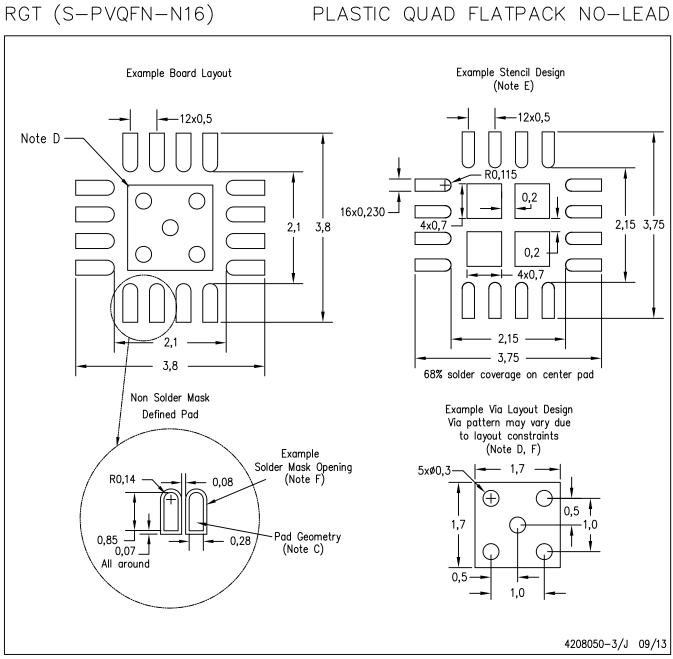

- Quad Flatpack, No-leads (QFN) package configuration. C.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-220.

## RGT (S-PVQFN-N16)

## PLASTIC QUAD FLATPACK NO-LEAD

## THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

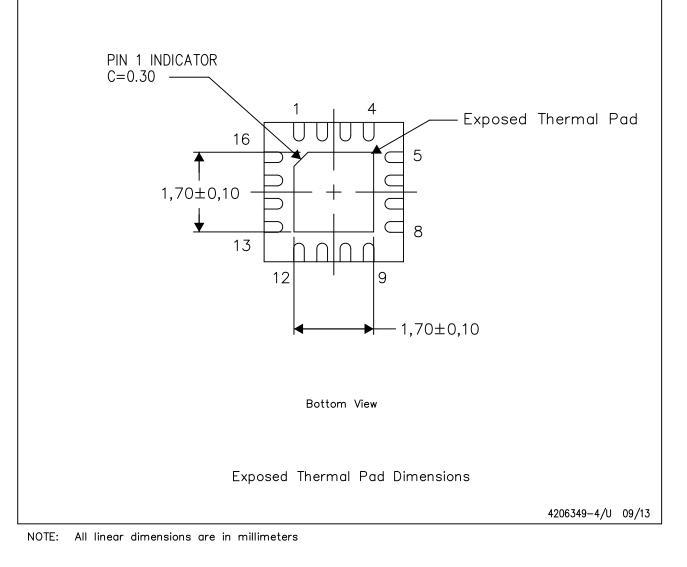

The exposed thermal pad dimensions for this package are shown in the following illustration.

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated