# 1.5K-Bit Serial EPROM With SDQ Interface

Check for Samples: bq2026

# **FEATURES**

- 1536 bits of One-Time Programmable (OTP) EPROM For Storage Of User-Programmable Configuration Data

- Factory-Programmed Unique 64-Bit Identification Number

- Single-Wire Interface to Reduce Circuit Board Routing

- Synchronous Communication Reduces Host Interrupt Overhead

- 6KV IEC 61000-4-2 ESD Compliance on Data

Pin

- No Standby Power Required

- Available in a 3-Pin SOT23 Package and TO-92 Package

# APPLICATIONS

- Security Encoding

- Inventory Tracking

- Product-Revision Maintenance

- Battery-Pack Identification

# DESCRIPTION

The bq2026 is a 1.5K-bit serial EPROM containing a factory-programmed, unique 48-bit identification number, 8-bit family code, and a 64-bit status register.

The bq2026 SDQ<sup>m</sup> interface requires only a single connection and a ground return. The SDQ pin is also the sole power source for the bq2026.

The small surface-mount package options saves printed-circuit-board space, while the low cost makes it ideal for applications such as battery pack configuration parameters, record maintenance, asset tracking, product-revision status, and access-code security.

#### **ORDERING INFORMATION**<sup>(1)</sup>

| PACKAGED DEVICES <sup>(3)</sup>                                                                                                                                    |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PART NUMBER                                                                                                                                                        | PACKAGE                                                                                        | STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| -20°C to 70°C                                                                                                                                                      |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

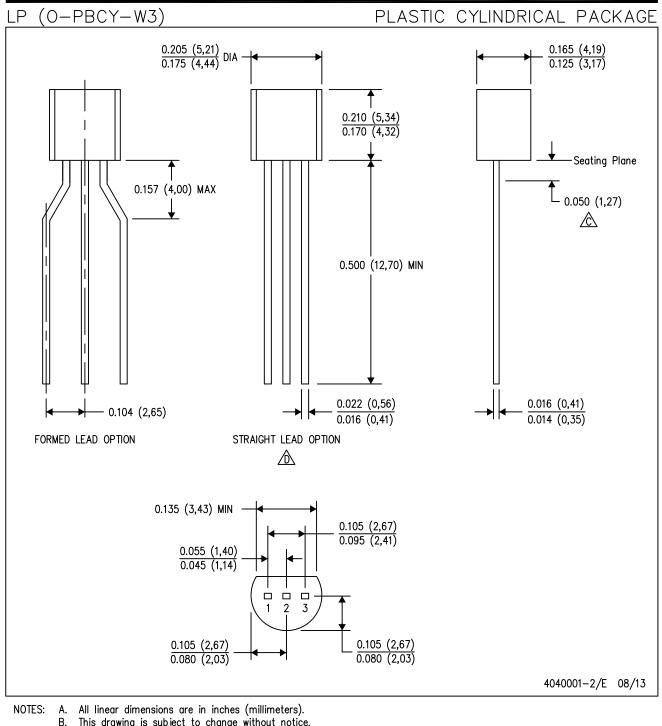

| bq2026LPR <sup>(4)</sup>                                                                                                                                           | TO-92                                                                                          | Production                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| (1) For the most current package and ordering information, see<br>the Package Option Addendum at the end of this document, or<br>see the TI Web site at www.ti.com |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                                                                                                                                                    | PART NUMBER<br>bq2026DBZR<br>bq2026LPR <sup>(4)</sup><br>current package a<br>tion Addendum at | PART NUMBER         PACKAGE           bq2026DBZR         SOT23-3           bq2026LPR <sup>(4)</sup> TO-92           current package and ordering info<br>tion Addendum at the end of this compared to the end of t |  |  |  |  |

(2) Device specified to communicate at -40°C to 85°C

(3) The device is available only in tape and reel with a base quantity of 3000 units for the bq2026DBZR and 2000 units for the bq2026LPR.

(4) ROHS Compliant

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SDQ is a trademark of Texas Instruments.

# bq2026

SLUS938-DECEMBER 2011

TEXAS INSTRUMENTS

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                                      |                                   | VA   | LUE  | UNIT |

|------------------------------------------------------|-----------------------------------|------|------|------|

|                                                      |                                   | MIN  | MAX  | UNIT |

| DC voltage applied to V <sub>PU</sub> See Figure 1   |                                   | -0.3 | 12.5 | V    |

| Low-level output current, I <sub>OL</sub>            |                                   |      | 5    | mA   |

| ESD IEC 61000-4-2 Air discharge                      | SDQ to $V_{SS}$ , $V_{SS}$ to SDQ |      | 6    | kV   |

| Operating free-air temperature range, T <sub>A</sub> |                                   | -20  | 70   | °C   |

| Storage temperature range, T <sub>stg</sub>          |                                   | -55  | 125  | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# DC ELECTRICAL CHARACTERISTICS

$T_A = -20^{\circ}C$  to 70°C;  $V_{PU(min)} = 2.65 V_{DC}$  to 5.5  $V_{DC}$ , all voltages relative to VSS

|                  | PARAMETER                       | TEST CONDITION                                      | MIN  | TYP             | MAX | UNIT |

|------------------|---------------------------------|-----------------------------------------------------|------|-----------------|-----|------|

| I <sub>SDQ</sub> | Supply current                  | V <sub>PU</sub> = 5.5 V                             |      |                 | 20  | μA   |

| V                |                                 | Logic 0, $V_{PU}$ = 5.5 V, $I_{OL}$ = 4 mA, SDQ pin |      |                 | 0.4 | V    |

| V <sub>OL</sub>  | Low-level output voltage        | Logic 0, $V_{PU}$ = 2.65 V, $I_{OL}$ = 2 mA         |      |                 | 0.4 | v    |

| V <sub>OH</sub>  | High-level output voltage       | Logic 1                                             |      | V <sub>PU</sub> | 5.5 |      |

| I <sub>OL</sub>  | Low-level output current (sink) | V <sub>OL</sub> = 0.4 V, SDQ pin                    |      |                 | 4   | mA   |

| VIL              | Low-level input voltage         | Logic 0                                             |      |                 | 0.8 | V    |

| VIH              | High-level input voltage        | Logic 1                                             | 2.2  |                 |     | V    |

| V <sub>PP</sub>  | Programming voltage             |                                                     | 11.5 |                 | 12  | V    |

| l <sub>lkg</sub> | Input leakage                   |                                                     |      | 1.4             |     | μA   |

| CI               | Input capacitance               |                                                     |      | 1.2             |     | nF   |

# AC SWITCHING CHARACTERISTCS

$T_A = -20^{\circ}C$  to 70°C;  $V_{PU(min)} = 2.65 V_{DC}$  to 5.5  $V_{DC}$ , all voltages relative to VSS

|                    | PARAMETER                | TEST CONDITION | MIN                | TYP | MAX            | UNIT |

|--------------------|--------------------------|----------------|--------------------|-----|----------------|------|

| t <sub>c</sub>     | Bit cycle time (1)       |                | 60                 |     | 120            | μs   |

| t <sub>WSTRB</sub> | Write start cycle (1)    |                | 1                  |     | 15             | μs   |

| t <sub>WDSU</sub>  | Write data setup (1)     |                | t <sub>WSTRB</sub> |     | 15             | μs   |

| t <sub>WDH</sub>   | Write data hold (1) (2)  |                | 60                 |     | t <sub>c</sub> | μs   |

| t <sub>rec</sub>   | Recovery time (1)        |                | 1                  |     |                | μs   |

| t <sub>RSTRB</sub> | Read start cycle (1)     |                | 1                  |     | 13             | μs   |

| t <sub>ODD</sub>   | Output data delay (1)    |                | t <sub>RSTRB</sub> |     | 13             | μs   |

| t <sub>ODHO</sub>  | Output data hold (1)     |                | 17                 |     | 60             | μs   |

| t <sub>RST</sub>   | Reset time (1)           |                | 480                |     |                | μs   |

| t <sub>PPD</sub>   | Presence pulse delay (1) |                | 15                 |     | 64             | μs   |

| t <sub>PP</sub>    | Presence pulse (1)       |                | 60                 |     | 240            | μs   |

| t <sub>EPROG</sub> | EPROM programming time   |                | 480                |     |                | μs   |

| t <sub>PSU</sub>   | Program setup time       |                | 5                  |     |                | μs   |

| t <sub>PREC</sub>  | Program recovery time    |                | 5                  |     |                | μs   |

(1) 5-k $\Omega$  series resistor between SDQ pin and V<sub>PU</sub>. (See Figure 1)

- (2)  $t_{WDH}$  must be less than  $t_c$  to account for recovery.

- 2 Submit Documentation Feedback

# AC SWITCHING CHARACTERISTCS (continued)

$T_A = -20^{\circ}C$  to 70°C;  $V_{PU(min)} = 2.65 V_{DC}$  to 5.5  $V_{DC}$ , all voltages relative to VSS

|                     | PARAMETER                 | TEST CONDITION | MIN | TYP | MAX | UNIT |

|---------------------|---------------------------|----------------|-----|-----|-----|------|

| t <sub>PRE</sub>    | Program rising-edge time  |                |     |     | 5   | μs   |

| t <sub>PFE</sub>    | Program falling-edge time |                |     |     | 5   | μs   |

| t <sub>RSTREC</sub> |                           |                | 480 |     |     | μs   |

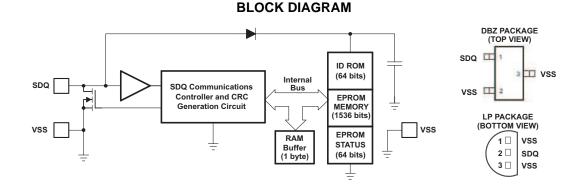

#### **Pin Functions**

| PI       | Ν    | I/O | DESCRIPTION |

|----------|------|-----|-------------|

| NAME     | NO.  | 1/0 | DESCRIPTION |

| bq2026DE | ZR   |     |             |

| SDQ      | 1    | I/O | Data        |

| VSS      | 2, 3 | -   | Ground      |

| bq2026LP | R    |     |             |

| VSS      | 1, 3 | -   | Ground      |

| SDQ      | 2    | I/O | Data        |

### FUNCTIONAL DESCRIPTION

### GENERAL OPERATION

The block diagram shows the relationships among the major control and memory sections of the bq2026. The bq2026 has three main data components: a 64-bit factory-programmed ROM, including 8-bit family code, 48-bit identification number and 8-bit CRC value, 1536-bit EPROM, and EPROM STATUS bytes. Power for read and write operations is derived from the SDQ pin. An internal capacitor stores energy while the signal line is high and releases energy during the low times of the SDQ pin, until the pin returns high to replenish the charge on the capacitor.

#### EPROM

Table 1 is a memory map of the 1536-bit EPROM section of the bq2026, configured as six pages of 32 bytes each. The 1-byte RAM buffer is an additional register used when programming the memory. Data are first written to the RAM buffer and then verified by reading a 16-bit CRC from the bq2026 that confirms proper receipt of the data. If the buffer contents are correct, a programming pluse is issued and a 1-byte segment of data is written into the selected address in memory. This process ensures data integrity when programming the memory. The details for reading and programming the 1536-bit EPROM portion of the bq2026 are in the *Memory Function Commands* section of this data sheet.

|               | · ·    |

|---------------|--------|

| ADDRESS (HEX) | PAGE   |

| 00A0-00BF     | Page 5 |

| 0080-009F     | Page 4 |

| 0060-007F     | Page 3 |

| 0040-005F     | Page 2 |

| 0020-003F     | Page 1 |

| 0000-001F     | Page 0 |

|               |        |

#### Table 1. 1536-Bit EPROM Data Memory Map

## EPROM STATUS MEMORY

In addition to the programmable 1536-bits of memory are 8 bytes of status information, the first 7 bytes are available to the user, contained in the EPROM STATUS memory. The STATUS memory is accessible with separate commands. The STATUS bytes are EPROM and are read or programmed to indicate various conditions to the software interrogating the bq2026. These general purpose bytes can be used by the customer to store various information.

Copyright © 2011, Texas Instruments Incorporated

TEXAS INSTRUMENTS

www.ti.com

#### Table 2. EPROM Status Bytes

| ADDRESS (HEX) | PAGE                              |

|---------------|-----------------------------------|

| 100h-107h     | General Purpose OTP Status Memory |

#### Error Checking

Error checking can be implemented by comparing the 16-bit CRC values transmitted by the bq2026. If the two CRC values match, the transmission is error-free. Details are found in the CRC Generation section of this data sheet.

#### Customizing the bq2026

The 64-bit ID identifies each bq2026. The 48-bit serial number is unique and programmed by Texas Instruments. The default 8-bit family code is 09h; however, a different value can be reserved on an individual customer basis. Contact your Texas Instruments sales representative for more information.

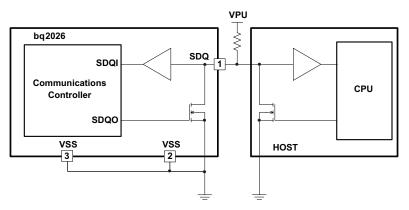

#### **Bus Termination**

Because the drive output of the bq2026 is an open-drain, N-channel MOSFET, the host must provide a source current or a 5-k $\Omega$  external pullup, as shown in the typical application circuit in Figure 1.

Figure 1. Typical Applications Circuit

## **Serial Communication**

A host reads, programs, or checks the status of the bq2026 through the hierarchical command structure of the SDQ interface. Figure 2 shows that the host must first issue a ROM command before the EPROM memory or status can be read or modified.

| Initialization | ROM Command Sequence | Memory/Status Command Sequence |

|----------------|----------------------|--------------------------------|

|                |                      | ·                              |

#### Figure 2. General Command Sequence

#### Initialization

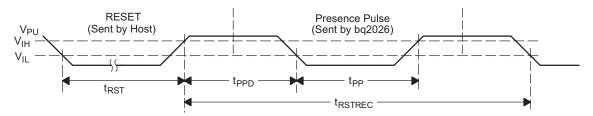

Initialization consists of two pulses, the RESET and the PRESENCE pulses. The host generates the RESET pulse, while the bq2026 responds with the PRESENCE pulse. The host resets the bq2026 by driving the DATA bus low for at least 480 µs. For more details, see the *RESET* section under *SDQ Signaling*.

#### **ROM COMMANDS**

#### READ ROM

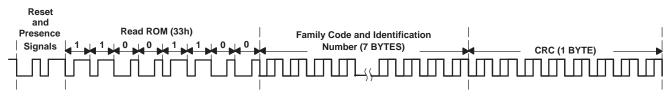

The READ ROM command sequence is the fastest sequence that allows the host to read the 8-bit family code and 48-bit identification number. The READ ROM sequence starts with the host generating the RESET pulse of at least 480 µs. The bq2026 responds with a PRESENCE pulse. Next, the host continues by issuing the READ ROM command, 33h, and then reads the ROM and CRC byte using the READ signaling (see the READ and WRITE signals section) during the data frame.

Figure 3. READ ROM Sequence

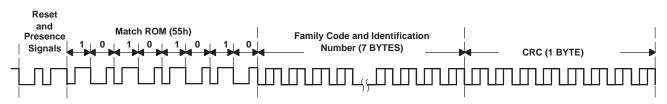

#### MATCH ROM

The MATCH ROM command, 55h, is used by the host to select a specific SDQ device when the family code and identification number is known. The host issues the MATCH ROM command followed by the family code, ROM number, and the CRC byte. The device that matches the 64-bit ROM sequence is selected and available to perform subsequent Memory/Status Function commands.

Figure 4. MATCH ROM Sequence

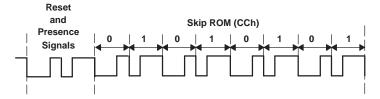

#### **SKIP ROM**

This SKIP ROM command, CCh, allows the host to access the memory/status functions without issuing the 64-bit ROM code sequence. The SKIP ROM command is directly followed by a memory/status functions command.

Figure 5. SKIP ROM Sequence

# MEMORY/STATUS FUNCTION COMMANDS

Four memory/status function commands allow read and modification of the 1536-bit EPROM data memory or the 7-byte EPROM status memory. There is a READ MEMORY/Field CRC command, plus the WRITE MEMORY, READ STATUS, and WRITE STATUS commands. The bq2026 responds to memory/status function commands only after a part is selected by a ROM command.

## **READ MEMORY/Field CRC**

To read the memory, the ROM command is followed by the READ MEMORY command, F0h, followed by the address low byte and then the address high byte.

### NOTE

As shown in Figure 6, individual bytes of address and data are transmitted LSB first.

The host then issues read time slots and receives data from the bq2026 starting at the initial address and continuing until the end of the 1536-bit data field is reached or until a reset pulse is issued. If reading occurs through the end of memory space, the host may issue sixteen additional read time slots and the bq2026 responds with a 16-bit CRC of all data bytes read from the initial starting byte through the last byte of memory. After the CRC is received by the host, any subsequent read time slots appears as logical 1s until a reset pulse is issued. Any reads ended by a reset pulse prior to reaching the end of memory does not have the 16-bit CRC available.

| Initialization and ROM<br>Command Sequence | READ MEMORY Command<br>F0h | Address Low<br>Byte | Ad | ldress High<br>Byte | Read EPROM Memory Until<br>End of EPROM Memory | Read and<br>Verify 16-bit<br>CRC |  |

|--------------------------------------------|----------------------------|---------------------|----|---------------------|------------------------------------------------|----------------------------------|--|

|                                            |                            | A0 A7               | A8 | A15                 |                                                |                                  |  |

### Figure 6. READ MEMORY/Field CRC

#### www.ti.com

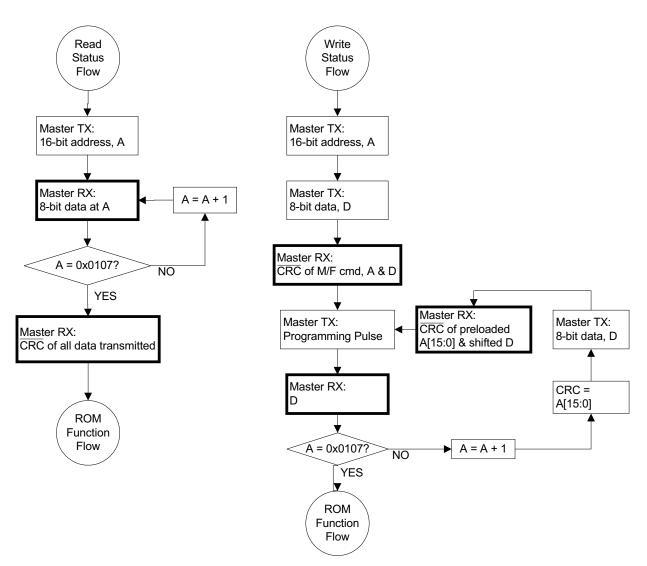

## **READ STATUS**

The READ STATUS command is used to read data from the EPROM status data field. After issuing a ROM command, the host issues the READ STATUS command, AAh, followed by the address low byte and then the address high byte.

#### NOTE

An 16-bit CRC of the command byte and address bytes is computed by the bq2026 and read back by the host to confirm that the correct command word and starting address were received.

If the CRC read by the host is incorrect, a reset pulse must be issued and the entire sequence must be repeated. If the CRC received by the host is correct, the host issues read time slots and receives data from the bq2026 starting at the supplied address and continuing until the end of the EPROM Status data field is reached. At that point, the host receives a 16-bit CRC that is the result of shifting into the CRC generator all of the data bytes from the initial starting byte through the final byte.

This feature is provided because the EPROM status information may change over time making it impossible to program the data once and include an accompanying CRC that is always valid. Therefore, the READ status command supplies a 16-bit CRC that is based on (and always is consistent with) the current data stored in the EPROM status data field.

After the 16-bit CRC is read, the host receives logical 1s from the bq2026 until a reset pulse is issued. The READ STATUS command sequence can be ended at any point by issuing a reset pulse.

| Initialization and ROM<br>CommandSequence | READ MEMORY<br>Command<br>AAh | Address Low<br>Byte | Address High<br>Byte | Read STATUS Memory Until<br>End of Page | Read and<br>Verify 16-bit<br>CRC   |

|-------------------------------------------|-------------------------------|---------------------|----------------------|-----------------------------------------|------------------------------------|

|                                           |                               | A0 A7               | A8 A15               |                                         | of command,<br>address and<br>data |

Figure 7. READ STATUS Command

Figure 8. Status Memory Read and Write Flowchart

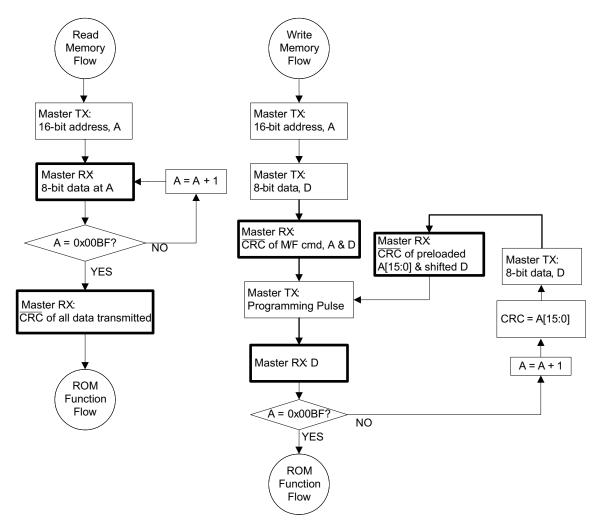

### WRITE MEMORY

The WRITE MEMORY command is used to program the 1536-bit EPROM memory field. The 1536-bit memory field is programmed in 1-byte segments. Data is first written into an 1-byte RAM buffer. The contents of the RAM buffer is then ANDed with the contents of the EPROM memory field when the programming command is issued.

Figure 9 illustrates the sequence of events for programming the EPROM memory field. After issuing a ROM command, the host issues the WRITE MEMORY command, 0Fh, followed by the low byte and then the high byte of the starting address. The host then transmits 1 byte of data to the bq2026.

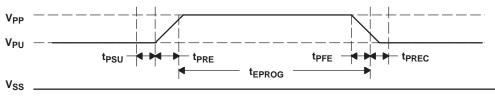

a 16-bit CRC is calculated and transmitted based on the command, address and data. If this CRC agrees with the CRC calculated by the host, the host applies the programming voltage for at least 480 µs or t<sub>EPROG</sub>.

If at any time during the WRITE MEMORY process, the CRC read by the host is incorrect, a reset pulse must be issued, and the entire sequence must be repeated.

The WRITE DATA MEMORY command sequence can be terminated at any point by issuing a reset pulse except during the program pulse period t<sub>PROG</sub>.

#### NOTE

The bq2026 responds with the data from the selected EPROM address sent least significant-bit first. This response should be checked to verify the programmed byte. If the programmed byte is incorrect, then the host must reset the part and begin the write sequence again.

For both of these cases, the decision to continue programming is made entirely by the host, because the bq2026 is not able to determine if the 16-bit CRC calculated by the host agrees with the 16-bit CRC calculated by the bq2026.

Prior to programming, bits in the 1536-bit EPROM data field appear as logical 1s.

TEXAS INSTRUMENTS

www.ti.com

Figure 9. General Use OTP Memory Read and Write Flowchart

## WRITE STATUS

The Write Status command is used to program the EPROM Status data field after the bq2026 has been selected by a ROM command

The flow chart in Figure 9 illustrates that the host issues the Write Status command, 55h, followed by the address low byte and then the address high byte followed by the byte of data to be programmed.

#### **NOTE** Individual bytes of address and data are transmitted LSB first. a 16-bit CRC of the command byte, address bytes, and data byte is computed by the bq2026 and read back by the host to confirm that the correct command word, starting address, and data byte were received.

If the CRC read by the host is incorrect, a reset pulse must be issued and the entire sequence must be repeated. If the CRC received by the host is correct, the programming voltage,  $V_{PP}$  is applied to the SDQ pin for period  $t_{PROG}$ . Prior to programming, the first 7 bytes of the EPROM STATUS data field appear as logical 1s. For each bit in the data byte provided by the host that is set to a logical 0, the corresponding bit in the selected byte of the EPROM STATUS data field is programmed to a logical 0 after the programming pulse has been applied at the byte location.

After the programming pulse is applied and the data line returns to  $V_{PU}$ , the host issues eight read time slots to verify that the appropriate bits have been programmed. The bq2026 responds with the data from the selected EPROM STATUS address sent least significant bit first. This response should be checked to verify the programmed byte. If the programmed byte is incorrect, then the host must reset the device and begin the write sequence again. If the bq2026 EPROM data byte programming was successful, the bq2026 automatically increments its address counter to select the next byte in the STATUS MEMORY data field. The least significant byte of the new two-byte address is also loaded into the 16-bit CRC generator as a starting value. The host issues the next byte of data using eight write time slots.

As the bq2026 receives this byte of data into the RAM buffer, it also shifts the data into the CRC generator that has been preloaded with the LSB of the current address and the result is a 16-bit CRC of the new data byte and the new address. After supplying the data byte, the host reads this 16-bit CRC from the bq2026 with eight read time slots to confirm that the address incremented properly and the data byte was received correctly. If the CRC is incorrect, a Reset Pulse must be issued and the Write Status command sequence must be restarted. If the CRC is correct, the host issues a programming pulse and the selected byte in memory is programmed.

#### NOTE

The initial write of the WRITE STATUS command, generates a 16-bit CRC value that is the result of shifting the command byte into the CRC generator, followed by the two-address bytes, and finally the data byte. Subsequent writes within this WRITE STATUS command due to the bq2026 automatically incrementing its address counter generates a 16-bit CRC that is the result of loading (not shifting) the LSB of the new (incremented) address into the CRC generator and then shifting in the new data byte.

For both of these cases, the decision to continue programming the EPROM Status registers is made entirely by the host, because the bq2026 is not able to determine if the 16-bit CRC calculated by the host agrees with the 16-bit CRC calculated by the bq2026. If an incorrect CRC is ignored and a program pulse is applied by the host, incorrect programming could occur within the bq2026. Also note that the bq2026 always increments its internal address counter after the receipt of the eight read time slots used to confirm the programming of the selected EPROM byte. The decision to continue is again made entirely by the host, therefore if the EPROM data byte does not match the supplied data byte but the master continues with the WRITE STATUS command, incorrect programming could occur within the bq2026. The WRITE STATUS command sequence can be ended at any point by issuing a reset pulse.

**NSTRUMENTS**

ÈXAS

| COMMAND<br>(HEX) | DESCRIPTION                    | CATEGORY                                  |

|------------------|--------------------------------|-------------------------------------------|

| 33h              | Read Serialization ROM and CRC |                                           |

| 55h              | Match Serialization ROM        | ROM Commands Available in Command Level I |

| CCh              | Skip Serialization ROM         |                                           |

| F0h              | Read Memory/Field CRC          |                                           |

| AAh              | Read EPROM Status              | Memory Function Commands                  |

| 0Fh              | Write Memory                   | Available in Command Level II             |

| 55h              | Write EPROM Status             |                                           |

#### Table 3. Command Code Summary

## SDQ SIGNALING

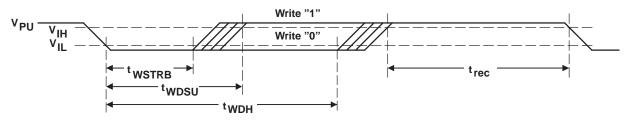

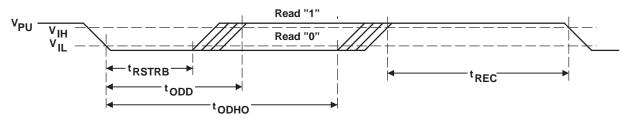

All SDQ signaling begins with initializing the device, followed by the host driving the bus low to write a 1 or 0, or to begin the start frame for a bit read. Figure 10 shows the initialization timing, whereas Figure 11 and Figure 12 show that the host initiates each bit by driving the DATA bus low for the start period,  $t_{WSTRB} / t_{RSTRB}$ . After the bit is initiated, either the host continues controlling the bus during a WRITE, or the bq2026 responds during a READ.

#### **RESET AND PRESENCE PULSE**

If the DATA bus is driven low for more than 120  $\mu$ s, the bq2026 may be reset. Figure 10 shows that if the DATA bus is driven low for more than 480  $\mu$ s, the bq2026 resets and indicates that it is ready by responding with a PRESENCE PULSE.

Figure 10. Reset Timing Diagram

#### WRITE

The WRITE bit timing diagram in Figure 11 shows that the host initiates the transmission by issuing the  $t_{WSTRB}$  portion of the bit and then either driving the DATA bus low for a WRITE 0, or releasing the DATA bus for a WRITE 1.

Figure 11. Write Bit Timing Diagram

## READ

The READ bit timing diagram in Figure 12 shows that the host initiates the transmission of the bit by issuing the  $t_{RSTRB}$  portion of the bit. The bq2026 then responds by either driving the DATA bus low to transmit a READ 0 or releasing the DATA bus to transmit a READ 1.

Figure 12. Read Bit Timing Diagram

## **PROGRAM PULSE**

Figure 13. Program Pulse Timing Diagram

## IDLE

If the bus is high, the bus is in the IDLE state. Bus transactions can be suspended by leaving the DATA bus in IDLE. Bus transactions can resume at any time from the IDLE state.

### **CRC** Generation

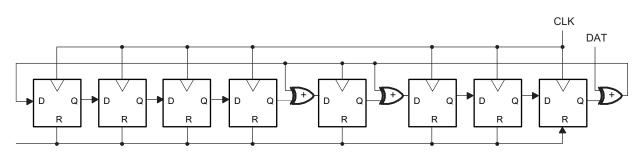

The bq2026 has a 8-bit CRC stored in the most significant byte of the 64-bit ROM. The bus master can compute a CRC value from the first 56 bits of the 64-bit ROM and compare it to the value stored within the bq2026 to determine if the ROM data has been received error-free by the bus master. The equivalent polynomial function of this CRC is shown in Figure 14.

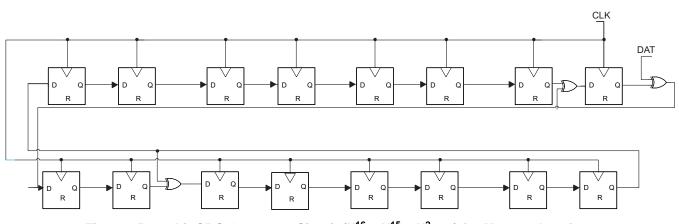

Under certain conditions, the bq2026 also generates a 16-bit CRC value using the polynomial function is shown in Figure 15 and provides this value to the bus master which validates the transfer of command, address, and data bytes from the bus master to the bq2026. The bq2026 computes a 16-bit CRC for the command, address, and data bytes received for the WRITE MEMORY and the WRITE STATUS commands, and then outputs this value to the bus master which confirms proper transfer. Similarly, the bq2026 computes a 16-bit CRC for the command and address bytes received from the bus master for the READ MEMORY, and READ STATUS commands to confirm that these bytes have been received correctly.

In each case, where a CRC is used for data transfer validation, the bus master must calculate a CRC value using the polynomial function in Figure 14 or Figure 15 and compares the calculated value to either the 8-bit CRC value stored in the 64-bit ROM portion of the bq2026 (for ROM reads) or the 16-bit CRC value computed within the bq2026. The comparison of CRC values and the decision to continue with an operation are determined entirely by the bus master. No circuitry on the bq2026 prevents a command sequence from proceeding if the CRC stored in or calculated by the bq2026 does not match the value generated by the bus master. Proper use of the CRC can result in a communication channel with a high level of integrity.

Figure 14. 8-bit CRC Generator Circuit ( $X^8 + X^5 + X^4 + 1$ ) for Serial Number Read

Figure 15. 16-bit CRC Generator Circuit ( $X^{16} + X^{15} + X^2 + 1$ ) for Memory Interface

11-Apr-2013

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        |                  | (3)                |              | (4)               |         |

| BQ2026DBZR       | ACTIVE | SOT-23       | DBZ     | 3    | 3000    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -20 to 70    | WAIS              | Samples |

| BQ2026LPR        | ACTIVE | TO-92        | LP      | 3    | 2000    | Pb-Free<br>(RoHS)          | CU SN            | N / A for Pkg Type | -20 to 70    | BQ2026            | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW**: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

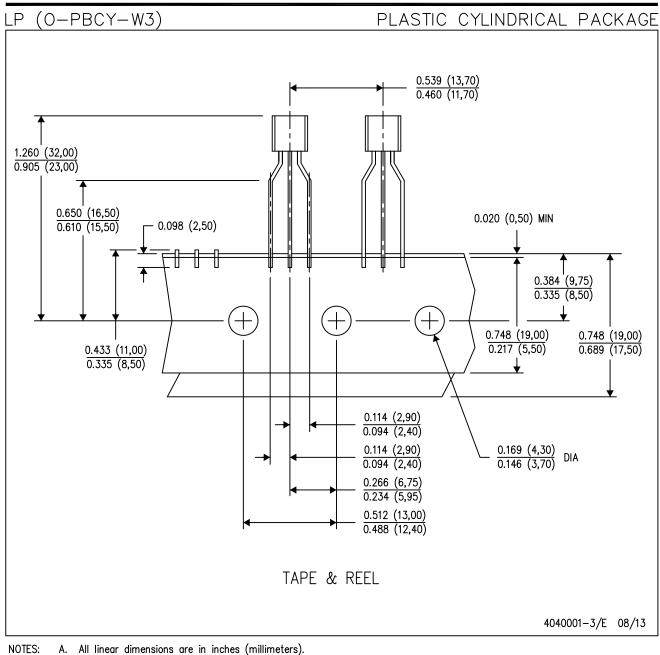

## TAPE AND REEL INFORMATION

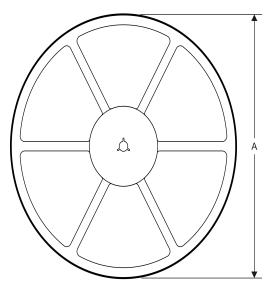

#### REEL DIMENSIONS

TEXAS INSTRUMENTS

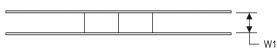

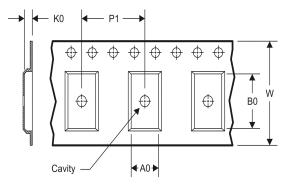

#### TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## TAPE AND REEL INFORMATION

\*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| BQ2026DBZR | SOT-23          | DBZ                | 3 | 3000 | 179.0                    | 8.4                      | 3.15       | 2.95       | 1.22       | 4.0        | 8.0       | Q3               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

7-Sep-2012

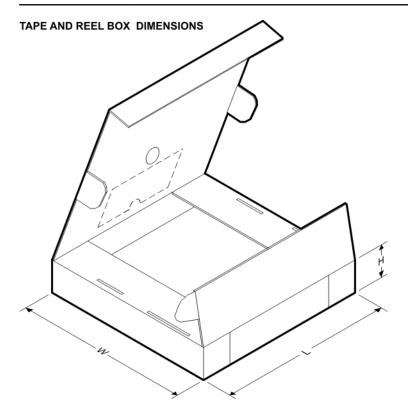

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ2026DBZR | SOT-23       | DBZ             | 3    | 3000 | 203.0       | 203.0      | 35.0        |

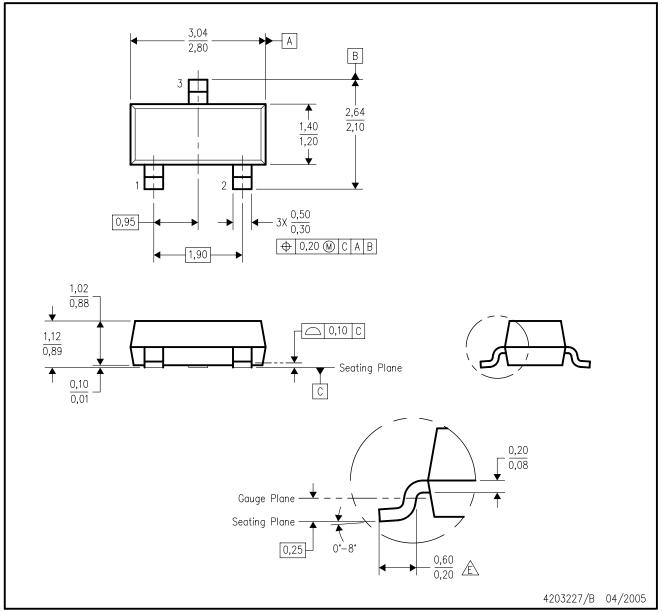

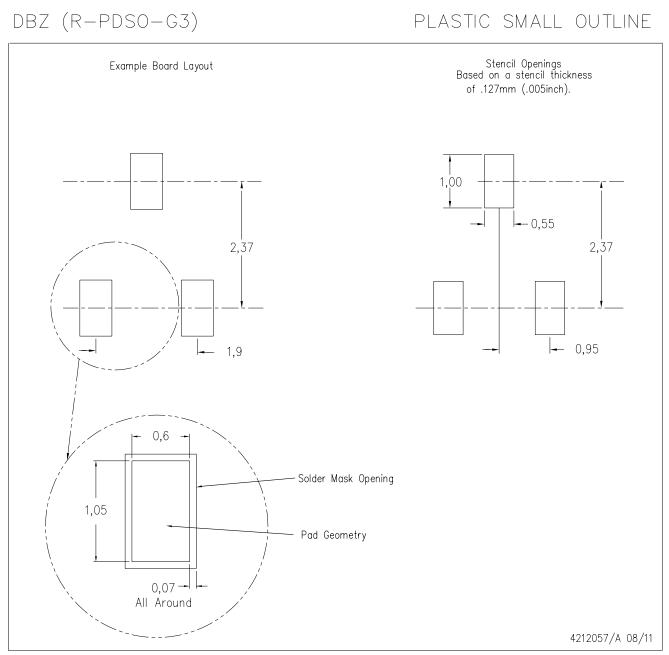

DBZ (R-PDSO-G3)

PLASTIC SMALL-OUTLINE

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

C. Lead dimensions are inclusive of plating.

D. Body dimensions are exclusive of mold flash and protrusion. Mold flash and protrusion not to exceed 0.25 per side.

E Falls within JEDEC TO-236 variation AB, except minimum foot length.

NOTES:

- A. All linear dimensions are in millimeters.B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- B. This drawing is subject to change without notice.

- Lead dimensions are not controlled within this area.

- ⚠ Falls within JEDEC TO-226 Variation AA (TO-226 replaces TO-92).

- Shipping Method: E. Straight lead option available in bulk pack only. Formed lead option available in tape & reel or ammo pack. Specific products can be offered in limited combinations of shipping mediums and lead options. Consult product folder for more information on available options.

# **MECHANICAL DATA**

- B. This drawing is subject to change without notice.

- C. Tape and Reel information for the Formed Lead Option package.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated