# **ADS574**

# Microprocessor-Compatible Sampling CMOS ANALOG-TO-DIGITAL CONVERTER

## FEATURES

- REPLACES ADC574 FOR NEW DESIGNS

- COMPLETE SAMPLING A/D WITH REFERENCE, CLOCK AND MICROPROCESSOR INTERFACE

- FAST ACQUISITION AND CONVERSION: 25µs max

- ELIMINATES EXTERNAL SAMPLE/HOLD IN MOST APPLICATIONS

- GUARANTEED AC AND DC PERFORMANCE

- SINGLE +5V SUPPLY OPERATION

- LOW POWER: 100mW max

- PACKAGE OPTIONS: 0.6" and 0.3" DIPs, SOIC

# DESCRIPTION

The ADS574 is a 12-bit successive approximation analog-to-digital converter using an innovative capacitor array (CDAC) implemented in low-power CMOS technology. This is a drop-in replacement for ADC574 models in most applications, with internal sampling, much lower power consumption, and capability to operate from a single +5V supply.

The ADS574 is complete with internal clock, microprocessor interface, three-state outputs, and internal scaling resistors for input ranges of 0V to +10V, 0V to +20V,  $\pm$ 5V, or  $\pm$ 10V. The maximum throughput time for 12-bit conversions is 25µs over the full operating temperature range, including both acquisition and conversion.

Complete user control over the internal sampling function facilitates elimination of external sample/hold amplifiers in most existing designs.

The ADS574 requires +5V, with -12V or -15V optional, depending on usage. No +15V supply is required. Available packages include 0.3" or 0.6" wide 28-pin plastic DIPs and 28-lead SOICs.

# SPECIFICATIONS

### ELECTRICAL

At  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{DD} = +5V$ ,  $V_{EE} = -15V$  to +5V, sampling frequency of 40kHz, and  $f_{IN} = 10kHz$ , unless otherwise specified.

|                                                                                 | A          | DS574JE, JP, | JU           | A                     | 0S574KE, KP, | KU          | 1                  |

|---------------------------------------------------------------------------------|------------|--------------|--------------|-----------------------|--------------|-------------|--------------------|

| PARAMETER                                                                       | MIN        | TYP          | MAX          | MIN                   | ТҮР          | MAX         | UNITS              |

| RESOLUTION                                                                      |            |              | 12           |                       |              | *           | Bits               |

| INPUTS                                                                          |            | 1            |              | •                     |              |             |                    |

| ANALOG                                                                          |            |              |              |                       |              |             |                    |

| Voltage Ranges: Unipolar                                                        |            |              |              | ), 0 to +20           |              |             | V                  |

| Bipolar<br>Impedance: 0 to +10V, ±5V                                            | 15         | 21           | ±5           | , ±10<br>  *          | *            | I           | V<br>kΩ            |

| ±10V, 0V to +20V                                                                | 60         | 84           |              | *                     | *            |             | kΩ                 |

| <b>DIGITAL</b> (CE, $\overline{CS}$ , $R/\overline{C}$ , $A_0$ , 12/8)          |            |              |              |                       |              |             |                    |

| Voltages: Logic 1                                                               | +2.0       |              | +5.5         | *                     |              | *           | V                  |

| Logic 0<br>Current                                                              | -0.5<br>-5 | 0.1          | +0.8<br>+5   | *                     | *            | *           | ν<br>μΑ            |

| Capacitance                                                                     |            | 5            | +5           | -14                   | *            | -*          | μA<br>pF           |

| TRANSFER CHARACTERISTICS                                                        |            |              |              |                       |              |             | . ·                |

| DC ACCURACY                                                                     |            |              |              |                       |              |             |                    |

| At +25°C                                                                        |            |              |              |                       |              |             |                    |

| Linearity Error<br>Unipolar Offset Error (adjustable to zero)                   |            |              | ±1<br>±2     |                       |              | ±1/2<br>*   | LSB<br>LSB         |

| Bipolar Offset Error (adjustable to zero)                                       |            |              | ±10          |                       |              | ±4          | LSB                |

| Full-Scale Calibration Error <sup>(1)</sup>                                     |            |              |              |                       |              |             |                    |

| (adjustable to zero)<br>No Missing Codes Resolution (Diff. Linearity)           | 12         |              | ±0.25        | 12                    |              | *           | % of FS (2<br>Bits |

| $T_{MIN}$ to $T_{MAX}$ <sup>(3)</sup>                                           |            |              |              |                       |              |             |                    |

| Linearity Error                                                                 |            |              | ±1           |                       |              | ±1/2        | LSB                |

| Full-Scale Calibration Error<br>Unipolar Offset                                 |            |              | ±0.47<br>±4  |                       |              | ±0.37<br>±3 | % of FS<br>LSB     |

| Bipolar Offset                                                                  |            |              | ±12          |                       |              | ±5          | LSB                |

| No Missing Codes Resolution                                                     | 12         |              |              | 12                    |              |             | Bits               |

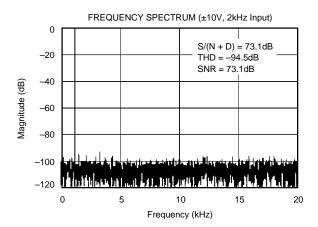

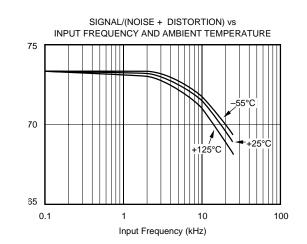

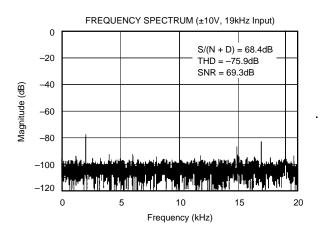

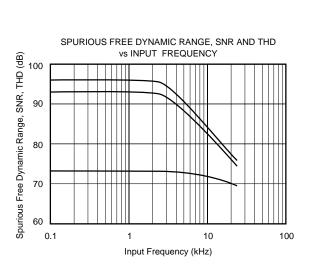

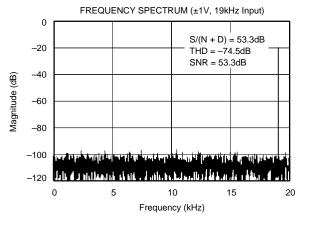

| AC ACCURACY (4)                                                                 |            |              |              |                       |              |             |                    |

| Spurious Free Dynamic Range<br>Total Harmonic Distortion                        | 73         | 78<br>-77    | -72          | 76                    | *            | -75         | dB<br>dB           |

| Signal-to-Noise Ratio                                                           | 69         | 72           | -12          | 71                    | *            | -75         | dB                 |

| Signal-to-(Noise + Distortion) Ratio                                            | 68         | 71           |              | 70                    | *            |             | dB                 |

| Intermodulation Distortion<br>( $F_{IN1} = 10$ kHz, $F_{IN2} = 11.5$ kHz)       |            | -75          |              |                       | *            |             |                    |

| TEMPERATURE COEFFICIENTS (5)                                                    |            |              |              |                       |              |             |                    |

| Unipolar Offset                                                                 |            | ±1           |              |                       | *            |             | ppm/°C             |

| Bipolar Offset                                                                  |            | ±2           |              |                       | *            |             | ppm/°C             |

| Full-Scale Calibration                                                          |            | ±12          |              |                       | *            |             | ppm/°C             |

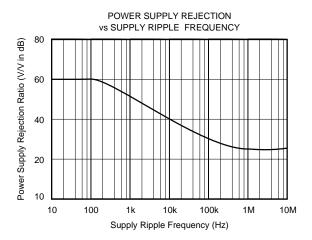

| POWER SUPPLY SENSITIVITY                                                        |            |              |              |                       |              |             |                    |

| Change in Full-Scale Calibration <sup>(6)</sup><br>+4.75V < $V_{DD}$ < +5.25V   |            |              | ±1/2         |                       |              | *           | LSB                |

| CONVERSION TIME (Including Acquisition Time)                                    |            |              |              |                       |              |             |                    |

| $t_{AQ} + t_C \text{ at } 25^{\circ}\text{C}$ :                                 |            |              |              |                       |              |             |                    |

| 8-Bit Cycle                                                                     |            | 16           | 18           |                       | *            | *           | μs                 |

| 12-Bit Cycle<br>12-Bit Cycle, T <sub>MIN</sub> to T <sub>MAX</sub>              |            | 22<br>22     | 25<br>25     |                       | *            | *           | μs<br>μs           |

| SAMPLING DYNAMICS                                                               |            |              |              |                       |              |             |                    |

| Sampling Rate                                                                   | 40         |              |              | *                     |              |             | kHz                |

| Aperture Delay, t <sub>AP</sub>                                                 |            |              |              |                       | - J.         |             |                    |

| With $V_{EE} = +5V$<br>With $V_{FF} = 0V$ to $-15V$                             |            | 20<br>4.0    |              |                       | *            |             | ns<br>μs           |

| Aperture Uncertainty (Jitter)                                                   |            |              |              |                       |              |             |                    |

| With $V_{EE} = +5V$<br>With $V_{ee} = 0V(to - 15V)$                             |            | 300<br>30    |              |                       | *            |             | ps, rms            |

| With $V_{EE} = 0V$ to $-15V$                                                    |            | 30           |              |                       | 7            |             | ns, rms            |

| OUTPUTS                                                                         |            |              |              |                       |              |             | 1                  |

| DIGITAL (DB <sub>11</sub> - DB <sub>0</sub> , STATUS)<br>Output Codes: Unipolar |            | I            | Unipolar Str | I<br>aight Binary (US | i<br>B)      | I           |                    |

| Bipolar                                                                         |            |              | Bipolar Of   | fset Binary (BOE      |              |             |                    |

| Logic Levels: Logic 0 ( $I_{SINK} = 1.6mA$ )                                    | 10.4       |              | +0.4         | ×-                    |              | *           | V                  |

| Logic 1 (I <sub>SOURCE</sub> = 500µA)<br>Leakage, Data Bits Only, High-Z State  | +2.4<br>-5 | 0.1          | +5           | * *                   | *            | *           | ν<br>μΑ            |

| Capacitance                                                                     | I -        | 5            | 1            | 1                     | *            | 1           | pF                 |

# SPECIFICATIONS (CONT)

### ELECTRICAL

At  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{DD} = +5V$ ,  $V_{EE} = -15V$  to +5V, sampling frequency of 40kHz, and  $f_{IN} = 10$ kHz, unless otherwise specified.

|                                                           | A     | DS574JE, JP, | JU              | A   | DS574KE, KP, | KU  |       |

|-----------------------------------------------------------|-------|--------------|-----------------|-----|--------------|-----|-------|

| PARAMETER                                                 | MIN   | TYP          | MAX             | MIN | TYP          | MAX | UNITS |

| INTERNAL REFERENCE VOLTAGE                                |       |              |                 |     |              |     |       |

| Voltage                                                   | +2.4  | +2.5         | +2.6            | *   | *            | *   | V     |

| Source Current Available for External Loads               | 0.5   |              |                 | *   |              |     | mA    |

| POWER SUPPLY REQUIREMENTS                                 |       |              |                 |     |              |     |       |

| Voltage: V <sub>FF</sub> <sup>(7)</sup>                   | -16.5 |              | V <sub>DD</sub> | *   |              | *   | V     |

| V <sub>DD</sub>                                           | +4.5  |              | +5.5            | *   |              | *   | V     |

| Current: $I_{FE}^{(7)}$ (V <sub>EE</sub> = -15V)          |       | -1           |                 |     | *            |     | mA    |

|                                                           |       | +13          | +20             |     | *            | *   | mA    |

| Power Dissipation (T <sub>MIN</sub> to T <sub>MAX</sub> ) |       |              |                 |     |              |     |       |

| $(V_{EE} = 0V \text{ to } +5V)$                           |       | 65           | 100             |     | *            | *   | mW    |

| TEMPERATURE RANGE                                         |       |              |                 |     |              |     |       |

| Specification                                             | 0     |              | +70             | *   |              | *   | °C    |

| Operating:                                                | -40   |              | +85             | *   |              | *   | °C    |

| Storage                                                   | -65   |              | +150            | *   |              | *   | °C    |

\* Same specification as ADS574JE, JP, JU.

NOTES: (1) With fixed  $50\Omega$  resistor from REF OUT to REF IN. This parameter is also adjustable to zero at +25°C. (2) FS in this specification table means Full Scale Range. That is, for a ±10V input range, FS means 20V; for a 0 to +10V range, FS means 10V. (3) Maximum error at T<sub>MIN</sub> and T<sub>MAX</sub>. (4) Based on using V<sub>EE</sub> = +5V, which starts a conversion immediately upon a convert command. Using V<sub>EE</sub> = 0V to -15V makes the ADS574/ADS774 emulate standard ADC574 operation. In this mode, the internal sample/hold acquires the input signal after receiving the convert command, and does not assume that the input level has been stable before the convert command arrives. (5) Using internal reference. (6) This is worst case change in accuracy from accuracy with a +5V supply. (7) V<sub>EE</sub> is optional, and is only used to set the mode for the internal sample/hold. When V<sub>EE</sub> = -15V, I<sub>EE</sub> = -1mA typ; when V<sub>EE</sub> = 0V, I<sub>EE</sub> = ±5µA typ; when V<sub>EE</sub> = +5V, I<sub>EE</sub> = +167µA typ.

### **ABSOLUTE MAXIMUM RATINGS**

|   | V <sub>EE</sub> to Digital Common+V <sub>DD</sub> to -16.5V |

|---|-------------------------------------------------------------|

|   | V <sub>DD</sub> to Digital Common 0V to +7V                 |

|   | Analog Common to Digital Common                             |

|   | Control Inputs (CE, CS, Ao, 12/8, R/C)                      |

|   | to Digital Common0.5V to V <sub>DD</sub> +0.5V              |

|   | Analog Inputs (Ref In, Bipolar Offset, 10V <sub>IN</sub> )  |

|   | to Analog Common±16.5V                                      |

|   | 20V <sub>IN</sub> to Analog Common±24V                      |

|   | Ref Out Indefinite Short to Common,                         |

|   | Momentary Short to V                                        |

|   | Max Junction Temperature                                    |

|   | Power Dissipation                                           |

|   | Lead Temperature (soldering,10s)+300°C                      |

|   | Thermal Resistance, $\theta_{IA}$ : Plastic DIPs            |

|   | SOIC 100°C/W                                                |

| I |                                                             |

### **PACKAGE/ORDERING INFORMATION**

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT  | PACKAGE          | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> | SINAD <sup>(2)</sup> | TEMPERATURE<br>RANGE | LINEARITY<br>ERROR (LSB) |

|----------|------------------|------------------------------------------|----------------------|----------------------|--------------------------|

| ADS574JE | 0.3" Plastic DIP | 246                                      | 68                   | 0°C to +70°C         | ±1                       |

| ADS574KE | 0.3" Plastic DIP | 246                                      | 70                   | 0°C to +70°C         | ±1/2                     |

| ADS574JP | 0.6" Plastic DIP | 215                                      | 68                   | 0°C to +70°C         | ±1                       |

| ADS574KP | 0.6" Plastic DIP | 215                                      | 70                   | 0°C to +70°C         | ±1/2                     |

| ADS574JU | SOIC             | 217                                      | 68                   | 0°C to +70°C         | ±1                       |

| ADS574KU | SOIC             | 217                                      | 70                   | 0°C to +70°C         | ±1/2                     |

NOTES: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book. (2) SINAD is Signal-to-(Noise and Distortion) expressed in dB.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

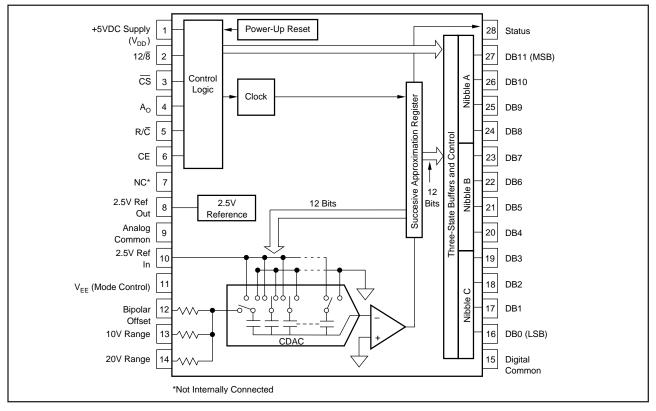

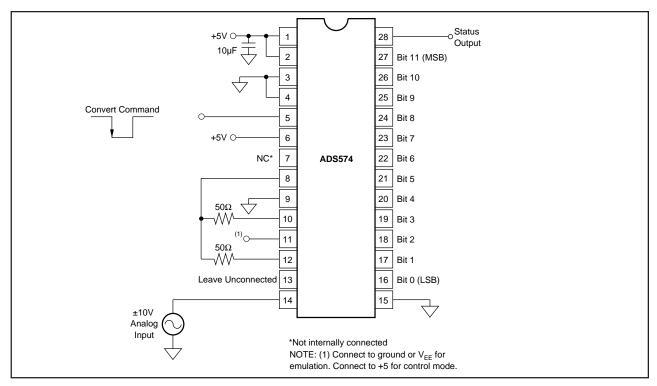

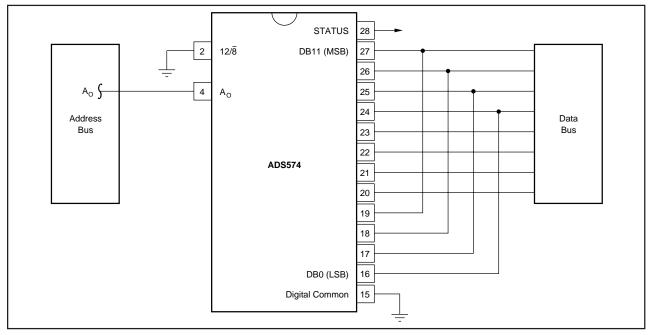

#### **CONNECTION DIAGRAM**

# **TYPICAL PERFORMANCE CURVES**

At T<sub>A</sub> = +25°C, V<sub>DD</sub> = V<sub>EE</sub> = +5V; Bipolar ±10V Input Range; sampling frequency of 40kHz; unless otherwise specified. All plots use 4096 point FFTs.

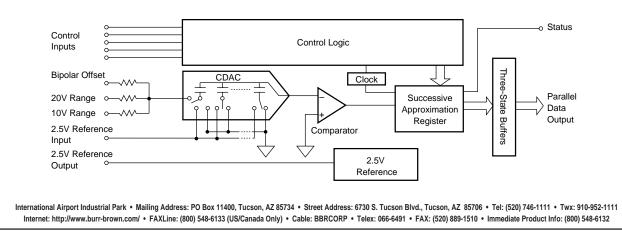

# THEORY OF OPERATION

In the ADS574, the advantages of advanced CMOS technology—high logic density, stable capacitors, precision analog switches—and Burr-Brown's state of the art laser trimming techniques are combined to produce a fast, low power analog-to-digital converter with internal sample/hold.

The charge-redistribution successive-approximation circuitry converts analog input voltages into digital words.

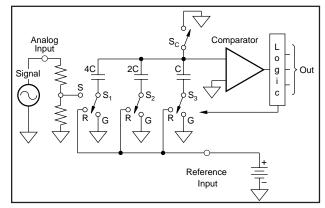

A simple example of a charge-redistribution A/D converter with only 3 bits is shown in Figure 1.

FIGURE 1. 3-Bit Charge Redistribution A/D.

#### **INPUT SCALING**

Precision laser-trimmed scaling resistors at the input divide standard input ranges (0V to +10V, 0V to +20V,  $\pm$ 5V or  $\pm$ 10V) into levels compatible with the CMOS characteristics of the internal capacitor array.

### SAMPLING

While sampling, the capacitor array switch for the MSB capacitor  $(S_1)$  is in position "S", so that the charge on the MSB capacitor is proportional to the voltage level of the analog input signal. The remaining array switches  $(S_2 \text{ and } S_3)$  are set to position "G". Switch  $S_c$  is closed, setting the comparator input offset to zero.

#### CONVERSION

When a conversion command is received, switch  $S_1$  is opened to trap a charge on the MSB capacitor proportional to the analog input level at the time of the sampling command, and switch  $S_c$  is opened to float the comparator input. The charge trapped in the capacitor array can now be moved between the three capacitors in the array by connecting switches  $S_1, S_2$ , and  $S_3$  to positions "R" (to connect to the reference) or "G" (to connect to GND), thus changing the voltage generated at the comparator input.

During the first approximation, the MSB capacitor is connected through switch  $S_1$  to the reference, while switches  $S_2$  and  $S_3$  are connected to GND. Depending on whether the comparator output is HIGH or LOW, the logic will then latch  $S_1$  in position "R" or "G". Similarly, the second

approximation is made by connecting  $S_2$  to the reference and  $S_3$  to GND, and latching  $S_2$  according to the output of the comparator. After three successive approximation steps have been made the voltage level at the comparator will be within 1/2LSB of GND, and a digital word which represents the analog input can be determined from the positions of  $S_1$ ,  $S_2$  and  $S_3$ .

### **OPERATION**

#### **BASIC OPERATION**

Figure 2 shows the minimum circuit required to operate the ADS574 in a basic ±10V range in the Control Mode (discussed in detail in a later section.) The falling edge of a Convert Command (a pulse taking pin 5 LOW for a minimum of 25ns) both switches the ADS574 input to the hold state and initiates the conversion. Pin 28 (STATUS) will output a HIGH during the conversion, and falls only after the conversion is completed and the data has been latched on the data output pins (pins 16 to 27.) Thus, the falling edge of STATUS on pin 28 can be used to read the data from the conversion. Also, during conversion, the STATUS signal puts the data output pins in a High-Z state and inhibits the input lines. This means that pulses on pin 5 are ignored, so that new conversions cannot be initiated during the conversion, either as a result of spurious signals or to short-cycle the ADS574.

The ADS574 will begin acquiring a new sample as soon as the conversion is completed, even before the STATUS output falls, and will track the input signal until the next conversion is started. The ADS574 is designed to complete a conversion and accurately acquire a new signal in  $25\mu$ s max over the full operating temperature range, so that conversions can take place at a full 40kHz.

### **CONTROLLING THE ADS574**

The Burr-Brown ADS574 can be easily interfaced to most microprocessor systems and other digital systems. The microprocessor may take full control of each conversion, or the converter may operate in a stand-alone mode, controlled only by the R/ $\overline{C}$  input. Full control consists of selecting an 8- or 12-bit conversion cycle, initiating the conversion, and reading the output data when ready—choosing either 12 bits all at once, or the 8 MSB bits followed by the 4 LSB bits in a left-justified format. The five control inputs ( $12/\overline{8}$ ,  $\overline{CS}$ , A<sub>0</sub>, R/ $\overline{C}$ , and CE) are all TTL/CMOS-compatible. The functions of the control inputs are described in Table II. The control function truth table is shown in Table III.

### STAND-ALONE OPERATION

For stand-alone operation, control of the converter is accomplished by a single control line connected to  $R/\overline{C}$ . In this mode  $\overline{CS}$  and  $A_0$  are connected to digital common and CE and  $12/\overline{8}$  are connected to +5V. The output data are presented as 12-bit words. The stand-alone mode is used in systems containing dedicated input ports which do not require full bus interface capability.

FIGURE 2. Basic ±10V Operation.

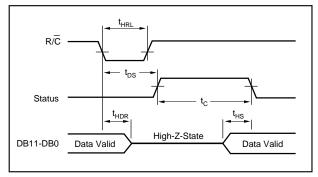

Conversion is initiated by a HIGH-to-LOW transition of  $R/\overline{C}$ . The three-state data output buffers are enabled when  $R/\overline{C}$  is HIGH and STATUS is LOW. Thus, there are two possible modes of operation; data can be read with either a positive pulse on  $R/\overline{C}$ , or a negative pulse on STATUS. In either case the  $R/\overline{C}$  pulse must remain LOW for a minimum of 25ns.

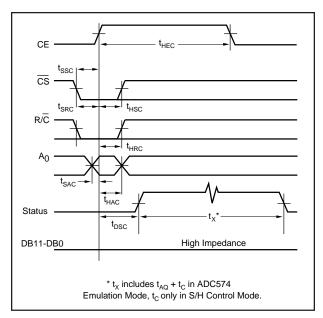

Figure 3 illustrates timing with an  $R/\overline{C}$  pulse which goes LOW and returns HIGH during the conversion. In this case, the three-state outputs go to the high-impedance state in response to the falling edge of  $R/\overline{C}$  and are enabled for external access of the data after completion of the conversion.

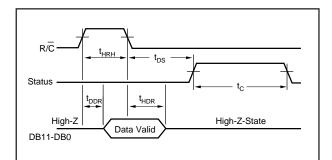

Figure 4 illustrates the timing when a positive  $R/\overline{C}$  pulse is used. In this mode the output data from the previous conversion is enabled during the time  $R/\overline{C}$  is HIGH. A new conversion is started on the falling edge of  $R/\overline{C}$ , and the three-state outputs return to the high-impedance state until the next occurrence of a HIGH  $R/\overline{C}$  pulse. Timing specifications for stand-alone operation are listed in Table IV.

#### FULLY CONTROLLED OPERATION

#### **Conversion Length**

Conversion length (8-bit or 12-bit) is determined by the state of the  $A_0$  input, which is latched upon receipt of a conversion start transition (described below). If  $A_0$  is latched HIGH, the conversion continues for 8 bits. The full 12-bit conversion will occur if  $A_0$  is LOW. If all 12 bits are read following an 8-bit conversion, the 4LSBs (DB0-DB3) will be LOW (logic 0).  $A_0$  is latched because it is also involved in enabling the output buffers. No other control inputs are latched.

#### **CONVERSION START**

The converter initiates a conversion based on a transition occurring on any of three logic inputs (CE,  $\overline{CS}$ , and  $R/\overline{C}$ ) as shown in Table III. Conversion is initiated by the last of the three to reach the required state and thus all three may be dynamically controlled. If necessary, all three may change state simultaneously, and the nominal delay time is the same regardless of which input actually starts the conversion. If it is desired that a particular input establish the actual start of conversion, the other two should be stable a minimum of 50ns prior to the transition of the critical input. Timing relationships for start of conversion timing are illustrated in Figure 5. The specifications for timing are contained in Table V.

The STATUS output indicates the current state of the converter by being in a high state only during conversion. During this time the three state output buffers remain in a high-impedance state, and therefore data cannot be read during conversion. During this period additional transitions of the three digital inputs which control conversion will be ignored, so that conversion cannot be prematurely terminated or restarted. However, if  $A_0$  changes state after the beginning of conversion, any additional start conversion transition will latch the new state of  $A_0$ , possibly resulting in an incorrect conversion length (8 bits vs 12 bits) for that conversion.

| Binary (BIN) Output                                                                                                                                                                                                                |                                                                                                                   | Input Voltage Range and LSB Values           |                                            |                                                   |                                                |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------|---------------------------------------------------|------------------------------------------------|--|--|--|

| Analog Input Voltage Range                                                                                                                                                                                                         | Defined As:                                                                                                       | ±10V                                         | +5V                                        | 0V to +10V                                        | 0V to +20V                                     |  |  |  |

| One Least Significant Bit<br>(LSB)                                                                                                                                                                                                 | <u>FSR</u><br>2 <sup>n</sup><br>n = 8<br>n = 12                                                                   | 20V<br>2 <sup>n</sup><br>78.13mV<br>4.88mV   | 10V<br>2 <sup>n</sup><br>39.06mV<br>2.44mV | <u>10V</u><br>2 <sup>n</sup><br>39.06mV<br>2.44mV | 20V<br>2 <sup>n</sup><br>78.13mV<br>4.88mV     |  |  |  |

| $\begin{array}{l} \text{Output Transition Values} \\ \text{FFE}_{\text{H}} \text{ to } \text{FFF}_{\text{H}} \\ \text{7FFF}_{\text{H}} \text{ to } 800_{\text{H}} \\ \text{000}_{\text{H}} \text{ to } 001_{\text{H}} \end{array}$ | + Full-Scale Calibration<br>Midscale Calibration (Bipolar Offset)<br>Zero Calibration ( – Full-Scale Calibration) | +10V – 3/2LSB<br>0 – 1/2LSB<br>–10V + 1/2LSB | +5V – 3/2LSB<br>0 – 1/2LSB<br>–5V + 1/2LSB | +10V – 3/2LSB<br>+5V – 1/2LSB<br>0 to +1/2LSB     | +10V – 3/2LSB<br>±10V – 1/2LSB<br>0 to +1/2LSB |  |  |  |

TABLE I. Input Voltages, Transition Values, and LSB Values.

| DESIGNATION            | DEFINITION                                            | FUNCTION                                                                                                                                                                                                                                                     |

|------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE (Pin 6)             | Chip Enable<br>(active high)                          | Must be HIGH ("1") to either initiate a conversion or read output data. 0-1 edge may be used to initiate a<br>conversion.                                                                                                                                    |

| CS (Pin 3)             | Chip Select<br>(active low)                           | Must be LOW ("0") to either initiate a conversion or read output data. 1-0 edge may be used to initiate a<br>conversion.                                                                                                                                     |

| R/C (Pin 5)            | Read/Convert<br>("1" = read)<br>("0" = convert)       | Must be LOW ("0") to initiate either 8- or 12-bit conversions. 1-0 edge may be used to initiate a conversion.<br>Must be HIGH ("1") to read output data. 0-1 edge may be used to initiate a read operation.                                                  |

| A <sub>O</sub> (Pin 4) | Byte Address<br>Short Cycle                           | In the start-convert mode, $A_O$ selects 8-bit ( $A_O = $ "1") or 12-bit ( $A_O = $ "0") conversion mode. When reading output data in two 8-bit bytes, $A_O =$ "0" accesses 8 MSBs (high byte) and $A_O =$ "1" accesses 4 LSBs and trailing "0s" (low byte). |

| 12/8 (Pin 2)           | Data Mode Select<br>("1" = 12 bits)<br>("0" = 8 bits) | When reading output data, $12/\overline{8}$ = "1" enables all 12 output bits simultaneously. $12/\overline{8}$ = "0" will enable the MSBs or LSBs as determined by the A <sub>O</sub> line.                                                                  |

TABLE II. Control Line Functions.

| CE         | <del>c</del> s | R/Ĉ          | 12/8 | Ao | OPERATION                  |

|------------|----------------|--------------|------|----|----------------------------|

| 0          | Х              | Х            | Х    | Х  | None                       |

| Х          | 1              | Х            | Х    | Х  | None                       |

| ↑          | 0              | 0            | Х    | 0  | Initiate 12-bit conversion |

| $\uparrow$ | 0              | 0            | Х    | 1  | Initiate 8-bit conversion  |

| 1          | $\downarrow$   | 0            | Х    | 0  | Initiate 12-bit conversion |

| 1          | $\downarrow$   | 0            | Х    | 1  | Initiate 8-bit conversion  |

| 1          | 0              | $\checkmark$ | Х    | 0  | Initiate 12-bit conversion |

| 1          | 0              | $\checkmark$ | Х    | 1  | Initiate 8-bit conversion  |

| 1          | 0              | 1            | 1    | Х  | Enable 12-bit output       |

| 1          | 0              | 1            | 0    | 0  | Enable 8 MSBs only         |

| 1          | 0              | 1            | 0    | 1  | Enable 4 LSBs plus 4       |

|            |                |              |      |    | trailing zeroes            |

TABLE III. Control Input Truth Table.

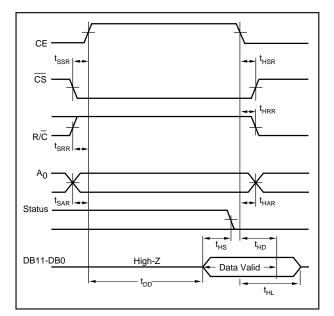

#### **READING OUTPUT DATA**

After conversion is initiated, the output data buffers remain in a high-impedance state until the following four logic conditions are simultaneously met:  $R/\overline{C}$  HIGH, STATUS LOW, CE HIGH, and  $\overline{CS}$  LOW. Upon satisfaction of these conditions the data lines are enabled according to the state of inputs  $12/\overline{8}$  and  $A_0$ . See Figure 6 and Table V for timing relationships and specifications.

In most applications the  $12/\overline{8}$  input will be hard-wired in either the high or low condition, although it is fully TTL and CMOS-compatible and may be actively driven if desired. When  $12/\overline{8}$  is HIGH, all 12 output lines (DB0-DB11) are enabled simultaneously for full data word transfer to a 12-bit or 16-bit bus. In this situation the A<sub>0</sub> state is ignored when reading the data.

When  $12/\overline{8}$  is LOW, the data is presented in the form of two 8-bit bytes, with selection of the byte of interest accomplished by the state of A<sub>0</sub> during the read cycle. When A<sub>0</sub> is LOW, the byte addressed contains the 8MSBs. When  $A_0$  is HIGH, the byte addressed contains the 4LSBs from the conversion followed by four logic zeros which have been forced by the control logic. The left-justified formats of the two 8-bit bytes are shown in Figure 7. Connection of the ADS574 to an 8-bit bus for transfer of the data is illustrated in Figure 8. The design of the ADS574 guarantees that the  $A_0$  input may be toggled at any time with no damage to the converter; the outputs which are tied together in Figure 8 cannot be enabled at the same time. The A<sub>0</sub> input is usually driven by the least significant bit of the address bus, allowing storage of the output data word in two consecutive memory locations.

FIGURE 3. R/C Pulse Low—Outputs Enabled After Conversion.

FIGURE 4.  $R/\overline{C}$  Pulse High — Outputs Enabled Only While  $R/\overline{C}$  Is High.

### S/H CONTROL MODE AND ADC574 EMULATION MODE

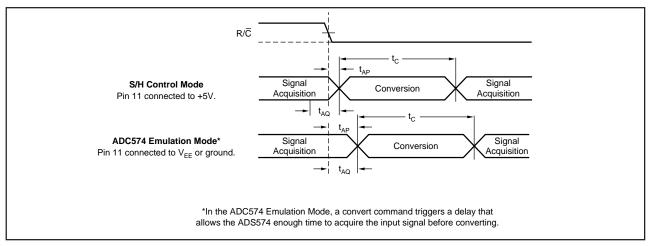

The basic difference between these two modes is the assumptions about the state of the input signal both before and during the conversion. The differences are shown in Figure 9 and Table VI. In the Control Mode it is assumed that during the required  $4\mu$ s acquisition time the signal is not slewing faster than the slew rate of the ADS574. No assumption is made about the input level after the convert command arrives, since the input signal is sampled and conversion begins immediately after the convert command.

This means that a convert command can also be used to switch an input multiplexer or change gains on a programmable gain amplifier, allowing the input signal to settle before the next acquisition at the end of the conversion. Because aperture jitter is minimized by the internal sample/ hold circuit, a high input frequency can be converted without an external sample/hold.

In the Emulation Mode, no assumption is made about the input signal prior to the convert command. A delay time is introduced between the convert command and the start of conversion to allow the ADS574 enough time to acquire the input signal before converting. The delay increases the effective aperture time from  $0.02\mu s$  to  $4\mu s$ , but allows the ADS574 to replace the ADC574 in any circuit. Any slewing of the analog input prior to the convert command in existing

| SYMBOL                                                  | PARAMETER                                                             | MIN | TYP | MAX | UNITS          |

|---------------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|----------------|

| t <sub>HRL</sub><br>t <sub>DS</sub><br>t <sub>HDR</sub> | Low R/Ĉ Pulse Width<br>STS Delay from R/Ĉ<br>Data Valid After R/Ĉ Low | 25  |     | 200 | ns<br>ns<br>ns |

| чыя<br>t <sub>нкн</sub><br>t <sub>ddr</sub>             | High R/C Pulse Width<br>Data Access Time                              | 100 |     | 150 | ns             |

TABLE IV. Stand-Alone Mode Timing. ( $T_A = T_{MIN}$  to  $T_{MAX}$ ).

| SYMBOL           | PARAMETER                           | MIN | ТҮР | MAX  | UNITS |

|------------------|-------------------------------------|-----|-----|------|-------|

| Convert Mode     |                                     |     |     |      |       |

| t <sub>DSC</sub> | STS delay from CE                   |     | 60  | 200  | ns    |

| t <sub>HEC</sub> | CE Pulse width                      | 50  | 30  |      | ns    |

| t <sub>ssc</sub> | CS to CE setup                      | 50  | 20  |      | ns    |

| t <sub>HSC</sub> | CS low during CE high               | 50  | 20  |      | ns    |

| t <sub>SRC</sub> | R/C to CE setup                     | 50  | 0   |      | ns    |

| t <sub>HRC</sub> | $R/\overline{C}$ low during CE high | 50  | 20  |      | ns    |

| t <sub>SAC</sub> | A <sub>o</sub> to CE setup          | 0   |     |      | ns    |

| t <sub>HAC</sub> | A <sub>O</sub> valid during CE high | 50  | 20  |      | ns    |

| Read Mode        |                                     |     |     |      |       |

| t <sub>DD</sub>  | Access time from CE                 |     | 75  | 150  | ns    |

| t <sub>HD</sub>  | Data valid after CE low             | 25  | 35  |      | ns    |

| t <sub>HL</sub>  | Output float delay                  |     | 100 | 150  | ns    |

| t <sub>SSR</sub> | CS to CE setup                      | 50  | 0   |      | ns    |

| t <sub>SRR</sub> | $R/\overline{C}$ to CE setup        | 0   |     |      | ns    |

| t <sub>SAR</sub> | A <sub>O</sub> to CE setup          | 50  | 25  |      | ns    |

| t <sub>HSR</sub> | CS valid after CE low               | 0   |     |      | ns    |

| t <sub>HRR</sub> | $R/\overline{C}$ high after CE low  | 0   |     |      | ns    |

| t <sub>HAR</sub> | Ao valid after CE low               | 50  |     |      | ns    |

| t <sub>HS</sub>  | STC delay after data valid          | 300 | 400 | 1000 |       |

TABLE V. Timing Specifications, Fully Controlled Operation. ( $T_A = T_{MIN}$  to  $T_{MAX}$ ).

FIGURE 5. Conversion Cycle Timing.

FIGURE 6. Read Cycle Timing.

| Word 1    |      |      |     |     |     |     |     |     |     |     |     | Word | 2   |     |     |     |

|-----------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|

| Processor | DB7  | DB6  | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | DB7 | DB6 | DB5 | DB4  | DB3 | DB2 | DB1 | DB0 |

| Converter | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0  | 0   | 0   | 0   | 0   |

FIGURE 7. 12-Bit Data Format for 8-Bit Systems.

FIGURE 8. Connection to an 8-Bit Bus.

systems (due to multiplexers, sample/holds, etc. in front of the converter) does not affect the accuracy of the ADS574 conversion in the Emulation Mode.

In both modes, as soon as the conversion is completed the internal sample/hold circuit immediately begins slewing to track the input signal.

Basically, the Control Mode is provided to allow full use of the internal sample/hold, eliminating the need for an external sample/hold in most applications. As compared with systems using separate sample/hold and A/D, the ADS574 in the Control Mode also eliminates the need for one of the control signals, usually the convert command. The command that puts the internal sample/hold in the hold state also initiates a conversion, reducing timing constraints in many systems.

The Emulation Mode allows the ADS574 to be dropped into almost all existing ADC574 sockets without changes to any other existing system hardware or software. The input to the ADS574 in the Emulation Mode does not need to be stable before a convert command is received, so that multiplexers, programmable gain amplifiers, etc., can be slewing quickly any time before a convert command is given as long as the analog input to the ADS574 is stable after the convert command is received, as it needs to be in existing ADC574 systems for accurate operation. In fact, even in the Emulation Mode, system throughput can be speeded up, since the input to the ADS574 can start slewing before the end of a conversion (after the acquisition time), which is not possible with existing ADC574s.

### INSTALLATION LAYOUT PRECAUTIONS

Analog (pin 9) and digital (pin 15) commons are not connected together internally in the ADS574, but should be connected together as close to the unit as possible and to an analog common ground plane beneath the converter on the component side of the board. In addition, a wide conductor pattern should run directly from pin 9 to the analog supply common, and a separate wide conductor pattern from pin 15 to the digital supply common.

If the single-point system common cannot be established directly at the converter, pin 9 and pin 15 should still be connected together at the converter. A single wide conductor pattern then connects these two pins to the system common. In either case, the common return of the analog input signal should be referenced to pin 9 of the ADC. This prevents any voltage drops that might occur in the power supply common returns from appearing in series with the input signal.

|                                                      |                                                             |     | CONTROL M<br>1 Connected |          | ADC57<br>(Pin 11 C |                 |          |                |

|------------------------------------------------------|-------------------------------------------------------------|-----|--------------------------|----------|--------------------|-----------------|----------|----------------|

| SYMBOL                                               | PARAMETER                                                   | MIN | TYP                      | MAX      | MIN                | TYP             | MAX      | UNITS          |

| t <sub>AQ</sub> + t <sub>C</sub>                     | Throughput Time:<br>12-bit Conversions<br>8-bit Conversions |     | 22<br>16                 | 25<br>18 |                    | 22<br>16        | 25<br>18 | μs<br>μs       |

| t <sub>C</sub>                                       | Conversion Time:<br>12-bit Conversions<br>8-bit Conversions |     | 18<br>12                 |          |                    | 18<br>12        |          | μs<br>µs       |

| t <sub>AQ</sub><br>t <sub>AP</sub><br>t <sub>J</sub> | Acquisition Time<br>Aperture Delay<br>Aperture Uncertainty  |     | 4<br>20<br>0.3           |          |                    | 4<br>4000<br>30 |          | μs<br>ns<br>ns |

TABLE VI. Conversion Timing,  $T_{MIN}$  to  $T_{MAX}$ .

FIGURE 9. Signal Acquisition and Conversion Timing.

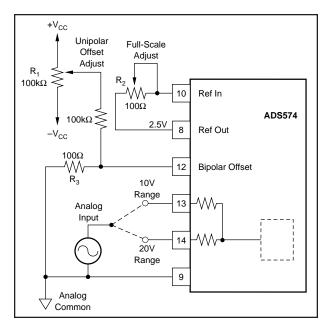

FIGURE 10. Unipolar Configuration.

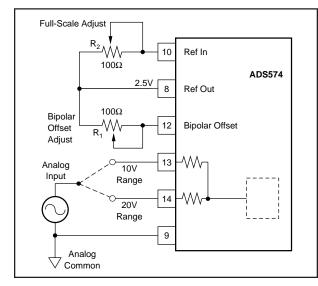

FIGURE 11. Bipolar Configuration.

If the 10V analog input range is used (either bipolar or unipolar), the 20V range input (pin 14) should be shielded with ground plane to reduce noise pickup.

Coupling between analog input and digital lines should be minimized by careful layout. For instance, if the lines must cross, they should do so at right angles. Parallel analog and digital lines should be separated from each other by a pattern connected to common.

If external full scale and offset potentiometers are used, the potentiometers and associated resistors should be as close as possible to the ADS574.

#### POWER SUPPLY DECOUPLING

On the ADS574, +5V (to Pin 1) is the only power supply required for correct operation. Pin 7 is not connected internally, so there is no problem in existing ADC574 sockets where this is connected to +15V. Pin 11 ( $V_{EE}$ ) is only used as a logic input to select modes of control over the sampling function as described above. When used in an existing ADC574 socket, the -15V on pin 11 selects the ADC574 Emulation Mode. Since pin 11 is used as a logic input, it is immune to typical supply variations.

The +5V supply should be bypassed with a  $10\mu$ F tantalum capacitor located close to the converter to promote noise-free operations, as shown in Figure 2. Noise on the power supply lines can degrade the converter's performance. Noise and spikes from a switching power supply are especially troublesome.

#### **RANGE CONNECTIONS**

The ADS574 offers four standard input ranges: 0V to +10V, 0V to +20V,  $\pm$ 5V, or  $\pm$ 10V. Figures 10 and 11 show the necessary connections for each of these ranges, along with the optional gain and offset trim circuits. If a 10V input range is required, the analog input signal should be connected to pin 13 of the converter. A signal requiring a 20V range is connected to pin 14. In either case the other pin of the two is left unconnected. Pin 12 (Bipolar Offset) is connected either to Pin 9 (Analog Common) for unipolar operation, or to Pin 8 (2.5V Ref Out), or the external reference, for bipolar operation. Full-scale and offset adjustments are described below.

The input impedance of the ADS574 is typically  $84k\Omega$  in the 20V ranges and  $21k\Omega$  in the 10V ranges. This is significantly higher than that of traditional ADC574 architectures, reducing the load on the input source in most applications.

### **INPUT STRUCTURE**

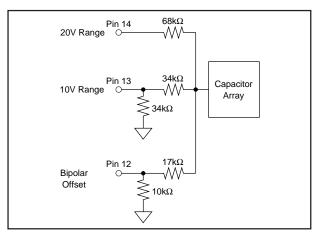

Figure 12 shows the resistor divider input structure of the ADS574. Since the input is driving a capacitor in the CDAC during acquisition, the input is looking into a high imped-

FIGURE 12. ADS574 Input Structure.

ance node as compared with traditional ADC574 architectures, where the resistor divider network looks into a comparator input node at virtual ground.

To understand how this circuit works, it is necessary to know that the input range on the internal sampling capacitor is from 0V to +3.33V, and the analog input to the ADS574 must be converted to this range. Unipolar 20V range can be used as an example of how the divider network functions. In 20V operation, the analog input goes into pin 14. Pin 13 is left unconnected and pin 12 is connected to analog common pin 9. From Figure 12, it is clear that the input to the capacitor array will be the analog input voltage on pin 14 divided by the resistor network ( $68k\Omega + 68k\Omega \parallel 17k\Omega$ ). A 20V input at pin 14 is divided to 3.33V at the capacitor array, while a 0V input at pin 14 gives 0V at the capacitor array.

The main effect of the  $10k\Omega$  internal resistor on pin 12 is to provide offset adjust response the same as that of traditional ADC574 architectures without needing to change the external trimpot values.

### SINGLE SUPPLY OPERATION

The ADS574 is designed to operate from a single +5V supply, and handle all of the unipolar and bipolar input ranges, in either the Control Mode or the Emulation Mode as described above. Pin 7 is not connected internally. This is where +12V or +15V is supplied on traditional ADC574s. Pin 11, the -12V or -15V supply input on traditional ADC574s, is used only as a logic input on the ADS574. There is a resistor divider internally on pin 11 to reduce that input to a correct logic level within the ADS574, and this resistor will add 10mW to 15mW to the power consumption of the ADS574 when -15V is supplied to pin 11. To minimize power consumption in a system, pin 11 can be simply grounded (for Emulation Mode) or tied to +5V (for Control Mode.)

There are no other modifications required for the ADS574 to function with a single +5V supply.

## CALIBRATION

#### OPTIONAL EXTERNAL FULL-SCALE AND OFFSET ADJUSTMENTS

Offset and full-scale errors may be trimmed to zero using external offset and full-scale trim potentiometers connected to the ADS574 as shown in Figures 10 and 11 for unipolar and bipolar operation.

### CALIBRATION PROCEDURE— UNIPOLAR RANGES

If external adjustments of full-scale and offset are not required, replace  $R_2$  in Figure 10 with a 50 $\Omega$ , 1% metal film resistor, omitting the other adjustment components. Connect pin 12 to pin 9.

If adjustment is required, connect the converter as shown in Figure 10. Sweep the input through the end-point transition voltage (0V + 1/2LSB; +1.22mV for the 10V range, +2.44mV for the 20V range) that causes the output code to be DB0 ON (HIGH). Adjust potentiometer  $R_1$  until DB0 is alternately toggling ON and OFF with all other bits OFF. Then adjust full scale by applying an input voltage of nominal full-scale minus 3/2LSB, the value which should cause all bits to be ON. This value is +9.9963V for the 10V range and +19.9927V for the 20V range. Adjust potentiometer  $R_2$  until bits DB1-DB11 are ON and DB0 is toggling ON and OFF.

#### **CALIBRATION PROCEDURE—BIPOLAR RANGES**

If external adjustments of full-scale and bipolar offset are not required, replace the potentiometers in Figure 11 by  $50\Omega$ , 1% metal film resistors.

If adjustments are required, connect the converter as shown in Figure 11. The calibration procedure is similar to that described above for unipolar operation, except that the offset adjustment is performed with an input voltage which is 1/2LSB above the minus full-scale value (-4.9988V for the  $\pm 5V$  range, -9.9976V for the  $\pm 10V$  range). Adjust R<sub>1</sub> for DB0 to toggle ON and OFF with all other bits OFF. To adjust full-scale, apply a DC input signal which is 3/2LSBbelow the nominal plus full-scale value (+4.9963V for  $\pm 5V$ range, +9.9927V for  $\pm 10V$  range) and adjust R<sub>2</sub> for DB0 to toggle ON and OFF with all other bits ON.

www.ti.com

29-Sep-2009

### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| ADS574AU         | OBSOLETE              | SOIC            | DW                 | 28   |                | TBD                        | Call TI          | Call TI                      |

| ADS574AU/1K      | OBSOLETE              | SOIC            | DW                 | 28   |                | TBD                        | Call TI          | Call TI                      |

| ADS574JE         | ACTIVE                | PDIP            | NT                 | 28   | 13             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | N / A for Pkg Type           |

| ADS574JEG4       | ACTIVE                | PDIP            | NT                 | 28   | 13             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | N / A for Pkg Type           |

| ADS574JP         | ACTIVE                | PDIP            | NTD                | 28   | 13             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | N / A for Pkg Type           |

| ADS574JP-2       | OBSOLETE              | PDIP            | NTD                | 28   |                | TBD                        | Call TI          | Call TI                      |

| ADS574JPG4       | ACTIVE                | PDIP            | NTD                | 28   | 13             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | N / A for Pkg Type           |

| ADS574JU         | OBSOLETE              | SOIC            | DW                 | 28   |                | TBD                        | Call TI          | Call TI                      |

| ADS574JU/1K      | OBSOLETE              | SOIC            | DW                 | 28   |                | TBD                        | Call TI          | Call TI                      |

| ADS574KE         | ACTIVE                | PDIP            | NT                 | 28   | 13             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | N / A for Pkg Type           |

| ADS574KEG4       | ACTIVE                | PDIP            | NT                 | 28   | 13             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | N / A for Pkg Type           |

| ADS574KP         | ACTIVE                | PDIP            | NTD                | 28   | 13             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | N / A for Pkg Type           |

| ADS574KPG4       | ACTIVE                | PDIP            | NTD                | 28   | 13             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | N / A for Pkg Type           |

| ADS574KU-2       | OBSOLETE              | SOIC            | DW                 | 28   |                | TBD                        | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

#### www.ti.com

29-Sep-2009

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated