www.ti.com

# ADC10DL065 Dual 10-Bit, 65 MSPS, 3.3V, 370mW A/D Converter

Check for Samples: ADC10DL065

### **FEATURES**

- Single +3.3V Supply Operation

- Internal Sample-and-Hold

- Internal Reference

- Outputs 2.4V to 3.6V Compatible

- Power Down Mode

- Duty Cycle Stabilizer

- Multiplexed Output Mode

## **KEY SPECIFICATIONS**

- Resolution 10 Bits

- DNL ±0.16 LSB (typ)

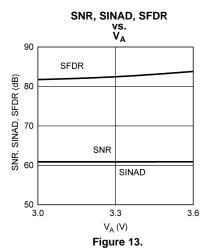

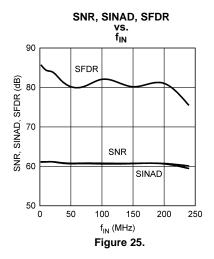

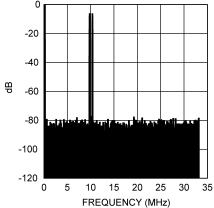

- SNR (f<sub>IN</sub> = 10 MHz) 61 dB (typ)

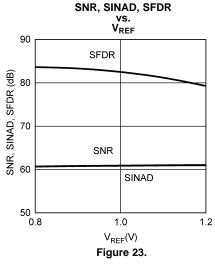

- SFDR (f<sub>IN</sub> = 10 MHz) 85 dB (typ)

- Data Latency 7 Clock Cycles

- Power Consumption

- Operating 370 mW (typ)

- Power Down Mode 36 mW (typ)

### **APPLICATIONS**

- Ultrasound and Imaging

- Instrumentation

- Communications Receivers

- Sonar/Radar

- xDSL

- DSP Front Ends

### DESCRIPTION

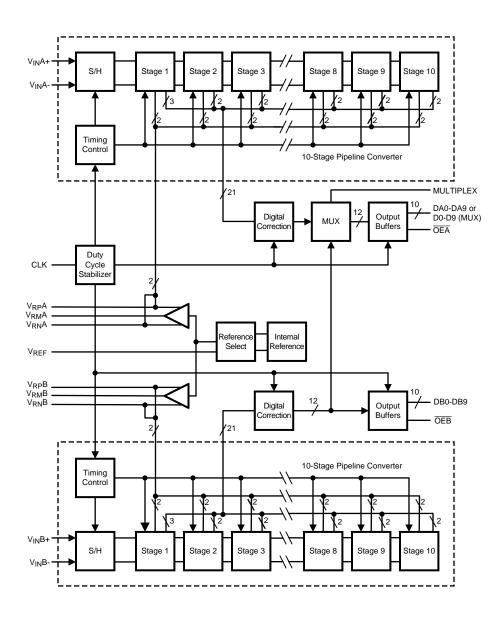

The ADC10DL065 is a dual, low power monolithic CMOS analog-to-digital converter capable of converting analog input signals into 10-bit digital words at 65 Megasamples per second (MSPS). This converter uses a differential, pipeline architecture with digital error correction and an on-chip sample-and-hold circuit to minimize power consumption while providing excellent dynamic performance and a 250 MHz Full Power Bandwidth. Operating on a single +3.3V power supply, the ADC10DL065 achieves 9.8 effective bits at nyquist and consumes just 370 mW at 65 MSPS, including the reference current. The Power Down feature reduces power consumption to 36 mW.

The differential inputs provide a full scale differential input swing equal to 2 times  $V_{REF}$  with the possibility of a single-ended input. Full use of the differential input is recommended for optimum performance. The digital outputs from the two ADC's are available on a single multiplexed 10-bit bus or on separate buses. Duty cycle stabilization and output data format are selectable using a quad state function pin. The output data can be set for offset binary or two's complement.

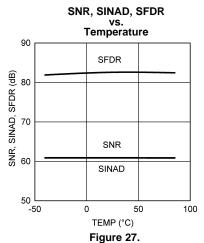

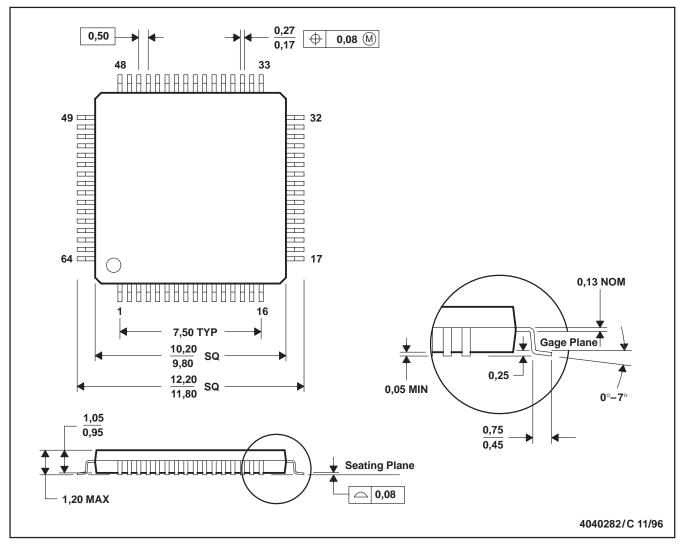

To ease interfacing to lower voltage systems, the digital output driver power pins of the ADC10DL065 can be connected to a separate supply voltage in the range of 2.4V to the analog supply voltage. This device is available in the 64-lead TQFP package and will operate over the industrial temperature range of -40°C to +85°C. An evaluation board is available to ease the evaluation process.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

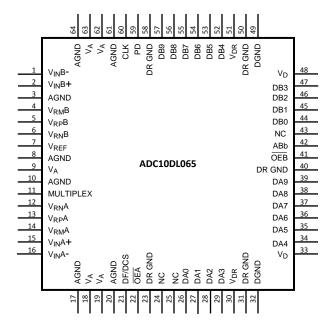

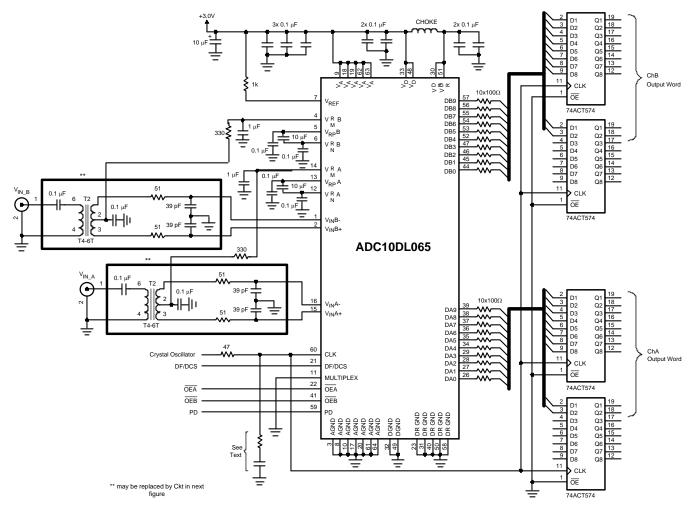

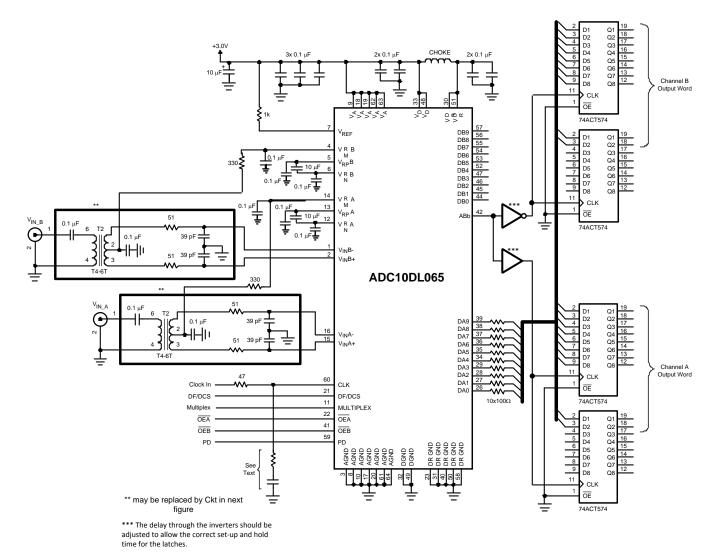

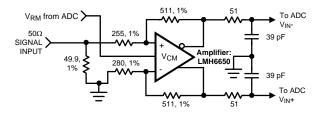

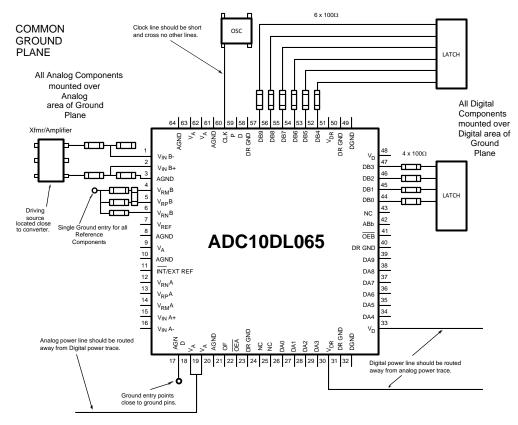

# **Connection Diagram**

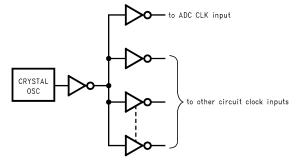

# **Block Diagram**

# **Pin Descriptions and Equivalent Circuits**

|                    | Pin Descriptions and Equivalent Circuits                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin No.            | Symbol                                                                               | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| ANALOG I/O         |                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

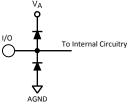

| 15<br>2<br>16<br>1 | V <sub>IN</sub> A+<br>V <sub>IN</sub> B+<br>V <sub>IN</sub> A-<br>V <sub>IN</sub> B- | VA OF THE PROPERTY OF THE PROP | Differential analog input pins. With a 1.0V reference voltage the differential full-scale input signal level is 2.0 $V_{P-P}$ with each input pin voltage centered on a common mode voltage, $V_{CM}$ . The negative input pins may be connected to $V_{CM}$ for single-ended operation, but a differential input signal is required for best performance.                                                                                                                                      |  |  |  |  |  |  |  |

| 7                  | V <sub>REF</sub>                                                                     | VA AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This pin is the reference select pin and the external reference input. If (V <sub>A</sub> - 0.3V) < V <sub>REF</sub> < V <sub>A</sub> , the internal 1.0V reference is selected. If AGND < V <sub>REF</sub> < (AGND + 0.3V), the internal 0.5V reference is selected. If a voltage in the range of 0.8V to 1.2V is applied to this pin, that voltage is used as the reference. V <sub>REF</sub> should be bypassed to AGND with a 0.1 $\mu F$ capacitor when an external reference is used.     |  |  |  |  |  |  |  |

| 21                 | DF/DCS                                                                               | V <sub>A</sub> V <sub>Float</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | This is a four-state pin. DF/DCS = $V_A$ , output data format is offset binary with duty cycle stabilization applied to the input clock DF/DCS = AGND, output data format is 2's complement, with duty cycle stabilization applied to the input clock. DF/DCS = $V_{RM}$ A or $V_{RM}$ B, output data is 2's complement without duty cycle stabilization applied to the input clock DF/DCS = "float", output data is offset binary without duty cycle stabilization applied to the input clock. |  |  |  |  |  |  |  |

| 13                 | V <sub>RP</sub> A                                                                    | V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 5<br>14<br>4       | V <sub>RP</sub> B<br>V <sub>RM</sub> A<br>V <sub>RM</sub> B                          | V <sub>A</sub> V <sub>A</sub> V <sub>A</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 12<br>6            | V <sub>RN</sub> A<br>V <sub>RN</sub> B                                               | VA VA AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | These pins are high impedance reference bypass pins. All these pins should each be bypassed to ground with a 0.1 $\mu F$ capacitor. A 10 $\mu F$ capacitor should be placed between the $V_{RP}A$ and $V_{RN}A$ pins and between the $V_{RP}B$ and $V_{RN}B$ pins. $V_{RM}A$ and $V_{RM}B$ may be loaded to 1mA for use as a temperature stable 1.5V reference. The remaining pins should not be loaded.                                                                                        |  |  |  |  |  |  |  |

# Pin Descriptions and Equivalent Circuits (continued)

| Pin No.                     | Symbol         | Equivalent Circuit             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------|----------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL I/O                 | <u> </u>       |                                | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 60                          | CLK            | V <sub>A</sub>                 | Digital clock input. The range of frequencies for this input is as specified in the electrical tables with specified performance at 65 MHz. The input is sampled on the rising edge.                                                                                                                                                                                                                                                                                                           |

| 22<br>41                    | OEA<br>OEB     | AGND DGND                      | OEA and OEB are the output enable pins that, when low, holds their respective data output pins in the active state. When either of these pins is high, the corresponding outputs are in a high impedance state.                                                                                                                                                                                                                                                                                |

| 59                          | PD             | V <sub>A</sub> V <sub>D</sub>  | PD is the Power Down input pin. When high, this input puts the converter into the power down mode. When this pin is low, the converter is in the active mode.                                                                                                                                                                                                                                                                                                                                  |

| 11                          | MULTIPLEX      | AGND DGND                      | When low, "A" & "B" data is present on it's respective data output lines (Parallel Mode).  When high, both "A" and "B" channel data is present on the "DA0:DA9" digital outputs (Multiplex Mode). The ABb pin is used to synchronize the data.                                                                                                                                                                                                                                                 |

| 26–29<br>34–39              | DA0-DA9        | V <sub>DR</sub> V <sub>A</sub> | Digital data output pins that make up the 10-bit conversion results of                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 44–47<br>52–57              | DB0-DB9        |                                | their respective converters. DA0 and DB0 are the LSBs, while DA9 and DB9 are the MSBs of the output word. Output levels are TTL/CMOS compatible. Optimum loading is < 10pF.                                                                                                                                                                                                                                                                                                                    |

| 42                          | ABb            | DR GND                         | When MULTIPLEX is low, this pin is not used. When MULTIPLEX is high this is the ABb signal, which is used to synchronize the multiplexed data. ABb changes synchronously with the Multiplexed "A" and "B" channels. ABb is "high" when "A" channel data is valid and is "low" when "B" channel data is valid.                                                                                                                                                                                  |

| 24, 25, 43                  | NC             |                                | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ANALOG POV                  | VER            |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9, 18, 19, 62,<br>63        | V <sub>A</sub> |                                | Positive analog supply pins. These pins should be connected to a quiet +3.3V source and bypassed to AGND with 0.1 $\mu$ F capacitors located within 1 cm of these power pins, and with a 10 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                 |

| 3, 8, 10, 17,<br>20, 61, 64 | AGND           |                                | The ground return for the analog supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DIGITAL POW                 | ER             |                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 33, 48                      | V <sub>D</sub> |                                | Positive digital supply pin. This pin should be connected to the same quiet +3.3V source as is $V_A$ and be bypassed to DGND with a 0.1 $\mu$ F capacitor located within 1 cm of the power pin and with a 10 $\mu$ F capacitor.                                                                                                                                                                                                                                                                |

| 32, 49                      | DGND           |                                | The ground return for the digital supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

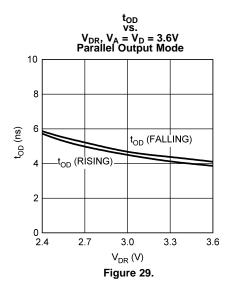

| 30, 51                      | $V_{DR}$       |                                | Positive driver supply pin for the ADC10DL065's output drivers. This pin should be connected to a voltage source of +2.4V to $V_D$ and be bypassed to DR GND with a 0.1 $\mu\text{F}$ capacitor. If the supply for this pin is different from the supply used for $V_A$ and $V_D$ , it should also be bypassed with a 10 $\mu\text{F}$ capacitor. $V_{DR}$ should never exceed the voltage on $V_D$ . All 0.1 $\mu\text{F}$ bypass capacitors should be located within 1 cm of the supply pin. |

| 23, 31, 40,<br>50, 58       | DR GND         |                                | The ground return for the digital supply for the ADC10DL065's output drivers. These pins should be connected to the system digital ground, but not be connected in close proximity to the ADC10DL065's DGND or AGND pins. See Layout and Grounding for more details.                                                                                                                                                                                                                           |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1)(2)

| / NOOTIGEO MIGAMINA                               | ramige                                                   |                                               |  |  |

|---------------------------------------------------|----------------------------------------------------------|-----------------------------------------------|--|--|

| V <sub>A</sub> , V <sub>D</sub> , V <sub>DR</sub> |                                                          | 4.2V                                          |  |  |

| V <sub>A</sub> -V <sub>D</sub>                    |                                                          | ≤ 100 mV                                      |  |  |

| Voltage on Any Input or Out                       | put Pin                                                  | $-0.3V$ to $(V_A \text{ or } V_D + 0.3V)$     |  |  |

| Input Current at Any Pin (3)                      |                                                          | ±25 mA                                        |  |  |

| Package Input Current <sup>(3)</sup>              | ±50 mA                                                   |                                               |  |  |

| Package Dissipation at T <sub>A</sub> =           | 25°C                                                     | See (4)                                       |  |  |

| ESD Susceptibility                                | Human Body Model (5)                                     | 2500V                                         |  |  |

|                                                   | Machine Model <sup>(5)</sup>                             | 250V                                          |  |  |

| Soldering Temperature, Infrared, 10 sec. (6)      |                                                          |                                               |  |  |

| Storage Temperature -65°C to                      |                                                          |                                               |  |  |

| Soldering process must con                        | ply with TI's Reflow Temperature Profile specifications. | Refer to www.ti.com/packaging. <sup>(6)</sup> |  |  |

- (1) All voltages are measured with respect to GND = AGND = DGND = 0V, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is specified to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Range is not recommended.

- (3) When the input voltage at any pin exceeds the power supplies (that is, V<sub>IN</sub> < AGND, or V<sub>IN</sub> > V<sub>A</sub>), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two.

- (4) The absolute maximum junction temperature (T<sub>J</sub>max) for this device is 150°C. The maximum allowable power dissipation is dictated by T<sub>J</sub>max, the junction-to-ambient thermal resistance (θ<sub>JA</sub>), and the ambient temperature, (T<sub>A</sub>), and can be calculated using the formula P<sub>D</sub>MAX = (T<sub>J</sub>max T<sub>A</sub>)/θ<sub>JA</sub>. In the 64-pin TQFP, θ<sub>JA</sub> is 50°C/W, so P<sub>D</sub>MAX = 2 Watts at 25°C and 800 mW at the maximum operating ambient temperature of 85°C. Note that the power consumption of this device under normal operation will typically be about 400 mW (360 typical power consumption + 30 mW TTL output loading). The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Obviously, such conditions should always be avoided.

- (5) Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through 0Ω.

- (6) Reflow Reflow temperature profiles are different for lead-free and non-lead-free packages.

# Operating Ratings<sup>(1)(2)</sup>

| <u> </u>                                          |                                    |

|---------------------------------------------------|------------------------------------|

| Operating Temperature                             | -40°C ≤ T <sub>A</sub> ≤ +85°C     |

| Supply Voltage (V <sub>A</sub> , V <sub>D</sub> ) | +3.0V to +3.6V                     |

| Output Driver Supply (V <sub>DR</sub> )           | +2.4V to V <sub>D</sub>            |

| CLK, PD, OEA, OEB                                 | -0.05V to (V <sub>D</sub> + 0.05V) |

| Analog Input Pins                                 | 0V to 2.6V                         |

| V <sub>CM</sub>                                   | 0.5V to 2.0V                       |

| AGND-DGND                                         | ≤100mV                             |

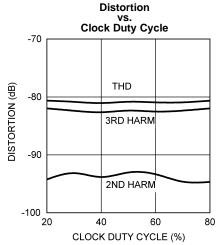

| Clock Duty Cycle (DCS On)                         | 20% to 80%                         |

| Clock Duty Cycle (DCS Off)                        | 40% to 60%                         |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is specified to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Range is not recommended.

- (2) All voltages are measured with respect to GND = AGND = DGND = 0V, unless otherwise specified.

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

# Converter Electrical Characteristics (1)(2)(3)

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V,  $V_A = V_D = +3.3V$ ,  $V_{DR} = +2.5V$ , PD = 0V, External  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 10$  MHz,  $C_L = 15$  pF/pin, Duty Cycle Stabilizer On, parallel output mode. **Boldface limits apply for T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>:** all other limits T<sub>J</sub> = 25°C

| Symbol                                  | Parameter                                            |                                                  |            |       |           | Units<br>(Limits) |

|-----------------------------------------|------------------------------------------------------|--------------------------------------------------|------------|-------|-----------|-------------------|

| STATIC C                                | CONVERTER CHARACTERISTICS                            |                                                  |            | 1     |           |                   |

|                                         | Resolution with No Missing Codes                     |                                                  |            |       | 10        | Bits (min)        |

| INL                                     | Integral Non Linearity <sup>(5)</sup>                |                                                  |            | ±0.25 | ±1        | LSB (max)         |

| DNL                                     | Differential Non Linearity                           |                                                  |            | ±0.16 | ±0.65     | LSB (max)         |

| PGE                                     | Positive Gain Error                                  |                                                  |            | ±0.1  | ±3.3      | %FS (max)         |

| NGE                                     | Negative Gain Error                                  |                                                  |            | ±0.2  | ±3.5      | %FS (max)         |

| TC GE                                   | Gain Error Tempco                                    | -40°C ≤ T <sub>A</sub> ≤ +85°C                   |            | 10    |           | ppm/°C            |

| V <sub>OFF</sub>                        | Offset Error (V <sub>IN</sub> + = V <sub>IN</sub> -) |                                                  | 0.1        | ±0.85 | %FS (max) |                   |

| TC V <sub>OFF</sub>                     | Offset Error Tempco                                  | $-40$ °C $\leq T_A \leq +85$ °C                  |            | 6     |           | ppm/°C            |

|                                         | Under Range Output Code                              |                                                  |            | 0     | 0         |                   |

|                                         | Over Range Output Code                               | 1023                                             | 1023       |       |           |                   |

| REFEREN                                 | NCE AND ANALOG INPUT CHARACTERIS                     | STICS                                            |            |       |           |                   |

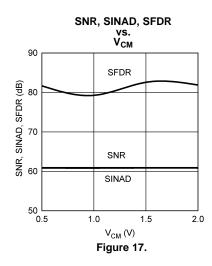

| V                                       | Common Made Innut Valtage                            |                                                  |            | 4.5   | 0.5       | V (min)           |

| $V_{CM}$                                | Common Mode Input Voltage                            |                                                  |            | 1.5   | 2.0       | V (max)           |

| V <sub>RM</sub> A,<br>V <sub>RM</sub> B | Reference Output Voltage                             | Output load = 1 mA                               |            | 1.5   |           | V                 |

| 0                                       | V Land Caracitana (and min to CND)                   | V 05.V/I- 0.7.V                                  | (CLK LOW)  | 8     |           | pF                |

| C <sub>IN</sub>                         | V <sub>IN</sub> Input Capacitance (each pin to GND)  | $V_{IN} = 2.5 \text{ Vdc} + 0.7 \text{ V}_{rms}$ | (CLK HIGH) | 7     |           | pF                |

| \ /                                     | Fitamal Deference Valteres (6)                       |                                                  |            | 4.00  | 0.8       | V (min)           |

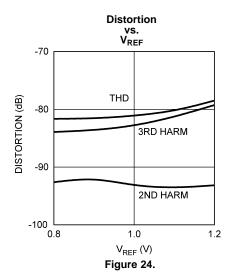

| $V_{REF}$                               | External Reference Voltage (6)                       |                                                  |            | 1.00  | 1.2       | V (max)           |

|                                         | Reference Input Resistance                           |                                                  |            | 1     |           | MΩ (min)          |

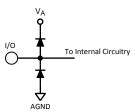

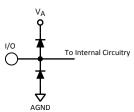

(1) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 3 under the Absolute Maximum Ratings. However, errors in the A/D conversion can occur if the input goes above V<sub>A</sub> or below GND by more than 100 mV. As an example, if V<sub>A</sub> is +3.3V, the full-scale input voltage must be ≤+3.4V to ensure accurate conversions.

- (2) To ensure accuracy, it is required that |V<sub>A</sub>-V<sub>D</sub>| ≤ 100 mV and separate bypass capacitors are used at each power supply pin.

- (3) With the test condition for  $V_{REF} = +1.0V$  ( $2V_{P-P}$  differential input), the 10-bit LSB is 1.95 mV.

- (4) Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms at the time of characterization. The typical specifications are not ensured.

- (5) Integral Non Linearity is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive and negative full-scale.

- (6) Optimum performance will be obtained by keeping the reference input in the 0.8V to 1.2V range. The LM4051CIM3-ADJ (SOT-23 package) is recommended for external reference applications.

# Converter Electrical Characteristics (continued)(1)(2)(3)

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V,  $V_A = V_D = +3.3V$ ,  $V_{DR} = +2.5V$ , PD = 0V, External  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 10$  MHz,  $C_L = 15$  pF/pin, Duty Cycle Stabilizer On, parallel output mode. **Boldface limits apply for T**<sub>J</sub> = **T**<sub>MIN</sub> **to T**<sub>MAX</sub>: all other limits T<sub>J</sub> = 25°C

| Symbol                                     | Parameter                      | Conditions                                               | Typical (4) | Limits<br>(4) | Units<br>(Limits) |

|--------------------------------------------|--------------------------------|----------------------------------------------------------|-------------|---------------|-------------------|

| DYNAMIC                                    | CONVERTER CHARACTERISTICS      | ,                                                        |             |               | i.                |

| FPBW                                       | Full Power Bandwidth           | 0 dBFS Input, Output at −3 dB                            | 250         |               | MHz               |

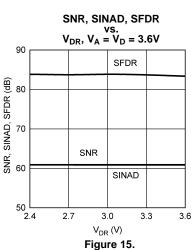

|                                            |                                | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$     | 61          |               | dBc               |

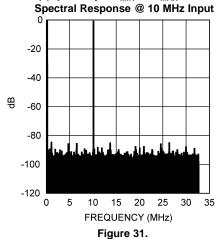

| SNR                                        | Signal-to-Noise Ratio          | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$    | 61          | 60            | dBc (min)         |

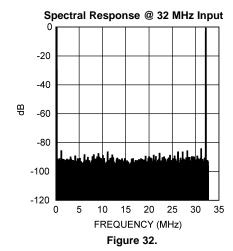

|                                            |                                | $f_{IN} = 32.5 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$  | 60.9        | 59.5          | dBc (min)         |

|                                            |                                | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$     | 60.9        |               | dBc               |

| SINAD                                      | Signal-to-Noise and Distortion | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$    | 60.9        | 59.8          | dBc (min)         |

| DYNAMIC FPBW SNR SINAD ENOB THD H2 H3 SFDR |                                | $f_{IN} = 32.5 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$  | 60.8        | 59            | dBc (min)         |

|                                            |                                | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$     | 9.8         |               | Bits              |

| ENOB                                       | Effective Number of Bits       | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$    | 9.8         | 9.64          | Bits (min)        |

|                                            |                                | $f_{IN} = 32.5 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$  | 9.8         | 9.5           | Bits (min)        |

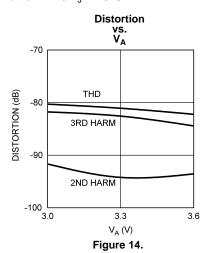

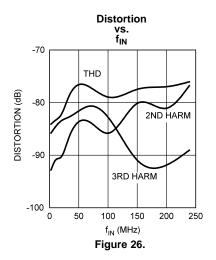

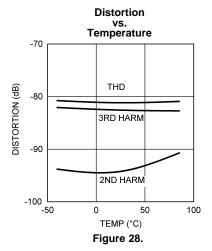

|                                            |                                | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$     | -84         |               | dBc               |

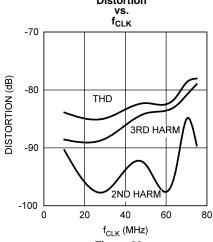

| THD                                        | Total Harmonic Distortion      | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$    | -83         | -75           | dBc (min)         |

|                                            |                                | $f_{IN} = 32.5 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$  | -81         | -73.5         | dBc (min)         |

|                                            |                                | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$     | -93         |               | dBc               |

| H2                                         | Second Harmonic Distortion     | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$    | -92         | -79           | dBc (min)         |

| SNR SINAD ENOB THD H2 H3 SFDR              |                                | $f_{IN} = 32.5 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$  | -92         | -77.6         | dBc (min)         |

|                                            |                                | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$     | -89         |               | dBc               |

| H3                                         | Third Harmonic Distortion      | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$    | -89         | -77           | dBc (min)         |

|                                            |                                | $f_{IN} = 32.5 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$  | -82         | -74           | dBc (min)         |

|                                            |                                | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$     | 86          |               | dBc               |

| SFDR                                       | Spurious Free Dynamic Range    | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$    | 85          | 77            | dBc (min)         |

|                                            |                                | $f_{IN} = 32.5 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$  | 82          | 74            | dBc (min)         |

| IMD                                        | Intermodulation Distortion     | $f_{\text{IN}}$ = 9.6 MHz and 10.2 MHz, each = -7.0 dBFS | -66         |               | dBFS              |

| INTER-CI                                   | HANNEL CHARACTERISTICS         |                                                          |             |               |                   |

|                                            | Channel—Channel Offset Match   |                                                          | ±0.3        |               | %FS               |

|                                            | Channel—Channel Gain Match     |                                                          | ±4          |               | %FS               |

|                                            | Crosstalk                      | 10 MHz Tested, Channel;<br>32.5 MHz Other Channel        | 90          |               | dB                |

(1) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 3 under the Absolute Maximum Ratings. However, errors in the A/D conversion can occur if the input goes above V<sub>A</sub> or below GND by more than 100 mV. As an example, if V<sub>A</sub> is +3.3V, the full-scale input voltage must be ≤+3.4V to ensure accurate conversions.

- (2) To ensure accuracy, it is required that |V<sub>A</sub>-V<sub>D</sub>| ≤ 100 mV and separate bypass capacitors are used at each power supply pin.

- 3) With the test condition for  $V_{REF} = +1.0V$  ( $2V_{P-P}$  differential input), the 10-bit LSB is 1.95 mV.

- (4) Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms at the time of characterization. The typical specifications are not ensured.

# DC and Logic Electrical Characteristics (1)(2)(3)

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V,  $V_A = V_D = +3.3V$ ,  $V_{DR} = +2.5V$ , PD = 0V, External  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 10$  MHz,  $C_L = 15$  pF/pin, Duty Cycle Stabilizer On, parallel output mode. **Boldface limits apply for T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>:** all other limits T<sub>J</sub> = 25°C

| Symbol              | Parameter                           | Condit                                                          | ions                                                 | Typical    | Limits<br>(4)  | Units<br>(Limits) |

|---------------------|-------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|------------|----------------|-------------------|

| CLK, PD,            | OEA, OEB DIGITAL INPUT CHARACTE     | RISTICS                                                         |                                                      |            | l.             | 1                 |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage           | $V_D = 3.6V$                                                    |                                                      |            | 2.0            | V (min)           |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage           | V <sub>D</sub> = 3.0V                                           |                                                      |            | 1.0            | V (max)           |

| I <sub>IN(1)</sub>  | Logical "1" Input Current           | V <sub>IN</sub> = 3.3V                                          | 10                                                   |            | μA             |                   |

| I <sub>IN(0)</sub>  | Logical "0" Input Current           | V <sub>IN</sub> = 0V                                            |                                                      | -10        |                | μΑ                |

| C <sub>IN</sub>     | Digital Input Capacitance           |                                                                 |                                                      | 5          |                | pF                |

| DA0-DA1             | 1, DB0-DB11 DIGITAL OUTPUT CHAR     | ACTERISTICS                                                     |                                                      |            |                |                   |

|                     | Lacial (42) Output Valtage          | 0.5 4                                                           | V <sub>DR</sub> = 2.5V                               |            | 2.3            | V (min)           |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage          | $I_{OUT} = -0.5 \text{ mA}$                                     | $V_{DR} = 3V$                                        |            | 2.7            | V (min)           |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage          | $I_{OUT} = 1.6 \text{ mA}, V_{DR} = 3^{\circ}$                  |                                                      | 0.4        | V (max)        |                   |

| _                   | TDI CTATE Output Course             | V <sub>OUT</sub> = 2.5V or 3.3V                                 |                                                      | 100        |                | nA                |

| l <sub>OZ</sub>     | TRI-STATE Output Current            | V <sub>OUT</sub> = 0V                                           | -100                                                 |            | nA             |                   |

| +I <sub>SC</sub>    | Output Short Circuit Source Current | V <sub>OUT</sub> = 0V                                           | -20                                                  |            | mA             |                   |

| -I <sub>SC</sub>    | Output Short Circuit Sink Current   | $V_{OUT} = V_{DR}$                                              | 20                                                   |            | mA             |                   |

| C <sub>OUT</sub>    | Digital Output Capacitance          |                                                                 |                                                      | 5          |                | pF                |

| POWER S             | SUPPLY CHARACTERISTICS              |                                                                 |                                                      |            |                |                   |

| I <sub>A</sub>      | Analog Supply Current               | PD Pin = DGND, V <sub>REF</sub> :<br>PD Pin = V <sub>D</sub>    | = V <sub>A</sub>                                     | 93.7<br>12 | 111            | mA (max)<br>mA    |

| I <sub>D</sub>      | Digital Supply Current              | PD Pin = DGND<br>PD Pin = V <sub>D</sub> , f <sub>CLK</sub> = 0 |                                                      | 18.5<br>0  | 20.5           | mA (max)<br>mA    |

| I <sub>DR</sub>     | Digital Output Supply Current       | PD Pin = DGND, $C_L = 1$<br>PD Pin = $V_D$ , $f_{CLK} = 0$      | PD Pin = DGND, C <sub>L</sub> = 10 pF <sup>(5)</sup> |            |                | mA<br>mA          |

|                     | Total Power Consumption             | PD Pin = DGND, $C_L = 1$<br>PD Pin = $V_D$                      | 370<br>36                                            | 434        | mW (max)<br>mW |                   |

| PSRR1               | Power Supply Rejection Ratio        | Rejection of Full-Scale V <sub>A</sub> =3.0V vs. 3.6V           | Error with                                           | 58         |                | dB                |

(1) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 3 under the Absolute Maximum Ratings. However, errors in the A/D conversion can occur if the input goes above V<sub>A</sub> or below GND by more than 100 mV. As an example, if V<sub>A</sub> is +3.3V, the full-scale input voltage must be ≤+3.4V to ensure accurate conversions.

- (2) To ensure accuracy, it is required that |V<sub>A</sub>−V<sub>D</sub>| ≤ 100 mV and separate bypass capacitors are used at each power supply pin.

- (3) With the test condition for  $V_{REF} = +1.0V$  ( $2V_{P-P}$  differential input), the 10-bit LSB is 1.95 mV.

- (4) Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms at the time of characterization. The typical specifications are not ensured.

- (5) I<sub>DR</sub> is the current consumed by the switching of the output drivers and is primarily determined by load capacitance on the output pins, the supply voltage, V<sub>DR</sub>, and the rate at which the outputs are switching (which is signal dependent). I<sub>DR</sub>=V<sub>DR</sub>(C<sub>0</sub> x f<sub>0</sub> + C<sub>1</sub> x f<sub>1</sub> +....C<sub>9</sub> x f<sub>9</sub>) where V<sub>DR</sub> is the output driver power supply voltage, C<sub>n</sub> is total capacitance on the output pin, and f<sub>n</sub> is the average frequency at which that pin is toggling.

- (6) Excludes I<sub>DR</sub>. See Note 5.

# AC Electrical Characteristics (1)(2)(3)(4)

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V,  $V_A = V_D = +3.3V$ ,  $V_{DR} = +2.5V$ , PD = 0V, External  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 10$  MHz,  $C_L = 15$  pF/pin, Duty Cycle Stabilizer On, parallel output mode. Boldface limits apply for  $T_J = T_{MIN}$  to  $T_{MAX}$ : all other limits  $T_J = 25^{\circ}C$

| Symbol                          | Parameter                            | Conditions                                                                                      | Typical (5) | Limits<br>(5) | Units<br>(Limits) |

|---------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------|-------------|---------------|-------------------|

| f <sub>CLK</sub> <sup>1</sup>   | Maximum Clock Frequency              |                                                                                                 |             | 65            | MHz (min)         |

| f <sub>CLK</sub> <sup>2</sup>   | Minimum Clock Frequency              |                                                                                                 | 15          |               | MHz               |

| t <sub>CH</sub>                 | Clock High Time                      | Duty Cycle Stabilizer On                                                                        | 7.7         | 3             | ns (min)          |

| $t_{CL}$                        | Clock Low Time                       | Duty Cycle Stabilizer On                                                                        | 7.7         | 3             | ns (min)          |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Times            | Duty Cycle Stabilizer On                                                                        | 2           | 4             | ns (max)          |

| t <sub>CH</sub>                 | Clock High Time                      | Duty Cycle Stabilizer Off                                                                       | 7.7         | 6.2           | ns (min)          |

| t <sub>CL</sub>                 | Clock Low Time                       | Duty Cycle Stabilizer Off                                                                       | 7.7         | 6.2           | ns (min)          |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Times            | Duty Cycle Stabilizer Off                                                                       | 2           |               | ns (max)          |

| t <sub>CONV</sub>               | Conversion Latency                   | Parallel mode                                                                                   |             | 7             | Clock Cycles      |

| 4                               | Data Output Delay after Rising Clock | Devellel weeds                                                                                  | F 40        | 3.5           | ns (max)          |

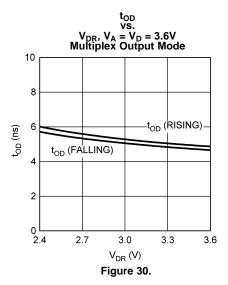

| t <sub>OD</sub>                 | Edge                                 | Parallel mode                                                                                   | 5.42        | 8             | ns (max)          |

| t <sub>CONV</sub>               | Conversion Latency                   | Multiplex mode, Channel A                                                                       |             | 7.5           | Clock Cycles      |

| t <sub>CONV</sub>               | Conversion Latency                   | Multiplex mode, Channel B                                                                       |             | 8             | Clock Cycles      |

| 4                               | Data Output Dalau after Clask Edge   | Multiplande                                                                                     | F. F.4      | 3.5           | ns (min)          |

| t <sub>OD</sub>                 | Data Output Delay after Clock Edge   | Multiplex mode                                                                                  | 5.54        | 8             | ns (max)          |

| t <sub>SKEW</sub>               | ABb to Data Skew                     |                                                                                                 | ±0.5        |               | ns (max)          |

| t <sub>AD</sub>                 | Aperture Delay                       |                                                                                                 | 2           |               | ns                |

| $t_{AJ}$                        | Aperture Jitter                      |                                                                                                 | 1.2         |               | ps rms            |

| t <sub>DIS</sub>                | Data outputs into Hi-Z Mode          |                                                                                                 | 10          |               | ns                |

| $t_{\text{EN}}$                 | Data Outputs Active after Hi-Z Mode  |                                                                                                 | 10          |               | ns                |

| t <sub>PD</sub>                 | Power Down Mode Exit Cycle           | 1.0 μF on pins 4, 14; 0.1 μF on pins 5,6,12,13; 10 μF between pins 5, 6 and between pins 12, 13 | 1           |               | μs                |

(1) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 3 under the Absolute Maximum Ratings. However, errors in the A/D conversion can occur if the input goes above V<sub>A</sub> or below GND by more than 100 mV. As an example, if V<sub>A</sub> is +3.3V, the full-scale input voltage must be ≤+3.4V to ensure accurate conversions.

- To ensure accuracy, it is required that  $|V_A V_D| \le 100$  mV and separate bypass capacitors are used at each power supply pin.

- With the test condition for  $V_{REF} = +1.0V$  ( $2V_{P-P}$  differential input), the 10-bit LSB is 1.95 mV.

- Timing specifications are tested at TTL logic levels,  $V_{IL} = 0.4V$  for a falling edge and  $V_{IH} = 2.4V$  for a rising edge. Typical figures are at  $T_A = 25$ °C, and represent most likely parametric norms at the time of characterization. The typical specifications are not ensured.

### **Specification Definitions**

**APERTURE DELAY** is the time after the rising edge of the clock to when the input signal is acquired or held for conversion.

**APERTURE JITTER (APERTURE UNCERTAINTY)** is the variation in aperture delay from sample to sample. Aperture jitter manifests itself as noise in the output.

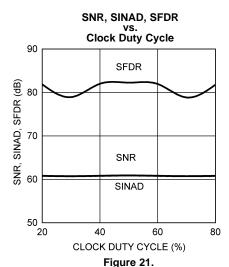

**CLOCK DUTY CYCLE** is the ratio of the time during one cycle that a repetitive digital waveform is high to the total time of one period. The specification here refers to the ADC clock input signal.

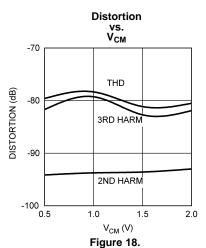

**COMMON MODE VOLTAGE (V<sub>CM</sub>)** is the common d.c. voltage applied to both input terminals of the ADC.

**CONVERSION LATENCY** is the number of clock cycles between initiation of conversion and when that data is presented to the output driver stage. Data for any given sample is available at the output pins the Pipeline Delay plus the Output Delay after the sample is taken. New data is available at every clock cycle, but the data lags the conversion by the pipeline delay.

CROSSTALK is coupling of energy from one channel into the other channel.

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

**EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion or SINAD. ENOB is defined as (SINAD - 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

**FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

GAIN ERROR is the deviation from the ideal slope of the transfer function. It can be calculated as:

Gain Error = Positive Full Scale Error - Negative Full Scale Error (1)

Gain Error can also be separated into Positive Gain Error and Negative Gain Error, which are:

PGE = Positive Full Scale Error - Offset Error (2)

NGE = Offset Error - Negative Full Scale Error (3)

**GAIN ERROR MATCHING** is the difference in gain errors between the two converters divided by the average gain of the converters.

**INTEGRAL NON LINEARITY (INL)** is a measure of the deviation of each individual code from a line drawn from negative full scale (½ LSB below the first code transition) through positive full scale (½ LSB above the last code transition). The deviation of any given code from this straight line is measured from the center of that code value.

**INTERMODULATION DISTORTION (IMD)** is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to the ADC input at the same time. It is defined as the ratio of the power in the intermodulation products to the total power in the original frequencies. IMD is usually expressed in dBFS.

**LSB (LEAST SIGNIFICANT BIT)** is the bit that has the smallest value or weight of all bits. This value is  $V_{FS}/2^n$ , where " $V_{FS}$ " is the full scale input voltage and "n" is the ADC resolution in bits.

**MISSING CODES** are those output codes that will never appear at the ADC outputs. The ADC10DL065 is ensured not to have any missing codes.

MSB (MOST SIGNIFICANT BIT) is the bit that has the largest value or weight. Its value is one half of full scale.

**NEGATIVE FULL SCALE ERROR** is the difference between the actual first code transition and its ideal value of ½ LSB above negative full scale.

**OFFSET ERROR** is the difference between the two input voltages  $[(V_{IN}+) - (V_{IN-})]$  required to cause a transition from code 2047 to 2048.

**OUTPUT DELAY** is the time delay after the rising edge of the clock before the data update is presented at the output pins.

**OVER RANGE RECOVERY TIME** is the time required after  $V_{IN}$  goes from a specified voltage out of the normal input range to a specified voltage within the normal input range and the converter makes a conversion with its rated accuracy.

PIPELINE DELAY (LATENCY) See CONVERSION LATENCY.

**POSITIVE FULL SCALE ERROR** is the difference between the actual last code transition and its ideal value of 1½ LSB below positive full scale.

**POWER SUPPLY REJECTION RATIO (PSRR)** is a measure of how well the ADC rejects a change in the power supply voltage. For the ADC10DL065, PSRR is the ratio of the change in Full-Scale Error that results from a change in the d.c. power supply voltage, expressed in dB.

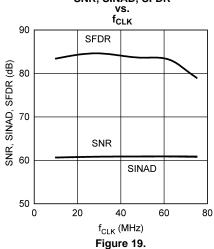

**SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sampling frequency, not including harmonics or d.c.

**SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD)** Is the ratio, expressed in dB, of the rms value of the input signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c.

**SPURIOUS FREE DYNAMIC RANGE (SFDR)** is the difference, expressed in dB, between the rms values of the input signal and the peak spurious signal, where a spurious signal is any signal present in the output spectrum that is not present at the input.

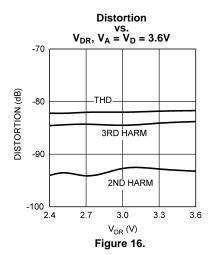

**TOTAL HARMONIC DISTORTION (THD)** is the ratio, expressed in dB, of the rms total of the first nine harmonic levels at the output to the level of the fundamental at the output. THD is calculated as

THD =

$$20 \times \log \sqrt{\frac{f_2^2 + \dots + f_{10}^2}{f_1^2}}$$

(4)

where  $f_1$  is the RMS power of the fundamental (output) frequency and  $f_2$  through  $f_{10}$  are the RMS power of the first 9 harmonic frequencies in the output spectrum.

**SECOND HARMONIC DISTORTION (2ND HARM)** is the difference expressed in dB, between the RMS power in the input frequency at the output and the power in its 2nd harmonic level at the output.

**THIRD HARMONIC DISTORTION (3RD HARM)** is the difference, expressed in dB, between the RMS power in the input frequency at the output and the power in its 3rd harmonic level at the output.

2

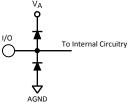

# **Timing Diagram**

Figure 1. Output Timing

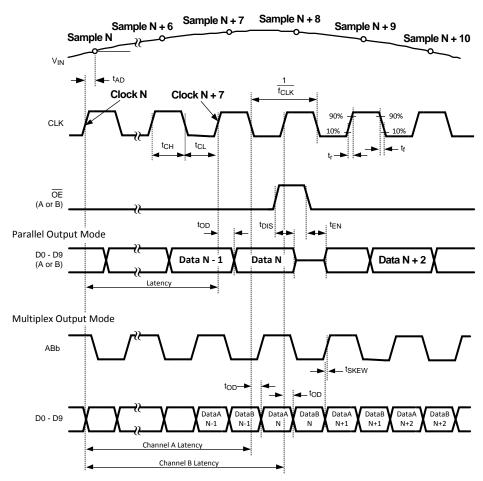

### **Transfer Characteristic**

Figure 2. Transfer Characteristic

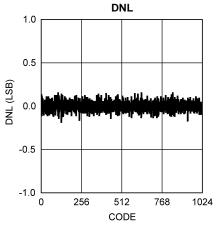

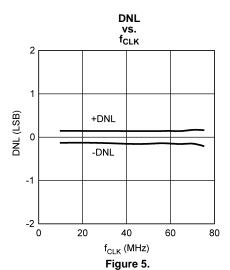

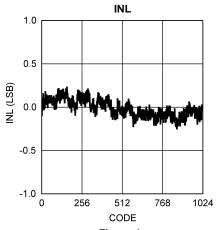

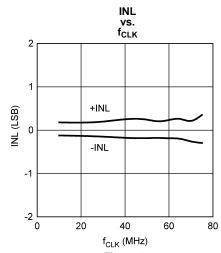

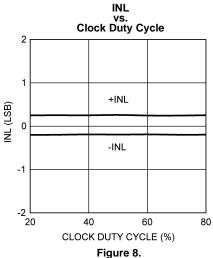

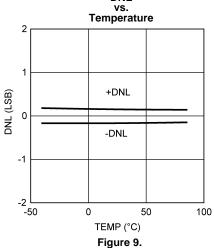

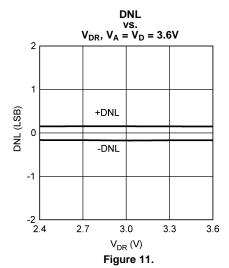

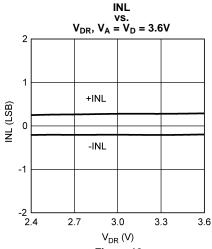

# Typical Performance Characteristics DNL, INL

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V,  $V_A = V_D = +3.3V$ ,  $V_{DR} = +2.5V$ , PD = 0V,  $V_{REF} = +1.0V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 0$ ,  $C_L = 15$  pF/pin, Duty Cycle Stabilizer On, parallel output mode. **Boldface limits apply for T**<sub>J</sub> = **T**<sub>MIN</sub> **to T**<sub>MAX</sub>: all other limits T<sub>J</sub> = 25°C

2 +DNL DNL (LSB) -DNL -1 -2 └ 20 60 80 40 CLOCK DUTY CYCLE (%)

Figure 7.

DNL

vs. Clock Duty Cycle

Figure 4.

Figure 6.

# Typical Performance Characteristics DNL, INL (continued)