# Low Power, 8-Bit, Dual 500 MSPS A/D Converter

Check for Samples: ADC08DL502

## **FEATURES**

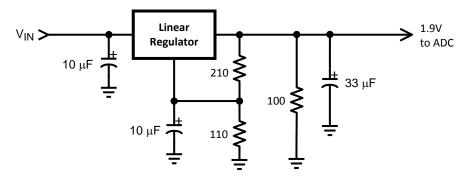

- Single +1.9V ±0.1V Operation

- Duty Cycle Corrected Sample Clock

### **KEY SPECIFICATIONS**

Resolution: 8 Bits

• Max Conversion Rate: 500 MSPS

Code Error Rate: 10<sup>-18</sup> (typ)

ENOB @ 125 MHz Input: 7.5 Bits (typ)

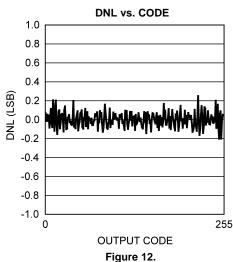

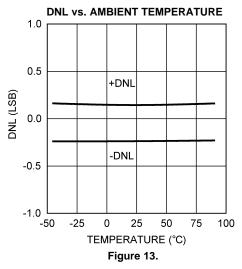

DNL: ±0.15 LSB (typ)

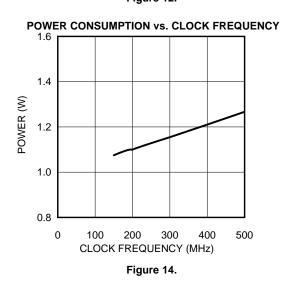

Power Consumption

- Operating in 1:2 Demux Output: 1.25W (typ)

- Power Down Mode: 3.3 mW (typ)

### **APPLICATIONS**

- Satellite Modems

- Digital Oscilloscopes

- Direct RF Down Conversion

- Communications Systems

- Test Instrumentation

## **DESCRIPTION**

The ADC08DL502 is a dual, low power, high performance, CMOS analog-to-digital converter. The ADC08DL502 digitizes signals to 8 bits of resolution at sample rates up to 500 MSPS. Consuming a typical 1.2 Watts in demultiplex mode at 500 MSPS from a single 1.9 Volt supply, this device is ensured to have no missing codes over the full operating temperature range. The unique folding interpolating architecture, the fully differential comparator design, the innovative design of the internal sample-and-hold amplifier and the calibration schemes enable a very flat response of all dynamic parameters beyond Nyquist, producing a high 7.5 Effective Number of Bits (ENOB) with a 125 MHz input signal and a 500 MHz sample rate while providing a 10<sup>-18</sup> Code Error Rate (C.E.R.)

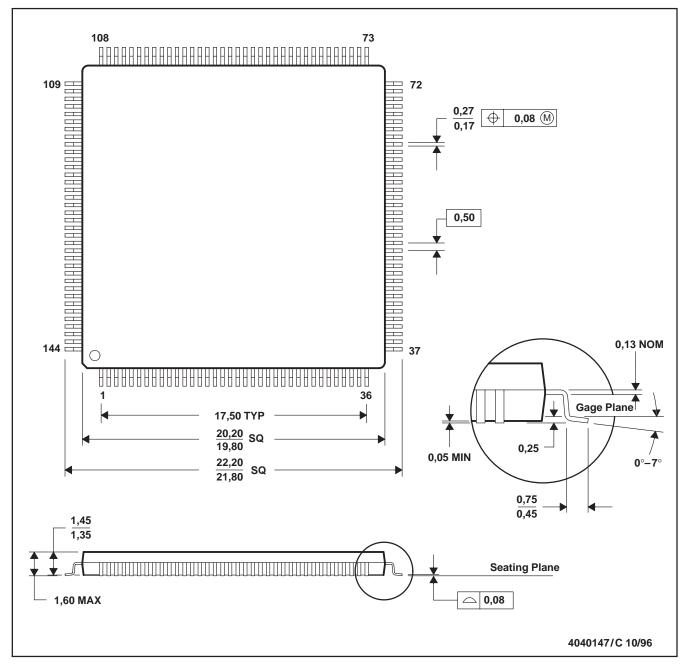

The converter typically consumes 3.3 mW in the Power Down Mode and is available in a lead-free 144-lead LQFP and operates over the modified Industrial (-40°C  $\leq$  T<sub>A</sub>  $\leq$  +70°C) temperature range.

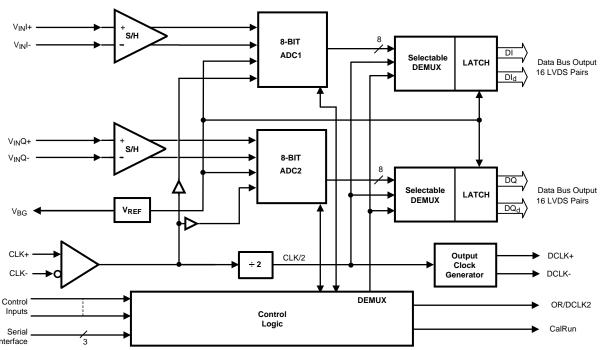

## **Block Diagram**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

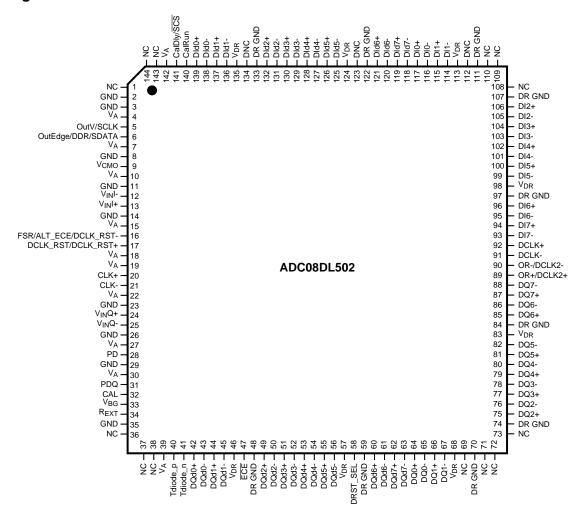

## **Pin Configuration**

## **Table 1. PIN DESCRIPTIONS AND EQUIVALENT CIRCUITS**

| Pin No. | Symbol                    | Equivalent Circuit                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | OutV / SCLK               | V <sub>A</sub> 50k                                                                                                                                                                                                                                                            | Output Voltage Amplitude and Serial Interface Clock. Tie this pin high for normal differential DCLK and data amplitude. Ground this pin for a reduced differential output amplitude and reduced power consumption. When the extended control mode is enabled, this pin functions as the SCLK input which clocks in the serial data. For OutV functionality, see (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 31      | PDQ                       | GND                                                                                                                                                                                                                                                                           | A logic high on the PDQ pin puts only the "Q" ADC into the Power Down mode. For PDQ functionality, see (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6       | OutEdge / DDR /<br>SDATA  | SDATA VA  SOR  SOR  SOR  SOR  SOR  SOR  SOR  VA  SOR  SOR  VA  SOR  SOR  VA  SOR  VA  SOR  VA  SOR  VA  SOR  SOR  SOR  SOR  SOR  SOR  SOR  SO | DCLK Edge Select, Double Data Rate Enable and Serial Data Input. This input sets the output edge of DCLK+ at which the output data transitions. When this pin is floating or connected to 1/2 the supply voltage, DDR clocking is enabled. When the extended control mode is enabled, this pin functions as the SDATA input. For OutEdge functionality, see (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

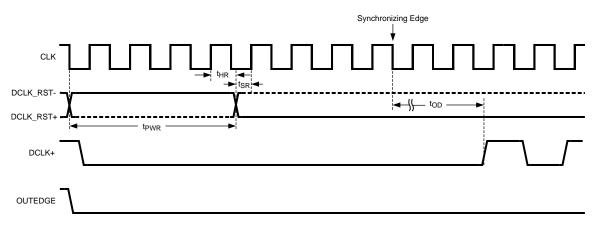

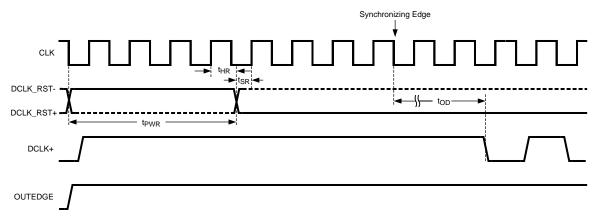

| 17      | DCLK_RST /<br>DCLK_RST+   | V <sub>A</sub>                                                                                                                                                                                                                                                                | DCLK Reset. When single-ended DCLK_RST is selected by floating or setting pin 58 logic high, a positive pulse on this pin is used to reset and synchronize the DCLK outputs of multiple converters. When differential DCLK_RST is selected by setting pin 58 logic low, this pin receives the positive polarity of a differential pulse signal used to reset and synchronize the DCLK outputs of multiple converters. For DCLK_RST, DCLK_RST+ functionality, see (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28      | PD                        |                                                                                                                                                                                                                                                                               | Power Down Pins. A logic high on the PD pin puts the entire device into the Power Down Mode. For PD functionality, see (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

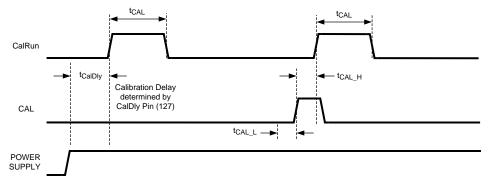

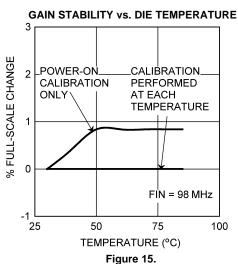

| 32      | CAL                       | <b>o</b><br>GND                                                                                                                                                                                                                                                               | Calibration Cycle Initiate. A minimum $t_{CAL\_L}$ input clock cycles logic low followed by a minimum of $t_{CAL\_H}$ input clock cycles high on this pin initiates the calibration sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16      | FSR/ALT_ECE/DC<br>LK_RST- | 50k 200k 50k 8 pF                                                                                                                                                                                                                                                             | Full Scale Range Select, Alternate Extended Control Enable and DCLK_RST This pin has three functions. It can conditionally control the ADC full-scale voltage, enable the extended control mode, or become the negative polarity signal of a differential pair in differential DCLK_RST mode. If pin 58 and pin 47 are floating or at logic high, this pin can be used to set the full-scale-range or can be used as an alternate extended control enable pin . When used as the FSR pin, a logic low on this pin sets the full-scale differential input range to a reduced $V_{\rm IN}$ input level. A logic high on this pin sets the full-scale differential input range to a higher $V_{\rm IN}$ input level. To enable the extended control mode, whereby the serial interface and control registers are employed, allow this pin to float or connect it to a voltage equal to $V_{\rm A}/2$ . Note that pin 47 overrides the extended control enable of this pin. When pin 58 is held at logic low, this pin acts as the DCLK_RST- pin. When in differential DCLK_RST mode, there is no pin-controlled FSR and the full-scale-range is defaulted to the higher $V_{\rm IN}$ input level. For FSR, ALT_ECE, DCLK_RST- functionality, see $^{(1)}$ |

<sup>(1)</sup> This pin/bit functionality is not tested in production test; performance is tested in the specified/default mode only.

| Pin No.              | Symbol                                   | Equivalent Circuit                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 141                  | CalDly / SCS                             | VA<br>SOIK<br>SOIK<br>GND                    | Calibration Delay and Serial Interface Chip Select. With a logic high or low on pin 16, and a logic high on pin 47, this pin functions as Calibration Delay and sets the number of input clock cycles after power up before calibration begins With pin 16 floating, and a logic low on pin 47, this pin acts as the enable pin for the serial interface input and the CalDly value becomes "0" (short delay with no provision for a long powerup calibration delay). For CalDly functionality, see (2) |

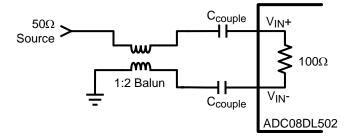

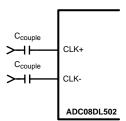

| 20<br>21             | CLK+<br>CLK-                             | AGND 50k VBIAS                               | LVDS Clock input pins for the ADC. The differential clock signal must be a.c. coupled to these pins. The input signal is sampled on the falling edge of CLK+.                                                                                                                                                                                                                                                                                                                                           |

|                      | V <sub>IN</sub> I+<br>V <sub>IN</sub> I- | VA                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

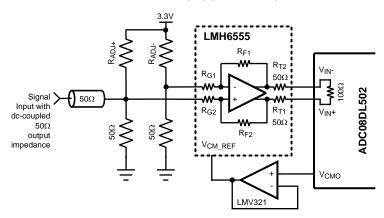

| 13<br>12<br>24<br>25 | V <sub>IN</sub> Q+<br>V <sub>IN</sub> Q- | AGND VCMO  150 Control from VCMO  AGND  AGND | Analog signal inputs to the ADC. The differential full-scale input range of this input is programmable using the FSR pin 16 in normal mode and the Input Full-Scale Voltage Adjust register in the extended control mode. Refer to the $V_{\rm IN}$ specification in the Converter Electrical Characteristics for the full-scale input range in the normal mode.                                                                                                                                        |

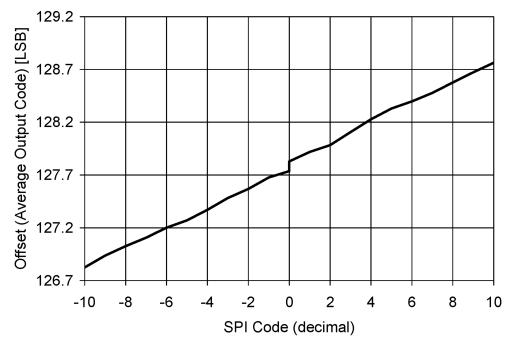

| 9                    | V <sub>СМО</sub>                         | VCMO VCMO Enable AC Coupling                 | Common Mode Voltage. This pin is the common mode output in d.c. coupling mode and also serves as the a.c. coupling mode select pin. When d.c. coupling is used, the voltage output at this pin is required to be the common mode input voltage at $V_{\text{IN}}+$ and $V_{\text{IN}}-$ when d.c. coupling is used. This pin should be grounded when a.c. coupling is used at the analog inputs. This pin is capable of sourcing or sinking 100 $\mu\text{A}.$                                          |

(2) This pin/bit functionality is not tested in production test; performance is tested in the specified/default mode only.

| Pin No.  | Symbol               | Equivalent Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33       | $V_{BG}$             | V <sub>A</sub>     | Bandgap output voltage capable of 100 $\mu$ A source/sink and can drive a load up to 80 pF. For $V_{BG}$ functionality, see $^{(3)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 140      | CalRun               | GND                | Calibration Running indication. This pin is at a logic high when calibration is running. For CalRun functionality, see <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 34       | R <sub>EXT</sub>     | VA<br>GND          | External bias resistor connection. Nominal value is 4.7 k $\Omega$ (±0.1%) to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 40<br>41 | Tdiode_P<br>Tdiode_N | Tdiode_P O         | Temperature Diode Positive (Anode) and Negative (Cathode). These pins may be used for die temperature measurements, however no specified accuracy is implied or enured. Noise coupling from adjacent output data signals has been shown to affect temperature measurements using this feature. For Tdiode_P, Tdiode_N functionality, see (3)                                                                                                                                                                                                                                                                                                                                                               |

| 47       | ECE                  | FS (PIN 14)        | Extended Control Enable. This pin always enables and disables Extended Control Enable. When this pin is set logic high, the extended control mode is inactive and all control of the device must be through control pins only . When it is set logic low, the extended control mode is active. This pin overrides the Extended Control Enable signal set using pin 16.                                                                                                                                                                                                                                                                                                                                     |

| 58       | DRST_SEL             | VA<br>S10k         | DCLK_RST select. This pin selects whether the DCLK is reset using a single-ended or differential signal. When this pin is floating or logic high, the DCLK_RST operation is single-ended and pin 16 functions as FSR/ALT_ECE. When this pin is logic low, the DCLK_RST operation becomes differential with functionality on pin 17 (DCLK_RST+) and pin 16 (DCLK_RST-). When in differential DCLK_RST mode, there is no pin-controlled FSR and the full-scale-range is defaulted to the higher V <sub>IN</sub> input level. When pin 47 is set logic low, the extended control mode is active and the Full-Scale Voltage Adjust registers can be programmed. For DRST_SEL functionality, see <sup>(3)</sup> |

(3) This pin/bit functionality is not tested in production test; performance is tested in the specified/default mode only.

| Pin No.                                                                                                                                                                                      | Symbol                                                                                                                                                                                                                                        | Equivalent Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                              | DI7- / DQ7-                                                                                                                                                                                                                                   | Equivalent Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 93 / 88<br>94 / 87<br>95 / 86<br>96 / 85<br>99 / 82<br>100 / 81<br>101 / 80<br>102 / 79<br>103 / 78<br>104 / 77<br>105 / 76<br>106 / 75<br>114 / 67<br>115 / 66<br>116 / 65<br>117 / 64      | DI7- / DQ7- DI7+ / DQ7+ DI6- / DQ6- DI6- / DQ6- DI5- / DQ5- DI5+ / DQ5- DI4- / DQ4- DI4+ / DQ4- DI3- / DQ3- DI3+ / DQ3- DI2- / DQ2- DI2+ / DQ2- DI1- / DQ1- DI1+ / DQ1+ DI0- / DQ0- DI0+ / DQ0-                                               |                    | I and Q channel LVDS Data Outputs that are not delayed in the output demultiplexer. Compared with the Dld and DQd outputs, these outputs represent the later time samples. These outputs should always be terminated with a 100 $\Omega$ differential resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 118 / 63<br>119 / 62<br>120 / 61<br>121 / 60<br>125 / 56<br>126 / 55<br>127 / 54<br>128 / 53<br>129 / 52<br>130 / 51<br>131 / 50<br>132 / 49<br>136 / 45<br>137 / 44<br>138 / 43<br>139 / 42 | DId7- / DQd7- DId7+ / DQd7+ DId6- / DQd6- DId6+ / DQd6+ DId5- / DQd5- DId5+ / DQd5+ DId4- / DQd4- DId4- / DQd4+ DId3- / DQd3- DId3+ / DQd3- DId3+ / DQd2- DId2- / DQd2- DId2+ / DQd1- DId1- / DQd1- DId1+ / DQd1+ DId0- / DQd0- DId0+ / DQd0+ |                    | I and Q channel LVDS Data Outputs that are delayed by one CLK cycle in the output demultiplexer. Compared with the DI/DQ outputs, these outputs represent the earlier time sample. These outputs should be terminated with a 100 $\Omega$ differential resistor when enabled. In non-demultiplexed mode, these outputs are disabled and are high impedance when enabled. When disabled, these outputs must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 89<br>90                                                                                                                                                                                     | OR+/DCLK2+<br>OR-/DCLK2-                                                                                                                                                                                                                      | DR GND             | Out Of Range output. A differential high at these pins indicates that the differential input is out of range (outside the range ±V <sub>IN</sub> /2 as programmed by the FSR pin in non-extended control mode or the Input Full-Scale Voltage Adjust register setting in the extended control mode). DCLK2 is the exact mirror of DCLK and should output the same signal at the same rate. For DCLK2+/- functionality, see (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 92<br>91                                                                                                                                                                                     | DCLK+<br>DCLK-                                                                                                                                                                                                                                |                    | Data Clock. Differential Clock outputs used to latch the output data. Delayed and non-delayed data outputs are supplied synchronous to this signal. In 1:2 demultiplexed mode, this signal is at 1/2 the input clock rate in SDR mode and at 1/4 the input clock rate in the DDR mode. By default, the DCLK outputs are not active during the termination resistor trim section of the calibration cycle. If a system requires DCLK to run continuously during a calibration cycle, the termination resistor trim portion of the cycle can be disabled by setting the Resistor Trim Disable (RTD) bit to logic high in the Extended Configuration Register (address 9h). This disables all subsequent termination resistor trims after the initial trim which occurs during the power on calibration. Therefore, this output is not recommended as a system clock unless the resistor trim is disabled. When the device is in the non-demultiplexed mode, DCLK can only be in DDR mode and the signal is at 1/2 the input clock rate. |

| 4, 7, 10, 15,<br>18, 19, 22,<br>27, 30, 39,<br>142                                                                                                                                           | V <sub>A</sub>                                                                                                                                                                                                                                | NONE               | Analog power supply pins. Bypass these pins to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 46, 57, 68,<br>83, 98, 113,<br>124, 135                                                                                                                                                      | $V_{DR}$                                                                                                                                                                                                                                      | NONE               | Output Driver power supply pins. Bypass these pins to DR GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

(4) This pin/bit functionality is not tested in production test; performance is tested in the specified/default mode only.

| Pin No.                                                            | Symbol | Equivalent Circuit | Description                                                                                                               |

|--------------------------------------------------------------------|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| 2, 3, 8, 11,<br>14, 23, 26,<br>29, 35                              | GND    | NONE               | Ground return for V <sub>A</sub> .                                                                                        |

| 48, 59, 70,<br>74, 84, 97,<br>107, 111,<br>122, 133                | DR GND | NONE               | Ground return for $V_{DR}$ .                                                                                              |

| 1, 36, 37,<br>38, 69, 71,<br>72, 73, 108,<br>109, 110,<br>143, 144 | NC     | NONE               | Not Connected. These pins are not bonded and may be left floating or connected to any potential.                          |

| 112, 123,<br>134                                                   | DNC    | NONE               | Do Not Connect. These pins are used for internal purposes and should not be connected, i.e. left floating. Do not ground. |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Copyright © 2012–2013, Texas Instruments Incorporated

# Absolute Maximum Ratings (1)(2)(3)

| Supply Voltage (V <sub>A</sub> , V <sub>DR</sub> )                           |                      | 2.2V                              |

|------------------------------------------------------------------------------|----------------------|-----------------------------------|

| Supply Difference $V_{DR} - V_A$                                             |                      | 0V to 100 mV                      |

| Voltage on Any Input Pin (Except V <sub>IN</sub> +, V <sub>IN</sub> -)       |                      | -0.15V to (V <sub>A</sub> +0.15V) |

| Voltage on V <sub>IN</sub> +, V <sub>IN</sub> -<br>(Maintaining Common Mode) |                      | -0.15 to 2.5V                     |

| Ground Difference<br> GND - DR GND                                           |                      | 0V to 100 mV                      |

| Input Current at Any Pin (4)                                                 |                      | ±25 mA                            |

| Package Input Current <sup>(4)</sup>                                         |                      | ±50 mA                            |

| Junction Temperature                                                         |                      | T <sub>J</sub> ≤ 145°C            |

| ESD Susceptibility <sup>(5)</sup>                                            | Human Body Model     | 2500V                             |

|                                                                              | Machine Model        | 250V                              |

|                                                                              | Charged Device Model | 1000V                             |

| Storage Temperature                                                          |                      | −65°C to +150°C                   |

- (1) All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. There is no specification of operation at the Absolute Maximum Ratings. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) When the input voltage at any pin exceeds the power supply limits (that is, less than GND or greater than V<sub>A</sub>), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two. This limit is not placed upon the power, ground and digital output pins.

- (5) Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through ZERO Ohms. Charged device model simulates a pin slowly acquiring charge (such as from a device sliding down the feeder in an automated assembler) then rapidly being discharged.

# Operating Ratings (1)(2)

| Ambient Temperature Range <sup>(3)</sup>                                     | -40°C ≤ T <sub>A</sub> ≤ +70°C                               |

|------------------------------------------------------------------------------|--------------------------------------------------------------|

| Supply Voltage (V <sub>A</sub> )                                             | +1.8V to +2.0V                                               |

| Driver Supply Voltage (V <sub>DR</sub> )                                     | +1.8V to V <sub>A</sub>                                      |

| Common Mode Input Voltage                                                    | V <sub>CMO</sub> ± 50 mV                                     |

| V <sub>IN</sub> +, V <sub>IN</sub> − Voltage Range (Maintaining Common Mode) | 0V to 2.15V (100% duty cycle)<br>0V to 2.5V (10% duty cycle) |

| Ground Difference ( GND - DR GND )                                           | 0V                                                           |

| CLK Pins Voltage Range                                                       | 0V to V <sub>A</sub>                                         |

| Differential CLK Amplitude                                                   | 0.4V <sub>P-P</sub> to 2.0V <sub>P-P</sub>                   |

| Common Mode Input Voltage                                                    | $V_{CMO}$ - 50mV < $V_{CMI}$ < $V_{CMO}$ + 50mV              |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. There is no specification of operation at the Absolute Maximum Ratings. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (2) All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.

- (3) The 4-layer standard JEDEC thermal test board or 4LJEDEC is 4"x3" in size. The board has two embedded copper layers which cover roughly the same size as the board. The copper thickness for the four layers, starting from the top one, is 2 oz., 1 oz., 1 oz., 2 oz. Detailed description of the board can be found in the JESD 51-7 standard.

## **Package Thermal Resistance**

| Package                                                                                                      | $\theta_{JA}$ | θ <sub>JC</sub> | psi <sub>JB</sub> |  |  |

|--------------------------------------------------------------------------------------------------------------|---------------|-----------------|-------------------|--|--|

| 144-Lead,<br>LQFP                                                                                            | 43.6°C / W    | 12.5°C / W      | 39.0°C / W        |  |  |

| Soldering process must comply with Reflow Temperature Profile specifications. Refer to www.tj.com/packaging. |               |                 |                   |  |  |

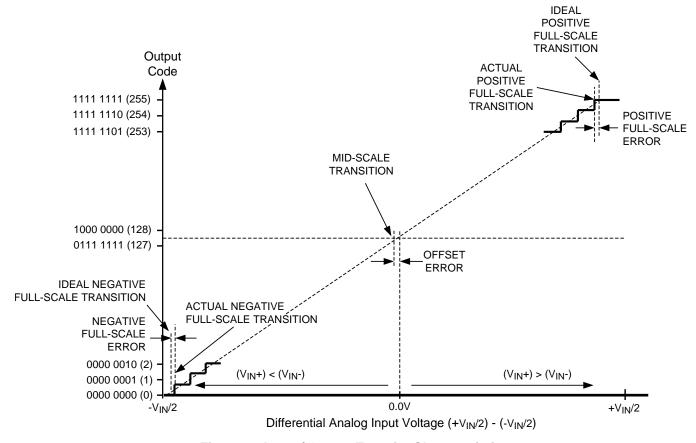

## **Static Converter Characteristics**

The following specifications apply after calibration for  $V_A = V_{DR} = 1.9V$ ; OutV = 1.9V;  $V_{IN}$  FSR (a.c. coupled) = differential 840  $mV_{P-P}$ ;  $C_L = 10$  pF; Differential, a.c. coupled Sine Wave Input Clock,  $f_{CLK} = 500$  MHz at 0.5  $V_{P-P}$  with 50% duty cycle;  $V_{BG} = 10$ Floating; Extended Control Mode default values; DDR 0° Mode; R<sub>EXT</sub> = 4700 Ω ±0.1%; 1:2 Output Demultiplex; Duty Cycle Stabilizer on. Boldface limits apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ . All other limits  $T_A = 25^{\circ}$ C, unless otherwise noted. (1) (2)

| Symbol                | Parameter                                    | Conditions                                                            | Typ <sup>(3)</sup> | Lim   | Units<br>(Limits) |

|-----------------------|----------------------------------------------|-----------------------------------------------------------------------|--------------------|-------|-------------------|

|                       | Resolution with No Missing Codes             |                                                                       |                    | 8     | Bits              |

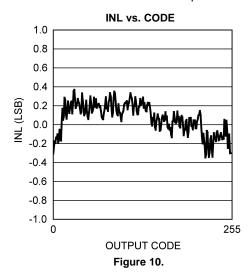

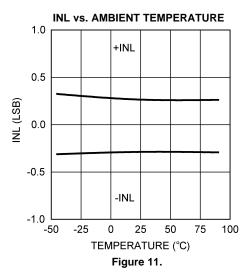

| INL                   | Integral Non-Linearity<br>(Best fit)         | DC Coupled, 1 MHz Sine Wave<br>Overanged, SDR, Non-ECM, FSR<br>= High | ±0.3               | ±0.9  | LSB (max)         |

| DNL                   | Differential Non-Linearity                   | DC Coupled, 1 MHz Sine Wave<br>Overanged, SDR, Non-ECM, FSR<br>= High | ±0.15              | ±0.75 | LSB (max)         |

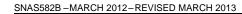

| V <sub>OFF</sub>      | Offset Error                                 | SDR, Non-ECM Mode                                                     | -0.45              |       | LSB               |

| V <sub>OFF</sub> _ADJ | Input Offset Adjustment Range <sup>(4)</sup> | Extended Control Mode                                                 | ±45                |       | mV                |

| PFSE                  | Positive Full-Scale Error                    | See (5)                                                               |                    | ±25   | mV (max)          |

| NFSE                  | Negative Full-Scale Error                    | See (5)                                                               |                    | ±25   | mV (max)          |

|                       | Out of Range Output Code                     | (V <sub>IN</sub> +) - (V <sub>IN</sub> -) > + Full Scale              |                    | 255   |                   |

|                       |                                              | (V <sub>IN</sub> +) - (V <sub>IN</sub> -) < - Full Scale              |                    | 0     |                   |

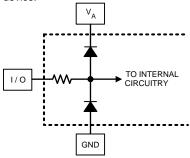

The analog inputs are protected as shown below. Input voltage magnitudes beyond the Absolute Maximum Ratings may damage this device.

- To ensure accuracy, it is required that  $V_A$  and  $V_{DR}$  be well bypassed. Each supply pin must be decoupled with separate bypass capacitors. Additionally, achieving rated performance requires that the backside exposed pad be well grounded.

- Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms. Test limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

- Only the end points of the range, not the full sweep, are tested in production test.

- Calculation of Full-Scale Error for this device assumes that the actual reference voltage is exactly its nominal value. Full-Scale Error for this device, therefore, is a combination of Full-Scale Error and Reference Voltage Error. For relationship between Gain Error and Full-Scale Error, see Specification Definitions for Gain Error.

Product Folder Links: ADC08DL502

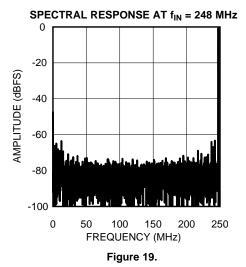

## **Dynamic Converter Characteristics**

| Symbol   | Parameter                            | Conditions                            | Typ <sup>(1)</sup> | Lim  | Units<br>(Limits) |

|----------|--------------------------------------|---------------------------------------|--------------------|------|-------------------|

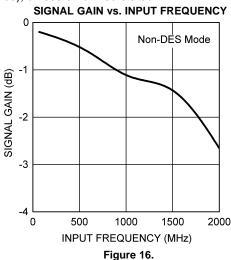

| FPBW     | Full Power Bandwidth                 |                                       | 2.0                |      | GHz               |

|          | Gain Flatness                        | d.c. to 248 MHz                       | ±0.8               |      | dBFS              |

|          |                                      | d.c. to 500 MHz                       | ±1.0               |      | dBFS              |

| C.E.R.   | Code Error Rate                      |                                       | 10 <sup>-18</sup>  |      | Error/<br>Sample  |

| NPR      | Noise Power Ratio                    | See (2)                               | 38.4               |      | dB                |

| IMD3     | 3rd order Intermodulation Distortion |                                       | 71.4               |      | dBFS              |

|          |                                      | f <sub>IN2</sub> =121.47 MHz @ −7dBFS | @ -7dBFS           | dBc  |                   |

|          | Noise Floor                          | See (3)                               | -135.4             |      | dBm/Hz            |

|          |                                      |                                       | -133.3             |      | dBFS/Hz           |

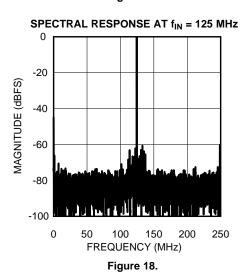

| ENOB     | Effective Number of Bits             | A <sub>IN</sub> = 125 MHz @ -0.5dBFS  | 7.5                | 6.8  | bits              |

|          |                                      | A <sub>IN</sub> = 248 MHz @ -0.5dBFS  | 7.6                |      | bits (min)        |

| SINAD    | Signal-to-Noise Plus Distortion      | A <sub>IN</sub> = 125 MHz @ -0.5dBFS  | 46.9               | 42.4 | dB                |

|          | Ratio                                | A <sub>IN</sub> = 248 MHz @ -0.5dBFS  | 47.6               |      | dB (min)          |

| SNR      | Signal-to-Noise Ratio                | A <sub>IN</sub> = 125 MHz @ -0.5dBFS  | 47.8               | 43.5 | dB                |

|          |                                      | A <sub>IN</sub> = 248 MHz @ -0.5dBFS  | 48.5               |      | dB (min)          |

| THD      | Total Harmonic Distortion            | A <sub>IN</sub> = 125 MHz @ -0.5dBFS  | -54.2              | -49  | dB                |

|          |                                      | A <sub>IN</sub> = 248 MHz @ -0.5dBFS  | -54.8              |      | dB (max)          |

| 2nd Harm | Second Harmonic Distortion           | A <sub>IN</sub> = 125 MHz @ -0.5dBFS  | -60                |      | dB                |

|          |                                      | A <sub>IN</sub> = 248 MHz @ -0.5dBFS  | -59                |      | dB                |

| 3rd Harm | Third Harmonic Distortion            | A <sub>IN</sub> = 125 MHz @ -0.5dBFS  | -68                |      | dB                |

|          |                                      | A <sub>IN</sub> = 248 MHz @ -0.5dBFS  | -60                |      | dB                |

| SFDR     | Spurious-Free dynamic Range          | A <sub>IN</sub> = 125 MHz @ -0.5dBFS  | 58.5               | 49   | dB                |

|          |                                      | A <sub>IN</sub> = 248 MHz @ -0.5dBFS  | 59.1               |      | dB (min)          |

<sup>(1)</sup> Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms. Test limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

<sup>(2)</sup> The NPR was measured using an Agilent N6030A Arbitrary Waveform Generator (ARB) to generate the input signal. The "noise" portion of the signal was created by tones spaced at 500 kHz and the "notch" was a 12.5 MHz absence of tones centered at 175 MHz.

<sup>(3)</sup> For the case where the inputs are shorted or terminted with 50Ω, the LSB of the ADC never transitions because the Noise Floor is limited by quantization noise, not thermal noise. Therefore, the Noise Floor was measured with a low-level wideband input from 10 MHz to 30 MHz; the noise floor was measured in the band from 126 MHz to 175 MHz.

## **Analog Input/Output and Reference Characteristics**

| Symbol              | Parameter                                            | Conditions                                                                            | Typ <sup>(1)</sup> | Lim | Units<br>(Limits) |

|---------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------|-----|-------------------|

| Analog Input        | ts                                                   |                                                                                       |                    |     | •                 |

| V <sub>IN_FSR</sub> | Analog Differential Input Full Scale                 | Non-Extended Control Mode <sup>(2)</sup>                                              |                    |     |                   |

|                     | Range                                                | FSR Pin High, SDR                                                                     | 840                | 900 | $mV_{P-P}$        |

|                     |                                                      | FSR Pin Low, SDR                                                                      | 650                |     | $mV_{P-P}$        |

|                     |                                                      | Extended Control Mode <sup>(3)</sup>                                                  |                    |     | •                 |

|                     |                                                      | FS_ADJ(15:7) = 1111 1111 1 <b>b</b>                                                   | 840                |     | $mV_{P-P}$        |

|                     |                                                      | FS_ADJ(15:7) = 1000 0000 0 <b>b</b> (default)                                         | 700                |     | mV <sub>P-P</sub> |

|                     |                                                      | FS_ADJ(15:7) = 0000 0000 0 <b>b</b>                                                   | 560                |     | $mV_{P-P}$        |

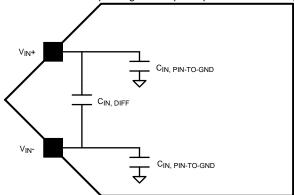

| C <sub>IN</sub>     | Analog Input Capacitance (4)(5)(6)                   | Differential                                                                          | 0.02               |     | pF                |

|                     |                                                      | Each input pin to ground                                                              | 1.6                |     | pF                |

| R <sub>IN</sub>     | Differential Input Resistance                        | Measured at D.C.                                                                      | 140                |     | Ω                 |

| Common Mo           | de Output                                            |                                                                                       |                    |     | •                 |

| V <sub>CMO</sub>    | Common Mode Output Voltage                           | $I_{CMO} = \pm 100 \mu A$                                                             | 1.26               | 0.9 | V (min)           |

|                     |                                                      |                                                                                       |                    | 1.6 | V (max)           |

| Bandgap Re          | ference                                              |                                                                                       |                    |     |                   |

| $V_{BG}$            | Bandgap Reference Output<br>Voltage                  | I <sub>BG</sub> = ±100 μA                                                             | 1.26               |     | V                 |

| TC_V <sub>BG</sub>  | Bandgap Reference Voltage<br>Temperature Coefficient | $T_A = -40^{\circ}\text{C to } +70^{\circ}\text{C},$ $I_{BG} = \pm 100 \ \mu\text{A}$ | 28                 |     | ppm/°C            |

| $C_{LOAD} V_{BG}$   | Maximum Bandgap Reference load Capacitance           |                                                                                       |                    | 80  | pF                |

- Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms. Test limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

This pin/bit functionality is not tested in production test; performance is tested in the specified/default mode only.

- Only the end points of the range, not the full sweep, are tested in production test.

- The analog and clock input capacitances are die capacitances only. Additional package capacitances of 0.65 pF differential and 0.95 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.

- This parameter is specified by design and is not tested in production.

- The differential and pin-to-ground input capacitances are lumped capacitance values from design; they are defined as shown below.

#### I-Channel to Q-Channel Characteristics

| Symbol | Parameter                                          | Conditions                                        | Typ <sup>(1)</sup> | Lim | Units<br>(Limits) |

|--------|----------------------------------------------------|---------------------------------------------------|--------------------|-----|-------------------|

|        | Offset Match                                       |                                                   | 1                  |     | LSB               |

|        | Positive Full-Scale Match                          | Zero offset selected in Control<br>Register       | 1                  |     | LSB               |

|        | Negative Full-Scale Match                          | Zero offset selected in Control<br>Register       | 1                  |     | LSB               |

|        | Phase Matching (I, Q)                              | f <sub>IN</sub> = 500 MHz                         | < 1                |     | Degree            |

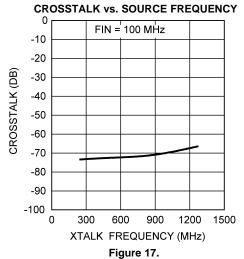

| X-TALK | Crosstalk from I (Aggressor) to Q (Victim) Channel | Aggressor = 467 MHz F.S.<br>Victim = 100 MHz F.S. | -65                |     | dB                |

|        | Crosstalk from Q (Aggressor) to I (Victim) Channel | Aggressor = 467 MHz F.S.<br>Victim = 100 MHz F.S. | -65                |     | dB                |

<sup>(1)</sup> Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms. Test limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

## **Sampling Clock Characteristics**

| Symbol              | Parameter                      | Conditions           | Typ <sup>(1)</sup> | Lim | Units<br>(Limits)      |

|---------------------|--------------------------------|----------------------|--------------------|-----|------------------------|

| V <sub>IN_CLK</sub> | Differential Clock Input Level | Sine Wave Clock      | 0.6                | 0.4 | V <sub>P-P</sub> (min) |

|                     |                                |                      |                    | 2.0 | V <sub>P-P</sub> (max) |

|                     |                                | Square Wave Clock    | 0.6                | 0.4 | V <sub>P-P</sub> (min) |

|                     |                                |                      |                    | 2.0 | V <sub>P-P</sub> (max) |

| R <sub>IN_CLK</sub> | Sampling Clock Input Impedance | Measured at D.C.     | 100                |     | Ω                      |

| C <sub>IN_CLK</sub> | Input Capacitance (2)(3)       | Differential         | 0.02               |     | pF                     |

|                     |                                | Each input to ground | 1.5                |     | pF                     |

| V <sub>OSI</sub>    | Input Offset Voltage           |                      | 1.2                |     | V                      |

Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms. Test limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

### **Digital Control and Output Pin Characteristics**

| Symbol              | Parameter                    | Conditions                           | Typ <sup>(1)</sup> | Lim                    | Units<br>(Limits) |

|---------------------|------------------------------|--------------------------------------|--------------------|------------------------|-------------------|

| Digital Cont        | trol Pins                    | ·                                    |                    |                        |                   |

| V <sub>IH</sub>     | Logic High Input Voltage (2) | PD,CAL, OutV, PDQ, ECEb,<br>DRST_SEL |                    | 0.69 x V <sub>A</sub>  | V (min)           |

|                     |                              | OUTEDGE, FSR, CalDly                 |                    | 0.815 x V <sub>A</sub> | V (min)           |

| V <sub>IL</sub>     | Logic Low Input Voltage (2)  | PD,CAL, OutV, PDQ, ECEb,<br>DRST_SEL |                    | 0.28 x V <sub>A</sub>  | V (max)           |

|                     |                              | OUTEDGE, FSR, CalDly                 |                    | 0.21 x V <sub>A</sub>  | V (max)           |

| C <sub>IN_DIG</sub> | Input Capacitance (3)(4)     | Each input to ground                 | 1.2                |                        | pF                |

| Digital Outp        | out Pins                     |                                      |                    | •                      | •                 |

<sup>(2)</sup> The analog and clock input capacitances are die capacitances only. Additional package capacitances of 0.65 pF differential and 0.95 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.

<sup>(3)</sup> This parameter is specified by design and is not tested in production.

<sup>(1)</sup> Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms. Test limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

<sup>(2)</sup> This parameter is specified by design and/or characterization and is not tested in production.

<sup>(3)</sup> This parameter is specified by design and is not tested in production.

<sup>(4)</sup> The digital control pin capacitances are die capacitances only. Additional package capacitance of 1.6 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.

## **Digital Control and Output Pin Characteristics (continued)**

| Symbol                | Parameter                                            | Conditions                                                                        | Typ <sup>(1)</sup>  | Lim | Units<br>(Limits)          |

|-----------------------|------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------|-----|----------------------------|

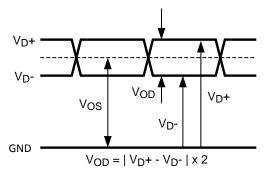

| V <sub>OD</sub>       | LVDS Differential Output Voltage                     | Measured differentially, OutV = $V_A$ , $V_{BG}$ = Floating <sup>(5)(6)</sup>     | 590                 | 400 | mV <sub>P-P</sub> (min)    |

|                       |                                                      |                                                                                   |                     | 850 | mV <sub>P-P</sub><br>(max) |

|                       |                                                      | Measured differentially, OutV = GND, V <sub>BG</sub> = Floating <sup>(5)(6)</sup> | 432                 |     | mV <sub>P-P</sub>          |

| ΔV <sub>O DIFF</sub>  | Change in LVDS Output Swing Between Logic Levels     |                                                                                   | ±1                  |     | mV                         |

| Vos                   | Output Offset Voltage                                | V <sub>BG</sub> = Floating                                                        | 0.8                 |     | V                          |

|                       |                                                      | $V_{BG} = V_A^{(5)(6)}$                                                           | 1.2                 |     | V                          |

| ΔV <sub>OS</sub>      | Output Offset Voltage Change<br>Between Logic Levels |                                                                                   | ±1                  |     | mV                         |

| I <sub>OS</sub>       | Output Short Circuit Current                         | Output+ & Output - connected to 0.8V                                              | ±4                  |     | mA                         |

| Z <sub>O</sub>        | Differential Output Impedance                        |                                                                                   | 100                 |     | Ω                          |

| V <sub>OH</sub>       | CalRun H level output                                | I <sub>OH</sub> = -400 μA <sup>(2)</sup>                                          | 1.65                |     | V                          |

| V <sub>OL</sub>       | CalRun L level output                                | I <sub>OH</sub> = 400 μA <sup>(2)</sup>                                           | 0.15                |     | V                          |

| Differential [        | OCLK Reset Pins (DCLK_RST) <sup>(7)</sup>            |                                                                                   | *                   |     | -                          |

| V <sub>CMI_DRST</sub> | DCLK_RST Common Mode Input<br>Voltage                |                                                                                   | 1.25                |     | V                          |

| V <sub>ID_DRST</sub>  | Differential DCLK_RST Input Voltage                  |                                                                                   | V <sub>IN_CLK</sub> |     | V <sub>P-P</sub>           |

| R <sub>IN_DRST</sub>  | Differential DCLK_RST Input<br>Resistance            |                                                                                   | 100                 |     | Ω                          |

Tying V<sub>BG</sub> to the supply rail will increase the output offset voltage (V<sub>OS</sub>) by 400 mV (typical), as shown in the V<sub>OS</sub> specification above. Tying  $V_{BG}$  to the supply rail will also affect the differential LVDS output voltage ( $V_{OD}$ ), causing it to increase by 40 mV (typical). This pin/bit functionality is not tested in production test; performance is tested in the specified/default mode only.

## **Power Supply Characteristics**

| Symbol          | Parameter                    | Conditions       | Тур <sup>(1)</sup> | Lim  | Units<br>(Limits) |  |

|-----------------|------------------------------|------------------|--------------------|------|-------------------|--|

| $I_A$           | Analog Supply Current        | 1:2 Demux Output |                    |      |                   |  |

|                 |                              | PD = Low         | 494                | 650  | mA (max)          |  |

|                 |                              | PD = High        | 1.7                |      | mA                |  |

| I <sub>DR</sub> | Output Driver Supply Current | 1:2 Demux Output |                    |      | ·                 |  |

|                 |                              | PD = Low         | 168                | 275  | mA (max)          |  |

|                 |                              | PD = High        | 0.054              |      | mA                |  |

| P <sub>C</sub>  | Power Consumption            | 1:2 Demux Output |                    |      | ·                 |  |

|                 |                              | PD = Low         | 1.25               | 1.61 | W (max)           |  |

|                 |                              | PD = High        | 3.3                |      | mW                |  |

<sup>(1)</sup> Typical figures are at  $T_A = 25$ °C, and represent most likely parametric norms. Test limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

Submit Documentation Feedback Copyright © 2012-2013, Texas Instruments Incorporated

<sup>(7)</sup> This feature functionality is not tested in production test; performance is tested in the specified/default mode only.

### **AC Electrical Characteristics**

| Symbol                 | Parameter                                                        | Conditions                                                                    | Typ <sup>(1)</sup> | Lim      | Units<br>(Limits)          |

|------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------|----------|----------------------------|

| Sampling C             | lock (CLK)                                                       |                                                                               |                    |          |                            |

| f <sub>CLK (max)</sub> | Maximum Sampling Clock Frequency                                 |                                                                               |                    | 500      | MHz                        |

| f <sub>CLK (min)</sub> | Minimum Sampling Clock Frequency                                 |                                                                               |                    | 200      | MHz                        |

|                        | Sampling Clock Duty Cycle                                        | 200 MHz ≤ f <sub>CLK</sub> ≤ 500 MHz <sup>(2)</sup>                           | 50                 | 20<br>80 | % (min)<br>% (max)         |

| t <sub>CL</sub>        | Sampling Clock Low Time                                          | See <sup>(3)</sup>                                                            | 1000               | 400      | ps (min)                   |

| t <sub>CH</sub>        | Sampling Clock High Time                                         | See (3)                                                                       | 1000               | 400      | ps (min)                   |

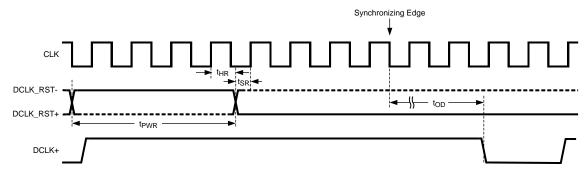

| DCLK_RST               | (4)                                                              |                                                                               |                    |          | ,                          |

| t <sub>SR</sub>        | Setup Time DCLK_RST±                                             | Differential DCLK_RST <sup>(2)</sup>                                          | 90                 |          | ps                         |

| t <sub>HR</sub>        | Hold Time DCLK_RST±                                              | Differential DCLK_RST <sup>(2)</sup>                                          | 30                 |          | ps                         |

| t <sub>PWR</sub>       | Pulse Width DCLK_RST±                                            | See <sup>(3)</sup>                                                            |                    | 4        | CLK±<br>Cycles<br>(min)    |

| Data Clock             | (DCLK)                                                           |                                                                               |                    |          |                            |

|                        | DCLK Duty Cycle                                                  | See (3)                                                                       | 50                 | 45       | % (min)                    |

|                        |                                                                  |                                                                               |                    | 55       | % (max)                    |

| t <sub>LHT</sub>       | Differential Low-to-High Transition Time                         | 10% to 90%                                                                    | 150                |          | ps                         |

| t <sub>HLT</sub>       | Differential High-to-Low Transition Time                         | 10% to 90%                                                                    | 150                |          | ps                         |

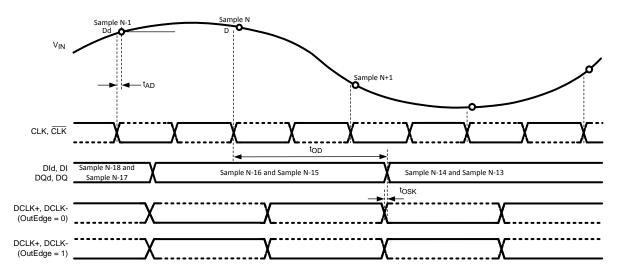

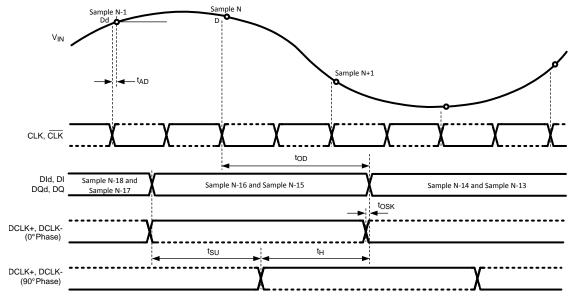

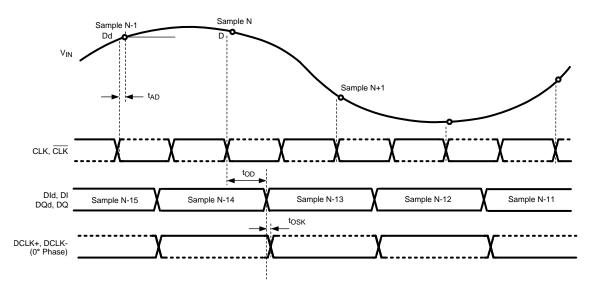

| tosk                   | DCLK-to-Data Output Skew                                         | 50% of DCLK transition to 50% of Data transition                              | ±50                |          | ps                         |

| t <sub>SU</sub>        | Data-to-DCLK Set-Up Time                                         | DDR Mode, 90° DCLK <sup>(3)</sup>                                             | 750                |          | ps                         |

| t <sub>H</sub>         | DCLK-to-Data Hold Time                                           | DDR Mode, 90° DCLK <sup>(3)</sup>                                             | 890                |          | ps                         |

| Data Input-t           | o-Output                                                         |                                                                               |                    |          |                            |

| t <sub>AD</sub>        | Sampling (Aperture) Delay                                        | Input CLK+ Fall to Acquisition of Data                                        | 1.6                |          | ns                         |

| $t_{AJ}$               | Aperture Jitter                                                  |                                                                               | 0.4                |          | ps (rms)                   |

| t <sub>OD</sub>        | Input Clock-to Data Output Delay (in addition to Pipeline Delay) | 50% of Input Clock transition to 50% of Data transition                       | 4.0                |          | ns                         |

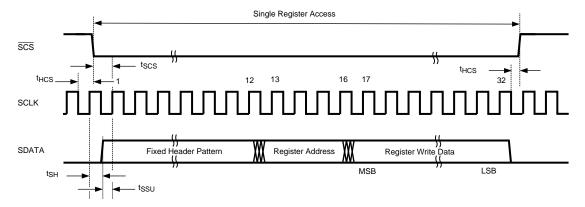

| t <sub>LAT</sub>       | Pipeline Delay (Latency) in 1:2<br>Demux Mode <sup>(3)(5)</sup>  | DI Outputs                                                                    |                    | 13       | Sampling                   |

|                        | Demux Mode (3) (5)                                               | Dld Outputs                                                                   |                    | 14       | Clock<br>Cycles            |