### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### **Customer Notification**

# **IE-V850ES-G1**

**In-Circuit Emulator**

**Operating Precautions**

Target device V850ES

Global Document No. U18079EE6V0IF00 (6th edition)

Document No. TPS-HE-B-3105 Date Published October 2004

#### **DISCLAIMER**

The related documents in this customer notification may include preliminary versions. However, preliminary versions may not have been marked as such.

The information in this customer notification is current as of its date of publication. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC PRODUCT(S). Not all PRODUCT(S) and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

No part of this customer notification may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this customer notification. NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC PRODUCT(S) listed in this customer notification or any other liability arising from the use of such PRODUCT(S).

No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others. Descriptions of circuits, software and other related information in this customer notification are provided for illustrative purposes of PRODUCT(S) operation and/or application examples only. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

While wherever feasible, NEC endeavors to enhance the quality, reliability and safe operation of PRODUCT(S) the customer agree and acknowledge that the possibility of defects and/or erroneous thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects and/or errors in PRODUCT(S) the customer must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

The customer agrees to indemnify NEC against and hold NEC harmless from any and all consequences of any and all claims, suits, actions or demands asserted against NEC made by a third party for damages caused by one or more of the items listed in the enclosed table of content of this customer notification for PRODUCT(S) supplied after the date of publication.

#### Applicable Law:

The law of the Federal Republic of Germany applies to all information provided by NEC to the Customer under this Operating Precaution document without the possibility of recourse to the Conflicts Law or the law of 5th July 1989 relating to the UN Convention on Contracts for the International Sale of Goods (the Vienna CISG agreement).

Düsseldorf is the court of jurisdiction for all legal disputes arising directly or indirectly from this information. NEC is also entitled to make a claim against the Customer at his general court of jurisdiction.

If the supplied goods/information are subject to German, European and/or North American export controls, the Customer shall comply with the relevant export control regulations in the event that the goods are exported and/or re-exported. If deliveries are exported without payment of duty at the request of the Customer, the Customer accepts liability for any subsequent customs administration claims with respect to NEC.

**Notes**: (1) **NEC** as used in this statement means NEC Corporation and also includes its direct or indirect owned or controlled subsidiaries.

(2) **PRODUCT(S)** means NEC sericonductor products (*NEC semiconductor products* means any semiconductor product developed or manufactured by or for NEC) and/or TOOLS TOOLS means hadware and/or software development tools of NEC semiconductor products developed, manufactured and supplied by NEC and/or hadware and/or software development tools supplied by NEC but developed and/or manufactured by independent 3<sup>rd</sup> Party vendors worldwide as their own product or on contract from NEC)

### Operating Precautions for IE-V850ES-G1<sup>TM</sup>

| (A) | Product Version                      | . 5 |

|-----|--------------------------------------|-----|

| (B) | Table of Operating Precautions       | . 6 |

| (C) | Description of Operating Precautions | . 8 |

| (D) | Valid Specification                  | 25  |

| (E) | Revision History                     | 26  |

#### (A) Product Version

#### 1. Product Code: IE-V850ES-G1

| Control Code <sup>Note</sup> | EVA Chip                     | Usable Exec Version                |

|------------------------------|------------------------------|------------------------------------|

| А                            | D703191AR DS4.5-3V or higher | EX85032.DLL version 5.41 or higher |

| В                            | D703191AR DS4.5-3V or higher | EX85032.DLL version 5.41 or higher |

| С                            | D703191AR DS4.5-3V or higher | EX85032.DLL version 5.41 or higher |

| D                            | D703191AR DS4.5-3V or higher | EX85032.DLL version 5.41 or higher |

| E                            | D703191AR DS4.5-3V or higher | EX85032.DLL version 5.41 or higher |

| F                            | D703191AR DS4.5-3V or higher | EX85032.DLL version 5.41 or higher |

**Note:** The control code is the digit from the left od a 10-digit control code that starts from E, e.g. EA9040009L means control code A.

In case of an version update you may find an additional label on the bottom of the emulator case where you can take the control code (update level) from.

Caution: In conjunction with the usable exec version a qualified device file (Dxxxxx.800) is additionally necessary for the corresponding device, which has to be emulated. Make sure that you use the appropriated version of the device file. Please refer to the documentation of the dedicated EM1-board.

### (B) Table of Operating Precautions

|                                         |                                                                         |                                                                        |        |   | IE-V850ES-G1 |        |       |   |  |

|-----------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------|--------|---|--------------|--------|-------|---|--|

| ı                                       | No.                                                                     | Outline Control code                                                   |        | Α | В            | O      | D/E   | F |  |

| nctions                                 | a-1                                                                     | Restriction on DMA transfer forcible termination                       |        |   | Х            | X      | Х     | X |  |

| CPU fu                                  | a-2                                                                     | Restriction on program execution and DMA transfer in internal RAM      |        |   | X            | X      | Х     | X |  |

| Restrictions dependent on CPU functions |                                                                         |                                                                        |        |   |              |        |       |   |  |

|                                         | b-1                                                                     | Restriction on operating frequ                                         | ency   | X | X            | X      | X     | 1 |  |

|                                         | b-2                                                                     | Restrictions on break timing when guard area is fetched                |        |   | X            | X      | X     | х |  |

|                                         | b-3                                                                     | ROM contents are rewritten if emulation ROM area is accessed for write |        |   | Х            | Х      | Х     | Х |  |

|                                         | b-4                                                                     | Restriction of SFR illegal break                                       |        |   | Х            | Х      | Х     | Х |  |

| tions                                   | b-5                                                                     | Restriction on programmable I/O space                                  |        |   | Х            | Х      | Х     | Х |  |

| on debug functions                      | b-6                                                                     | Break does not occur even if breakpoint is set                         |        |   | Х            | Х      | Х     | х |  |

|                                         | b-7                                                                     | Restriction related to access address during DMA trace                 |        | × | Х            | Х      | Х     | Х |  |

| Restrictions                            | b-8                                                                     | Restriction on DBPC and DBPSW access during a break                    |        | X | Х            | Х      | Х     | х |  |

| Re                                      | b-9 Restriction on DBTRAP instruction                                   |                                                                        | ıction | Х | Х            | Х      | Х     | Х |  |

|                                         | b-10                                                                    | Restriction on access data                                             |        | Х | Х            | Х      | Х     | Х |  |

|                                         | b-11                                                                    | 1 Restriction on SFR access during break                               |        |   | orted b      | y debu | ıgger |   |  |

|                                         | b-12                                                                    | Restriction on target operating                                        | Х      | 1 | 1            | 1      | 1     |   |  |

|                                         | b-13 Restriction on accessinf emulation ROM area and emulation RAM area |                                                                        |        | X | Х            | Х      | Х     | х |  |

**Remark:** ✓ : Not applicable ✗ : Applicable

|                                 |                                       |                                                                                                         |              |   | IE-V850ES-G1 |   |     |   |

|---------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|--------------|---|--------------|---|-----|---|

| I                               | No.                                   | Outline                                                                                                 | Control code | А | В            | С | D/E | F |

| ctions                          | b-14                                  | Restriction that the debugger hangs up depending on the software break setting upon PSC register access |              | Х | Х            | Х | Х   | х |

| ebug fur                        | b-15                                  | Restriction that the same bra tion is traced twice                                                      | nch instruc- | Х | Х            | × | X   | X |

| ns on de                        | b-16                                  | Restriction on 48-bit length mov instruction trace                                                      |              |   | Х            | х | Х   | Х |

| Restrictions on debug functions | b-17                                  | Restriction on illegal trace of consecutive sld instructions                                            |              | Х | Х            | Х | Х   | Х |

| <u> </u>                        | b-18 Restriction on pin mask function |                                                                                                         | X            | X | X            | X | X   |   |

|                                 | c-1                                   | Use of emulation memory                                                                                 |              | Х | Х            | Х | Х   | Х |

| ase                             | c-2 Pin handling                      |                                                                                                         | Х            | Х | Х            | Х | X   |   |

| Directions of use               | c-3                                   | Power saving                                                                                            |              | Х | Х            | Х | Х   | X |

| ction                           | c-4                                   | Pin control with target power OFF                                                                       |              | Х | Х            | Х | Х   | X |

| Dire                            | c-5                                   | Notes on trace data                                                                                     |              | Х | Х            | Х | Х   | Х |

|                                 | c-6 Notes on instruction cache        |                                                                                                         | Х            | Х | Х            | Х | Х   |   |

**Remark:**  $\checkmark$ : Not applicable  $\checkmark$ : Applicable

#### (C) Description of Operating Precautions

#### 1. Restrictions Dependent on CPU Functions

No. a-1 Restriction on DMA transfer forcible termination (Specification change notice)

#### Details

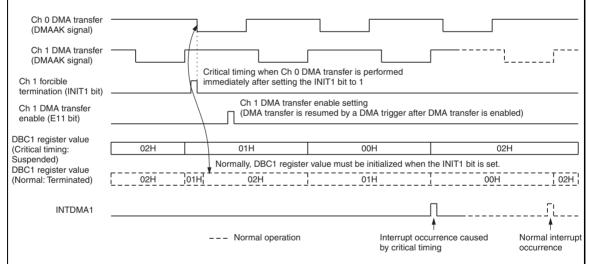

When terminating a DMA transfer by setting the corresponding INITn bit of the DCHCn register, the transfer may not be terminated, but just suspended, even though the INITn bit is set (1). As a result, when the DMA transfer of a channel that should have been terminated is resumed, the DMA transfer will terminate after an unexpected number of transfers are completed and a DMA transfer completion interrupt may occur. In addition, a DMA transfer of a channel n for which the INITn bit is set after forcible termination may be performed once again with the initialized value (n= 0 to 3).

The critical situation occurs if a DMA transfer is executed immediately after a forcible termination is set (by setting the INITn bit), refer to figure below.

The critical timing does not depend on the number of transfer channels, transfer type, transfer target, transfer mode, or trigger, and can occur with any combination of the above elements that can be set under the specifications. In addition, another channel may affect the occurrence of this critical timing.

Operation example: Both DMA channels, ch 0 and ch 1, are in single transfer mode, and ch 1 DMA transfer count is 3 (DBC1 register value = 02H).

The following registers are buffer register with a 2-stage FIFO configuration of master and slave:

- DMA source address register (DSAnH, DSAnL)

- DMA destination address register (DDAnH, DDAnL)

- DMA transfer count register (DBCn)

If these registers are overwritten during a DMA transfer, or in the DMA suspended status, the value is written to the master register, and reflected in the slave register when the DMA transfer of the overwritten channel is terminated.

The "initialization" in the figure above means that the contents of the master register are reflected in the slave register.

# No. a-1 Restriction on DMA transfer forcible termination (Specification change notice)

(cont.)

#### **Workaround**

The critical situation can be avoided by implementing any of the following procedures.

#### <1> Stop all transfers from DMA channels temporarily.

The following measure is effective if the program does not assume that the TCn bit of the DCHCn register is 1 except for the following workaround processing. (Since the TCn bit of the DCHCn register is cleared (0) when it is read, execution of the following procedure b) under <5> clears this bit.)

Procedure to avoid the critical timing:

- <1> Disable interrupts (DI state)

- <2> Read the DMA restart register (DRST) and transfer the ENn bit of each channel to a general purpose register (value A).

- <3> Write 00H to the DMA restart register (DRST) twice Note.

By executing twice Note, the DMA transfer is definitely stopped before proceeding to <4>.

- <4> Set (1) the INITn bit of the DCHCn register of the channel that should be terminated forcibly.

- <5> Perform the following operations for value A read in (2) to obtain value B.

- a) Clear (0) the bit of the channel that is not terminated forcibly.

- b) If the TCn and ENn bits of the channel that is not terminated forcibly are 1, clear (0) the bit of the channel.

- <6> Write value B in <5> to the DRST register.

- <7> Enable interrupts (El state)

**Note:** Execute three times if the transfer target (transfer source or transfer destination) is the internal RAM.

**Remarks: 1.** Be sure to execute <5> to prevent the ENn bit from being set illegally for channels that are terminated normally during the period of <2> and <3>

**2.** n = 0 to 3

### <2> Repeat setting the INITn bit until the forcible DMA transfer termination is correctly performed (n = 0 to 3)

Procedure to avoid the critical timing:

- <1> Copy the initial transfer count of the channel that should be terminated forcibly to a general-purpose register.

- <2> Set (1) the INITn bit of the DCHCn register of the channel that should be terminated forcibly.

- <3> Read the value of the DMA transfer count register (DBCn) of the channel that should be terminated forcibly and compare the value with the one copied in <1>. If the value do not match, repeat <2> and <3>.

**Remarks: 1.** When the DBCn register is read in procedure <3>, the remaining transfer count will be read if the DMA is stopped due to this bug. If the forcible DMA termination is performed correctly, the initial transfer count will be read.

2. Note that it may take some time for forcible termination to take effect if this workaround is implemented in an application in which DMA transfer other than for channels subject to forcible termination are frequently performed.

# No. a-2 Restriction on program execution and DMA transfer in internal RAM (Specification change notice)

#### Details

When a DMA transfer for the internal RAM and a bit manipulation instruction (SET1, CLR1, or NOT1) allocated in the internal RAM or a data access instruction for a misaligned address are executed simultaneously, the CPU may deadlock due to conflict between the internal bus operations. At this time, only a reset can be acknowledged, an NMI or an maskable interrupt cannot be acknowledged any more.

#### Unaffected cases

The critical situation does not occur if no instruction is executed in the internal RAM, or no DMA transfer is performed on the internal RAM.

#### Workaround

Implement any of the following workarounds.

- Do not perform a DMA transfer for the internal RAM when an instruction allocated in the internal RAM is being executed.

- Do not execute an instruction allocated in the internal RAM when a DMA transfer for the internal RAM is being performed.

#### 2. Restrictions on Debug Functions

### No. b-1 Restrictions on operating frequency (Technical limitation)

#### Details

The maximum operating frequency is 20 MHz.

#### Workaround

None. Use a frequency of 20 MHz or lower.

### No. b-2 Restrictions on break timing when guard area is fetched (Specification change notice)

#### **Details**

When program execution enters the guard area, one instruction in the guard area is executed and then a break occurs.

#### Workaround

None.

# No. b-3 ROM contents are rewritten if emulation ROM area is accessed for write (Specification change notice)

#### **Details**

An illegal break occurs if the emulation ROM area is accessed for write, and the data of ROM is rewritten.

#### **Workaround**

None.

### No. b-4 Restriction on SFR illegal break (Specification change notice)

#### <u>Details</u>

SFR illegal break is detected by "address condition + R/W attribute". However, a break occurs if an 8-bit SFR is written in half-word units (break does not occur if an 8-bit SFR is read in half-word units).

#### Workaround

# No. b-5 Restriction on programmable I/O space (Specification change notice)

#### <u>Details</u>

- a) If a programmable I/O space is mapped to the high-order 32 MB area, the programmable I/O space cannot be accessed during break.

- b) If the programmable I/O space is access during program execution, an SFR illegal break occurs.

#### **Workaround**

- a) Map the programmable I/O space to the low-order 32 MB area.

- b) Map the area where the programmable I/O space exists to the emulation memory or target memory.

No. b-6 Break does not occur even if breakpoint is set (Specification change notice)

#### Details

• (Dis)assembly level:

If breakpoints are set for two instructions in a row and a break occurs at the first instruction, a break may not occur at the second instruction in response to the subsequent request for resumption of execution.

Source level:

If breakpoints are set for two execution statements in a row (of which each is expanded for a single instruction) and a break occurs at the first statement, a break may not occur at the second statement in response to the subsequent request for resumption of execution.

```

10 a = b; (mov r9, r10) \leftarrow Setting of breakpoint

11 a += c; (add r7, r10) \leftarrow Setting of breakpoint

```

#### Cause

If resumption of execution is requested at the position where program execution is stopped at a breakpoint, the instruction at the breakpoint is internally executed in one instruction step, and execution is resumed.

Some CPUs execute two instructions at a time, dependeing on the combination of instructions. In the above (dis)assembly level example, execution is resumed from address 0x8004a0. Therefore, the breakpoint set at address 0x80049e is not hit.

#### Workaround

For software breakpoints preventive measures are implemented to the following debugger versions:

NEC debugger: ID850 E2.20f and later versions.

GHS Multi: Use EX85032.DLL version 5.40 or later.

IAR Embedded Workbench: Use EX85032.DLL version 5.40 or later.

· There is no preventive measure for hardware breaks.

No. b-7 Restrictions related to access address during DMA trace (Specification change notice)

#### <u>Details</u>

If DMA is started while internal RAM is accessed or the program in the internal RAM is executed, either the source address or destination address of DMA will become 3FFExxxh, indicating an internal RAM address for either of the above or for trace data.

#### Workaround

## No. b-8 Restriction on DBPC and DBPSW access during a break (Specification change notice)

#### Details

Although DBPC and DBPSW can be read during a break, they cannot be written to.

#### Workaround

None.

### No. b-9 Restriction on DBTRAP instruction (Specification change notice)

#### Details

If a break occurs in the interrupt processing of a DBTRAP instruction that is executed while a user program is running, the DBPC and DBPSW will be read incorrectly by subsequent RUN instructions.

#### Workaround

None.

### No. b-10 Restriction on access data traced by DMA (Specification change notice)

#### **Details**

When data in internal RAM is read by DMA, the read data value is not traced correctly. However, read address, write data, and write address are traced correctly.

#### Workaround

None.

### No. b-11 Restriction on SFR read access during break (Specification change notice)

#### **Details**

The SFR bits that are normally cleared by a read access (e.g. TC bit of the DCHC register) are also cleared when displayed during a break by using the SFR display function in the debugger. (Even though these SFR bits are not read by the program they are cleared by displaying them.)

#### **Workaround**

None. However, the bit is not reset if the relevant SFR is not displayed by the debugger. In addition, this restriction can be avoided by using the recent versions of device files and debuggers.

### No. b-12 Restriction on target operating voltage (Technical limitation)

#### Details

Emulation cannot be performed when the target operating voltage is 3.5 V or higher.

#### Workaround

None.

### No. b-13 Restriction on accessing emulation ROM area and emulation RAM area (Specification change notice)

#### Details

The emulation ROM area and emulation RAM area cannot be accessed via the 8-bit bus.

#### Workaround

Use the 16-bit bus for accessing the emulation ROM area and emulation RAM area.

# No. b-14 Restriction that the debugger hangs up depending on the software break setting upon PSC register access

#### (Specification change notice)

#### **Details**

The debugger hangs up if the STB bit of the PSC register is set (1) and a software break is set for the subsequent instruction.

#### Workaround

Do not set a software break for the subsequent instruction.

#### **Example**

mov 0x2, r1

st.b r1, prcmd

st.b r1,psc

nop nop ← The debugger hangs up if a software break is set here.

← Setting a software break hereafter causes no problem.

### No. b-15 Restriction that the same branch instruction is traced twice (Specification change notice)

#### **Details**

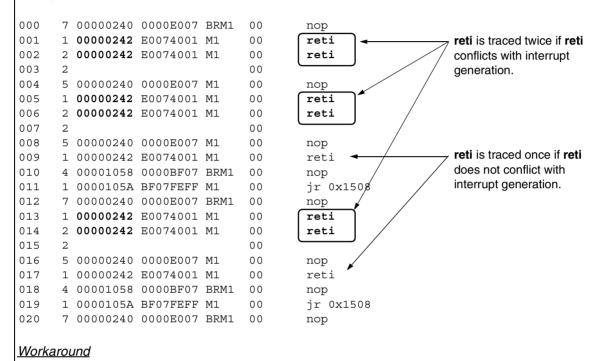

If interrupt generation and execution of a branch instruction (such as JMP, BR CALLT, or CTRET) conflict, the branch instruction is traced twice.

This restriction affects the trace display only. The actual instruction is executed only once.

#### Example

### No. b-16 Restriction on 48-bit length mov instruction trace (Specification change notice)

#### Details

If an interrupt occurs at the same time as a 48-bit length mov instruction is executed, the trace result is illegal. At this time, the trace result of the subsequent instruction may also be illegal. This restriction affects the trace display only. The actual instruction is executed normally.

#### **Example**

• Trace result when instruction and interrupt do not conflict (the restriction does not apply).

```

00110 1 000010BE 2F061851 M1 00 mov 0x205118,r15

00111 2 000010BE 2F062000 00

00112 1 000010C4 6F070000 M1 0205118 xxxxxxxx0 W 00 st.h r0,0x0[r15]

00113 1 000010C8 BF07EAFF M1 00 jr 0x10b2

```

Trace result when instruction and interrupt conflict (the restriction applies).

```

00110 1 000010BE 2F061851 M1 00 ****

00111 2 000010BE 2F062000 00 mov 0x20f146,r15

not r0, r0

```

#### Workaround

None.

```

No. b-17 Restriction on illegal trace of consecutive sld instructions (Specification change notice)

```

#### Details

When the sld instruction is executed successively, the access data or access address in the trace data may not be displayed. The disassemble data is displayed normally.

This restriction affects the trace display only. The actual instruction is executed normally.

#### **Example**

```

021 1 0000002C 00000000 M1

00 nop

022 1 0000002E 00000000 M1

00 nop

023 1 00000030 0000005D M1 0FFFC000 A0077C96 R 00 nop

sld.w 0x0[ep],r11

024 1 00000034 0265046D M1

0.0

sld.w 0x4[ep],r12

025 1 00000036 046D0675 M1 0FFFC004 5DD89D8B R 00

sld.w 0x8[ep],r13

026 1 00000038 0675087D M1

00

sld.w 0xc[ep],r14

027 1 0000003A 087D0A85 M1

0.0

sld.w 0x10[ep],r15

sld.w 0x14[ep],r16

028 1 0000003C 0A850C8D M1

029 1 0000003E 0CD80E95 M1

0FFFC018 3FA7F8B4 R

00/

sld.w 0x18[ep],r17

030 1 00000040 0E950000 M1

90 (sld.w 0x1c[ep],r18

0,0

031 1 00000042 00000000 M1

nop

```

Instructions for which access address/access data is not displayed.

#### Workaround

# No. b-18 Restriction on pin mask function (Specification change notice)

#### <u>Details</u>

When using Green Hills MULTI, the  $\overline{\text{WAIT}}$  and  $\overline{\text{HLDRQ}}$  pins are not masked even if pin masking is set using the PINMASK command.

When using IAR Embedded Workbench, the WAIT and HLDRQ pins are not masked even if pin masking is set in the pin mask field of the Emulator→Hardware Setup dialog box.

The RESET, STOP, and NMI pins can be masked normally.

#### **Workaround**

#### 3. Directions of Use

| No. c-1 | Use of emulation memory |

|---------|-------------------------|

|         | (Direction of use)      |

#### Details

- The emulation memory cannot be mapped to addresses higher that 4000000H in the 64 MB mode.

- The number of wait cycles for the emulation memory is not affected by the WAIT signal but is determined by the setting of the debugger or the setting of the wait control register (see table below).

|                                    |              | Emulation Memory Access                                                         | External Memory Access                                                     |

|------------------------------------|--------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| WAIT: Unmasked<br>EMWAIT: Masked   | Data wait    | Fixed to 1 wait                                                                 | Depends on the DWC0,<br>DWC1 registers settings<br>and WAIT signal status. |

|                                    | Address wait | Fixed to 0 waits                                                                | Depends on the AWC register settings.                                      |

|                                    | Idle state   | Fixed to 0 cycles                                                               | Depends on the BCC register settings                                       |

| WAIT: Unmasked<br>EMWAIT: Unmasked | Data wait    | Depends on the DWC0,<br>DWC1 registers settings.<br>1 wait when set to 0 waits. | Depends on the DWC0,<br>DWC1 registers settings<br>and WAIT signal status. |

|                                    | Address wait | Fixed to 0 waits                                                                | Depends on the AWC register settings.                                      |

|                                    | Idle state   | Fixed to 0 cycles                                                               | Depends on the BCC register settings                                       |

When setting the number of waits for the emulation memory to the same number as for the actual external memory for the purpose of performance testing, select "Target Wait" using the debugger.

Address waits cannot be inserted in the emulation memory.

If it is necessary to insert an address wait, set as follows.

Number of data waits for CS space in emulation memory

Number of address waits for external memory or external I/O Number of data waits for external memory or external I/O

This setting is effective to make the speed of access to the emulation memory equal to that to the external memory or external I/O when measuring the performance, etc.

Refer to the table above for how to insert waits in the emulation memory.

# No. c-1 Use of emulation memory (Direction of use)

(cont)

#### **Details**

The setting of the EXIMC register is not valid for the emulation memory; it is only valid for the memory and I/O that are mapped to the target. The emulation memory oprates via the separate bus regardless of the EXIMC settings.

Since the difference between the cycle lengths of the multiplexed bus and separate bus is 1 clock, set the multiplexed bus as follows when it is used.

This setting is effective to make the speed of access to the emulation memory equal to that to the external memory or external I/O when measuring the performance, etc.

Number of data waits for CS space in emulation memory

1

Number of data waits for external memory or external I/O

### No. c-2 Pin handling (Direction of use)

#### **Details**

- The in-circuit emulator uses minimum pin handling, giving priority to compatibility with the device. Take adequate countermeasures against static electricity if the in-circuit emulator is used without the target connected.

- Inside the in-circuit emulator, pin handling is performed by the option board. For details, refer to the corresponding User's Manual of the option board.

| No. c-3 |     | Power saving (Direction of use)                                                                                                                                |                                                                       |                                                                                       |  |  |  |

|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

|         | Det | <u>Details</u>                                                                                                                                                 |                                                                       |                                                                                       |  |  |  |

|         |     | To save power, be sure to insert five NOP instructions after executing the HALT instruction and an instruction that sets the STB (or STP) bit of PSC register. |                                                                       |                                                                                       |  |  |  |

|         | a)  | STB (or                                                                                                                                                        | STP) bit (PSC register) se                                            | etting instruction                                                                    |  |  |  |

|         |     | mov<br>movea<br>st.b<br>st.b<br>nop<br>nop<br>nop                                                                                                              | 0x2, r11<br>base_address, r0, r20<br>r11, PRCMD[r20]<br>r11, PSC[r20] | ; base_address = FFFF0000H<br>; PRCMD = 01FCH<br>; PSC = 01FEH<br>; insert five nop's |  |  |  |

|         | b)  | HALT inst                                                                                                                                                      | struction                                                             | ; insert five nop's                                                                   |  |  |  |

|         |     | nop<br>nop<br>nop<br>nop                                                                                                                                       |                                                                       |                                                                                       |  |  |  |

### No. c-4 Pin control with target power OFF (Direction of use)

#### Details

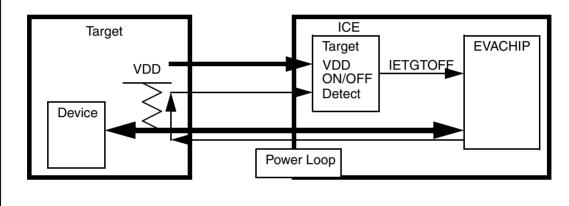

When power to the emulator is ON and that to the target is OFF, leakage current may flow from the emulator to the target.

When the target is connected, the emulator always senses the target supply voltage by using a target supply voltage detector circuit, and the emulator is automatically reset when the target power is turned ON or OFF. In this reset status, the external bus signal go inter a high-impedance state.

Some external bus signals, however, drive a high level, and a current may leak into Vdd of the target via the pull-up resistor of the target.

The target supply voltage detector circuit of the emulator detects this VDD, and the emulator assumes that power is applied to the target. Consequently, reset is cleared and the external bus signals are driven. As a result, a leakage current flows.

### No. c-5 Notes on trace data (Direction of use)

#### Details

#### Trace sequence of access data of LD and ST instructions

If the LD and ST instructions are executed in that order, access of the ST instruction and access of the LD instruction are traced in this order for trace data.

If the LD instruction is the shortest (IRAM access), the read data is written to the same frame as the LD instruction. If the bus cycle is extended because of external memory access, the read data is written to trace after the ST instruction.

For instruction execution (fetch), the instruction that comes first is traced, and relation can be established based on the information on the access validity flag and direction of read/write.

Basically, because the data is known in the write cycle, preparation for writing the data to the tracer is made when the ST instruction is executed. In the read cycle, the data is written to the tracer when the read cycle is completed and the data is loaded. If the LD and ST instructions are arranged, therefore, the sequence of only the access data of the trace data may be reversed, like the data of the ST instruction  $\rightarrow$  data of the LD instruction.

#### · Trace timing of external logic data

It takes the external logic data the number of clocks required for fetching 8 x 1 times to be output to the tracer.

The external logic data is sampled in synchronization with instruction execution and differs depending whether a program is stored in IROM or external memory, and on the number of wait cycles.

When a program is placed in the external memory, it also differs depending on whether a read/write cycle is inserted in the external memory.

The shortest time is 8 clocks when a program is placed in IROM.

The point to be noted is that the external logic data is not sampled every clock.

Because it is not sampled unless instruction execution is performed, a signal that changes after execution of on instruction and before execution of another cannot be detected.

If there is a possibility that an instruction is executed every clock as is the case with IROM, therefore the chance of missing the external logic data decreases. Conversely, if many wait cycles are inserted in the external memory, the chance of missing the external logic data increases.

## No. c-6 Caution on fail-safe break in internal ROM/RAM area (Direction of use)

#### <u>Details</u>

The internal ROM/RAM of the in-circuit emulator is set as follows depending on the debugger setting.

| Internal ROM     |                                                                         |  |  |  |

|------------------|-------------------------------------------------------------------------|--|--|--|

| Debugger Setting | Internal ROM space to Be Mapped<br>(When Mapped from 00000000H Address) |  |  |  |

| 0 KB             | None                                                                    |  |  |  |

| 32 KB            | 00000000H to 00007FFFH                                                  |  |  |  |

| 64 KB            | 00000000H to 0000FFFFH                                                  |  |  |  |

| 128 KB           | 00000000H to 0001FFFFH                                                  |  |  |  |

| 256 KB           | 00000000H to 0003FFFFH                                                  |  |  |  |

| 512 KB           | 00000000H to 0007FFFFH                                                  |  |  |  |

| 1024 KB          | 00000000H to 000FFFFFH                                                  |  |  |  |

| Other            | Depends on the target device                                            |  |  |  |

#### Remark:

No fail-safe occurs in any mapping case when an access (instruction fetch or data read access) to 00000000H to 000FFFFFH is performed. A write protect break occurs when a write access is performed.

To disable accessing to the space from 00080000H to 000FFFFFH, for example when 512 KB is set, implement a measure such as setting an event break.

In addition, no fail-safe break occurs when an access (instruction fetch or data read access) to 00100000H to 001FFFFFH is performed if internal ROM exists from address 00100000H.

### (D) Valid Specification

| Item | Date published | Document No.    | Document Title                                   |

|------|----------------|-----------------|--------------------------------------------------|

| 1    | March 2003     | U16313EJ1V0UM00 | IE-V850ES-G1 In-Circuit Emulator (User's Manual) |

### (E) Revision History

| Item | Date published | Document No.  | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | June 2002      | TPS-HE-B-3100 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2    | June 2002      | TPS-HE-B-3101 | Revision of table of operating precautions                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3    | September 2002 | TPS-HE-B-3102 | Addition of control code C                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4    | October 2002   | TPS-HE-B-3103 | Addition of control code D                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5    | December 2003  | TPS-HE-B-3104 | Release in new format.  Operating precautions are divided into "Restrictios dependent on CPU functions" (a), "Restrictions on debug functions" (b) and "Directions of use" (c)  Former operating precaution no. 1 has been deleted.  Former operating precautions no. 2 to 13 have got new no. b-1 to b-12.  Addition of operating precautions no. a-1, a-2, b-13 to b-18.  Former chapter of cautions adapted to the table format (c-1 to c-6). |

| 6    | October 2004   | TPS-HE-B-3105 | Addition of control F, for which restriction b-1 has been abolished.                                                                                                                                                                                                                                                                                                                                                                             |