#### Features

#### PCI Interfaces

- Industry-standard 32-bit, 66-MHz PCI bridge

- Fully PCI Local Bus Specification, Revision 2.3 compliant

- Supports up to nine PCI bus masters on the secondary interface

- Ten independent secondary clock outputs to the secondary slots

- Primary and secondary interfaces can be operated using asynchronous clocks

- Secondary clock can either be derived from the input primary clock or supplied by an external clock source

- Secondary clocks can be masked through the GPIO interface during power up

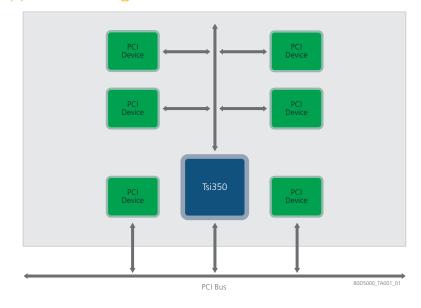

The Tsi350 makes it possible to extend a system's load capability limit beyond that of a single PCI bus by allowing motherboard designers to add more PCI devices or more PCI option card slots than a single PCI bus can support.

- Supports four independent delayed transactions in each direction

- Supports up to nine secondary requests and grants

- External arbiter support on the secondary bus

- Supports CompactPCI Hot Swap functionality

- CI Power management with D3Hot support with option to disable clocks during D3Hot state

- Supports Bus Locking mechanism

- VGA/Palette memory and I/O decoding options

- Optional non-posted entry flush upon posted writes traveling the same direction

- Compatible with existing solutions from Intel, TI, PLX, and Pericom

The Tundra Semiconductor Tsi350 is a PCI-to-PCI bridge that is fully compliant with *PCI Local Bus Specification, Revision 2.3*. The Tsi350 has sufficient clock and arbitration pins to support nine PCI bus master devices directly on its secondary interface.

The Tsi350 allows the two PCI buses to operate concurrently. This means that a master and a target on the same PCI bus can communicate while the other PCI bus is busy. This traffic isolation may increase system performance in applications such as multimedia.

The Tsi350 makes it possible to extend a system's load capability limit beyond that of a single PCI bus by allowing motherboard designers to add more PCI devices or more PCI option card slots than a single PCI bus can support.

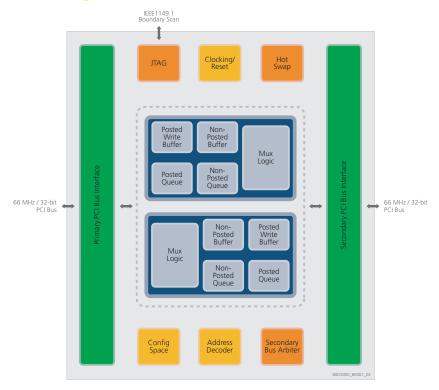

The Tsi350 has two identical PCI Interfaces that each handle PCI transactions for its respective bus, and, depending on the type of transaction, can act as either a bus master or a bus slave. These interfaces transfer data and control information flowing to and from the blocks shown below.

#### **Block Diagram**

### **Benefits**

- Extend PCI load capability

- Straightforward system design through the Tsi350's highly configurable features

#### **Physical**

- 208-PQFP and 256 PBGA packages

- 3.3 V I/O, 5 V tolerant

#### **Applications**

- Industrial PC's (IPC) backplanes

- Video capture cards

- Embedded video recorders (EVRs)

- Multi-function printers

- Storage host bus adapters (HBAs)

- Network interface cards (NICs)

- Firewall and security gateways

- Printers, graphics and imaging systems

# Design Support Tools

Tundra is committed to helping customers minimize their time to market. That's why we provide one of the highest levels of design support in the industry, including:

- Application notes

- Evaluation boards

- IC models

- Hardware and software development tools

For more information, see the Tundra website at www.tundra.com/dst.

# Ordering Information

Available immediately

Part numbers: Tsi350-66CQ, Tsi350-66CQY, Tsi350-66CLVZ1

For ordering information, see the Tundra website at www.tundra.com/Tsi350

## Typical Applications

Option card designers can use Tsi350 to implement multiple-device PCI option cards. Without a PCI-to- PCI bridge, PCI loading rules would limit option cards to one device. The *PCI Local Bus Specification* loading rules limit PCI option cards to a single connection per PCI signal in the option card connector. The Tsi350 overcomes this restriction by providing, on the option card, an independent PCI bus to which up to nine devices can be attached.

Figure 2 shows how the Tsi350 enables the design of a multi-component option card or expand exisitng PCI buses.

#### Application Diagram