## **TP3410 ISDN Basic Access Echo-Cancelling 2B1Q U Transceiver**

## **General Description**

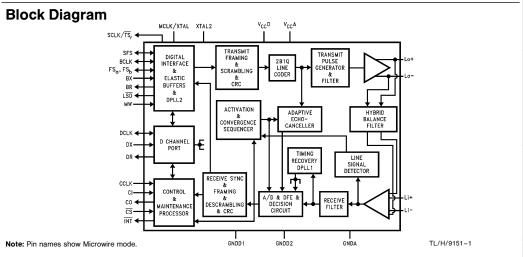

The TP3410 is a complete monolithic transceiver for ISDN Basic Access data transmission at either end of the U interface. Fully compatible with ANSI specification T1.601, it is built on National's advanced double-metal CMOS process, and requires only a single +5V power supply. A total of 160 kbps full-duplex transmission on a single twisted-pair is provided, with user-accessible channels including 2 'B' channels, each at 64 kbps, 1 'D' channel at 16 kbps, and an additional 4 kbps for loop maintenance. 12 kbps of bandwidth is reserved for framing. 2B1Q Line coding is used, in which pairs of binary bits are coded into 1 of 4 quantum levels for transmission at 80k symbols/sec (hence 2 Binary/ 1 Quaternary). To meet the very demanding specifications for <1 in 10e7 Bit Error Rate even on long loops with crosstalk, the device includes 2 Adaptive Digital Signal Processors, 2 Digital Phase-locked Loops and a controller for automatic activation.

The digital interface on the device can be programmed for compatibility with either of two types of control interface for chip control and access to all spare bits. In one mode a Microwire serial control interface is used together with a 2B+D digital interface which is compatible with the Time-division Multiplexed format of PCM Combo devices and backplanes. This mode allows independent time-slot assignment for the 2 B channels and the D channel.

Alternatively, the GCI (General Circuit Interface) may be selected, in which the 2B + D data is multiplexed together with control, spare bits and loop maintenance data on 4 pins.

Combo® and TRI-STATE® are registered trademarks of National Semiconductor Corporation

WIIGROWIRE™ is a trademark of National Semiconductor Corporation.

The General Circuit Interface (G.C.I.) is an interface specification of the Group-of-Four Eur pean Telecommunications Companies.

#### **Features**

- 2 'B'+'D' channel 160 kbps transceiver for LT and NT

- Meets ANSI T1.601 U.S. Standard

- 2B1Q line coding with scrambler/descrambler

- Range exceeds 18 kft of #26 AWG

- >70 dB adaptive echo-cancellation and equalization

- On-chip timing recovery, no precision external components

- Direct connection to small line transformer

- Automatic activation controller

- Selectable digital interface formats:

- TDM with time-slot assigner up to 64 slots, plus MICROWIRE™ control interface

- GCI (General Circuit Interface), or

- IDL (Inter-chip Digital Link)

- Backplane clock DPLL allows free-running XTAL

- Elastic data buffers meet Q.502 wander/jitter for Slaveslave mode on PBX Trunk Cards and DLC

- EOC and spare bits access with automatic validation

- Block error counter

- 6 loopback test modes

- Single +5V supply, 325 mW active power

- 20 mW idle mode with line signal "wake-up" detector

## **Applications**

- LT, NT-1, NT-2 Trunks, U-TE's, Regenerators etc.

- Digital Loop Carrier

- POTS Pair-Gain Systems

- Easy Interface to:

- Line Card Backplanes

- "S" Interface Device

- Codec/Filter Combos - LAPD Processor

- HDLC Controller

TP3420A TP3054/7 and TP3075/6

MC68302, HPC16400 TP3451

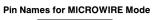

## **Connection Diagrams**

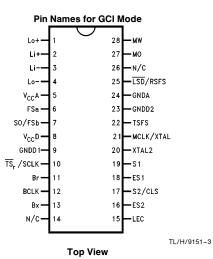

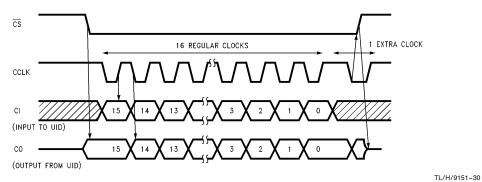

Order Number TP3410J See NS Package Number J28A

## **Pin Descriptions**

|               | <b>D</b> 000.          | iptionio                                                                                                                                                                                                                                                                                                                                                                                                              |            |          |                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No.    | Symbol                 | Description                                                                                                                                                                                                                                                                                                                                                                                                           | Pin<br>No. | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                                               |

| 24<br>9<br>23 | GNDA<br>GNDD1<br>GNDD2 | Negative power supply pins, which must<br>be connected together close to the de-<br>vice. All digital signals are referenced to<br>these pins, which are normally at the sys-<br>tem OV (Ground) potential.                                                                                                                                                                                                           | 22         | TSFS     | The Transmit Superframe Sync pin, which indicates the start of each 12 ms transmit superframe at the U Interface. In NT mode this pin is always an output. In LT mode it may be selected to be either an input or                                                                                                                                                                                         |

| 5             | V <sub>CC</sub> A      | Positive power supply input for the analog sections, which must be $\pm 5V \pm 5\%$ and must be directly connected to $V_{CC}D$ .                                                                                                                                                                                                                                                                                     |            |          | CMOS output via Register CR2; when selected as an output the signal is a square-<br>wave. Must be tied low if selected as input                                                                                                                                                                                                                                                                           |

| 8             | V <sub>CC</sub> D      | Positive power supply input for the digital section, which must be $+5V$ $\pm5\%$ and must be directly connected to $V_{CC}A$ .                                                                                                                                                                                                                                                                                       | 25         | LSD/RSFS | yet not driven.  This pin is an open-drain n-channel Line Signal Detector output, which is normally                                                                                                                                                                                                                                                                                                       |

| 21            | MCLK/<br>XTAL          | The 15.36 MHz Master Clock input, which requires either a parallel resonance crystal to be tied between this pin and XTAL2, or a CMOS logic level clock input from a stable source (a TTL Logic "1" level is not suitable). This clock does not need to be synchronized to the system clock (BCLK and FS), see Section 5.1.                                                                                           |            |          | high-impedance and pulls low only when the device is powered down and an incoming wake-up signal is detected from the far-end. As an option this pin can be programmed to be an output indicating the start of the received superframe at the U interface; an external pull-up resistor is required.                                                                                                      |

| 20            | XTAL2                  | The output of the crystal oscillator, which should be connected to one end of the crystal, if used; otherwise this pin must be left open-circuit. Not recommended to drive additional logic.                                                                                                                                                                                                                          |            |          | The RSFS signal indicates the start of each 12 ms receive superframe from the U Interface and is available in NT and LT modes. The Received Superframe Synch clock output is accessible on pin 25 by writing X'1C04 and X'100C (or X'100E)                                                                                                                                                                |

| 10            | TSr/<br>SCLK           | This pin has 2 functions: in LT mode it is an open-drain n-channel TSr output, which goes low only during the time-slots assigned to the B1 and B2 channels at the Br pin in order to enable the TRI-STATE control of the backplane line-driver. In NT mode it is a full CMOS 15.36 MHz synchronous clock output which is frequency-locked to the received line signal (unlike the XTAL pins it is not free-running). | 1 4        |          | writing X*1C04 and X*100C (or X*100E) during device initialization. See TP3410 users manual AN-913, Part II Section 4.18).  Transmit 2B1Q signal differential outputs to the line transformer. When used with an appropriate 1:1.5 step-up transformer and the line coupling circuit recommended in the Applications section, the line signal conforms to the output specifications in the ANSI standard. |

|               |                        |                                                                                                                                                                                                                                                                                                                                                                                                                       |            |          |                                                                                                                                                                                                                                                                                                                                                                                                           |

## Pin Descriptions (Continued)

| PIN DESCRIPTIONS SPECIFIC TO MICROWIRE MODI | Ε |

|---------------------------------------------|---|

| ONLY (MW = 1)                               |   |

| ONL                  | Y (MW = 1)           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | No.                           | -,                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No.           | Symbol               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                            | CCLK                      | The Microwire control channel Clock input, which may be asynchronous with BCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2                    | Li+<br>Li-           | Receive 2B1Q signal differential inputs from the line transformer. For normal full-duplex operation, these pins should be connected to the Lo± pins through the recommended explains clinicities, shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27                            | <u>CS</u>                 | The Chip Select input, which enables the Control channel data to be shifted in and out when pulled low. When high, this pin inhibits the Control interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 28                   | MW                   | recommended coupling circuit, as shown in the Applications section.  The Microwire/GCI Select pin, which must be tied to V <sub>CC</sub> D to enable the Microwire Interface with any of the data formats at the Digital System Interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26                            | ĪNT                       | The Interrupt output, a latched open-drain output signal which is normally high-impedance, and goes low to indicate a change of status of the loop transmission system. This latch is cleared when the Status Register is read by the microproc-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12                   | BCLK                 | The Bit Clock pin, which determines the data shift rate for 'B' and 'D' channel data on the digital interface side of the device. When Digital System Interface (DSI) Slave mode is selected (see Digital Interfaces section), BCLK is an input which may be any multiple of 8 kHz from 256 kHz to                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16                            | Dx                        | essor.  When the D-port is enabled this pin is the digital input for D channel data to be transmitted to the line clocked by DCLK or BCLK, see Register CR2. When the D-port is disabled via CR2, this pin must be tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      |                      | 4.096 MHz. It need not be synchronous with MCLK.  When DSI Master mode is selected, this pin is a CMOS output clock at 256 kHz,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15                            | Dr                        | When the D-port is enabled this pin is the TRI-STATE output for D channel data to be received from the line clocked by DCLK or BCLK, see Register CR2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      |                      | 512 kHz, 1.536 MHz, 2.048 MHz or 2.56 MHz, depending on the selection in Command Register 1. It is synchronous with the data on Bx and Br.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14                            | DCLK                      | When the D-port is enabled, in DSI Slave or Master mode, this is a 16 kHz clock CMOS output for D channel data. When the D-port is disabled or not used, this pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6                    | FSa                  | In DSI Slave mode, this pin is the Transmit Frame Sync pulse input, requiring a posi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIN I                         | NECCDIDT.                 | must be left open-circuit.  IONS SPECIFIC TO GCI MODE ONLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                      |                      | tive edge to indicate the start of the active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (MW                           |                           | IONS SPECIFIC TO GCI MODE ONLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      |                      | tive edge to indicate the start of the active<br>channel time for transmit B1 channel data<br>into Bx. In DSI Master mode, this pin is a<br>Frame Sync CMOS output pulse conform-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7                    | FSb                  | channel time for transmit B1 channel data into Bx. In DSI Master mode, this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (MW<br>Pin                    | =0)                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7                    | FSb                  | channel time for transmit B1 channel data<br>into Bx. In DSI Master mode, this pin is a<br>Frame Sync CMOS output pulse conform-<br>ing with the selected Digital Interface for-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (MW<br>Pin<br>No.             | =0)<br>Symbol             | Description  The Microwire/GCl select input, which must be tied to GND to enable the GCl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7                    | FSb                  | channel time for transmit B1 channel data into Bx. In DSI Master mode, this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface format.  In DSI Slave mode, this pin is the Receive Frame Sync pulse input, requiring a positive edge to indicate the start of the active channel time of the device for receive B channel data out from Br (see DSI Format section). In DSI Master mode this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface for-                                                                                                                                                                                                                                              | (MW<br>Pin<br>No.<br>28       | =0)<br>Symbol<br>MW       | Description  The Microwire/GCI select input, which must be tied to GND to enable the GCI mode at the Digital System Interface.  The GCI Master/Slave select input for the clock direction. Connect this pin low to select BCLK and FSa as inputs i.e., GCI Slave; Selection of LT or NT mode must be made in register CR2. When MO is connected high, NT Mode is automatically selected, and BCLK, FSa and FSb are outputs, i.e., the GCI Master, see Section 8.  The Bit Clock pin, which controls the shifting of data on the Bx and Br pins, at a rate of 2 BCLK cycles per data bit. When GCI                                                                                                                                                              |

|                      |                      | channel time for transmit B1 channel data into Bx. In DSI Master mode, this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface format.  In DSI Slave mode, this pin is the Receive Frame Sync pulse input, requiring a positive edge to indicate the start of the active channel time of the device for receive B channel data out from Br (see DSI Format section). In DSI Master mode this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface format.  The digital input for B and, if selected, D channel data to be transmitted to the line;                                                                                                                                                  | (MW<br>Pin<br>No.<br>28<br>27 | =0)<br>Symbol<br>MW<br>MO | Description  The Microwire/GCI select input, which must be tied to GND to enable the GCI mode at the Digital System Interface.  The GCI Master/Slave select input for the clock direction. Connect this pin low to select BCLK and FSa as inputs i.e., GCI Slave; Selection of LT or NT mode must be made in register CR2. When MO is connected high, NT Mode is automatically selected, and BCLK, FSa and FSb are outputs, i.e., the GCI Master, see Section 8.  The Bit Clock pin, which controls the shifting of data on the Bx and Br pins, at a rate of 2 BCLK cycles per data bit. When GCI Slave mode is selected (see Digital Interfaces section), BCLK is an input which may be any multiple of 16 kHz from                                           |

| 13                   | Вх                   | channel time for transmit B1 channel data into Bx. In DSI Master mode, this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface format.  In DSI Slave mode, this pin is the Receive Frame Sync pulse input, requiring a positive edge to indicate the start of the active channel time of the device for receive B channel data out from Br (see DSI Format section). In DSI Master mode this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface format.  The digital input for B and, if selected, D channel data to be transmitted to the line; must be synchronous with BCLK.  The TRI-STATE output for B and, if selected, D channel data received from the line;                              | (MW<br>Pin<br>No.<br>28<br>27 | =0)<br>Symbol<br>MW<br>MO | Description  The Microwire/GCI select input, which must be tied to GND to enable the GCI mode at the Digital System Interface.  The GCI Master/Slave select input for the clock direction. Connect this pin low to select BCLK and FSa as inputs i.e., GCI Slave; Selection of LT or NT mode must be made in register CR2. When MO is connected high, NT Mode is automatically selected, and BCLK, FSa and FSb are outputs, i.e., the GCI Master, see Section 8.  The Bit Clock pin, which controls the shifting of data on the Bx and Br pins, at a rate of 2 BCLK cycles per data bit. When GCI Slave mode is selected (see Digital Interfaces section), BCLK is an input which may be any multiple of 16 kHz from 512 kHz to 6.144 MHz. It need not be syn- |

| 13<br>11<br>18<br>19 | Bx<br>Br<br>Cl<br>CO | channel time for transmit B1 channel data into Bx. In DSI Master mode, this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface format.  In DSI Slave mode, this pin is the Receive Frame Sync pulse input, requiring a positive edge to indicate the start of the active channel time of the device for receive B channel data out from Br (see DSI Format section). In DSI Master mode this pin is a Frame Sync CMOS output pulse conforming with the selected Digital Interface format.  The digital input for B and, if selected, D channel data to be transmitted to the line; must be synchronous with BCLK.  The TRI-STATE output for B and, if selected, D channel data received from the line; it is synchronous with BCLK. | (MW<br>Pin<br>No.<br>28<br>27 | =0)<br>Symbol<br>MW<br>MO | Description  The Microwire/GCI select input, which must be tied to GND to enable the GCI mode at the Digital System Interface.  The GCI Master/Slave select input for the clock direction. Connect this pin low to select BCLK and FSa as inputs i.e., GCI Slave; Selection of LT or NT mode must be made in register CR2. When MO is connected high, NT Mode is automatically selected, and BCLK, FSa and FSb are outputs, i.e., the GCI Master, see Section 8.  The Bit Clock pin, which controls the shifting of data on the Bx and Br pins, at a rate of 2 BCLK cycles per data bit. When GCI Slave mode is selected (see Digital Interfaces section), BCLK is an input which may be any multiple of 16 kHz from                                           |

Pin

Symbol

Description

| Pin        | Descr  | iptions (Continued)                                                                                                                                                                                                        |               |                        |                                                                                                                                                                       |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Symbol | Description                                                                                                                                                                                                                | Pin<br>No.    | Symbol                 | Description                                                                                                                                                           |

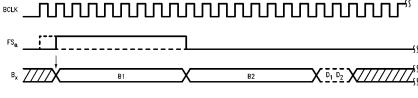

| 13         | Вх     | The digital input for multiplexed B, D and control data clocked by BCLK at the rate of 1 data bit per 2 BCLK cycles, and 32 data bits per 8 kHz frame defined by FSa.                                                      | 17<br>19<br>7 | S2/CLS<br>S1<br>SO/FSb | In GCI Slave mode (MO $=$ 0): input pins S2, S1 and S0 together provide a 3-bit binary-coded select port for the GCI channel number; S2 is the msb.                   |

| 11         | Br     | The open-drain n-channel output for multi-<br>plexed B, D and control data clocked by<br>BCLK at the rate of 1 data bit per 2 BCLK<br>cycles, and 32 data bits per 8 kHz frame                                             |               |                        | These pins must be connected either to $V_{CC}D$ or GND to select the 1-of-8 GCI slots which are available if BCLK $\geq$ 4.096 MHz is used.                          |

|            |        | defined by FSa. A pull-up resistor is required to define the logical 1 state.                                                                                                                                              |               |                        | In GCI Master mode (MO $=$ 1) S2/CLS is the GCI Clock Select input.                                                                                                   |

| 6          | FSa    | In GCI Slave mode (MO connected low),<br>this pin is the 8 kHz Frame Sync pulse in-<br>put, requiring a positive edge to indicate<br>the start of the GCI slot time for both<br>transmit and receive data at Bx and Br. In |               |                        | Connect this pin high to select BCLK = 1.536 MHz; connect CLS low to select BCLK = 512 kHz. SO/FSb is a Frame Sync CMOS output pulse which identifies the B2 channel. |

|            |        | GCI Master mode, this pin is the 8 kHz Frame Sync CMOS output pulse.                                                                                                                                                       |               | ES1 }                  | While in GCI mode, the ES1, ES2 pins are local input pins. The status of the pins can be accessed via the RXM56 register bits 5,6 corresponding to ES1, ES2.          |

|            |        |                                                                                                                                                                                                                            | 15            | LEC                    | Latched External Control output, which is the output of a latched bit in the TXM56 Register.                                                                          |

## **Functional Description**

#### 1.1 Power-On Initialization

When power is first applied, power-on reset circuitry initializes the TP3410 and puts it into the power-down state, in which all the internal circuits including the Master oscillator are inactive and in a low power state except for the Line-Signal Detect circuit; the line outputs Lo+/Lo— are in a high impedance state. All programmable registers and the Activation Sequence Controller are reset.

All states in the Command Registers initialize as shown in their respective code tables. The desired modes for all programmable functions may be selected by writing to these registers via the control channel (Microwire or Monitor channel, as appropriate). Microwire is functional regardless of whether the device is powered up or down, whereas the GCI channel requires the BCLK to be running.

#### 1.2 Power-Up/Power-Down Control

Before powering up the device, the Configuration Registers should be programmed with the required modes.

In Microwire mode and GCI Slave mode, the device is powered up and the MCLK started by writing the PUP command, as described in the Activation section. In GCI Master mode, there are 2 methods of powering up the device: the Bx data input can be pulled low (local power-up command) or the 10 kHz wake-up tone may be received from the far-end.

The power-down state may be re-entered by writing a Power-down command. In the power-down state, all programmed register data is retained. Also, if the loop had been successfully activated and deactivated, the adaptive circuits are "frozen" and the coefficients in the Digital Signal Processors are stored to enable rapid reactivation ("warmstart").

#### 1.3 Reset

A software reset command is provided to enable the clearing of the Activation sequencer without disconnecting the power supply to the device, see the Activation section.

#### 2.0 TRANSMISSION SECTION

#### 2.1 Line Coding And Frame Format

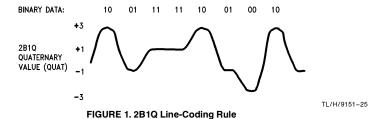

For both directions of transmission, 2B1Q coding is used, as illustrated in Figure 1. This coding rule requires that binary data bits are grouped in pairs, and each pair is transmitted as a symbol, the magnitude of which may be 1 out of 4 equally spaced voltage levels (a "Quat"). There is no symbol value at 0V in this code, the relative quat magnitudes being  $\pm 1$  (the "inner" levels) and  $\pm 3$  (the "outer" levels). No redundacy is included in this code, and in the limit there is no bound to the RDS, although scrambling controls the RDS in a practical sense ( RDS is the Running Digital Sum, which is the algebraic summation of all symbol values in a transmission session).

The frame format used in the TP3410 follows the ANSI standard, shown in Table I. Each complete frame consists of 120 quats, with a line bit rate of 80 kq/s, giving a frame duration of 1.5 ms. A 9 quat syncword defines the framing boundary. Furthermore, a "superframe" consisting of 8 frames is defined in order to provide sub-channels within the spare bits M1 to M6. Inversion of the syncword defines the superframe boundary. Prior to transmission, all data, with the exception of the syncword, is scrambled using a self-synchronizing scrambler to implement the specified 23rd-order polynomial. Descrambling is included in the receiver.

| First Bit<br>(Sign) | Second Bit<br>(Magnitude) | Quat | Pulse Amplitude<br>(Note 1) |

|---------------------|---------------------------|------|-----------------------------|

| 1                   | 0                         | +3   | + 2.5V                      |

| 1                   | 1                         | +1   | + 0.83V                     |

| 0                   | 1                         | -1   | -0.83V                      |

| 0                   | 0                         | -3   | -2.5V                       |

Note 1: For isolated pulses into a  $135\Omega$  termination with recommended transformer interface

|              |                | Framing   | 12x(2B + D) | Overhead Bits (M <sub>1</sub> -M <sub>6</sub> ) |                   |                   |                |                   |                   |  |  |  |

|--------------|----------------|-----------|-------------|-------------------------------------------------|-------------------|-------------------|----------------|-------------------|-------------------|--|--|--|

|              | Quat Positions | 1-9       | 10-117      | 118s                                            | 118m              | 119s              | 119m           | 120s              | 120m              |  |  |  |

|              | Bit Positions  | 1–18      | 19-234      | 235                                             | 236               | 237               | 238            | 239               | 240               |  |  |  |

| Superframe # | Basic Frame #  | Sync Word | 2B + D      | M <sub>1</sub>                                  | M <sub>2</sub>    | M <sub>3</sub>    | M <sub>4</sub> | M <sub>5</sub>    | M <sub>6</sub>    |  |  |  |

| 1            | 1              | ISW       | 2B + D      | eoca <sub>1</sub>                               | eoca <sub>2</sub> | eoca <sub>3</sub> | act            | 1                 | 1                 |  |  |  |

|              | 2              | SW        | 2B + D      | eocd <sub>m</sub>                               | eoci <sub>1</sub> | eoci <sub>2</sub> | dea            | 1                 | febe              |  |  |  |

|              | 3              | SW        | 2B + D      | eoci <sub>3</sub>                               | eoci <sub>4</sub> | eoci <sub>5</sub> | 1              | crc <sub>1</sub>  | crc <sub>2</sub>  |  |  |  |

|              | 4              | SW        | 2B + D      | eoci <sub>6</sub>                               | eoci <sub>7</sub> | eoci <sub>8</sub> | 1              | crc <sub>3</sub>  | crc <sub>4</sub>  |  |  |  |

|              | 5              | SW        | 2B + D      | eoca <sub>1</sub>                               | eoca <sub>2</sub> | eoca <sub>3</sub> | 1              | crc <sub>5</sub>  | crc <sub>6</sub>  |  |  |  |

|              | 6              | SW        | 2B + D      | eocd <sub>m</sub>                               | eoci <sub>1</sub> | eoci <sub>2</sub> | 1              | crc <sub>7</sub>  | crc <sub>8</sub>  |  |  |  |

|              | 7              | SW        | 2B + D      | eoci <sub>3</sub>                               | eoci <sub>4</sub> | eoci <sub>5</sub> | uoa            | crc <sub>9</sub>  | crc <sub>10</sub> |  |  |  |

|              | 8              | SW        | 2B+D        | eoci <sub>6</sub>                               | eoci <sub>7</sub> | eoci <sub>8</sub> | aib            | crc <sub>11</sub> | crc <sub>12</sub> |  |  |  |

| 2, 3,        | 1              | ISW       |             |                                                 |                   |                   |                |                   |                   |  |  |  |

#### (a) Network $\rightarrow$ NT

|              |                | Framing   | 12x(2B+D) | Overhead Bits (M <sub>1</sub> -M <sub>6</sub> ) |                   |                   |                 |                   |                   |  |  |

|--------------|----------------|-----------|-----------|-------------------------------------------------|-------------------|-------------------|-----------------|-------------------|-------------------|--|--|

|              | Quat Positions | 1-9       | 10-117    | 118s                                            | 118m              | 119s              | 119m            | 120s              | 120m              |  |  |

|              | Bit Positions  | 1–18      | 19-234    | 235                                             | 236               | 237               | 238             | 239               | 240               |  |  |

| Superframe # | Basic Frame #  | Sync Word | 2B+D      | M <sub>1</sub>                                  | M <sub>2</sub>    | M <sub>3</sub>    | M <sub>4</sub>  | M <sub>5</sub>    | M <sub>6</sub>    |  |  |

| 1            | 1              | ISW       | 2B+D      | eoca <sub>1</sub>                               | eoca <sub>2</sub> | eoca <sub>3</sub> | act             | 1                 | 1                 |  |  |

|              | 2              | SW        | 2B+D      | eoc <sub>dm</sub>                               | eoci <sub>1</sub> | eoci <sub>2</sub> | ps <sub>1</sub> | 1                 | febe              |  |  |

|              | 3              | SW        | 2B+D      | eoci <sub>3</sub>                               | eoci <sub>4</sub> | eoci <sub>5</sub> | ps <sub>2</sub> | crc <sub>1</sub>  | crc <sub>2</sub>  |  |  |

|              | 4              | SW        | 2B+D      | eoci <sub>6</sub>                               | eoci <sub>7</sub> | eoci <sub>8</sub> | ntm             | crc <sub>3</sub>  | crc <sub>4</sub>  |  |  |

|              | 5              | SW        | 2B+D      | eoca <sub>1</sub>                               | eoca <sub>2</sub> | eoca <sub>3</sub> | cso             | crc <sub>5</sub>  | crc <sub>6</sub>  |  |  |

|              | 6              | SW        | 2B+D      | eoc <sub>dm</sub>                               | eoci <sub>1</sub> | eoci <sub>2</sub> | 1               | crc <sub>7</sub>  | crc <sub>8</sub>  |  |  |

|              | 7              | SW        | 2B+D      | eoci <sub>3</sub>                               | eoci <sub>4</sub> | eoci <sub>5</sub> | 1               | crc <sub>9</sub>  | crc <sub>10</sub> |  |  |

|              | 8              | SW        | 2B+D      | eoci <sub>6</sub>                               | eoci <sub>7</sub> | eoci <sub>8</sub> | 1               | crc <sub>11</sub> | crc <sub>12</sub> |  |  |

| 2, 3,        | 1              | ISW       |           |                                                 |                   |                   |                 |                   |                   |  |  |

#### (b) NT → Network

Note: 8 × 1.5 ms Basic Frames = 12 ms/Superframe. NT-to-Network superframe is offset from Network-to-NT superframe by 60 ± 2 quats (about 0.75 ms). All bits other than the Sync Word are scrambled.

sai

= start-up bit (= 1 during start-up) act aib

= alarm indication bit (= 0 to indicate interrup-

tion)

crc

febe

= cyclic redundacy check: covers  $2B+D+M_4$

1 = most significant bit

2 = next significant bit etc.

= cold-start-only bit (= 1 to indicate cold-startcso

only)

= turn off bit (= 0 to announce turn off) dea eoc a = address bits

= embedded operations channel

dm = data/message indicator (0 = data,

1 = message)

i = information (data or message)

= far end block error bit (= 0 for errored superframe)

= NT in test mode bit (= 0 to indicate test mode)

ps1, ps2 = power status bits (= 0 to indicate power prob-

lems)

= pair of bits forming quaternary symbol Quat

s = sign bit (first in quat)

m = magnitude bit (second in quat)

= S-activation-indication bit (= 1 for S/T activity)

= U-only-activation bit (= 1 to activate S/T) uoa "1" = reserved bit for future standard (= 1)

= network indicator bit (= 1, reserved for network use)

2B+D = user data, bits 19-234 in frame = M-channel, bits 235-240 in frame

$SW/ISW = synchronization \ word/inverted \ synchronization$

word, bits 1-18 in frame

TABLE I. 2B1Q Superframe Format and Overhead Bit Assignments

#### 2.2 Line Transmit Section

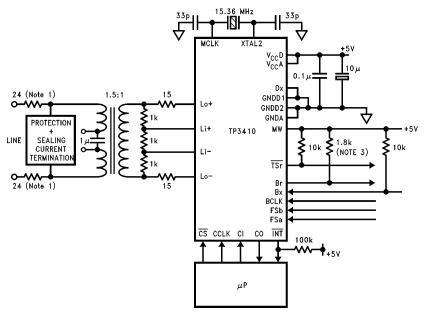

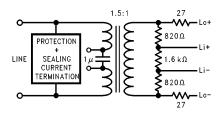

Data to be transmitted to the line consists of the customer's 2B+D channel data and the data from the maintenance processor, plus other "spare" bits in the overhead channels. This data is multiplexed and scrambled prior to addition of the syncword. A pulse waveform synthesizer then drives the transmit filter, which in turn passes the line signal to the line driver. The differential line-driver outputs, Lo  $\pm$ and Lo-, are designed to drive a transformer through an external termination circuit. A 1:1.5 transformer, designed as shown in the Applications section, results in a signal amplitude of nominally 2.5V pk on the line for single quats of the outer ( $\pm 3$ ) levels. Note, however, that because of the RDS accumulation of the 2B1Q line code, continuous random data will produce signal swings considerably greater than this on the line. Short-circuit protection is included in the output stage; overvoltage protection must be provided

#### 2.3 Line Receive Section

The receive input signal should be derived from the transformer by means of a coupling circuit as shown in the Applications section. At the front-end of the receive section is a continuous filter followed by a switched-capacitor low-pass filter, which limits the noise bandwidth. A Hybrid Balance Filter provides a degree of analog echo-cancellation in order to limit the dynamic range of the composite signal. An A/D converter then samples the composite received signal prior to the cancellation of the "echo" from the local transmitter by means of an adaptive digital transversal filter (i.e., the "echo-canceller"). Following this, the attenuation and distortion (inter-symbol interference) of the received signal from the far-end, caused by the transmission line, are equalized by a second adaptive digital filter configured as a Decision Feedback Equalizer (DFE), thereby restoring a "flat" channel response with maximum received eye opening over a wide spread of cable attenuation characteristics.

From the received line signal, a Timing Recovery circuit based on a DPLL (Digital Phase-Locked Loop) recovers a low-jitter clock for optimum sampling of the received symbols. The MCLK input provides the reference clock for the DPLL at 15.36 MHz. Received data is then detected, with automatic correction for line signal polarity if necessary, and a flywheel synchronization circuit searches for and locks onto the frame and superframe syncwords. Frame lock will be maintained until errored sync words are detected for

480 ms. If a loss-of-sync condition persists for 480 ms the device will cease transmitting and go into a RESET state.

While the receiver is synchronized, data is descrambled using the specified polynomial, and the individual channels demultiplexed and passed to their respective processing circuits

Whenever the loop is deactivated, either powered up or powered down, a Line Signal Detect circuit is enabled to detect the presence of an incoming 10 kHz wake-up tone if the far-end starts to activate the loop. The LSD circuit generates an interrupt and, if the device is powered down, pulls the  $\overline{\text{LSD}}$  pin low; either of these indicators may be used to alert an external controller, which must respond with the appropriate commands to initiate the activation sequence (see the Activation section).

#### 3.0 ACTIVATION CONTROL: OVERVIEW

The TP3410 contains an automatic sequencer for the complete control of the start-up activation sequence specified in the ANSI standard. Both the "cold-start" and the fast "warm-start" are supported. Interaction with an external controller requires only Activate Request and Deactivate Request commands, with the option of inserting breakpoints in the sequence for additional external control if desired. Automatic control of the "act" and "dea" bits in the M4 bit positions is provided, along with the specified 40 ms and 480 ms timers used during deactivation. A 15 second default timer is also included, to prevent system lock-up in the event of a failed activation attempt. Section 11 gives an overview of the activation handshake between the TP3410 and the controller. See TP3410 User's Manual AN-913 for additional information.

#### 4.0 MAINTENANCE FUNCTIONS: OVERVIEW

#### 4.1 M Channel Processing

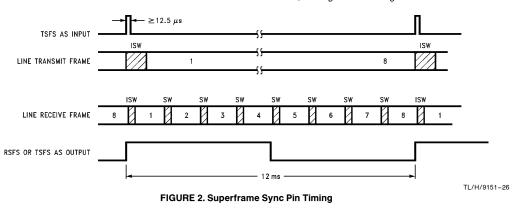

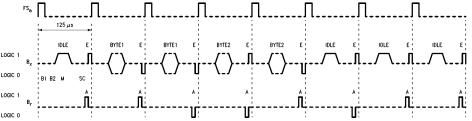

In each frame of the superframe there are 6 "Overhead" bits assigned to various control and maintenance functions of the DSL. Some processing of these bits may be programmed via the Command Registers, while interaction with an external controller provides the flexibility to take full advantage of the maintenance channels. New data written to any of the overhead bit Transmit Registers is resynchronized internally to the next available complete superframe or half-superframe, as appropriate. In addition, the SFS pin may be used to indicate the start of each superframe in 1 direction, see *Figure 2* and Register CR2.

#### 4.2 Embedded Operations Channel

The EOC channel consists of 2 complete 12-bit messages per superframe, distributed through the M1, M2 and M3 bits of each half-superframe as shown in Table I. Each message is composed of 3 fields; a 3-bit address identifying the message destination, a 1-bit indicator for the data mode, i.e., encoded message or raw data, and an 8-bit information byte. The Microwire port or GCI Monitor Channel provides access to the complete 12 bits of every message in the TX EOC and the RXEOC Registers. If one of the defined encoded messages is received, e.g., Send Corrupted CRC, then the appropriate Command Register instruction must be written to the device to invoke the function.

#### 4.3 M4 Bits

The M4 bit position of every frame is a transparent channel in which are transmitted data bits loaded from the M4 Transmit Register TXM4, one byte per superframe. On the receive side the M4 bits from one complete superframe are sent to a checking circuit which holds each new M4 byte and compares it against the previous M4 byte(s) for validation prior to sending it to the RXM4 Receive Register; Register OPR provides several options for control of this validation

#### 4.4 Spare M5 And M6 Bits

Overhead bits M5 and M6 in frame 1 (M51 and M61) and M5 in frame 2 (M52) are transparently transmitted from the Transmit M56 Spare Bit Register to the line. In the receive direction, data from these bit positions is sent to a checking circuit which holds the new M5/M6 spare bits and compares them against the previous M5/M6 bits for validation prior to sending them to the Receive M56 Spare Bit Register; the OPR Register provides several options for control of this validation.

#### 4.5 CRC Circuit

In the transmit direction an on-chip crc calculation circuit automatically generates a checksum of the 2B+D+M4 bits using the polynomial x12+x11+x3+x2+x+1. Once per superframe the crc is transmitted in the specified M5 and M6 bit positions (see Table I). In the receive direction a checksum is again calculated on the same bits as they are received and, at the end of the superframe, compared against the crc transmitted with the data. The result of this comparison generates a "Far End Block Error" bit (the febe bit), which is transmitted back towards the other end of the DSL in the next superframe. If there are no errors in a superframe, febe is set  $=\,$  1, and if there is one or more errors febe is set  $=\,$  0.

The TP3410 also includes a readable 8-bit Block Error Counter BEC1, which is decremented by 1 each superframe in which febe = 0 or nebe = 0 is received. Section 10.5 describes the operation of this counter.

On first application of power, and after the software reset (X'1880, X'1800), both the ECT1 as well as BEC1 are initialized to X'FF. See the Block Error Counter section for more details.

#### **5.0 DIGITAL INTERFACE: ALL FORMATS**

#### 5.1 Clocking

In LT applications (network end of the Loop), the Digital System Interface (DSI) normally accepts BCLK and FS signals from the network, requiring the selection of DSI or GCI Slave mode in Register CR1. A Digital Phase-Locked Loop (DPLL #2) on the TP3410 allows the MCLK frequency to be plesiochronous (i.e. free-running) with respect to the network clocks, (BCLK and the 8 kHz FSa input). With a tolerance on the MCLK oscillator of 15.36 MHz  $\pm$ 100 ppm, the lock-in range of DPLL2 allows the network clock frequency to deviate up to  $\pm$ 50 ppm from nominal.

In NT applications, when the device is in NT mode and is slaved to loop timing recovered from the received line signal, DSI or GCI Master mode should normally be selected. In this case BCLK, FS and SCLK (15.36 MHz) signals are outputs which are phase-locked to the recovered clock. A slave-slave mode is also provided, however, in which the Digital Interface data buffers on the TP3410 allow BCLK and FSa/b to be input from an external source, which must be frequency-locked (but may take an arbitrary phase) to the received line signal; in this case DSI or GCI Slave mode should be selected.

#### 5.2 Data Buffers

The TP3410 buffers the 2B+D data at the Digital Interface in elastic FIFOs, which are 3 frames deep in each direction. When the Digital Interface is a timing slave these FIFOs compensate for relative jitter and wander between the Digital Interface clocks (BCLK and FSa/b) and bit and frame timing at the Line Interface. Each buffer can absorb wander up to 18  $\mu s$  in  $\geq$  10 secs without "slip", exceeding CCITT recommendation Q.502. Excessive wander causes a controlled slip of one complete frame.

# 6.0 DIGITAL INTERFACE DATA FORMATS IN MICROWIRE MODE (MW = 1)

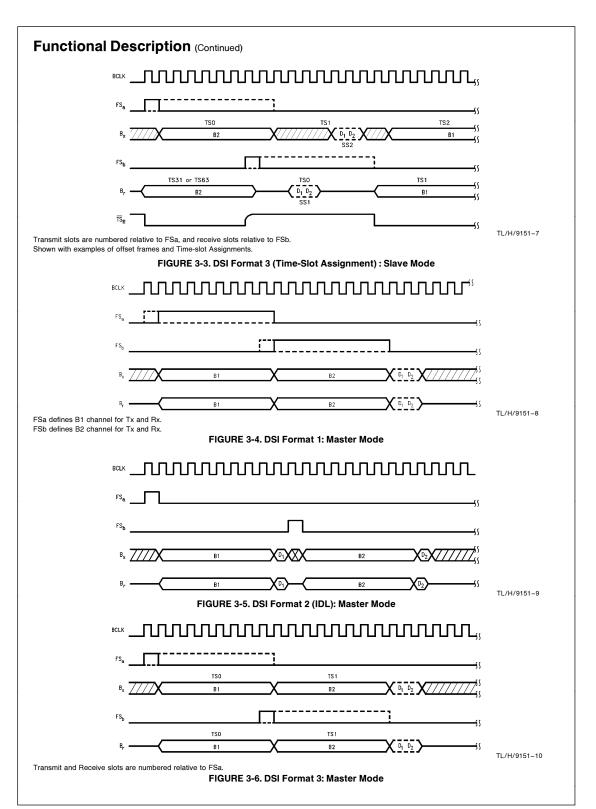

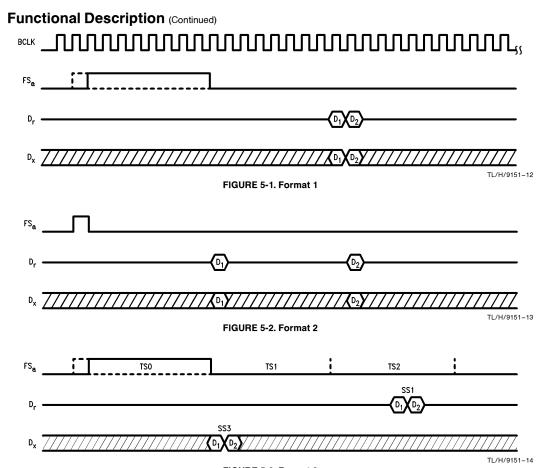

When the MW pin is tied high to enable the Microwire Port for control and status, the Digital System Interface on the TP3410 provides a choice of four multiplexed formats for the B and D channel data, as shown in *Figure 3*. These apply in both LT and NT modes of the device, and selection is made via Register CR1. Selection of DSI Master or Slave mode must also be made in CR1. Within each format there is also an independent selection available to either multiplex the D channel (Tx and Rx) data on the same pins as the B channels, or via the separate D-channel access pins, DCLK, Dx and Dr, see Section 6.3.

Format 1: In Format 1, the 2B + D data transfer is assigned to the first 18 bits of the frame on the Bx and Br pins. Channels are assigned as follows: B1 (8 bits), B2 (8 bits), D (2 bits), with the remaining bits ignored until the next frame sync pulse. When the D channel port is enabled (see CR2), only the 2 B channels use the Bx and Br pins; the D bits are assigned to the 17th and 18th bits of the frame on the Dx and Dr pins. Figure 3-1 shows this format in DSI Slave Mode, and Figure 3-4 shows DSI Master Mode.

Format 2: Format 2 is the IDL, in which the 2B+D data transfer is assigned to the first 19 bits of the frame on the Bx and Br pins. Channels are assigned as follows: B1 (8 bits), D (1 bit), 1 bit ignored, B2 (8 bits), D (1 bit), with the remaining bits ignored until the next frame sync pulse. Figure 3-2 shows this format in DSI Slave Mode, and Figure 3-5 shows DSI Master Mode.

Format 3: This format provides time-slot assignment capability for the B1 and B2 channels, which can be independently assigned to any 8-bit wide time-slot from 64 (or less) on the Bx and Br pins; the Transmit and Receive directions are also independently assignable. Also the D channel can be assigned to any 2-bit wide time-slot from 256 (or less) on the Bx and Br pins (D port disabled) or

on the Dx and Dr pins (see D-Channel Port section). Figure 3-3 shows this format in DSI Slave Mode, and Figure 3-6 shows DSI Master Mode; see also Section 6.2.

Format 4: This is similar to the GCI format for the 2B+D channels, but excludes the Monitor channel and C/I channel. Channels are assigned to the first 26 bits of each frame as follows: B1 (8 bits), B2 (8 bits), ignored (8 bits), D (2 bits). The remaining bits in the frame are ignored until the next frame sync pulse. The relationship between BCLK and data is the same as in the GCI mode for GCI Channel 0, see *Figure 7* (in DSI Master Mode, BCLK = 512 kHz and FS<sub>a</sub> is a square wave output)

TL/H/9151-5

TL/H/9151-6

FSa defines B1 channel for Tx. FSb defines B1 channel for Rx.

FIGURE 3-1. DSI Format 1: Slave Mode

#

Delayed timing mode must be selected; Time-slot immediate mode only (no TSA).

FIGURE 3-2. DSI Format 2 (IDL): Slave Mode

#### 6.1 FS Relationship To Data (Microwire Mode)

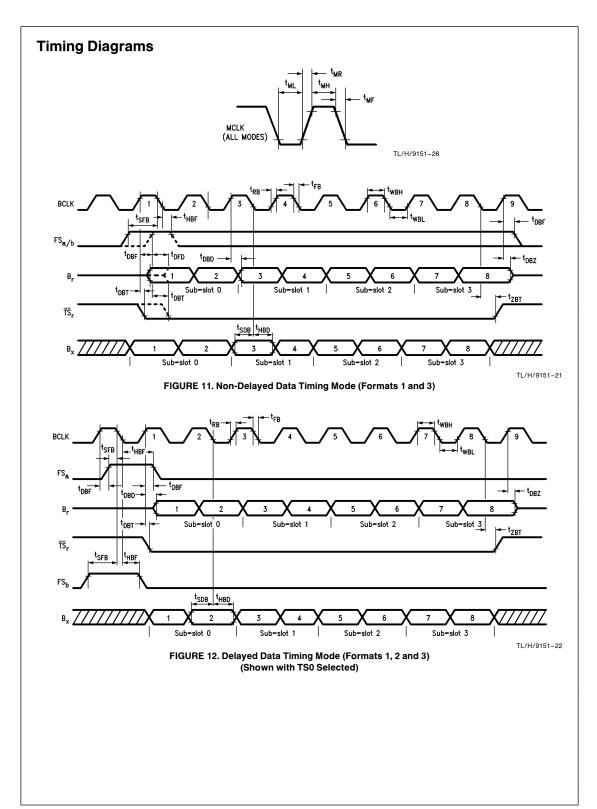

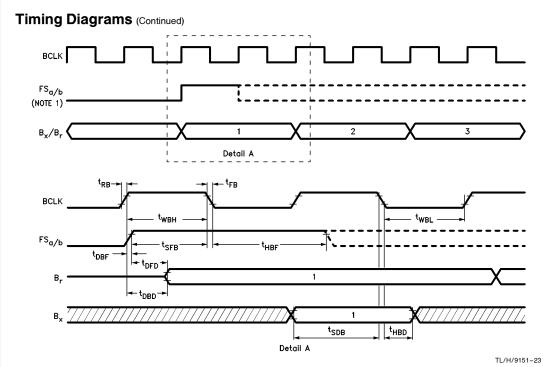

For applications on a line-card, in DSI Slave Mode, the B and D channel slots can be interfaced to a Time-Division Multiplexed (TDM) bus and assigned to a time-slot. The repetition rate of the FS input signals must be 8 kHz and must be synchronized to the BCLK input, which may be any frequency from 256 kHz to 4.096 MHz in 8 kHz increments. Two different relationships may be established between the FS inputs and the actual time-slots on the PCM busses by setting the DDM bit in Control Register CR1, see *Figures 3*, 11 and 12. Non-delayed data mode is similar to long frame timing on the TP3050/60 series of devices (COMBO I): the time-slots are defined by the 8-bit duration FSa and FSb signals. The alternative is to use Delayed Data Mode, which is similar to short frame sync timing on COMBO I, in which each FS input indicates the start of the first time-slot.

Serial B channel data is shifted into the Bx input during each assigned Transmit time-slot on the falling edges of BCLK. During each assigned Receive time-slot, the Br output shifts data out on the rising edges of BCLK. Also, with the device in LT Mode, the TSr pin is an open drain n-channel pull-down output which goes low during the selected time-slots for the received B1 and B2 channels at the Br pin to control the TRI-STATE Enable of a backplane line-driver; it is high-impedance at all other times.

In NT Mode, when DSI Master mode is selected, FSa and FSb are outputs indicating the B1 (or TS0) and the B2 (or TS1) channels respectively. BCLK is also an output at the serial data shift rate, which is dependent on the format selected. Again, either a delayed or non-delayed relationship between FSa, FSb and the start of the first time-slot can be selected.

# **6.2 B Channel Time-slot Assignment; Format 3 Only (Microwire Mode)**

In Format 3 only, the TP3410 provides programmable time-slot assignment for selecting the Transmit and Receive B channel time-slots. Following power-on, the device is automatically in Non-delayed Data Mode; if Delayed Data Mode is required it must first be selected (see CR1) prior to using Time-slot Assignment, and the FS pulses must conform to the Delayed Data timing format. The actual transmit and receive time-slots are then determined by the internal Time-slot Assignment counters, programmed via Control Registers TXB1, TXB2, RXB1 and RXB2. Normally used in DSI Slave mode, Format 3 allows a frame to consist of up to 64 time-slots of 8 bits each with BCLK up to 4.096 MHz.

A new assignment becomes active on the second frame following the end of the 16-bit Chip Select.

#### 6.3 D Channel Port Selection (Microwire Mode)

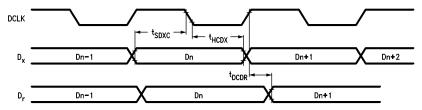

In any of the DSI Formats, the 2 D channel bits per frame may either be multiplexed with the B channels on the Bx and Br pins, or may be accessed via the separate D channel port consisting of Dx and Dr. Furthermore, when using the separate D port the data shift clock may either be a continuous, unframed data stream using the 16 kHz clock output at DCLK, see *Figure 4*, or may use the BCLK, see *Figure 5*. Selection of these options is via Control Register CR2.

#### 6.4 D Channel Time-Slot Assignment

In addition to B channel TSA, Format 3 allows independent Time Slot Assignment for the Transmit and Receive D channels, which may be programmed via Registers TXD and RXD. As with the B channels, up to 64 time-slots are available if BCLK = 4.096 MHz, and in addition the 2 D bits may be assigned, in pairs, to specific bit locations within the time-slot; that is in bits 1 and 2; 3 and 4; 5 and 6; or 7 and 8. D channel TSA may be used either with the D channel multiplexed with the B channel data, or with the separate D Channel port clocked with BCLK; it cannot be used with the 16 kHz clock option at DCLK.

**Summary of DSI Slave Mode Options**

| Function              | Format Number |       |        |       |  |  |  |  |  |

|-----------------------|---------------|-------|--------|-------|--|--|--|--|--|

| Tunction              | 1             | 2     | 3      | 4     |  |  |  |  |  |

| FSa                   | Tx B1         | Tx B1 | Tx TS0 | Tx B1 |  |  |  |  |  |

| FSb                   | Rx B1         | Rx B1 | Rx TS0 | Rx B1 |  |  |  |  |  |

| Non-Delayed Timing?   | Yes           | No    | Yes    | Yes   |  |  |  |  |  |

| Delayed Timing?       | Yes           | Yes   | Yes    | No    |  |  |  |  |  |

| Tx and Rx Frames with | Yes           | Yes   | Yes    | Yes   |  |  |  |  |  |

| Any Phase?            |               |       |        |       |  |  |  |  |  |

| TSA Available?        | No            | No    | Yes    | No    |  |  |  |  |  |

| D Port Available?     | Yes           | Yes   | Yes    | Yes   |  |  |  |  |  |

#### **Summary of DSI Master Mode Options**

| Function          | Format Number |              |         |         |  |  |  |  |  |  |

|-------------------|---------------|--------------|---------|---------|--|--|--|--|--|--|

| Tunction          | 1             | 2            | 3       | 4       |  |  |  |  |  |  |

| FSa               | B1            | B1           | TS0     | B1      |  |  |  |  |  |  |

| FSb               | B2            | B2           | TS1     | B2      |  |  |  |  |  |  |

| FS Formats        | Non-          | Non- Delayed |         | Non-    |  |  |  |  |  |  |

|                   | Delayed       | Only         | Delayed | Delayed |  |  |  |  |  |  |

|                   | and           |              | and     | Only    |  |  |  |  |  |  |

|                   | Delayed       |              | Delayed |         |  |  |  |  |  |  |

| TSA Available?    | No            | No           | Yes     | No      |  |  |  |  |  |  |

| D Port Available? | Yes           | Yes          | Yes     | Yes     |  |  |  |  |  |  |

Note: All Formats: Tx and Rx frames always aligned.

FIGURE 4. D-Port Interface Timing Using DCLK in 16 kHz Mode

TL/H/9151-11

$\label{eq:FIGURE 5-3.} \textbf{FIGURE 5-3. Format 3}$  Shown with example of Time-slot Assignment, and  $\text{FS}_a = \text{FS}_b$

#### FIGURE 5. D-Port Interface Timing Using BCLK

## 7.0 MICROWIRE CONTROL PORT (MW = 1)

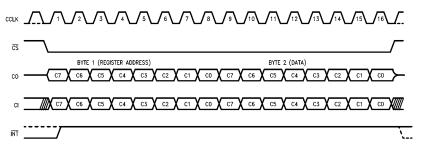

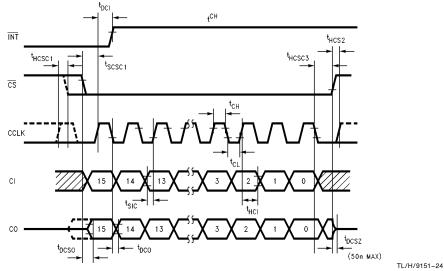

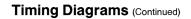

When Format 1, 2, 3 or 4 is used, control information and maintenance channel data is written into and read back from the TP3410 via the Microwire port consisting of the control clock CCLK; the serial data input, CI, and output, CO; the Chip Select input,  $\overline{\text{CS}}$  and the interrupt output  $\overline{\text{INT}}$ . The MW pin must be tied high to enable this port, and the port may be used regardless of whether the device is powered up or down. *Figures 6* and 14 show the timing, which is compatible with the Microwire port on the HPC and COPs families of microcontrollers, and Tables II and III list the control functions and status indicators.

All read and write operations require 2 contiguous bytes. As shown in Tables II and III, the first byte is the register ad-

dress and the second byte is the data byte. Status Registers request service under control of the Interrupt Stack, with the priority order listed in Table III.

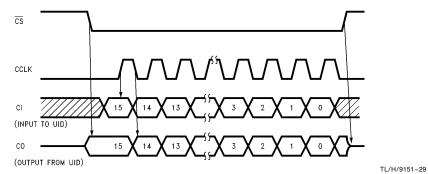

To shift data to and from the TP3410, CCLK must be pulsed high 16 times while  $\overline{\text{CS}}$  is low. Data on the Cl input is shifted into the serial input register on the rising edge of each CCLK pulse; simultaneously, data is shifted out from CO on each falling edge of CCLK. Bit 7 of byte 1 is shifted first.  $\overline{\text{CS}}$  must return high at the end of the 2nd byte, after which the contents of the input shift register are decoded, and the data is loaded into the appropriate programmable register. Pulling  $\overline{\text{CS}}$  low also clears the  $\overline{\text{INT}}$  pin if it was pulled low; if another interrupt condition is queued on the Interrupt Stack it can only pull the  $\overline{\text{INT}}$  pin low when  $\overline{\text{CS}}$  is high. When  $\overline{\text{CS}}$  is high the CO pin is in the high-impedance state, enabling the CO pins of many devices to be multiplexed together.

The TP3410 has an enhanced MICROWIRE port such that it can connect to standard MICROWIRE master devices (such an NSC's HPC and COP families) as well as the SCP (serial control port) interface master from the Motorola micro-controller family. SCP is supported on devices such as MC68302 or the MC145488 HDLC.

TP3410 supports two popular formats used in typical terminal equipment applications.

- 1. CCLK idling LOW when \(\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overline{\overli

- 2. CCLK idling HIGH when \$\overline{CS}\$ pin inactive HIGH, pulsing HIGH/LOW/HIGH for 17 clocks, then returning back to HIGH for idle condition. Data is output on CO pin on the negative edge and data sampled in on the positive edge of CCLK. This format (shown in Figure 14c) is normally used with other alternate microcontrollers in the industry. The first 16 clock pulses are the normal low-going pulses to shift and sample the microwire data. The 17th pulse is generated with software by toggling the CCLK clock polarity bit on the SCP port of MC6302 or MC145488. It is necessary to deactivate the \$\overline{CS}\$ pin (bring it high) while the CCLK is low as shown in Figure 14c.

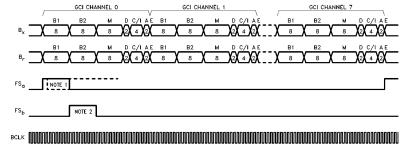

#### 8.0 GCI MODE (MW = 0)