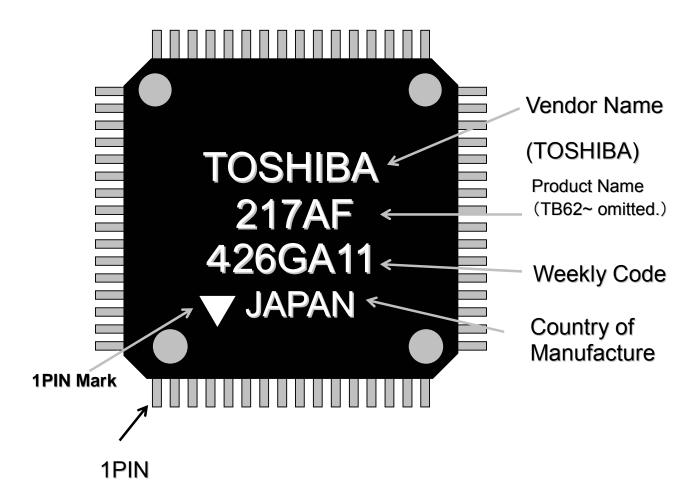

TOSHIBA BiCD Process Integrated Circuit Silicon Monolithic

# **TB62217AFG**

PWM drive Stepping Motor Driver / Brush DC Motor Driver Selectable, DC-DC Converter and Reset function IC

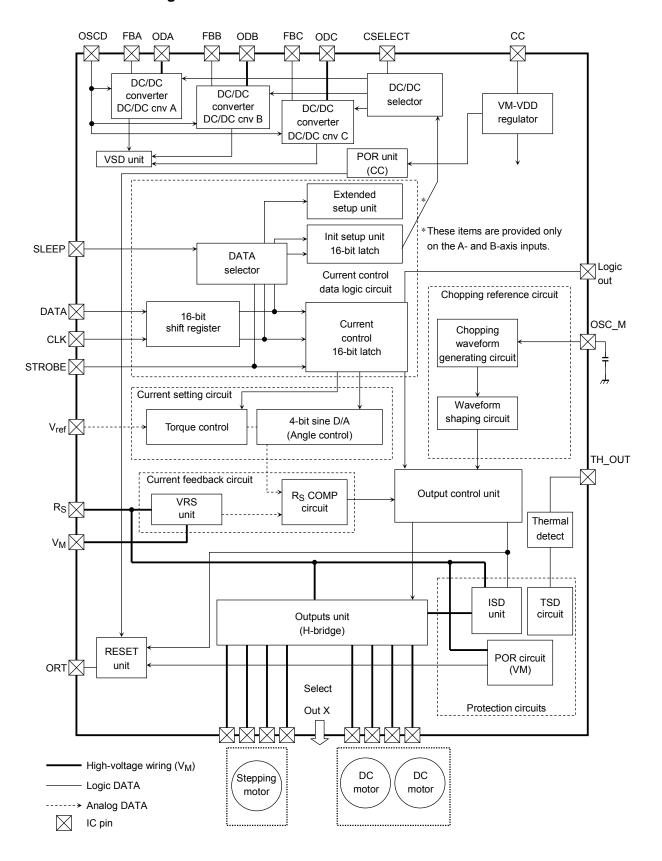

The TB62217AFG is a dual stepping motor driver driven by PWM chopper micro step, with 3- channel step-down DC-DC converters and an external-IC reset function.

To drive a two-phase bipolar-type stepping motor, a 16-bit latch and a 16-bit shift register are built into the IC. The IC is suitable for driving stepping motors with low-torque ripple in a highly efficient manner. In addition, a signal axis can be switched to serve as a PWM driver for two DC motors.

By equipping the stepping motor driver with Selectable Mixed Decay Mode for switching the attenuation ratio during chopping, and also equipping it with a DC-DC converter, it is possible for the IC to supply external voltage.

With a built-in timer that starts running when the IC is supplied with power, the IC can be used in resetting (initializing) external devices.

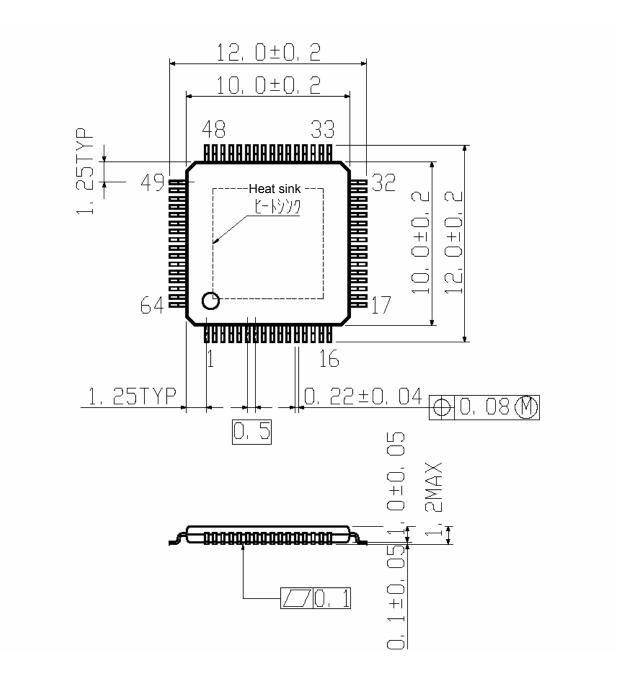

Weight: 0.45 g (typ.)

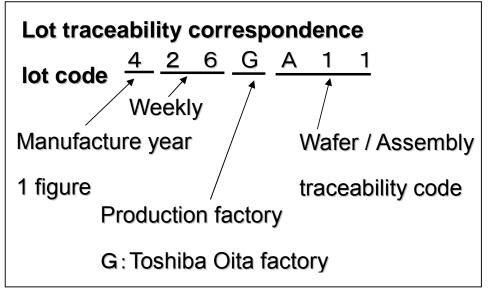

The suffix (G) appended to the part number represents a Lead (Pb) -Free product.

#### **Features**

The following motor combinations can be used.

|     | Stepper DC Large DC (L) |              | DC Small DC (S)  |  |

|-----|-------------------------|--------------|------------------|--|

| (1) | Dual motors             | _            |                  |  |

| (2) | Single motor            | Single motor | _                |  |

| (3) | Single motor            | _            | Dual motors      |  |

| (4) |                         | Single motor | Dual motors      |  |

| (5) |                         | Dual motors  |                  |  |

| (6) | _                       | _            | Quadruple motors |  |

Note Hereafter, DC Large will be referred to as DC (L) and DC Small will be referred to as DC (S).

| Stepping Motor      | 1. OA (MAX)   | (Single Motor) |

|---------------------|---------------|----------------|

| DC Motor Mode       | DC Large      | DC Small       |

| Pulse spike Peak    | 8. 0A (500ns) | 8. 0A (500ns)  |

| Recommended maximum | 3. 0A (100ms) | 2.5A (100ms)   |

| current             |               |                |

| Stationary current  | 0. 8A         | 0. 8A          |

The large current standard is achieved by shorting a small current H-Bridge across two ICs. In addition, if the thermal setting is designed to be within the prescribed thermal range, the initial torque current can be used as the normal operating current.

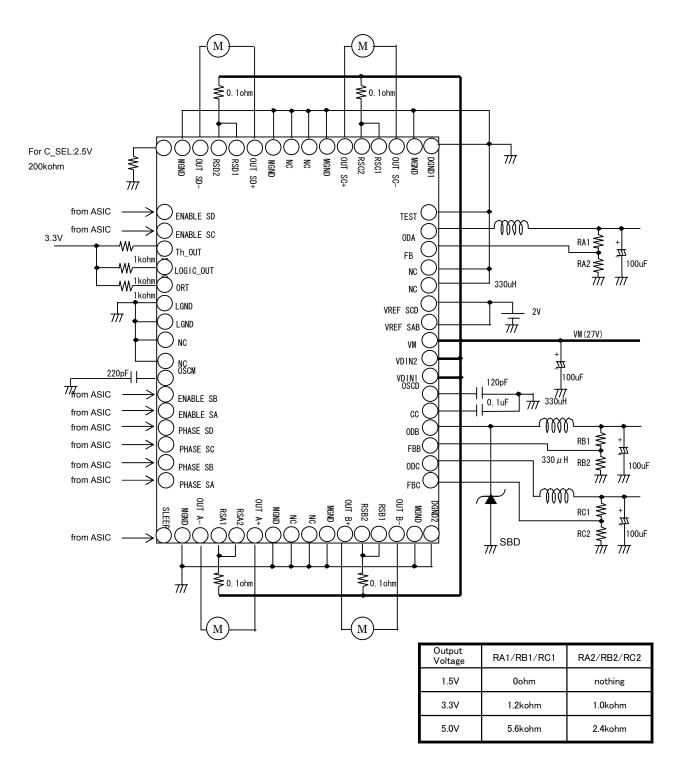

- It is possible to supply external voltage by incorporating three step-down 1.5 V to 5.0 V variable DC-DC converters.

- A Reset function has been added making it possible to deliver an external reset signal.

- The DMOS motor driver output of this monolithic BiCD IC is capable of achieving a low ON resistance of Ron =  $0.6 \Omega$  (@T<sub>j</sub> = 25°C, 0.6A: typ.)

- With two sets of internal 16-bit shift register and latch, the IC can drive stepping motors using a 4-bit micro step.

- Equipped protection circuits: DC-DC converter over current/increased voltage protection, motor over current

protection and total IC over temperature protection.

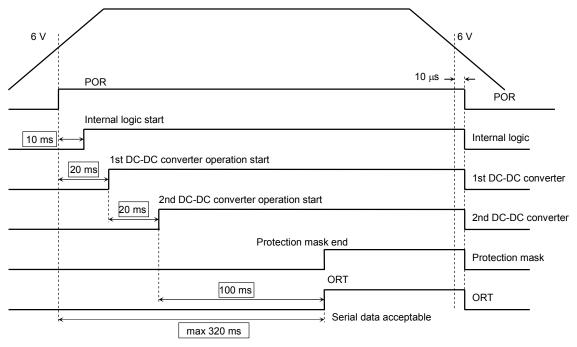

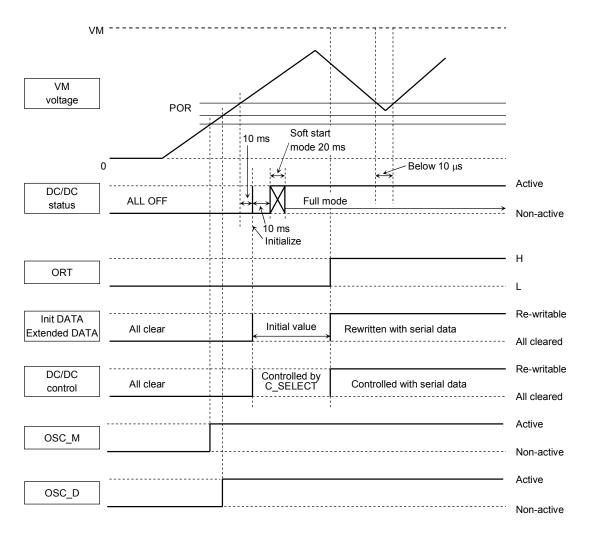

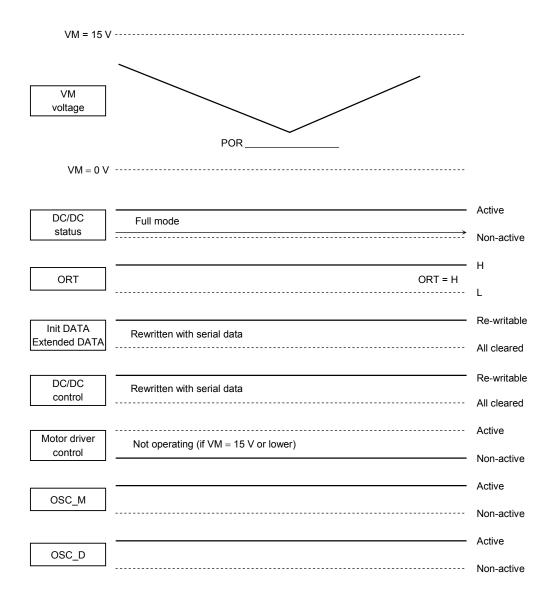

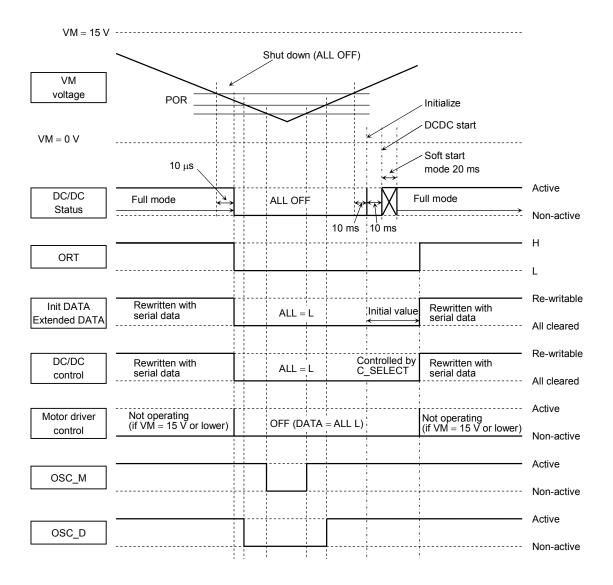

In addition, equipped with Power On Reset circuit for initializing the IC when the power is turned on and off.

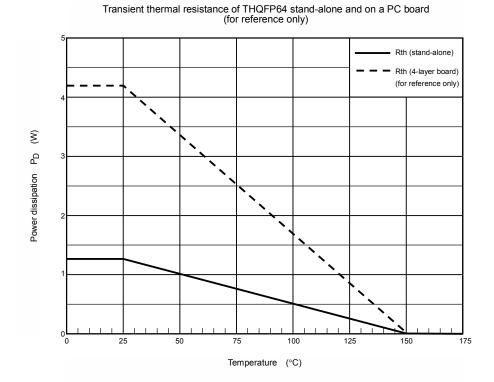

- Package: 64-pin Pb-free QFP package with a heat sink (THQFP64-P-1010-0.50)

- Motor maximum output pressure: 50 V

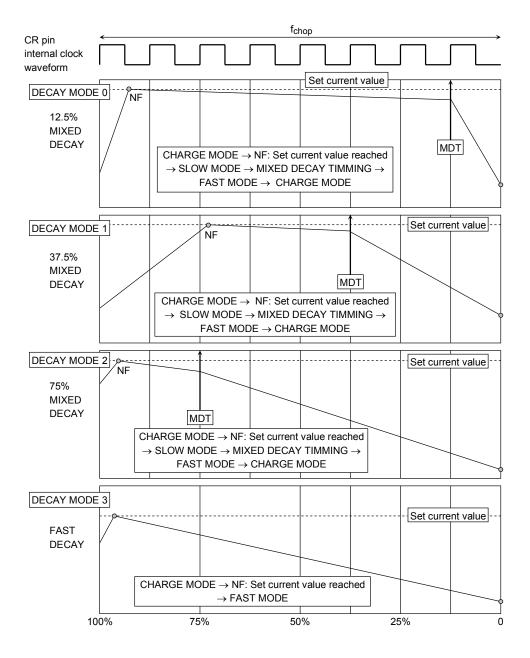

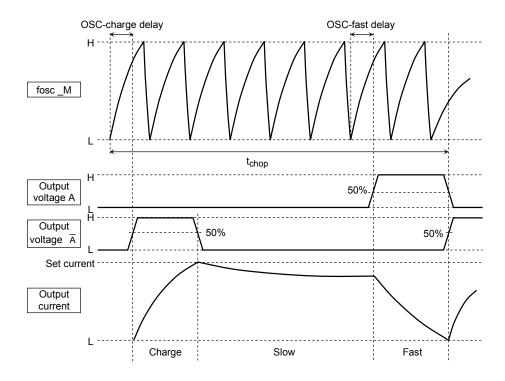

- On-chip Mixed Decay Mode enables specification of four-stage attenuation ratio.

- Chopping frequency can be set by external oscillator. High-speed chopping is possible at 100 kHz or higher.

Note: When using the IC, exercise great care in regard to thermal conditions.

This device is easy damaged by high static voltage (ESD). For this reason, please handle with care.

Please Insert an SBD (Schottky Barrier Diode: Recommended "TSB CRS04") between "ODB" pin and "D-GND" pin, if using C channel.

2

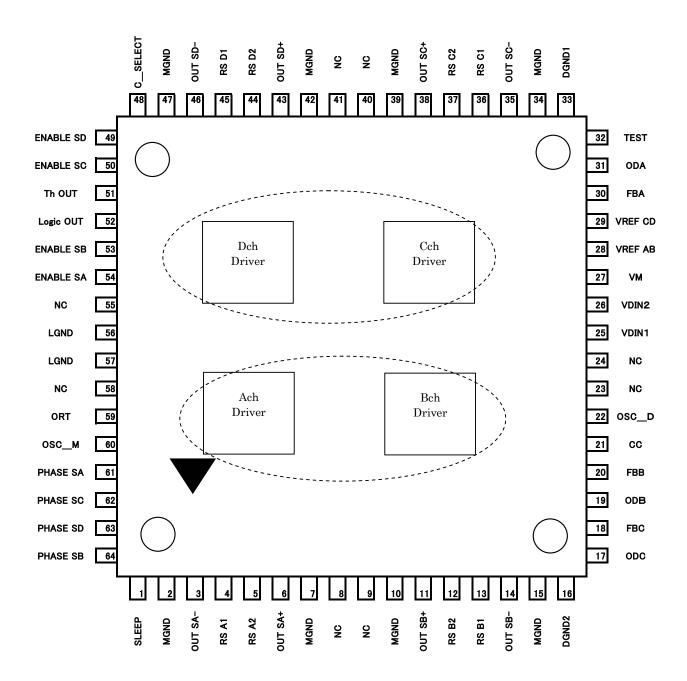

\* Pin Layout (4-channel DC Motor Mode, example)

T-HQFP64-1010-P-0.50

Combinations enclosed in the blue dashed lines are used when in DC (L) mode (A- and B-axis drivers in a pair, and C- and D-axis drivers in a pair).

3 2006-01-20

# Cautions on connection to the IC pins

- Note1 Connect all NC pins (pins left unused) to the lowest potential level (usually to GND).

- Note2 Connect any unused Vref pins (28pin,29pin) to GND.

- Note3 Unused DATA, CLOCK, and STROBE input pins are pulled down internally, so connect them to GND. Please ensure that noise is not introduced into the external circuit

- Note4 Connect any unused RS pins to VM.

- Note5 Connect the feedback pins (FBA, FBB, and FBC) to GND if the corresponding DC-DC converter is

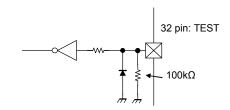

- Note6 Always connect the TEST pin to the lowest potential level (usually to GND).

#### Note7: TEST pin

The TB62217FG has a test mode function for inspection at the factory. The test mode reduces the "initial and normal protection mask time" and "ORT output time" to 1/1024 of the respective ratings so as to make the inspection easier.

To maintain normal operation, therefore, be sure to connect pin 32 to a ground so that it will not be used.

#### Conditions to use the test mode

| Input level | 32                 |

|-------------|--------------------|

| High        | standard operation |

| Low         | TEST Mode          |

- Note 8 If the IC is inserted in an incorrect orientation, it will be damaged because a high voltage is applied to low-voltage blocks. To avoid such damage, always confirm the position of pin 1 and the position and dimensions of each lead when installing the IC.

- Note 9 The IC has no on-chip over voltage protection circuit. Avoid applying a voltage higher than any rated voltage (such as absolute maximum ratinss) to the IC.

- Note 10 Solder the heat sink provided on the bottom surface of the IC to a ground-level pattern arranged for heat release so as to ensure stable operation and efficient heat release.

- Note11 Once set up, since the IC is not affected by a logical input from a "Don't care" pin even if a voltage is applied to the pin, as long as the applied voltage is not higher than its rating, no problem (such as a malfunction) will occur.

# Pin Descriptions (initial setup mode)

SLEEP = Low supports a write mode for the initial setup or extended setup mode data.

- (1) Pin description (SETUP mode, that is, initial setup or extended setup mode)

- (2) Pin description (dual axis stepping motor mode)

- (3) Pin description (single axis stepping motor and single axis DC (L) mode)

- (4) Pin description (single axis stepping motor and dual axis DC (S) mode)

- (5) Pin description (dual axis DC (S) and single axis DC (L) mode)

- (6) Pin description (dual axis DC (L) mode)

- (7) Pin description (quadruple axis DC (S) mode)

## **Pin Name Assignment Table**

| SETUP   STEP   STEP   STEP   DC (L)   Dual DC (L)   Dual DC (L)   Dual DC (L)   Dual DC (L)   Remark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | (1)       | (2)       | (3)       | (4)         | (5)           | (6)         | (7)        |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------|-----------|-----------|-------------|---------------|-------------|------------|--------|

| MODE   Chard   + OC (L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | SETUP     | STEP      | STEP      | STEP+       | DC (L)+       | D 100(1)    | 4   50 (0) |        |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | MODE      | (Dual)    | + DC (L)  | Dual DC (S) | Dual ( DC (S) | Dual DC (L) | 4ch DG (S) | Remark |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1  | SLEEP (L) | SLEEP (H) | SLEEP (H) | SLEEP ( H   | SLEEP ( H     | SLEEP ( H   | SLEEP ( H  |        |

| A   (RS AI)   RS AI   RS AI | 2  | MGND      | MGND      | MGND      | MGND        | MGND          | MGND        | MGND       |        |

| 5         (RS A2)         RS A2         PS B2         P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3  | (OUT A-   | OUT A-    | OUT A-    | OUT A-      | OUT LAB-      | OUT LAB-    | OUT SA-    |        |

| OUT A(+)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4  | (RS A1)   | RS A1     | RS A1     | RS A1       | RS A1         | RS A1       | RS A1      |        |

| MGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5  | (RS A2)   | RS A2     | RS A2     | RS A2       | RS A2         | RS A2       | RS A2      |        |

| 8         NC         NC </td <td>6</td> <td>(OUT A(+)</td> <td>OUT A+</td> <td>OUT A+</td> <td>OUT A+</td> <td>OUT LAB+</td> <td>OUT LAB+</td> <td>OUT SA+</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6  | (OUT A(+) | OUT A+    | OUT A+    | OUT A+      | OUT LAB+      | OUT LAB+    | OUT SA+    |        |

| NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7  | MGND      | MGND      | MGND      | MGND        | MGND          | MGND        | MGND       |        |

| MGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8  | NC        | NC        | NC        | NC          | NC            | NC          | NC         |        |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9  | NC        | NC        | NC        | NC          | NC            | NC          | NC         |        |

| 12         (RS B2)         RS B2         RS B2         RS B2         RS B2         RS B2         RS B2         RS B1         PS B1         DUT LAB-         OUT LAB-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10 | MGND      | MGND      | MGND      | MGND        | MGND          | MGND        | MGND       |        |

| 13         (RS B1)         RS B1         PS B2         PS B3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 | (OUT B+)  | OUT B+    | OUT B+    | OUT B+      | OUT LAB+      | OUT LAB+    | OUT SB+    |        |

| 14         (OUT B-)         OUT B-         OUT B-         OUT B-         OUT LAB-         OUT LAB-         OUT LAB-         OUT SB-           15         MGND         MGND         MGND         MGND         MGND         MGND         MGND           16         DGND2         DGND2         DGND2         DGND2         DGND2         DGND2         DGND2           17         (ODC)         ODC         ODC         ODC         ODC         ODC         ODC           18         (FBC)         FBC         CC         CC         CC <td>12</td> <td>(RS B2)</td> <td>RS B2</td> <td>RS B2</td> <td>RS B2</td> <td>RS B2</td> <td>RS B2</td> <td>RS B2</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12 | (RS B2)   | RS B2     | RS B2     | RS B2       | RS B2         | RS B2       | RS B2      |        |

| 15         MGND         M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13 | (RS B1)   | RS B1     | RS B1     | RS B1       | RS B1         | RS B1       | RS B1      |        |

| 16         DGND2         DGND2         DGND2         DGND2         DGND2         DGND2         DGND2           17         (ODC)         ODC         ODD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14 | (OUT B-)  | OUT B-    | OUT B-    | OUT B-      | OUT LAB-      | OUT LAB-    | OUT SB-    |        |

| 17         (ODC)         ODC         ODC         ODC         ODC         ODC           18         (FBC)         FBC         FBC         FBC         FBC         FBC           19         (ODB)         ODB         ODB         ODB         ODB         ODB           20         (FBB)         FBB         FBB         FBB         FBB         FBB         FBB           21         CC         CC         CC         CC         CC         CC         CC           22         OSC_D         OSC_D <td>15</td> <td>MGND</td> <td>MGND</td> <td>MGND</td> <td>MGND</td> <td>MGND</td> <td>MGND</td> <td>MGND</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15 | MGND      | MGND      | MGND      | MGND        | MGND          | MGND        | MGND       |        |

| 18         (FBC)         FBC         FBB         FBC         CC         CC <td>16</td> <td>DGND2</td> <td>DGND2</td> <td>DGND2</td> <td>DGND2</td> <td>DGND2</td> <td>DGND2</td> <td>DGND2</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 | DGND2     | DGND2     | DGND2     | DGND2       | DGND2         | DGND2       | DGND2      |        |

| 19         (ODB)         ODB         DEX         DEX <td>17</td> <td>(ODC)</td> <td>ODC</td> <td>ODC</td> <td>ODC</td> <td>ODC</td> <td>ODC</td> <td>ODC</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 | (ODC)     | ODC       | ODC       | ODC         | ODC           | ODC         | ODC        |        |

| 20         (FBB)         FBB         FBB <td>18</td> <td>(FBC)</td> <td>FBC</td> <td>FBC</td> <td>FBC</td> <td>FBC</td> <td>FBC</td> <td>FBC</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 | (FBC)     | FBC       | FBC       | FBC         | FBC           | FBC         | FBC        |        |

| 21         CC         CC<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19 | (ODB)     | ODB       | ODB       | ODB         | ODB           | ODB         | ODB        |        |

| 22         OSC_D         OS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 | (FBB)     | FBB       | FBB       | FBB         | FBB           | FBB         | FBB        |        |

| 23         NC         NC<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21 | СС        | CC        | CC        | CC          | СС            | СС          | CC         |        |

| 30         NC         ND         ND<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22 | OSC_D     | OSC_D     | OSC_D     | OSC_D       | OSC_D         | OSC_D       | OSC_D      |        |

| 25         VDIN1         VDIN2         VD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 | NC        | NC        | NC        | NC          | NC            | NC          | NC         |        |

| 26         VDIN2         VDIN2         VDIN2         VDIN2         VDIN2         VDIN2           27         VM         VM         VM         VM         VM         VM         VM           28         (VREF AB)         VREF AB         VREF AB         VREF LAB         VREF LAB         VREF SAB           29         (VREF CD)         VREF CD         VREF SCD         VREF LCD         VREF SCD           30         (FBA)         FBA         FBA         FBA         FBA         FBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 | NC        | NC        | NC        | NC          | NC            | NC          | NC         |        |

| 27         VM         VM<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25 | VDIN1     | VDIN1     | VDIN1     | VDIN1       | VDIN1         | VDIN1       | VDIN1      |        |

| 28 (VREF AB) VREF AB VREF AB VREF LAB VREF LAB VREF LAB VREF SAB 29 (VREF CD) VREF CD VREF LCD VREF SCD VREF LCD VREF SCD 30 (FBA) FBA FBA FBA FBA FBA FBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26 | VDIN2     | VDIN2     | VDIN2     | VDIN2       | VDIN2         | VDIN2       | VDIN2      |        |

| 29 (VREF CD) VREF CD VREF LCD VREF SCD VREF LCD VREF SCD 30 (FBA) FBA FBA FBA FBA FBA FBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27 | VM        | VM        | VM        | VM          | VM            | VM          | VM         |        |

| 30 (FBA) FBA FBA FBA FBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28 | (VREF AB) | VREF AB   | VREF AB   | VREF AB     | VREF LAB      | VREF LAB    | VREF SAB   |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29 | (VREF CD) | VREF CD   | VREF LCD  | VREF SCD    | VREF SCD      | VREF LCD    | VREF SCD   |        |

| 31 (ODA) ODA ODA ODA ODA ODA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30 | (FBA)     | FBA       | FBA       | FBA         | FBA           | FBA         | FBA        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31 | (ODA)     | ODA       | ODA       | ODA         | ODA           | ODA         | ODA        |        |

5 2006-01-20

# **TOSHIBA**

|    | (1)       | (2)       | (3)        | (4)         | (5)           | (6)         | (7)        |                |

|----|-----------|-----------|------------|-------------|---------------|-------------|------------|----------------|

|    | SETUP     | STEP      | STEP       | STEP+       | DC (L)+       | Dual DC (L) | 4ch DC (S) | Domayle        |

|    | MODE      | (Dual)    | + DC (L)   | Dual DC (S) | Dual ( DC (S) | Dual DC (L) | 4ch DC (5) | Remark         |

| 32 | TEST      | TEST      | TEST       | TEST        | TEST          | TEST        | TEST       | Connect to GND |

| 33 | DGND1     | DGND1     | DGND1      | DGND1       | DGND1         | DGND1       | DGND1      |                |

| 34 | MGND      | MGND      | MGND       | MGND        | MGND          | MGND        | MGND       |                |

| 35 | (OUT C-)  | OUT C-    | OUT LCD-   | OUT SC-     | OUT SC-       | OUT LCD-    | OUT SC-    |                |

| 36 | (RS C1)   | RS C1     | RS C1      | RS C1       | RS C1         | RS C1       | RS C1      |                |

| 37 | (RS C2)   | RS C2     | RS C2      | RS C2       | RS C2         | RS C2       | RS C2      |                |

| 38 | (OUT C+)  | OUT C+    | DOUT LC(   | OUT SC(     | OUT SC(       | OUT LCD(    | OUT SC(    |                |

| 39 | MGND      | MGND      | MGND       | MGND        | MGND          | MGND        | MGND       |                |

| 40 | NC        | NC        | NC         | NC          | NC            | NC          | NC         |                |

| 41 | NC        | NC        | NC         | NC          | NC            | NC          | NC         |                |

| 42 | MGND      | MGND      | MGND       | MGND        | MGND          | MGND        | MGND       |                |

| 43 | (OUT D()  | OUT D(    | OUT LCD(   | OUT SD(     | OUT SD+       | OUT LCD+    | OUT SD+    |                |

| 44 | (RSD1)    | RSD1      | RSD1       | RSD1        | RSD1          | RSD1        | RSD1       |                |

| 45 | (RSD2)    | RSD2      | RSD2       | RSD2        | RSD2          | RSD2        | RSD2       |                |

| 46 | OUT D-    | OUT D-    | OUT LCD-   | OUT SD-     | OUT SD-       | OUT LCD-    | OUT SD-    |                |

| 47 | MGND      | MGND      | MGND       | MGND        | MGND          | MGND        | MGND       |                |

| 48 | C_SELECT  | C_SELECT  | C_SELECT   | C_SELECT    | C_SELECT      | C_SELECT    | C_SELECT   |                |

| 49 | -         | -         | -          | ENABLE SD   | ENABLE SD     | -           | ENABLE SD  |                |

| 50 | -         | STROBE CD | ENABLE LCD | ENABLE SC   | ENABLE SC     | ENABLE LCD  | ENABLE SC  |                |

| 51 | TH_OUT    | TH_OUT    | TH_OUT     | TH_OUT      | TH_OUT        | TH_OUT      | TH_OUT     |                |

| 52 | LOGIC OUT | LOGIC OUT | LOGIC OUT  | LOGIC OUT   | LOGIC OUT     | LOGIC OUT   | LOGIC OUT  |                |

| 53 | -         | -         | -          | -           | -             | =           | ENABLE SB  |                |

| 54 | STROBE AB | STROBE AB | STROBE AB  | STROBE AB   | ENABLE LAB    | ENABLE LAB  | ENABLE SA  |                |

| 55 | NC        | NC        | NC         | NC          | NC            | NC          | NC         |                |

| 56 | LGND      | LGND      | LGND       | LGND        | LGND          | LGND        | LGND       | AGND (LGND)    |

| 57 | LGND      | LGND      | LGND       | LGND        | LGND          | LGND        | LGND       | AGND (LGND)    |

| 58 | NC        | NC        | NC         | NC          | NC            | NC          | NC         |                |

| 59 | ORT       | ORT       | ORT        | ORT         | ORT           | ORT         | ORT        |                |

| 60 | OSC_M     | OSC_M     | OSC_M      | OSC_M       | OSC_M         | OSC_M       | OSC_M      |                |

| 61 | -         | DATA CD   | -          | PHASE SD    | PHASE SD      | -           | PHASE SA   |                |

| 62 | -         | CLK CD    | PHASE LCD  | PHASE SC    | PHASE SC      | PHASE LCD   | PHASE SC   |                |

| 63 | DATA AB   | DATA AB   | DATA AB    | DATA AB     | -             | -           | PHASE SD   |                |

| 64 | CLK AB    | CLK AB    | CLK AB     | CLK AB      | PHASE LAB     | PHASE LAB   | PHASE SB   |                |

<sup>-:</sup> Don't care

6 2006-01-20

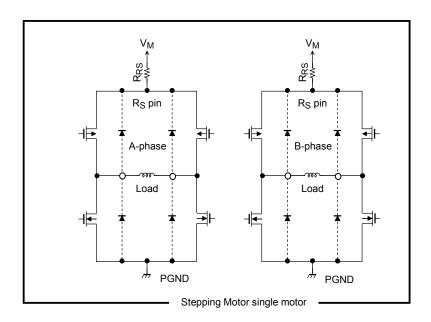

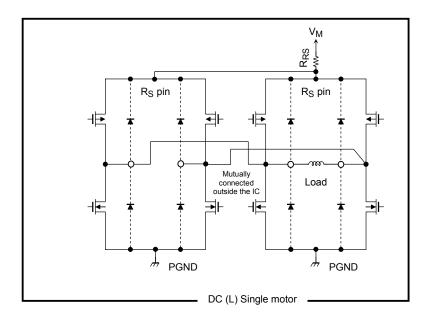

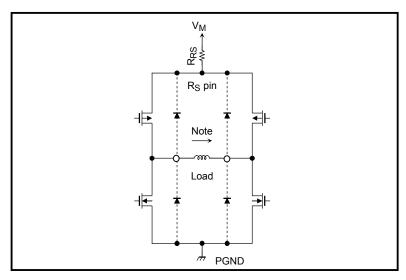

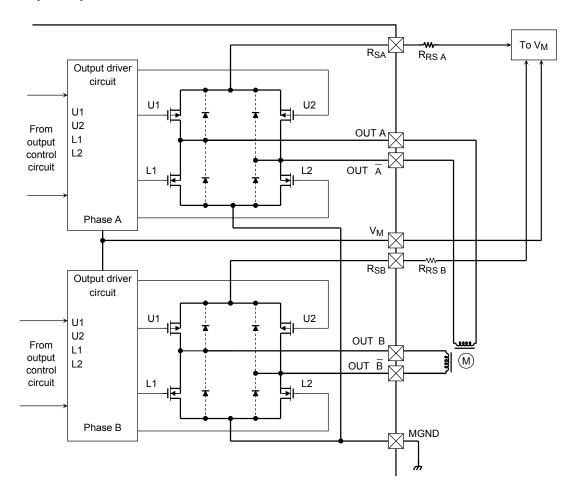

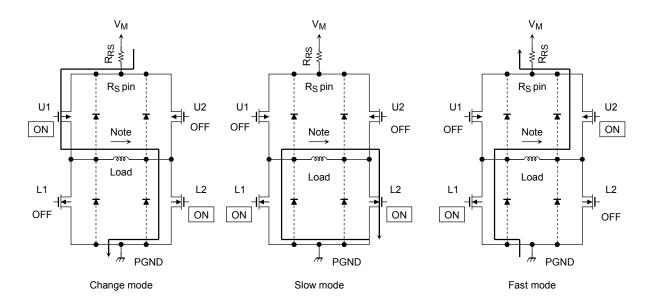

□ Note:H-bridge combination (connection method) for each type of motor driver

O ··· The white circle indicates an IC pin.

Note1: When driving a DC motor in DC (L) mode, avoid an impedance difference outside the IC.

Note2: If the impedance of wiring to mutually connected output transistors is unbalanced, the current that flows through the transistor also becomes unbalanced and may exceed the absolute maximum rating of the transistor, thus damaging the transistor.

7

DC (S) Single motor

O ··· The white circle indicates an IC pin.

# 1. Overall Block Diagram

9 2006-01-20

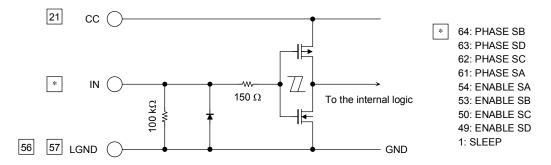

# 2-1. Input Equivalent Circuits

# (1) Logic Input Pin

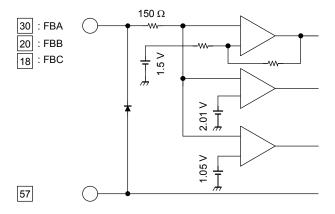

## (2) Vref Input Pin

# (3) DC/DC Feed Back Pin (FBx)

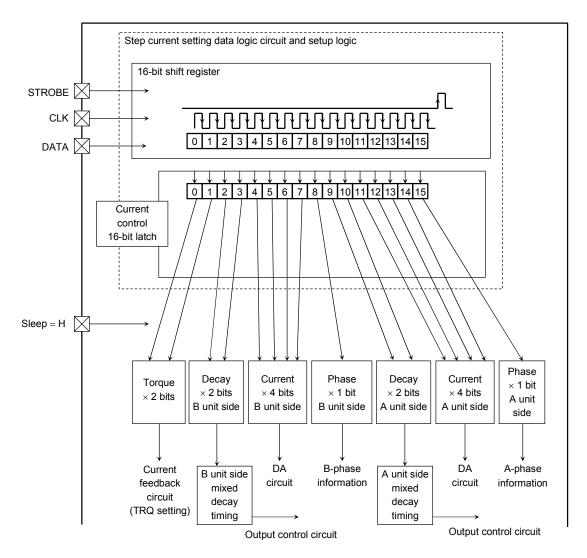

# 2-2. Stepping Motor Logic Unit (with the same functions for both an A-/B-axis pair and a C-/D-axis pair)

#### **Function**

This circuit receives step current setting data entered from the DATA pin and transfers it to the subsequent stage. It is enabled when the SLEEP pin is high. (If the SLEEP pin is low, the IC enters the initial setup or extended setup mode.)

Once ORT is released, driving the SLEEP pin high puts the IC in a write mode for stepping motor current control data. Driving the SLEEP pin from high to low and back to high clears any latched motor control data (to all low).

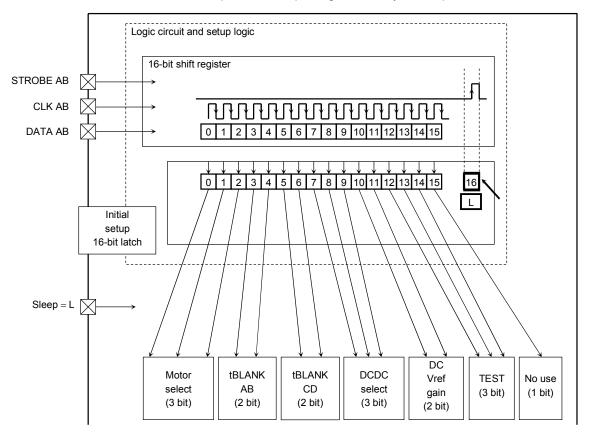

# 2-3. Initial Setup Logic Unit (available only for the A- / B-axis pair)

#### **Function**

This circuit is used to set up driver functions (initial setup) according to signals entered from the DATA pin. The functions that can be set up include motor re-configuration, digital tBLANK, DC-DC converter ON/OFF setting, and DC motor mode Vref (gain) setting.

Note: Do not use the TEST mode. Keep all the corresponding bits and any unused pins at a low level.

Note: The setting entered in initial setup mode is in effect if the DATA signal is low when the STROBE signal is supplied. The initial setup mode data is cleared at POR (power-on reset).

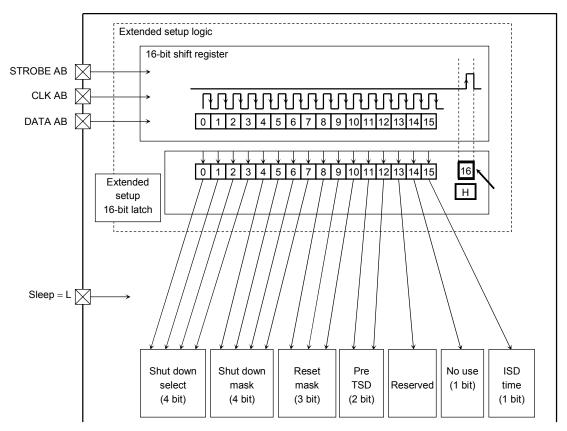

# 2-4. Extended Setup Logic Unit (available only for the A- and B-axis pair)

#### **Function**

This circuit sets up the monitor functions of the driver IC internal circuits according to a signal entered from the DATA pin.

Note: The internal-signal monitoring setting (entered in extended setup mode) is in effect if the DATA signal is high when the STROBE signal is supplied. Data for the extended setup mode is cleared at POR (power-on reset).

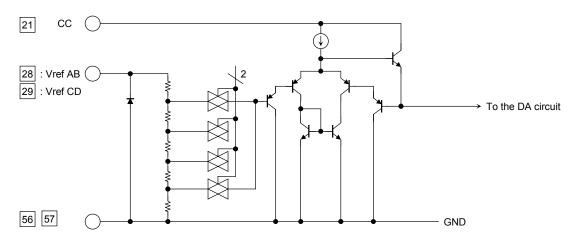

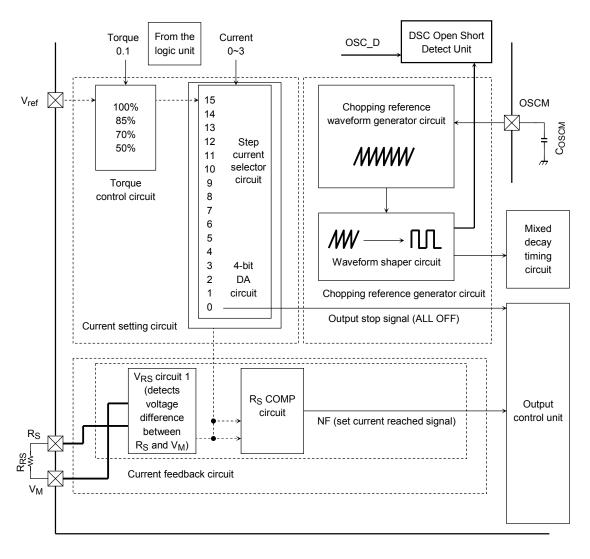

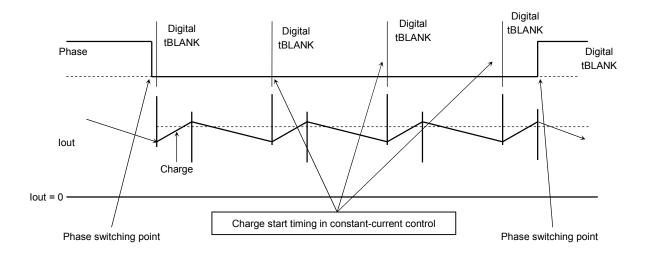

# 3. Current Feedback Circuit and Current Setting Circuit for Motor Driver

#### **Function**

The current setting circuit is used to set the reference voltage of the output current using the step current setting data entered from the serial input pin.

The current feedback circuit is used to deliver a signal to the output control circuit when the output current reaches the set current. This is done by comparing the reference voltage delivered from the current setting circuit with the potential difference generated when current flows through the current sense resistor (RRS) connected between RS and VM.

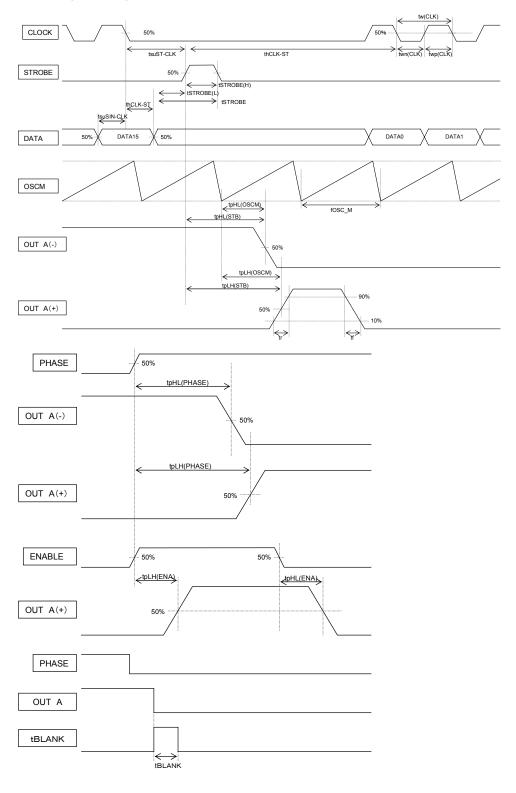

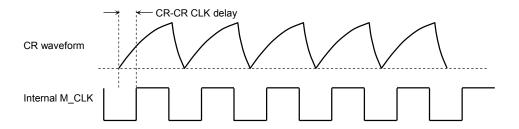

The chopping waveform generator, to which a capacitor is connected, generates the OSC M (OSC-CLK) as a chopping frequency reference.

If the Osc\_M pin becomes open, the open condition detection function works, thus shutting down the IC. If the pin is shorted to GND when the IC starts operating, the detection function also works and the IC does not operate.

Note: The RE COMP circuit compares the set current with the output current and generates a signal when the output current reaches the set current.

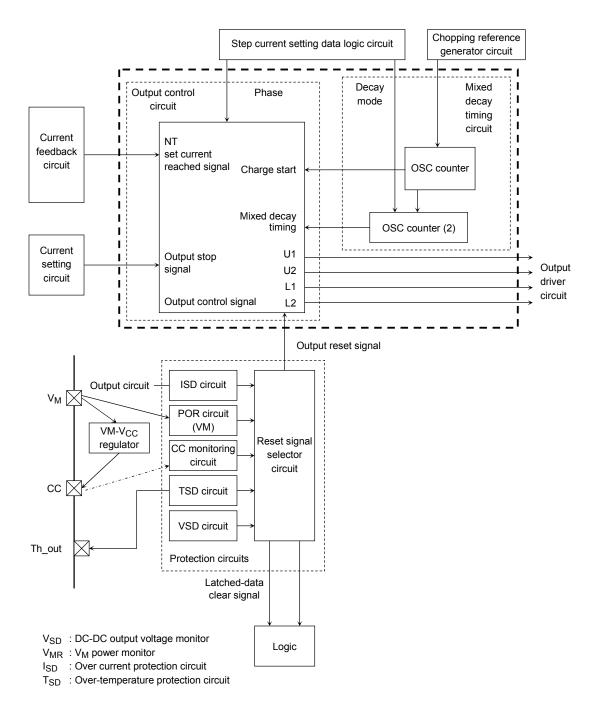

# 4. Output Control Circuit, Current Feedback Circuit, and Current Setting Circuit for Motor Driver

# 5. Output Equivalent Circuit for Motor Driver

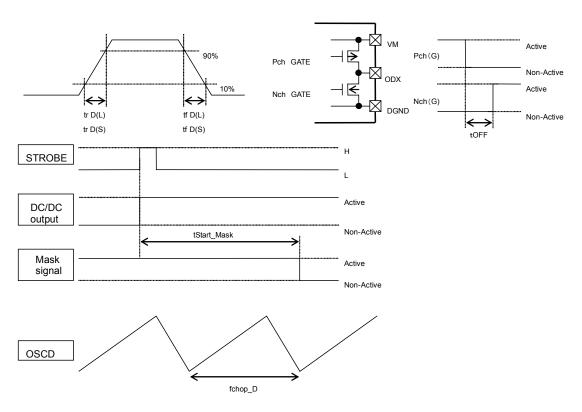

The motor output H switch block consists of the upper P-channel DEMOS FET and lower N-channel DEMOS FET.

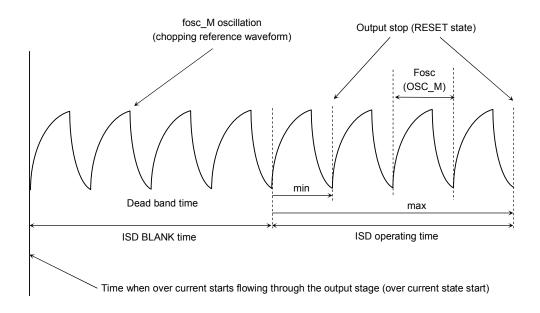

Each output DEMOS FET is connected to an over current sense circuit (ISD detection circuit) in parallel.

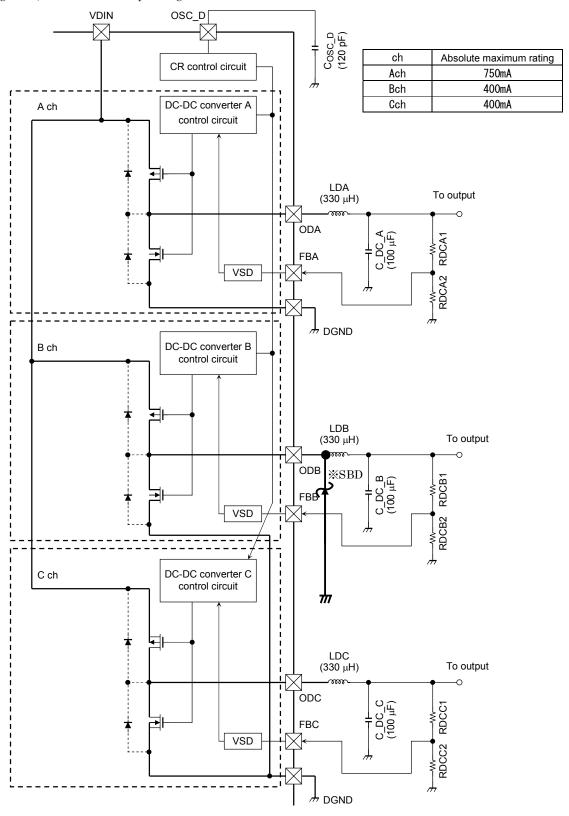

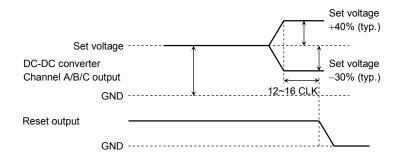

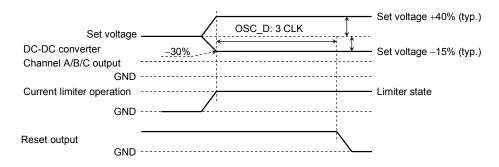

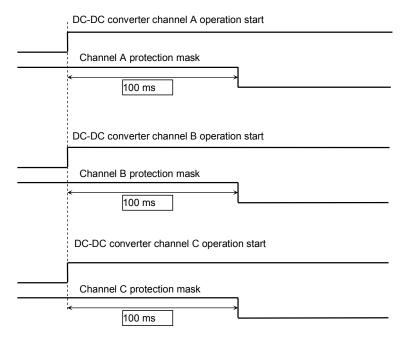

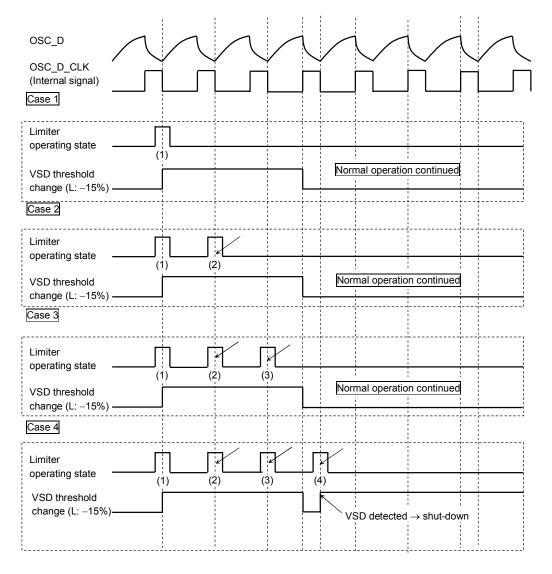

#### 6. DC-DC Converter Circuit

When an open detection circuit is available, Osc\_D pin is set to open, the IC shuts down. If the pin is shorted to GND at startup, the IC fails to start operating. (It does not detect in a default.) In the DC-DC converter operating mode, channel B starts operating before channel A or C.

\*\*Please Insert a SBD( Schottky Barrier Diode : Recommended "TSB CRS04) between "ODB" Pin to "D-GND" pin.

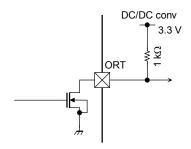

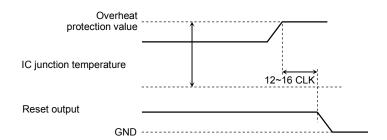

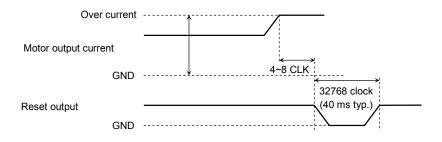

# 7. Reset Circuit (ORT)

This circuit has an open-drain output. If the output is pulled up with a resistor to the supply voltage, its level becomes low (internally on) at reset and high (internally Hi-Z) during normal operation (at a non-reset).

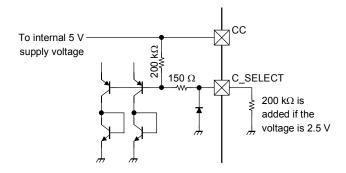

# 8. DC-DC Converter Select Circuit (C\_SELECT)

\*: Each internal circuit resistance varies by ±30%.

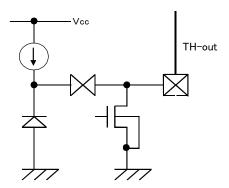

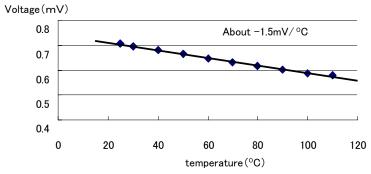

# 9. Set Temperature Detection Output Pin (TH-OUT)

It is not necessary to connect a pull-up resistor when choosing ANALOG output mode (terminal :OPEN)

# 10. Internal Logic Signal Select Output Pin (LOGIC OUT)

Both the TH-OUT and LOGIC OUT circuits have the same open-drain circuit as the ORT circuit. If their output pins are pulled up with a resistor to the supply voltage, their levels become low (internally on) at reset and high (internally Hi-Z) during normal operation (at non-reset).

18

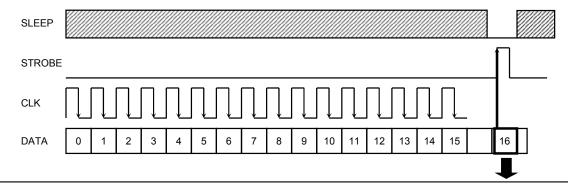

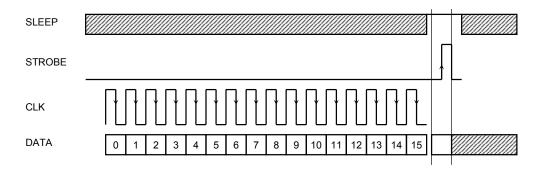

# 16-Bit Serial Input Signals

Three different pieces of data can be entered and set up by combining the CLK, DATA, STROBE and SLEEP pin inputs.

- (1) Extended setup mode (for setting up protection circuits)

- (2) Initial setup mode (for setting up motor drive modes)

- (3) Stepping motor drive mode (normal drive mode)

# Setup Mode Specifications (Initial setup and extended setup modes)

Note: The internal-signal monitoring setting (entered in extended setup mode) is in effect if the DATA signal is high when the STROBE signal is supplied. If the DATA signal is low, initial setup is in effect (initial setup mode).

# (1) Extended Setup Mode Function (write enabled only when SLEEP = L and Setup Select = H)

• In the extended setup mode, the protection circuits are set up and a monitor setup (output of a Lo\_out pin) of a shutdown signal etc. is performed.

| Data Bit | Name                        | Function                                                                               | Setting                                                                                                                                                                                                                          | Default<br>Value |

|----------|-----------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0        | SD SELECT 0                 |                                                                                        |                                                                                                                                                                                                                                  | 0                |

| 1        | SD SELECT 1                 | Selecting a signal at shut-down                                                        | These 4 bits select what shut-down signal to produce.                                                                                                                                                                            | 0                |

| 2        | SD SELECT 2                 | - Selecting a signal at shut-down                                                      | See the next item for explanations about the 4-bit data combinations.                                                                                                                                                            | 0                |

| 3        | SD SELECT 3                 |                                                                                        |                                                                                                                                                                                                                                  | 0                |

| 4        | Unused                      | _                                                                                      | _                                                                                                                                                                                                                                | 0                |

| 5        | DCDC VSD SD MASK            |                                                                                        | 0: Normal operation.                                                                                                                                                                                                             | 0                |

| 6        | Motor ISD SD MASK           | Shut-down signal mask                                                                  | See the corresponding item below for explanations about the 3-bit data                                                                                                                                                           | 0                |

| 7        | TSD SD MASK                 |                                                                                        | combinations.                                                                                                                                                                                                                    | 0                |

| 8        | RESET MASK C                |                                                                                        | 0: Normal operation.                                                                                                                                                                                                             | 0                |

| 9        | RESET MASK B                |                                                                                        | 1: If the DC-DC converter concerned is shut down:                                                                                                                                                                                | 0                |

| 10       | RESET MASK A                | Disabling the RESET signal at the shut-down of the corresponding DC-DC converter.      | (1) The RESET signal is not generated. (2) All DC-DC converters other than the DC-DC converter of interest operate normally. (3) The DC-DC converter concerned returns to normal when the SLEEP signal changes from low to high. | 0                |

| 11       | PRE TSD 0                   |                                                                                        | 12 11 (← bit)                                                                                                                                                                                                                    | 0                |

| 12       | PRE TSD 1                   | Generating a low signal at the Th_out pin at a temperature of the TSD temperature – X. | 0 0: TSD-20°C<br>0 1: TSD-30°C<br>1 0: TSD-40°C<br>1 1: Analog                                                                                                                                                                   | 0                |

| 13       | Unused                      | Unused                                                                                 | _                                                                                                                                                                                                                                | 0                |