# **Quick Start**

## **DEMO AD0801 Demonstration Board for ADC0801S040**

Rev. 0.1 — 24 July 2008

**Quick Start**

#### **Document information**

| Info     | Content                                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------------------|

| Keywords | DEMO AD0801, BSX0046-1, Demonstration board, ADC, Converter, ADC0801S040                                                |

| Abstract | This document describes how to use the demonstration board DEMO AD0801 for the analog-to-digital converter ADC0801S040. |

#### Overview

#### **Revision history**

| Rev | Date     | Description      |

|-----|----------|------------------|

| 0.1 | 20080624 | Initial version. |

#### 1. Quick start

#### 1.1 Setup overview

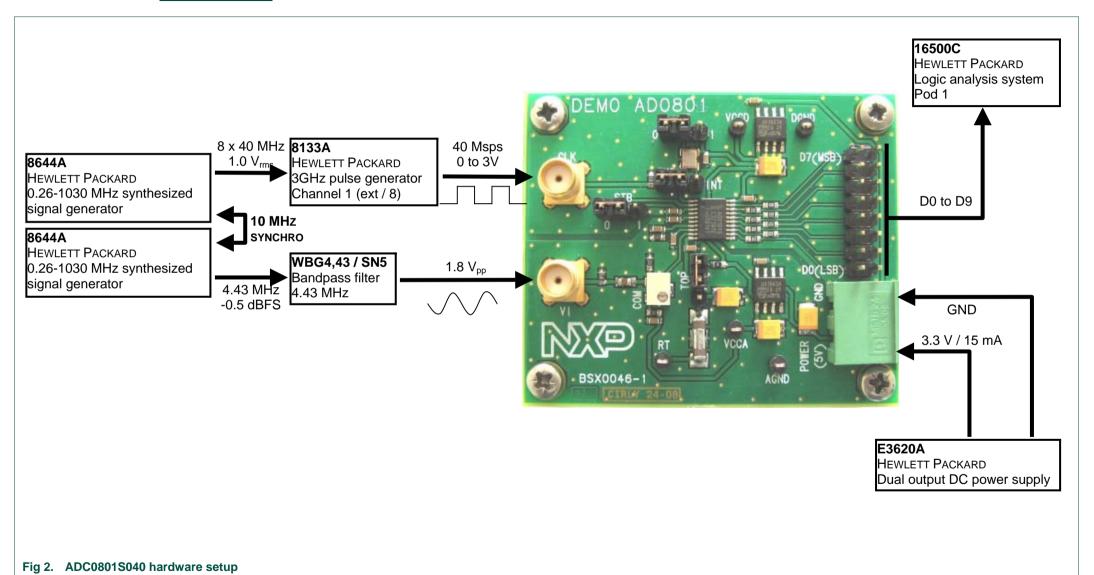

Figure Fig 1 presents the connections to measure DEMO AD0801.

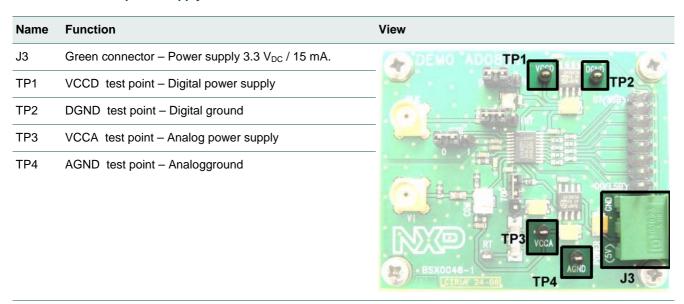

## 1.2 Power supply

The board is powered with a single 3.3  $V_{DC}$  power supply. Two power supply regulators are used to supply all the 3.3V circuitry on the board.

Table 1. General power supply

## 1.3 DC voltage adjustments

Table 2. DC voltage adjustments

| Name | Function                                                           | View                                        |

|------|--------------------------------------------------------------------|---------------------------------------------|

| P1   | COM trimmer – Input signal DC offset adjustment                    | DEMO ADOBO 1                                |

| TP5  | RT connector – External TOP reference adjustment (typ 3.3V V)      |                                             |

| ST4  | TOP switch – Selection between external and on-board TOP reference | P1 ST4  P1 ST4  WOOA  ACHD  EXCEPTION 24-08 |

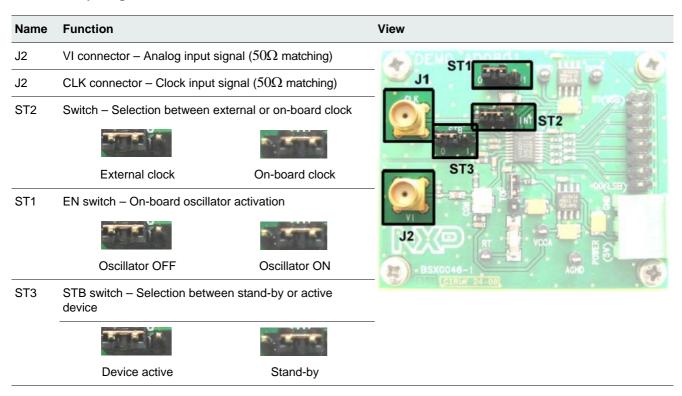

#### 1.4 Input signals (IN, CLK)

To ensure a good evaluation of the device, the input signal and the input clock must be synchronized together.

Moreover, the input frequency (Fi, MHz) and the clock frequency (Fclk, Msps) should follow the formula:

$$\frac{Fi}{Fclk} = \frac{M}{N}$$

,where M is an odd number of period and N is the number of samples.

Table 3. Input signals

#### 1.5 Output signals (D0 to D7)

Table 4. Output signals

| Name | Function                                        | View                                                                                                           |

|------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| J4   | Array connector – ADC digital output (D0 to D7) | DEMO ADOBO  THE JAMES DO(LSB)  DO(LSB)  DO(LSB)  DO(LSB)  DO(LSB)  DO(LSB)  DO(LSB)  DO(LSB)  DO(LSB)  DO(LSB) |

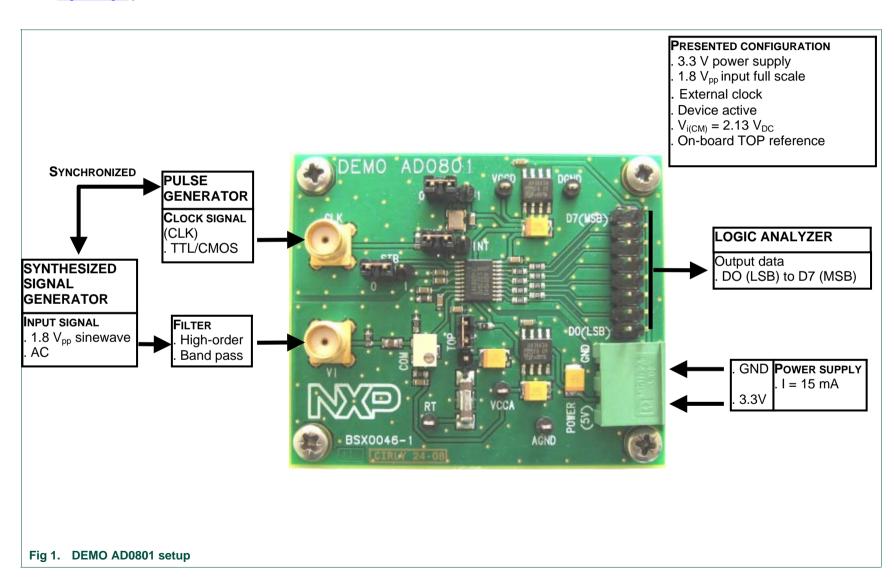

## 2. Example

#### 2.1 Setup example