## **PI3EQX5801**

#### Features

- → PCIe 2.0 compatible

- → Two 5.0Gbps differential signal pairs

- → Adjustable Receiver Equalization

- → 100Ω Differential CML I/O's

- → Pin Configured Output Emphasis and Output Swing Control

- → Input signal level detect and squelch for each channel

- → Automatic Receiver Detect

- → Low Power : ~330mW

- → Industrial Temp Support -40°C~ +85°C

- → Stand-by Mode Power Down State

- → Two power options: 3.3V or 1.5V

- → Packaging: 20-Pin TQFN (4x4mm)

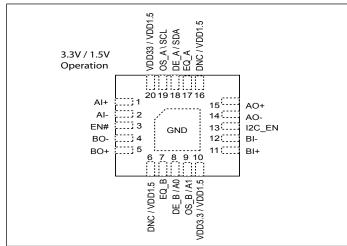

#### Figure 1. Pin Diagram (Top Side View)

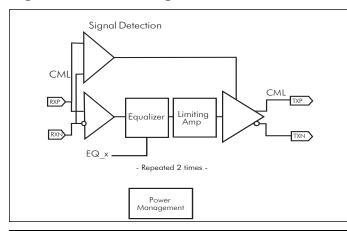

#### Figure 2. Block Diagram

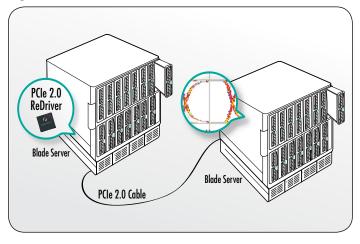

# 5.0Gbps, 1-Lane, PCIe 2.0 ReDriver<sup>™</sup> with I<sup>2</sup>C Programming Interface

#### Description

Pericom Semiconductor's PI3EQX5801 is a low power, high performance 5.0 Gbps signal ReDriver<sup>™</sup> designed specifically for the PCIe 2.0 protocol. The device provides programmable equalization, De-Emphasis, and output swing controls to optimize performance over a variety of physical mediums by reducing Inter-Symbol Interference. PI3EQX5801 supports two 100 $\Omega$  Differential CML data I/O's between the Protocol ASIC to a switch fabric, over cable, or to extend the signals across other distant data pathways on the user's platform. The integrated equalization circuitry provides flexibility with signal integrity of the signal before the ReDriver. A low-level input signal detection and output squelch function is provided for each channel.

When the channels are enabled, EN#=0, and operating, that channels' input signal level (on xI+/-) determines whether the output is active. If the input signal level of the channel falls below the active threshold level (Vth-) then the outputs are driven to the common mode voltage. In addition to signal conditioning, when EN#=1, the device enters alow power standby mode. The PI3EQX5801 also includes a fully programmable I<sup>2</sup>C interface. When I<sup>2</sup>C control mode is enabled, I2C\_EN = 1, equalization, output swing, and de-emphasis settings can be adjusted by programming the related registers.

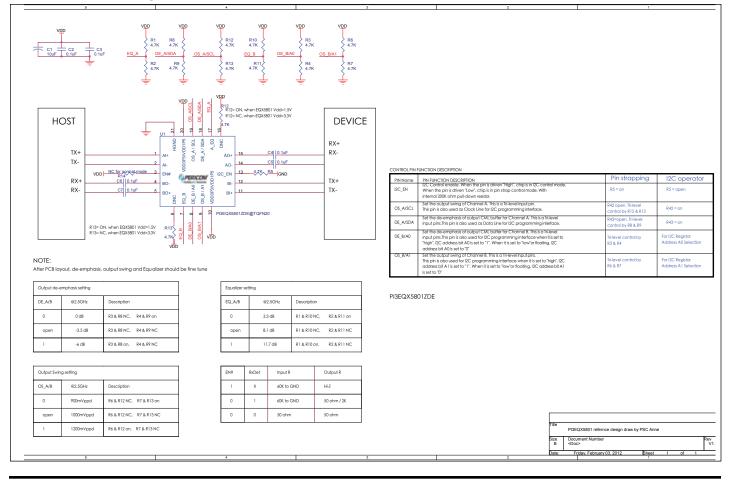

#### Figure 3

## **Pin Description**

| Pin #              | Pin Name                 | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------------------|--------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1<br>2<br>11<br>12 | AI+<br>AI-<br>BI+<br>BI- | Input          | CML input channels with selectable input termination between $50\Omega$ to internal $V_{bias}$ or internal $60k\Omega$ pull-down to GND.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 3                  | EN#                      | Input          | Chip Enable. When the pin is driven "Low", chip is in normal operation. When the pin is driven "High", chip is in power down mode. With internal $200k\Omega$ pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 4<br>5<br>14<br>15 | BO-<br>BO+<br>AO-<br>AO+ | Output         | Selectable output termination between 50 $\Omega$ to internal V <sub>bias</sub> 2k $\Omega$ to internal V <sub>bias</sub> , or Hi-Z.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 6<br>16            | DNC /<br>VDD1.5          | DNC /<br>Power | Do Not Connect / 1.5V Voltage Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 7<br>17            | EQ_B,<br>EQ_A            | Input          | Set the equalization of two channels. These are Tri-level input pins. When set to "HIGH" the pin becomes Logic "1"; when set to "open", the pin becomes "open", when set to "low", the pin becomes logic "0". Please refer to Mode Adjustment on page 3.                                                                                                                                                                                                                                                                                                 |  |  |

| 8                  | DE_B/A0                  | Input          | Set the de-emphasis of the output CML buffer for Channel B. This is a Tri-level input<br>pins When set to "high", the pin becomes logic "1"; when set to "open", the pin becomes<br>"open"; when set to "low", the pin becomes logic "0". Please refer to Mode Adjustment on<br>page 3.<br>This pin is also used for I <sup>2</sup> C programming interface. When set to "high" or floating I <sup>2</sup> C                                                                                                                                             |  |  |

| 9                  | OS_B/A1                  | Input          | <ul> <li>address bit A0 is set to "1". When set to "low" I<sup>2</sup>C address bit A0 is set to "0".</li> <li>Set the output swing of Channel B. This is a Tri-level input pins When set to "HIGH", the pin becomes Logic "1"; when set to "open", the pin becomes "open", when set to "low", the pin becomes logic "0".</li> <li>This pin is also used for I<sup>2</sup>C programming interface. When set to "high" or floating I<sup>2</sup>C address bit A1 is set to "1". When set to "low" I<sup>2</sup>C address bit A1 is set to "0".</li> </ul> |  |  |

| 10<br>20           | VDD3.3 /<br>VDD1.5       | Power          | 3.3V Voltage Supply / 1.5V Voltage Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 13                 | I2C_EN                   | Input          | $I^2C$ Control Enable. When the pin is driven "High", chip is in $I^2C$ Control Mode. When the pin is driven "Low", chip is in pin strap control mode. With internal 200k $\Omega$ pull-down resistor.                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 18                 | DE_A /<br>SDA            | Input          | Set the de-emphasis of the output CML buffer for Channel A. These is a Tri-level input pin. When set to "high", the pin becomes logic "1"; when set to "open", the pin becomes "open"; when set to "low", the pin becomes logic "0". Please refer to Mode Adjustment on page 3.                                                                                                                                                                                                                                                                          |  |  |

|                    |                          |                | This pin is also used as Data Line for I <sup>2</sup> C programming interface 3.3V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 19                 | OS_A/<br>SCL             | Input          | Set the output swing of Channel A. This is a Tri-level input pins When set to "HIGH", the pin becomes Logic "1"; when set to "open", the pin becomes "open", when set to "low", the pin becomes logic "0".                                                                                                                                                                                                                                                                                                                                               |  |  |

| Cont. D.1          |                          |                | This pin is also used as Clock Line for I <sup>2</sup> C programming interface3.3 tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Center Pad         | GND                      | GND            | Supply Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

## **Configuration Table**

| EN# | Function                                         | Input R           | Output R |

|-----|--------------------------------------------------|-------------------|----------|

| 1   | Channels disable if EN# is high, Chip Power Down | $60\Omega$ to GND | Hi-Z     |

| 0   | Chip and channels enabled                        | 50Ω               | 50Ω      |

| I2C_EN | Function                                                                                                 |  |

|--------|----------------------------------------------------------------------------------------------------------|--|

| 1      | I <sup>2</sup> C Mode is enabled when I <sup>2</sup> C_EN pin is pulled up to "1"                        |  |

| 0      | $I^2C$ Mode is disabled and configured in Pin-strap control<br>when $I^2C\_EN$ pin is pulled down to "0" |  |

## **Mode Adjustment**

#### **Equalization Setting through Pin Strap:**

EQ\_A/B are the selection pins for the equalization selection for each direction.

| Equalizer setting |                  |  |  |  |

|-------------------|------------------|--|--|--|

| EQ_A/B            | @ 2.5GHz         |  |  |  |

| 0                 | 3.3 dB           |  |  |  |

| NC                | 8.1 dB (Default) |  |  |  |

| 1                 | 11.7 dB          |  |  |  |

| <b>Equalization Settin</b> | g through I <sup>2</sup> C Pros | gramming Interface: |

|----------------------------|---------------------------------|---------------------|

|                            |                                 | ,                   |

| Equalizer setting           |                  |  |  |  |  |

|-----------------------------|------------------|--|--|--|--|

| A/B_CH Byte Register [7:4]* | @ 2.5GHz         |  |  |  |  |

| 0000                        | 0 dB             |  |  |  |  |

| 0001                        | 3.3 dB           |  |  |  |  |

| 0010                        | 4.5 dB           |  |  |  |  |

| 0011                        | 5.6 dB           |  |  |  |  |

| 0100                        | 6.8 dB           |  |  |  |  |

| 0101                        | 7.4 dB           |  |  |  |  |

| 0110                        | 8.1 dB (Default) |  |  |  |  |

| 0111                        | 8.7 dB           |  |  |  |  |

| 1000                        | 9.3 dB           |  |  |  |  |

| 1001                        | 10 dB            |  |  |  |  |

| 1010                        | 10.8 dB          |  |  |  |  |

| 1011                        | 11.7 dB          |  |  |  |  |

| 1100                        | 12.5 dB          |  |  |  |  |

| 1101                        | 13.3 dB          |  |  |  |  |

| 1110                        | 14.2 dB          |  |  |  |  |

| 1111                        | 15 dB            |  |  |  |  |

**Note:** \*Bits A/B\_CH[3:0] are for other settings, see I<sup>2</sup>C register definition

#### **Output Swing Setting through Pin Strap:**

OS\_A/B are the selection pins for the output swing selection for each direction.

| Output swing setting |                      |  |  |

|----------------------|----------------------|--|--|

| OS_A/B               | Output swing @ 5Gbps |  |  |

| 0                    | 900mVppd             |  |  |

| NC (Default)         | 1000mVppd (Default)  |  |  |

| V <sub>DD</sub>      | 1200mVppd            |  |  |

## Output Swing Setting through I<sup>2</sup>C Programming Interface:

| Output swing setting |                      |  |  |  |

|----------------------|----------------------|--|--|--|

| A/B_CH[3:2]*         | Output swing @ 5Gbps |  |  |  |

| 00                   | 900mVppd             |  |  |  |

| 01                   | 1000mVppd (Default)  |  |  |  |

| 10                   | 1100mVppd            |  |  |  |

| 11                   | 1200mVppd            |  |  |  |

Note: \*Bits A/B\_CH[7:4,1:0] are for other settings, see  $I^2C$  register definition

#### De-emphasis Setting through Pin Strap:

DE\_A/B are the selection pins for the de-emphasis selection for each direction.

| De-emphasis setting |                     |  |  |  |

|---------------------|---------------------|--|--|--|

| DE_A/B              | De-emphasis @ 5Gbps |  |  |  |

| 0                   | 0dB                 |  |  |  |

| NC                  | -3.5dB (Default)    |  |  |  |

| V <sub>DD</sub>     | -6dB                |  |  |  |

## De-emphasis Setting through I<sup>2</sup>C Programming Interface:

| De-emphasis setting |                     |  |  |  |

|---------------------|---------------------|--|--|--|

| A/B_CH[1:0]*        | De-emphasis @ 5Gbps |  |  |  |

| 00                  | 0dB                 |  |  |  |

| 01                  | -2dB                |  |  |  |

| 10                  | -3.5dB (Default)    |  |  |  |

| 11                  | -6dB                |  |  |  |

Note: \*Bits A/B\_CH[7:2] are for other settings, see I<sup>2</sup>C register definition

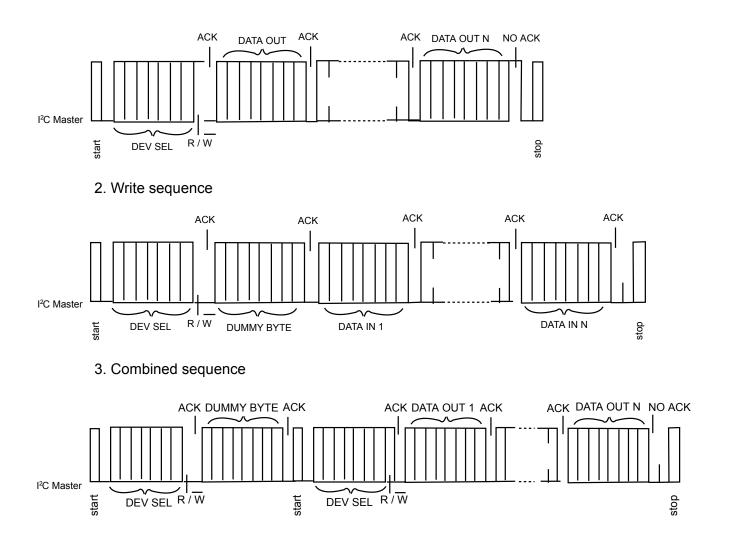

## **Transferring Data**

Every byte put on the SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (see the I<sup>2</sup>C Data Transfer diagram). The PI3EQX5801 will never hold the clock line SCL LOW to force the master into a wait state.

Note: Block-write and Block-read transfers have a fixed offset of 0x00, because of the very small number of configuration bytes. An offset byte presented by a host to the PI3EQX5801 is not used.

## Addressing

Up to four PI3EQX5801 devices can be connected to a single  $I^2C$  bus. The PI3EQX5801 supports 7-bit addressing, with the LSB indicating either a read or write operation. The address for a specific device is determined by the A0 and A1 input pins.

| Address Assignment |                          |   |   |   |         |        |          |  |

|--------------------|--------------------------|---|---|---|---------|--------|----------|--|

| A6                 | A6 A5 A4 A3 A2 A1 A0 R/W |   |   |   |         |        |          |  |

| 1                  | 1                        | 0 | 0 | 0 | Program | nmable | 1=R, 0=W |  |

## Acknowledge

Data transfer with acknowledge is required from the master. When the master releases the SDA line (HIGH) during the acknowledge clock pulse, the PI3EQX5801 will pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse as indicated in the I<sup>2</sup>C Data Transfer diagram. The PI3EQX5801 will generate an acknowledge after each byte has been received.

## Data Transfer

A data transfer cycle begins with the master issuing a start bit. After recognizing a start bit, the PI3EQX5801 will watch the next byte of information for a match with its address setting. When a match is found it will respond with a read or write of data on the following clocks. Each byte must be followed by an acknowledge bit, except for the last byte of a read cycle which ends with a stop bit. For a write cycle, the first data byte following the address byte is a dummy or fill byte that is not used by the PI3EQX5801. This byte is provided to provided compatibility with systems implementing 10-bit addressing. Data is transferred with the most significant bit (MSB) first.

## I<sup>2</sup>C Data Transfer

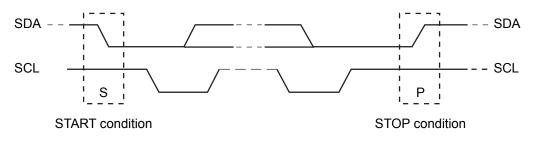

#### Start & Stop Conditions

A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition, as shown in the figure below.

Figure 4. I<sup>2</sup>C START and STOP conditions.

## I<sup>2</sup>C Data Transfer

1. Read sequence

Notes:

1. only block read and block write from the lowest byte are supported for this application.

2. for some I2C application, an offset address byte will be presented at the second byte in write command, which is called dummy byte here and will be simply ignored in this application for correct interoperation.

## **Register Description**

| Bit | Туре | Power-on State | Control Signal | Description                                     |

|-----|------|----------------|----------------|-------------------------------------------------|

| 7   | R/W  | latch from pin | A_EQ[3]        | Controls Equalization setting of CH A           |

| 6   | R/W  | latch from pin | A_EQ[2]        | Default setting is 8.1dB; latched from pin A_EQ |

| 5   | R/W  | latch from pin | A_EQ[1]        |                                                 |

| 4   | R/W  | latch from pin | A_EQ[0]        |                                                 |

| 3   | R/W  | 0              | A_OS[1]        | Controls output swing of CH A.                  |

| 2   | R/W  | 1              | A_OS[0]        | Default setting is 1000mVppd; A_OS[1:0]="01"    |

| 1   | R/W  | 1              | A_DE[1]        | Controls output de-emphasis of CH A             |

| 0   | R/W  | 0              | A_DE[0]        | Default setting is -3.5dB; A_DE[1:0]="10"       |

#### BYTE 0 - Channel A Setting Register (A\_CH[7:0])

#### BYTE 1 - Channel B Setting Register (B\_CH[7:0])

| Bit | Туре | Power-on State | Control Signal | Description                                     |

|-----|------|----------------|----------------|-------------------------------------------------|

| 7   | R/W  | latch from pin | B_EQ[3]        | Controls Equalization setting of CH B           |

| 6   | R/W  | latch from pin | B_EQ[2]        | Default setting is 8.1dB; latched from pin B_EQ |

| 5   | R/W  | latch from pin | B_EQ[1]        |                                                 |

| 4   | R/W  | latch from pin | B_EQ[0]        |                                                 |

| 3   | R/W  | 0              | B_OS[1]        | Controls output swing of CH B                   |

| 2   | R/W  | 1              | B_OS[0]        | Default setting is 1000mVppd; B_OS[1:0]="01"    |

| 1   | R/W  | 1              | B_DE[1]        | Controls output de-emphasis of CH B             |

| 0   | R/W  | 0              | B_DE[0]        | Default setting is -3.5dB; B_DE[1:0]="10"       |

#### BYTE 2 - Global Function Setting Register (GBL\_FUNC[7:0])

| Bit | Туре | Power-on State | Control Signal | Description                      |

|-----|------|----------------|----------------|----------------------------------|

| 7   | R/W  | 1              | TDET_EN        | Termination Detect Enable        |

| 6   | R/W  | 0              | APD_EN         | Auto Slumber Mode Enable         |

| 5   | R/W  | 0              | ADE_EN         | Auto-De-emphasis Enable          |

| 4   | R/W  | 0              | EM_HALF        | Half bit de-emphasis Enable      |

| 3   | R/W  | 0              | UNPLUG_EN      | Unplug detector Enable           |

| 2   | R/W  | 1              | UNPLUG_VTH     | Unplug Detector Threshold        |

| 1   | R/W  | 0              | Reserved       | For normal operation, set to "0" |

| 0   | R/W  | 0              | Reserved       | For normal operation, set to "0" |

| -   |      |                |                |                                                                      |  |  |  |  |

|-----|------|----------------|----------------|----------------------------------------------------------------------|--|--|--|--|

| Bit | Туре | Power-on State | Control Signal | Description                                                          |  |  |  |  |

| 7   | R    | N/A            | TDET_A         | "HIGH" indicates receiver detected at channel A                      |  |  |  |  |

| 6   | R    | N/A            | APD_A          | "HIGH" indicates power saving mode at channel A                      |  |  |  |  |

| 5   | R    | N/A            | SDET_A         | "HIGH" indicates signal detected at channel A                        |  |  |  |  |

| 4   | R    | N/A            | ADE_A          | "HIGH" indicates de-emphasis enable @5Gbps data<br>only at channel A |  |  |  |  |

| 3   | R    | 0              | Reserved       |                                                                      |  |  |  |  |

| 2   | R    | 0              | Reserved       |                                                                      |  |  |  |  |

| 1   | R    | 0              | Reserved       |                                                                      |  |  |  |  |

| 0   | R    | 0              | Reserved       |                                                                      |  |  |  |  |

#### BYTE 3 - Channel A Status Register (A\_STAT[7:0])

#### BYTE 4 - Channel B Status Register (B\_STAT[7:0])

| Bit | Туре | Power-on State | Control Signal Description |                                                                      |  |

|-----|------|----------------|----------------------------|----------------------------------------------------------------------|--|

| 7   | R    | N/A            | TDET_B                     | "HIGH" indicates receiver detected at channel B                      |  |

| 6   | R    | N/A            | APD_B                      | "HIGH" indicates power saving mode at channel B                      |  |

| 5   | R    | N/A            | SDET_B                     | "HIGH" indicates signal detected at channel B                        |  |

| 4   | R    | N/A            | ADE_B                      | "HIGH" indicates de-emphasis enable @5Gbps data<br>only at channel B |  |

| 3   | R    | 0              | Reserved                   |                                                                      |  |

| 2   | R    | 0              | Reserved                   |                                                                      |  |

| 1   | R    | 0              | Reserved                   |                                                                      |  |

| 0   | R    | 0              | Reserved                   |                                                                      |  |

BYTE 5 - RESREVED, Offset = 0x05, Default Power On State = "00010000"

BYTE 6-14 - RESREVED

Note:

#### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                | 65°C to +150°C           |

|------------------------------------|--------------------------|

| Supply Voltage to Ground Potential | 0.5V to +4.6V            |

| DC SIG Voltage                     | $0.5V$ to $V_{DD}$ +0.5V |

| Current Output                     | 25mA to +25mA            |

| Power Dissipation Continuous       | 1W                       |

| Operating Temperature              | -40 to +85°C             |

| ESD, Human Body Model              | 7kv to +7kV              |

| ESD, Machine Model                 | 200V to +200V            |

| ESD, Charged Device Model          | 500V to +500V            |

Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **AC/DC Electrical Characteristics**

| 3.3V Power Supply Characteristics |                              |                                                                     |      |      |      |         |

|-----------------------------------|------------------------------|---------------------------------------------------------------------|------|------|------|---------|

| Symbol                            | Parameter                    | Conditions                                                          | Min. | Тур. | Max. | Units   |

| V <sub>DD33</sub>                 | Power Supply Voltage         |                                                                     | 3.0  |      | 3.6  | V       |

| P <sub>STANDBY33</sub>            | Supply Power Standby         | EN# = 1                                                             |      | 0.18 |      |         |

| P <sub>DEVICE_UNPLUG</sub>        | Supply Power Device Unplug   | EN# = 0, TDET = 0                                                   |      | 7.3  |      | mW      |

| P <sub>ACTIVE33</sub>             | Supply Power Active          | $EN\# = 0, V_{RX-DIFF-P} \ge V_{TH-SD},$<br>Output Swing = 900mVppd |      | 330  |      | 111 V V |

| I <sub>DD-STANDBY33</sub>         | Supply Current Standby       | EN# = 1                                                             |      |      | 0.5  | mA      |

| I <sub>DD-DEVICE_UNPLUG</sub>     | Supply Current Device Unplug | EN# = 0, $TDET = 0$                                                 |      | 2.2  |      |         |

| I <sub>DD-ACTIVE33</sub>          | Supply Current Active        | Output Swing = 900mV <sub>ppd</sub>                                 |      | 100  |      | mA      |

| Symbol                  | Parameter                               | Conditions           | Min. | Тур. | Max. | Units |  |

|-------------------------|-----------------------------------------|----------------------|------|------|------|-------|--|

| t <sub>PD</sub>         | Latency                                 | From input to output |      | 1    | 2    | ns    |  |

| CML Receiver            | Input (100 $\Omega$ Differential)       |                      |      |      |      |       |  |

| Z <sub>RX-DC</sub>      | DC Input Impedance                      |                      | 40   | 50   | 60   |       |  |

| Z <sub>RX-DIFF-DC</sub> | DC Differential Input Impedance         |                      | 80   | 100  | 120  | Ω     |  |

| V <sub>RX-DIFFP-P</sub> | Differential Input Peak-to-peak Voltage |                      | 175  |      | 1200 |       |  |

| V <sub>RX-CM-ACP</sub>  | AC Peak Common Mode Input Voltage       |                      |      |      | 150  | mV    |  |

| V <sub>TH-SD</sub>      | Signal detect Threshold                 | EN# = 0              | 65   |      | 175  | mVppd |  |

| Equalization            |                                         |                      |      |      |      | ·     |  |

| J <sub>RS</sub>         | Residual Jitter <sup>(1,2)</sup>        | Total Jitter         |      |      | 0.3  | Ulp-p |  |

#### AC/DC Electrical Characteristics (Continued..)

Notes

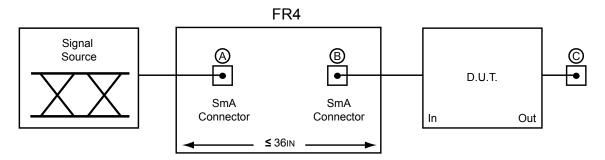

1. K28.7 pattern is applied differentially at point A as shown in Figure 5.

2. Total jitter does not include the signal source jitter. Total jitter (TJ) = (14.1 × RJ + DJ) where RJ is random RMS jitter and DJ is maximum deterministic jitter. Signal source is a K28.5 ± pattern (00 1111 1010 11 0000 0101) for the deterministic jitter test and K28.7 (0011111000) or equivalent for random jitter test. Residual jitter is that which remains after equalizing media-induced losses of the environment of Figure 1 or its equivalent. The deterministic jitter at point B must be from media-induced loss, and not from clock source modulation. Jitter is measured at 0V at point C of Figure 5.

| Symbol                        | Parameter                                                       | Conditions                                                                 | Min.                 | Тур. | Max.                                                 | Units |  |  |

|-------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------|----------------------|------|------------------------------------------------------|-------|--|--|

| CML Transmitter               | CML Transmitter Output (100 $\Omega$ differential) <sup>1</sup> |                                                                            |                      |      |                                                      |       |  |  |

| Z <sub>OUT</sub>              | Output Resistance                                               | Single-Ended                                                               | 40                   | 50   | 60                                                   |       |  |  |

| Z <sub>TX-DIFF-DC</sub>       | DC Differential TX Impedance                                    |                                                                            | 72                   | 100  | 120                                                  | Ω     |  |  |

| V <sub>TX-DIFFP-P</sub>       | Differential Peak-to-peak Output Voltage                        | V <sub>TX-DIFFP-P</sub> = 2 *  <br>V <sub>TX-D+</sub> - V <sub>TX-D-</sub> | 900                  |      | 1200                                                 | mV    |  |  |

| V <sub>TX-C</sub>             | Common-Mode Voltage                                             | $ V_{TX-D+} + V_{TX-D-} /2$                                                | 0.5                  |      | 1.2                                                  | V     |  |  |

| V <sub>cm_ac</sub>            | TX AC common mode voltage                                       |                                                                            |                      |      | 100                                                  | mVpp  |  |  |

| V <sub>TX-Pre-Ratio-max</sub> | Max TX De-emphasis Level                                        |                                                                            |                      |      | -6                                                   | dB    |  |  |

| C <sub>AC</sub> -coupling     | AC coupling capacitor                                           |                                                                            | 75                   |      | 200                                                  | nF    |  |  |

| LVCMOS Control                | Pins (Pins: 3, 13)                                              |                                                                            |                      |      |                                                      |       |  |  |

| V <sub>OL</sub>               | DC Output Logic Low                                             | $I_{OL} = 4mA$                                                             |                      |      | 0.4                                                  |       |  |  |

| V <sub>IH</sub>               | Input High Voltage (Bi-Level)                                   |                                                                            | $0.65 \times V_{DD}$ |      |                                                      | V     |  |  |

| V <sub>IL</sub>               | Input Low Voltage (Bi-Level)                                    |                                                                            |                      |      | $\begin{array}{c} 0.35 \times \\ V_{DD} \end{array}$ |       |  |  |

## AC/DC Electrical Characteristics (Continued..)

#### **AC/DC Electrical Characteristics (Continued..)**

| Symbol                                             | Parameter                      | Conditions | Min.               | Тур. | Max.        | Units |

|----------------------------------------------------|--------------------------------|------------|--------------------|------|-------------|-------|

| Tri-level Control Pins (Pins: 7, 17, 8, 18, 9, 19) |                                |            |                    |      |             |       |

| V <sub>IH</sub>                                    | Input High Voltage (Tri-Level) |            | 0.8V <sub>DD</sub> |      |             | v     |

| V <sub>IL</sub>                                    | Input Low Voltage (Tri-Level)  |            |                    |      | $0.2V_{DD}$ | V     |

| I <sub>IH</sub>                                    | Input High Current             |            |                    |      | 50          | A     |

| I <sub>IL</sub>                                    | Input Low Current              |            | -50                |      |             | μA    |

#### Note:

1. Recommended output coupling capacitor is 75nF to 200nF (on each output)

#### Figure 5. Test Condition Referenced in the Electrical Characteristic Table

11/19/12

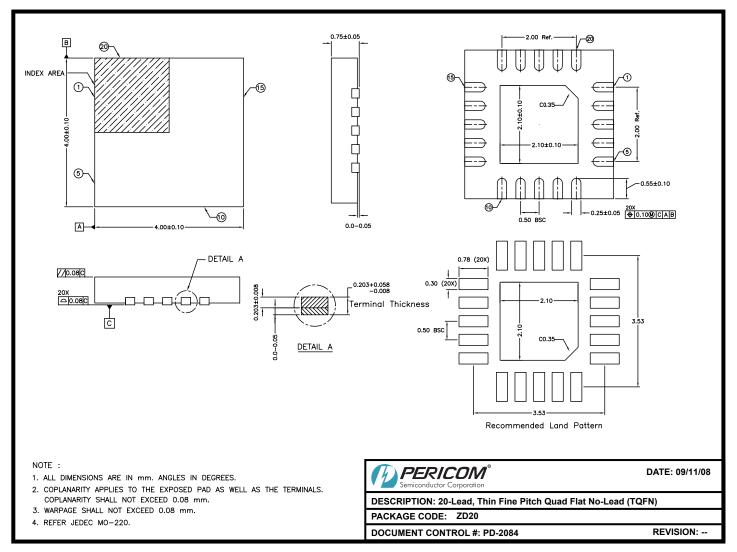

## Packaging Mechanical: 20-contact TQFN (ZD)

#### **Ordering Information**

| Ordering Number | Package Code | Package Description                   |

|-----------------|--------------|---------------------------------------|

| PI3EQX5801ZDE   | ZD           | Pb-Free and Green 20-pin TQFN (4x4mm) |

Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

• X suffix = Tape/Reel