# Lattice **CORE**

PCI Express 2.0 x1, x4 Endpoint IP Core User's Guide

# **Table of Contents**

| Chapter 1. Introduction                                                     | 6    |

|-----------------------------------------------------------------------------|------|

| Quick Facts                                                                 |      |

| Features                                                                    |      |

| PHY Laver                                                                   |      |

| Data Link Layer                                                             |      |

| Transaction Layer                                                           |      |

| Configuration Space Support                                                 |      |

| Top Level IP Support                                                        |      |

| Chapter 2. Functional Description                                           |      |

| Overview                                                                    |      |

| Interface Description                                                       |      |

| Transmit TLP Interface.                                                     |      |

| Receive TLP Interface                                                       |      |

| Using the Transmit and Receive Interfaces                                   |      |

| As a Completer                                                              |      |

| As a Requestor                                                              |      |

| Unsupported Request Generation                                              |      |

|                                                                             |      |

| Configuration Space                                                         |      |

| Base Configuration Type0 Registers<br>Power Management Capability Structure |      |

|                                                                             |      |

| MSI Capability Structure<br>How to Enable/Disable MSI                       |      |

|                                                                             |      |

| How to issue MSI                                                            |      |

| PCI Express Capability Structure                                            |      |

| Device Serial Number Capability Structure                                   |      |

| Advanced Error Reporting Capability Structure                               |      |

| Handling of Configuration Requests                                          |      |

| Wishbone Interface                                                          |      |

| Error Handling                                                              |      |

| Chapter 3. Parameter Settings                                               |      |

| General Tab                                                                 |      |

| PCI Express Link Configuration                                              |      |

| Use Hard LTSSM MACO Block (LatticeSCM Only)                                 |      |

| Include System Bus Interface for PCS Access (LatticeSCM Only)               |      |

| Include Wishbone Interface                                                  |      |

| Endpoint Type                                                               |      |

| PCS Pipe Options Tab                                                        |      |

| Config                                                                      |      |

| Quad Location                                                               |      |

| Physical Layer Tab                                                          |      |

| Include Master Loopback Data Path                                           |      |

| Data Link Layer Tab                                                         |      |

| Update Flow Control Generation Control                                      |      |

| Number of P TLPs Between UpdateFC                                           |      |

| Number of PD TLPs Between UpdateFC                                          |      |

| Number of NP TLPs Between UpdateFC                                          |      |

| Number of NPD TLPs Between UpdateFC                                         |      |

| Worst Case Number of 125MHz Clock Cycles Between UpdateFC                   |      |

| Transaction Layer Tab                                                       | . 52 |

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Include ECRC Support                                      | 52 |

|-----------------------------------------------------------|----|

| Initial Receive Credits                                   | 52 |

| Infinite PH Credits                                       | 52 |

| Initial PH Credits Available                              | 52 |

| Infinite PD Credits                                       | 52 |

| Initial PD Credits Available                              | 52 |

| Initial NPH Credits Available                             | 53 |

| Initial NPD Credits Available                             | 53 |

| Configuration Space Tab                                   | 53 |

| Configuration Space Options                               |    |

| Type 0 Config Space.                                      |    |

| Device ID                                                 |    |

| Vendor ID                                                 | 54 |

| Class Code                                                | 54 |

| Revision ID                                               | 54 |

| BIST                                                      | 54 |

| Header Type                                               | 54 |

| BAR Enable                                                | 54 |

| BAR                                                       | 54 |

| CardBus CIS Pointer                                       | 54 |

| Subsystem ID                                              | 54 |

| Subsystem Vendor ID                                       |    |

| Expansion ROM Enable                                      | 54 |

| Expansion ROM Enable                                      |    |

| Load IDs From Ports                                       |    |

| Power Management Capability Structure                     | 55 |

| Power Management Cap Reg (31:16)                          | 55 |

| Data Scale Multiplier                                     |    |

| Power Consumed in D0, D1, D2, D3                          |    |

| Power Dissipated in D0, D1, D2, D3                        |    |

| Message Signaled Interrupts Capability Structure Options  |    |

| Use Message Signaled Interrupts                           | 55 |

| Number of Messages Requested                              |    |

| PCI Express Capability Structure Options                  |    |

| Next Capability Pointer                                   |    |

| PCIe Capability Version                                   |    |

| Max Payload Size                                          |    |

| Device Capabilities Register (27:3)                       |    |

| Enable Relaxed Ordering                                   |    |

| Maximum Link Width                                        |    |

| Link Capabilities Register (17:10)                        |    |

| Device Serial Number Version                              |    |

| Device Serial Number                                      |    |

| Use Advanced Error Reporting                              |    |

| Advanced Error Reporting Version                          |    |

| Terminate All Config TLPs                                 |    |

| User Extended Capability Structure                        |    |

| Chapter 4. IP Core Generation and Evaluation              |    |

| Licensing the IP Core                                     | 58 |

| Licensing Requirements for LatticeECP2M/LatticeECP3       |    |

| Licensing Requirements for LatticeSCM                     |    |

| Getting Started                                           | 59 |

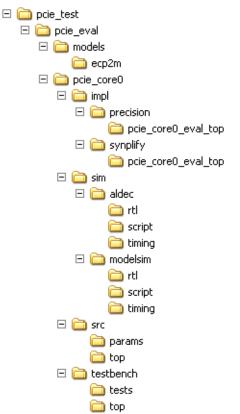

| IPexpress-Created Files and Top Level Directory Structure |    |

| Instantiating the Core                                    | 63 |

| Synthesizing and Implementing the Core in a Top-Level Design                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| Hardware Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

| Enabling Hardware Evaluation in Diamond                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| Enabling Hardware Evaluation in ispLEVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                   |

| Updating/Regenerating the IP Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

| Regenerating an IP Core in Diamond                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   |

| Regenerating an IP Core in ispLEVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

| Chapter 5. Using the IP Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

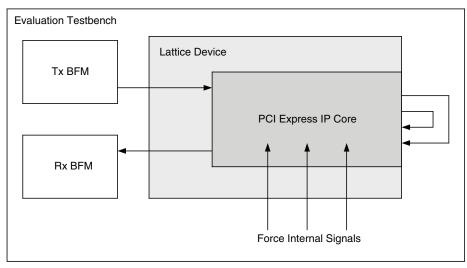

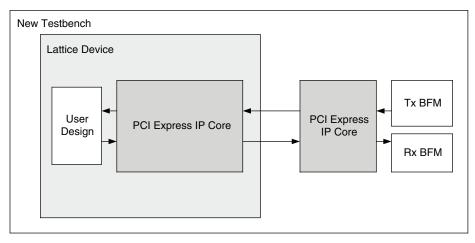

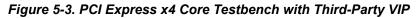

| Simulation and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

| Simulation Strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   |

| Alternative Testbench Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                   |

| Third Party Verification IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

| FPGA Design Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |

| Setting Up the Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

| Setting Design Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |

| LatticeSCM-Specific Preferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| Errors and Warnings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

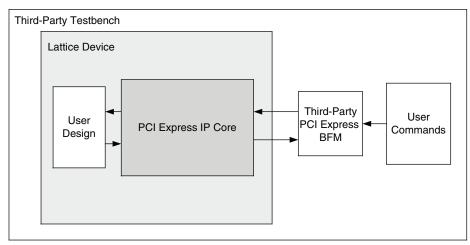

| Clocking Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| Locating the IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| Board-Level Implementation Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                   |

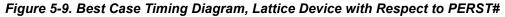

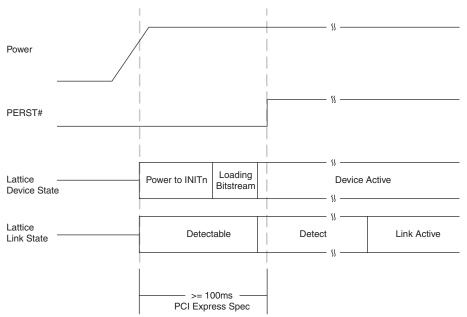

| PCI Express Power-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

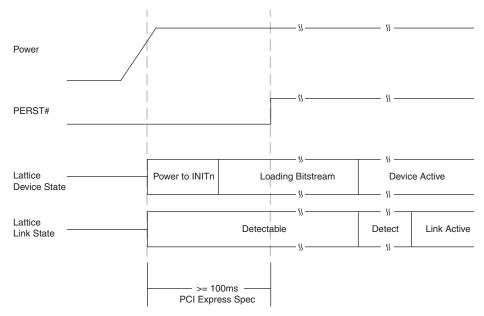

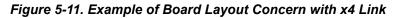

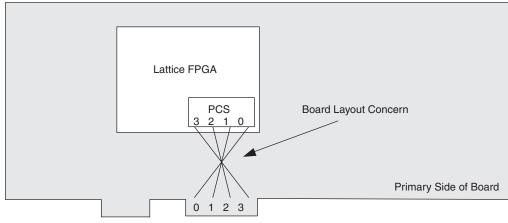

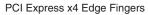

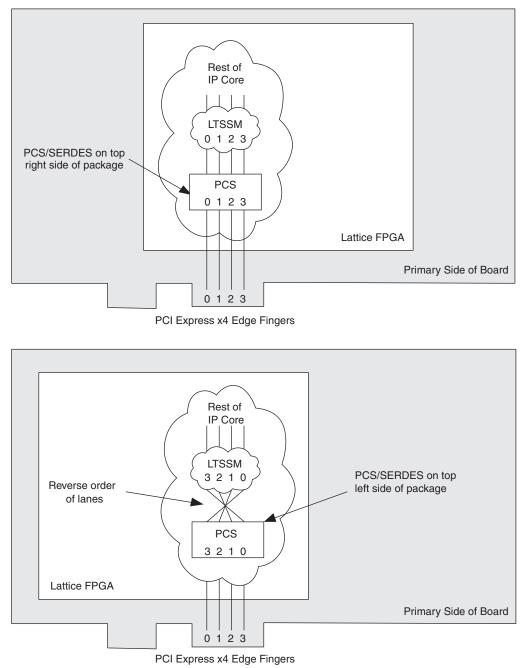

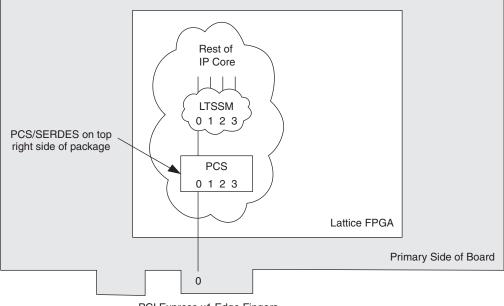

| Board Layout Concerns for Add-in Cards                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                   |

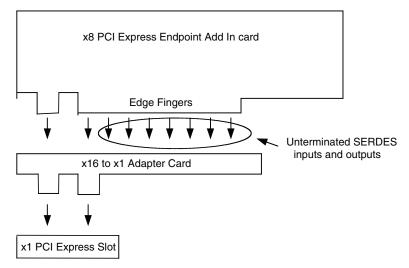

| Adapter Card Concerns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   |

| Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| Chapter 6. Core Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

| Core Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| Chapter 7. Support Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

| Lattice Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                   |

| Online Forums                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

| Telephone Support Hotline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                   |

| E-mail Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                   |

| Local Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 01                                                                                                                                |

| Internet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| Internet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                   |

| Internet<br>PCIe Solutions Web Site                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                   |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3                                                                                                                                                                                                                                                                                                                                                                                                                       | 91<br>91<br>92<br>92<br>92<br>92                                                                                                  |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>LatticeSCM                                                                                                                                                                                                                                                                                                                                                                                         | 91<br>91<br>92<br>92<br>92<br>92<br>92<br>92                                                                                      |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>LatticeSCM<br>Revision History                                                                                                                                                                                                                                                                                                                                                                     | 91<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>93                                                                                |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>LatticeSCM<br>Revision History<br>Appendix A. Resource Utilization                                                                                                                                                                                                                                                                                                                                 | 91<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>93<br><b>94</b>                                                                   |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>LatticeSCM<br>Revision History<br><b>Appendix A. Resource Utilization</b><br>LatticeSCM-15/40/80/115 Utilization                                                                                                                                                                                                                                                                                   | 91<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br>93<br>94                                                              |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>LatticeSCM<br>Revision History<br><b>Appendix A. Resource Utilization</b><br>LatticeSCM-15/40/80/115 Utilization<br>Ordering Part Number                                                                                                                                                                                                                                                           | 91<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br><b>94</b><br>94                                                       |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>LatticeSCM<br>Revision History<br><b>Appendix A. Resource Utilization</b><br>LatticeSCM-15/40/80/115 Utilization<br>Ordering Part Number<br>Configuration                                                                                                                                                                                                                                          | 91<br>91<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br><b>94</b><br>94<br>94<br>94                                                 |

| Internet PCIe Solutions Web Site PCI-SIG Website References LatticeECP3 LatticeECP2M LatticeSCM Revision History Appendix A. Resource Utilization LatticeSCM-15/40/80/115 Utilization Ordering Part Number Configuration LatticeSCM-25 Utilization                                                                                                                                                                                                                                                        | 91<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br><b>94</b><br>94<br>94<br>94<br>95                                                 |

| Internet PCIe Solutions Web Site PCI-SIG Website References LatticeECP3 LatticeECP2M LatticeSCM Revision History Appendix A. Resource Utilization Ordering Part Number Configuration LatticeSCM-25 Utilization Ordering Part Number                                                                                                                                                                                                                                                                       | 91<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br><b>94</b><br>94<br>94<br>94<br>95<br>95                                           |

| Internet.<br>PCIe Solutions Web Site.<br>PCI-SIG Website.<br>References.<br>LatticeECP3.<br>LatticeECP2M.<br>LatticeSCM.<br>Revision History.<br><b>Appendix A. Resource Utilization</b> .<br>LatticeSCM-15/40/80/115 Utilization.<br>Ordering Part Number.<br>Configuration.<br>LatticeSCM-25 Utilization.<br>Ordering Part Number.<br>Configuration.                                                                                                                                                    | 91<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br>93<br>94<br>94<br>94<br>94<br>95<br>95<br>95                                      |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>LatticeSCM<br>Revision History<br><b>Appendix A. Resource Utilization</b><br>LatticeSCM-15/40/80/115 Utilization<br>Ordering Part Number<br>Configuration<br>LatticeSCM-25 Utilization<br>Ordering Part Number<br>Configuration<br>LatticeECP2M Utilization (x1 Endpoint)                                                                                                                          | 91<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br>93<br>93<br>94<br>94<br>94<br>94<br>95<br>95<br>95<br>95<br>96                    |

| Internet.<br>PCIe Solutions Web Site.<br>PCI-SIG Website.<br>References.<br>LatticeECP3.<br>LatticeECP3.<br>LatticeSCM.<br>Revision History.<br><b>Appendix A. Resource Utilization</b><br>LatticeSCM-15/40/80/115 Utilization.<br>Ordering Part Number.<br>Configuration.<br>LatticeSCM-25 Utilization.<br>Ordering Part Number.<br>Configuration.<br>LatticeECP2M Utilization (x1 Endpoint).<br>Ordering Part Number.                                                                                   | 91<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br><b>94</b><br>94<br>94<br>94<br>94<br>95<br>95<br>95<br>95<br>95<br>96<br>96       |

| Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>LatticeSCM<br>Revision History<br><b>Appendix A. Resource Utilization</b><br>LatticeSCM-15/40/80/115 Utilization<br>Ordering Part Number<br>Configuration<br>LatticeSCM-25 Utilization<br>Ordering Part Number<br>Configuration<br>LatticeECP2M Utilization (x1 Endpoint)<br>Ordering Part Number<br>Configuration (x1 Endpoint)<br>Ordering Part Number<br>LatticeECP2M Utilization (x4 Endpoint) | 91<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br>93<br>94<br>94<br>94<br>94<br>94<br>95<br>95<br>95<br>95<br>95<br>95<br>95        |

| Internet.<br>PCIe Solutions Web Site.<br>PCI-SIG Website.<br>References.<br>LatticeECP3.<br>LatticeECP3.<br>LatticeSCM.<br>Revision History.<br><b>Appendix A. Resource Utilization</b><br>LatticeSCM-15/40/80/115 Utilization.<br>Ordering Part Number.<br>Configuration.<br>LatticeSCM-25 Utilization.<br>Ordering Part Number.<br>Configuration.<br>LatticeECP2M Utilization (x1 Endpoint).<br>Ordering Part Number.                                                                                   | 91<br>92<br>92<br>92<br>92<br>93<br>93<br><b>94</b><br>94<br>94<br>94<br>94<br>95<br>95<br>95<br>95<br>95<br>95<br>95<br>95<br>95 |

## **Table of Contents**

| Ordering Part Number                  |  |

|---------------------------------------|--|

| LatticeECP3 Utilization (x4 Endpoint) |  |

| Ordering Part Number                  |  |

PCI Express is a high performance, fully scalable, well defined standard for a wide variety of computing and communications platforms. It has been defined to provide software cPCI Express 2.0 x1, x4 IP Coreompatibility with existing PCI drivers and operating systems. Being a packet based serial technology, PCI Express greatly reduces the number of required pins and simplifies board routing and manufacturing. PCI Express is a point-to-point technology, as opposed to the multidrop bus in PCI. Each PCI Express device has the advantage of full duplex communication with its link partner to greatly increase overall system bandwith. The basic data rate for a single lane is double that of the 32 bit/33 MHz PCI bus. A four lane link has eight times the data rate in each direction of a conventional bus.

Lattice's PCI Express core provides a x1 or x4 endpoint solution from the electrical SERDES interface to the transaction layer. This solution supports the LatticeECP3<sup>™</sup>, LatticeECP2M<sup>™</sup> and LatticeSCM<sup>™</sup> FPGA device families. The LatticeSCM PCI Express core utilizes Lattice's unique MACO<sup>™</sup> technology to support the data link layer using the flexiMAC<sup>™</sup> MACO core and the portions of the PHY layer using the LTSSM MACO core. The Lattice MACO technology is only available on the LatticeSCM family of the devices. When used with the LatticeECP3<sup>™</sup> and LatticeECP2M families, the PCI Express core is implemented using an extremely economical and high value FPGA platform.

This user's guide covers three versions of the Lattice PCI Express core:

- The Native PCI Express x4 Core targets the LatticeECP3, LatticeECP2M and LatticeSCM families of devices.

- The **x4 Downgraded x1 Core** also targets the LatticeECP3, LatticeECP2M and LatticeSCM families. The x4 Downgraded x1 core is a x4 core that has three channels powered down to create a x1 core. This is designed for users who wish to use a 64-bit datapath with a x1 link width.

- The Native PCI Express x1 Core is only available in the LatticeECP3 and LatticeECP2M families. This is a reduced LUT count x1 core with a 16-bit datapath.

Refer to Lattice's PCIe Solutions web site at:

http://www.latticesemi.com/solutions/technologysolutions/pciexpresssolutions.cfm?source=topnav

for links to the following documents, solutions, and IP related to the PCI Express IP core:

- LatticeECP3 PCI Express Development Kit and LatticeECP2M PCI Express Development Kit

- LatticeECP2M PCI Express Solutions Board and LatticeECP3 PCI Express Solutions Board (contained in the Development Kits listed above)

- LatticeSC PCI Express x4 Evaluation Board

- PCI Express Endpoint IP Core Demo for LatticeECP3, LatticeECP2M and LatticeSCM

- Lattice Scatter-Gather Direct Memory Access (DMA) Controller IP Core

# **Quick Facts**

Table 1-1 gives quick facts about the Lattice PCI Express IP core.

#### Table 1-1. PCI Express IP Core Quick Facts

|                         |                                    | PCI Express IP Configuration                                             |                                                              |                           |                      |                                                     |                                                     |  |  |

|-------------------------|------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|----------------------|-----------------------------------------------------|-----------------------------------------------------|--|--|

|                         |                                    | =                                                                        | t1<br>point                                                  | x<br>Endp                 |                      | x4<br>Endpoint,<br>Soft<br>LTSSM <sup>1, 2, 3</sup> | x4<br>Endpoint,<br>Hard<br>LTSSM <sup>1, 2, 3</sup> |  |  |

| Core                    | FPGA Families Supported            | La                                                                       | tticeECP2M a                                                 | and LatticeEC             | P3                   | LatticeSCM                                          |                                                     |  |  |

| Requirements            | Minimal Device Needed <sup>4</sup> | LFE3-17E-<br>7FN484C                                                     | LFE2M-20E-<br>6F484C                                         | LFE3-70E-<br>7FN672C      | LFE2M-50E-<br>6F672C | LFSC3GA15E<br>-6F900C                               | LFSC3GA15E<br>-6F900C                               |  |  |

|                         | Targeted Device                    | LFE3-17E-<br>7FN484C                                                     | LFE2M-20E-<br>6F484C                                         | LFE3-70E-<br>7FN672C      | LFE2M-50E-<br>6F672C | LFSC3GA25E<br>-6FC1020C                             | LFSC3GA80E<br>-6FC1704C                             |  |  |

| Typical                 | Data Path Width                    | 16                                                                       | 16                                                           | 64                        | 64                   | 64                                                  | 64                                                  |  |  |

| Resource<br>Utilization | LUTs                               | 6100                                                                     | 6000                                                         | 12100                     | 12200                | 8200                                                | 4700                                                |  |  |

| otilization             | sysMEM EBRs                        | 4                                                                        | 4                                                            | 11                        | 11                   | 13                                                  | 13                                                  |  |  |

|                         | Registers                          | 4000                                                                     | 4100                                                         | 9800                      | 9600                 | 6100                                                | 4700                                                |  |  |

|                         | Lattice Implementation             |                                                                          | Lattice D                                                    | Diamond™ 1.               | or ispLEVE           | R <sup>®</sup> 8.1 SP1                              |                                                     |  |  |

|                         | Curthopia                          | Synopsys <sup>®</sup> Synplify <sup>®</sup> Pro for Lattice D-2009.12L-1 |                                                              |                           |                      |                                                     |                                                     |  |  |

| Design Tool             | Synthesis                          | Mentor Graphics <sup>®</sup> Precision <sup>®</sup> RTL                  |                                                              |                           |                      |                                                     |                                                     |  |  |

| Support <sup>5</sup>    |                                    | ŀ                                                                        | Aldec Active-H                                               | IDL <sup>®</sup> 8.2 (Win | dows only, Ve        | erilog and VHD                                      | DL)                                                 |  |  |

|                         | Simulation                         |                                                                          | Mentor Graphics ModelSim <sup>®</sup> SE 6.5F (Verilog Only) |                           |                      |                                                     |                                                     |  |  |

|                         |                                    |                                                                          | Ca                                                           | dence® NC-V               | erilog® (Linux       | only)                                               |                                                     |  |  |

1. When the x4 cores downgrades to x1 mode, utilization and performance results for x1 are identical to x4 mode for LatticeECP2M, LatticeECP3, and LatticeSCM families.

2. LTSSM MACO is available in LFSC3GA15/40/80/115 devices. LTSSM MACO not available in LFSC3GA25; soft LTSSM is required.

3. Resource utilization and performance results for x1 and x4 mode are identical in LatticeSCM devices.

4. The packages specified in the Minimal Device Needed row relate to the many user interface signals implemented as I/Os in the evaluation design. Depending on the application, it might be possible to implement a design in a package with fewer I/O pins since the majority of the user interface signals are terminated inside the FPGA.

5. Design tool support for IP core version 4.1.

# Features

The Lattice PCI Express IP core supports the following features.

## **PHY Layer**

- 2.5 Gbps CML electrical interface

- PCI Express 1.1 electrical compliance for the LatticeECP2M and LatticeSCM families, and 2.0 electrical compliance for the LatticeECP3 family

- Many options for signal integrity including differential output voltage, transmit pre-emphasis and receiver equalization

- · Serialization and de-serialization

- 8b10b symbol encoding/decoding

- Data scrambling and de-scrambling

- · Link state machine for symbol alignment

- Clock tolerance compensation supports +/- 300 ppm

- · Framing and application of symbols to lanes

- Data scrambling

- Lane-to-lane de-skew

- Link Training and Status State Machine (LTSSM)

- Electrical idle generation

- Receiver detection

- TS1/TS2 generation/detection

- Lane polarity inversion

- Link width negotiation

- Higher layer control to jump to defined states

- MACO-based LTSSM available in the following LatticeSCM devices: LFSCM15, LFSCM40, LFSCM80, and LFSCM115

## **Data Link Layer**

- Data link control and management state machine

- Flow control initialization

- Ack/Nak DLLP generation/termination

- Power management DLLP generation/termination through simple user interface

- LCRC generation/checking

- Sequence number appending/checking/removing

- Retry buffer and management

#### **Transaction Layer**

- Supports all types of TLPs (memory, I/O, configuration and message)

- · Power management user interface to easily send and receive power messages

- Optional ECRC generation/checking

- 128, 256, 512, 1 k, 2 k, or 4 kbyte maximum payload size

## **Configuration Space Support**

- PCI-compatible Type 0 Configuration Space Registers contained inside the core (0x0-0x3C)

- PCI Express Capability Structure Registers contained inside the core

- Power Management Capability Structure Registers contained inside the core

- MSI Capability Structure Registers contained inside the core

- Device Serial Number Capability Structure contained inside the core

- Advanced Error Reporting Capability Structure contained inside the core

## **Top Level IP Support**

- 125 MHz user interface

- Native x4 and Downgraded x1 support a 64-bit datapath

- Native x1 supports a 16-bit datapath

- In transmit, user creates TLPs without ECRC, LCRC, or sequence number

- In receive, user receives valid TLPs without ECRC, LCRC, or sequence number

- Credit interface for transmit and receive for PH, PD, NPH, NPD, CPLH, CPLD credit types

- Upstream/downstream, single function endpoint topology

- Higher layer control of LTSSM via ports

- · Access to select configuration space information via ports

This chapter provides a functional description of the Lattice PCI Express Endpoint IP core.

# Overview

The PCI Express core is implemented in several different FPGA technologies. These technologies include soft FPGA fabric elements such as LUTs, registers, embedded block RAMs (EBRs), embedded hard elements with the PCS/SERDES, and Lattice's unique MACO technology (LatticeSCM family only).

The IPexpress<sup>™</sup> design tool is used to customize and create a complete IP module for the user to instantiate in a design. Inside the module created by the IPexpress tool are several blocks implemented in heterogeneous technologies. All of the connectivity is provided, allowing the user to interact at the top level of the IP core.

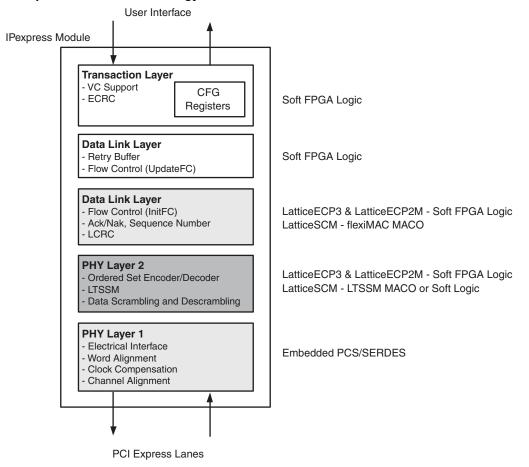

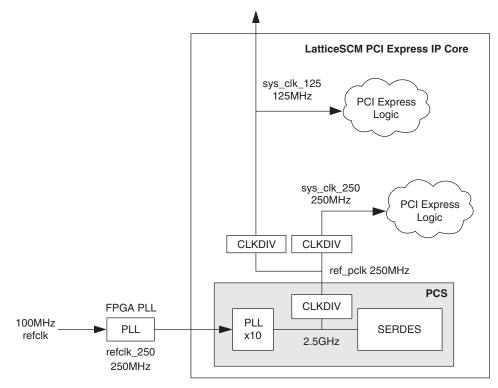

Figure 2-1 provides a high-level block diagram to illustrate the main functional blocks and the technology used to implement PCI Express functions.

#### Figure 2-1. PCI Express IP Core Technology and Functions

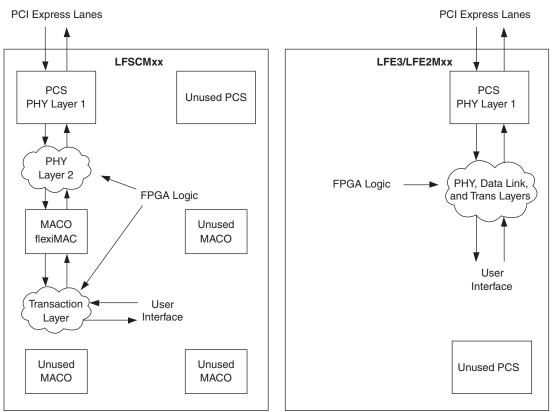

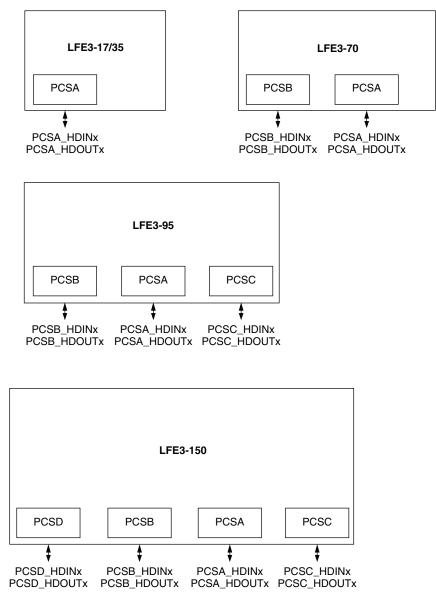

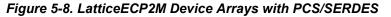

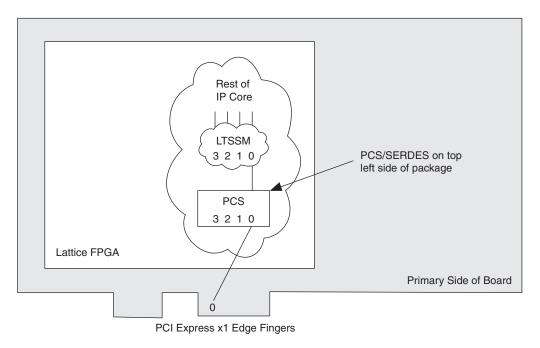

As the PCI Express core proceeds through the Diamond or ispLEVER software design flow specific technologies are targeted to their specific locations on the device. Figure 2-2 provides implementation representations of the LFSCMxx and LFE3/LFE2Mxx devices with a PCI Express core.

As shown, the data flow moves in and out of the heterogeneous FPGA technology. The user is responsible for selecting the location of the hard blocks (this topic will be discussed later in this document). The FPGA logic placement and routing is the job of the Diamond or ispLEVER design tools to select regions nearby the hard blocks to achieve the timing goals.

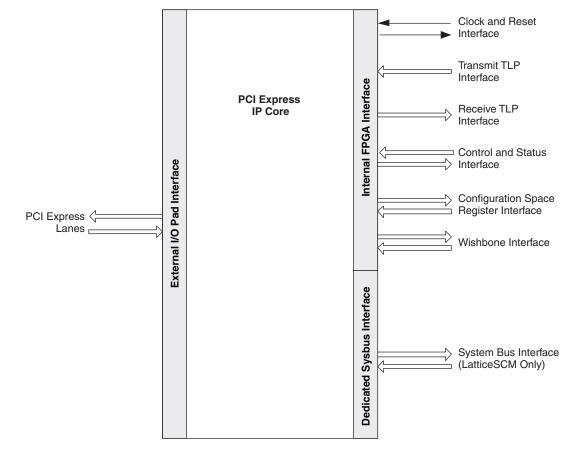

Figure 2-3 provides a high-level interface representation.

#### Figure 2-3. PCI Express Interfaces

Table 2-1 provides the list of ports and descriptions for the PCI Express IP core.

#### Table 2-1. PCI Express IP Core Port List

| Port Name                                          | Direction | Clock | Description                                                                                                                                                                                                                  |

|----------------------------------------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock and Reset Interface                          |           |       |                                                                                                                                                                                                                              |

| refclk[p,n] (LatticeECP3 and<br>LatticeECP2M only) | Input     |       | 100 MHz PCI Express differential reference clock used to generate the 2.5 Gbps data.                                                                                                                                         |

|                                                    |           |       | 250 MHz reference clock to the Physical Layer. This clock input must use a primary clock route to reduce SERDES transmit jitter.                                                                                             |

| refclk_250 (LatticeSCM only)                       | Input     |       | For the LatticeSCM device, a FPGA-based PLL is used to synthesize the PCI Express reference clock to the 250 MHz required for this port. This topic is covered in the Clocking Scheme section of this document.              |

| sys_clk_125                                        | Output    |       | 125 MHz clock derived from refclk to be used in the user application.                                                                                                                                                        |

| rst_n                                              | Input     |       | Active-low asynchronous datapath and state machine<br>reset. This port will be connected to the GSR for the entire<br>device. This reset is pulsed after bitstream download and<br>will not need to be asserted by the user. |

| Port Name                     | Direction | Clock       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| serdes_rst (Lattice SCM only) | Input     |             | Active-high asynchronous SERDES PLL reset. This resets<br>the SERDES. The serdes_rst can be tied low. This is not<br>required unless the refclk changes or stops. This is typically<br>not the case in most systems.                                                                                                                                                                                                                                                                                                                                                               |

| rx_rst (LatticeSCM only)      | Input     |             | Active-high asynchronous receive PHY layer reset. This reset only resets the PCS/SERDES receive datapath. The rx_rst must be toggled after the PCS multi-channel aligner settings have changed. The uML reference design provided and documented in "Resource Utilization" on page 94 produces this signal.                                                                                                                                                                                                                                                                        |

| clk_50 (LatticeSCM only)      | Input     |             | Control plane clock used by the flexiMAC. This clock can run up to 50MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PCI Express Lanes             | • • • • • |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| hdin[p,n]_[0,1,2,3]           | Input     |             | PCI Express 2.5 Gbps CML inputs for lanes 0,1,2, and 3.<br>The port "flip_lanes" is used to define the connection of<br>PCS/SERDES channel to PCI Express lane.<br>flip_lanes=0<br>hdin[p,n]_0 - PCI Express Lane 0<br>hdin[p,n]_1 - PCI Express Lane 1<br>hdin[p,n]_2 - PCI Express Lane 2<br>hdin[p,n]_3 - PCI Express Lane 3<br>flip_lanes=1<br>hdin[p,n]_0 - PCI Express Lane 3<br>hdin[p,n]_1 - PCI Express Lane 3<br>hdin[p,n]_2 - PCI Express Lane 3<br>hdin[p,n]_2 - PCI Express Lane 3<br>hdin[p,n]_3 - PCI Express Lane 3                                                |

| hdout[p,n]_[0,1,2,3]          | Output    |             | PCI Express 2.5 Gbps CML outputs for lanes 0,1,2, and 3.<br>The port "flip_lanes" is used to define the connection of<br>PCS/SERDES channel to PCI Express lane.<br>flip_lanes=0<br>hdout[p,n]_0 - PCI Express Lane 0<br>hdout[p,n]_1 - PCI Express Lane 1<br>hdout[p,n]_2 - PCI Express Lane 2<br>hdout[p,n]_3 - PCI Express Lane 3<br>flip_lanes=1<br>hdout[p,n]_0 - PCI Express Lane 3<br>hdout[p,n]_2 - PCI Express Lane 2<br>hdout[p,n]_2 - PCI Express Lane 3<br>hdout[p,n]_2 - PCI Express Lane 1<br>hdout[p,n]_3 - PCI Express Lane 1<br>hdout[p,n]_3 - PCI Express Lane 0 |

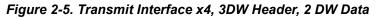

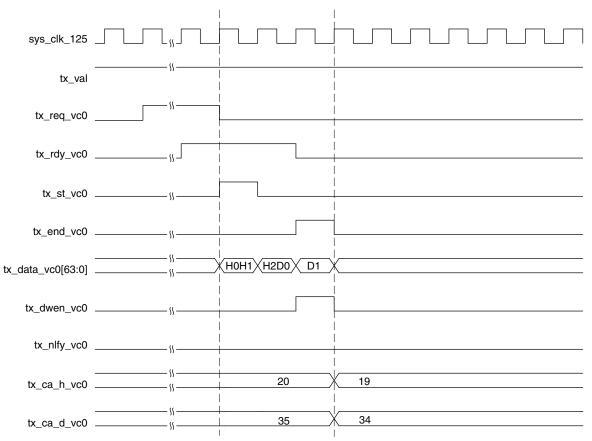

| Transmit TLP Interface        |           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| tx_data_vc0[n:0]              | Input     | sys_clk_125 | Native x4 and Downgraded x1 Transmit data bus<br>[63:56] Byte N<br>[55:48] Byte N+1<br>[47:40] Byte N+2<br>[39:32] Byte N+3<br>[31:24] Byte N+4<br>[23:16] Byte N+5<br>[15: 8] Byte N+5<br>[15: 8] Byte N+6<br>[7: 0] Byte N+7<br>Native x1 Transmit data bus<br>[15:8] Byte N<br>[7:0] Byte N+1                                                                                                                                                                                                                                                                                   |

| Port Name                     | Direction | Clock       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

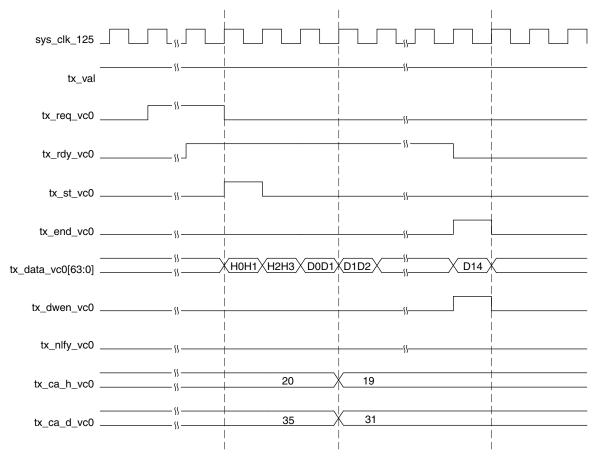

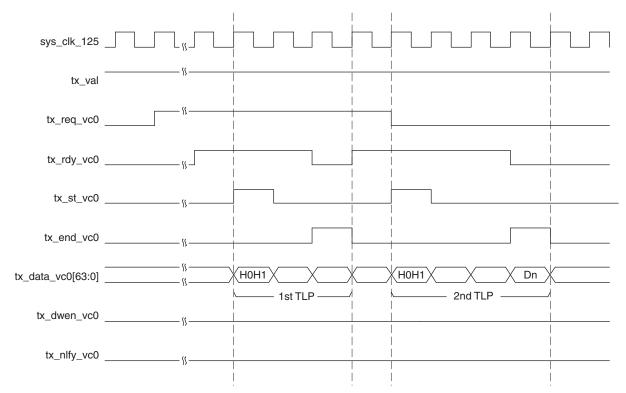

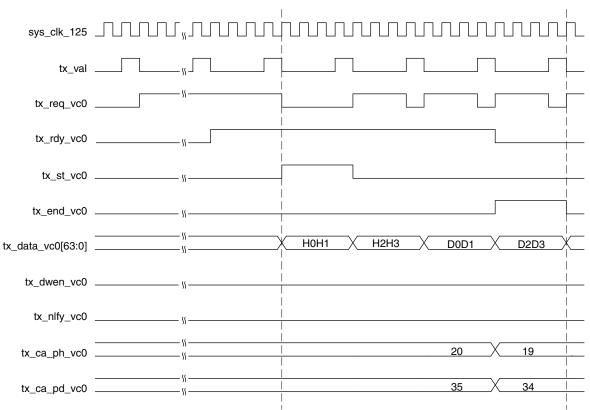

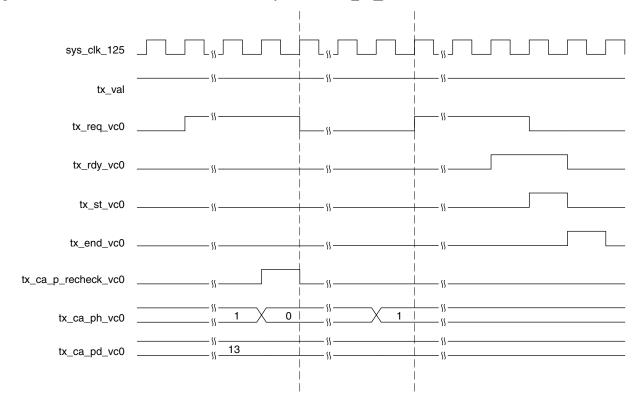

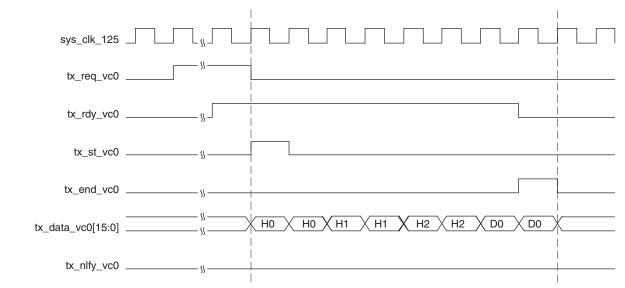

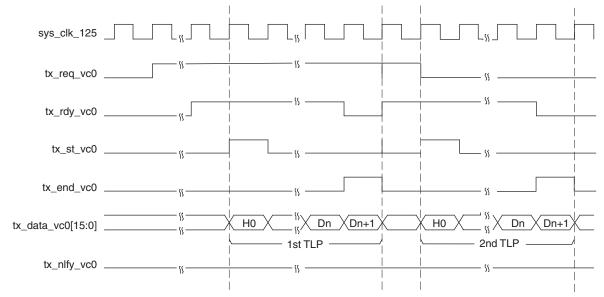

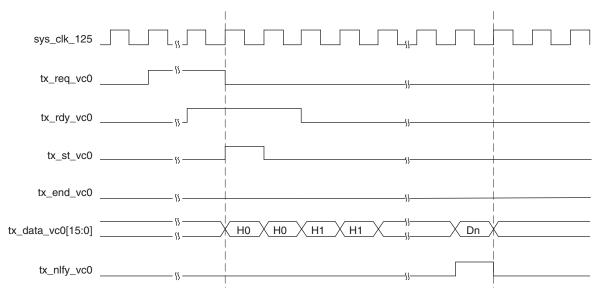

| tx_req_vc0                    | Input     | sys_clk_125 | Active high transmit request. This port is asserted when the user wants to send a TLP. If several TLPs will be provided in a burst, this port can remain high until all TLPs have been sent.                                                                                                                                                                                                                                                                                                                    |

| tx_rdy_vc0                    | Output    | sys_clk_125 | Active high transmit ready indicator. Tx_st should be pro-<br>vided next clock cycle after tx_rdy is high. This port will go<br>low between TLPs.                                                                                                                                                                                                                                                                                                                                                               |

| tx_st_vc0                     | Input     | sys_clk_125 | Active high transmit start of TLP indicator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| tx_end_vc0                    | Input     | sys_clk_125 | Active high transmit end of TLP indicator. This signal must go low at the end of the TLP.                                                                                                                                                                                                                                                                                                                                                                                                                       |

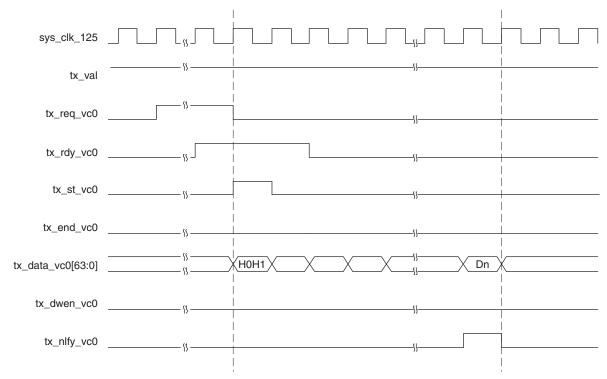

| tx_nlfy_vc0                   | Input     | sys_clk_125 | Active high transmit nullify TLP. Can occur anywhere during<br>the TLP. If tx_nlfy_vc0 is asserted to nullify a TLP the<br>tx_end_vc0 port should not be asserted. The tx_nlfy_vc0<br>terminates the TLP.                                                                                                                                                                                                                                                                                                       |

| tx_dwen_vc0                   | Input     | sys_clk_125 | Active high transmit 32-bit word indicator. Used if only bits [63:32] provide valid data. This port is available only on the Native x4 and x4 Downgraded x1 cores.                                                                                                                                                                                                                                                                                                                                              |

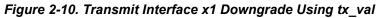

| tx_val                        | Output    | sys_clk_125 | Active high transmit clock enable. When a x4 is down-<br>graded to a x1, this signal is used as the clock enable to<br>downshift the transmit bandwidth. This port is available only<br>on the Native x4 and x4 Downgraded x1 cores.                                                                                                                                                                                                                                                                            |

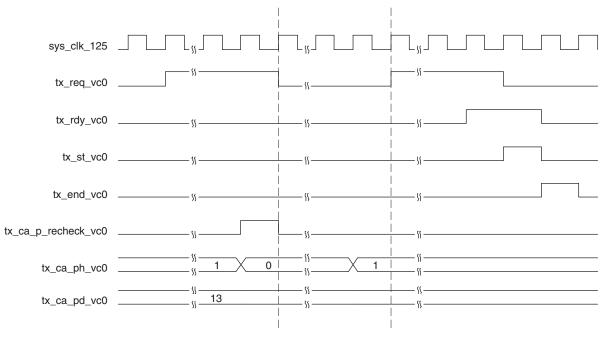

| tx_ca_[ph,nph,cplh]_vc0[8:0]  | Output    | sys_clk_125 | Transmit Interface credit available bus. This port will decre-<br>ment as TLPs are sent and increment as UpdateFCs are<br>received.<br>Ph - Posted header<br>Nph - Non-posted header<br>Cplh - Completion header<br>This credit interface is only updated when an UpdateFC<br>DLLP is received from the PCI Express line.<br>[8] - This bit indicates the receiver has infinite credits. If this<br>bit is high then bits. [7:0] should be ignored. [7:0] - The<br>amount of credits available at the receiver. |

| tx_ca_[pd,npd,cpld]_vc0[12:0] | Output    | sys_clk_125 | Transmit Interface credit available bus.<br>This port will decrement as TLPs are sent and increment as<br>UpdateFCs are received.<br>pd - posted data<br>npd - non-posted data<br>cpld - completion data<br>[12] - This bit indicates the receiver has infinite credits. If<br>this bit is high, then bits [11:0] should be ignored.<br>[11:0] - The amount of credits available at the receiver.                                                                                                               |

| tx_ca_p_recheck_vc0           | Output    | sys_clk_125 | Active high signal that indicates the core sent a Posted TLP which changed the tx_ca_p[h,d]_vc0 port. This might require a recheck of the credits available if the user has asserted tx_req_vc0 and is waiting for tx_rdy_vc0 to send a Posted TLP.                                                                                                                                                                                                                                                             |

| tx_ca_cpl_recheck_vc0         | Output    | sys_clk_125 | Active high signal that indicates the core sent a Completion TLP which changed the tx_ca_cpl[h,d]_vc0 port. This might require a recheck of the credits available if the user has asserted tx_req_vc0 and is waiting for tx_rdy_vc0 to send a Completion TLP.                                                                                                                                                                                                                                                   |

| Port Name                        | Direction | Clock       | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive TLP Interface            |           |             |                                                                                                                                                                                                                                                                                                                                                                                                                 |

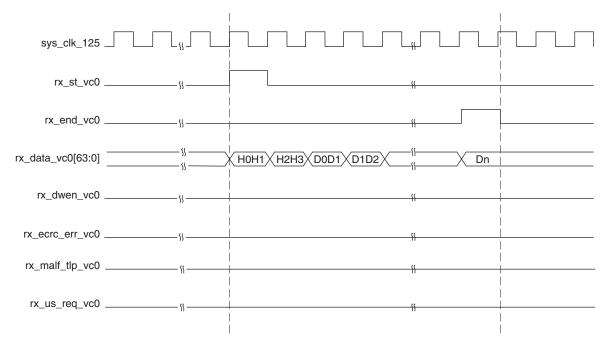

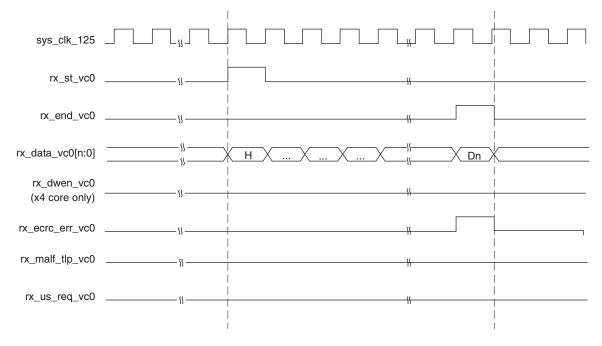

| rx_data_vc0[n:0]                 | Output    | sys_clk_125 | Native x4 and Downgraded x1 Receive data bus<br>[63:56] Byte N<br>[55:48] Byte N+1<br>[47:40] Byte N+2<br>[39:32] Byte N+3<br>[31:24] Byte N+4<br>[23:16] Byte N+5<br>[15: 8] Byte N+6<br>[7: 0] Byte N+7                                                                                                                                                                                                       |

|                                  |           |             | Native x1 Receive data bus<br>[15:8] Byte N<br>[7:0] Byte N+1                                                                                                                                                                                                                                                                                                                                                   |

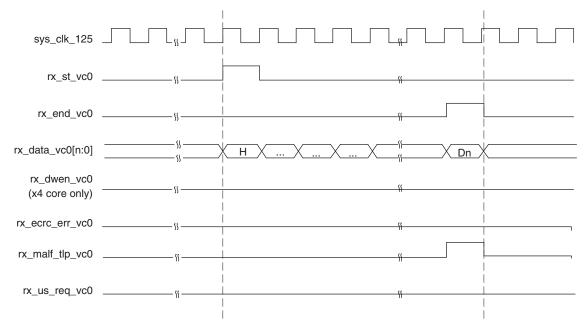

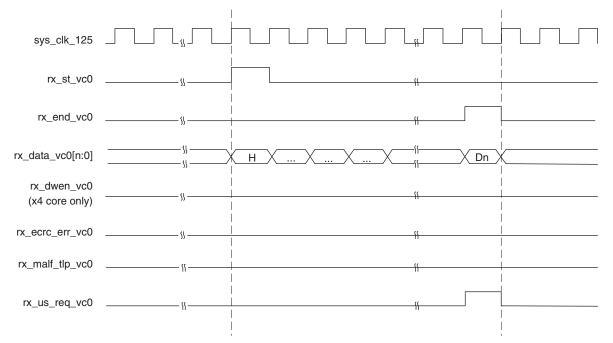

| rx_st_vc0                        | Output    | sys_clk_125 | Active high receive start of TLP indicator.                                                                                                                                                                                                                                                                                                                                                                     |

| rx_end_vc0                       | Output    | sys_clk_125 | Active high receive end of TLP indicator.                                                                                                                                                                                                                                                                                                                                                                       |

| rx_dwen_vc0                      | Output    | sys_clk_125 | Active high 32-bit word indicator. Used if only bits [63:32] contain valid data. This port is available only on the Native x4 and x4 Downgraded x1 cores.                                                                                                                                                                                                                                                       |

| rx_ecrc_err_vc0                  | Output    | sys_clk_125 | Active high ECRC error indicator. Indicates a ECRC error in the current TLP. Only available if ECRC is enabled in the IPexpress tool.                                                                                                                                                                                                                                                                           |