# MPC5643L Microcontroller Reference Manual

**Devices Supported:**MPC5643L

MPC5643LRM Rev. 10 26 June 2013

# Chapter 1 Introduction

| The MP     | C5643L microcontroller                                                                                                                                                                                                                                                                     | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPC564     | 43L device summary                                                                                                                                                                                                                                                                         | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

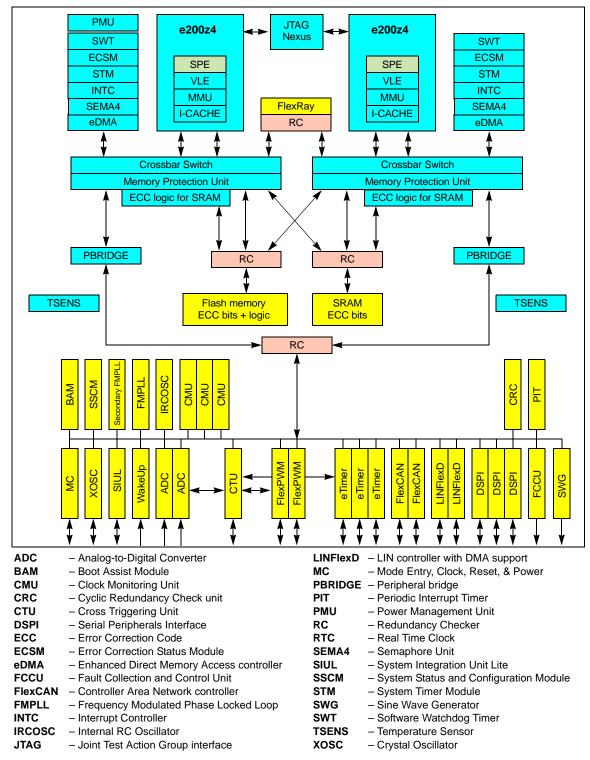

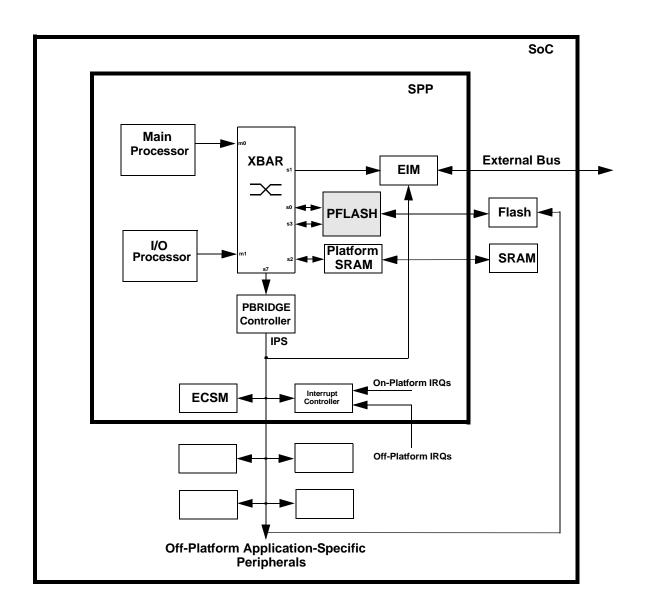

| Device b   | block diagram                                                                                                                                                                                                                                                                              | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Feature s  | summary                                                                                                                                                                                                                                                                                    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Feature of | details                                                                                                                                                                                                                                                                                    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

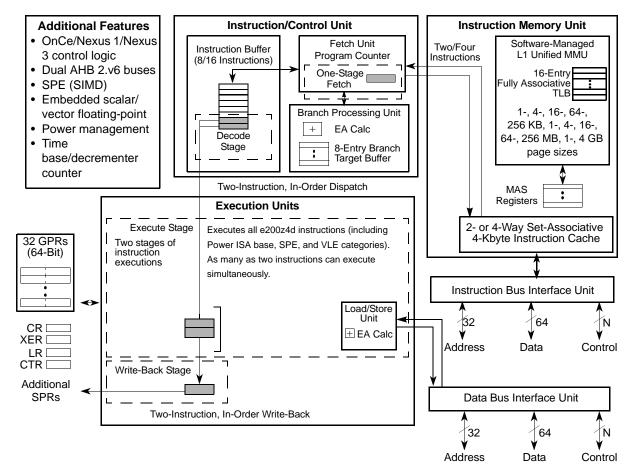

| 1.5.1      | High-performance e200z4d core                                                                                                                                                                                                                                                              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.2      | Crossbar switch (XBAR)                                                                                                                                                                                                                                                                     | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.3      | Memory Protection Unit (MPU)                                                                                                                                                                                                                                                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

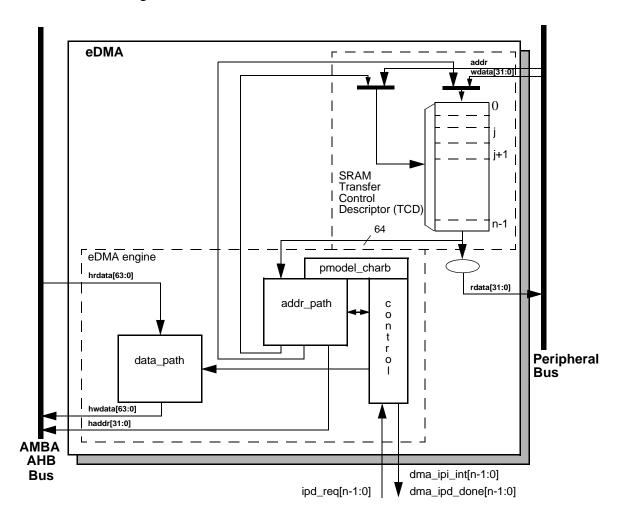

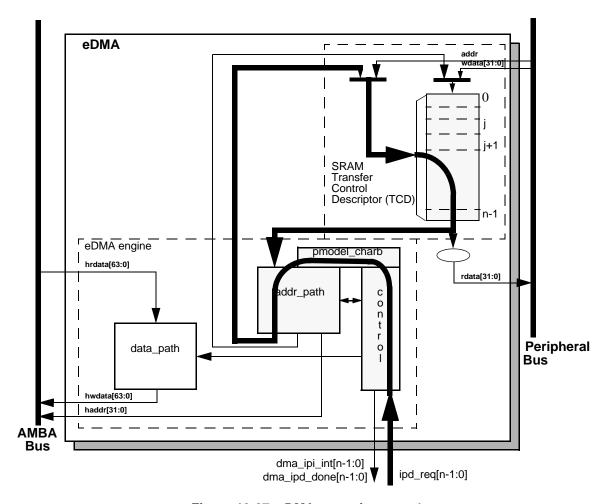

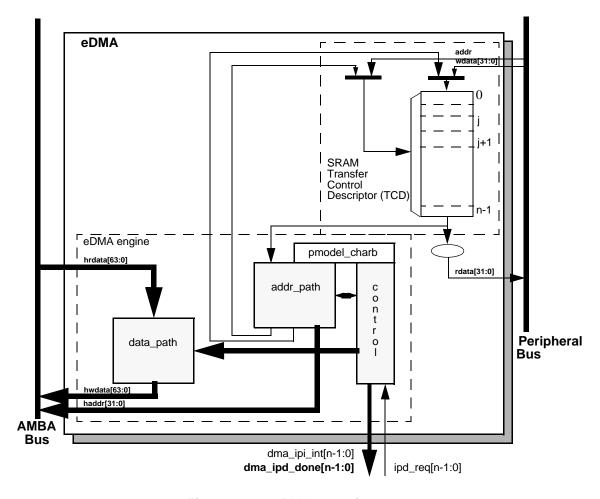

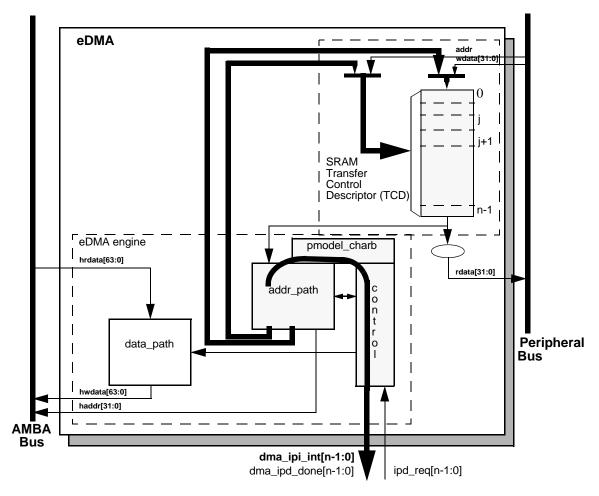

| 1.5.4      | Enhanced Direct Memory Access (eDMA)                                                                                                                                                                                                                                                       | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.5      | On-chip flash memory with ECC                                                                                                                                                                                                                                                              | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.6      | On-chip SRAM with ECC                                                                                                                                                                                                                                                                      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

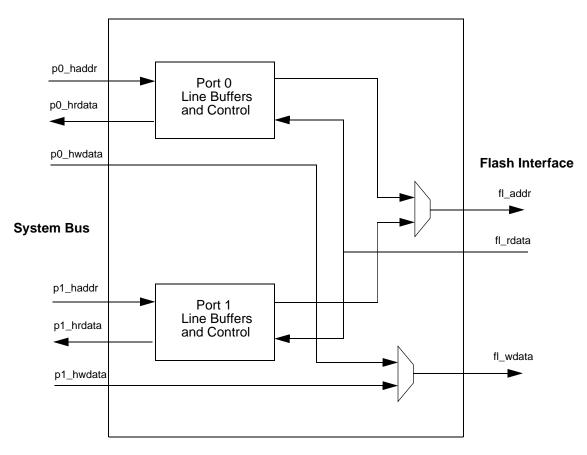

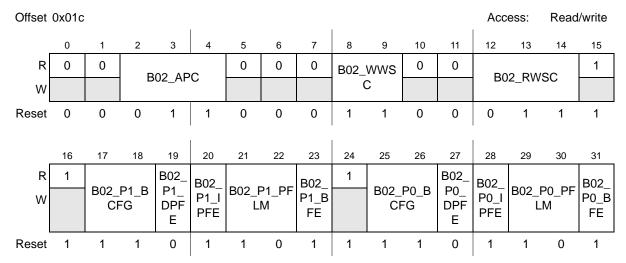

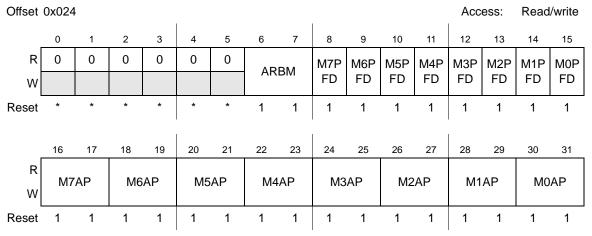

| 1.5.7      | Platform flash memory controller                                                                                                                                                                                                                                                           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.8      | Platform Static RAM Controller (SRAMC)                                                                                                                                                                                                                                                     | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.9      | Memory subsystem access time                                                                                                                                                                                                                                                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.10     | Error Correction Status Module (ECSM)                                                                                                                                                                                                                                                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

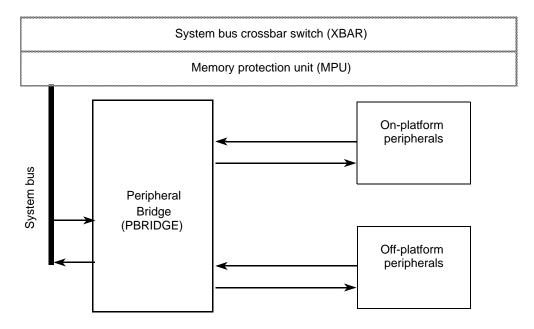

| 1.5.11     | Peripheral bridge (PBRIDGE)                                                                                                                                                                                                                                                                | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

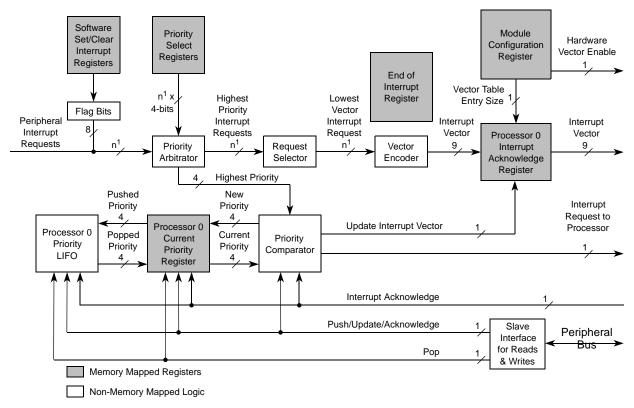

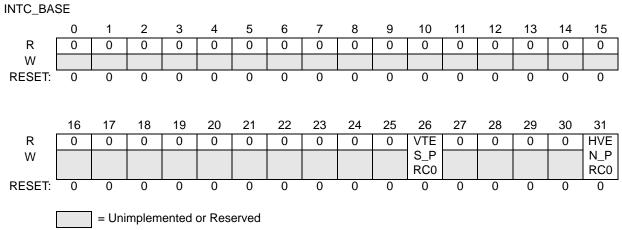

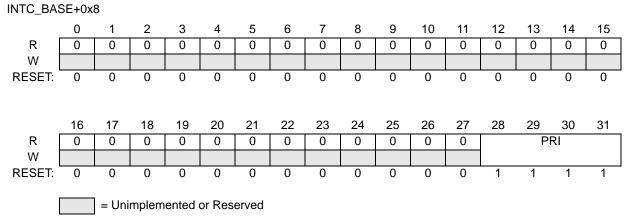

| 1.5.12     | Interrupt Controller (INTC)                                                                                                                                                                                                                                                                | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

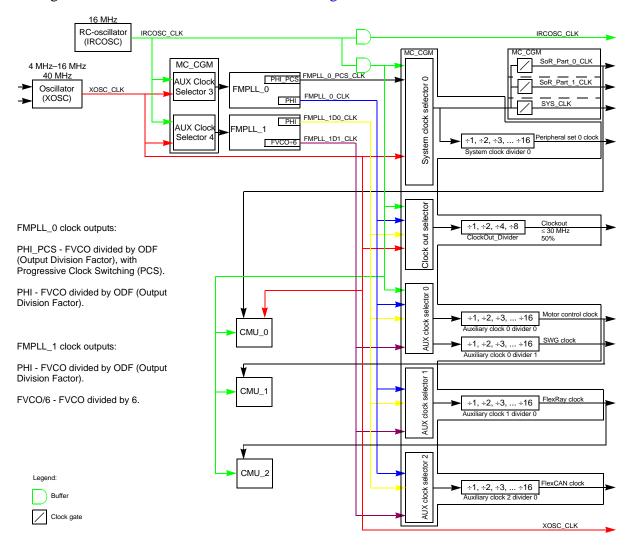

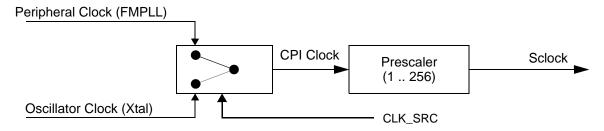

| 1.5.13     | System clocks and clock generation                                                                                                                                                                                                                                                         | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

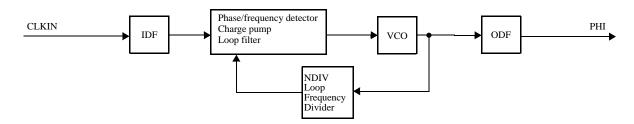

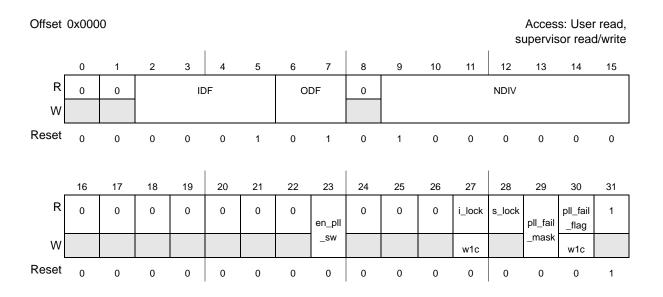

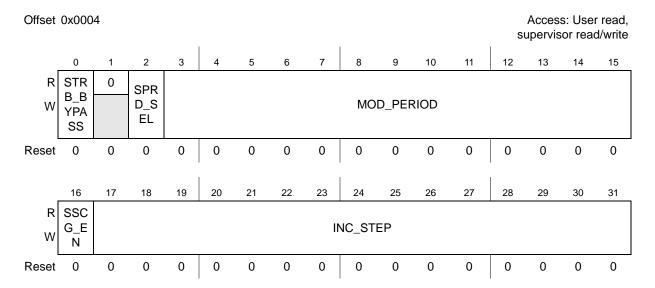

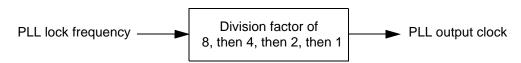

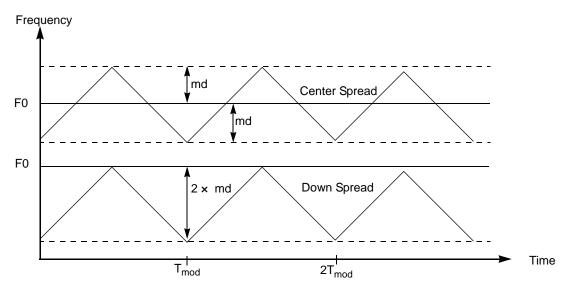

| 1.5.14     | Frequency-Modulated Phase-Locked Loop (FMPLL)                                                                                                                                                                                                                                              | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.15     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.16     | Internal Reference Clock (RC) oscillator                                                                                                                                                                                                                                                   | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

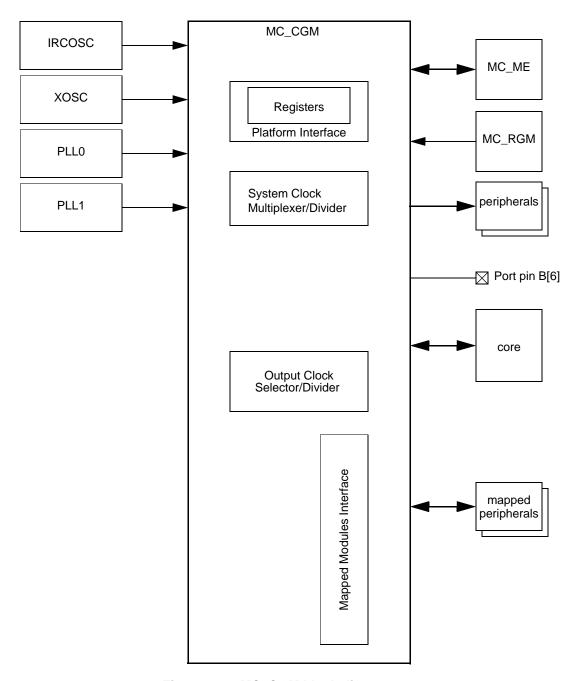

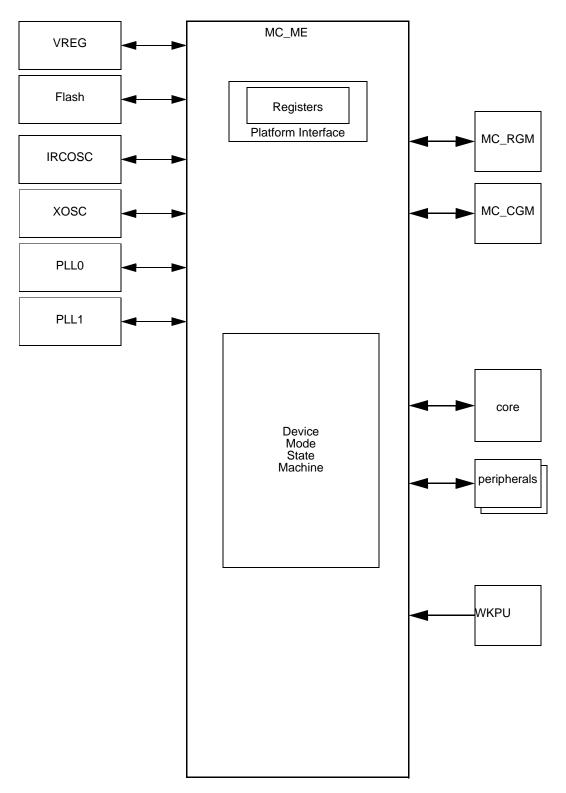

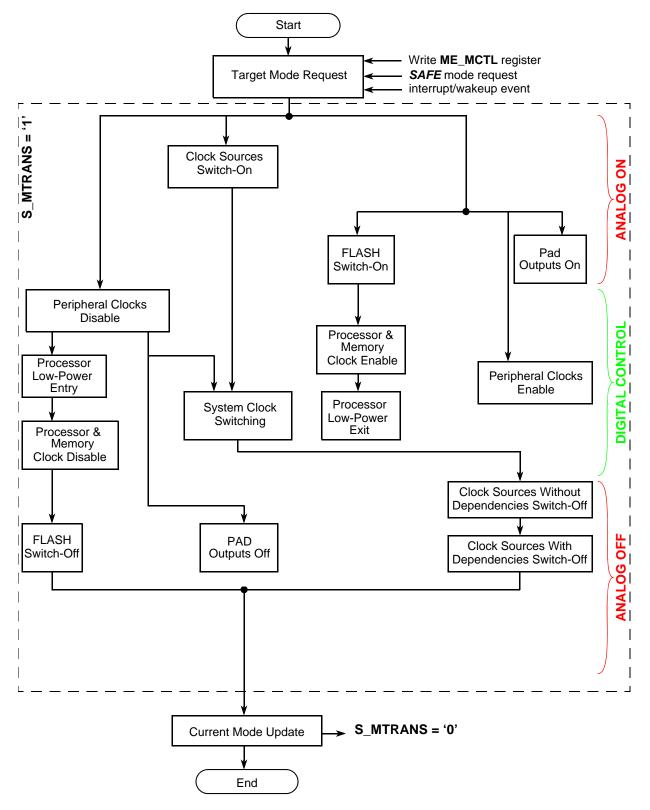

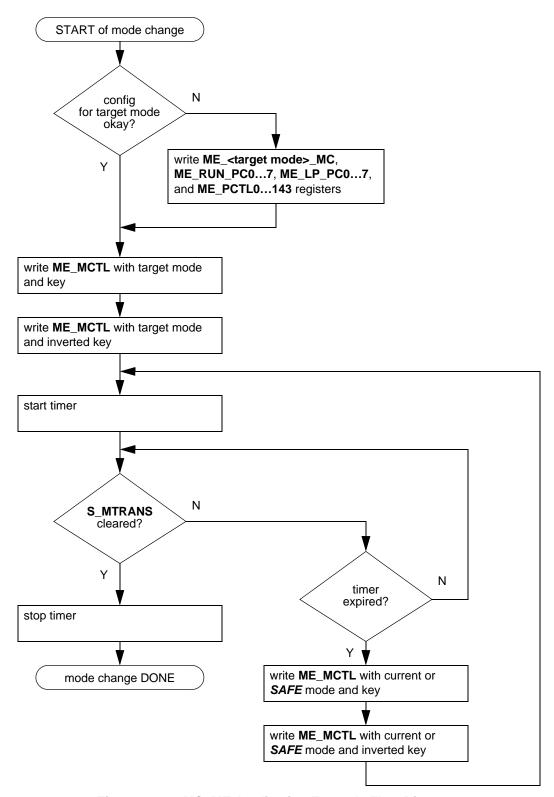

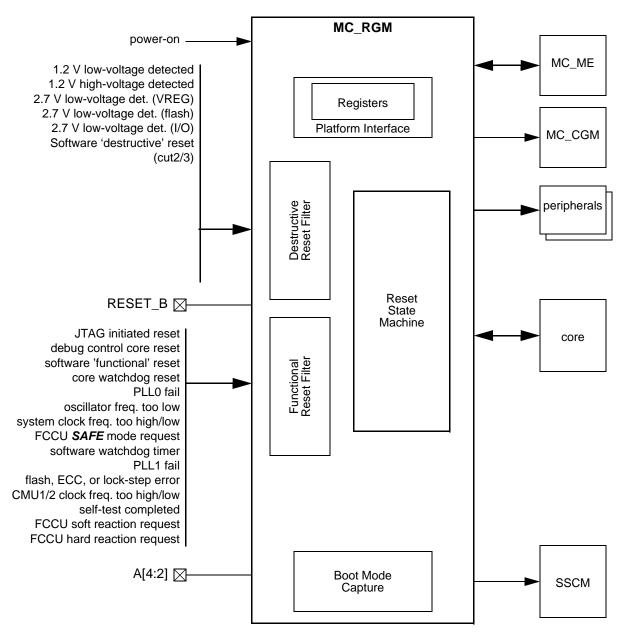

| 1.5.17     | Clock, reset, power, mode and test control modules (MC_CGM, MC_RGM, MC_F                                                                                                                                                                                                                   | CU,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| and MC_    | _ME)                                                                                                                                                                                                                                                                                       | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

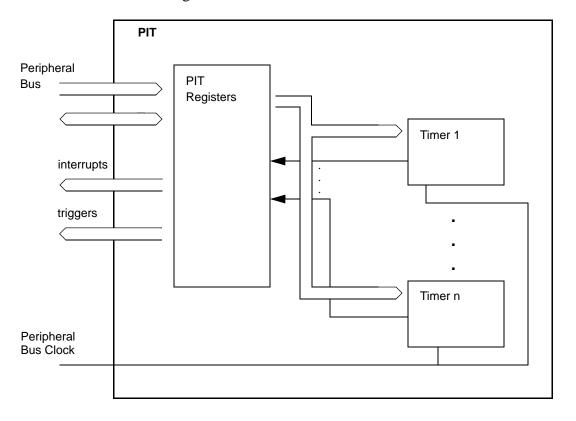

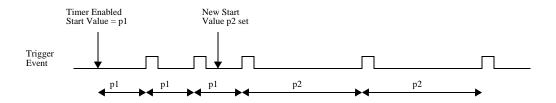

| 1.5.18     | Periodic Interrupt Timer Module (PIT)                                                                                                                                                                                                                                                      | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.19     | System Timer Module (STM)                                                                                                                                                                                                                                                                  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.20     | Software Watchdog Timer (SWT)                                                                                                                                                                                                                                                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

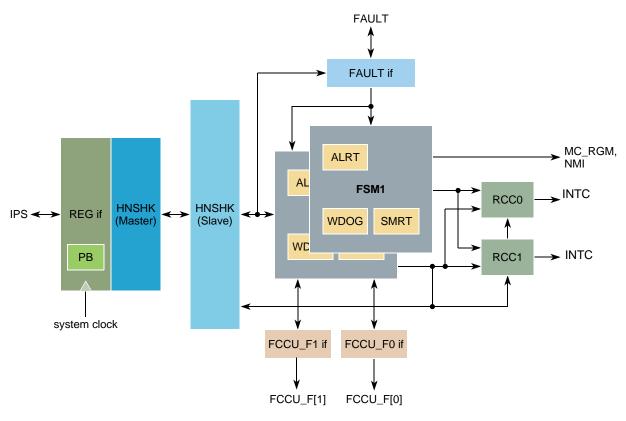

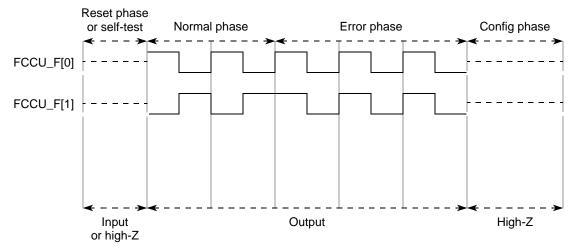

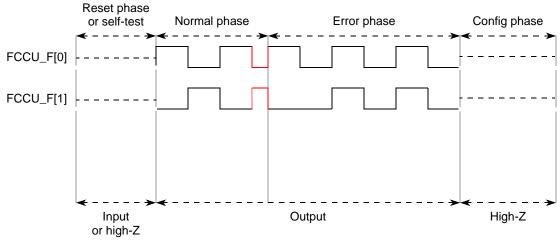

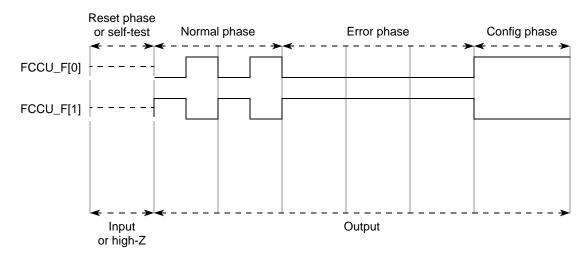

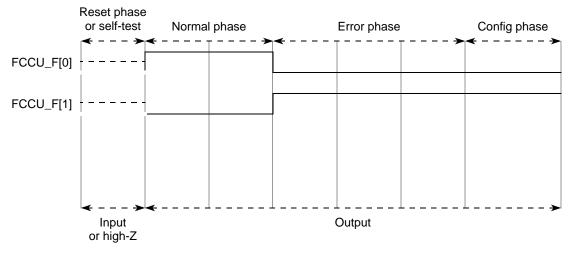

| 1.5.21     | Fault Collection and Control Unit (FCCU)                                                                                                                                                                                                                                                   | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5.22     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.23     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.24     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.25     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.26     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

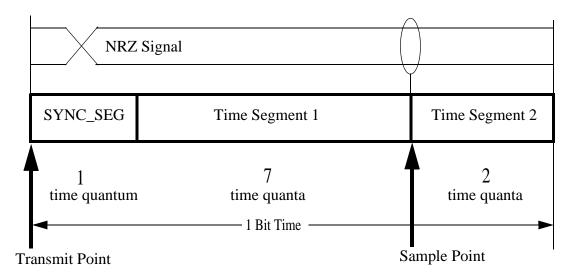

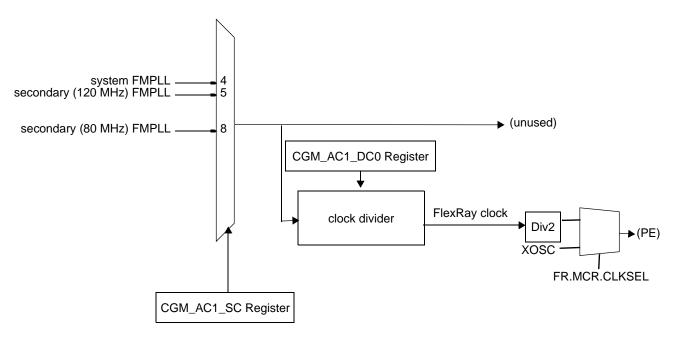

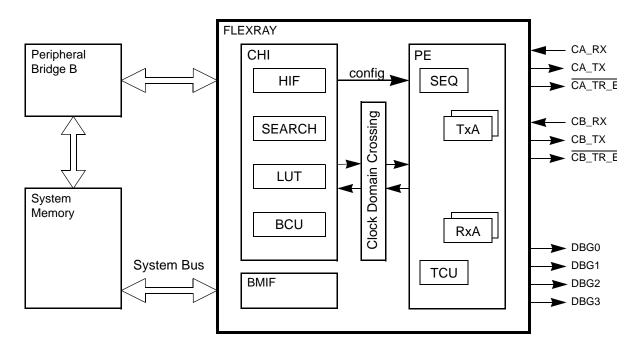

|            | FlexRay                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.28     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.29     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.30     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

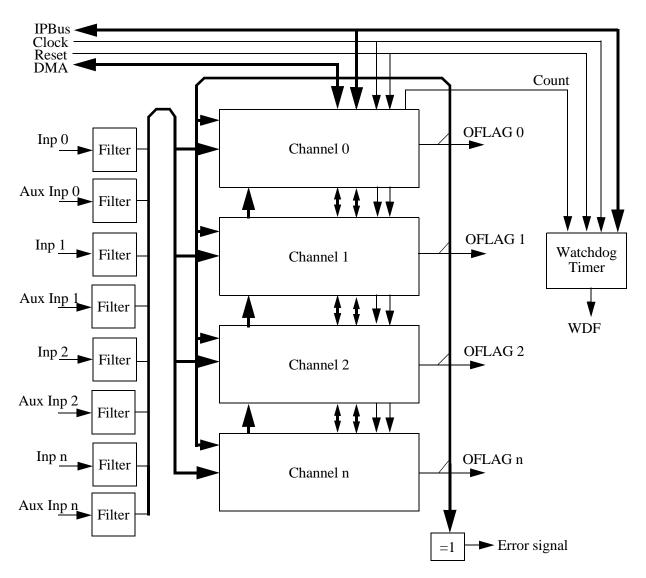

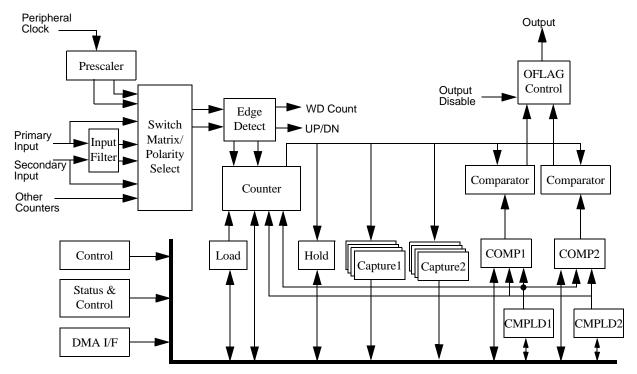

| 1.5.31     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.32     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.33     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.34     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.35     |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.36     | Redundancy Control and Checker Unit (RCCU)                                                                                                                                                                                                                                                 | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

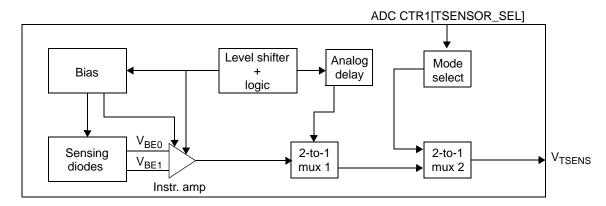

| 1.5.37     | Junction temperature sensor                                                                                                                                                                                                                                                                | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

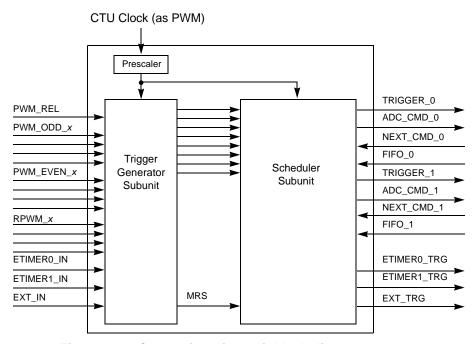

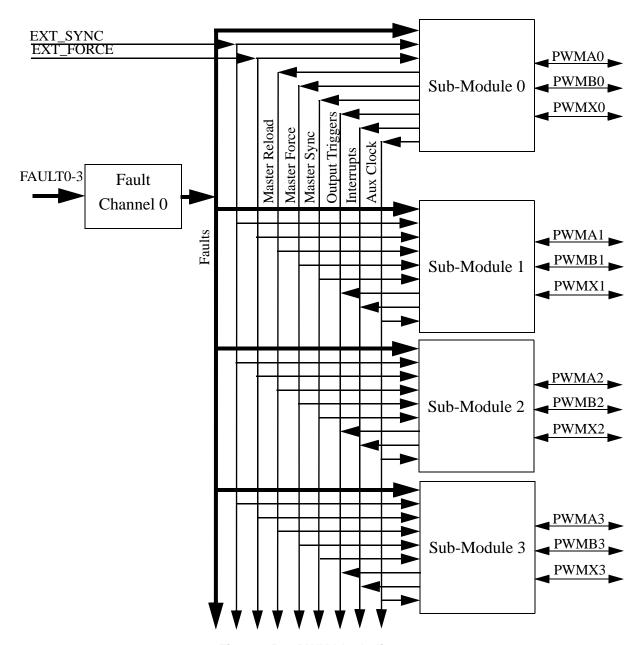

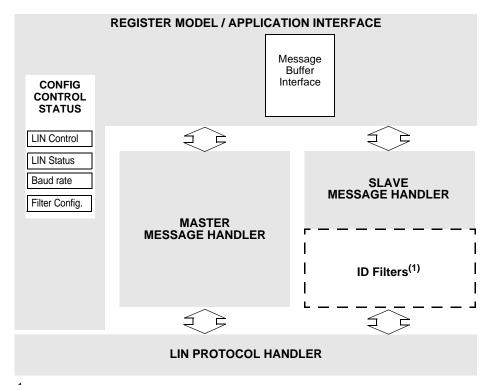

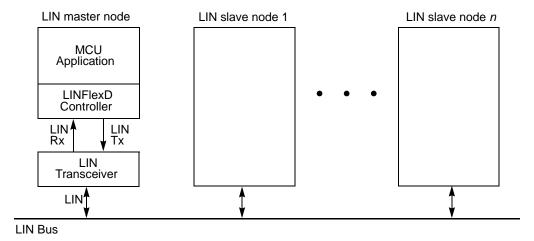

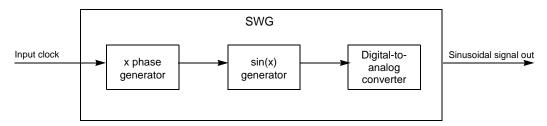

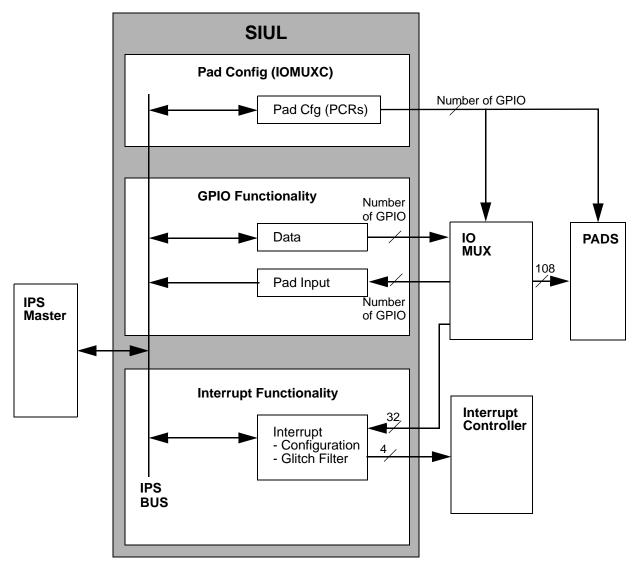

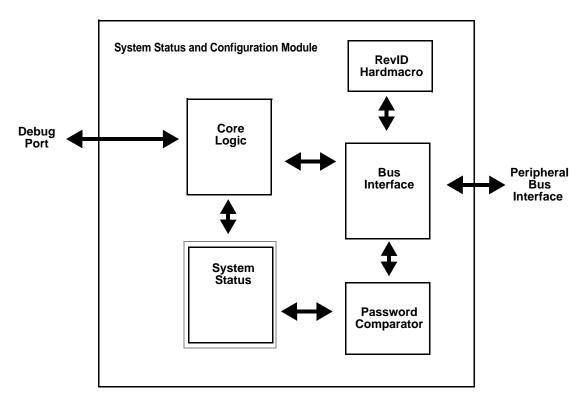

|            | MPC564 Device to Feature Feature 1.5.1 1.5.2 1.5.3 1.5.4 1.5.5 1.5.6 1.5.7 1.5.8 1.5.9 1.5.10 1.5.11 1.5.12 1.5.13 1.5.14 1.5.15 1.5.16 1.5.17 and MC 1.5.18 1.5.19 1.5.20 1.5.21 1.5.22 1.5.23 1.5.24 1.5.25 1.5.26 1.5.27 1.5.28 1.5.29 1.5.30 1.5.31 1.5.32 1.5.33 1.5.34 1.5.35 1.5.36 | 1.5.2 Crossbar switch (XBAR) 1.5.3 Memory Protection Unit (MPU) 1.5.4 Enhanced Direct Memory Access (eDMA) 1.5.5 On-chip flash memory with ECC 1.5.6 On-chip SRAM with ECC 1.5.7 Platform flash memory controller 1.5.8 Platform Static RAM Controller (SRAMC) 1.5.9 Memory subsystem access time 1.5.10 Error Correction Status Module (ECSM) 1.5.11 Peripheral bridge (PBRIDGE) 1.5.12 Interrupt Controller (INTC) 1.5.13 System clocks and clock generation 1.5.14 Frequency-Modulated Phase-Locked Loop (FMPLL) 1.5.15 Main oscillator 1.5.16 Internal Reference Clock (RC) oscillator 1.5.17 Clock, reset, power, mode and test control modules (MC_CGM, MC_RGM, MC_F and MC_ME) 1.5.18 Periodic Interrupt Timer Module (PIT) 1.5.19 System Timer Module (STM) 1.5.20 Software Watchdog Timer (SWT) 1.5.21 Fault Collection and Control Unit (FCCU) 1.5.22 System Integration Unit Lite (SIUL) 1.5.23 Non-Maskable Interrupt (NMI) 1.5.24 Boot Assist Module (BAM) 1.5.25 System Status and Configuration Module (SSCM) 1.5.26 FlexCAN 1.5.27 FlexRay 1.5.28 Serial communication interface module (LINFlexD) 1.5.29 Deserial Serial Peripheral Interface (DSPI) 1.5.30 FlexPWM 1.5.31 eTimer module 1.5.32 Sine Wave Generator (SWG) 1.5.33 Analog-to-Digital Converter module (ADC) 1.5.34 Cross Triggering Unit (CTU) 1.5.35 Cyclic Redundancy Checker (CRC) Unit 1.5.36 Redundancy Control and Checker Unit (RCCU) |

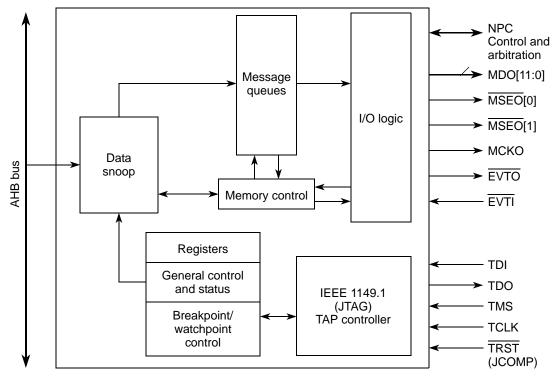

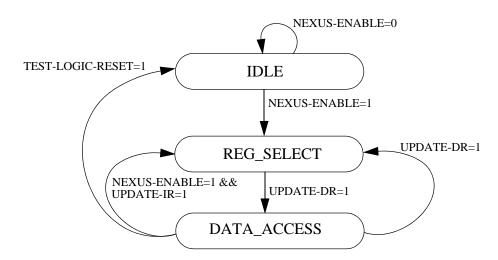

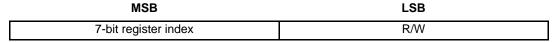

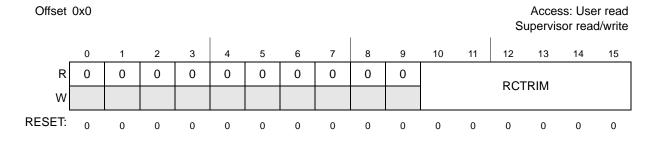

|     | 1.5.38 Nexus Port      | Controller (NPC)                            | 51  |

|-----|------------------------|---------------------------------------------|-----|

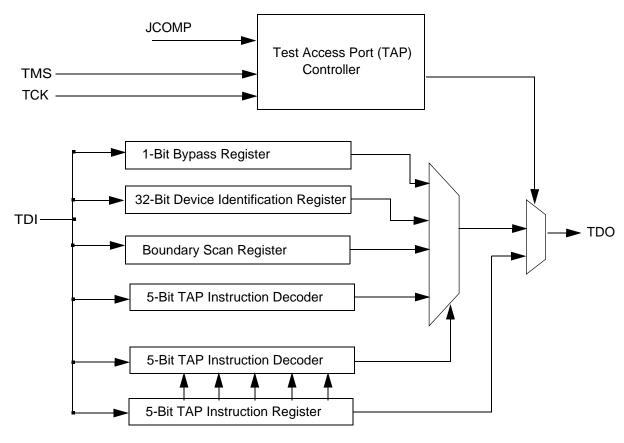

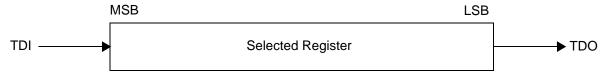

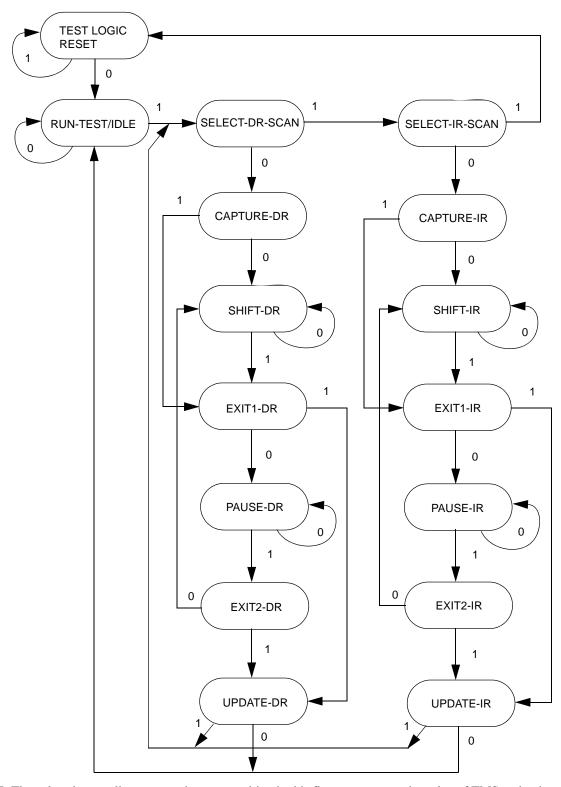

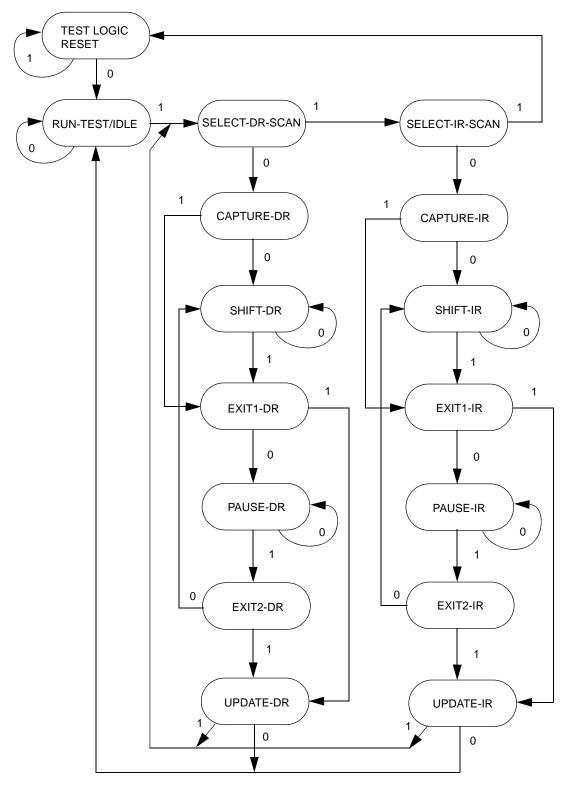

|     | 1.5.39 IEEE 1149.      | 1 JTAG Controller (JTAGC)                   | 52  |

|     | 1.5.40 Voltage regu    | ulator / Power Management Unit (PMU)        | 53  |

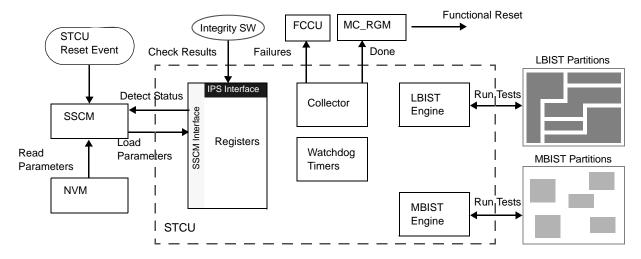

|     | 1.5.41 Built-In Sel    | f-Test (BIST) capability                    | 53  |

|     |                        | •                                           |     |

|     |                        | Chapter 2                                   |     |

|     |                        | Memory Map                                  |     |

|     |                        | Chapter 3                                   |     |

|     |                        | Signal Description                          |     |

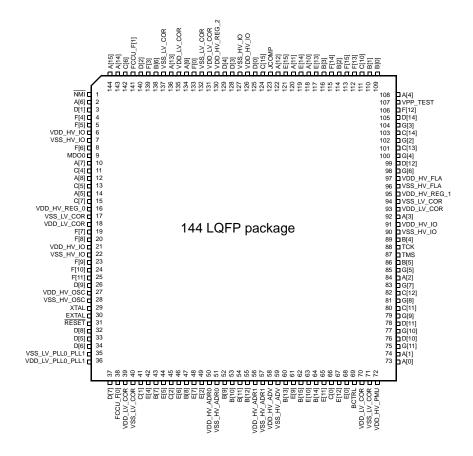

| 3.1 | Package pinouts        |                                             | 61  |

| 3.2 |                        |                                             |     |

| 3.3 |                        |                                             |     |

| 3.4 |                        |                                             |     |

| 3.5 | Mapping of ports to Po | GPDO/I registers                            | 117 |

|     |                        | Chapter 4                                   |     |

|     |                        | Operating Modes                             |     |

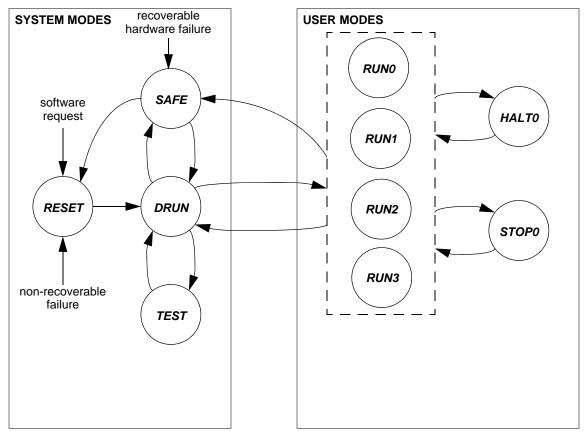

| 4.1 | Overview               |                                             | 121 |

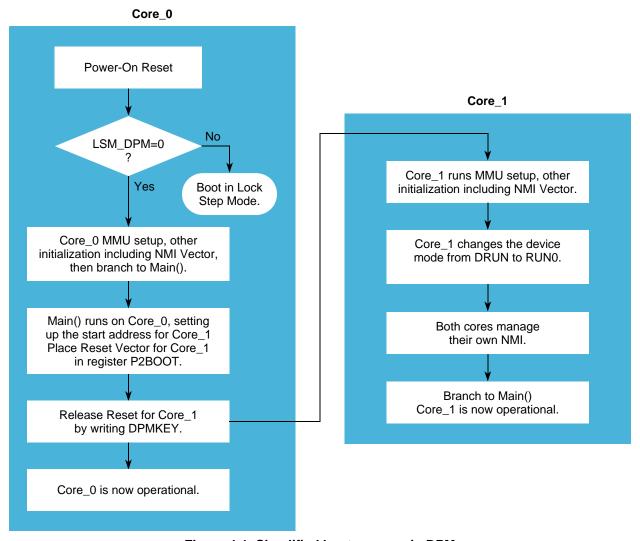

| 4.2 | Lock Step Mode (LSM    | <b>1</b> )                                  | 121 |

| 4.3 | Decoupled Parallel Mo  | ode (DPM)                                   | 122 |

| 4.4 |                        | M                                           |     |

|     |                        | SM                                          |     |

|     | 4.4.2 Entering DF      | PM                                          | 123 |

|     |                        | Chapter 5                                   |     |

|     |                        | Device Boot Modes                           |     |

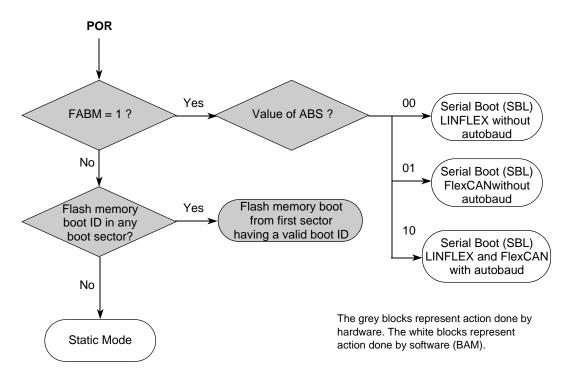

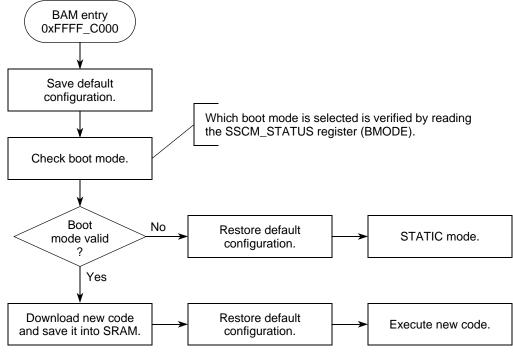

| 5.1 | Boot mode functionali  | ty                                          | 125 |

| 5.2 | Hardware configuration | on                                          | 125 |

|     | 5.2.1 Single Chip      | boot mode                                   | 125 |

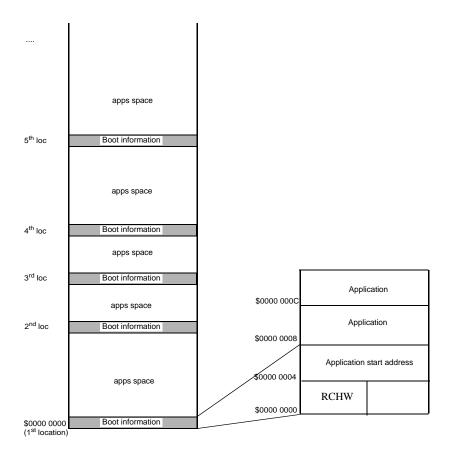

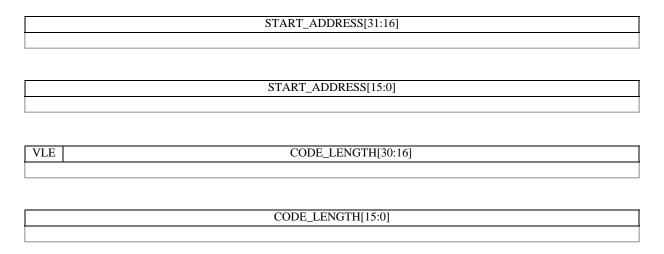

| 5.3 | Boot-sector search     |                                             | 126 |

|     |                        | oot sectors                                 |     |

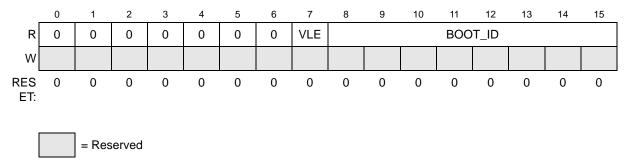

|     | 5.3.2 Reset Confi      | guration Half-Word                          | 127 |

|     |                        | ternate boot                                |     |

| 5.4 | •                      | oot mode                                    |     |

|     |                        | Mode — Unsecured                            |     |

|     |                        | Mode — Secured                              |     |

|     |                        | Loader Mode — Public Password Enabled       |     |

|     |                        | Loader Mode — Flash Memory Password Enabled |     |

|     | •                      | ot Mode                                     |     |

|     | 5.4.6 Static Mode      | ·                                           | 129 |

|     |                        | Chapter 6                                   |     |

|     |                        | Device Security                             |     |

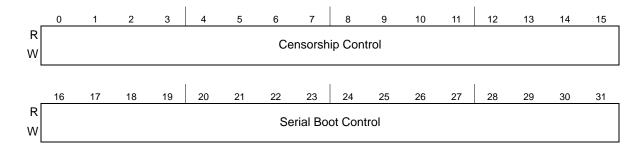

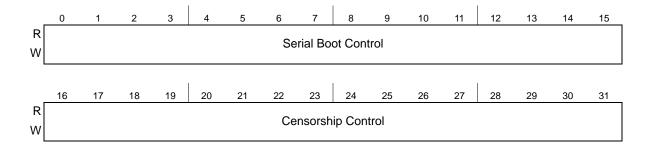

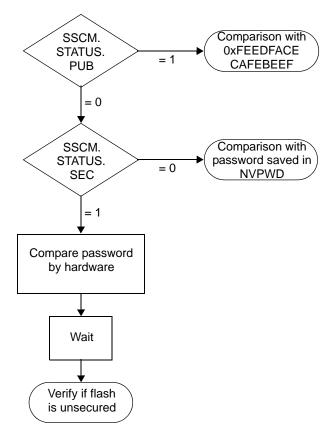

| 6.1 | Security               | -                                           | 131 |

|     | 6.1.1          | Securing the microcontroller                         | 131 |

|-----|----------------|------------------------------------------------------|-----|

|     | 6.1.2          | Unsecuring the microcontroller                       | 132 |

| 6.2 | Serial ac      | ccess                                                | 133 |

|     |                | <b>A.</b>                                            |     |