# Dual 36V Op Amp for 18-Bit SAR ADC Front-End

### **General Description**

The MAX9633 is a low-noise, low-distortion operational amplifier that is optimized to drive ADCs for use in applications from DC to a few MHz. The MAX9633 features low noise ( $3NV/\sqrt{Hz}$  at 1kHz and  $3.5NV/\sqrt{Hz}$  at 100Hz) and low distortion (130dB at 10kHz), making it suitable for industrial, medical, and test applications.

The exceptionally fast settling-time and low input offset voltage makes the IC an excellent solution to drive high-resolution 12-bit to 18-bit SAR ADCs.

The IC operates from a wide supply voltage range up to 36V with only 3.5mA of quiescent current per amplifier.

The IC is offered in an 8-pin, 3mm x 3mm TDFN package for operation over the -40°C to +125°C temperature range.

Data Acquisition and Instrumentation

**Test and Measurement Equipments**

High-Performance Audio Circuitry

ADC Drivers

Motor Control

**Imaging Systems**

Power Grid Systems

#### **Applications**

#### **Features**

- Low-Noise (3nV/√Hz at 1kHz) and Low-Distortion (130dB at 10kHz) ADC Driver

- Very Fast 750ns Settling Time to 16-Bit Accuracy

- Low Input Voltage Offset 200µV (max)

- ♦ Low 0.9µV/°C Input Offset Temperature Coefficient

- Gain-Bandwidth Product 27MHz

- ♦ 4.5V to 36V Wide Supply Range

- Unity Gain Stable

- ◆ ±6kV ESD Protection HBM

- 8-Pin TDFN and SOIC Packages

#### **Ordering Information**

| PART        | TEMP RANGE      | PIN-<br>PACKAGE | TOP<br>MARK |

|-------------|-----------------|-----------------|-------------|

| MAX9633ASA+ | -40°C to +125°C | 8 SO-EP*        | _           |

| MAX9633ATA+ | -40°C to +125°C | 8 TDFN-EP*      | BMM         |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

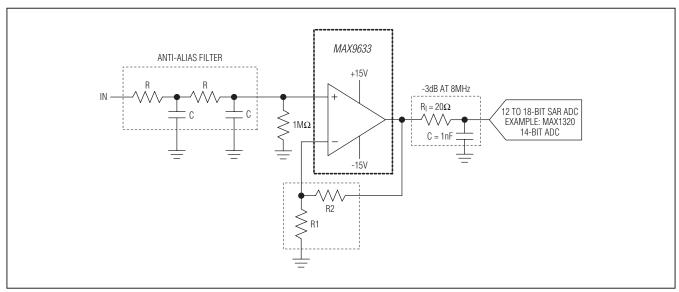

## **Typical Application Circuit**

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

# Dual 36V Op Amp for 18-Bit SAR ADC Front-End

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (VCC to VEE)                      | 0.3V to +40V          |

|--------------------------------------------------|-----------------------|

| All Other Pins(VEE -                             | 0.3V) to (VCC + 0.3V) |

| Short-Circuit Duration of OUTA, OUTB             | 10s                   |

| Continuous Input Current (any pins)              | ±20mA                 |

| Continuous Power Dissipation ( $T_A = +70^\circ$ | °C)                   |

| SO (derate 24.4mW/°C above +70°C)                |                       |

| Multilayer Board                                 | 1951.2mW              |

| TDFN (derate 24.4mW/°C above +70°C) |                |

|-------------------------------------|----------------|

| Multilayer Board                    | 1905mW         |

| Operating Temperature Range         | 40°C to +125°C |

| Junction Temperature                | +150°C         |

| Storage Temperature Range           | 65°C to +150°C |

| Soldering Temperature (reflow)      | +260°C         |

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

#### SO-EP

TDFN-EP

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +15V, V_{EE} = -15V, V_{CM} = 0V, R_L = 10k\Omega$  to  $V_{GND} = 0V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                              | SYMBOL     | CON                                                                             | MIN                                                                        | ТҮР | MAX  | UNITS        |       |  |

|----------------------------------------|------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|------|--------------|-------|--|

| POWER SUPPLY                           |            | •                                                                               |                                                                            |     |      |              |       |  |

| Supply Voltage Range                   | VCC - VEE  | Guaranteed by PSR                                                               | 4.5                                                                        |     | 36   | V            |       |  |

|                                        |            |                                                                                 | $T_A = +25^{\circ}C$                                                       |     | 3.5  | .5 5         |       |  |

| Supply Current                         | Icc        | Per amplifier                                                                   | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                    |     |      | 6            | mA    |  |

|                                        |            |                                                                                 | $-40^{\circ}C \le T_A \le +125^{\circ}C$                                   |     |      | 6.5          |       |  |

| Power-Supply Rejection Ratio           | PSRR       | $+4.5V \le (V_{CC} - V_{EE})$                                                   | $T_A = +25^{\circ}C$                                                       | 112 | 135  |              | dB    |  |

|                                        | 1 3111     | ≤+36V                                                                           | $-40^\circ C \le T_A \le +125^\circ C$                                     | 110 |      |              | uв    |  |

| DC SPECIFICATIONS                      |            |                                                                                 |                                                                            |     |      |              |       |  |

| Input Offset Voltage                   | Vos        | T <sub>A</sub> = +25°C                                                          |                                                                            |     | ±70  | ±200         |       |  |

|                                        | V05        | $-40^{\circ}C \le TA \le +125^{\circ}C$                                         |                                                                            |     | ±290 | μV           |       |  |

| Input Offset Voltage Drift<br>(Note 3) | ΔVos       | $-40^{\circ}C \le T_A \le +125^{\circ}C$                                        |                                                                            |     | 0.2  | 0.9          | µV/°C |  |

|                                        |            | (VEE + 0.45V) ≤ VCN                                                             |                                                                            | ±42 | ±400 | nA           |       |  |

| Input Bias Current                     | IB         | $V_{EE} \le V_{CM} \le (V_{CC} -$                                               | 1.8V)                                                                      |     | 4.5  | 22           | μA    |  |

| Innut Offert Ourrent                   | 100        | (V <sub>EE</sub> + 0.45V) ≤ V <sub>CN</sub>                                     |                                                                            | ±30 | ±300 | ~ ^          |       |  |

| Input Offset Current                   | los        | $V_{EE} \le V_{CM} \le (V_{CC} - $                                              | 1.8V)                                                                      |     | ±200 | ±2000        | nA    |  |

| land Valtana Daaraa                    |            |                                                                                 | $T_A = +25^{\circ}C$                                                       | VEE |      | VCC -<br>1.7 | .,    |  |

| Input Voltage Range                    | VIN+, VIN- | Guaranteed by CMF                                                               | $\begin{array}{c} -40^{\circ}C \leq T_A \leq \\ +125^{\circ}C \end{array}$ | VEE |      | Vcc -<br>1.8 | V     |  |

|                                        |            | $V_{EE} \le V_{CM} \le (V_{CC} -$                                               | 1.7V), T <sub>A</sub> = +25°C                                              | 106 | 130  |              |       |  |

| Common-Mode Rejection Ratio            | CMRR       | $V_{EE} \le V_{CM} \le (V_{CC} - 1.8V), -40^{\circ}C \le T_A \le +125^{\circ}C$ |                                                                            | 105 | 130  |              | dB    |  |

## Dual 36V Op Amp for 18-Bit SAR ADC Front-End

#### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = +15V, V<sub>EE</sub> = -15V, V<sub>CM</sub> = 0V, R<sub>L</sub> = 10k $\Omega$  to V<sub>GND</sub> = 0V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                      | SYMBOL          | CONDIT                                                | IONS                                     | MIN  | TYP  | MAX      | UNITS             |  |

|--------------------------------|-----------------|-------------------------------------------------------|------------------------------------------|------|------|----------|-------------------|--|

| Open-Loop Gain                 | A. ( )          | $(V_{EE} + 0.3V) \le V_{OUT} \le (V_{EE} + 0.3V)$     | $_{\rm CC}$ - 2V), R <sub>L</sub> = 10kΩ | 118  | 140  |          | dB                |  |

| Open-Loop Gain                 | Avol            | $(V_{EE} + 0.45V) \le V_{OUT} \le (V_{EE} + 0.45V)$   | 115                                      | 138  |      |          |                   |  |

|                                | Vou             | Vcc - Vout                                            | $R_L = 10k\Omega$                        |      | 1.6  | 1.9      | V                 |  |

|                                | Voh             |                                                       | $R_L = 1k\Omega$                         |      | 1.7  | 2.0      |                   |  |

| Output Voltage Swing           |                 |                                                       | $R_L = 10k\Omega$                        |      | 70   | 150      | -<br>- mV         |  |

| Output voltage Swing           | Vol             | Vout - Vee                                            | $R_L = 1k\Omega$                         |      | 170  | 300      |                   |  |

|                                | VOL             | VOUT - VEE                                            | $R_L = 10 k\Omega$ to $V_{EE}$           |      | 20   | 100      |                   |  |

|                                |                 |                                                       | $R_L = 1k\Omega$ to $V_{EE}$             |      | 20   | 100      |                   |  |

| Short-Circuit Current          | Isc             | $T_A = +25^{\circ}C$                                  |                                          | 50   |      | mA       |                   |  |

| AC SPECIFICATIONS              |                 |                                                       |                                          |      |      |          |                   |  |

| Gain Bandwidth                 | GBWP            |                                                       |                                          |      | 27   |          | MHz               |  |

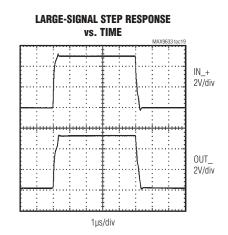

| Slew Rate                      | SR              | 5V step, Rs = $20\Omega$ , CL                         | = 1nF, Av = 1V/V                         |      | 18   |          | V/µs              |  |

| Output Transient Recovery Time | t <sub>TR</sub> | To 0.001%, ΔV <sub>OUT</sub> = 2<br>= 1nF, AV = +1V/V |                                          | 500  |      | ns       |                   |  |

| 0. W. T.                       | ts              | To 0.001%, 5V step,                                   | $R_{S} = 100\Omega, C_{L} = 30pF$        |      | 750  |          |                   |  |

| Settling Time                  |                 | AV = -1V/V                                            | $R_S = 20\Omega, C_L = 1$ nF             |      | 750  |          | – ns              |  |

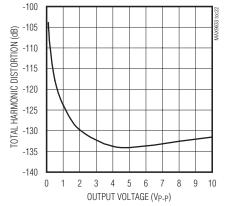

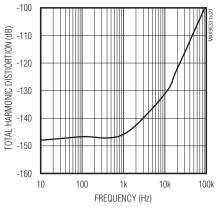

|                                |                 | Vout = 10VP-P, Rs =                                   | f = 1kHz                                 |      | 145  |          |                   |  |

| Total Harmonic Distortion      | THD             | $20\Omega$ , CL = 1nF, AV =                           | f = 10kHz                                |      | 130  |          | dB                |  |

|                                |                 | +1V/V                                                 | f = 100kHz                               | -100 |      | 1        |                   |  |

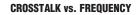

| Orecetalle                     |                 | Vout = 10VP-P, Rs =                                   | f = 1kHz                                 |      | -100 |          |                   |  |

| Crosstalk                      |                 | $20\Omega$ , CL = 1nF                                 | f = 10kHz                                | -90  |      | - dB     |                   |  |

| Input Valtage Naise Depaits    |                 | f = 100Hz                                             |                                          | 3.5  |      |          |                   |  |

| Input Voltage Noise Density    | en              | f = 1kHz                                              |                                          |      | 3    |          | nV/√Hz            |  |

| Input Voltage Noise            |                 | $0.1Hz \le f \le 10Hz$                                |                                          |      | 250  |          | nV <sub>P-P</sub> |  |

| Input Current Naine Daneit     |                 | f = 100Hz                                             |                                          |      | 12   | 12       |                   |  |

| Input Current Noise Density    | in              | f = 1kHz                                              |                                          | 10   |      | - pA/√Hz |                   |  |

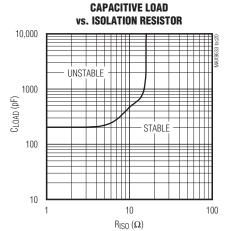

| Capacitive Loading             | CL              | No sustained oscillation                              | n, Av = +1V/V                            |      | 50   |          | pF                |  |

**Note 2:** All devices are 100% production tested at  $T_A = +25$ °C. Temperature limits are guaranteed by design.

Note 3: Guaranteed by design.

## **Dual 36V Op Amp for 18-Bit SAR ADC Front-End**

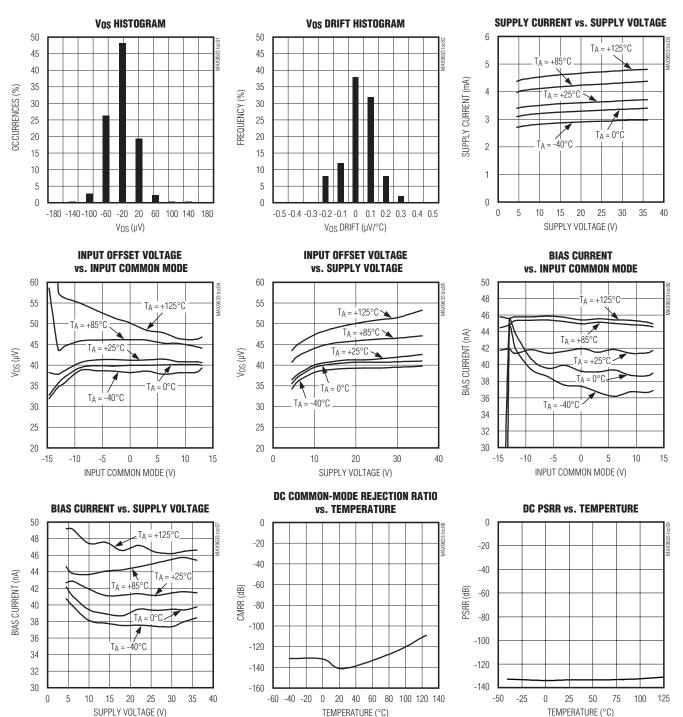

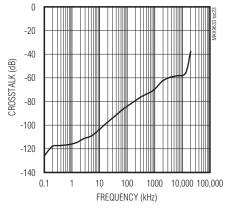

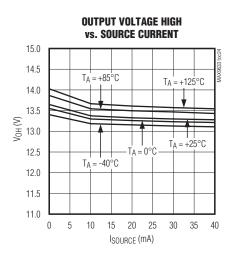

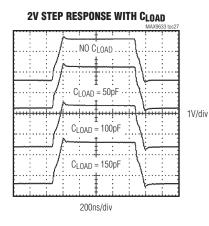

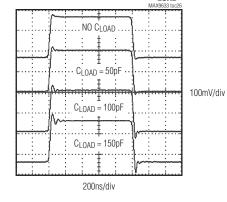

#### **Typical Operating Characteristics**

$(V_{CC} = +15V, V_{EE} = -15V, V_{CM} = 0V)$ , outputs have  $R_L = 10k\Omega$  connected to  $V_{GND} = 0V$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

Maxim Integrated

# Dual 36V Op Amp for 18-Bit SAR ADC Front-End

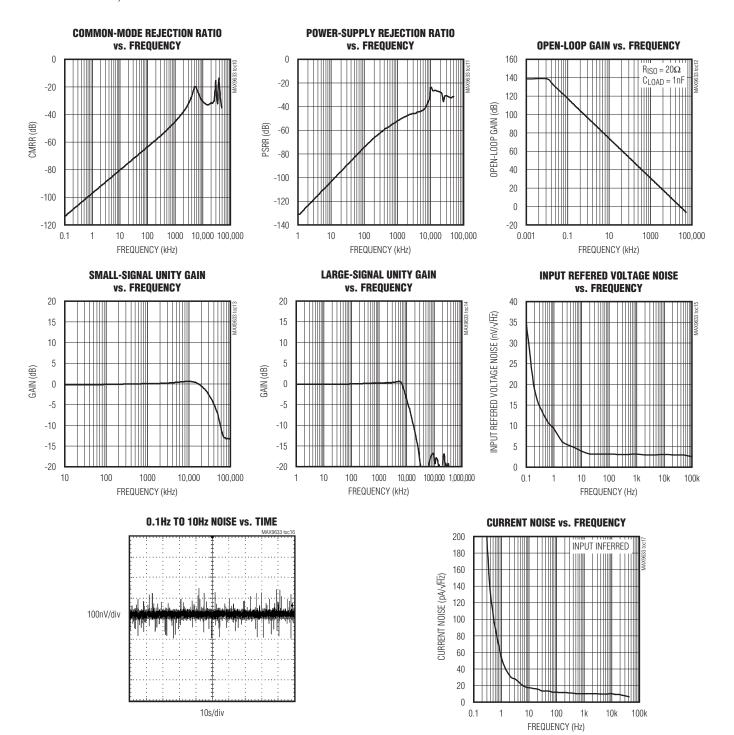

## **Typical Operating Characteristics (continued)**

$(V_{CC} = +15V, V_{EE} = -15V, V_{CM} = 0V)$ , outputs have  $R_L = 10k\Omega$  connected to  $V_{GND} = 0V$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## Dual 36V Op Amp for 18-Bit SAR ADC Front-End

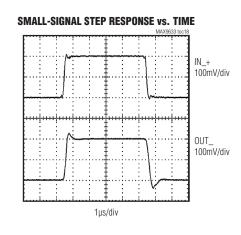

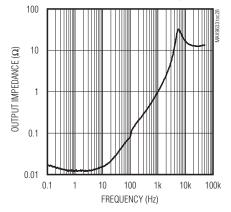

### **Typical Operating Characteristics (continued)**

$(V_{CC} = +15V, V_{EE} = -15V, V_{CM} = 0V)$ , outputs have  $R_L = 10k\Omega$  connected to  $V_{GND} = 0V$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

TOTAL HARMONIC DISTORTION vs. FREQUENCY Vout = 10VP-P

Maxim Integrated

## Dual 36V Op Amp for 18-Bit SAR ADC Front-End

### **Typical Operating Characteristics (continued)**

$(V_{CC} = +15V, V_{EE} = -15V, V_{CM} = 0V)$ , outputs have  $R_L = 10k\Omega$  connected to  $V_{GND} = 0V$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

**OUTPUT IMPEDANCE vs. FREQUENCY**

# **Dual 36V Op Amp for 18-Bit SAR ADC Front-End**

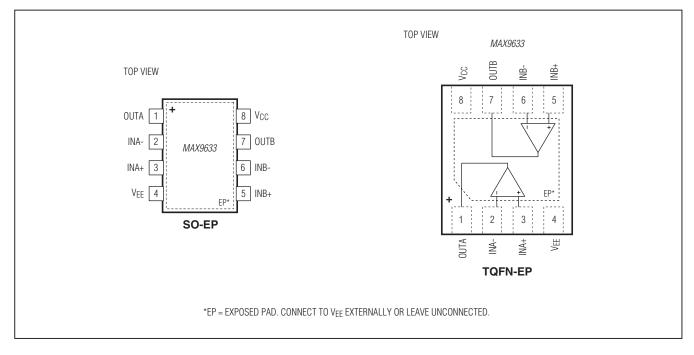

### Pin Configuration

### **Pin Description**

| PIN | NAME | FUNCTION                                                          |

|-----|------|-------------------------------------------------------------------|

| 1   | OUTA | Output A                                                          |

| 2   | INA- | Negative Input A                                                  |

| 3   | INA+ | Positive Input A                                                  |

| 4   | VEE  | Negative Supply Voltage. Bypass with a 0.1µF capacitor to ground. |

| 5   | INB+ | Positive Input B                                                  |

| 6   | INB- | Negative Input B                                                  |

| 7   | OUTB | Output B                                                          |

| 8   | VCC  | Positive Supply Voltage. Bypass with a 0.1µF capacitor to ground. |

|     | EP   | Exposed Pad. Connect to VEE externally or leave unconnected.      |

## **Dual 36V Op Amp for 18-Bit** SAR ADC Front-End

#### **Detailed Description**

The MAX9633 is designed in a new 36V, high-speed complementary BiCMOS process that is optimized for excellent AC dynamic performance combined with highvoltage operation.

The exceptionally fast settling time, low noise, low distortion, high bandwidth, and low input offset voltage make the IC an excellent solution to drive (up to 18-bit)highresolution and fast SAR ADCs.

The MAX9633 is unity gain stable and operates either with a single supply voltage up to 36V or with dual supplies up to  $\pm 18V$ .

#### **Applications Information**

#### **Driving High-Resolution SAR ADCs**

High-resolution SAR ADCs typically switch an input capacitor in the order of tens of pF during the track and hold phases. Such capacitor switching can cause a voltage glitch at the input of the ADC that behaves as a load-transient condition for the driving amplifier. In many applications, this glitch is avoided by placing an external capacitor at the ADC input that is in the order of 20 to 50 times the ADC input capacitor. If the ADC input capacitor ranges from 15pF to 30pF, then the external capacitor is anything between 300pF to 1.5nF, depending on the application. An isolation resistor can be placed in series between the amplifier's output and the external capacitor, as shown in the Typical Application Circuit.

During the load-transient condition described, the driving amplifier must be able to settle to 0.5 x LSB within the ADC acquisition time (tACQ). Assuming a first order approximation, the number of time constants required to settle to 0.5 x LSB is a logarithm function of the number N of bits:

1)

$$k = ln(2^{N+1})$$

The external RC time constant must be such that: 2)

$$k \ge R_L \ge C < t_{ACQ}$$

As an example, consider a 16-bit SAR ADC with 500ns acquisition time and 20pF input capacitor.

From 1): k = 12

Assuming a factor of 50 for the external capacitor:

$$C = 1nF$$

Finally, formula 2) gives:  $R_{L} \leq 40\Omega$

The IC is optimized for very fast load-transient recovery with big capacitive loads and small isolation resistors.

Maxim Integrated

This makes it ideal to drive high-resolution and fast SAR ADCs.

#### **Recommended SAR ADCs**

The MAX9633's wide supply range and fast settling make it ideal for driving high-resolution SAR ADCs, such as the MAX1320. The MAX1320 is a 14-bit, 8-channel, simultaneous-sampling ADC that measures analog inputs up to ±5V. Sampling up to 250ksps per channel for eight channels, the MAX1320 achieves 77dB SNR, 90dBc SFDR, and -86dB THD. The MAX1320's fast sample rate and typical input resistance of  $8.6 \text{k}\Omega$  often make it necessary to have a low-noise op amp, such as the MAX9633, driving its inputs. The MAX9633 is also a good fit for an anti-aliasing active filter prior to the MAX1320 as shown in the Typical Application Circuit.

The MAX1320 is part of a family of simultaneous sampling ADCs (MAX1316–MAX1326). Other options include ADCs that measure 0V to 5V inputs, or ±10V inputs, and two 4 or 8 simultaneous input channels. The MAX1320's high speed and resolution make it a fit for multiphase motor control and power-grid monitoring.

The MAX9633 is also well-suited to drive the 16-bit MAX11046 8-channel, simultaneous-sampling, SAR ADC. The MAX11046 is rated for up to 250ksps. An input driver is typically not necessary at sampling rates below 100ksps. For applications that require > 100ksps sample rates, the MAX9633 offers small size, high bandwidth, and ultra-low -100dB THD at 100kHz.

#### Low Noise and Low Distortion

The MAX9633 is designed for applications that require very low voltage noise, making it ideal for low source impedance. When driving 16-bit SAR ADCs with a ±5V full-scale input, such as the MAX11046, the MAX9633 very low input voltage noise density specification guarantees 16-bit resolution up to 10MHz of signal bandwidth.

The MAX9633 is also designed for ultra-low distortion performance. THD specifications in the Electrical Characteristics and Typical Operating Characteristics is calculated up to the 5th harmonic. Even when driving high voltage swing up to 10VP-P, the MAX9633 maintains excellent low distortion operation up and beyond 100kHz of bandwidth.

Besides driving high-resolution and high-bandwidth SAR ADCs, applications that benefit for low-noise and lowdistortion applications can be found in industrial powergrid and smart-grid, industrial motor-control, medical imaging, automated test equipment, instrumentation, and professional audio equipment.

# **Dual 36V Op Amp for 18-Bit SAR ADC Front-End**

#### Input Common Mode and Output Swing

The IC's input common-mode range as well as the output range can swing to the negative rail VEE. These two features are very important for applications where the MAX9633 is used with a single supply (VEE connected to ground). In such a case, being able to swing the input common-mode to the negative rail offers ground-sensing capability.

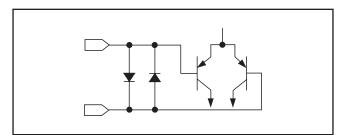

#### **Input Differential Voltage Protection**

During normal op-amp operation, the inverting and noninverting inputs of the IC are at essentially the same voltage. However, either due to fast input voltage transients or due to other fault conditions, these pins can be forced to be at two different voltages.

Internal back-to-back diodes protect the inputs from an excessive differential voltage (Figure 1). Therefore, IN+ and IN- can be any voltage within the range shown in the *Absolute Maximum Ratings*. Note the protection time is still dependent on the package thermal limits.

If the input signal is fast enough to create the internal diode's forward bias condition (0.7), the input signal current must be limited to 20mA or less. If the input signal current is not inherently limited, an external input series resistor can be used to limit the signal input current. Care should be taken in choosing the input series resistor value, since it degrades the low-noise performance of the device.

Figure 1. Input Protection Circuit

#### Electrostatic Discharge (ESD)

The IC has built-in circuits to protect from electrostatic discharge (ESD) events. An ESD event produces a short, high-voltage pulse that is transformed into a short current pulse once it discharges through the device. The built-in protection circuit provides a current path around the op amp that prevents it from being damaged. The energy absorbed by the protection circuit is dissipated as heat. ESD protection is guaranteed up to 6kV with the Human Body Model (HBM).

The Human Body Model simulates the ESD phenomenon wherein a charged body directly transfers its accumulated electrostatic charge to the ESD-sensitive device. A common example of this phenomenon is when a person accumulates static charge by walking across a carpet and then transfers all of the charge to an ESD-sensitive device by touching it.

#### **Power Supplies and Layout**

The IC can operate with dual supplies from  $\pm 2.25V$  to  $\pm 18V$  or with a single supply from  $\pm 4.5V$  to  $\pm 36V$  with respect to ground. When used with dual supplies, bypass both V<sub>CC</sub> and V<sub>EE</sub> with their own 0.1µF capacitor to ground. When used with a single supply, bypass V<sub>CC</sub> with a 0.1µF capacitor to ground. Careful layout technique helps optimize performance by decreasing the amount of stray capacitance at the op amp's inputs and outputs. To decrease stray capacitance, minimize trace lengths by placing external components close to the op amp's pins.

For high-frequency designs, ground vias are critical to provide a ground return path for high-frequency signals and should be placed around the signal traces and near the decoupling capacitors. Signal routing should be short and direct to avoid parasitic effects. Avoid using right angle connectors since they may introduce a capacitive discontinuity and ultimately limit the frequency response.

**Chip Information**

PROCESS: BICMOS

# Dual 36V Op Amp for 18-Bit SAR ADC Front-End

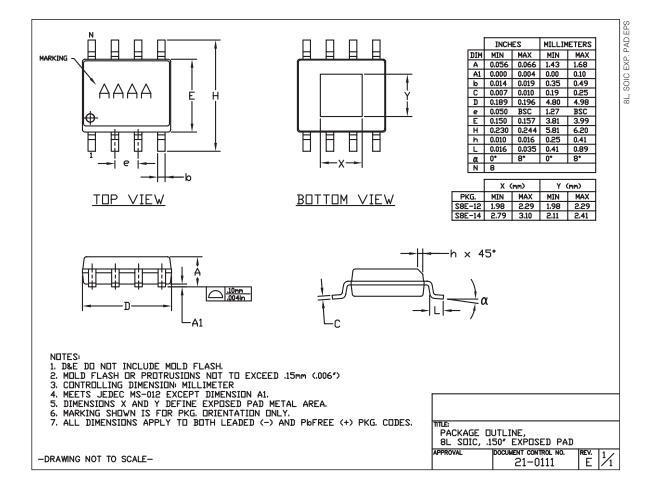

#### **Package Information**

For the latest package outline information and land patterns, go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 8 SO-EP      | S8E+14       | <u>21-0111</u> | <u>90-0151</u>   |

| 8 TDFN-EP    | T833+3       | <u>21-0137</u> | <u>90-0058</u>   |

# MAX9633 Dual 36V Op Amp for 18-Bit SAR ADC Front-End

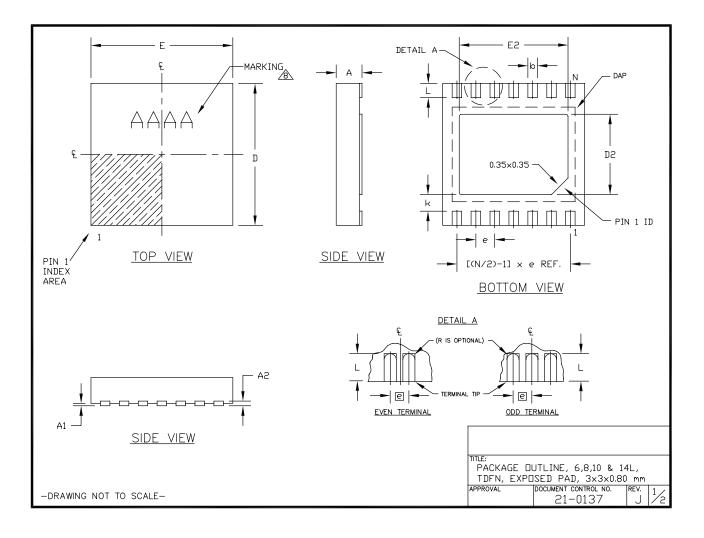

## Package Information (continued)

For the latest package outline information and land patterns, go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

# Dual 36V Op Amp for 18-Bit SAR ADC Front-End

## Package Information (continued)

For the latest package outline information and land patterns, go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

|                                                                                        |                                                                     | ISIONS                                                                |                                                                          | PACKAGE V                                                             | AR IA T                                   | IONS                                             |            |             |                         |           |               |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------|------------|-------------|-------------------------|-----------|---------------|

| SYMBOL                                                                                 | MIN.                                                                | MAX.                                                                  |                                                                          | PKG.CODE                                                              | Ν                                         | D2                                               | E2         | е           | JEDEC SPE C             | b         | [(N/2)-1] x e |

| А                                                                                      | 0.70                                                                | 0.80                                                                  |                                                                          | T633-2                                                                | 6                                         | 1.50±0.10                                        | 2.30±0.10  | 0.95 B SC   | MO229/WEEA              | 0.40±0.05 | 1.90 R EF     |

| D                                                                                      | 2.90                                                                | 3.10                                                                  |                                                                          | T833-2                                                                | 8                                         | 1.50±0.10                                        | 2.30±0.10  | 0.65 B SC   | MO229/WEEC              | 0.30±0.05 | 1.95 R EF     |

| E                                                                                      | 2.90                                                                | 3.10                                                                  |                                                                          | T833-3                                                                | 8                                         | 1.50±0.10                                        | 2.30±0.10  | 0.65 B SC   | MO229/WEEC              | 0.30±0.05 | 1.95 R EF     |

| A1                                                                                     | 0.00                                                                | 0.05                                                                  |                                                                          | T1033-1                                                               | 10                                        | 1.50±0.10                                        | 2.30±0.10  | 0.50 B SC   | MO229 / WE E D3         | 0.25±0.05 | 2.00 R EF     |

| L                                                                                      | 0.20                                                                | 0.40                                                                  |                                                                          | T1033MK-1                                                             | 10                                        | 1.50±0.10                                        | 2.30±0.10  | 0.50 B SC   | MO229/WEED3             | 0.25±0.05 | 2.00 R EF     |

| k                                                                                      | 0.25                                                                | MIN.                                                                  |                                                                          | T1033-2                                                               | 10                                        | 1.50±0.10                                        | 2.30±0.10  | 0.50 B SC   | MO229 / WE E D3         | 0.25±0.05 | 2.00 R EF     |

| A2                                                                                     | 0.20                                                                | R₽F.                                                                  |                                                                          | T1433-1                                                               | 14                                        | 1.70±0.10                                        | 2.30±0.10  | 0.40 B SC   |                         | 0.20±0.05 | 2.40 R EF     |

|                                                                                        |                                                                     |                                                                       |                                                                          | T1433-2                                                               | 14                                        | 1.70±0.10                                        | 2.30±0.10  | 0.40 B SC   |                         | 0.20±0.05 | 2.40 R EF     |

|                                                                                        |                                                                     |                                                                       |                                                                          | T1433-3F                                                              | 14                                        | 1.70±0.10                                        | 2.30±0.10  | 0.40 B SC   |                         | 0.20±0.05 | 2.40 R EF     |

| NOTES:                                                                                 |                                                                     |                                                                       |                                                                          |                                                                       | DECE                                      | DEES                                             |            |             |                         |           |               |

| 1. ALL E<br>2. COPL<br>3. WARP<br>4. PACK<br>5. DRAW<br>6. "N" E<br>7. NUME            | ANARITY<br>AGE SH<br>AGE LE<br>'ING CO<br>S THE<br>BER OF           | ′SHALL<br>IALL NO'<br>NGTH/P,<br>NFORMS<br>TOTAL N<br>LEADS           | NOT EXC<br>F EXCEEL<br>ACKAGE W<br>TO JEDI<br>UMBER C<br>SHOWN A         | OF LEADS.<br>ARE FOR REF                                              | m.<br>DNSID<br>XCEP <sup>-</sup><br>EREN( | ERED AS S<br>T DIMENSIO<br>CE ONLY.              | NS "D2" AN |             | C(S).<br>ND T1433-1 & T | 1433–2.   |               |

| 1. ALL E<br>2. COPL<br>3. WARP<br>4. PACK<br>5. DRAW<br>6. "N" E<br>7. NUME<br>8. MARK | ANARITY<br>AGE SH<br>AGE LE<br>VING CO<br>S THE<br>BER OF<br>ING IS | ´SHALL<br>IALL NO`<br>NGTH/P/<br>NFORMS<br>TOTAL N<br>LEADS<br>FOR PA | NOT EXC<br>EXCEED<br>ACKAGE V<br>TO JED<br>UMBER C<br>SHOWN A<br>CKAGE O | CEED 0.08 m<br>) 0.10 mm.<br>VIDTH ARE C(<br>EC MO229, E<br>)F LEADS. | m.<br>DNSID<br>XCEP<br>EREN<br>EFER       | ERED AS S<br>T DIMENSIO<br>CE ONLY.<br>ENCE ONLY | NS "D2" AN | ND "E2", AN | ( )                     | 1433–2.   |               |

## **Dual 36V Op Amp for 18-Bit SAR ADC Front-End**

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION         | PAGES<br>CHANGED |

|--------------------|------------------|---------------------|------------------|

| 0                  | 9/10             | Initial release     | —                |

| 1                  | 1/11             | Added SO-EP package | 1, 2, 8, 11      |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

14

Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.