HYB25D128160C[E/F/T] HYB25D128400C[C/E/T] HYB25D128800C[C/E/F/T]

128-Mbit Double-Data-Rate SDRAM DDR SDRAM

Rev. 1.51

| HYB25D12                             | HYB25D128160C[E/F/T], HYB25D128400C[C/E/T]                                         |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Revision History: 2006-09, Rev. 1.51 |                                                                                    |  |  |  |  |  |  |  |  |  |  |

| Page                                 | Subjects (major changes since last revision)                                       |  |  |  |  |  |  |  |  |  |  |

| All                                  | Qimonda update                                                                     |  |  |  |  |  |  |  |  |  |  |

| All                                  | Adapted internet edition                                                           |  |  |  |  |  |  |  |  |  |  |

| Previous F                           | Revision: 2006-02, Rev. 1.5                                                        |  |  |  |  |  |  |  |  |  |  |

| 5                                    | Removed product type HYB25D128800CTL-6 and HYB25D128800CE-6                        |  |  |  |  |  |  |  |  |  |  |

| 11                                   | Added product type HYB25D128800CE-5, HYB25D128800CC-5 and HYB25D128800CC-6         |  |  |  |  |  |  |  |  |  |  |

| 74                                   | Changed for D11 tRFC(DDR400) from 70 ns to 65 ns as programmed in byte 42 SPD Code |  |  |  |  |  |  |  |  |  |  |

| Previous F                           | Revision: 2005-11, Rev. 1.4                                                        |  |  |  |  |  |  |  |  |  |  |

### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

techdoc@qimonda.com

## 1 Overview

This chapter contains features and the description.

## 1.1 Features

- · Double data rate architecture: two data transfers per clock cycle

- · Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver

- · DQS is edge-aligned with data for reads and is center-aligned with data for writes

- Differential clock inputs

- Four internal banks for concurrent operation

- · Data mask (DM) for write data

- · DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- · Burst Lengths: 2, 4, or 8

- CAS Latency: 2, 2.5, 3

- · Auto Precharge option for each burst access

- · Auto Refresh and Self Refresh Modes

- RAS-lockout supported  $t_{RAP}$ = $t_{RCD}$

- 7.8 μs Maximum Average Periodic Refresh Interval

- 2.5 V (SSTL\_2 compatible) I/O

- $V_{\rm DDQ}$  = 2.5 V  $\pm$  0.2 V (DDR266A, DDR333);  $V_{\rm DDQ}$  = 2.6 V  $\pm$  0.1 V (DDR400)

- $V_{\rm DD}$  = 2.5 V ± 0.2 V (DDR266A, DDR333);  $V_{\rm DD}$  = 2.6 V ± 0.1 V (DDR400)

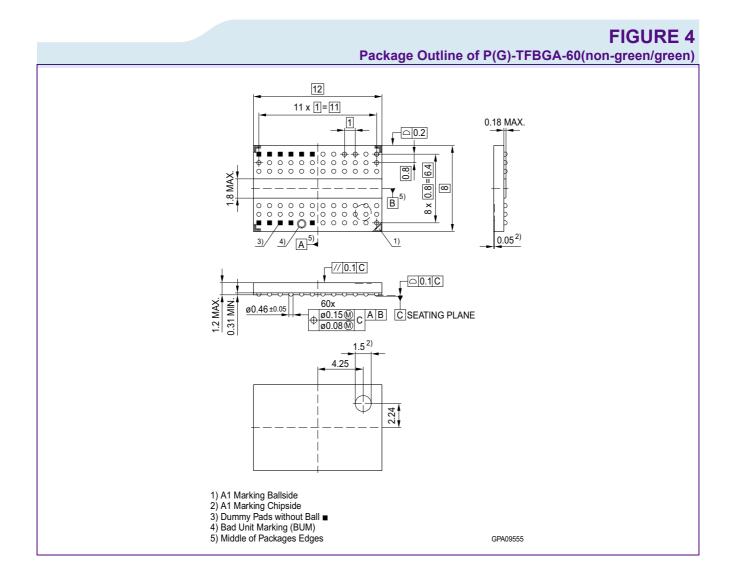

- P(G)-TFBGA-60 package with 3 depopulated rows (8 × 12 mm²)

- P(G)-TSOPII-66 package

- · Lead- and halogene-free = green product

|                        |           |                      |             |             | TABI        | LE 1 |  |  |  |  |  |  |  |

|------------------------|-----------|----------------------|-------------|-------------|-------------|------|--|--|--|--|--|--|--|

| Performan              |           |                      |             |             |             |      |  |  |  |  |  |  |  |

| Part Number Speed Code |           |                      | <b>-5</b>   | -6          | <b>-</b> 7  | Unit |  |  |  |  |  |  |  |

| Speed Grade            | Component |                      | DDR400B     | DDR333      | DDR266A     | _    |  |  |  |  |  |  |  |

|                        | Module    |                      | PC3200-3033 | PC2700-2533 | PC2100-2033 | _    |  |  |  |  |  |  |  |

| max. Clock Frequency   | @CL3      | $f_{\rm CK3}$        | 200         | 166         | _           | MHz  |  |  |  |  |  |  |  |

|                        | @CL2.5    | $f_{\mathrm{CK2.5}}$ | 166         | 166         | 143         | MHz  |  |  |  |  |  |  |  |

|                        | @CL2      | $f_{\rm CK2}$        | 133         | 133         | 133         | MHz  |  |  |  |  |  |  |  |

## 1.2 Description

The 128-Mbit Double-Data-Rate SDRAM is a high-speed CMOS, dynamic random-access memory containing 134,217,728 bits. It is internally configured as a quad-bank DRAM

The 128-Mbit Double-Data-Rate SDRAM uses a double-data-rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2n prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the 128-Mbit Double-Data-Rate SDRAM effectively consists of a single 2n-bit wide, one clock cycle data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins.

A bidirectional data strobe (DQS) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the DDR SDRAM during Reads and by the memory controller during Writes. DQS is edgealigned with data for Reads and center-aligned with data for Writes.

The 128-Mbit Double-Data-Rate SDRAM operates from a differential clock (CK and  $\overline{\text{CK}}$ ; the crossing of CK going HIGH and  $\overline{\text{CK}}$  going LOW is referred to as the positive edge of CK). Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK.

Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an Active command, which is then followed by a Read or Write command. The address bits registered coincident with the Active command are used to select the bank and row to be accessed. The address bits registered coincident with the Read or Write command are used to select the bank and the starting column location for the burst access.

The DDR SDRAM provides for programmable Read or Write burst lengths of 2, 4 or 8 locations. An Auto Precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

As with standard SDRAMs, the pipelined, multibank architecture of DDR SDRAMs allows for concurrent operation, thereby providing high effective bandwidth by hiding row precharge and activation time.

An auto refresh mode is provided along with a power-saving power-down mode. All inputs are compatible with the JEDEC Standard for SSTL\_2. All outputs are SSTL\_2, Class II compatible.

Note: The functionality described and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.

## **TABLE 2**

|                           | Ordering Informationfor non RoHS Compliant Products |                          |                |                         |                |         |               |                    |  |  |  |  |  |  |

|---------------------------|-----------------------------------------------------|--------------------------|----------------|-------------------------|----------------|---------|---------------|--------------------|--|--|--|--|--|--|

| Part Number <sup>1)</sup> | Org.                                                | CAS-RCD-<br>RP Latencies | Clock<br>(MHz) | CAS-RCD-RP<br>Latencies | Clock<br>(MHz) | Speed   | Package       | Note <sup>2)</sup> |  |  |  |  |  |  |

| HYB25D128160CT-5          | ×16                                                 | 3-3-3                    | 200            | 2.5-3-3                 | 166            | DDR400B | P-TSOPII-66-2 |                    |  |  |  |  |  |  |

| HYB25D128800CT-6          | ×8                                                  | 2.5-3-3                  | 166            | 2-3-3                   | 133            | DDR333  |               |                    |  |  |  |  |  |  |

| HYB25D128160CT-6          | ×16                                                 |                          |                |                         |                |         |               |                    |  |  |  |  |  |  |

| HYB25D128400CT-7          | ×4                                                  |                          | 143            |                         |                | DDR266A |               |                    |  |  |  |  |  |  |

| HYB25D128800CC-5          | ×8                                                  | 3-3-3                    | 200            | 2.5-3-3                 | 166            | DDR400B | P-FBGA-60-12  |                    |  |  |  |  |  |  |

| HYB25D128400CC-6          | × <b>4</b>                                          | 2.5-3-3                  | 166            | 2-3-3                   | 133            | DDR333  |               |                    |  |  |  |  |  |  |

| HYB25D128800CC-6          | ×8                                                  |                          |                |                         |                |         |               |                    |  |  |  |  |  |  |

## **TABLE 3**

|                           | Order Information for RoHS Compliant Products |                         |                |                         |                |         |                |                    |  |  |  |  |  |  |

|---------------------------|-----------------------------------------------|-------------------------|----------------|-------------------------|----------------|---------|----------------|--------------------|--|--|--|--|--|--|

| Part Number <sup>1)</sup> | Org.                                          | CAS-RCD-RP<br>Latencies | Clock<br>(MHz) | CAS-RCD-RP<br>Latencies | Clock<br>(MHz) | Speed   | Package        | Note <sup>2)</sup> |  |  |  |  |  |  |

| HYB25D128160CE-5          | ×16                                           | 3-3-3                   | 200            | 2.5-3-3                 | 166            | DDR400B | PG-TSOPII-66-1 |                    |  |  |  |  |  |  |

| HYB25D128800CE-5          | ×8                                            |                         |                |                         |                |         |                |                    |  |  |  |  |  |  |

| HYB25D128800CF-5          |                                               |                         |                |                         |                |         | PG-FBGA-60-19  |                    |  |  |  |  |  |  |

| HYB25D128160CE-6          | ×16                                           | 2.5-3-3                 | 166            | 2-3-3                   | 133            | DDR333  | PG-TSOPII-66-1 |                    |  |  |  |  |  |  |

| HYB25D128400CE-6          | × <b>4</b>                                    |                         |                |                         |                |         |                |                    |  |  |  |  |  |  |

| HYB25D128800CE-6          | ×8                                            |                         |                |                         |                |         |                |                    |  |  |  |  |  |  |

| HYB25D128800CF-6          |                                               |                         |                |                         |                |         | PG-FBGA-60-19  |                    |  |  |  |  |  |  |

| HYB25D128400CE-7          | ×4                                            |                         | 143            |                         |                | DDR266A | PG-TSOPII-66-1 |                    |  |  |  |  |  |  |

<sup>1)</sup> HYB: designator for memory components 25D: DDR SDRAMs at  $V_{\rm DDQ}$  = 2.5 V 128: 128-Mbit density 400/800/160: Product variations ×4, ×8 and ×16 C: Die revision C T/E/C: Package type TSOP and FBGA L: Low power version (available on request) - these components are specifically selected for low  $I_{\rm DD6}$  Self Refresh currents -5/6/7/7F/8: speed grade - see **Table 2**

<sup>2)</sup> RoHS Compliant Product: Restriction of the use of certain hazardous substances (RoHS) in electrical and electronic equipment as defined in the directive 2002/95/EC issued by the European Parliament and of the Council of 27 January 2003. These substances include mercury, lead, cadmium, hexavalent chromium, polybrominated biphenyls and polybrominated biphenyl ethers.

# 2 Pin Configuration

The pin configuration of a DDR SDRAM is listed by function in **Table 4** (60 pins). The abbreviations used in the Pin#/Buffer# column are explained in **Table 5** and **Table 6** respectively. The pin numbering for FBGA is depicted in **Figure 1** and that of the TSOP package in **Figure 2**.

|              |      |             |                | TABLE 4                                         |

|--------------|------|-------------|----------------|-------------------------------------------------|

|              |      |             |                | Pin Configuration of DDR SDRAM                  |

| Ball#/Pin#   | Name | Pin<br>Type | Buffer<br>Type | Function                                        |

| Clock Signal | s    |             |                |                                                 |

| G2, 45       | CK   | I           | SSTL           | Clock Signal                                    |

| G3, 46       | CK   | I           | SSTL           | Complementary Clock Signal                      |

| H3, 44       | CKE  | I           | SSTL           | Clock Enable                                    |

| Control Sign | als  |             | •              | ·                                               |

| H7, 23       | RAS  | I           | SSTL           | Row Address Strobe                              |

| G8, 22       | CAS  | I           | SSTL           | Column Address Strobe                           |

| G7, 21       | WE   | I           | SSTL           | Write Enable                                    |

| H8, 24       | CS   | I           | SSTL           | Chip Select                                     |

| Address Sign | nals |             |                |                                                 |

| J8, 26       | BA0  | I           | SSTL           | Bank Address Bus 2:0                            |

| J7, 27       | BA1  | I           | SSTL           |                                                 |

| K7, 29       | A0   | I           | SSTL           | Address Bus 11:0                                |

| L8, 30       | A1   | I           | SSTL           |                                                 |

| L7, 31       | A2   | I           | SSTL           |                                                 |

| M8, 32       | A3   | I           | SSTL           |                                                 |

| M2, 35       | A4   | I           | SSTL           |                                                 |

| L3, 36       | A5   | I           | SSTL           |                                                 |

| L2, 37       | A6   | I           | SSTL           |                                                 |

| K3, 38       | A7   | I           | SSTL           |                                                 |

| K2, 39       | A8   | I           | SSTL           |                                                 |

| J3, 40       | A9   | I           | SSTL           |                                                 |

| K8, 28       | A10  | I           | SSTL           |                                                 |

|              | AP   | I           | SSTL           |                                                 |

| J2, 41       | A11  | I           | SSTL           |                                                 |

| H2, 42       | A12  | I           | SSTL           | Address Signal 12 Note: 256 Mbit or larger dies |

|              | NC   | NC          | _              | Note: 128 Mbit or smaller dies                  |

| F9, 17       | A13  | I           | SSTL           | Address Signal 13                               |

|              |      |             |                | Note: 1 Gbit based dies                         |

|              | NC   | NC          | _              | Note: 512 Mbit or smaller dies                  |

| Ball#/Pin#     | Name            | Pin<br>Type | Buffer<br>Type | Function         |

|----------------|-----------------|-------------|----------------|------------------|

| Data Signals > | <br>∢4 organiza | tion        |                |                  |

| B7, 5          | DQ0             | I/O         | SSTL           | Data Signal 3:0  |

| D7, 11         | DQ1             | I/O         | SSTL           |                  |

| D3, 56         | DQ2             | I/O         | SSTL           |                  |

| B3, 62         | DQ3             | I/O         | SSTL           |                  |

| Data Strobe ×4 | 4 organisat     | ion         | '              |                  |

| E3, 51         | DQS             | I/O         | SSTL           | Data Strobe      |

| Data Mask ×4   | organizatio     | n           |                |                  |

| F3, 47         | DM              | 1           | SSTL           | Data Mask        |

| Data Signals > | <8 organiza     | tion        |                |                  |

| A8, 2          | DQ0             | I/O         | SSTL           | Data Signal 7:0  |

| B7, 5          | DQ1             | I/O         | SSTL           |                  |

| C7, 8          | DQ2             | I/O         | SSTL           |                  |

| D7, 11         | DQ3             | I/O         | SSTL           |                  |

| D3, 56         | DQ4             | I/O         | SSTL           |                  |

| C3, 59         | DQ5             | I/O         | SSTL           | Data Signal      |

| B3, 62         | DQ6             | I/O         | SSTL           |                  |

| A2, 65         | DQ7             | I/O         | SSTL           |                  |

| Data Strobe ×  | 8 organisat     | ion         |                |                  |

| E3, 51         | DQS             | I/O         | SSTL           | Data Strobe      |

| Data Mask ×8   | organizatio     | n           |                |                  |

| F3, 47         | DM              | I           | SSTL           | Data Mask        |

| Data Signals > | ⊲16 organiz     | ation       | ·              |                  |

| A8, 2          | DQ0             | I/O         | SSTL           | Data Signal 15:0 |

| B9, 4          | DQ1             | I/O         | SSTL           |                  |

| B7, 5          | DQ2             | I/O         | SSTL           |                  |

| C9, 7          | DQ3             | I/O         | SSTL           |                  |

| C7, 8          | DQ4             | I/O         | SSTL           |                  |

| D9, 10         | DQ5             | I/O         | SSTL           |                  |

| D7, 11         | DQ6             | I/O         | SSTL           |                  |

| E9, 13         | DQ7             | I/O         | SSTL           |                  |

| E1, 54         | DQ8             | I/O         | SSTL           |                  |

| D3, 56         | DQ9             | I/O         | SSTL           |                  |

| D1, 57         | DQ10            | I/O         | SSTL           |                  |

| C3, 59         | DQ11            | I/O         | SSTL           |                  |

| C1, 60         | DQ12            | I/O         | SSTL           |                  |

| B3, 62         | DQ13            | I/O         | SSTL           |                  |

| B1, 63         | DQ14            | I/O         | SSTL           |                  |

| A2, 65         | DQ15            | I/O         | SSTL           |                  |

| Ball#/Pin#                                  | Name         | Pin<br>Type | Buffer<br>Type | Function                             |

|---------------------------------------------|--------------|-------------|----------------|--------------------------------------|

| Data Strobe ×10                             | organiza     | tion        | '              |                                      |

| E3, 51                                      | UDQS         | I/O         | SSTL           | Data Strobe Upper Byte               |

| E7, 16                                      | LDQS         | I/O         | SSTL           | Data Strobe Lower Byte               |

| Data Mask ×16                               | organizati   | on          |                |                                      |

| F3, 47                                      | UDM          | I           | SSTL           | Data Mask Upper Byte                 |

| F7, 20                                      | LDM          | I           | SSTL           | Data Mask Lower Byte                 |

| Power Supplies                              | 5            |             |                |                                      |

| F1, 49                                      | $V_{REF}$    | Al          | <b>—</b>       | I/O Reference Voltage                |

| A9, B2, C8, D2,<br>E8, 3, 9, 15, 55,<br>61  | $V_{DDQ}$    | PWR         | _              | I/O Driver Power Supply              |

| A7, F8, M3, M7,<br>1, 18, 33                | $V_{DD}$     | PWR         | _              | Power Supply                         |

| A1, B8, C2, D8,<br>E2, 6, 12, 52,<br>58, 64 | $V_{SSQ}$    | PWR         | _              | Power Supply                         |

| F2, 34                                      | $V_{\rm SS}$ | PWR         | _              | Power Supply                         |

| Not Connected                               |              |             |                |                                      |

| A2, 65                                      | NC           | NC          | _              | Not Connected                        |

|                                             |              |             |                | Note: x4 organization                |

| A8, 2                                       | NC           | NC          | -              | Not Connected                        |

|                                             |              |             |                | Note: x4 organization                |

| B1, 63                                      | NC           | NC          | -              | Not Connected                        |

|                                             |              |             |                | Note: x8 and x4 organisation         |

| B9, 4                                       | NC           | NC          | -              | Not Connected                        |

| 0.4.00                                      |              | 1           |                | Note: ×8 and ×4 organization         |

| C1, 60                                      | NC           | NC          | -              | Not Connected                        |

| 00.50                                       | NO           | NO          |                | Note: ×8 and ×4 organization         |

| C3, 59                                      | NC           | NC          | -              | Not Connected  Note: ×4 organization |

| C7, 8                                       | NC           | NC          |                | Not Connected                        |

| C7, 6                                       | INC          | INC         | -              | Note: ×4 organization                |

| C9, 7                                       | NC           | NC          | +_             | Not Connected                        |

|                                             | 1            |             |                | Note: ×8 and ×4 organization         |

| D1, 57                                      | NC           | NC          | +_             | Not Connected                        |

| , -                                         |              |             |                | Note: ×8 and ×4 organization         |

| D9, 10                                      | NC           | NC          | <del> </del>   | Not Connected                        |

|                                             |              |             |                | Note: x8 and x4 organization         |

| E1, 54                                      | NC           | NC          | _              | Not Connected                        |

|                                             |              |             |                | Note: x8 and x4 organization         |

| Ball#/Pin#      | Name | Pin<br>Type | Buffer<br>Type | Function                         |

|-----------------|------|-------------|----------------|----------------------------------|

| E7, 16          | NC   | NC          | _              | Not Connected                    |

|                 |      |             |                | Note: x8 and x4 organization     |

| E9, 13          | NC   | NC          | <u> </u>       | Not Connected                    |

|                 |      |             |                | Note: x8 and x4 organization     |

| F7, 20          | NC   | NC          | _              | Not Connected                    |

|                 |      |             |                | Note: x8 and x4 organization     |

| F9, 14, 17, 19, | NC   | NC          | _              | Not Connected                    |

| 25,43, 50, 53   |      |             |                | Note: x16,x8 and x4 organization |

## **TABLE 5**

### **Abbreviations for Pin Type**

|              | Abbieviations for i'm Type                  |

|--------------|---------------------------------------------|

| Abbreviation | Description                                 |

| I            | Standard input-only pin. Digital levels.    |

| 0            | Output. Digital levels.                     |

| I/O          | I/O is a bidirectional input/output signal. |

| Al           | Input. Analog levels.                       |

| PWR          | Power                                       |

| GND          | Ground                                      |

| NC           | Not Connected                               |

## **TABLE 6**

## **Abbreviations for Buffer Type**

| Abbreviation | Description                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| SSTL         | Serial Stub Terminated Logic (SSTL2)                                                                                                    |

| LV-CMOS      | Low Voltage CMOS                                                                                                                        |

| CMOS         | CMOS Levels                                                                                                                             |

| OD           | Open Drain. The corresponding pin has 2 operational states, active low and tristate, and allows multiple devices to share as a wire-OR. |

## FIGURE 1

#### Pin Configuration P-TFBGA-60 Top View

|               |               |              |   |      |               |                    |               |           |       |               |               | oin C         | ontig     | urati | on F | '-TFB    | GA-6          | 0 Top     |

|---------------|---------------|--------------|---|------|---------------|--------------------|---------------|-----------|-------|---------------|---------------|---------------|-----------|-------|------|----------|---------------|-----------|

|               |               |              |   |      |               |                    |               |           |       |               |               |               |           |       |      |          |               |           |

|               |               |              |   |      |               |                    |               |           |       |               |               |               |           |       |      |          |               |           |

|               |               |              |   |      |               |                    |               |           |       |               |               |               |           |       |      |          |               |           |

| 1             | 2             | 3            | 4 | 5    | 6             | 7                  | 8             | 9         |       | 1             | 2             | 3             | 4         | 5     | 6    | 7        | 8             | 9         |

| $V_{\rm SSQ}$ | N.C.          | $V_{\rm SS}$ |   | Α    |               | $V_{DD}$           | N.C.          | $V_{DDQ}$ |       | $V_{\rm SSQ}$ | DQ7           | $V_{\rm SS}$  |           | Α     |      | $V_{DD}$ | DQ0           | $V_{DDQ}$ |

| N.C.          | $V_{DDQ}$     | DQ3          |   | В    |               | DQ0                | $V_{\rm SSQ}$ | N.C.      |       | N.C.          | $V_{DDQ}$     | DQ6           |           | В     |      | DQ1      | $V_{\rm SSQ}$ | N.C.      |

| N.C.          | $V_{\rm SSQ}$ | N.C.         |   | С    |               | N.C.               | $V_{DDQ}$     | N.C.      |       | N.C.          | $V_{\rm SSQ}$ | DQ5           |           | С     |      | DQ2      | $V_{DDQ}$     | N.C.      |

| N.C.          | $V_{DDQ}$     | DQ2          |   | D    |               | DQ1                | $V_{\rm SSQ}$ | N.C.      |       | N.C.          | $V_{DDQ}$     | DQ4           |           | D     |      | DQ3      | $V_{\rm SSQ}$ | N.C.      |

| N.C.          | $V_{\rm SSQ}$ | DQS          |   | E    |               | N.C.               | $V_{DDQ}$     | N.C.      |       | N.C.          | $V_{\rm SSQ}$ | DQS           |           | Е     |      | N.C.     | $V_{DDQ}$     | N.C.      |

| $V_{REF}$     | $V_{\rm SS}$  | DM           |   | F    |               | N.C.               | _             | NC/A13    |       | $V_{REF}$     | $V_{\rm SS}$  | DM            |           | F     |      | N.C.     |               | NC/A13    |

|               | СК            | СК           |   | G    |               | WE                 | CAS           |           |       |               | СК            | СК            |           | G     |      | WE       | CAS           |           |

|               | NC/A12        | CKE          |   | Н    |               | RAS                | cs            |           |       |               | NC/A12        | CKE           |           | Н     |      | RAS      | CS            |           |

|               | A11           | A9           |   | J    |               | BA1                | BA0           |           |       |               | A11           | A9            |           | J     |      | BA1      | BA0           |           |

|               | A8            | A7           |   | K    |               | A0                 | A10/AP        |           |       |               | A8            | A7            |           | K     |      | A0       | A10/AP        |           |

|               | A6            | A5           |   | L    |               | A2                 | A1            |           |       |               | A6            | A5            |           | L     |      | A2       | A1            |           |

|               | A4            | $V_{\rm SS}$ |   | М    |               | $V_{DD}$           | А3            |           |       |               | A4            | $V_{\rm SS}$  |           | М     |      | $V_{DD}$ | A3            |           |

|               |               |              |   | (x4) |               |                    |               |           |       |               |               |               |           | (x8)  |      |          |               |           |

|               |               |              |   |      | 1             | 2                  | 3             | 4         | 5     | 6             | 7             | 8             | 9         |       |      |          |               |           |

|               |               |              |   |      | $V_{\rm SSQ}$ | DQ15               | $V_{\rm SS}$  |           | Α     |               | $V_{DD}$      | DQ0           | $V_{DDQ}$ |       |      |          |               |           |

|               |               |              |   |      | DQ14          | $V_{\mathrm{DDQ}}$ | DQ13          |           | В     |               | DQ2           | $V_{\rm SSQ}$ | DQ1       |       |      |          |               |           |

|               |               |              |   |      | DQ12          | $V_{\rm SSQ}$      | DQ11          |           | С     |               | DQ4           | $V_{DDQ}$     | DQ3       |       |      |          |               |           |

|               |               |              |   |      | DQ10          | $V_{DDQ}$          | DQ9           |           | D     |               | DQ6           | $V_{\rm SSQ}$ | DQ5       |       |      |          |               |           |

|               |               |              |   |      | DQ8           | $V_{\rm SSQ}$      | UDQS          |           | Е     |               | LDQS          | $V_{DDQ}$     | DQ7       |       |      |          |               |           |

|               |               |              |   |      | $V_{REF}$     | $V_{\rm SS}$       | UDM           |           | F     |               | LDM           | $V_{DD}$      | NC/A13    |       |      |          |               |           |

|               |               |              |   |      |               | СК                 | СК            |           | G     |               | WE            | CAS           |           |       |      |          |               |           |

|               |               |              |   |      |               | NC/A12             | CKE           |           | Н     |               | RAS           | cs            |           |       |      |          |               |           |

|               |               |              |   |      |               | A11                | A9            |           | J     |               | BA1           | BA0           |           |       |      |          |               |           |

|               |               |              |   |      |               | A8                 | A7            |           | K     |               | A0            | A10/AP        |           |       |      |          |               |           |

|               |               |              |   |      |               | A6                 | A5            |           | L     |               | A2            | A1            |           |       |      |          |               |           |

|               |               |              |   |      |               | A4                 | $V_{\rm SS}$  |           | М     |               | $V_{DD}$      | A3            |           |       |      |          |               |           |

|               |               |              |   |      |               |                    |               |           | (x16) |               |               |               |           |       |      |          | MPPI          | 00060     |

MPPD0072

FIGURE 2 Pin Configuration P-TSOPII-66-1 x 4 x 8 x 16  $V_{\rm SS}$  $V_{\mathsf{DD}}$  $V_{\mathsf{DD}}$  $V_{\mathsf{DD}}$ 66  $V_{\rm SS}$  $V_{\rm SS}$ □2 65 N.C. DQ0 DQ0 DQ15 DQ7 N.C. □ 3 64  $V_{\mathsf{DDQ}}$  $V_{\mathsf{DDQ}}$  $V_{\rm SSQ}$  $V_{SSQ}$  $V_{\mathsf{DDQ}}$  $V_{\rm SSQ}$ N.C. N.C. DQ1 63 DQ14 N.C. N.C. DQ0 DQ1 DQ2 □ 5 62 DQ13 DQ6 DQ3 6 61  $V_{\mathsf{DDQ}}$  $V_{\mathsf{DDQ}}$  $V_{\rm SSQ}$  $V_{\mathrm{SSQ}}$  $V_{\mathrm{SSQ}}$  $V_{\mathsf{DDQ}}$ DQ3 □7 60 N.C. N.C. DQ12 N.C. N.C. N.C. DQ2 DQ4 **□**8 59 DQ11 DQ5 N.C. □9 58  $V_{\mathsf{DDQ}}$  $V_{\mathsf{DDQ}}$  $V_{\mathsf{DDQ}}$  $V_{\rm SSO}$  $V_{\rm SSQ}$  $V_{SSQ}$ N.C. N.C. DQ5 10 57 DQ10 N.C. N.C. DQ6 □ 11 DQ9 DQ2 DQ1 DQ3 56 DQ4 ☐ 12  $V_{\mathrm{SSQ}}$ 55  $V_{\mathsf{DDQ}}$  $V_{\mathsf{DDQ}}$  $V_{\rm SSQ}$  $V_{\rm SSQ}$  $V_{\mathsf{DDQ}}$ N.C. N.C. DQ7 13 54 DQ8 N.C. N.C. N.C. ☐ 14 N.C. N.C. 53 N.C. N.C. N.C.  $V_{\mathsf{DDQ}}$ ☐ 15 52  $V_{\rm SSQ}$  $V_{\mathsf{DDQ}}$  $V_{\mathsf{DDQ}}$  $V_{\rm SSQ}$  $V_{\mathrm{SSQ}}$ □ 16 **LDQS** 51 **UDQS** DQS DQS N.C. N.C. N.C.,A13 N.C.,A13 N.C.,A13 17 50 N.C. N.C. N.C. ☐ 18 49  $V_{\mathsf{DD}}$  $V_{\mathsf{DD}}$  $V_{\mathsf{DD}}$  $V_{\mathsf{REF}}$  $V_{\mathsf{REF}}$  $V_{\mathsf{REF}}$ ☐ 19 48 N.C. N.C. N.C.  $V_{\mathrm{SS}}$  $V_{\rm SS}$  $V_{\mathrm{SS}}$ **20** N.C. N.C. LDM 47 UDM DM DM WE WE WE ☐ 21 СK СK  $\overline{\mathsf{CK}}$ 46 CAS CAS CAS 22 45 CK CK CK RAS RAS RAS ☐ 23 44 CKE CKE CKE CS0 CS<sub>0</sub> CS<sub>0</sub> 24 43 N.C. N.C. N.C. N.C. ☐ 25 42 N.C.,A12 N.C.,A12 N.C.,A12 N.C. N.C. ☐ 26 BA0 BA0 BA0 41 A11 A11 A11 ☐ 27 Α9 Α9 BA1 BA1 BA1 40 Α9 28 A10/AP A10/AP A10/AP 39 Α8 Α8 **A8 29** 38 A0 A0 A0 Α7 A7 Α7 Α1 Α1 Α1 **30** 37 Α6 A6 A6 □ 31 A2 A2 36 Α5 Α5 Α5 A2 □ 32 А3 А3 А3 35 A4 A4 A4 □ 33 34  $V_{\mathsf{DD}}$  $V_{\mathsf{DD}}$  $V_{\mathsf{DD}}$  $V_{\rm SS}$  $V_{\mathrm{SS}}$  $V_{\rm SS}$

## 3 Functional Description

The 128-Mbit Double-Data-Rate SDRAM is a high-speed CMOS, dynamic random-access memory containing 134,217,728 bits. The 128-Mbit Double-Data-Rate SDRAM is internally configured as a quad-bank DRAM.

The 128-Mbit Double-Data-Rate SDRAM uses a double-data-rate architecture to achieve high-speed operation. The double-data-rate architecture is essentially a 2n prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the 128-Mbit Double-Data-Rate SDRAM consists of a single 2n-bit wide, one clock cycle data transfer at the internal DRAM core and two corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an Active command, which is then followed by a Read or Write command. The address bits registered coincident with the Active command are used to select the bank and row to be accessed (BA0, BA1 select the bank; A0-A11 select the row). The address bits registered coincident with the Read or Write command are used to select the starting column location for the burst access.

Prior to normal operation, the DDR SDRAM must be initialized. The following sections provide detailed information covering device initialization, register definition, command descriptions and device operation.

| BA1 | BA0 | A12      | A11      | A10 | A9       | A8 | A7       | A6 | A5       | A4 | А3       | A2 | A1       | A0       |

|-----|-----|----------|----------|-----|----------|----|----------|----|----------|----|----------|----|----------|----------|

| 0   | 0   | MODE     |          |     |          |    |          |    | CL       |    |          | BL |          |          |

|     |     | <u> </u> | <u> </u> |     | <u> </u> |    | <u> </u> |    | <u> </u> | I  | <u> </u> |    | <u> </u> | MPBL0160 |

## **TABLE 7**

## MR Mode Register Definition (BA[1:0] = $00_R$ )

|          |        |                    | int mode register berinden (BA[1.0] 008/                                                                                                                                                                                                      |

|----------|--------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field    | Bits   | Type <sup>1)</sup> | Description                                                                                                                                                                                                                                   |

| BL       | [2:0]  | w                  | Burst Length Number of sequential bits per DQ related to one read/write command.  Note: All other bit combinations are RESERVED.  001 <sub>B</sub> 2 010 <sub>B</sub> 4 011 <sub>B</sub> 8                                                    |

| ВТ       | 3      | w                  | Burst Type See Table 8 for internal address sequence of low order address bits.  0 <sub>B</sub> Sequential 1 <sub>B</sub> Interleaved                                                                                                         |

| CL       | [6:4]  | w                  | CAS Latency Number of full clocks from read command to first data valid window.  Note: All other bit combinations are RESERVED.  010 <sub>B</sub> 2 011 <sub>B</sub> 3 101 <sub>B</sub> 1.5 Note: DDR200 components only 110 <sub>B</sub> 2.5 |

| MOD<br>E | [11:7] | w                  | Operating Mode  Note: All other bit combinations are RESERVED.  00000 <sub>B</sub> Normal Operation without DLL Reset  00010 <sub>B</sub> Normal Operation with DLL Reset                                                                     |

<sup>1)</sup> w=write

## TABLE 8

| Burst Definition |                         |   |            |                                  |                    |  |  |  |  |  |

|------------------|-------------------------|---|------------|----------------------------------|--------------------|--|--|--|--|--|

| Burst Length     | Starting Column Address |   | nn Address | Order of Accesses Within a Burst |                    |  |  |  |  |  |

|                  | A2 A1                   |   | A0         | Type = Sequential                | Type = Interleaved |  |  |  |  |  |

| 2                |                         |   | 0          | 0-1                              | 0-1                |  |  |  |  |  |

|                  |                         |   | 1          | 1-0                              | 1-0                |  |  |  |  |  |

| 4                |                         | 0 | 0          | 0-1-2-3                          | 0-1-2-3            |  |  |  |  |  |

|                  |                         | 0 | 1          | 1-2-3-0                          | 1-0-3-2            |  |  |  |  |  |

|                  |                         | 1 | 0          | 2-3-0-1                          | 2-3-0-1            |  |  |  |  |  |

|                  |                         | 1 | 1          | 3-0-1-2                          | 3-2-1-0            |  |  |  |  |  |

| 8                | 0                       | 0 | 0          | 0-1-2-3-4-5-6-7                  | 0-1-2-3-4-5-6-7    |  |  |  |  |  |

|                  | 0                       | 0 | 1          | 1-2-3-4-5-6-7-0                  | 1-0-3-2-5-4-7-6    |  |  |  |  |  |

|                  | 0                       | 1 | 0          | 2-3-4-5-6-7-0-1                  | 2-3-0-1-6-7-4-5    |  |  |  |  |  |

|                  | 0                       | 1 | 1          | 3-4-5-6-7-0-1-2                  | 3-2-1-0-7-6-5-4    |  |  |  |  |  |

|                  | 1                       | 0 | 0          | 4-5-6-7-0-1-2-3                  | 4-5-6-7-0-1-2-3    |  |  |  |  |  |

|                  | 1                       | 0 | 1          | 5-6-7-0-1-2-3-4                  | 5-4-7-6-1-0-3-2    |  |  |  |  |  |

|                  | 1                       | 1 | 0          | 6-7-0-1-2-3-4-5                  | 6-7-4-5-2-3-0-1    |  |  |  |  |  |

|                  | 1                       | 1 | 1          | 7-0-1-2-3-4-5-6                  | 7-6-5-4-3-2-1-0    |  |  |  |  |  |

#### **Notes**

- 1. For a burst length of two, A1-Ai selects the two-data-element block; A0 selects the first access within the block.

- 2. For a burst length of four, A2-Ai selects the four-data-element block; A0-A1 selects the first access within the block.

- 3. For a burst length of eight, A3-Ai selects the eight-data- element block; A0-A2 selects the first access within the block.

- 4. Whenever a boundary of the block is reached within a given sequence above, the following access wraps within the block.

## **TABLE 9**

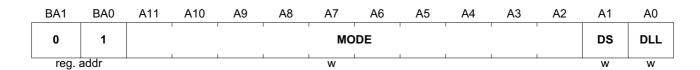

## Extended Mode Register Definition (BA[1:0] = 01<sub>B</sub>)

|       |        |                    | 3 · · · · · · · · · · · · · · · · · · ·                                                       |

|-------|--------|--------------------|-----------------------------------------------------------------------------------------------|

| Field | Bits   | Type <sup>1)</sup> | Description                                                                                   |

| DLL   | 0      | w                  | DLL Status 0 <sub>B</sub> Enabled 1 <sub>B</sub> Disabled                                     |

| DS    | 1      | w                  | Drive Strength  0 <sub>B</sub> Normal  1 <sub>B</sub> Weak                                    |

| MODE  | [11:2] | w                  | Operating Mode  Note: All other bit combinations are RESERVED.  00000000000B Normal Operation |

<sup>1)</sup> w=write

## TABLE 10

## Truth Table 1a: Commands

|                                                        |    |     |     |    | Truth Table | ra: Con | imanus |

|--------------------------------------------------------|----|-----|-----|----|-------------|---------|--------|

| Name (Function)                                        | cs | RAS | CAS | WE | Address     | MNE     | Note   |

| Deselect (NOP)                                         | Н  | Х   | Х   | Х  | Х           | NOP     | 1)2)   |

| No Operation (NOP)                                     | L  | Н   | Н   | Н  | Х           | NOP     | 1)2)   |

| Active (Select Bank And Activate Row)                  | L  | L   | Н   | Н  | Bank/Row    | ACT     | 1)3)   |

| Read (Select Bank And Column, And Start Read Burst)    | L  | Н   | L   | Н  | Bank/Col    | Read    | 1)4)   |

| Write (Select Bank And Column, And Start Write Burst)  | L  | Н   | L   | L  | Bank/Col    | Write   | 1)4)   |

| Burst Terminate                                        | L  | Н   | Н   | L  | Х           | BST     | 1)5)   |

| Precharge (Deactivate Row In Bank Or Banks)            | L  | L   | Н   | L  | Code        | PRE     | 1)6)   |

| Auto Refresh Or Self Refresh (Enter Self Refresh Mode) | L  | L   | L   | Н  | Х           | AR/SR   | 1)7)8) |

| Mode Register Set                                      | L  | L   | L   | L  | Op-Code     | MRS     | 1)9)   |

|                                                        |    |     |     |    |             |         |        |

- 1) CKE is HIGH for all commands shown except Self Refresh.  $V_{\rm REF}$  must be maintained during Self Refresh operation.

- 2) Deselect and NOP are functionally interchangeable.

- 3) BA0-BA1 provide bank address and A0-A11 provide row address.

- 4) BA0, BA1 provide bank address; A0-Ai provide column address (where i = 8 for x16, i = 9 for x8 and 9, 11 for x4); A10 HIGH enables the Auto Precharge feature (nonpersistent), A10 LOW disables the Auto Precharge feature.

- 5) Applies only to read bursts with Auto Precharge disabled; this command is undefined (and should not be used) for read bursts with Auto Precharge enabled or for write bursts.

- 6) A10 LOW: BA0, BA1 determine which bank is precharged. A10 HIGH: all banks are precharged and BA0, BA1 are "Don't Care".

- 7) This command is Auto Refresh if CKE is HIGH; Self Refresh if CKE is LOW.

- 8) Internal refresh counter controls row and bank addressing; all inputs and I/Os are "Don't Care" except for CKE.

- 9) BA0, BA1 select either the Base or the Extended Mode Register (BA0 = 0, BA1 = 0 selects Mode Register; BA0 = 1, BA1 = 0 selects Extended Mode Register; other combinations of BA0-BA1 are reserved; A0-A11 provide the op-code to be written to the selected Mode Register).

## **TABLE 11**

| Truth Table 1b: DM Operat |    |       |      |  |  |  |

|---------------------------|----|-------|------|--|--|--|

| Name (Function)           | DM | DQs   | Note |  |  |  |

| Write Enable              | L  | Valid | 1)   |  |  |  |

| Write Inhibit             | Н  | Х     | 1)   |  |  |  |

<sup>1)</sup> Used to mask write data; provided coincident with the corresponding data.

## **TABLE 12**

| Truth Table 2: Clock Enable (CKE |                   |                  |                 |                            |       |  |  |  |  |  |

|----------------------------------|-------------------|------------------|-----------------|----------------------------|-------|--|--|--|--|--|

| <b>Current State</b>             | CKE n-1           | CKEn             | Command n       | Action n                   | Notes |  |  |  |  |  |

|                                  | Previous<br>Cycle | Current<br>Cycle |                 |                            |       |  |  |  |  |  |

| Self Refresh                     | L                 | L                | X               | Maintain Self-Refresh      | 1)    |  |  |  |  |  |

| Self Refresh                     | L                 | Н                | Deselect or NOP | Exit Self-Refresh          | 2)    |  |  |  |  |  |

| Power Down                       | L                 | L                | X               | Maintain Power-Down        |       |  |  |  |  |  |

| Power Down                       | L                 | Н                | Deselect or NOP | Exit Power-Down            |       |  |  |  |  |  |

| All Banks Idle                   | Н                 | L                | Deselect or NOP | Precharge Power-Down Entry |       |  |  |  |  |  |

| All Banks Idle                   | Н                 | L                | AUTO REFRESH    | Self Refresh Entry         |       |  |  |  |  |  |

| Bank(s) Active                   | Н                 | L                | Deselect or NOP | Active Power-Down Entry    |       |  |  |  |  |  |

|                                  | Н                 | Н                | See Table 13    | _                          |       |  |  |  |  |  |

<sup>1)</sup>  $V_{\mathrm{REF}}$  must be maintained during Self Refresh operation

#### **Notes**

- 1. CKEn is the logic state of CKE at clock edge n: CKE n-1 was the state of CKE at the previous clock edge.

- 2. Current state is the state of the DDR SDRAM immediately prior to clock edge n.

- 3. COMMAND n is the command registered at clock edge n, and ACTION n is a result of COMMAND n.

- 4. All states and sequences not shown are illegal or reserved.

<sup>2)</sup> Deselect or NOP commands should be issued on any clock edges occurring during the Self Refresh Exit ( $t_{XSNR}$ ) period. A minimum of 200 clock cycles are needed before applying a read command to allow the DLL to lock to the input clock.

#### TABLE 13

#### Truth Table 3: Current State Bank n - Command to Bank n (same bank)

| Tradit Table 5. Current State Bank II - Command to Bank II (Same Bank) |             |                       |                  |                  |                                                                |                                                                                                                                                                                                                                        |                                                                                                       |  |  |  |

|------------------------------------------------------------------------|-------------|-----------------------|------------------|------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| Current State                                                          | cs          | RAS                   | CAS              | WE               | Command                                                        | Action                                                                                                                                                                                                                                 | Note                                                                                                  |  |  |  |

| Any                                                                    | Н           | Х                     | Х                | Х                | Deselect                                                       | NOP. Continue previous operation.                                                                                                                                                                                                      | 1)2)3)4)5)6)                                                                                          |  |  |  |

|                                                                        | L           | Н                     | Н                | Н                | No Operation                                                   | NOP. Continue previous operation.                                                                                                                                                                                                      | 1) to 6)                                                                                              |  |  |  |

| Idle                                                                   | L           | L                     | Н                | Н                | Active                                                         | Select and activate row                                                                                                                                                                                                                | 1) to 6)                                                                                              |  |  |  |

|                                                                        | L           | L                     | L                | Н                | AUTO REFRESH                                                   | -                                                                                                                                                                                                                                      | 1) to 7)                                                                                              |  |  |  |

|                                                                        | L           | L                     | L                | L                | MODE REGISTER<br>SET                                           | -                                                                                                                                                                                                                                      | 1) to 7)                                                                                              |  |  |  |

| Row Active                                                             | L           | Н                     | L                | Н                | Read                                                           | Select column and start Read burst                                                                                                                                                                                                     | 1) to 6), 8)                                                                                          |  |  |  |

|                                                                        | L           | Н                     | L                | L                | Write                                                          | Select column and start Write burst                                                                                                                                                                                                    | 1) to 6), 8)                                                                                          |  |  |  |

|                                                                        | L           | L                     | Н                | L                | Precharge                                                      | Deactivate row in bank(s)                                                                                                                                                                                                              | 1) to 6), 9)                                                                                          |  |  |  |

| Read (Auto                                                             | L           | Н                     | L                | Н                | Read                                                           | Select column and start new Read burst                                                                                                                                                                                                 | 1) to 6), 8)                                                                                          |  |  |  |

| _                                                                      | L           | L                     | Н                | L                | Precharge                                                      | Truncate Read burst, start Precharge                                                                                                                                                                                                   | 1) to 6), 9)                                                                                          |  |  |  |

| Disabled)                                                              | L           | Н                     | Н                | L                | BURST<br>TERMINATE                                             | BURST TERMINATE                                                                                                                                                                                                                        | 1) to 6), 10)                                                                                         |  |  |  |

| Write (Auto                                                            | L           | Н                     | L                | Н                | Read                                                           | Select column and start Read burst                                                                                                                                                                                                     | 1) to 6), 8), 11)                                                                                     |  |  |  |

| Precharge                                                              | L           | Н                     | L                | L                | Write                                                          | Select column and start Write burst                                                                                                                                                                                                    | 1) to 6), 8)                                                                                          |  |  |  |

| Disabled)                                                              | L           | L                     | Н                | L                | Precharge                                                      | Truncate Write burst, start Precharge                                                                                                                                                                                                  | 1) to 6), 9), 11)                                                                                     |  |  |  |

| Read (Auto<br>Precharge<br>Disabled)                                   | L<br>L<br>L | H<br>L<br>H<br>L<br>H | H<br>L<br>H<br>H | L<br>L<br>H<br>L | Read Write Precharge Read Precharge BURST TERMINATE Read Write | Select column and start Write burst  Deactivate row in bank(s)  Select column and start new Read burst  Truncate Read burst, start Precharge  BURST TERMINATE  Select column and start Read burst  Select column and start Write burst | 1) to 6), 8)  1) to 6), 9)  1) to 6), 8)  1) to 6), 9)  1) to 6), 10)  1) to 6), 8), 11  1) to 6), 8) |  |  |  |

- 1) This table applies when CKE n-1 was HIGH and CKE n is HIGH (see **Table 12** and after  $t_{XSNR}/t_{XSRD}$  has been met (if the previous state was self refresh).

- 2) This table is bank-specific, except where noted, i.e., the current state is for a specific bank and the commands shown are those allowed to be issued to that bank when in that state. Exceptions are covered in the notes below.

- 3) Current state definitions:

- Idle: The bank has been precharged, and  $t_{\rm RP}$  has been met.

- Row Active: A row in the bank has been activated, and  $t_{RCD}$  has been met. No data bursts/accesses and no register accesses are in progress.

- Read: A Read burst has been initiated, with Auto Precharge disabled, and has not yet terminated or been terminated.

- Write: A Write burst has been initiated, with Auto Precharge disabled, and has not yet terminated or been terminated.

- 4) The following states must not be interrupted by a command issued to the same bank.

- Precharging: Starts with registration of a Precharge command and ends when  $t_{\rm RP}$  is met. Once  $t_{\rm RP}$  is met, the bank is in the idle state. Row Activating: Starts with registration of an Active command and ends when  $t_{\rm RCD}$  is met. Once  $t_{\rm RCD}$  is met, the bank is in the "row active" state

- Read w/Auto Precharge Enabled: Starts with registration of a Read command with Auto Precharge enabled and ends when  $t_{RP}$  has been met. Once  $t_{RP}$  is met, the bank is in the idle state.

- Write w/Auto Precharge Enabled: Starts with registration of a Write command with Auto Precharge enabled and ends when  $t_{RP}$  has been met. Once  $t_{RP}$  is met, the bank is in the idle state.

- Deselect or NOP commands, or allowable commands to the other bank should be issued on any clock edge occurring during these states. Allowable commands to the other bank are determined by its current state and according to **Table 14**.

- 5) The following states must not be interrupted by any executable command; Deselect or NOP commands must be applied on each positive clock edge during these states.

- Refreshing: Starts with registration of an Auto Refresh command and ends when  $t_{RFC}$  is met. Once  $t_{RFC}$  is met, the DDR SDRAM is in the "all banks idle" state.

- Accessing Mode Register: Starts with registration of a Mode Register Set command and ends when  $t_{MRD}$  has been met. Once  $t_{MRD}$  is met, the DDR SDRAM is in the "all banks idle" state.

- Precharging All: Starts with registration of a Precharge All command and ends when  $t_{RP}$  is met. Once  $t_{RP}$  is met, all banks is in the idle state.

- 6) All states and sequences not shown are illegal or reserved.

- 7) Not bank-specific; requires that all banks are idle.

- 8) Reads or Writes listed in the Command/Action column include Reads or Writes with Auto Precharge enabled and Reads or Writes with Auto Precharge disabled.

- 9) May or may not be bank-specific; if all/any banks are to be precharged, all/any must be in a valid state for precharging.

- 10) Not bank-specific; BURST TERMINATE affects the most recent Read burst, regardless of bank.

- 11) Requires appropriate DM masking.

## **TABLE 14**

| Current State    | cs | RAS | CAS | WE | Command                                       | Action                                  | Note         |

|------------------|----|-----|-----|----|-----------------------------------------------|-----------------------------------------|--------------|

| Any              | Н  | Х   | Х   | Х  | Deselect                                      | NOP. Continue previous operation.       | 1)2)3)4)5)6  |

|                  | L  | Н   | Н   | Н  | No Operation                                  | NOP. Continue previous operation.       | 1) to 6)     |

| Idle             | Х  | Х   | Х   | Х  | Any Command<br>Otherwise Allowed to<br>Bank m | _                                       | 1) to 6)     |

| Row Activating,  | L  | L   | Н   | Н  | Active                                        | Select and activate row                 | 1) to 6)     |

| Active, or       | L  | Н   | L   | Н  | Read                                          | Select column and start Read burst      | 1) to 7)     |

| Precharging      | L  | Н   | L   | L  | Write                                         | Select column and start Write burst     | 1) to 7)     |

|                  | L  | L   | Н   | L  | Precharge                                     | -                                       | 1) to 6)     |

| Read (Auto       | L  | L   | Н   | Н  | Active                                        | Select and activate row                 | 1) to 6)     |

| Precharge        | L  | Н   | L   | Н  | Read                                          | Select column and start new Read burst  | 1) to 7)     |

| Disabled)        | L  | L   | Н   | L  | Precharge                                     | -                                       | 1) to 6)     |

| Write (Auto      | L  | L   | Н   | Н  | Active                                        | Select and activate row                 | 1) to 6)     |

| Precharge        | L  | Н   | L   | Н  | Read                                          | Select column and start Read burst      | 1) to 8)     |

| Disabled)        | L  | Н   | L   | L  | Write                                         | Select column and start new Write burst | 1) to 7)     |

|                  | L  | L   | Н   | L  | Precharge                                     | -                                       | 1) to 6)     |

| Read (With Auto  | L  | L   | Н   | Н  | Active                                        | Select and activate row                 | 1) to 6)     |

| Precharge)       | L  | Н   | L   | Н  | Read                                          | Select column and start new Read burst  | 1) to 7), 9) |

|                  | L  | Н   | L   | L  | Write                                         | Select column and start Write burst     | 1) to 7), 10 |

|                  | L  | L   | Н   | L  | Precharge                                     | -                                       | 1) to 6)     |

| Write (With Auto | L  | L   | Н   | Н  | Active                                        | Select and activate row                 | 1) to 6)     |

| Precharge)       | L  | Н   | L   | Н  | Read                                          | Select column and start Read burst      | 1) to 7)     |

|                  | L  | Н   | L   | L  | Write                                         | Select column and start new Write burst | 1) to 7)     |

|                  | L  | L   | Н   | L  | Precharge                                     | _                                       | 1) to 6)     |

- This table applies when CKE n-1 was HIGH and CKE n is HIGH (see Table 12: Clock Enable (CKE) and after t<sub>XSNR</sub>/t<sub>XSRD</sub> has been met (if the previous state was self refresh).

- 2) This table describes alternate bank operation, except where noted, i.e., the current state is for bank n and the commands shown are those allowed to be issued to bank m (assuming that bank m is in such a state that the given command is allowable). Exceptions are covered in the notes below.

- 3) Current state definition:

- Idle: The bank has been precharged, and  $t_{RP}$  has been met.

Row Active: A row in the bank has been activated, and  $t_{RCD}$  has been met. No data bursts/accesses and no register accesses are in progress.

Read: A Read burst has been initiated, w. Auto Precharge disabled, and has not yet terminated or been terminated.

Write: A Write burst has been initiated, w. Auto Precharge disabled, and has not yet terminated or been terminated.

Read w. Auto Precharge Enabled: See 10).

Write w. Auto Precharge Enabled: See 10).

- 4) AUTO REFRESH and Mode Register Set commands may only be issued when all banks are idle.

- 5) A BURST TERMINATE command cannot be issued to another bank; it applies to the bank represented by the current state only.

- 6) All states and sequences not shown are illegal or reserved.

- 7) Reads or Writes listed in the Command/Action column include Reads or Writes with Auto Precharge enabled and Reads or Writes with Auto Precharge disabled.

- 8) Requires appropriate DM masking.

- 9) Concurrent Auto Precharge:

This device supports "Concurrent Auto Precharge". When a read with auto precharge or a write with auto precharge is enabled any command may follow to the other banks as long as that command does not interrupt the read or write data transfer and all other limitations apply (e.g. contention between READ data and WRITE data must be avoided). The minimum delay from a read or write command with auto precharge enable, to a command to a different banks is summarized in **Table 15**.

10) A Write command may be applied after the completion of data output.

|              |                             | TA Truth Table 5: Concurrent Auto                       | BLE 15<br>Precharge |

|--------------|-----------------------------|---------------------------------------------------------|---------------------|

| From Command | To Command (different bank) | Minimum Delay with Concurrent Auto<br>Precharge Support | Unit                |

| WRITE w/AP   | Read or Read w/AP           | 1 + (BL/2) + t <sub>WTR</sub>                           | $t_{CK}$            |

|              | Write to Write w/AP         | BL/2                                                    | $t_{CK}$            |

|              | Precharge or Activate       | 1                                                       | $t_{CK}$            |

| Read w/AP    | Read or Read w/AP           | BL/2                                                    | $t_{CK}$            |

|              | Write or Write w/AP         | CL (rounded up) + BL/2                                  | $t_{CK}$            |

|              | Precharge or Activate       | 1                                                       | t <sub>CK</sub>     |

## 4 Electrical Characteristics

This chapter lists the electrical characteristics.

## 4.1 Operating Conditions

This chapter contains the operating conditions tables.

|                                                          | TABLE 16 e Maximum Ratings |      |       |                        |            |           |

|----------------------------------------------------------|----------------------------|------|-------|------------------------|------------|-----------|

| Parameter                                                | Symbol                     |      | Value | Unit                   | Note/ Test |           |

|                                                          |                            | min. | typ.  | max.                   |            | Condition |

| Voltage on I/O pins relative to $V_{\rm SS}$             | $V_{IN},V_{OUT}$           | -0.5 | _     | V <sub>DDQ</sub> + 0.5 | V          |           |

| Voltage on inputs relative to $V_{\rm SS}$               | $V_{IN}$                   | -1   | _     | +3.6                   | V          |           |

| Voltage on $V_{\rm DD}$ supply relative to $V_{\rm SS}$  | $V_{DD}$                   | -1   | _     | +3.6                   | V          |           |

| Voltage on $V_{\rm DDQ}$ supply relative to $V_{\rm SS}$ | $V_{DDQ}$                  | -1   | _     | +3.6                   | V          |           |

| Operating temperature (ambient)                          | $T_{A}$                    | 0    | _     | +70                    | °C         |           |

| Storage temperature (plastic)                            | $T_{STG}$                  | -55  | _     | +150                   | °C         |           |

| Power dissipation (per SDRAM component)                  | PD                         | _    | 1.5   | _                      | W          |           |

| Short circuit output current                             | $I_{OUT}$                  | _    | 50    | _                      | mA         |           |

Attention: Stresses above the max. values listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values maycause irreversible damage to the integrated circuit.

## **TABLE 17**

#### **Input and Output Capacitances**

| Input and Output Capacitances                      |           |           |      |      |      |                             |  |  |  |

|----------------------------------------------------|-----------|-----------|------|------|------|-----------------------------|--|--|--|

| Parameter                                          | Symbol    | ol Values |      |      | Unit | Note/                       |  |  |  |

|                                                    |           | Min.      | Тур. | Max. |      | Test Condition              |  |  |  |

| Input Capacitance: CK, CK                          | $C_{11}$  | 1.5       | _    | 2.5  | pF   | P(G)-TFBGA-60 1)            |  |  |  |

|                                                    |           | 2.0       | _    | 3.0  | pF   | P(G)-TSOPII-66              |  |  |  |

| Delta Input Capacitance                            | $C_{dl1}$ | _         | _    | 0.25 | pF   |                             |  |  |  |

| Input Capacitance: All other input-only pins       | $C_{12}$  | 1.5       | _    | 2.5  | pF   | P(G)-TFBGA-60               |  |  |  |

|                                                    |           | 2.0       | _    | 3.0  | pF   | P(G)-TSOPII-66              |  |  |  |

| Delta Input Capacitance: All other input-only pins | $C_{dIO}$ | _         | _    | 0.5  | pF   |                             |  |  |  |

| Input/Output Capacitance: DQ, DQS, DM              | $C_{IO}$  | 3.5       | _    | 4.5  | pF   | P(G)-TFBGA-60 <sup>2)</sup> |  |  |  |

|                                                    |           | 4.0       | _    | 5.0  | pF   | P(G)-TSOPII-66              |  |  |  |

| Delta Input/Output Capacitance: DQ, DQS, DM        | $C_{dIO}$ | _         | _    | 0.5  | pF   |                             |  |  |  |

<sup>1)</sup> These values are not subject to production test - verified by design/characterization and are tested on a sample base only.  $V_{\rm DDQ}$  =  $V_{\rm DD}$  = 2.5 V ± 0.2 V, f = 100 MHz,  $T_{\rm A}$  = 25 °C,  $V_{\rm OUT(DC)}$  =  $V_{\rm DDQ}/2$ ,  $V_{\rm OUT}$  (Peak to Peak) 0.2 V. Unused pins are tied to ground.

<sup>2)</sup> DM inputs are grouped with I/O pins reflecting the fact that they are matched in loading to DQ and DQS to facilitate trace matching at the board level.

## **TABLE 18**

## **Electrical Characteristics and DC Operating Conditions**

| Electrical Characteristics and DC Operating Conditions |                             |                                |                               |                           |                                    |                                                                                                 |  |