# **Product Specification**

# 802.11b/g Advanced Enterprise Device Server

Revision: v1.0

# **April 2011**

File name: dp550 platform product specification.doc

Document Number: 100-8090-100

<Page Intentionally Left Blank>

# **Quatech Confidential**

Copyright © 2011 QUATECH ® Inc.

ALL RIGHTS RESERVED. No part of this publication may be copied in any form, by photocopy, microfilm, retrieval system, or by any other means now known or hereafter invented without the prior written permission of QUATECH ® Inc.. This document may not be used as the basis for manufacture or sale of any items without the prior written consent of QUATECH Inc..

QUATECH Inc. is a registered trademark of QUATECH Inc..

Airborne™ is a trademark of QUATECH Inc..

All other trademarks used in this document are the property of their respective owners.

#### Disclaimer

The information in the document is believed to be correct at the time of print. The reader remains responsible for the system design and for ensuring that the overall system satisfies its design objectives taking due account of the information presented herein, the specifications of other associated equipment, and the test environment.

QUATECH <sup>®</sup> Inc. has made commercially reasonable efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice. No responsibility is assumed by QUATECH for the use of the information or for infringements of patents or other rights of third parties. This document is the property of QUATECH <sup>®</sup> Inc. and does not imply license under patents, copyrights, or trade secrets.

#### Quatech, Inc. Headquarters

QUATECH <sup>®</sup> Inc.. 5675 Hudson Industrial Parkway Hudson, OH 44236 USA

Telephone: 330.655.9000 Toll Free (USA): 800.553.1170 Fax: 330.655.9010

Technical Support: 800.553.1170 / support@quatech.com

Web Site: www.quatech.com

100-8090-100 4/14/2011 3

<Page Intentionally Left Blank>

# **Contents**

| 1.0  | Conventions                                   | 7  |

|------|-----------------------------------------------|----|

| 1.1  | Terminology                                   | 7  |

| 1.2  | Notes                                         | 7  |

| 1.3  | Caution                                       | 7  |

| 1.4  | File Format                                   | 7  |

| 2.0  | Product Description                           | 8  |

| 3.0  | Block Diagram                                 |    |

| 4.0  | Model Numbers                                 |    |

| 5.0  | Pin out and Connectors                        |    |

| 5.1  | Digital UART Ports                            |    |

| 5.2  | Ethernet PHY Port                             |    |

| 5.3  | Serial Peripheral Interface (SPI)             |    |

| 5.4  | Debug/Console Port                            |    |

| 5.5  | General Purpose Input/Output (GPIO)           |    |

| 5.6  | Connector Definition                          |    |

| 6.0  | Electrical & RF Specification                 |    |

| 6.1  | AC Electrical Characteristics – Transmitter   |    |

| 6.2  | Performance/Range                             |    |

| 7.0  | SPI Interface                                 |    |

| 7.1  | Pin-out                                       | _  |

| 7.2  | SPI AC Characteristics                        |    |

| 7.3  | SPI Protocol                                  |    |

| 7.4  | SPI Modes                                     |    |

| 7.5  | SPI Commands                                  |    |

| 8.0  | Antenna                                       |    |

| 8.1  | Antenna Selection                             |    |

| 8.2  | Host Board Mounted Antenna                    |    |

| 8.3  | Host Chassis Mounted Antenna                  |    |

| 8.4  | Embedded Antenna                              |    |

| 8.5  | Antenna Location                              |    |

| 8.6  | Performance                                   |    |

| 9.0  | RESET Function                                |    |

| 10.0 | Mechanical Outline                            |    |

| 11.0 | Recommended Footprint                         |    |

| 11.1 | Mounting Hole Specification                   |    |

| 11.2 | Alternate Mounting Hardware                   | 33 |

| 12.0 | Regulatory Certification and Agency Approvals |    |

| 12.1 | FCC Statement                                 |    |

| 12.2 | FCC RF Exposure Statement                     |    |

| 12.3 | Information for Canadian Users (IC Notice)    |    |

| 12.4 | FCC/IC Modular Approval                       |    |

| 12.5 | End Product Labeling                          |    |

| 12.6 | Regulatory Test Mode Support                  | 3/ |

| 13.0 | Physical & Environmental Approvals            |    |

| 14.0 | Change Log                                    | 40 |

# **Figures**

| Figure 1 - WLNG-SE/SP/AN/ET-DP550 Block Diagram   | g  |

|---------------------------------------------------|----|

| Figure 2 - SPI Read/Write Timing                  |    |

| Figure 3 - SPI Clock and Select Timing            | 21 |

| Figure 4 - Power on RESET Timing                  |    |

| Figure 5 - RESET Timing                           |    |

| Figure 6 – DP550 Mechanical Outline               |    |

| Figure 7 - Recommended PCB Footprint              |    |

| Figure 8 - Full FCC/IC Label                      | 37 |

| Figure 9 - Minimum FCC/IC Label                   |    |

|                                                   |    |

|                                                   |    |

| Tables                                            |    |

| I abics                                           |    |

| Table 1 - Model Numbers                           | 10 |

| Table 2 – Module Pin Definition                   |    |

| Table 3 - UART Pin Definition                     |    |

| Table 4- Absolute Maximum Values <sup>1</sup>     |    |

| Table 5 – Operating Conditions & DC Specification |    |

| Table 6 - RF Characteristics – 802.11b/g          |    |

| Table 7 - Supported Data Rates by Band            |    |

| Table 8 - Operating Channels                      |    |

| Table 9 - Radio Typical Performance Range         |    |

| Table 10 - SPI Pinout Details                     |    |

| Table 11 - SPI Signal Descriptions                | 20 |

| Table 12 - SPI AČ Timings                         |    |

| Table 13 - TX Message Header                      |    |

| Table 14 - RX Message Header                      |    |

| Table 15 - SPI Modes                              |    |

| Table 16 - SPI Command Description                |    |

| Table 17 - Embedded Antenna Options               |    |

| Table 18 - RESET Timing                           | 31 |

| Table 19 - Regulatory Approvals                   | 34 |

| Table 20 - Modular Grant Numbers                  |    |

| Table 21 - Mechanical Approvals                   | 39 |

|                                                   |    |

6

#### 1.0 Conventions

The following section outlines the conventions used within the document, where convention is deviated from the deviation takes precedence and should be followed. If you have any question related to the conventions used or clarification of indicated deviation please contact Quatech Sales or Wireless Support.

#### 1.1 Terminology

Airborne Enterprise Device Server and AirborneDirect Enterprise Device Server is used in the opening section to describe the devices detailed in this document, after this section the term **module** will be used to describe the devices.

#### 1.2 Notes

A note contains information that requires special attention. The following convention will be used. The area next to the indicator will identify the specific information and make any references necessary.

The area next to the indicator will identify the specific information and make any references necessary.

#### 1.3 Caution

A caution contains information that, if not followed, may cause damage to the product or injury to the user. The shaded area next to the indicator will identify the specific information and make any references necessary.

The area next to the indicator will identify the specific information and make any references necessary.

#### 1.4 File Format

These documents are provided as Portable Document Format (PDF) files. To read them, you need Adobe Acrobat Reader 4.0.5 or higher. For your convenience, Adobe Acrobat Reader is provided on the Radio Evaluation Kit CD. Should you not have the CD, for the latest version of Adobe Acrobat Reader, go to the Adobe Web site (<a href="www.adobe.com">www.adobe.com</a>).

### 2.0 Product Description

The WLNG-AN-DP550 family is the latest generation of 802.11 wireless device servers and adapters from Quatech. The radio features the following:

- 802.11b/g WiFi Radio with 32bit ARM9 CPU (128MB SDRAM, 64MB Flash)

- Atheros AR6002 802.11b/g radio chipset.

- Supports WEP, WPA, WPA2, 802.11i and 802.1x Supplicant, with Certificates.

- The wireless device server includes integrated:

- 802.11b/g radio driver

- TCP/IP stack, UDP, telnet, FTP server

- Data bridging and buffering

- Command Line Interface

- Web interface

- WPA Supplicant

- 802.11 Radio Driver

- Supports antenna diversity

- Operating Temperature (-40°C to 85°C)

- Storage temp (-50°C to 125°C)

- 36 pin high density SMT connector (Hirose DF12-36)

- Dual (2) Hirose U.FL RF connector for RF antenna

- Multiple host interfaces supported:

- Dual UART (921.6K BAUD)

- Serial (RS232/422/485)

- SPI

- 10/100 Ethernet PHY

- Advanced low power modes

- Rugged mounting options.

- No host driver required

- Small form factor module (Dimensions: 40.6mm x 29.6mm x 7.5mm)

- Worldwide Regulatory Support

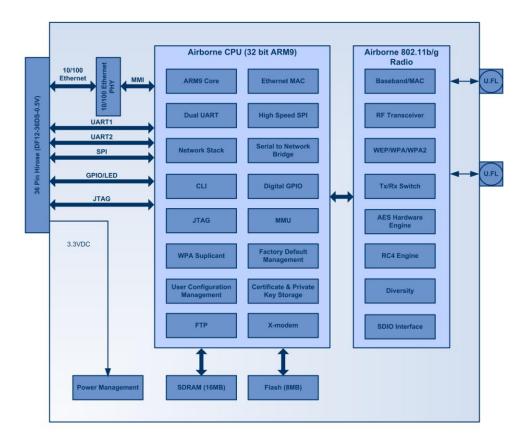

# 3.0 Block Diagram

The following outlines the block diagram of the radio:

Figure 1 - WLNG-SE/SP/AN/ET-DP550 Block Diagram

# 4.0 Model Numbers

The following table identifies the model numbers associated with the device server family. Please contact Quatech sales for details, quotes and availability.

**Table 1 - Model Numbers**

|               |                                                                                     |           | WiFi Interface |       |       |     |          | Security |     |     |      |         |      |

|---------------|-------------------------------------------------------------------------------------|-----------|----------------|-------|-------|-----|----------|----------|-----|-----|------|---------|------|

| Model Number  |                                                                                     | 802.11b/g | UART           | RS232 | RS485 | SPI | Ethernet | GPIO     | WEP | WPA | WPA2 | 802.11i | RoHS |

| WLNG-AN-DP551 | 802.11b/g, UART device server                                                       | •         | 2              | •     | •     |     |          | •        | •   | •   | •    | •       | •    |

| WLNG-ET-DP551 | 802.11b/g, 10/100 Ethernet device adapter                                           | •         |                |       |       |     | •        | •        | •   | •   | •    | •       | •    |

| WLNG-SE-DP551 | 802.11b/g, UART device server<br>with RS232/422/485 driver control                  | •         | 2              | •     | •     |     |          | •        | •   | •   | •    | •       | •    |

| WLNG-SP-DP551 | 802.11b/g, SPI device server                                                        | •         |                |       |       | •   |          | •        | •   | •   | •    | •       | •    |

|               | Evaluation Kits                                                                     |           |                |       |       |     |          |          |     |     |      |         |      |

| WLNG-EK-DP551 | WLNG-EK-DP551 802.11b/g Enterprise Class Serial Device Server Module Evaluation Kit |           |                |       |       |     | •        |          |     |     |      |         |      |

### 5.0 Pin out and Connectors

Pin definition is dependent upon the device type selected. The specific pin function is defined in Table 2 for each device type. Where multiple options are available for a single device type, these options are software selectable by the device firmware.

Table 2 - Module Pin Definition

| Pin | Name     | Device<br>Type | Description             |

|-----|----------|----------------|-------------------------|

| 1   | GND      | All            | Digital Ground          |

| 2   | TDI      | All            | JTAG: Test data in      |

| 3   | VDD      | All            | 3.3VDC                  |

| 4   | VDD      | All            | 3.3VDC                  |

| 5   | RTCK     | All            | JTAG: Return Test Clock |

| 6   | DTXD     | All            | D <sub>OUT</sub> Debug  |

| 7   | /RESET   | All            | Module RESET            |

| 8   | DRXD     | All            | D <sub>IN</sub> Debug   |

|     | RXD2     | UART           | D <sub>IN</sub> UART2   |

|     | RXD2     | Serial         | D <sub>IN</sub> UART2   |

| 9   | RXD2     | SPI            | D <sub>IN</sub> UART2   |

|     | RXD2     | Ethernet       | D <sub>IN</sub> UART2   |

|     | G6       | All            | GPIO                    |

| 10  | TDO      | All            | JTAG: Test data out     |

| 11  | /FRESET  | All            | Factory RESET           |

|     | CTS1     | UART           | Clear-to-Send UART1     |

|     | CTS      | Serial         | Clear-to-Send           |

| 12  | /SPI_SEL | SPI            | SPI Select              |

|     | CTS1     | Ethernet       | Clear-to-Send UART1     |

|     | F5       | All            | GPIO                    |

|     | NC       | UART           | No Connect              |

| 13  | NC       | Serial         | No Connect              |

| 15  | NC       | SPI            | No Connect              |

|     | RX+      | Ethernet       | Ethernet RX+            |

|     | NC       | UART           | No Connect              |

| 14  | NC       | Serial         | No Connect              |

| 1   | NC       | SPI            | No Connect              |

|     | RX-      | Ethernet       | Ethernet RX-            |

| 15  | GND      | All            | Digital Ground          |

| 16  | GND      | All            | Digital Ground          |

|     | RTS2     | UART           | Ready-to-Send UART2     |

|     | /TXEN    | Serial         | Line Driver Tx enable   |

| 17  | RTS2     | SPI            | Ready-to-Send UART2     |

|     | RTS2     | Ethernet       | Ready-to-Send UART2     |

|     | G2       | All            | GPIO                    |

|     | RTS1     | UART           | Ready-to-Send UART1     |

| 18  | RTS      | Serial         | Ready-to-Send           |

|     | SPI_CLK  | SPI            | SPI Clock Input         |

|     | RTS1     | Ethernet       | Ready-to-Send UART1     |

| Pin  | Name              | Device<br>Type | Description                                     |  |  |

|------|-------------------|----------------|-------------------------------------------------|--|--|

|      | F4                | All            | GPIO                                            |  |  |

|      | CTS2              | UART           | Clear-to-Send UART2                             |  |  |

|      | RXEN              | Serial         | Line driver Rx enable                           |  |  |

| 19   | CTS2              | SPI            | Clear-to-Send UART2                             |  |  |

|      | CTS2              | Ethernet       | Clear-to-Send UART2                             |  |  |

|      | G1                | All            | GPIO                                            |  |  |

| 20   | TCK               | All            | JTAG: Test clock                                |  |  |

|      | TXD2              | UART           | D <sub>OLIT</sub> UART2                         |  |  |

|      | TXD2              | Serial         | D <sub>OUT</sub> UART2                          |  |  |

| 21   | TXD2              | SPI            | D <sub>OUT</sub> UART2                          |  |  |

|      | TXD2              | Ethernet       | D <sub>OUT</sub> UART2                          |  |  |

|      | G7                | All            | GPIO                                            |  |  |

|      | G0                | UART           | GPIO                                            |  |  |

|      | SER_MODE          | Serial         | Serial interface type selection (RS232/422/485) |  |  |

| 22   | SPI_INT           | SPI            | SPI Interrupt                                   |  |  |

|      | G0                | Ethernet       | GPIO                                            |  |  |

|      | LED_CON           | Edicine        | Valid TCP/IP Connection Indicator               |  |  |

| 23   | F6                | All            | GPIO                                            |  |  |

|      | RXD1              | UART           |                                                 |  |  |

| -    |                   |                | D <sub>IN</sub> UART1                           |  |  |

| 24   | RXD1              | Serial         | D <sub>IN</sub> UART1                           |  |  |

| 24   | MOSI              | SPI            | D <sub>IN</sub> SPI                             |  |  |

| -    | RXD1              | Ethernet       | D <sub>IN</sub> UART1                           |  |  |

| -    | F7                | All            | GPIO                                            |  |  |

| 25 — | LED_POST          | All            | POST Status Indicator                           |  |  |

|      | F0                |                | GPIO                                            |  |  |

| 26   | LED_WLN_CFG       | All            | Module TCP/IP Configuration Indicator           |  |  |

|      | F3                |                | GPIO                                            |  |  |

| 27   | LED_RF_LINK       | All            | Module RF Link Status Indicator                 |  |  |

|      | F2                |                | GPIO                                            |  |  |

| _    | TXD1              | UART           | D <sub>OUT</sub> UART1                          |  |  |

| _    | TXD1              | Serial         | D <sub>OUT</sub> UART1                          |  |  |

| 28   | MISO              | SPI            | D <sub>OUT</sub> SPI                            |  |  |

| _    | TXD1              | Ethernet       | D <sub>OUT</sub> UART1                          |  |  |

|      | F1                | All            | GPIO                                            |  |  |

|      | NC                | UART           | No Connect                                      |  |  |

| 29   | NC                | Serial         | No Connect                                      |  |  |

|      | NC                | SPI            | No Connect                                      |  |  |

|      | TX-               | Ethernet       | Ethernet TX-                                    |  |  |

|      | NC                | UART           | No Connect                                      |  |  |

| 30   | NC                | Serial         | No Connect                                      |  |  |

| 30   | NC                | SPI            | No Connect                                      |  |  |

|      | TX+               | Ethernet       | Ethernet TX+                                    |  |  |

| 31   | NTRST             | All            | JTAG: Test RESET signal                         |  |  |

| 32   | TMS               | All            | JTAG: Test mode select                          |  |  |

| 33   | VDD               | All            | 3.3VDC                                          |  |  |

|      |                   |                | 2.21/DC                                         |  |  |

| 34   | VDD               | All            | 3.3VDC                                          |  |  |

|      | VDD<br>LED_RF_ACT | All            | Radio Status Indicator, driven by the radio.    |  |  |

#### 5.1 Digital UART Ports

The device supports two digital UART ports. Use of these ports is determined by the device type choice made in firmware. The details of the ports can be seen in Table 3.

The availability of UART2 is selected in firmware.

**UART2 UART2** Pin Pin Data out (D<sub>OUT</sub>) 28 21 6 21 28 Data In (D<sub>IN</sub>) 24 9 24 9 8 Clear-to-Send (CTS) 12 19 12 Ready-to-Send (RTS) 18 17 18 17 Transmit Enable (/TXEN) Receive Enable (/RXEN) 19 22 Serial Mode (SER\_MOD)

Table 3 - UART Pin Definition

The primary UART supports a 4-wire interface; the secondary port supports a 4-wire interface except when being used with the Serial Device type, in which case it is reduced to a 2-wire only.

The primary digital UART can be used as the primary connection for the Serial device type. This type supports a 7-wire interface to allow the definition of the serial interface type (RS232/3422/485) and the data transfer direction. Definitions of this interface can be seen in Table 3.

The UART1 and UART2 interfaces support the following possible configurations:

- BAUD: 300, 600, 1200, 2400, 4800, 9600, 14400, 19200, 28800, 38400, 57600, 115200, 230400, 460800, 921600

- Flow Control: None, Hardware (CTS/RTS), Software (XON/XOFF)

- Default settings: 9600, 8, N, 1, No Flow Control.

#### 5.2 Ethernet PHY Port

A 10/100 Ethernet PHY interface is supported on all device types (except SPI), it is enabled by default when the Ethernet device type is selected in firmware. This interface is a 10/100Mbps interface that supports auto negotiation and cross-over cabling. The interface also supports both half and full duplex for 10Mbps and 100Mbps.

The interface uses a Broadcom BCM5241A Ethernet PHY, please refer to the manufacturers datasheet for interface details and appropriate design guidelines.

#### 5.3 Serial Peripheral Interface (SPI)

Please refer to section 7.0 for details on this interface.

#### 5.4 Debug/Console Port

A debug/console port is supported by a 2-wire serial interface defined in Table 3. This port is a bidirectional serial port intended for debug of the unit only, it does not support data transfer.

It is recommended that a connection to this port be supported via test points or a two pin header. The default settings for the debug port are 115200, 8, N 1, No Flow Control.

**CAUTION**: Do not use the debug port without contacting Quatech Technical Support first. Potential damage to the module may occur.

#### 5.5 General Purpose Input/Output (GPIO)

A number of the interface pins support multiple functional definitions. Those alternately defined as GPIO pins can be selected as such via device firmware.

The GPIO pins are digital I/O capable of supporting up to a 16mA drive current at 3.3VDC.

#### 5.6 Connector Definition

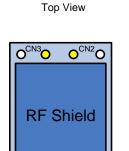

There are a total of three connectors to the radio:

CN1: 36 pin Digital Host interface.

Hirose: **DF12B-36DP-0.5V(XX)** (0.50mm (.020") Pitch Plug, Surface Mount, Dual Row, Vertical, 4.00mm Stack Height, 36

Circuits)

CN2: RF connector for 802.11b/g antenna (Default).

Hirose U.FL

CN3: RF connector for 802.11b/g antenna.

Hirose U.FL.

Bottom

View

# 6.0 Electrical & RF Specification

Table 4- Absolute Maximum Values<sup>1</sup>

| Parameter                   | Min  | Max  | Unit |

|-----------------------------|------|------|------|

| Supply Voltage              | -0.3 | 4.0  | VDC  |

| Power Dissipation           |      | 2.00 | W    |

| Operating Temperature Range | -40  | 85   | °C   |

| Storage Temperature         | -50  | 125  | °C   |

Note: 1. Values are absolute ratings, exceeding these values may cause permanent damage to the device.

Table 5 – Operating Conditions & DC Specification

| Symbol                | Parameter                                                    | Min                   | Тур  | Max            | Units |

|-----------------------|--------------------------------------------------------------|-----------------------|------|----------------|-------|

| V <sub>DD</sub>       | Supply Voltage                                               | 3.00                  | 3.30 | 3.60           | V     |

| V <sub>IL</sub>       | Input Low Level Voltage                                      | -0.3                  |      | 0.8            |       |

| V <sub>IH</sub>       | Input High Level Voltage                                     | 2.0                   |      | $V_{DD} + 0.3$ |       |

| V <sub>OL</sub>       | Output Low Level Voltage                                     |                       |      | 0.4            |       |

| V <sub>OH</sub>       | Output High Level Voltage                                    | V <sub>DD</sub> - 0.4 |      |                |       |

| $I_{IR}$              | Inrush current                                               |                       |      | 1900           | mA    |

|                       | 150μs duration, source resistance 150mΩ                      |                       |      |                |       |

| $I_{CCG}$             | Operating Current – UART Data (802.11g)                      |                       | 300  |                | mA    |

|                       | Connection Rate @ 54Mb/s<br>UART 100% Duty Cycle @ 920K BAUD |                       |      |                |       |

| I <sub>CCB</sub>      | Operating Current – UART Data (802.11b)                      |                       | 310  |                | mA    |

|                       | Connection rate @ 11Mb/s<br>UART 100% Duty Cycle @ 920K BAUD |                       |      |                |       |

| $I_{CCG\_ETH}$        | Operating Current – Ethernet Data (802.11g)                  |                       | 380  |                | mA    |

|                       | Transmitting @ 54Mb/s<br>10/100 Ethernet 100% Duty Cycle     |                       |      |                |       |

| $I_{\text{CCB\_ETH}}$ | Operating Current – Ethernet Data (802.11b)                  |                       | 360  |                | mA    |

|                       | Transmitting @ 11Mb/s<br>10/100 100% Duty Cycle              |                       |      |                |       |

| $I_{CCU}$             | Radio and CPU on. No data traffic (UART)                     |                       | 220  |                | mA    |

| I <sub>CCE</sub>      | Radio and CPU on. No data traffic (Ethernet)                 |                       | 260  |                | mA    |

| $I_{SBU0}$            | Radio off (UART)                                             |                       | 110  |                | mA    |

|                       | CPU Idle, radio off (f/w control)                            |                       |      |                |       |

| Symbol            | Parameter                                                                                                       | Min | Тур | Max | Units |

|-------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>SBE0</sub> | Radio off (Ethernet)                                                                                            |     | 150 |     | mA    |

|                   | CPU Idle, radio off (f/w control)                                                                               |     |     |     |       |

| $I_{SB1U}$        | Doze Mode (UART/Serial)                                                                                         |     | 130 |     | mA    |

|                   | IEEE PSPoll mode (DTIM = 10), Associated,<br>Idle, Beacon Interval = 100ms<br>CPU Idle, wake on UART traffic    |     |     |     |       |

| I <sub>SB1E</sub> | Doze Mode (Ethernet)                                                                                            |     | 160 |     | mA    |

|                   | IEEE PSPoll mode (DTIM = 10), Associated,<br>Idle, Beacon Interval = 100ms<br>CPU Idle, wake on Network traffic |     |     |     |       |

| I <sub>SB3U</sub> | Sleep Mode – UART/Serial                                                                                        |     | 110 |     | mA    |

|                   | Radio Off (disassociated)<br>CPU Idle, wake on UART traffic                                                     |     |     |     |       |

| I <sub>SB3E</sub> | Sleep Mode – Ethernet                                                                                           | 110 |     | 150 | mA    |

|                   | Radio Off (disassociated)<br>CPU Idle                                                                           |     |     |     |       |

100-8090-100 4/14/2011 17

Table 6 - RF Characteristics - 802.11b/g

| Symbol               | Parameter                        | Rate (Mb/s)                     | Min  |      | rage<br>/ mW | Pea<br>dBm / |   | Units |

|----------------------|----------------------------------|---------------------------------|------|------|--------------|--------------|---|-------|

| P <sub>OUTB</sub>    | Transmit Power<br>Output 802.11b | 11, 5.5, 2, 1                   |      | 15.0 | 31.6         |              |   | dBm   |

| P <sub>OUTG</sub>    | Transmit Power<br>Output 802.11g | 6, 9, 12, 18, 24,<br>36, 48, 54 |      | 15.0 | 31.6         |              |   | dBm   |

|                      | Receive                          | 11                              |      | -{   | 38           |              |   | ID    |

| P <sub>RSENB</sub>   | Sensitivity<br>802.11b           | 1                               |      | -98  |              |              |   | dBm   |

|                      |                                  | 54                              |      | -7   | 75           |              |   |       |

| Receive              |                                  | 36                              |      | -82  |              |              |   | dBm   |

| P <sub>RSENG</sub>   | Sensitivity<br>802.11g           | 18                              |      | -88  |              |              |   | UBIII |

|                      |                                  | 6                               |      | -93  |              |              |   |       |

| F <sub>RANGEBG</sub> | Frequency<br>Range               |                                 | 2401 |      |              | 249          | 5 | MHz   |

Table 7 - Supported Data Rates by Band

| Band    | Supported Data Rates (Mb/s)  |

|---------|------------------------------|

| 802.11b | 11, 5.5, 2, 1                |

| 802.11g | 54, 48, 36, 24, 18, 12, 9, 6 |

**Table 8 - Operating Channels**

| Band    | Region    | Freq Range<br>(GHz) | No. of<br>Channels | Channels |

|---------|-----------|---------------------|--------------------|----------|

|         | US/Canada | 2.401 - 2.473       | 11                 | 1 – 11   |

| 802.11b | Europe    | 2.401 - 2.483       | 13                 | 1 – 13   |

|         | Japan     | 2.401 - 2.495       | 14                 | 1 – 14   |

|         | US/Canada | 2.401 - 2.473       | 11                 | 1 – 11   |

| 802.11g | Europe    | 2.401 - 2.483       | 13                 | 1 – 13   |

|         | Japan     | 2.401 - 2.483       | 13                 | 1 – 13   |

- 1. Only channels 1, 6 and 11 are non-overlapping.

- 2. Channel 14 is non-overlapping (Japan only).

18 4/14/2011 100-8090-100

#### 6.1 AC Electrical Characteristics – Transmitter

Transmit power is automatically managed by the device for minimum power consumption. The MAXIMUM transmit power at the RF connector is typically  $\pm 15 \, \mathrm{dBm} \pm 2 \, \mathrm{dB}$  for B-Mode (all rates) and  $\pm 15 \, \mathrm{dBm} + 2 \, \mathrm{dB}$  for G-Mode (all rates).

#### 6.2 Performance/Range

The following table illustrates the typical data rates, performance and range the device is capable of providing using an omni directional antenna.

Table 9 - Radio Typical Performance Range

| Data Rate      | <b>Typical Outdoor Distance</b> (Unity gain antenna) | <b>Typical Outdoor Distance</b> (2dBi antenna gain on each end for B/G mode) |

|----------------|------------------------------------------------------|------------------------------------------------------------------------------|

| 1.0 Mb/s       | 240m                                                 | 380m                                                                         |

| 11.0 Mb/s      | 135m                                                 | 215m                                                                         |

| 6Mb/s 802.11g  | 135m                                                 | 215m                                                                         |

| 54Mb/s 802.11g | 12m                                                  | 19m                                                                          |

Ranges are based on receiver sensitivity, Transmitter power, free-space path loss estimates, antenna gain factors, and link margin estimates. Actual range will vary from those stated. Non line-of-sight applications will result in typical values less than shown above.

The Data Rate is the supported connection rate for the wireless link. However, the actual data throughput for the link will be less than the stated data rates.

#### 7.0 SPI Interface

The following section details the SPI interface specification for both hardware timing and SPI protocol. The device is a SPI slave and requires a compatible SPI master for operation.

#### 7.1 Pin-out

When the SPI interface is enabled, through the CLI or web interface, the following pins are assigned for communication.

SPI Master In Slave Out (MISO) 28 Master Out Slave In (MOSI) 24 SPI Interrupt (SPI\_INT) 22 SPI Clock (SPI\_CLK) 18 SPI Select (/SPI\_SEL) 12 Data In (RxD2, DTXD) 8 Data out (TxD2, DRXD) 21 6 Ready-to-Send (RTS2) 17 Clear-to-Send (CTS2) 19

Table 10 - SPI Pinout Details

Table 11 - SPI Signal Descriptions

| Pin Definition             | Description                                                             |

|----------------------------|-------------------------------------------------------------------------|

| Master In Slave Out (MISO) | Serial Data OUT; must be connected to the serial data in of the master. |

| Master Out Slave In (MOSI) | Serial Data IN; Must be connected to the serial data out of the master. |

| SPI Interrupt (SPI_INT)    | Interrupt signal driver by slave see Table 16 for details of operation. |

| SPI Clock (SPI_CLK)        | SPI clock sourced from the master.                                      |

| SPI Select (/SPI_SEL)      | Enable the SPI slave, sourced from the master. Active low signal.       |

Use of the SPI interface is mutually exclusive with the use of UART1 and the Ethernet ports, as the API interface reuses pins from both of these interfaces.

20 4/14/2011 100-8090-100

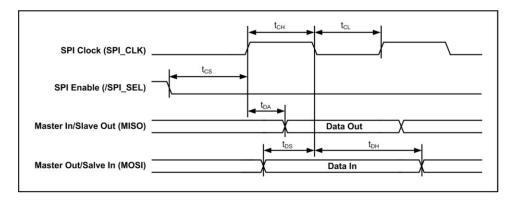

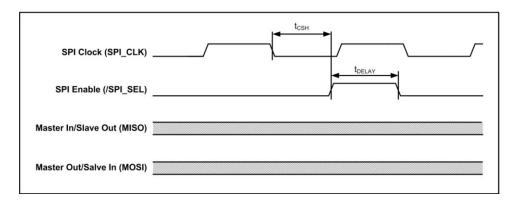

#### 7.2 SPI AC Characteristics

The following specification identifies the required hardware timing to successfully implement a SPI interface with the Airborne Device Server module.

$f_{\text{MAX}}$ Maximum Clock Frequency 8.00 MHz SPI Select Low to Clock Rising Edge 100  $t_{\text{CS}}$ ns Clock High 62.5 ns  $t_{CH}$ Clock Low 62.5 ns  $t_{\text{CL}}$ Clock High to Data Out 60 ns  $t_{\text{DA}} \\$ Clock Low to Data In Valid Set-up time  $t_{DS}$ 14 ns Clock Low to Data Valid Hold time 2  $t_{DH}$ ns Clock Falling Edge to SPI Select High 100  $t_{CSH}$ ns SPI Select High to SPI Select Low 40  $t_{\text{DELAY}} \\$ μs

Table 12 - SPI AC Timings

Figure 3 - SPI Clock and Select Timing

100-8090-100 4/14/2011 21

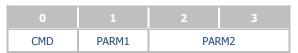

#### 7.3 SPI Protocol

A SPI message is composed of a 4 byte header followed by 0 or more bytes of data. The header data is full-duplex. That is, the TX message header is sent to the Airborne Device Server module by the host at the same time the RX message header is sent to the host from the Airborne Device Server.

The TX message header consists of a Command (CMD) byte, followed by three Parameter (PARM) bytes. They are described in the SPI Commands section 0 below.

The RX message header is shifted out as the first four bytes of a SPI message regardless of the contents of the TX message header. The RX message header consists of a RX Data Available field, and a TX Buffer Available field. The RX Data Available field indicates the number of data bytes the Device Server has available for the host. The data can be received by the RXDATA command. The TX Buffer Available field indicates how many data bytes the Device Server is able to accept from the host. This data is to be shifted in by the host using the TXDATA (Table 16) command. Both fields are 16 bit values and are stored in little-endian format (Least significant byte first).

The /SPI\_SEL signal must be deasserted between successive SPI messages. The messages will not be processed correctly if /SPI\_SEL is held asserted across multiple messages.

Table 13 - TX Message Header

Table 14 - RX Message Header

SPI data is transferred most significant bit first (msb).

22 4/14/2011 100-8090-100

#### 7.4 SPI Modes

The Airborne device supports the following four SPI modes. These are selectable through the command line or web interfaces. The default mode is zero (0).

Table 15 - SPI Modes

| SPI Mode | Clock Idle | Clocking Edge            |

|----------|------------|--------------------------|

| 0        | Low        | High-Low (trailing edge) |

| 1        | Low        | Low-High (leading edge)  |

| 2        | High       | Low-High (trailing edge) |

| 3        | High       | High-Low (leading edge)  |

#### 7.5 SPI Commands

The following commands are available for use in the CMD message header.

Unused parameters should be set to zero.

**Table 16 - SPI Command Description**

| Command<br>(Hex) | Name     | Description                                                                                                                                                                                                                                                                                         |

|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00             | NOP      | The NOP command does nothing.                                                                                                                                                                                                                                                                       |

|                  |          | It is intended to be used when the host wants to simply retrieve the RX Message Header without any other operation.                                                                                                                                                                                 |

|                  |          | PARM1 and PARM2 are unused for this command and should be set to zero.                                                                                                                                                                                                                              |

| 0x04             | BREAK    | The BREAK command will issue a break sequence to the module.                                                                                                                                                                                                                                        |

|                  |          | It is analogous to the BREAK signal on a common UART. Use this command to issue a BREAK if the <i>esc-mode-serial brk</i> setting is configured in the module.                                                                                                                                      |

|                  |          | PARM1 and PARM2 are unused for this command and should be set to zero.                                                                                                                                                                                                                              |

| 0x08             | TXINTCLR | The TXINTCLR command will clear the TX interrupt.                                                                                                                                                                                                                                                   |

|                  |          | Use this command when the module is issuing a TX interrupt but the host has no more data to send. This is analogous to the reset TX interrupt command on a common UART. The result of this command is that the TX interrupt is cleared even though the host is not writing more data to the module. |

|                  |          | PARM1 and PARM2 are unused for this command and should be set to zero.                                                                                                                                                                                                                              |

| Command<br>(Hex) | Name   | Description                                                                                                                                                                                                                                                                                                                                |  |

|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x10             | INTENA | The INTENA command will configure the specific interrupts to be enabled from the module. For this command, the PARM1 field will define the interrupts to be enabled.                                                                                                                                                                       |  |

|                  |        | The definition of the PARM1 field for this command is a bit-mask and is formatted as follows:                                                                                                                                                                                                                                              |  |

|                  |        | Bit 7 Interrupt Sense – Determines the asserted state of the interrupt pin. If this bit is set to a 1, the interrupt pin will be active high; otherwise the interrupt pin will be active low. The module will use the setting of this bit from the most recently issued INTENA command to determine the Interrupt Sense.                   |  |

|                  |        | Bit 1 TX Interrupt – If this bit is set to a 1, the interrupt pin will be asserted when there is space available in the TX buffer. The interrupt will be cleared when the module has TX data to process from the host.  Alternately, the host can clear this interrupt by using the TXINTCLR command if the host has no more data to send. |  |

|                  |        | <b>Bit 0 RX Interrupt</b> – If this bit is set to a 1, the interrupt pin will be asserted when there is RX data available. The interrupt will be cleared when the host has received all the RX data available from the module.                                                                                                             |  |

|                  |        | All other bits of PARM1 are unused for this command and should be set to zero.                                                                                                                                                                                                                                                             |  |

|                  |        | PARM2 is unused for this command and should be set to zero.                                                                                                                                                                                                                                                                                |  |

|                  |        | For example, to enable TX interrupts with the interrupt pin active high, use the SPI message 0x10 0x82 0x00 0x00. That is, SPI command 0x10, PARM1 is 0x82, PARM2 is 0x0000.                                                                                                                                                               |  |

|                  |        | <b>Important:</b> The INTENA command can only be used to enable the specified interrupts. This command cannot be used to disable specified interrupts by setting the corresponding interrupt enable bits to zero in PARM1. The INTDIS command must be used to disable the specified interrupts.                                            |  |

| 0x20             | INTDIS | The INTDIS command will configure the specific interrupts to be disabled from the module. For this command, the PARM1 field will define the interrupts to be disabled.                                                                                                                                                                     |  |

|                  |        | The definition of the PARM1 field for this command is a bit-mask and is formatted as follows:                                                                                                                                                                                                                                              |  |

|                  |        | <b>Bit 1 TX Interrupt</b> – If this bit is set to a 1, The TX interrupt function will be disabled.                                                                                                                                                                                                                                         |  |

|                  |        | Bit 0 RX Interrupt – If this bit is set to a 1, the RX interrupt function will be disabled.                                                                                                                                                                                                                                                |  |

|                  |        | All other bits of PARM1 are unused for this command and should be set to zero.                                                                                                                                                                                                                                                             |  |

|                  |        | PARM2 is unused for this command and should be set to zero.                                                                                                                                                                                                                                                                                |  |

|                  |        | For example, to disable TX interrupts, use the SPI message 0x20 0x02 0x00 0x00. That is, SPI command 0x20, PARM1 is 0x02, PARM2 is 0x0000.                                                                                                                                                                                                 |  |

24 4/14/2011 100-8090-100

| Command<br>(Hex) | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x40             | TXDATA    | The TXDATA command is used to send data to the module to be interpreted as commands if the module is in CLI mode, or to be transmitted on the wireless link if the module has an active data connection established.                                                                                                                                                                                                                                                     |

|                  |           | The host may send at most the number of bytes indicated by the TX Buffer Available field in the RX Message Header. The actual number of bytes sent by the host is determined by the 16 bit value in PARM2. The value in PARM2 is little-endian (least significant byte first) and must be less than or equal to the number in the TX Buffer Available field. Any bytes sent in excess of this number will be ignored.                                                    |

|                  |           | PARM1 is unused for this command and should be set to zero.                                                                                                                                                                                                                                                                                                                                                                                                              |

|                  |           | For example, to send the auth dpac dpac command, use the SPI message 0x40 0x00 0x0F 0x00 0x61 0x75 0x74 0x68 0x20 0x64 0x70 0x61 0x63 0x20 0x64 0x70 0x61 0x63 0x0D. That is, SPI command 0x40, PARM1 is 0x00, PARM2 is 0x000F, followed by the text for auth dpac dpac.                                                                                                                                                                                                 |

| 0x80             | 80 RXDATA | The RXDATA command is used to receive data from the module. In CLI mode, this data will be the local echoing of the commands issued to the module, as well as the command responses generated by the module. If the module has an active data connection established, this data will be the data received on the wireless link.                                                                                                                                          |

|                  |           | The host may receive at most the number of bytes indicated by the RX Data Available field in the RX Message Header. The actual number of bytes received by the host is determined by the 16 bit value in PARM2. The value in PARM2 is little-endian (least significant byte first) and must be less than or equal to the number in the RX Data Available field. If additional clock cycles are sent to the module beyond this number, meaningless data will be returned. |

|                  |           | PARM1 is unused for this command and should be set to zero.                                                                                                                                                                                                                                                                                                                                                                                                              |

The TXDATA and RXDATA commands can be combined for full-duplex operation. For example, a command byte of **0xC0** would be a TXDATA and RXDATA command combined. The result of this command would be that the module would accept data being shifted in as TX data, while at the same time, RX data would be shifted out. In this case, the number of bytes transferred for TXDATA must be equal to the number of bytes transferred for RXDATA. The PARM2 parameter will indicate the number of bytes to be transferred for both the TXDATA and RXDATA commands.

100-8090-100 4/14/2011 25

#### 8.0 Antenna

The unit supports antenna connections through two Hirose U.FL connectors (CN2 and CN3), located on the top surface of the device next to the RF shielding. The device supports both transmit and receive diversity. Antenna selection and diversity options are selectable through both the web and command line interfaces.

Any antenna used with the system must be designed for operation within the 2.4GHz ISM band and specifically must support the 2.412GHz to 2.482GHz for 802.11b/g operation. They are required to have a VSWR of 2:1 maximum referenced to a  $50\Omega$  system impedance.

#### 8.1 Antenna Selection

The Airborne radio supports a number of antenna options, all of which require connection to the U.FL connectors on the radio. Ultimately the antenna option selected will be determined by a number of factors, these include consideration of the application, mechanical construction and desired performance. Since the number of possible combinations is endless we will review some of the more common solutions in this section. If your application is not covered during this discussion please contact Technical Support for more specific answers.

The available antenna connections include:

- Host board mounted antenna

- Host chassis mounted antenna

- Embedded antenna

In addition to the above options, location and performance need to be considered, the following sections discuss these items.

#### 8.2 Host Board Mounted Antenna

Host board mounted requires that an antenna connection is physically mounted to the host system board. It also requires that the host board include a U.FL connector (two (2) if diversity is being used) to allow a U.FL to U.FL coaxial lead to connect from the radio to the host board. It will then require  $50\Omega$  matched PCB traces to be routed from the U.FL connector to the antenna mount.

There are several sources for the U.FL to U.FL coaxial cable these include Hirose, Sunridge and IPEX. Please contact Quatech for further part numbers and supply assistance.

This approach can simplify assembly but does require that the host system configuration can accommodate an antenna location that is determined by the host PCB. There are also limitations on the ability to seal the enclosure when using this approach.

This approach also restricts the selection of available antenna. When using this approach, antennas that screw or press fit to the PCB mount connector must be

used. There are many options for the antenna connector type, however if you wish to utilize the FCC/IOC modular approval the connector choice must comply with FCC regulations, these state a non-standard connector is required e.g. TNC/SMA are not allowed, RP-TNC/RP-SMA are allowed.

#### 8.3 Host Chassis Mounted Antenna

Host Chassis mounted antennas require no work on the host PCB. They utilize an antenna type called 'flying lead'. There are two types of flying leads; one which provides a bulkhead mounted antenna connector and one which provides a bulk head mounted antenna. The type you choose will be determined by the application.

A flying lead system connects a U.FL coaxial lead to the radio's U.FL connector, the other end of the coax is attached to either a bulkhead mounted antenna connector or directly to an antenna that has an integrated bulkhead mount.

In either of the two cases, the use of this approach significantly reduces the antenna system development effort and provides for greater flexibility in the available antenna types and placement in the host system chassis.

When using the flying lead antenna (integrated bulk head mounting), there are no connector choice restrictions for use with the FCC/IOC modular certification. However if the flying lead connector is used, the same restrictions as identified for the Host Mounted Antenna apply.

There are many suppliers of flying lead antenna and connectors; Quatech's Airborne Antenna product line offers a range of antenna solutions.

#### 8.4 Embedded Antenna

Use of Embedded antenna can be the most interesting approach for M2M, industrial and medical applications. Their small form factor and absence of any external mounting provides a very compelling argument for their use. There is a downside to this antenna type and it comes with performance. Antenna performance for all of the embedded options will, in most cases, be less that that achievable with external antenna. This does not make them unusable; it will impact choice of antenna type and requires more focus on placement.

The three main embedded antenna types are PCB embedded, chip (PCB mounted) and flying lead; each has its advantages and disadvantages (See Table 17).

| Automo Turo  | Features |         |              |             |

|--------------|----------|---------|--------------|-------------|

| Antenna Type | Cost     | Size    | Availability | Performance |

| PCB Embedded | Lowest   | Largest | Custom       | Poor        |

| Chip         | Low      | Small   | Standard     | Poor        |

| Flying Lead  | Low      | Small   | Standard     | Fair        |

**Table 17 - Embedded Antenna Options**

**PCB Embedded** – This approach embeds an antenna design into the host PCB. This approach is very common with add-in WiFi card (CF, PCMCIA, SDIO, etc.) as it requires no external connections and is the cheapest production approach. The lower production cost requires significant development cost and lack of performance and flexibility.

**Chip** – The integration of a chip antenna is simple and requires a relatively small footprint on the host system, however, it does suffer from the same limitations of flexibility and performance seen with the PCB embedded approach. There are relatively large numbers of suppliers of this type of antenna; there is also a range of configuration and performance options.

Flying Lead – This approach is similar to the flying lead solution for external antennas, the difference is that the form factors are smaller and provide a range of chassis and board mounting options, all for internal use. This approach suffers less from the performance and flexibility limitations of the other approaches, since the location of the antenna it not determined by the host PCB design. The assembly of a system using this approach maybe slightly more complex since the antenna is not necessarily mounted on the host PCBA.

#### 8.5 Antenna Location

The importance of this design choice cannot be over stressed; it can in fact be the determining factor between success and failure of the WiFi implementation.

There are several factors that need to be considered when determining location:

- Distance of Antenna from radio

- Location of host system

- Proximity to RF blocking or absorbing materials

- Proximity to potential noise or interference

- Position relative to infrastructure (Access Points or Laptops)

- Orientation of host system relative to infrastructure

- Is it known

- Is it static

To minimize the impact of the factors above the following things need to be considered during the development process:

- Minimize the distance between the radio and the location of the antenna. The

coaxial cable between the two impacts the Transmit Power and Receive

Sensitivity negatively. Quatech recommends using 1.32-1.37mm outer

diameter U.FL coaxial cables.

- Minimize the locations where metal surfaces come into contact or are close to the location of the antenna.

- Avoid locations where RF noise, close to or over lapping the ISM bands, may occur. This would include microwave ovens and wireless telephone systems in the 2.4GHz frequency range.

- Mount the antenna as high on the equipment as possible.

- Locate the antenna where there is a minimum of obstruction between the antenna and the location of the Access Points. Typically Access Points are located in the ceiling or high on walls.

- Keep the main antenna's polarization vertical, or in-line with the antenna of the Access Points. 802.11 systems utilize vertical polarization and aligning both transmit and receive antenna maximizes the link quality.

Even addressing all of the above factors, does not guarantee a perfect connection, however with experimentation an understanding of the best combination will allow a preferred combination to be identified.

#### 8.6 Performance

Performance is difficult to define as the appropriate metric changes with each application or may indeed be a combination of parameters and application requirements. The underlying characteristic that, in most cases, needs to be observed is the link quality. This can be defined as the bandwidth available over which communication, between the two devices, can be performed, the lower the link quality the less likely the devices can communicate.

Measurement of link quality can be made in several ways; Bit Error Rate (BER), Signal to Noise (SNR) ratio, Signal Strength and may also include the addition of distortion. The link quality is used by the radio to determine the link rate, generally as the link quality for a given link rate drops below a predefined limit, the radio will drop to the next lowest link rate and try to communicate using it.

The reciprocal is also true, if the radio observes good link quality at one rate it will try to move up to the next rate to see if communication can be sustained using it. It is important to note that for a given position the link quality improves as the link rate is reduced. This is because as the link rate drops the radios Transmit power and Receive sensitivity improve.

From this it can be seen that looking at the link rate is an indirect way of assessing the quality of the link between the device and an Access Point. You should strive to make the communication quality as good as possible in order to support the best link rate. However be careful not to *over specify* the link rate. Consider your applications bandwidth requirements and tailor your link rate to optimize the link quality e.g. the link quality for a location at 6Mb/s is better than it would be for 54Mb/s, if the application only needs 2Mb/s of data throughput, the 6Mb/s rate would provide a better link quality.

Aside from the radio performance, there are a number of other things that contribute to the link quality; these include the items discussed earlier and choices made when looking at the overall antenna gain. The antenna gain contributes to the Equivalent Isotropically Radiated Power (EIRP) of the system. This is part of an overall measurement of the link quality called link margin.

100-8090-100 4/14/2011 29

Link Margin provides a measure of all the parts of the RF path that impact the ability of two systems to communicate. The basic equation looks like this:

**EIRP (dB)** =

$$TxP + TxA - TxC$$

Link Margin (dB) = EIRP - FPL + (RxS + RxA - RxC)

Where: TxP = Transmitter output power (dBm)

TxA = Transmitter antenna gain (dBi)

TxC = Transmitter to Antenna coax cable loss (dB)

FPL = Free Path Loss (dB)

RxS = Receiver receive sensitivity (dBm)

RxA = Receiver antenna gain (dBi)

RxC = Receiver to Antenna coax cable loss (dB)

This is a complex subject and requires more information than is presented here, Quatech recommends at reviewing the subject and evaluating any system at a basic level.

It is then possible, with a combination of the above items and an understanding of the application demands, to achieve a link quality optimized for the application and host design. It is important to note that this is established with a combination of hardware selection, design choices and configuration of the radio.

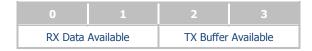

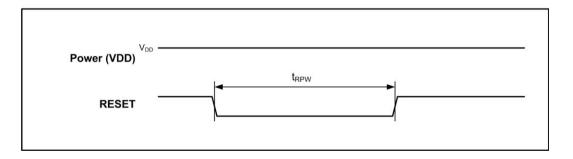

### 9.0 RESET Function

For correct operation of the on-board Power-on RESET (POR) and internal RESET controllers, the RESET pin on the WLNG-XX-DP550 family must obey the following timing and signal conditions.

Figure 4 - Power on RESET Timing

Figure 5 - RESET Timing

Table 18 - RESET Timing

| Symbol             | Parameter                                         | Min | Тур | Max | Units |

|--------------------|---------------------------------------------------|-----|-----|-----|-------|

| t <sub>PURST</sub> | Valid V <sub>DD</sub> to RESET valid              |     |     | 200 | ms    |

| t <sub>RLRV</sub>  | RESET Valid to RESET Low                          | 0   |     |     | ms    |

| t <sub>RPWI</sub>  | Valid V <sub>DD</sub> to Internal RESET completed |     |     | 200 | ms    |

| t <sub>RPW</sub>   | RESET Pulse Width                                 | 100 |     |     | μs    |

100-8090-100 4/14/2011 31

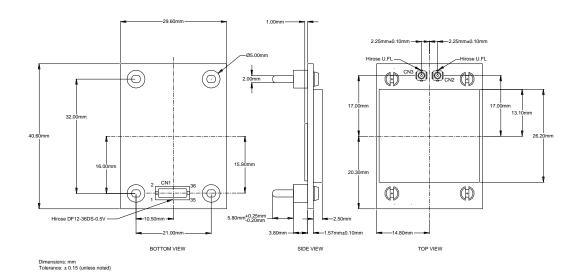

#### 10.0 Mechanical Outline

Figure 6 - DP550 Mechanical Outline

Module Connector: DF12B-36DS-0.5V(XX) (Hirose)

Hirose: 0.50mm (.020") Pitch Plug, Surface Mount, Dual Row, Vertical, 4.00mm

Stack Height, 36 Circuits

Board Connector: DF12(4.0)-36DP-0.5V(XX) (Hirose)

Hirose: 0.50mm (.020") Pitch Plug, Surface Mount, Dual Row, Vertical, 4.00mm

Stack Height, 36 Circuits

RF Connector: U.FL

Hirose: Ultra Small Surface Mount Coaxial Connector

The mounting hardware for the DP550 device utilizes a friction fit for retention of the thru-hole pins to the host board.

To support this configuration the maximum diameter of the thru-hole pin is 2.8mm. Although this exceeds the recommended mounting hole size (see section 11.1), the pin diameter is compliant and will compress to fit the recommended hole diameter.

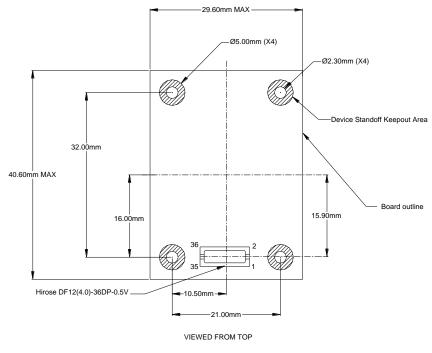

# 11.0 Recommended Footprint

Figure 7 - Recommended PCB Footprint

Dimensions: mm Tolerance: ± 0.15 (unless noted)

## 11.1 Mounting Hole Specification

The mounting hole specification is important to maintain a tight and reliable friction based interference between the host PCB and the DP550 stand-off hardware.

Nominal Radius: 2.2mm

Tolerance: +0.15mm/-0.00mm

Host Board Thickness: 0.8mm to 1.6mm

#### 11.2 Alternate Mounting Hardware

Quatech does support alternate mounting hardware for the DP550 platform. Please contact your Quatech sales representative for further details.

#### 12.0 Regulatory Certification and Agency Approvals

It is required that the following section be read and understood before use of the Quatech Airborne™ device is permitted.

Use of approved antenna is required for compliance to FCC and IC regulations.

The unit complies with the following agency approvals:

FCC Part 15 North America Sec. 15.107, 15.109, 15.207, 15.209, 15.247 Complete (US & Canada) Modular Approval CISPR 16-1:1993 Complete Europe ETSI EN 300 328 Part 1 V1.2.2 (2000-07) ETSI EN 300 328 Part 2 V1.1.1 (2000-07) ARIB STD-T71 v1.0, 14 (Dec 2000) Japan ARIB RCR STD-T33 (June 19, 1997) Pending ARIB STD-T66 v2.0 (March 28, 2002)

Table 19 - Regulatory Approvals

#### 12.1 FCC Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates uses and can radiate radio frequency energy and if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment to an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for assistance.

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### 12.2 FCC RF Exposure Statement

To comply with FCC/IC RF exposure compliance requirements, the antenna used for this transmitter must be installed to provide a separation distance of at least 20 cm from all persons and must not be co-located or operate in conjunction with any other antenna or transmitter.

As such, the radio component of this device is intended only for OEM integrators under the following two conditions:

- The antenna must be installed such that 20 cm is maintained between the antenna and users.

- The transmitter module may not be co-located with any other transmitter or antenna.

As long as the two conditions above are met, further transmitter testing will not be required. However, the OEM integrator is still responsible for testing their end product for any additional compliance requirements required with this module installed (e.g., digital device emissions, PC peripheral requirements).

In the event that these conditions cannot be met (for example, co-location with another transmitter), then the FCC authorization is no longer considered valid and the FCC ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC authorization.

#### 12.3 Information for Canadian Users (IC Notice)

This device has been designed to operate with an antenna having a maximum gain of 5dBi for 802.11b/g band. An antenna having a higher gain is strictly prohibited per regulations of Industry Canada. The required antenna impedance is  $50\Omega$ . Only approved antenna may be used with this equipment.

Quatech maintains a full list of approved antenna, please contact your Quatech representative for the up to date list.

To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the Equivalent Isotropically Radiated Power (EIRP) is not more than required for successful communication.

The installer of this radio equipment must ensure that the antenna is located or pointed such that it does not emit RF field in excess of Health Canada limits for the general population; consult Safety Code 6, obtainable from Health Canada's website www.hc-sc.gc.ca.

Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes : (1) l'appareil ne doit pas produire de brouillage, et (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### 12.4 FCC/IC Modular Approval

This document describes the Airborne WLN FCC modular approval and the guidelines for use as outlined in FCC Public Notice (DA 00-1407).

The WLNG-XX-DP550 is covered by the following modular grants:

| Country            | Standard                                    | Grant         |

|--------------------|---------------------------------------------|---------------|

|                    | FCC Part 15                                 |               |

| North America (US) | Sec. 15.107, 15.109, 15.207, 15.209, 15.247 | F4AWLNG551    |

|                    | Modular Approval                            |               |

| Councide           | RSS 210                                     | 20124 MUNCEE1 |

| Canada             | Modular Approval                            | 3913A-WLNG551 |

Table 20 - Modular Grant Numbers

By providing FCC modular approval on the Airborne WLN modules, the customers are relieved of any need to perform FCC part15 subpart C Intentional Radiator testing and certification, except where they wish to use an antenna that is not already certified.

Quatech supports a group of pre-approved antenna; use of one of these antennas eliminates the need to do any further subpart C testing or certification. If an antenna is not on the list, it is a simple process to add it to the pre-approved list without having to complete a full set of emissions testing. Please contact Quatech Technical support for details of our qualification processes.

Please note that as part of the FCC requirements for the use of the modular approval, the installation of any antenna must require a professional installer. This is to prevent any non-authorized antenna being used with the radio. There are ways to support this requirement but the most popular is to utilize a non-standard antenna connector, this designation includes the reverse polarity versions of the most popular RF antenna types (SMA, TNC, etc.). For more details please contact Quatech.

The following documents are associated with this applications note:

- FCC Part 15 Radio Frequency Devices

- FCC Public Notice DA 00-1407 (June 26<sup>th</sup>, 2000)

Quatech recommends that during the integration of the radio, into the customers system, that any design guidelines be followed. Please contact Quatech Technical Support if you have any concerns regarding the hardware integration.

Contact Quatech Technical support for a copy of the FCC and IOC grant certificates, the test reports and updated approved antenna list.

#### 12.5 End Product Labeling

This transmitter module is authorized only for use in devices where the antenna may be installed such that 20 cm may be maintained between the antenna and users. The final end product must be labeled in a visible area with the FCC and Industry of Canada Grant numbers as shown in Table 20.

The following label or similar must be placed on the outside of the product, utilizing the Airborne<sup>™</sup> device, whenever physically possible:

Figure 8 - Full FCC/IC Label

Contains Transmitter Module, FCC ID: F4AWLNG551 Contains Canadian Certification Number, IC: 3913A-WLNG551

The radio component is an integral part of the equipment and cannot be removed.

This device complies with part 15 of the FCC Rules.

Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference, and

- (2) This device must accept any interference received, including interference that may cause undesired operation.

Figure 9 - Minimum FCC/IC Label

Contains

FCC ID: F4AWLNG551

IC: 3913A-WLNG551

USAGE RESTRICTIONS APPLY

(SEE DOCUMENTATION)

When the device is so small or for such use that it is not practicable to place the label shown in Figure 8, the label shown in Figure 9 may be used, however the information required shall also be placed in a prominent location in the instruction manual or pamphlet supplied to the user. Alternatively, the required information shown in Figure 8 shall be placed on the container in which the device is marketed.

In all cases the FCC and IC identifiers must be displayed on the device in which the module is installed.

#### 12.6 Regulatory Test Mode Support

The Airborne Device Server includes support for all FCC, IC and ETSI test modes required to perform regulatory compliance testing on the module, please

contact Quatech Technical Support for details on enabling and using these modes.

# 13.0 Physical & Environmental Approvals

The device has passed the following primary physical and environmental tests. The test methods referenced are defined in SAE J1455 Aug1994.

**Table 21 - Mechanical Approvals**