# LIN System Basis Chip with LIN Transceiver, 5V Regulator, Watchdog, 8-channel High Voltage Switch Interface with High Voltage Current Sources, 16-bit SPI

#### **DATASHEET**

#### **Features**

- 8-channel HV switch interface with HV current sources

- Linear low-drop voltage regulator, up to 80mA current capability, V<sub>CC</sub> = 5.0V ±2%

- Fulfills the OEM "Hardware Requirements for LIN in Automotive Applications Rev.1.3"

- LIN master and slave operation possible

- Supply voltage up to 40V

- Operating voltage V<sub>S</sub> = 5V to 27V

- Internal voltage divider for V<sub>Battery</sub> sensing (±2%)

- 16-bit serial interface (daisy-chain-capable) for configuration and diagnosis

- Typically 8µA supply current during Sleep Mode

- Typically 35μA supply current in Active Low-power Mode

- VCC-undervoltage detection (4ms reset time) and watchdog reset logical combined at NRES open drain output

- LIN High-speed Mode up to 200kBit/s

- Adjustable watchdog timer via external resistor

- Negative trigger input for watchdog

- LIN physical layer complies with LIN 2.1 specification and SAE J2602-2

- Wake-up capability via LIN bus and CL15

- Bus pin is overtemperature and short-circuit protected versus GND and Battery

- Advanced EMC and ESD performance

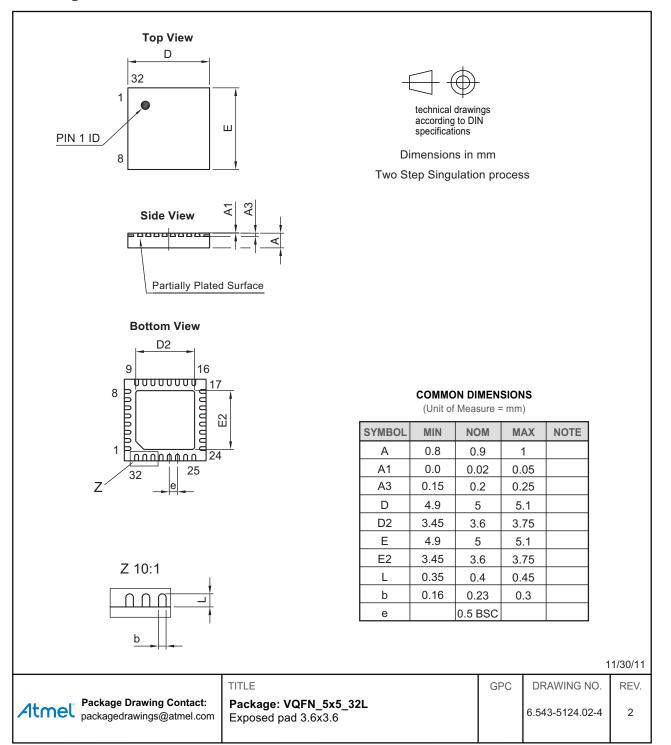

- Package: QFN32 5x5mm

# 1. Description

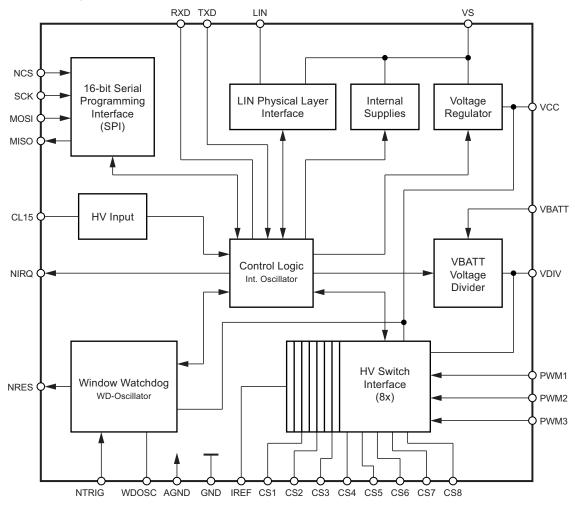

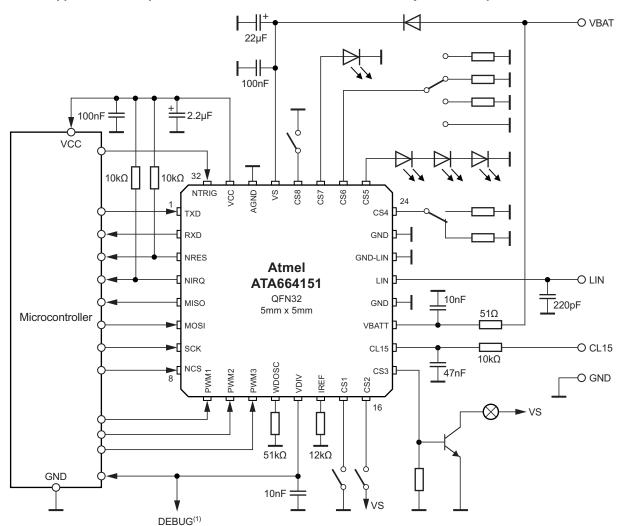

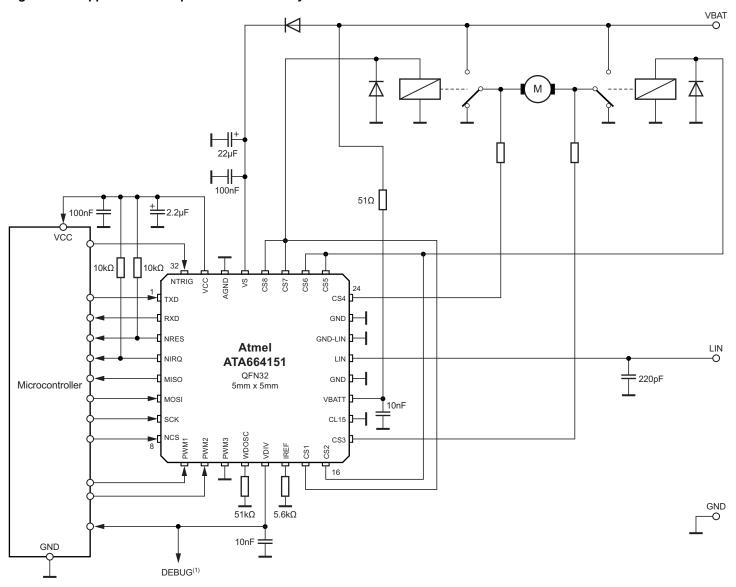

The Atmel® ATA664151 is a system basis chip with an eight-channel high voltage switch interface, a LIN 2.1 and SAEJ2602-2-compliant LIN transceiver, low-drop voltage regulator, and an adjustable Window Watchdog. The Atmel ATA664151 provides 5V output voltage with up to 80mA current capability. This chip combination makes it possible to develop inexpensive, simple, yet powerful slave and master nodes for LIN bus systems. The Atmel ATA664151 is especially designed for LIN switch applications and includes almost the entire LIN node. They are designed to handle low data-rate communication in vehicles (such as in convenience electronics). Improved slope control at the LIN driver ensures secure data communication up to 20kBaud. Sleep Mode and Active Low-power Mode guarantee minimal current consumption even in the case of a floating bus line or a short circuit on the LIN bus to GND.

Figure 1-1. Block Diagram

# 2. Pin Configuration

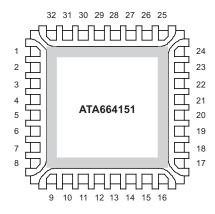

Figure 2-1. Pinning QFN32, 5x5mm

Table 2-1. Pinning

| Pin | Name  | Function                                                                |

|-----|-------|-------------------------------------------------------------------------|

| 1   | TXD   | LIN-bus logic data in from microcontroller                              |

|     |       | -                                                                       |

| 2   | RXD   | LIN-bus logic data out to microcontroller                               |

| 3   | NRES  | Watchdog and VCC undervoltage Reset Output pin (active low, open drain) |

| 4   | NIRQ  | Interrupt request output to microcontroller (active low, open drain)    |

| 5   | MISO  | SPI Master-In-Slave-Out output pin to microcontroller                   |

| 6   | MOSI  | SPI Master-Out-Slave-In input pin from microcontroller                  |

| 7   | SCK   | SPI clock input from microcontroller                                    |

| 8   | NCS   | SPI chip select logic input from microcontroller (active low)           |

| 9   | PWM1  | PWM control input port from microcontroller for first CS pin group      |

| 10  | PWM2  | PWM control input port from microcontroller for second CS pin group     |

| 11  | PWM3  | PWM control input port from microcontroller for third CS pin group      |

| 12  | WDOSC | Connection for external resistor to set watchdog frequency              |

| 13  | VDIV  | Voltage divider output / watchdog disable input pin                     |

| 14  | IREF  | Reference current adjustment pin                                        |

| 15  | CS1   | High-voltage current sink/source and switch I/O pin no. 1               |

| 16  | CS2   | High-voltage current sink/source and switch I/O pin no. 2               |

| 17  | CS3   | High-voltage current sink/source and switch I/O pin no. 3               |

| 18  | CL15  | Wake-up on ignition high-voltage input pin                              |

| 19  | VBATT | Battery voltage input for voltage divider                               |

| 20  | GND   | Ground connection                                                       |

| 21  | LIN   | LIN-bus connection                                                      |

|     |       |                                                                         |

Table 2-1. Pinning (Continued)

| Pin      | Name  | Function                                             |

|----------|-------|------------------------------------------------------|

| 22       | GND   | Ground connection                                    |

| 23       | GND   | Ground connection                                    |

| 24       | CS4   | High-voltage current source and switch I/O pin no. 4 |

| 25       | CS5   | High-voltage current source and switch I/O pin no. 5 |

| 26       | CS6   | High-voltage current source and switch I/O pin no. 6 |

| 27       | CS7   | High-voltage current source and switch I/O pin no. 7 |

| 28       | CS8   | High-voltage current source and switch I/O pin no. 8 |

| 29       | VS    | Supply input pin                                     |

| 30       | AGND  | Analog reference ground                              |

| 31       | VCC   | 5V Voltage regulator output pin                      |

| 32       | NTRIG | Watchdog trigger input from microcontroller          |

| Backside | GND   | Back Side Heat Slug, internally connected to GND     |

## 3. Pin and Functional Description

### 3.1 Physical Layer Compatibility

Since the LIN physical layer is independent of higher LIN layers (such as the LIN protocol layer), all nodes with a LIN physical layer as per release version 2.1 can be mixed with LIN physical layer nodes found in older versions (i.e., LIN 1.0, LIN 1.1, LIN 1.2, LIN 1.3, LIN 2.0), without any restrictions.

### 3.2 Supply Pin (VS)

The operating voltage is  $V_S$  = 5V to 27V. An undervoltage detection is implemented to disable data transmission via the LIN bus and the switch interface if  $V_{VS}$  falls below  $V_{VSth}$  in order to avoid false bus messages. After switching on VS, the IC starts in Active Mode (see also Section 4.1 "Active Mode" on page 9), with the VCC voltage regulator and the Window Watchdog switched on (the latter depends on the VDIV pin, see Section 10. "Watchdog" on page 28).

#### 3.3 Ground Pins GND and AGND

The IC is neutral on the LIN pin in the event of GND disconnection. It can handle a ground shift of up to 11.5% of VS.

Note: Please note that pin AGND is used for internal reference generation. This should be considered when designing the PCB in order to minimize the effect on the voltage thresholds.

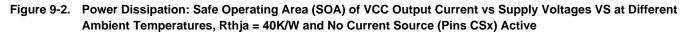

#### 3.4 Voltage Regulator Output Pin (VCC)

The internal 5V voltage regulator is capable of driving loads up to 80mA for supplying the microcontroller and other loads on the PCB. It is protected against overloads by means of current limitation and overtemperature shutdown. In addition, the output voltage is monitored and will cause a reset signal at the NRES output pin if it drops below a defined threshold V<sub>VCCthun</sub>.

A safe operating area (SOA) is defined for the voltage regulator, because the power dissipation caused by this block might exceed the system's thermal budget.

## 3.5 Bus Pin (LIN)

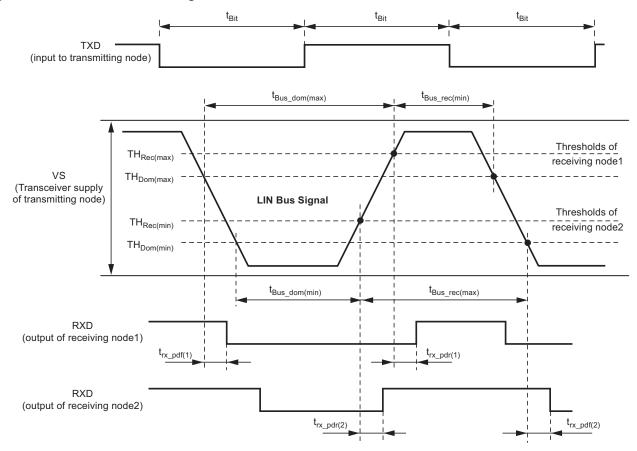

A low-side driver with internal current limitation, thermal shutdown and an internal pull-up resistor in compliance with the LIN 2.1 specification are implemented. The allowed voltage range is from –30V to +40V. Reverse currents from the LIN bus to VS are suppressed, even in the event of GND shifts or battery disconnection. The LIN receiver thresholds are compatible with the LIN protocol specification. The fall time from recessive to dominant bus state and the rise time from dominant to recessive bus state are slope-controlled.

For higher bit rates the slope control can be switched off by setting the SPI-bit LSME. Then the slope time of the LIN falling edge is <  $2\mu$ s. The slope time of the rising edge strongly depends on the capacitive load and the pull-up resistance at the LIN-line. To achieve a high bit rate it is recommended to use a small external pull-up resistor ( $500\Omega$ ) and a small capacitor. This allows very fast data transmission up to 200kBit/s, e.g., for electronic control tests of the ECU, microcontroller programming or data download. In this High-speed Mode a superior EMC performance is not guaranteed.

Note: The internal pull-up resistor is only switched on in Active Mode and when the LIN transceiver is activated by the LINE-Bit (Active Mode with LIN bus transceiver).

#### 3.6 Bus Logic Level Input Pin (TXD)

The TXD pin is the microcontroller interface for controlling the state of the LIN output. TXD must be pulled to ground in order to keep the LIN bus in the dominant state. If TXD is high or not connected (internal pull-up resistor), the LIN output transistor is turned off and the bus is in recessive state.

If configured, an internal timer prevents the bus line from being constantly driven in the dominant state. If TXD is forced to low for longer than  $t_{DOM}$ , the LIN bus driver is switched back to recessive state. TXD has to be switched to high for at least  $t_{TOrel}$  to reactivate the LIN bus driver (by resetting the timeout timer).

As mentioned above, this timeout function can be disabled via the SPI configuration register in order to achieve any long dominant state on the connected line (such as PWM transmission, or low bit rates).

### 3.7 Bus Logic Level Output Pin (RXD)

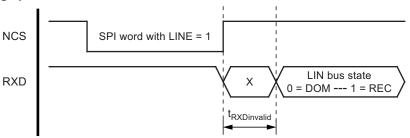

This output pin reports the state of the LIN bus to the microcontroller. LIN high (recessive state) is reported by a high level, LIN low (dominant state) is reported by a low level at RXD. The output has push-pull characteristics meaning no external time defining measures are required. During states of disabled LIN-PHY (configuration bit "LINE" = 0), pin RXD is at high level. Please note that the signal on the RXD pin is not valid for a certain period of time upon activation of the LIN transceiver (t<sub>RXDinvalid</sub>).

Figure 3-1. RXD Timing upon Transceiver Enable

RXD is switched off in Sleep- and Unpowered Mode.

#### 3.8 CL15 Pin

The CL15 pin is a high-voltage input that can be used to wake up the device from Sleep Mode. It is an edge-sensitive pin (low-to-high transition). Thus, even if CL15 pin is at high voltage ( $V_{CL15} > V_{CL15th}$ ), it is possible to switch into Sleep Mode. It is usually connected to the ignition for generating a local wake-up in the application if the ignition is switched on. The CL15 pin should be tied directly to ground if not needed. A debounce timer with a value  $t_{debCL15}$  of typically 160µs is implemented. The pin state (CL15 ON or OFF) can be read out through the SPI interface.

## 3.9 Reset Output Pin (NRES)

The Reset Output pin is an open drain output and switches to low during a VCC undervoltage event or a watchdog timing window failure. Please note the reset hold time of typically 4ms after the undervoltage condition has disappeared.

#### 3.10 Interrupt Request Output Pin (NIRQ)

The interrupt request output pin is an open drain output and switches to low whenever a chip-internal event occurs that is set up to trigger an interrupt. A power-up, a wake-up over LIN bus, a change in a switch state or an overtemperature condition are examples of such events. The pin remains at ground until the end of the next SPI command, where the interrupt source is passed to the SPI master (bits IRQS, see also section "Serial Programming Interface (SPI)" on page 17).

#### 3.11 WDOSC Output Pin

The WDOSC output pin provides a typical voltage of 1.2V intended to supply an external resistor with values between 34K and 120K. The value of the resistor and with it the pin output current adjusts the watchdog oscillator frequency to provide a certain range of time windows.

If the watchdog is disabled, the output voltage is switched off and the pin can either be tied to VCC or left open.

#### 3.12 NTRIG Input Pin

The NTRIG input pin is the trigger input for the Window Watchdog. A pull-up resistor is implemented. A falling edge triggers the watchdog. The trigger signal (low) must exceed a minimum time  $t_{trigmin}$  to generate a watchdog trigger and avoid false triggers caused by transients. The NTRIG pin should be tied directly to VCC if not needed.

#### 3.13 VBATT Input Pin

The VBATT is a high voltage input pin for measurement purposes by means of a voltage divider. The latter provides a low-voltage signal at the VDIV pin that is linearly dependent on the input voltage. In an application with battery voltage monitoring, this pin is connected to  $V_{Battery}$  via a 51 $\Omega$  resistor in series and a 10nF capacitor to GND. The divider ratio is 1:4. This results in maximum output voltages on pin VDIV when reaching 20V at the input. The VBATT pin can be tied directly to ground or left open if not needed.

#### 3.14 VDIV Input/Output Pin

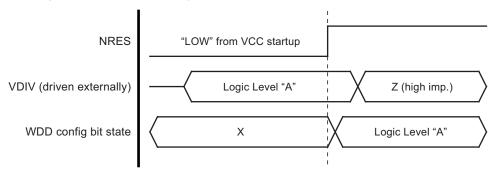

This pin handles two different functions. During the VCC startup and watchdog reset phase (pin NRES driven to LOW), the pin acts as input and determines the setting of the "WDD" bit within the SPI configuration register (see Figure 3-2). In other words, if the Window Watchdog operation shall be disabled directly after power-up (e.g., for µC programming or debugging purposes), pin VDIV must be tied to HIGH level until the reset phase ends (pin NRES has a positive slope from LOW to HIGH). In other cases, such as when pin VDIV is not driven actively by the application, the signal is assessed as LOW and the WDD bit (watchdog disable) is thus also low and the Window Watchdog is operational (see Figure 3-2).

Figure 3-2. WDD Configuration Bit Setup During VCC Startup

During normal operation this pin provides a low-voltage signal for the ADC such as for a microcontroller. It is sourced either by the VBATT pin or one of the switch input pins CS1 to CS8. An external ceramic capacitor is recommended for low-pass filtering of this signal. If selected in the configuration register of the SPI, this pin guarantees a voltage- and temperature-stable output ratio of the selected test input and is available in all modes except Sleep Mode. Please note that the current consumption values in the Active Low-power Mode of Atmel ATA664151 given in the electrical characteristics lose their validity if the VDIV output pin is being used in this Low-power Mode. The voltage on this pin is actively clamped to VCC if the input value would lead to higher values.

#### 3.15 IREF Output Pin

This pin is the connection for an external resistor towards ground. It provides a regulated voltage which will cause a resistor-dependent current used as reference for the current sources in the switch interface I/O ports. The resistor should be placed closely to the pin without any additional capacitor. A fail-safe circuitry detects if the resistor is missing or if there is a short towards ground or VCC on this pin. An internal fail-safe current is generated in this event. Please see also section "Switch Interface Unit" on page 22 for further details.

### 3.16 CS1 to CS8 High-voltage Input/Output Pins

These pins are intended for contact monitoring and/or constant current sourcing. A total of eight I/Os (pins CS1 through CS8) are available, of which three (CS1, CS2 and CS3) can be configured either as current sources (such as for switches towards ground) or as current sinks (such as for switches towards battery). The other five pins (CS4 to CS8) have only current sourcing capability. Apart from a high voltage (HV) comparator for simple switches, the I/Os are also equipped with a voltage divider to enable analog voltage measurements on HV pins by using the ADC of the application's microcontroller (see section "VDIV Input/Output Pin" on page 7 for further details). Also, each input can trigger an interrupt upon state change even during Active Low-power Mode. If one or more CSx pins are not needed, can be left open or directly connected to VS.

Note: Unused CSx-pins should be connected directly to VS.

#### 3.17 PWM1..3 Input Pins

These pins can be used to control the switch interface current sources directly, such as for pulse width-modulated load control or for pulsed switch scanning. They accept logic level signals from the microcontroller and are equipped with pull-down structures so in case of an open connection, the input is well defined. For more information see "Switch Interface Unit" on page 22.

The assignment of the current sources to the three PWM input pins is described in Section 8.1 "Current Sources" on page 22.

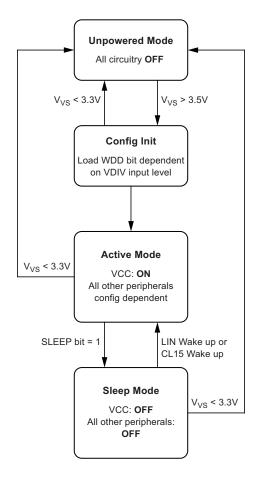

# 4. Operating Modes

There are two primary modes of operation available with the Atmel ATA664151.

- Active Mode:

- In this mode the VCC voltage regulator is active and the SPI is ready for operation. In addition, all other peripherals can be enabled or disabled by configuration via SPI. After power-up the watchdog is enabled (dependent on the VDIV pin only, see Section 3.14 "VDIV Input/Output Pin" on page 7), whereas the LIN transceiver and the Switch Interface Unit are switched off.

- Sleep Mode:

- All peripherals are switched off (including the VCC voltage regulator), a wake-up is only possible via the LIN bus or the CL15 pin. In this mode the IC has the lowest possible current consumption.

Figure 4-1. State Diagram

### 4.1 Active Mode

If sufficient voltage is applied to the IC at the VS pin, the configuration register is initialized and the chip changes to Active Mode. In this mode different states of power consumption are possible, depending on the configuration selected for the chip and activity on the SPI. The following table lists all power states (except unpowered) for the Atmel ATA664151.

Table 4-1. State and Current Consumption vs. Enabled Periphery

| State and VS Pin<br>Current<br>Consumption                                | LIN bus<br>Transceiver | Voltage<br>Divider | VCC Voltage<br>Regulator | Watchdog       | SPI Data<br>Comm. | Current<br>Sources                                        |

|---------------------------------------------------------------------------|------------------------|--------------------|--------------------------|----------------|-------------------|-----------------------------------------------------------|

| Sleep $I_{VS} = I_{VSsleep}$                                              | Off                    | Off                | Off                      | Off            | Off               | Off                                                       |

| Active Low-power $I_{VS} = I_{VSact\_lp}$                                 | Off<br>(LINE=0)        | Off<br>(VDIVE=0)   | On                       | Off<br>(WDD=1) | Off<br>(NCS=1)    | Off or<br>Standby<br>(CSEx=X and<br>CSCx=0 and<br>PWMy=0) |

| Active SPI Comm. $I_{VS} = I_{VSact\_spi}$                                | Off<br>(LINE=0)        | Off<br>(VDIVE=0)   | On                       | Off<br>(WDD=1) | On<br>(NCS=0)     | Off<br>(CSEx=0)                                           |

| Active with watchdog $I_{VS} = I_{VSact\_wd}$                             | Off<br>(LINE=0)        | Off<br>(VDIVE=0)   | On                       | On<br>(WDD=0)  | do not care       | Off<br>(CSEx=0)                                           |

| Active with LIN-bus transceiver $I_{VS} = I_{VSact\_lin}$                 | On<br>(LINE=1)         | Off<br>(VDIVE=0)   | On                       | Off<br>(WDD=1) | do not care       | Off<br>(CSEx=0)                                           |

| Active with Current<br>Sources<br>I <sub>VS</sub> = I <sub>VSact_cs</sub> | Off<br>(LINE=0)        | Off<br>(VDIVE=0)   | On                       | Off<br>(WDD=1) | do not care       | On  (CSEx=1 and (CSCx=1 or PWMy=1))                       |

| Active with Voltage Divider  I <sub>VS</sub> = I <sub>act_vdiv</sub>      | Off<br>(LINE=0)        | On<br>(VDIVE=1)    | On                       | Off<br>(WDD=1) | do not care       | Off<br>(CSEx=0)                                           |

Note: Legend:

0 = bit is programmed 0 1 = bit is programmed 1,

X = Disregards

The descriptions in brackets below the peripherals refer to the configuration register of Atmel ATA664151, accessible via SPI.

Please note that the table above only lists the Active Mode states with just one extra peripheral enabled. Except for Active Low-power, any combination of the states above and thus also the current consumption is possible - for example, the parallel operation of the LIN bus transceiver and the current sources. The required supply current is then at least the sum of the values given above.

#### 4.2 Sleep Mode

This mode must be initialized via the SPI configuration register. All peripherals, i.e., the LIN transceiver, the watchdog, the voltage dividers, the Switch Interface Unit and the VCC voltage regulator are switched off. The overall supply current on pin VS is then reduced to a minimum.

Two wake-up mechanisms are possible to leave Sleep Mode again: wake-up via LIN and wake-up via CL15.

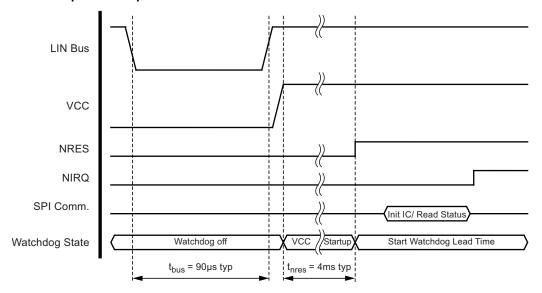

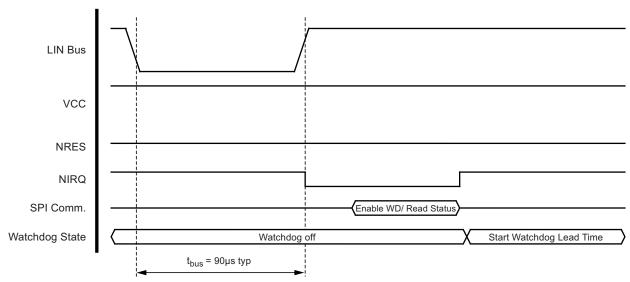

#### 4.2.1 Wake-up from Sleep Mode via LIN

A voltage below the LIN Pre-Wake threshold on the LIN pin activates a wake-up detection phase.

A falling edge at the LIN pin followed by a dominant bus level maintained for a time period of at least t<sub>bus</sub> and the following rising edge at the LIN pin (see Figure 4-2) results in a remote wake-up request. The device switches from Sleep Mode to Active-low Power Mode (VCC regulator enabled), but the LIN transceiver is still deactivated. Only the internal LIN slave termination resistor is switched on. The remote wake-up request is indicated by a low level at the NIRQ pin to interrupt the microcontroller (see Figure 4-2). In addition, the wake-up source is stated in the chip status register which can be read out via SPI. Configuring the chip via SPI must be used to enable the LIN transceiver and allow data to be send and/or transmited via the LIN bus. Note that this can only be done after the LOW level at the NRES pin has been eliminated (after VCC ramp-up and the stabilization phase).

Figure 4-2. LIN Wake-up from Sleep Mode

With the initialization of the configuration register by the microcontroller, the status word of Atmel ATA664151 is transmitted back, including the wake-up source. In other words, the two status bits "IRQS1" and "IRQS0" both read back as '1'. For more information see section "Serial Programming Interface (SPI)" on page 17.

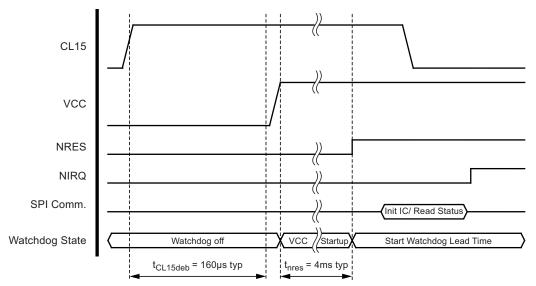

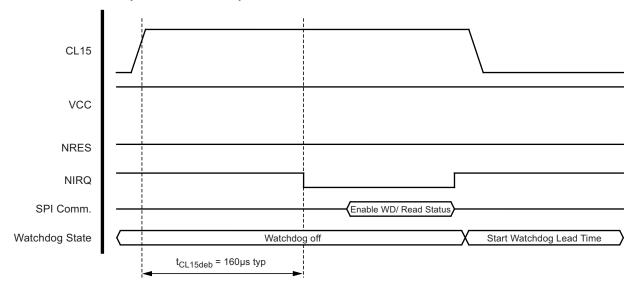

#### 4.2.2 Wake-up from Sleep Mode via CL15

Voltage above  $V_{CL15H}$  at pin CL15 activates a CL15 wake-up detection phase. This state must persist for at least  $t_{CLdeb}$  in order to detect a wake-up. If the pulse is too short, the IC remains in Sleep Mode.

When leaving Sleep Mode first the VCC voltage regulator is activated to enable the microcontroller supply. Then as soon as the VCC level reaches valid levels, the VCC startup timer is started. During this time, the NRES pin is kept low in order to keep the microcontroller from running. This ensures a proper voltage supply and signal stabilization in the application. With the rising edge at NRES, the SPI is ready for communication and the Atmel ATA664151 can be initialized.

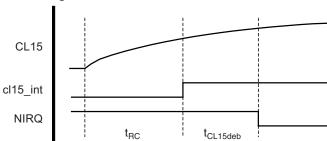

Figure 4-3. CL15 Wake-up from Sleep Mode

The wake-up behavior is analogous to a wake-up via the LIN bus as seen above. One difference is that no negative edge is required to start the wake-up procedure as is the case for LIN wake-ups. After the VCC startup time  $t_{WDnres}$  has elapsed, NRES is released and therefore pulled up, either by the internal or additional external resistors. The microcontroller can then configure the Atmel ATA664151 and thus be notified about the actual status including the wake-up source. Here, the two status bits "IRQS1" and "IRQS0" read back as '10'.

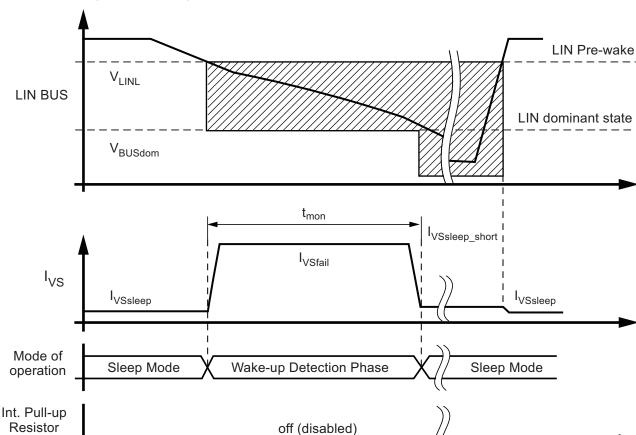

#### 4.2.3 Sleep Mode: Behavior at a Floating LIN bus or a Short-circuited LIN to GND

In Sleep Mode the device has very low current consumption even during short-circuits or floating conditions on the bus. A floating bus can arise if the master pull-up resistor is missing, such as when it is switched off while the LIN master is in Sleep Mode or even if the power supply of the master node is switched off.

In order to minimize the current consumption  $I_{VS}$  in Sleep Mode during voltage levels on the LIN pin below the LIN Pre-wake threshold, the receiver is activated only for a specific time  $t_{mon}$ . If  $t_{mon}$  elapses while the voltage at the bus is lower than Pre-wake detection low ( $V_{LINL}$ ) or higher than the LIN dominant level, the receiver is switched off again and the circuit changes back to Sleep Mode. The current consumption is then  $I_{VSsleep\_short}$  (typ. 10µA more than  $I_{VSsleep}$ ). If a dominant state is reached on the bus, no wake-up occurs. Even if the voltage rises above the Pre-wake detection high ( $V_{LINH}$ ), the IC will stay in Sleep Mode.

This means the LIN bus must be above the Pre-wake detection threshold  $V_{LINH}$  for a few microseconds before a new LIN wake-up is possible.

Figure 4-4. Floating LIN Bus During Sleep Mode

If the Atmel ATA664151 is in Sleep Mode and the voltage level at the LIN bus is in dominant state ( $V_{LIN} < V_{BUSdom}$ ) for a period exceeding  $t_{mon}$  (during a short circuit at LIN, for example), the IC switches back to Sleep Mode. The  $V_S$  current consumption is then  $I_{VSsleep\_short}$  (typ. 10µA more than  $I_{VSsleep}$ ). After a positive edge at the LIN pin the IC switches directly to Active Mode.

**RLIN**

LIN Pre-wake  $V_{\mathsf{LINL}}$ LIN BUS LIN dominant state  $V_{\rm BUSdom}$  $t_{mon}$  $t_{mon}$ IVSsleep\_short I<sub>VSfail</sub>  $I_{VS}$ I<sub>VSsleep</sub> Mode of Wake-up Detection Phase Sleep Mode Sleep Mode Active Mode operation Int. Pull-up on (enabled) Resistor off (disabled) **RLIN**

Figure 4-5. Short Circuit to GND on the LIN Bus During Sleep Mode

### 4.3 Active Low-power Mode

In this mode, the VCC voltage regulator is active and can therefore supply the application's microcontroller.

All other functions of the Atmel® ATA664151 are disabled in the configuration register respectively inhibited by the PWM pins for the CSx pin current sources. This reduces the current consumption of the chip itself to a low-power range of typically below  $50\mu$ A. Note that this is only valid if the chip select input of the SPI, NCS, is also kept at a high level. If it is pulled to ground, SPI communication is enabled, causing a higher current consumption.

If the LIN transceiver is disabled, the bus is monitored for a wake-up event, initialized with a voltage level below the LIN Prewake threshold at the LIN pin.

Figure 4-6. LIN Wake-up from Active Low-power Mode

The negative edge on the NIRQ pin indicates a change of conditions, in this case a wake-up request at the LIN bus. The microcontroller can check the IRQ source by assessing the "IRQS1" and "IRQS0" bits in the status register. Note that if a watchdog operation is desired, it must be enabled via the configuration register.

The behavior can be transferred to a wake-up over CL15 pin from Active Low-power Mode.

Figure 4-7. CL15 Wake-up from Active Low-power Mode

Apart from the LIN transceiver and the CL15 input, the high-voltage I/O ports CS1 to CS8 can also be used to generate interrupts while in Active Low-power Mode. This can be done by enabling the current sources so that they can generate an interrupt with the corresponding CSEx- and CSIEx bits in the configuration register. As long as the current source is not enabled (CSCx='0' and PWMy low), the IC stays in Active Low-power Mode (if all other conditions are met, such as disabled watchdog). The PWMy pin has to be set to high by the microcontroller, for example, controlled via a PWM timer unit, in order to check the condition of the connected switch. Because the switch interface unit is enabled, current consumption increases drastically. This "switch scanning phase" can be short compared to the interceding idle time so the mean current consumption of the IC remains close to the Active Low-power Mode current consumption. For more information, see sections "Current Sources" on page 22 and "Switch Inputs" on page 24 for further details.

### 4.4 Behavior under Low Supply Voltage Conditions

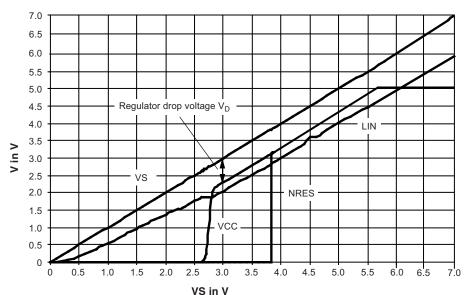

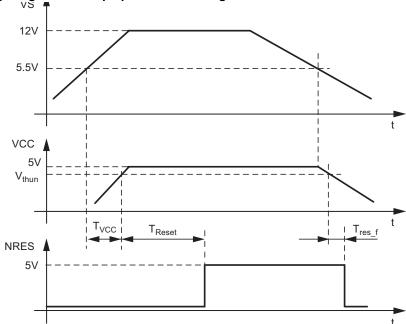

When connected to the car battery, the voltage at the VS pin increases according to the blocking capacitor (see Figure 4-8). As soon as  $V_{VS}$  exceeds its undervoltage threshold  $V_{VSthO}$ , the Switch Interface Unit and the LIN transceiver can be used. The IC is in Active Mode after power-up with the VCC voltage regulator and the Window Watchdog enabled – the latter depends on the state of the pin VDIV. The VCC output voltage reaches its nominal value after  $t_{VCC}$ . This time depends on the externally applied VCC capacitor and the load.

The NRES is low for the reset time delay  $t_{reset}$ . During this time  $t_{reset}$ , no SPI communication and thus no configuration changes or status checks are possible.

Figure 4-8. VCC versus VS

Please note that upper graph is only valid if the VS ramp-up time is much slower than the VCC ramp-up time  $t_{\text{VCC}}$  and the NRES delay time  $t_{\text{reset}}$ .

If during Active Mode the voltage level of VS drops below the undervoltage detection threshold  $V_{VSthU}$ , an interrupt is indicated to the microcontroller by means of a low-signal at the NIRQ pin. Furthermore, both the Switch Interface Unit and the LIN transceiver are shut down in order to avoid malfunctions or false bus messages. This shutdown is achieved by simply inhibiting the functions internally. The corresponding bits in the configuration register are not cleared. This means the functionality resumes if enabled after the supply voltage exceeds above  $V_{VSthO}$  again.

If during Sleep Mode the voltage level of VS drops below the undervoltage detection threshold  $V_{VSthU}$ , no change of mode or any other activity by the Atmel ATA664151 occurs as long as the level does not drop below the minimum operation value  $V_{VSopmin}$ .

## 5. Wake-up Scenarios from Sleep Mode

### 5.1 Remote Wake-up via the LIN Bus

A voltage lower than the LIN Pre-wake detection V<sub>LINL</sub> at the LIN pin activates the internal LIN receiver.

A falling edge at the LIN pin followed by a dominant bus level  $V_{BUSdom}$  of at least  $t_{BUS}$  and a rising edge at pin LIN results in a remote wake-up request. The device switches from Sleep Mode to Active Mode. The VCC voltage regulator is activated and the internal slave termination resistor is switched on. The remote wake-up request is indicated by a low level at the NIRQ pin. this generates an interrupt for the microcontroller and a corresponding flag in the SPI register.

#### 5.2 Local Wake-up via Pin CL15

A positive edge at pin CL15 followed by a high voltage level for a given time period ( $> t_{\text{CL15deb}}$ ) results in a local wake-up request. The device switches to Active Mode. The debouncing time ensures that no transients at CL15 create a wake-up. The local wake-up request is indicated by a low level at the NIRQ pin, generating an interrupt for the microcontroller. During high-level voltage at the CL15 pin, it is possible to switch to Sleep Mode via an SPI command. In this case the voltage at the CL15 pin has to be switched to low for at least  $t_{\text{CL15deb}}$  before the positive edge at this pin starts a new local wake-up request. Note that this time can be extended by adapting the external circuitry.

#### 5.3 Wake-up Source Recognition

The device can distinguish between different wake-up sources.

The source for the wake-up event can be read out of the SPI diagnosis register.

## 6. Wake-up Scenarios from Active Low-power Mode

Generally the Active Low-power Mode is only possible if all clock-dependent peripherals such as the LIN transceiver and the watchdog are disabled. In addition, no SPI communication is allowed to take place to minimize current consumption.

## 6.1 Wake-up from CSx Pins

The switch input pins can each be used to generate an interrupt request while in active low-power mode. A state change detection circuitry is implemented for this functionality (see section "Switch Inputs" on page 24). For this functionality, the respective current source needs to be configured so that it is controlled via the dedicated PWMy pin. A rising edge on this pin enables the current source, allowing a stable switch readback signal to be delivered at the CSx pin. The switch state is updated with a falling edge at the PWMy pin. If a change of state is monitored, an interrupt request is generated if the CSIE bit of the affected current source is set to '1' in the configuration register. If no wake-up should occur on a certain switch - either because there is no application demand for this or a failure such as a hanging switch or a connection line short-circuit is present - it can be prevented by disabling the current source in the SPI configuration register.

#### 6.2 Wake-up from LIN Bus

If during Active Low-power Mode (i.e., the LIN transceiver is disabled) the LIN bus is tied to ground for at least  $t_{bus}$ . This wake-up request is indicated by a negative edge at the NIRQ pin. Please note that the Atmel ATA664151 stays in active Low-power Mode for as long as no SPI communication occurs or configuration changes are made. Current consumption is only higher during the LIN bus assessment, in other words as long as the voltage on the LIN bus is below  $V_{LIN,preL}$ . Regardless of the LIN bus state, this assessment phase ends after  $t_{LIN\_wudet}$  at the latest. This ensures a low current consumption even during shorts on the LIN bus or when there are floating bus levels.

### 6.3 Wake-up from CL15

If during Active Low-power Mode the voltage on the CL15 pin exceeds  $V_{\text{CL15H}}$  for at least  $t_{\text{CL15deb}}$ , an interrupt request is triggered to indicate a change of state at the CL15 pin. Please note that after the  $t_{\text{CL15deb}}$  has elapsed, the Atmel ATA664151 stays in Active Low-power Mode for as long as no SPI communication occurs or configuration changes are made.

#### 6.4 Wake-up from SPI

If during Active Low-power Mode the chip select input NCS is tied to ground, Atmel ATA664151 leaves the Active Low-power Mode in order to complete a data communication with the SPI master. The operating mode of the IC is adapted in accordance with the configuration register update. If no change in configuration has taken place – for example, because only the actual status was polled or another bus member connected via daisy chaining was addressed – Atmel ATA664151 goes back to Active Low-power Mode as soon as NCS returns to High level.

# 7. Serial Programming Interface (SPI)

Most features of the IC are configured via SPI. Diagnostics are carried out using this interface also. It can be used in Active Mode as long as there is no undervoltage condition at the VCC pin.

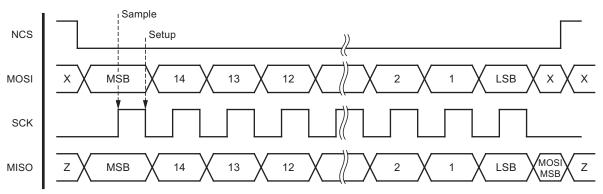

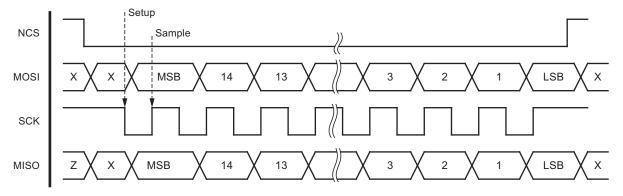

The Atmel ATA664151 SPI features both POL = 0 / PHA = 0 and POL = 1 / PHA = 1 operating modes.

Figure 7-1. POL = 0 / PHA = 0 Setup

Figure 7-2. POL = 1 / PHA = 1 Setup

The interface contains four pins.

- NCS (chip select pin, active low)

- SCK (serial data clock)

- MOSI (Master-Out-Slave-In serial data port input from master)

- MISO (Master-In-Slave-Out serial data port output from SBC; this pin is tri-state if NCS is high)

No data is loaded from MOSI on SCK edges or provided at MISO if chip select is not active. The output pin MISO is not actively driven (tri-state) during these phases.

The data transfer scheme (bit order) is MSB first, meaning the first bit that is transferred is the most significant bit of the register, with the transfer ending with the least significant bit. These bits are listed on the next pages. The MOSI bits 15 to 0 refer to the configuration register. This means the configuration register is updated with each SPI communication. At the same time the MISO word is built from the status register bits 15 to 0. Note that changes in the configuration are only visible in the next status query. This means, for example, that if you enable the watchdog with an SPI command, the status "Watchdog Active" is not reported in this data transmission but in the next one.

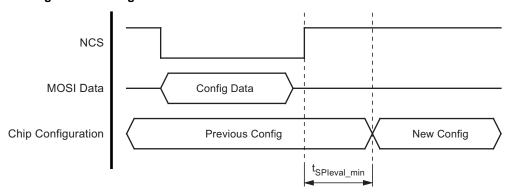

In order to load any data into the chip, the chip select signal must be removed (i.e., set to high) after the 16 SCK clock periods. A minimum data evaluation time t<sub>SPleval,min</sub> has to transpire before the next data transfer can start. Please note also that any change in configuration of the IC requires this time to go into effect.

Figure 7-3. SPI Configuration Timing

The following table lists the bits of the configuration register in the Atmel ATA664151.

Table 7-1. SPI Configuration Register

| #         | Bit Name | Description                       | Default ('0')               | Programmed with '1'                       | Remark                                                                               |

|-----------|----------|-----------------------------------|-----------------------------|-------------------------------------------|--------------------------------------------------------------------------------------|

| 15<br>MSB | LSME     | Enable LIN-bus<br>High-Speed Mode | Normal                      | HighSpeed                                 | See LIN transceiver description                                                      |

| 14        | TTTD     | Disable TxD Timeout<br>Timer      | Enabled                     | Disabled                                  | See Section 3.6 "Bus Logic<br>Level Input Pin (TXD)" on page 5                       |

| 13        | IMUL     | IREF Multiplier Value             | x100                        | x50                                       | See section Section 8. "Switch<br>Interface Unit" on page 22                         |

| 12        | LINE     | Enable LIN transceiver            | Disabled                    | Enabled                                   | See LIN transceiver description                                                      |

| 11        | SLEEP    | Go to Sleep                       | Stay in Active<br>Mode      | Enable Sleep<br>Mode                      | See Section 4. "Operating Modes" on page 8                                           |

| 10        | VDIVE    | Enable VDIV as output             | VDIV off<br>(high-ohmic)    | VDIV on (selected voltage divider active) | See Section 8.2.2 on page 26<br>and Section 8. "Switch Interface<br>Unit" on page 22 |

| 9         | VDIVP    | Programming VDIV output source    | VDIV shows<br>VBATT divider | VDIV shows one<br>CS divider output       | See Section 8.2.2 on page 26 and Section 8. "Switch Interface Unit" on page 22       |

Table 7-1. SPI Configuration Register (Continued)

|          | Table 7 1. Of Footingulation Register (Gontandea) |                                                    |                                          |                                 |                                                                                                                         |  |  |  |  |  |

|----------|---------------------------------------------------|----------------------------------------------------|------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| #        | Bit Name                                          | Description                                        | Default ('0')                            | Programmed with '1'             | Remark                                                                                                                  |  |  |  |  |  |

| 8        | CSPE                                              | Enable Switch Interface<br>Unit programming        | Disabled                                 | Enabled                         | See section Section 8. "Switch<br>Interface Unit" on page 22                                                            |  |  |  |  |  |

| 7        | CSA2                                              | Address bit 2 (MSB) for<br>Switch Input            | 0                                        | 1                               | Used as selector for VDIV and for Programming of one Current Source                                                     |  |  |  |  |  |

| 6        | CSA1                                              | Address bit 1 for Switch Input                     | 0                                        | 1                               | Used as selector for VDIV and for Programming of one Current Source                                                     |  |  |  |  |  |

| 5        | CSA0                                              | Address bit 0 (LSB) for Switch Input               | 0                                        | 1                               | Used as selector for VDIV and for Programming of one Current Source                                                     |  |  |  |  |  |

| 4        | CSE                                               | Enable addressed current source                    | Disabled                                 | Enabled                         | See section Section 8. "Switch<br>Interface Unit" on page 22                                                            |  |  |  |  |  |

| 3        | CSSSM                                             | Switch between<br>Source/Sink Mode                 | Source Mode<br>selected<br>(HighSide)    | Sink Mode<br>selected (LowSide) | Sink mode is only possible for<br>Switch Interfaces 1-3                                                                 |  |  |  |  |  |

| 2        | CSC                                               | Control of addressed current source                | External (CSE and PWMy)                  | Internal<br>(CSE only)          | See section Section 8. "Switch<br>Interface Unit" on page 22                                                            |  |  |  |  |  |

| 1        | CSIE<br>(CSPE=1)                                  | Enable Interrupt<br>from addressed Switch<br>Input | Disabled                                 | Enabled                         | CSIE will be altered if CSPE<br>of the SPI word is '1'.<br>See section Section 8. "Switch<br>Interface Unit" on page 22 |  |  |  |  |  |

| 1        | CSSCD<br>(CSPE=0)                                 | CS port current source slope control               | Enabled                                  | Disabled                        | CSSCD will be altered if CSPE of the SPI word is '0'. See section Section 8. "Switch Interface Unit" on page 22         |  |  |  |  |  |

| 0<br>LSB | WDD                                               | Disable watchdog                                   | Enabled<br>(if pin VDIV<br>on low level) | Disabled                        | See section Section 10. "Watchdog" on page 28                                                                           |  |  |  |  |  |

The following table lists the bits of the status register in Atmel ATA664151.

Figure 7-4. SPI Status Register

| #   | Bit Name            | Description                                               | Result = "0"                                                              | Result = "1"                          | Remark                                                                           |  |

|-----|---------------------|-----------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------|--|

| 15  | OTVCC<br>(VDIVE=0)  | Overtemperature prewarning from VCC regulator temp sensor | Temperature not critical                                                  | Temperature critical                  | See Section 9. on page 27; only valid if VDIVE of prev. command was '0'          |  |

| MSB | MVBATT<br>(VDIVE=1) | VBATT voltage monitor                                     | VBATT not<br>visible on<br>VDIV                                           | VBATT visible on VDIV                 | Only valid if VDIVE of prev. command was '1'                                     |  |

| 14  | OTLIN<br>(VDIVE=0)  | Overtemperature signal from LIN driver temp sensor        | no Over-<br>temperature                                                   | Over-<br>temperature                  | See Section 3.5 on page 5; only valid if VDIVE of prev. command was '0'          |  |

| 14  | MRDIV2<br>(VDIVE=1) | CS port voltage monitor, address bit 2 (MSB)              | MRDIV20 indi<br>of the CS port<br>visible on VDIV                         |                                       | This bit is only shown if VDIVE of previous command was '1'                      |  |

| 13  | OTCS<br>(VDIVE=0)   | Overtemperature signal from current sources temp sensor   | no Over-<br>temperature                                                   | Over-<br>temperature                  | See Section 8. on page 22; only valid if VDIVE of prev. command was '0'          |  |

| 13  | MRDIV1<br>(VDIVE=1) | CS port voltage monitor, address bit 1                    | MRDIV20 indicate the address of the CS port volt. monitor visible on VDIV |                                       | This bit is only shown if VDIVE of previous command was '1'                      |  |

| 12  | CL15S<br>(VDIVE=0)  | CL15 pin status                                           | V <sub>CL15</sub> < V <sub>CL15H</sub>                                    | $V_{CL15} \ge V_{CL15H}$              | See section Section 11. on page 30; only valid if VDIVE of prev. command was '0' |  |

| 12  | MRDIV0<br>(VDIVE=1) | CS port voltage monitor, address bit 0 (LSB)              | MRDIV20 indi<br>of the CS port<br>visible on VDIV                         |                                       | This bit is only shown if VDIVE of previous command was '1'                      |  |

| 11  | WDS                 | Watchdog status                                           | Watchdog<br>disabled                                                      | Watchdog<br>enabled                   | See Section 10. "Watchdog" on page 28                                            |  |

| 10  | VSS                 | VS voltage level status                                   | VS voltage<br>OK                                                          | VS<br>undervoltage                    | See Section 4.4 on page 15                                                       |  |

| 9   | IRQS1               | Interrupt request source                                  | "00" Power                                                                | ange                                  | Information will be cleared after                                                |  |

| 8   | IRQS0               |                                                           | "10" CL15 v<br>"11" LIN wa                                                | wake-up<br>ake-up                     | status register readout via SPI                                                  |  |

| 7   | CS8CS               | Switch Interface 8 comparator status                      | V <sub>CS8</sub> < V <sub>CSxth</sub>                                     | $V_{CS8} > V_{CSxth}$                 | See section Section 8. "Switch<br>Interface Unit" on page 22                     |  |

| 6   | CS7CS               | Switch Interface 7 comparator status                      | V <sub>CS7</sub> < V <sub>CSxth</sub>                                     | V <sub>CS7</sub> > V <sub>CSxth</sub> | See section Section 8. "Switch<br>Interface Unit" on page 22                     |  |

| 5   | CS6CS               | Switch Interface 6 comparator status                      | V <sub>CS6</sub> < V <sub>CSxth</sub>                                     | V <sub>CS6</sub> > V <sub>CSxth</sub> | See section Section 8. "Switch<br>Interface Unit" on page 22                     |  |

Figure 7-4. SPI Status Register

| #        | Bit Name | Description                          | Result = "0"                          | Result = "1"                          | Remark                                                       |

|----------|----------|--------------------------------------|---------------------------------------|---------------------------------------|--------------------------------------------------------------|

| 4        | CS5CS    | Switch Interface 5 comparator status | V <sub>CS5</sub> < V <sub>CSxth</sub> | V <sub>CS5</sub> > V <sub>CSxth</sub> | See section Section 8. "Switch<br>Interface Unit" on page 22 |

| 3        | CS4CS    | Switch Interface 4 comparator status | V <sub>CS4</sub> < V <sub>CSxth</sub> | $V_{CS4} > V_{CSxth}$                 | See section Section 8. "Switch<br>Interface Unit" on page 22 |

| 2        | CS3CS    | Switch Interface 3 comparator status | V <sub>CS3</sub> < V <sub>CSxth</sub> | V <sub>CS3</sub> > V <sub>CSxth</sub> | See section Section 8. "Switch<br>Interface Unit" on page 22 |

| 1        | CS2CS    | Switch Interface 2 comparator status | V <sub>CS2</sub> < V <sub>CSxth</sub> | $V_{CS2} > V_{CSxth}$                 | See section Section 8. "Switch<br>Interface Unit" on page 22 |

| 0<br>LSB | CS1CS    | Switch Interface 1 comparator status | V <sub>CS1</sub> < V <sub>CSxth</sub> | V <sub>CS1</sub> > V <sub>CSxth</sub> | See section Section 8. "Switch<br>Interface Unit" on page 22 |

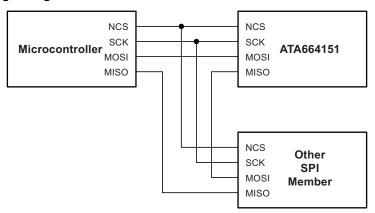

The SPI is capable of daisy chaining as well. In other words, if other ICs with a daisy-chaining-enabled SPI are to be used in the application, they can simply be interconnected one after the other (see Figure 7-5).

Figure 7-5. Daisy Chaining Configuration

It can be seen that the data output of Atmel ATA664151 is not connected to the data input of the master but of another SPI member which is also capable of daisy chaining. In order to transmit data, the microcontroller has to send the sum of clock pulses for all bus members. In the example above, if the other SPI member also features 16 bits, the microcontroller has to perform 32 clock cycles with NCS kept low to completely move the data. The first 16 bits of such a transmission are initially fed into the Atmel ATA664151. But when NCS stays low, the data is not loaded into its configuration register but instead shifted out again with the next 16 bits. At the same time the status register of Atmel ATA664151 is first fed into the other SPI bus member which then needs to transfer the data over to the microcontroller with the second 16 bits.

In summary, the daisy chaining is one way to have multiple bus members connected to a single master. Because not all devices support these operating modes, the Atmel ATA664151 still supports the direct addressing mode using the NCS pin. If NCS is not pulled to ground, all data traffic on the SPI is disregarded by the Atmel ATA664151.

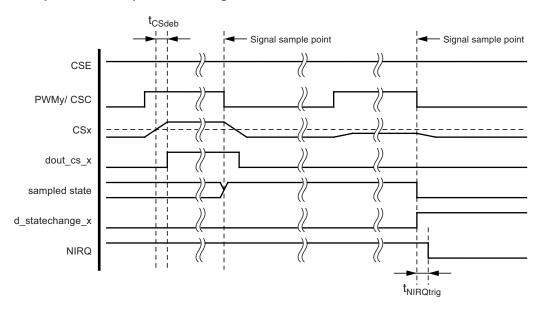

#### 8. Switch Interface Unit

A total of eight high-side current sources with high voltage comparators and voltage dividers are available for switch scanning or for example, LED driving purposes. Note that three of them (CS1, CS2, and CS3) can also be switched to low-side current sinks in the configuration register via the SPI. System wake-up from Active Low-power Mode is possible through state change monitoring. Please see Figure 8-1 for an overview of the interface structure.

VS CSE [1..8]  $I_{IREF} \times rI_{CS}$ PWM<sub>V</sub> CSC [1..8] State change d\_statechange detector V<sub>CSxth</sub> (4V DC) HV dout\_cs\_x CSx CSA [2..0] **VBATT** VDIV VDIVP **AGND VDIVE**

Figure 8-1. Principle Schematic of a High-Side-Only Switch Interface (CS4 - CS5)

The control signals CSE and CSC are configuration register bits, and unique for each of the eight interfaces. The output signal dout\_cs of the comparator can be probed via the SPI status register bit CSxCS.

#### 8.1 Current Sources

The current sources are available in Active Mode. They deliver a current level derived from a reference value measured at the IREF pin. This pin is voltage-stabilized ( $V_{IREF}$  = 1.23V typ.) so that the reference current is directly dependent on the externally applied resistor connected between IREF pin and ground. The resulting current at the CSx- pins is (1.23V/R<sub>Iref</sub>) x rI<sub>CS</sub>. For example, with a 12K resistor between IREF and GND the value of the current at the CSx-pins is 10mA (assumed IMUL = '0' => rI<sub>CS\_H</sub> = 100). For fail-safe reasons, both a missing and a short-circuited resistor are detected. In this case, an internally generated reference current I<sub>IREFfs</sub> is used instead to maintain a certain functionality.

The current sources of I/Os 1-3 (CS1..CS3) can be configured either as High-sides (current sources) or Low-sides (current sinks). This selection is done by the CSSSM bit of the configuration register. The default value of '0' enables the High-side source whereas a '1' enables the Low-side sink.

The output current level can be divided by 2 with the IMUL bit in the configuration register. With the default setting of IMUL = '0', the ratio between the output current  $I_{CSx}$  and the reference current  $I_{IREF}$  is  $I_{CS\_H}$  (typ. 100). If set to '1', the ratio reduces to  $I_{CS\_L}$  (typ. 50).

If a current source is enabled by the configuration register (set to ready state, bit CSE = '1'), it supports two different operating modes.

- Directly controlled by the configuration register bit CSC = '1'

- Externally gated (inhibited with the PWMy pin) bit CSC = '0' (default)

These modes can be selected independently for each current source via the configuration register. While the current source is permanently on with CSC = '1' it is controlled externally by the logic level input pins PWMy with CSC = '0' for switch scanning or LED driving (external PWM control). The following truth table summarizes all setup variants.

Table 8-1. CS Port Configuration Table

| CSEx | CSCx | CSSSM | PWMy | CS13 | CS48 | Active Low-power<br>Mode Possible |

|------|------|-------|------|------|------|-----------------------------------|

| 0    | Χ    | Χ     | Х    | Off  | Off  | Yes                               |

| 1    | 0    | Χ     | 0    | Off  | Off  | Yes                               |

| 1    | 1    | 0     | X    | 1    | 1    | No                                |

| 1    | 1    | 1     | Χ    | 0    | 1    | No                                |

| 1    | 0    | 0     | 1    | 1    | 1    | No                                |

| 1    | 0    | 1     | 1    | 0    | 1    | No                                |

#### Legend:

0 -> Bit = '0' for CSEx, CSCx and CSSSM; Logic low for PWMy; LS current source active for CS1..3

1 -> Bit = '1' for CSEx, CSCx and CSSSM; Logic high for PWMy; HS current source active for CS1..8

X -> Do not care for CSEx, CSCx, CSSM and PWMy

Off -> Current source disabled

Please see Table 8-2 for the assignment between the three available PWM control ports PWM1..3 and the eight current source outputs CS1..8.

Table 8-2. Assignment of Current Sources to the PWMy Ports

| PWM<br>Port | CS1 | CS2 | CS3 | CS4 | CS5 | CS6 | CS7 | CS8 |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| PWM1        | X   | -   | -   | -   | -   | -   | X   | Χ   |

| PWM2        | -   | X   | -   | -   | X   | X   | -   | -   |

| PWM3        | -   | -   | X   | X   | -   | -   | -   | -   |

There is one common control bit for all current sources, the bit "CSSCD". With this bit, the slope control of all eight sources can be disabled. By default, the slope control is activated and all currents are switched on and off smoothly (see also parameter  $dU_{CSx,rise}$  and  $dU_{CSx,rise}$ ). When setting this bit to '1', the current sources are enabled and disabled without transition times.

In order to change the configuration of a certain current source via SPI, it must be addressed and the current source programming bit CSPE must be set to '1'. Please see Table 8-3 for the eight available current sources.

Table 8-3. CS Port Addressing Table

| Current Source on Pin | Bit CSA0 | Bit CSA1 | Bit CSA2 |

|-----------------------|----------|----------|----------|

| CS1, High- or LowSide | 0        | 0        | 0        |

| CS2, High- or LowSide | 1        | 0        | 0        |

| CS3, High- or LowSide | 0        | 1        | 0        |

| CS4, HighSide only    | 1        | 1        | 0        |

| CS5, HighSide only    | 0        | 0        | 1        |

| CS6, HighSide only    | 1        | 0        | 1        |

| CS7, HighSide only    | 0        | 1        | 1        |

| CS8, HighSide only    | 1        | 1        | 1        |

That is, if any of the following configuration bits (CSE, CSSSM, CSIE, and CSC) of a certain I/O port shall be changed, the required data word for the SPI must contain the desired I/O number (bits CSA0..2) and the programming enable bit CSPE must be '1'. Only in this case, the corresponding bits in the SPI data word are loaded into the configuration register of the selected switch interface. For the global current source configuration bit CSSCD (slope control for current sources), the CSPE bit must be '0' in order to be changed via an SPI command. That is, either the four individual configuration bits (CSE, CSSSM, CSIE and CSC) or the global configuration bit (CSSCD) can be changed with one SPI command word.

Dependent on the selected current, the supply voltage, the externally applied load and the number of current sources activated, a not neglectable amount of power will be dissipated in Atmel ATA664151. In order to protect the IC from damage, the current sources are equipped with thermal monitors. If the temperature in one of the monitors exceeds  $T_{jsd}$ , all current sources will be shut down and an interrupt will be generated. Note that the current source enabled bits (CSE) in the configuration register are not cleared by this event. That is, the current sources will be enabled after a certain cooling time.

#### 8.2 Switch Inputs

## 8.2.1 Voltage Comparators

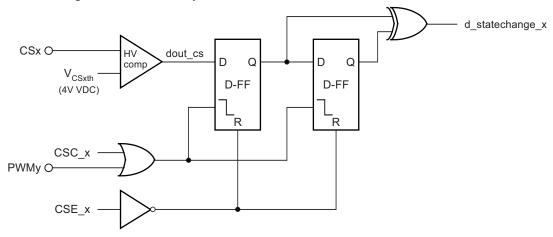

Each switch input has a high voltage comparator, a state-change-detection register for wake-up and interrupt request generation and a voltage divider with a low-voltage output that can be fed through to the measurement pin VDIV.

In Sleep Mode, the HV comparators and the voltage dividers of each input are switched off. In Active Mode, the comparator of a channel is activated together with its current source. It has a threshold of  $V_{CSxth}$ . The output signal dout\_csx of the comparator is debounced with a delay of  $t_{CSdeb}$ . A voltage above the threshold will generate a logical '1' in the status register bit CSxCS whereas a voltage below will lead to a '0'.

The comparator output signal is also fed into a state change detection logic that can be used to generate wake-up events in form of an interrupt request, signalized on pin NIRQ. Please see Figure 8-2 on page 25 for an overview of the state change detection unit.

Figure 8-2. State Change Detection Circuitry

As can be seen in Figure 8-2, the data from the comparator is latched with the falling edge of either the PWMy pin or the CSC bit. That is, the data is latched in the same moment when the current source is switched off. This ensures that the comparator signal was already stable when its output is evaluated. The output signal d\_statechange is evaluated by the main control logic. If the interrupt enable bit CSIE is set in the configuration register and d\_statechange is '1', an interrupt is generated and reported by a low level on pin NIRQ. Please see Figure 8-3 for an example of the state change detection system.

Figure 8-3. Interrupt Generation upon State Change

The output state of the HV comparator is sampled with each falling edge of the PWMy or CSC signal. As soon as the sampled state changes, an interrupt request is given.

In order to have minimum power consumption also for switch scanning applications, Atmel ATA664151 is able to switch to Active Low-power Mode even if current sources are enabled with the CSEx bit in the configuration register. As long as the current source is inhibited (for example, by having CSCx programmed to 0 and PWMy also at low level), the IC can be in Active Low-power Mode (dependent on the other peripherals, see also Table 4-1 on page 9). The current source is then in a kind of stand-by situation. As soon as the PWMy pin is raised, the IC switches to Active Mode with the defined current sources on.

### 8.2.2 Voltage Dividers

A voltage divider (division by 4) is included for each of the eight CS port channels. Please note that the divider is always referred to local ground (pin AGND), regardless of the respective current source/sink configuration. As there is only one output available for all voltage dividers of the chip, only one of them can be active at a time. The SPI data word must contain the following information in order to activate the voltage divider of a certain switch interface.

- The voltage divider enable bit VDIVE must be '1'.

- The VDIV programming source bit VDIVP must be '1'.

- The desired channel must be coded in the three address bits CSA0..2.

Please see Table 8-4 for a list of all voltage divider programming inputs and their corresponding VDIV output state.

Table 8-4. Voltage Divider Addressing Table

| VDIVE | VDIVP | CSA2 | CSA1 | CSA0 | VDIV      |

|-------|-------|------|------|------|-----------|

| 0     | X     | X    | X    | X    | Off       |

| 1     | 0     | X    | X    | X    | VBATT / 4 |

| 1     | 1     | 0    | 0    | 0    | CS1 / 4   |

| 1     | 1     | 0    | 0    | 1    | CS2 / 4   |

| 1     | 1     | 0    | 1    | 0    | CS3 / 4   |

| 1     | 1     | 0    | 1    | 1    | CS4 / 4   |

| 1     | 1     | 1    | 0    | 0    | CS5 / 4   |

| 1     | 1     | 1    | 0    | 1    | CS6 / 4   |

| 1     | 1     | 1    | 1    | 0    | CS7 / 4   |

| 1     | 1     | 1    | 1    | 1    | CS8 / 4   |

#### Legend:

0 -> Bit = '0'

1 -> Bit = '1'

X -> Do not care

## 9. Voltage Regulator

The VCC voltage regulator in Atmel ATA664151 is a linear low-drop regulator and requires an external capacitor for compensation and for smoothing the disturbances in the microcontroller. It is mandatory to use a capacitor with C > 1.8 $\mu$ F and ESR of below 5 $\Omega$ . An additional ceramic capacitor with C = 100nF is recommended for EMI suppression. The values of these capacitors can be varied depending on the application.

Figure 9-1. VCC Voltage Regulator: Ramp-up and Undervoltage Detection

The VCC output transistor is contributing to the ICs total power dissipation – defined by the voltage drop over the transistor and the output current  $I_{VCC}$ . In the figure below, the safe operating area of Atmel ATA664151 is shown. To avoid a thermal shutdown of the VCC output, the maximum load current decreases with rising ambient temperature and/or battery supply voltage. Please note also that the current sources contribute to power dissipation.

Because the VCC voltage generation is usually fundamental to sytem operation, there is a thermal prewarning implemented in the Atmel ATA664151. The thermal monitor of the VCC output transistor can indicate a critical temperature condition of T<sub>VCCprew</sub> by means of an interrupt and the status bit OTVCC in the status register of the chip. The microcontroller can thus react to these events by shutting down external loads that use the VCC or reducing its own power consumption in order to avoid a thermal shutdown.

Nevertheless, if the junction temperature of the output transistor exceeds the shutdown threshold  $T_{jsd}$ , the transistor as well as the VCC are shut down until the temperature has decreased at least by  $T_{jsdhyst}$ . After this cooling-down period, the regulator starts again in the same way as when powering up or for a wake-up from Sleep Mode.

For microcontroller programming, it may be necessary to supply the VCC output via an external power supply. It is then mandatory to disconnect pin VS of the system basis chip, and an operation of Atmel ATA664151 is not possible.

## 10. Watchdog

The watchdog expects a trigger signal from the microcontroller at the NTRIG (negative edge) input within a time window of  $t_{wd}$ . The trigger signal must exceed a minimum time  $t_{trigmin} > 7\mu s$ . If a triggering signal is not received, a reset signal will be generated at output NRES. The timing basis of the watchdog is provided by the internal watchdog oscillator. Its time period,  $t_{WDosc}$ , is adjustable via the external resistor  $R_{wd}$  osc (34k $\Omega$  to 120k $\Omega$ ).

During Sleep Mode the watchdog is switched off to reduce current consumption. In order to enter Active Low-power Mode, the watchdog also needs to be disabled via the configuration register. In order to avoid false watchdog disabling, this configuration bit (WDD) needs to be written twice, i.e., with two consecutive SPI words in order to be altered to '1'.

In order to disable the watchdog right from the start (i.e., after external power-up or after Sleep Mode), pin VDIV has to be tied to VCC until the startup time t<sub>reset</sub> of typ. 4ms has elapsed (see "VDIV Input/Output Pin" on page 7).

The minimum time for the first watchdog pulse is required after the undervoltage reset at NRES disappears. It is defined as lead time  $t_d$ . After wake-up from Sleep Mode, the lead time  $t_d$  starts with the positive edge of the NRES output.

## 10.1 Typical Timing Sequence with $R_{WD OSC} = 51k\Omega$

The trigger signal  $T_{wd}$  is adjustable between 20ms and 64ms using the external resistor  $R_{WD\ OSC}$ .

For example, with an external resistor of  $R_{WD OSC}$  = 51k $\Omega$  ± 1%, the typical parameters of the watchdog are as follows.

$$t_{osc} = 0.782 \times R_{WD\_OSC} + 1.7 \times 10^{-6} \times (R_{WD\_OSC})^2 \qquad [R_{WD\_OSC} \text{ in } k\Omega; t_{osc} \text{ in } \mu s]$$

$t_{OSC}$  = 39.9µs due to 51k $\Omega$

$t_d = 3948 \times 39.9 \mu s = 157.5 ms$

$t_1 = 553 \times 39.9 \mu s = 22.1 ms$

$t_2 = 527 \times 39.9 \mu s = 21 ms$

$t_{nres}$  = constant = 4ms

After ramping up the battery voltage, the VCC regulator is switched on. The reset output NRES stays low for the time  $t_{reset}$  (typically 4ms), then it switches to high, and the watchdog waits for the trigger sequence from the microcontroller. The lead time,  $t_d$ , follows the reset and  $t_d$  = 155ms. In this time, the first watchdog pulse from the microcontroller is required. If the trigger pulse NTRIG occurs during this time, the time  $t_1$  starts immediately. If no trigger signal occurs during the time  $t_d$ , a watchdog reset with  $t_{reset}$  = 4ms resets the microcontroller after  $t_d$  = 155ms. The times  $t_1$  and  $t_2$  have a fixed relationship. A triggering signal from the microcontroller is anticipated within the time frame of  $t_2$  = 21.6ms. To avoid false triggering from glitches, the trigger pulse must be longer than  $t_{TRIG,min}$  > 7 $\mu$ s. This slope restarts the watchdog sequence. If the triggering signal fails in this open window  $t_2$ , the NRES output is drawn to ground. A triggering signal during the closed window  $t_1$  immediately switches NRES to low.

Undervoltage Reset  $t_{reset} = 4ms$   $t_{d} = 155ms$   $t_{1} = 20.6ms$   $t_{wd}$   $t_{trig} > 7 \mu s$ Watchdog Reset  $t_{nres} = 4ms$

Figure 10-1. Timing Sequence with  $R_{WD\ OSC}$  = 51k $\Omega$

## 10.2 Worst Case Calculation with $R_{WD, OSC} = 51k\Omega$

The internal oscillator has a tolerance of 20%. This means that  $t_1$  and  $t_2$  can also vary by 20%. The worst-case calculation for the watchdog period  $t_{wd}$  is as follows.

The ideal watchdog time t<sub>wd</sub> is between the maximum t<sub>1</sub> and the minimum t<sub>2</sub>.

$$\begin{split} t_{1,\text{min}} &= 0.8 \times t_1 = 16.8 \text{ms}, \ t_{1,\text{max}} = 1.2 \times t_1 = 25.2 \text{ms} \\ t_{2,\text{min}} &= 0.8 \times t_2 = 17.7 \text{ms}, \ t_{2,\text{max}} = 1.2 \times t_2 = 26.5 \text{ms} \\ t_{\text{wdmax}} &= t_{1\text{min}} + t_{2\text{min}} = 16.8 \text{ms} + 17.7 \text{ms} = 34.5 \text{ms} \\ t_{\text{wdmin}} &= t_{1\text{max}} = 25.2 \text{ms} \\ t_{\text{wd}} &= 29.9 \text{ms} \pm 4.6 \text{ms} \ (\pm 15\%) \end{split}$$

A microcontroller with an oscillator tolerance of ±15% is sufficient to supply the trigger inputs correctly.

Table 10-1. Typical Watchdog Timings

| R <sub>WD_OSC</sub><br>kΩ | Oscillator<br>Period<br>t <sub>osc</sub> /µs | Lead<br>Time<br>t <sub>d</sub> /ms | Closed<br>Window<br>t <sub>1</sub> /ms | Open Window<br>t <sub>2</sub> /ms | Trigger Period from<br>Microcontroller t <sub>wd</sub> /ms | Reset Time<br>t <sub>nres</sub> /ms |

|---------------------------|----------------------------------------------|------------------------------------|----------------------------------------|-----------------------------------|------------------------------------------------------------|-------------------------------------|

| 34                        | 26.6                                         | 105                                | 14.0                                   | 14.7                              | 20.13                                                      | 4                                   |

| 51                        | 39.9                                         | 157.5                              | 21                                     | 22.1                              | 29.85                                                      | 4                                   |

| 91                        | 71.2                                         | 281                                | 37.5                                   | 39.4                              | 53.27                                                      | 4                                   |

| 120                       | 93.9                                         | 370.6                              | 49.5                                   | 51.9                              | 70.26                                                      | 4                                   |

Note that in the case of a missing or shorted resistor on pin WDOSC, the watchdog oscillator period will be well below or above the reachable values listed above. In other words, if not disabled after startup by using the VDIV pin or during operation with the SPI configuration, a watchdog reset will be generated all the time for fail-safe reasons.

## 11. CL15 HV Input

The CL15 pin can be used as ignition state detection and wake-up input. It has a weak internal pull-down structure, so if no voltage is connected to this pin, it is at ground level, the passive state of this input. In order to generate an interrupt request or to wake-up from Sleep Mode, a certain voltage needs to be applied to this pin.

The input voltage threshold can be adjusted by varying the external resistor due to the input current  $I_{CL_15}$ . To protect this pin against voltage transients, a serial resistor of  $10k\Omega$  and a ceramic capacitor of 47nF are recommended. With this RC combination you can increase the wake-up time  $t_{CL15deb}$  as well as enhance sensitivity against transients when ignition of the CL15 pin occurs.

You can also increase the wake-up time using external capacitors with higher values. In Figure 11-1, the reaction of the Atmel ATA664151 to a signal at the CL15 pin is shown. Note that the pin is connected via an R/C low-pass filter.

Figure 11-1. Timing for CL15 Debouncing

In the diagram above, the voltage at the CL15 pin is shown. Due to the R/C filter, the voltage does not immediately increase but instead slowly over time. As soon as the voltage exceeds approximately 3V, the internal debouncing time  $t_{CL15deb}$  starts. After this elapses, a wake-up is indicated by a falling edge on the NIRQ pin.

#### 12. Fail-safe Features

- During a short-circuit at LIN to V<sub>Battery</sub>, the output current is limited to I<sub>BUS\_lim</sub>. Due to power dissipation, the chip temperature might exceed T<sub>LINoff</sub>, causing a shutdown of the LIN output transistor. That in turn starts the chip cooling phase, and after a hysteresis of T<sub>hys</sub> the output can be switched on again with TXD = 0. During shutdown, RXD indicates the LIN bus state, which is typically recessive because the output transistor is off. Please note that the VCC voltage regulator works independently from the LIN output transistor temperature monitor because it is equipped with its own monitor.

- During a short-circuit at LIN to GND, the IC can be switched to Sleep Mode. If the short-circuit disappears, the IC starts with a remote wake-up.

- The reverse current is very low < 2μA at the LIN pin during loss of V<sub>Batt</sub>. This is optimal behavior for bus systems where some slave nodes are supplied from battery or ignition.

- During a short circuit at VCC, the output limits the output current to I<sub>VCClim</sub>. Because of undervoltage, NRES switches to low and can therefore reset the connected microcontroller. If the chip temperature of the VCC output transistor exceeds the value T<sub>VCCoff</sub>, the VCC output switches off. The chip cools down and after a hysteresis of T<sub>hys</sub>, the output is reactivated.

- The NCS pin provides a pull-up resistor to force the SPI output into tri-state mode if NCS is disconnected

- The TXD pin provides a pull-up resistor to force the transceiver into recessive mode if TXD is disconnected.

- If the WDOSC pin has a short-circuit to GND or the resistor is disconnected, the watchdog runs with an internal oscillator and ensures a reset takes place.

- If there is no NTRIG signal and short circuit at WDOSC, the NRES switches to low after t<sub>WDOfshi</sub>. For an open circuit (no resistor) at WDOSC it switches to low after t<sub>WDOfslo</sub>.

- The Watchdog Disable bit WDD in the configuration register needs to be written twice in order to take effect. This avoids unwanted watchdog shutdowns due to data misinterpretation caused by EMI.

- If the IREF pin has a short-circuit to GND or the resistor is disconnected/shorted to VCC, the current sources run with an internal reference current which guarantees basic functionality of the application.

# 13. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                                                                                                                                                  | Symbol                 | Min.       | Тур. | Max.                    | Unit   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|------|-------------------------|--------|

| Maximum voltage on supply pin VS <sup>1)</sup>                                                                                                                              | $V_{\text{sup,Stby}}$  | -0.4       |      | +40                     | V      |

| Operating Supply Voltage (load dump) Pulse time $\leq 500 \text{ms}$ $T_a = 25^{\circ}\text{C}$ VCC output current $I_{\text{VCC}} \leq 50 \text{mA}^{1}$                   | $V_{\text{sup,Idump}}$ |            |      | +40                     | V      |

| Operating Supply Voltage (jump start) Pulse time ≤ 2min T <sub>a</sub> = 25°C Output current I <sub>VCC</sub> ≤ 50mA <sup>1)</sup>                                          | $V_{sup,jstart}$       |            |      | 27                      | V      |

| Voltage Levels on pins - CS1-8 - CL15 (with 10kΩ/47nF) -> DC voltage <sup>1)</sup> -> Transient voltage due to ISO7637 (coupling via 1nF)                                   |                        | -2<br>-150 |      | +40<br>+100             | V<br>V |

| Voltage Levels on pins <sup>1)</sup><br>- LIN<br>- VBATT (with 51Ω/10nF)<br>-> DC voltage                                                                                   |                        | -27        |      | +40                     | V      |

| Voltage levels on logic/low-voltage pins:<br>RXD, TXD, NRES, NTRIG, WDOSC,<br>PWMy, VDIV, NCS, SCK,<br>MOSI, MISO                                                           |                        | -0.4       |      | V <sub>VCC</sub> + 0.4V | V      |

| Voltage levels on pin VCC                                                                                                                                                   | $V_{VCC}$              | -0.4       |      | +5.5                    | V      |

| ESD according to IBEE LIN EMC Test Spec. 1.0 following IEC 61000-4-2 - Pin VS, LIN to GND - Pin CL15 (10kΩ, 47nF) to GND - Pin VBATT (10nF) to GND - Pins CSx (10nF) to GND |                        | ±6         |      |                         | kV     |