SEARAY<sup>™\*</sup> Board To Board System Connector Routing Guide

## TABLE OF CONTENTS

| I. Overview of the Connector                                                        | 3                                     |

|-------------------------------------------------------------------------------------|---------------------------------------|

| II. <u>Routing Recommendations</u>                                                  |                                       |

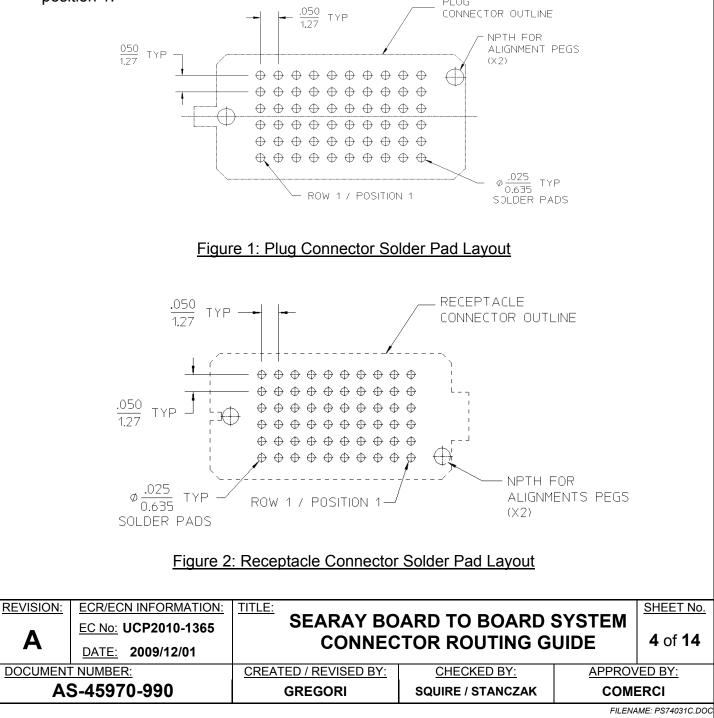

| PCB Pad Layout / Connector foot print                                               | 4                                     |

| PCB Pad Layout / Connector foot print<br>Figure 1: Plug Connector Solder Pad Layout | 4                                     |

| Figure 2: Receptacle Connector Solder Pad Layout                                    | 4                                     |

| Routing Pattern: Trace Geometry                                                     | 5                                     |

| Figure 3: 5-5-5 Trace Geometry                                                      | 5                                     |

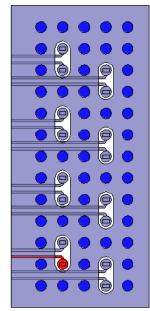

| Figure 4: Lateral Escape Routing                                                    | 6                                     |

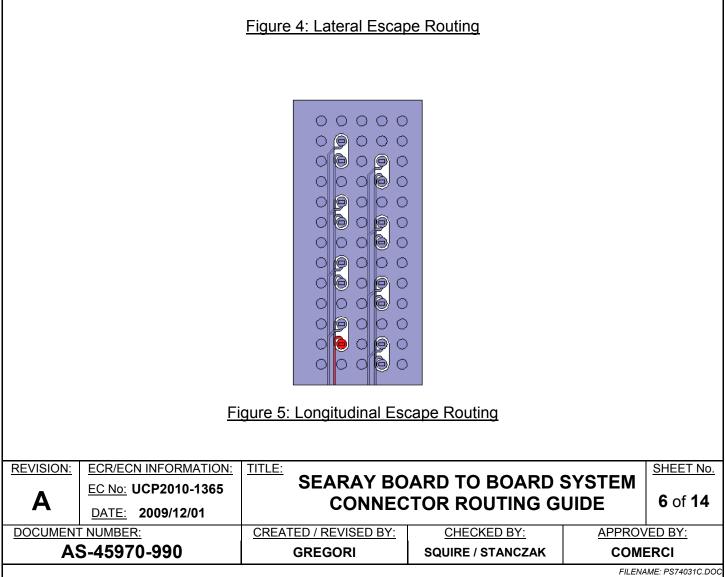

| Figure 5: Longitudinal Esacpe Routing                                               | 6                                     |

| Pair to Pair Spacing When Out of Pin Field                                          | 7                                     |

| Figure 6: Trace Expansion Out of Pin Field                                          | 7                                     |

| Grounding Patterns                                                                  | 7                                     |

| Figure 7: Grounding Patterns                                                        | 8                                     |

| Figure 8: Shielded Grounding Patterns                                               | 8                                     |

| Pad and Anti-Pad Guidelines                                                         |                                       |

| Figure 9: Trace Routing                                                             |                                       |

| Via Construction                                                                    | 10                                    |

|                                                                                     | 10                                    |

| Differential Trace to Signal Pad Attachment                                         | 10                                    |

| Figure 11: Flag Escape Detail Longitudinal Escape                                   |                                       |

| Intra-pair and Inter-pair skew control                                              | 11                                    |

| Figure 12: Flag Escape Detail                                                       | · · · · · · · · · · · · · · · · · · · |

| Depth of Rows                                                                       | 11                                    |

| Layer Allocation                                                                    |                                       |

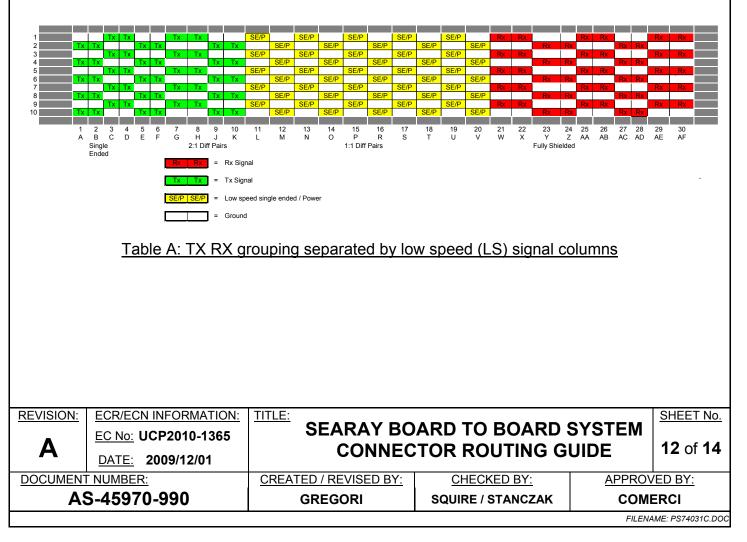

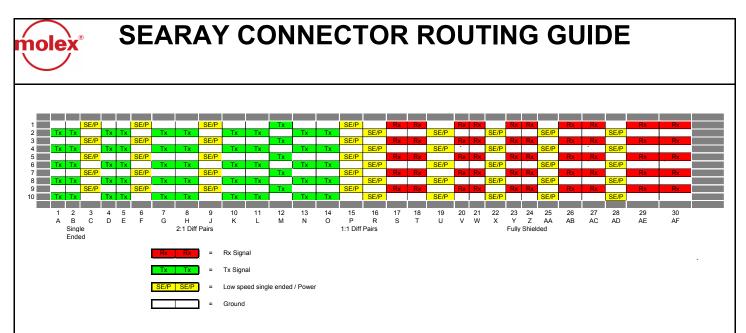

| III. Crosstalk Tx and Rx Arrangement                                                | 12                                    |

| Table A: TX RX grouping separated by low speed (LS) signal columns                  | 12                                    |

| Table B: TX RX pairs separated by low speed (LS) signal columns                     |                                       |

|                                                                                     |                                       |

| Back Drilling<br>Figure 13: Back Drill Specification                                | 13                                    |

| Keep Out Area                                                                       |                                       |

|                                                                                     |                                       |

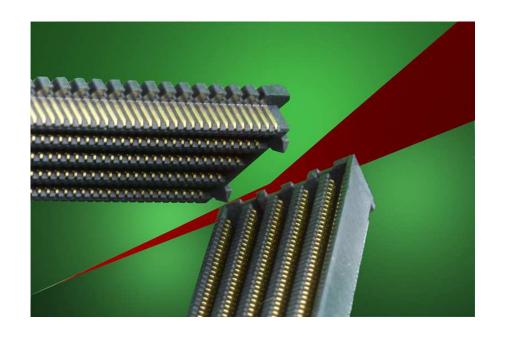

## I. OVERVIEW OF THE CONNECTOR

The SEARAY connector system provides data rates up to 15 Gbps and superior signal density up to 67 differential pairs per inch. The SEARAY open pin field provides designers with flexibility in signal allocation for high-speed differential pairs, low speed single ended lines and power.

SEARAY's recessed housing protects terminals from stubbing during mating and the shrouded housing with guide pins helps align mezzanine cards in blind mating situations. In processing, SEARAY benefits from Solder Charge<sup>™</sup> SMT Technology with many advantages over BGA such as increased PCB retention, easier x-ray inspection and more reliable interfacing to the PCB with a riveted terminal ensuring contact with the solder pad.

The SEARAY connector system is designed for mezzanine architectures to meet the growing demands of next-generation telecommunication and data networking equipment manufacturers. The SEARAY connector system is offered in a large variety of options with circuit sizes ranging from 40 to 500 circuits and stack heights covering the gamete of 7 to 15mm.

## II. ROUTING RECOMMENDATIONS

## PCB Pad Layout / Connector Footprint

The SEARAY connector system is designed for .025" (0.635mm) diameter solder pads. A simple .050" x .050" (1.27mm x 1.27mm) solder pad grid is shown in Figure 1. The solder pad layout is identical between the plug and receptacle with the exception of the non-plated thru holes (NPTH) for connector alignment pegs relative to row 1 / position 1.

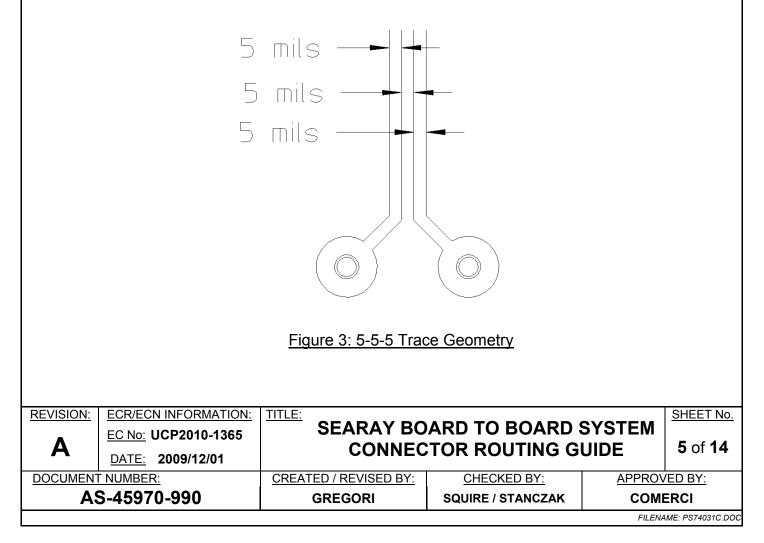

### **Routing Pattern: Trace Geometry**

For high speed applications it is recommended that the differential signals be routed through the via pin field as tightly coupled differential pairs in order to minimize the effects of crosstalk. The differential impedance of the pair should be tuned to be as close to the nominal system impedance as possible (typically 100 ohms). Other parameters such as common mode impedance, fabrication consistency, attenuation, and routing density may also influence the choice of trace dimensions for a particular application.

For the SEARAY connector the allowable trace geometry is bounded by the minimum dimensions constant with required impedance and fabrication capabilities and by the maximum allowable by the SEARAY pin field grid dimensions 050" x .050" (1.27mm x 1.27mm) of the solder pad grid. A 5-5-5 mil trace geometry is recommended within the via pin field. Other traces geometries may be used, but is recommended that the total differential pair width be restricted to 15mils or less. Outside the via pin field the traces may be expanded as a loosely coupled differential pair (for example 7-14-7) or uncoupled single ended traces as required by the application. It is recommended that the pairs be edge coupled and aligned parallel to the long axis of the connector. While broad side coupling may be used, it is likely to require additional skew compensation.

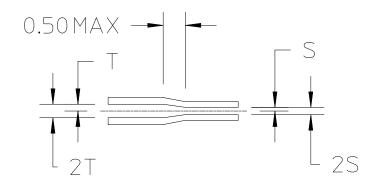

### Pair To Pair Spacing When Out of Pin Field

Outside of the pin field it is recommended that the pair to pair spacing be as wide as possible to minimize the pair to pair cross talk. Transitions from the pin field tracing spacing to the general board trace structure should be performed smoothly and symmetrically.

Figure 6: Trace Expansion Out of Pin Field

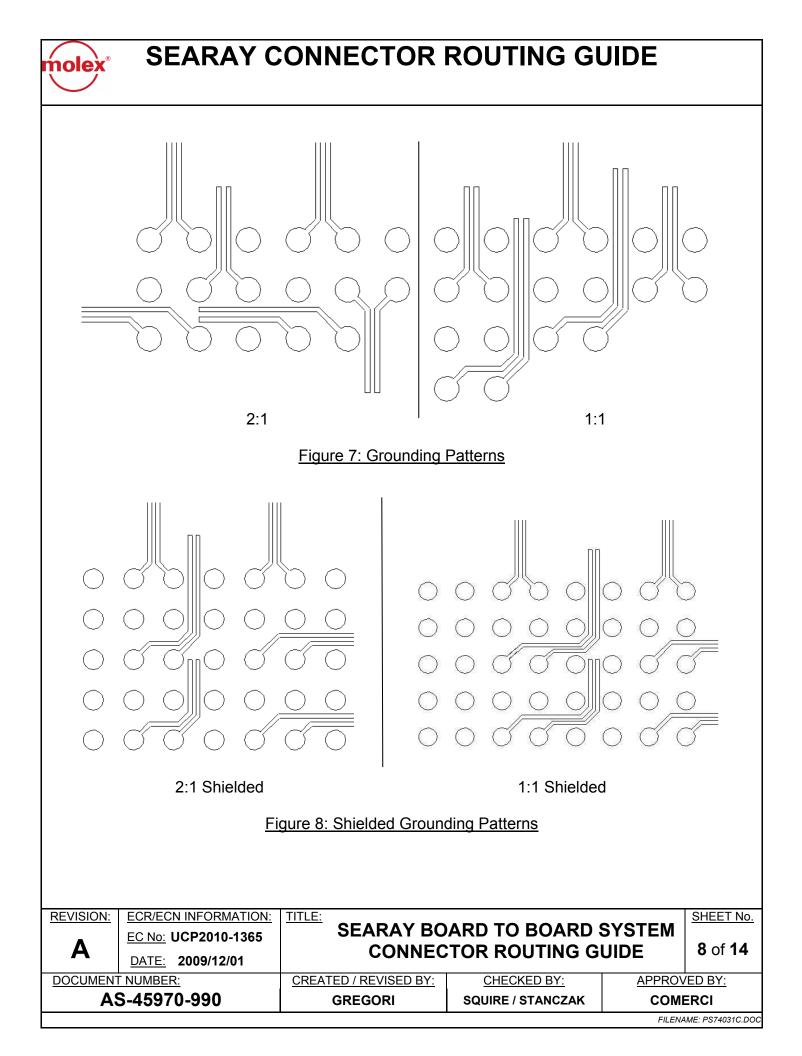

#### **Grounding Patterns**

The SEARAY connector being an open pin field connector allows various arrangements of signal pins and ground pins to be defined. For maximum density a staggered 2:1 signal / ground arrangement may be used. It should be noted that this arrangement may lead to higher crosstalk than other arrangements.

A staggered 1:1 signal / ground arrangement may be used to give improved crosstalk isolation relative to the 2:1 signal / ground arrangement.

For maximum crosstalk isolation a fully shielded ground pattern can be used at the expense of signal density.

| <b>REVISION:</b> | ECR/ECN INFORMATION:                           | TITLE:                                                  |                                                    | _       | SHEET No. |

|------------------|------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|---------|-----------|

| Α                | <u>EC No:</u> UCP2010-1365<br>DATE: 2009/12/01 | SEARAY BOARD TO BOARD SYSTEM<br>CONNECTOR ROUTING GUIDE |                                                    |         | 7 of 14   |

| DOCUMENT NUMBER: |                                                | CREATED / REVISED BY:                                   | ED / REVISED BY: <u>CHECKED BY:</u> <u>APPROVE</u> |         | /ED BY:   |

| AS-45970-990     |                                                | GREGORI                                                 | SQUIRE / STANCZAK                                  | COMERCI |           |

|                  |                                                |                                                         |                                                    |         |           |

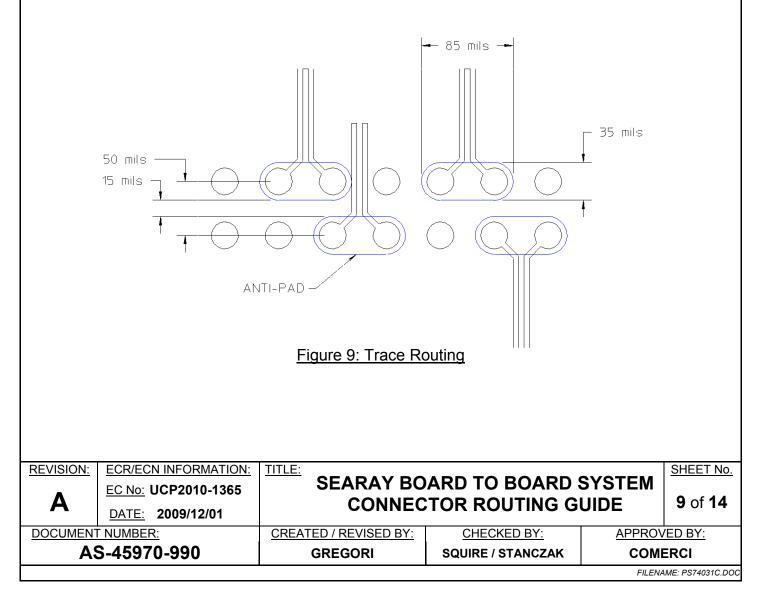

#### Pad and Anti-pad guidelines

For High-speed signaling applications Pad and anti-pad construction are of critical importance. For correct attachment of the SEARAY connector the top layer SMT pads are required to be .025" (0.635mm) in diameter. The internal pads should be small to minimize capacitance. The inner layer pads and annular ring with outer diameter of 18 mils is recommended. The number of pads on inner layers should be the minimal required to maintain good adhesion of the via to the PCB in order to minimize the capacitance for the via structure.

Anti-pads are recommended to be 35 mils in radius when used with 15mil (total width) differential pairs (for example 5-5-5 or 4-6-4 traces). The anti-pad should be large to allow for minimum deviation of impedance from the nominal value. However, it should not be so large that that the anti-pad cavity can extend over the trace causing impedance discontinuities and a reduction in cross talk isolation. Anti-pads may align with the outer edges of the differential traces, but should not extend over the differential pairs in order maintain control of crosstalk and impedance. Smaller than recommended anti-pads may be used but a negative influence on via impedance is expected.

## Via construction

For the SEARAY connector via in pad construction is recommended to minimize any impedance discontinuity at the via / pad transition. Dog bone via structures may be used but with an expected reduction in electrical performance.

As a surface mounted technology (SMT), the SEARAY connector does not constrain the choice of via size due to compliant pin or press fit requirements. A 10 mil (drill) via barrel was used in the SI analysis of the SEARAY via structure and this size or smaller is recommended depending on the host board thickness and allowable aspect ratio.

## Figure 10: Via Construction Used in SI Analysis

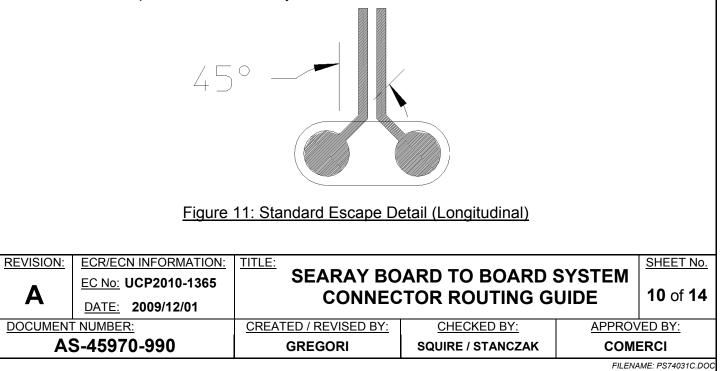

## **Differential Trace to Signal Pad Attachment**

For the SEARAY connector a 45° flag style launch (Figure 4) is preferred for high speed applications. The 45° flag provides a reduced capacitance and reduced differential impedance discontinuity.

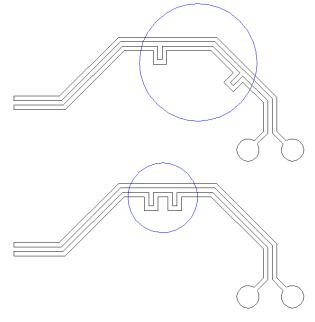

#### Intra-pair and Inter-pair skew control

Routing orthogonally to the differential pair directly though the pin field in a lateral escape configuration is recommended to minimize the intra-pair skew. A longitudinal escape may be used but some form of skew compensation may be required. It is recommended that the differential pairs be routed through opposite side of the connector on the top and bottom boards to minimize inter-pair skew. If this is impractical then skew compensation should be performed outside the pin field to achieve an acceptable level of inter-pair skew control. If the traces are routed longitudinally intrapair skew may be compensated by routing the traces on the top and bottom board in opposite directions so that the traces are essentially mirror image. It is recommended that any skew compensation applied to the traces be distributed along the traces outside of the pin field region rather than performed at a single point along the trace.

Figure 12: Flag Escape Detail

#### Depth of rows

It is recommended that the differential traces be routed to minimize the depth of rows through which the signal traces must pass. This means that ideally the signals be routed with center symmetry along the longitudinal axis of the connector so that cross talk and impedance variations observed by the signal traces are minimized.

| REVISION:              | ECR/ECN INFORMATION:<br>EC No: UCP2010-1365<br>DATE: 2009/12/01 |                       | ARD TO BOARD S<br>TOR ROUTING G |              | <u>SHEET No.</u><br><b>11</b> of <b>14</b> |

|------------------------|-----------------------------------------------------------------|-----------------------|---------------------------------|--------------|--------------------------------------------|

| DOCUMENT NUMBER:       |                                                                 | CREATED / REVISED BY: | CHECKED BY:                     | APPROVED BY: |                                            |

| AS-45970-990           |                                                                 | GREGORI               | SQUIRE / STANCZAK               | COMERCI      |                                            |

| FILENAME: PS74031C.DOC |                                                                 |                       |                                 |              |                                            |

#### Layer allocation

To avoid stub effects it is recommended that high speed differential pairs be routed on the bottom layers of the PCB board. Use of embedded micro-strip routing on the top layer and strip-line traces with micro-vias on the upper layers can allow high speed routing on the upper layers with minimum stub effects. Middle layers should be used with caution when routing high speed lines. If middle layer must be used then back drilling is highly recommended to optimize impedance and minimize crosstalk.

## III. CROSSTALK TX AND RX ARRANGEMENT

Cross talk is strongly influenced by the rise time of the input signal. High-speed signals can show significant increase in cross talk relative to lower speed signals in the same channel. For this reason careful consideration of signal arrangement should be made. It is recommended that Tx and Rx signals be grouped together in separate blocks to minimize cross talk. In addition high-speed signals can be separated by power return and low speed signaling to further increase crosstalk isolation. It is also recommended that Tx and Rx signals be routed out on different layers to increase cross talk isolation between traces

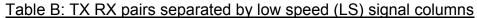

#### **Back drilling**

For high speed signals, it is highly recommended for any via that extends a significant number of layers below the active signal layer that the excess via stub below the active signal layer is removed by back drilling. In simulation back drilling has shown significant improvement in via impedance and crosstalk. Routing on bottom layer with minimal stub and routing on top layers with control depth via reduces the need for back drilling, but for signals routing on middle layers back drilling is strongly recommended. Since the Searay connector does not require any control of drilling depth to accommodate a press fit or compliant pin, back drilling depth is determined only by the depth of the active layer and the accuracy and resolution of the drilling process.

For a 10mils drill size it is recommended that a 12mils ~14mils drill size be used for back drilling.

#### Keep out area

Recommended clearance or keep out area allowed for reworking of this component is .200" (5.0mm) all the way around the perimeter of the part. Contact Molex if further assistance is required.

The required distance between the connector and an impedance discontinuity is highly dependent on the rise time and spectral content of the data transmitted. For a 6.25GHz NRZ differential signal it is recommended that a keep out distance of greater than 12.5mm be kept between the connector and any impedance dicontinuity (based on the 1/4 wavelength distance of the clock frequecy in the PCB dielectric).

| FILENAME: PS74031C.DOC |                         |                       |                   |               |                        |

|------------------------|-------------------------|-----------------------|-------------------|---------------|------------------------|

| AS                     | S-45970-990             | GREGORI               | SQUIRE / STANCZAK | СОМ           | ERCI                   |

| DOCUMENT               | <u> NUMBER:</u>         | CREATED / REVISED BY: | CHECKED BY:       | <u>APPROV</u> | <u>/ED BY:</u>         |

| Α                      | <u>DATE:</u> 2009/12/01 | CONNEC                | TOR ROUTING G     | UIDE          | <b>14</b> of <b>14</b> |

|                        | EC No: UCP2010-1365     |                       | ARD TO BOARD      |               |                        |

| <b>REVISION:</b>       | ECR/ECN INFORMATION:    | TITLE:                |                   |               | SHEET No.              |