# 2.5Gbps Ethernet Media Access Controller IP Core

User's Guide

## Introduction

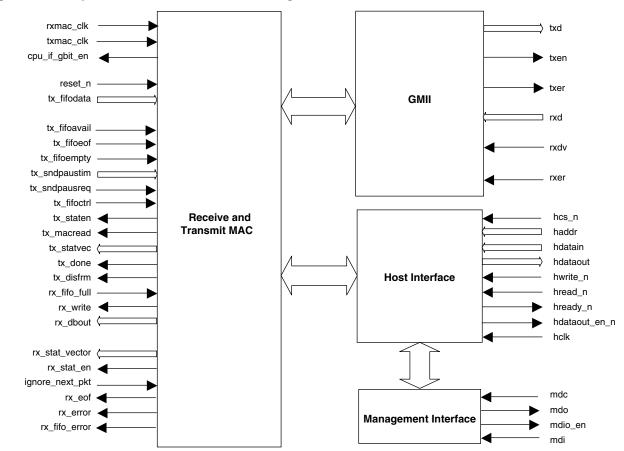

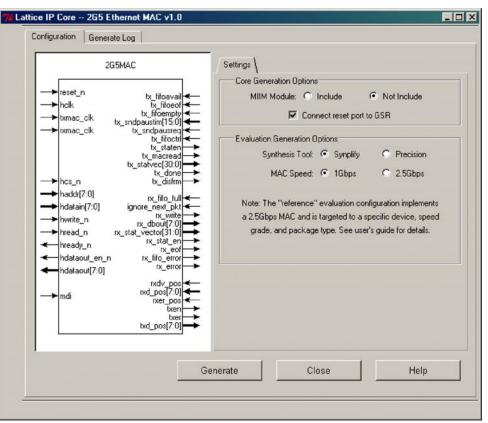

This document provides technical information about the Lattice 2.5Gbps Ethernet Media Access Controller (2.5Gbps MAC) IP core shown in Figure 1.

The 2.5Gbps MAC IP core comes with the following documentation and files:

- Protected netlist/database

- Behavioral RTL simulation model

- Source files for instantiating and evaluating the core

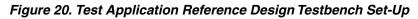

The 2.5Gbps MAC IP core evaluation package includes a reference design that is used to instantiate, simulate, map, place and route the core in an example working design. Additional details on this reference design are given in an appendix of this document.

The 2.5Gbps MAC IP core supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited period of time (approximately four hours) without requiring the purchase of an IP license. It may also be used to evaluate the core in hardware in user-defined designs. Details for using the hardware evaluation capability are described in the Hardware Evaluation section of this document.

## Features

- Compliant to IEEE 802.3z standard

- Generic 8-bit host interface

- 8-bit wide internal data path

- · Generic transmit and receive FIFO interface

- Full-duplex operation

- · Transmit and receive statistics vector

- Programmable Inter Packet Gap (IPG)

- Multicast address filtering

- Supports

- Full-duplex control using PAUSE frames

- VLAN tagged frames

- Automatic re-transmission on collision

- Automatic padding of short frames

- Multicast and Broadcast frames

- Optional FCS transmission and reception

- Optional MII management interface module

- Supports jumbo frames up to 9600 bytes

## **General Description**

The 2.5Gbps MAC core can support data rates of 1Gbps or 2.5Gbps in LatticeSC<sup>™</sup> and LatticeSCM<sup>™</sup> devices. The 2.5Gbps MAC transmits and receives data between a host processor and an Ethernet network. The main function of the Ethernet MAC is to ensure that the Media Access rules specified in the 802.3 IEEE standards are met while transmitting and receiving Ethernet frames. Figure 2 shows the frame format of Ethernet packets transmitted and received on the Ethernet network using the 2.5Gbps MAC.

The data received from the GMII interface is first buffered until sufficient data is available to be processed by the Receive MAC (Rx MAC). The Preamble and the Start of Frame Delimiter (SFD) information are then extracted from

the incoming frame to determine the start of a valid frame. The Receive MAC checks the address of the received packet and validates whether the frame can be received before transferring it into the FIFO. Only valid frames are transferred into the FIFO. The 2.5Gbps MAC however always calculates CRC to check whether the frame was received error-free or not.

When transmitting a frame the DA, SA, L/T, and DATA fields are derived from higher layers. This frame is sent via the FIFO interface to the Transmit MAC (Tx MAC) where it is encapsulated into an Un-tagged Ethernet frame. This frame is not sent over the network until the network has been idle for a minimum of Inter Packet Gap (IPG) time. The Frame encapsulation consists of adding the Preamble bits, the Start of Frame Data (SFD) bits and the CRC check sum to the end of the frame (FCS). If padding is not disabled, all short frames are padded with hexadecimal 55.

# Core Block Diagram

Figure 1. 2.5Gbps Ethernet MAC Core Block Diagram

Figure 2. Un-Tagged Ethernet Frame Format

| PREAMBLE | SFD    | DESTINATION<br>ADDRESS | SOURCE<br>ADDRESS | LENGTH/<br>TYPE | DATA/PAD      | FRAME CHECK<br>SEQUENCE |

|----------|--------|------------------------|-------------------|-----------------|---------------|-------------------------|

| 7 bytes  | 1 byte | 6 bytes                | 6 bytes           | 2 bytes         | 46-1500 bytes | 4 bytes                 |

A Tagged frame includes a 4-byte VLAN Tag field, which is located between the Source Address field and the Length/Type field. The VLAN Tag field includes the VLAN Identifier and other control information needed when operating with Virtual Bridged LANs as described in IEEE P802.1Q.

# System Block Diagrams

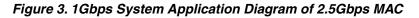

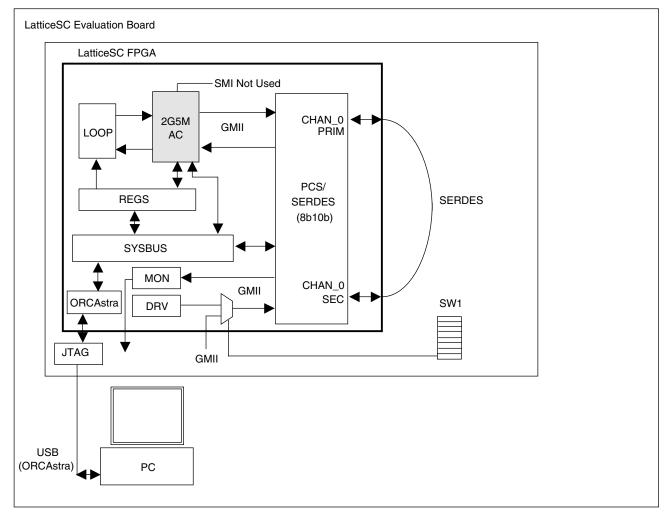

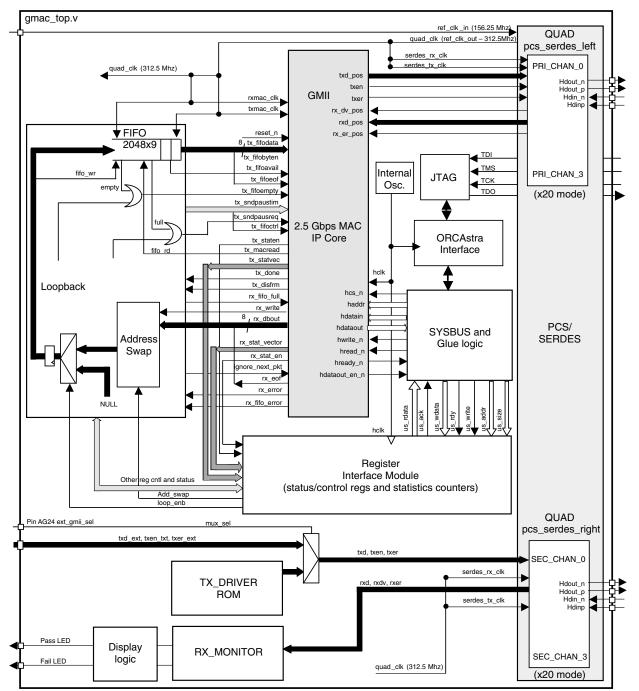

Figure 3 shows a FPGA system level block diagram of how the 2.5Gbps MAC core is instantiated and used in a 1Gbps application with a GMII interface. Note that the MAC core needs a certain amount of support logic like PLLs, I/O buffers and I/O flip flops to meet the IEEE 802.3 I/O specifications.

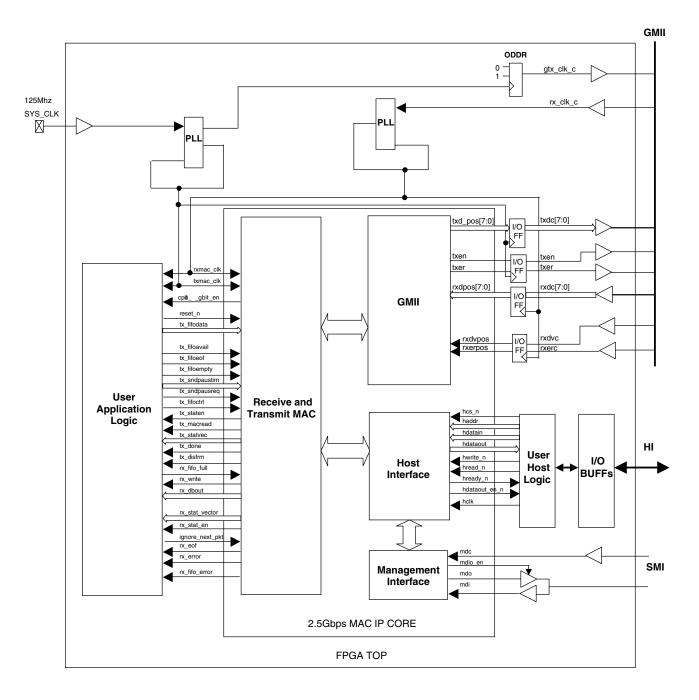

Figure 4 shows a FPGA system level block diagram of how the 2.5Gbps MAC core is instantiated and used in a 1Gbps or 2.5Gbps application with a SERDES interface.

Figure 4. 2.5Gbps System Application Diagram of 2.5Gbps MAC

# **Signal Descriptions**

## Table 1. 2.5Gbps MAC Input and Output Signals

| Port Name                       | Туре       | Active<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------------------------|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clocks, Reset and C             | Other      | I               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

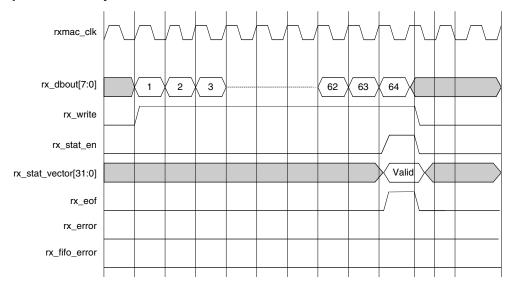

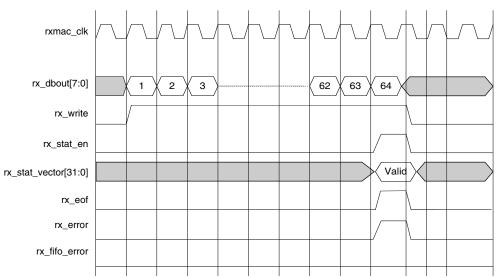

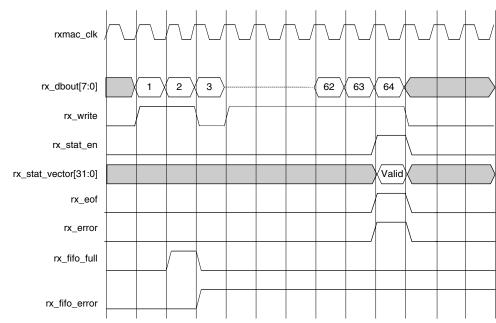

| rxmac_clk                       | Input      | N/A             | <b>Receive MAC Application I/F Clock</b> . This clock is used by the client application and MAC, all outputs driven by the Rx MAC on the client side are synchronous to this clock. This clock's frequency is 125 MHz or 312.5 MHz, depending on the rate of operation: 1Gbps or 2.5Gbps. All Rx MAC bytes are aligned with this clock. This clock is derived from the system GMII rx_clk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| txmac_clk                       | Input      | N/A             | <b>Transmit MAC Application I/F Clock</b> . This clock is used by the client application and MAC, all inputs to the Tx MAC on the client side should be synchronous to this clock. This clock's frequency is 125 MHz or 312.5 MHz, depending on the rate of operation: 1 Gbps or 2.5 Gbps. All Tx MAC bytes are aligned with this clock. This clock is derived from the system sys_clk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

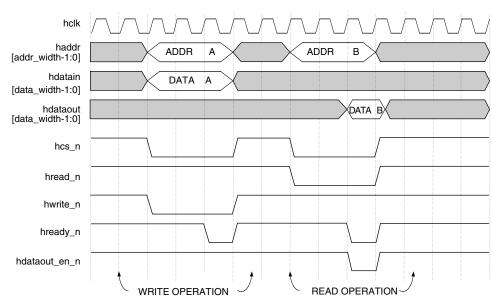

| hclk                            | Input      | N/A             | Host Clock. This is the Host Bus clock, and is used to clock the Host Bus interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

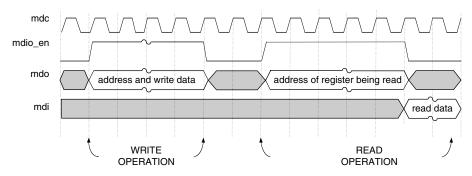

| mdc                             | Input      | N/A             | Management Data Clock. This clock is used only when the Management Interface module is implemented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| reset_n                         | Input      | Low             | <b>Reset</b> . This is an active low signal that resets the internal registers and internal logic. When activated, the I/O signals are driven to their inactive levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Host Interface                  |            |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| hcs_n                           | Input      | Low             | <b>Chip Select</b> . This is an active low signal used to select the core for register read/write operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| haddr[7:0]                      | Input      | N/A             | Address. This selects one of the internal core registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| hdatain[7:0]                    | Input      | N/A             | Data Bus Input. The CPU writes to the internal registers through the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| hwrite_n                        | Input      | Low             | Host Write. This active low signal is used to write data to the selected register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| hread_n                         | Input      | Low             | Host Read. This active low signal is used to read data from the selected register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| hready_n                        | Output     | Low             | <b>Ready</b> . This is an active low signal used to indicate the end of transfer. For write operations, hready_n is asserted after data is accepted (written). For read operations hready_n is asserted after data on the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of the hdataout bus is ready to be driven out of thdataout bus is ready to be driven out of t |  |

| hdataout_en_n                   | Output     | Low             | <b>Data Out Enable</b> . This signal is driven low whenever the 2.5Gbps MAC outputs valid data onto the hdataout bus. This signal can be used to build a bi-directional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| hdataout[7:0]                   | Output     | N/A             | Data Bus Output. The CPU reads the internal registers through the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Transmit MAC Appl               | ication In | terface         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

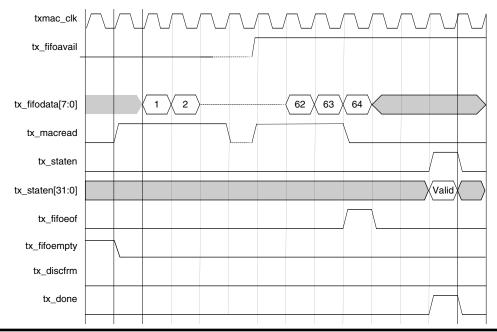

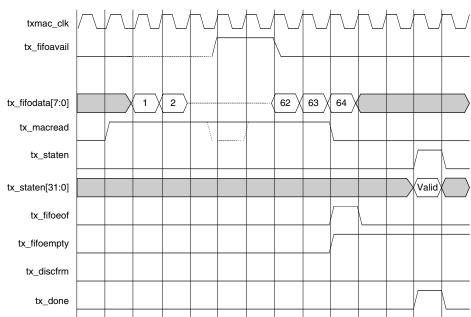

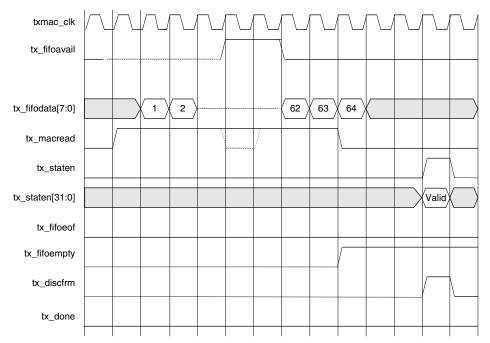

| <pre>tx_fifodata[7:0]</pre>     | Input      | N/A             | Transmit FIFO Read Data Bus. The data from the FIFO is presented on this bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| tx_fifoavail                    | Input      | High            | <b>Transmit FIFO Data Available</b> . When asserted, this indicates that the Tx FIFO has data ready for transmission on the GMII interface. Once this signal is asserted by the client, a short delay later the frame will be transmitted. Therefore, the client needs to use an appropriate threshold on the client FIFO to indicate that a frame is ready to be sent and use that threshold as the tx_fifo_avail signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| tx_fifoeof                      | Input      | High            | <b>Transmit FIFO End of Frame</b> . This signal is asserted along with the last byte of frame data indicating the end of the frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| tx_fifoempty                    | Input      | High            | <b>Transmit FIFO Empty</b> . This indicates that the Tx FIFO is empty. When this signal is asserted and the 2.5Gbps MAC is reading the FIFO, the under-run condition is transferred to the network through the txer signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| <pre>tx_sndpaustim[15 :0]</pre> | Input      | N/A             | <b>PAUSE Frame Timer</b> . This indicates the PAUSE time value that should be sent in the PAUSE frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| tx_sndpausreq                   | Input      | High            | <b>PAUSE Frame Request</b> . When asserted, the 2.5Gbps MAC transmits a PAUSE frame. This is also the qualifying signal for the tx_sndpausetim bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| tx_fifoctrl                     | Input      | N/A             | <b>FIFO Control Frame</b> . This signal indicates whether the current frame in the Tx FIFO is a control frame or a data frame. It is qualified by the $tx_avail$ signal. The following values apply: 1 = Control frame 0 = Normal frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Port Name        | Туре       | Active<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| tx_staten        | Output     | High            | <b>Transmit Statistics Vector Enable</b> . When asserted, the contents of the statistics vector bus tx_statvec are valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| tx_macread       | Output     | High            | <b>Transmit FIFO Read</b> . This is the 2.5Gbps MAC Transmit FIFO read request,<br>asserted by the 2.5Gbps MAC when it intends to read the client FIFO. The MAC core<br>will first assert the tx_macread signal if the client FIFO is Not Empty (i.e.,<br>tx_fifoempty = 0, after which the tx_macread may deassert, based on MAC pro-<br>cessing, or re-assert, based on MAC processing and if tx_fifoempty is still 0). The<br>tx_macread signal should be tied to the client FIFO read pin, and the FIFO empty<br>pin should be tied to the tx_fifoempty of the MAC core.                                                                                                                                                                                      |  |

| tx_statvec[30:0] | Output     | N/A             | Transmit Statistics Vector. This includes useful information about the frame that<br>was just transmitted. The corresponding bit locations of this bus are defined as fol-<br>lows:<br>tx_statvec[0] - UNICAST frame<br>tx_statvec[1] - Multicast frame<br>tx_statvec[2] - BROACAST frame<br>tx_statvec[3] - Bad FCS frame<br>tx_statvec[3] - Bad FCS frame<br>tx_statvec[4] - JUMBO frame<br>tx_statvec[5] - FIFO under-run<br>tx_statvec[6] - PAUSE frame<br>tx_statvec[6] - PAUSE frame<br>tx_statvec[21:8] - Number of bytes in the transmitted frame<br>tx_statvec[22] - Deferred transmission<br>tx_statvec[23] - Excessive deferred transmission tx_statvec[24:26] - RSVD<br>tx_statvec[30] - FCS generation is disabled and a short frame was transmitted |  |

| tx_done          | Output     | High            | <b>Transmit Done</b> . This signal is asserted for one clock cycle after transmitting a fram f no errors were present in transmission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| tx_discfrm       | Output     | High            | <b>Discard Frame</b> . This signal is asserted at the end of a frame transmit process if the 2.5Gbps MAC detected an error. The possible conditions are: A FIFO under-run The user application normally moves the pointer to the next frame in these conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Management Inter | face Signa | ls              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| mdi              | Input      | High            | Management Data Input. Used to transfer information from the PHY to the management module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| mdo              | Output     | High            | Management Data Output. Used to transmit information from the management module to the PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| mdio_en          | Output     | High            | <b>Management Data Out Enable</b> . Asserted whenever mdo is valid. This may be used to implement a bi-directional signal for mdi and mdo.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| GMII Signals     |            |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

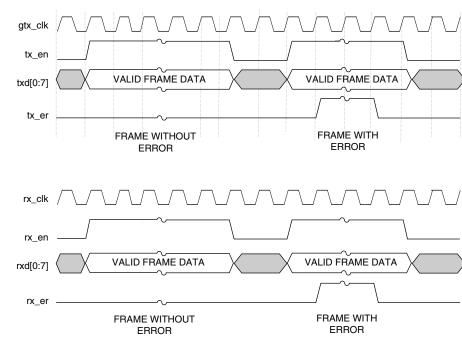

| txd_pos[7:0]     | Output     | High            | <b>txd_pos[7:0] - Transmit Data Sent to the PHY</b> . These are the GMII transmit data signals (txd[7:0]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| txen             | Output     | High            | <b>Transmit Enable</b> . Asserted by the 2.5Gbps MAC to indicate the txd bus contains valid frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| txer             | Output     | High            | <b>Transmit Error</b> . Asserted when the 2.5Gbps MAC generates a coding error on the byte currently being transferred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| rxdv_pos         | Input      | High            | Receive Data Valid. GMII rxdv signal. This signal indicates receive data is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| rxd_pos[7:0]     | Input      | N/A             | Receive Data Bus. Data is driven by the PHY on these lines, and is valid whenever rxdv is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| rxer_pos         | Input      | High            | <b>Receive Data Error</b> . This signal is asserted by the external PHY device when it detects an error during frame reception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Management Inter | face Signa | ls              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| rx_fifo_full     | Input      | High            | <b>Receive FIFO Full</b> . This signal indicates the Rx FIFO is full and cannot accept any more data. This is an error condition and should never happen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| rx_write         | Output     | High            | <b>Receive FIFO Write</b> . This signal is asserted by the 2.5Gbps MAC core to request a FIFO write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

## Table 1. 2.5Gbps MAC Input and Output Signals (Continued)

| Port Name       | Туре   | Active<br>State                                                                                                                                                                                                                              | Description                                                                                                                                                                                                              |  |

|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rx_dbout[7:0]   | Output | N/A                                                                                                                                                                                                                                          | <b>Receive FIFO Data Output</b> . This bus contains the data that is to be written into the Receive FIFO.                                                                                                                |  |

|                 |        | <b>Receive Statistics Vector</b> . This bus indicates the events encountered during frame reception. This bus is qualified by the rx_stat_en signal. The definition of each signal is explained in the Receive MAC section of this document. |                                                                                                                                                                                                                          |  |

| rx_stat_en      | Output | High                                                                                                                                                                                                                                         | <b>Receive Statistics Vector Enable</b> . When asserted, this indicates that the contents of the rx_stat_vector bus is valid.                                                                                            |  |

| ignore_next_pkt | Input  | High                                                                                                                                                                                                                                         | <b>Ignore Next Packet</b> . This signal is asserted by the host to prevent a Receive FIFO Full condition. The Receive MAC continues dropping packets as long as this signal is asserted. This is an asynchronous signal. |  |

| rx_eof          | Output | High                                                                                                                                                                                                                                         | <b>End Of Frame</b> . Indicates all the data for the current packet has passed on to the FIFO.                                                                                                                           |  |

| rx_error        | Output | High                                                                                                                                                                                                                                         | <b>Receive Packet Error</b> . When asserted, this signal indicates the packet contains error(s). This signal is qualified with the rx_eof signal.                                                                        |  |

| rx_fifo_error   | Output | High                                                                                                                                                                                                                                         | <b>Receive FIFO Error</b> . This signal is asserted when the rx_fifo_full signal was detected asserted during a FIFO write. It is qualified by rx_eof.                                                                   |  |

| Table 1. 2.5Gbps MAC Input and Output Signals ( | Continued) |

|-------------------------------------------------|------------|

|-------------------------------------------------|------------|

# **Parameter Descriptions**