# Application Manual

Real Time Clock Module

**RX-8571NB**

**EPSON TOYOCOM CORPORATION**

#### **NOTICE**

- The material is subject to change without notice.

- Any part of this material may not be reproduced or duplicated in any form or any means without the written permission of Epson Toyocom.

- The information, applied circuit, program, usage etc., written in this material is just for reference. Epson Toyocom does not assume any liability for the occurrence of infringing any patent or copyright of a third party. This material does not authorize the licensing for any patent or intellectual copyrights.

- Any product described in this material may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export licence from the Ministry of International Trade and industry or other approval from another government agency.

- You are requested not to use the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes. You are also requested that you would not make the products available to any third party who may use the products for such prohibited purposes.

- These products are intended for general use in electronic equipment. When using them in specific applications that require extremely high reliability such as applications stated below, it is required to obtain the permission from Epson Toyocom in advance.

- / Space equipment (artificial satellites, rockets, etc) / Transportation vehicles and related (automobiles, aircraft, trains, vessels, etc) / Medical instruments to sustain life / Submarine transmitters / Power stations and related / Fire work equipment and security equipment / traffic control equipment / and others requiring equivalent reliability.

- In this manual for Epson Tyocom, product code and marking will still remain as previously identified prior to the merger. Due to the on going strategy of gradual unification of part numbers, please review product code and marking as they will change during the course of the coming months. We apologize for the inconvenience, but we will eventually have a unified part numbering system for Epson Toyocom which will be user friendly.

# Contents

| 1. Overview                                                                                                                                                                                                                                | 2      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2. Block Diagram                                                                                                                                                                                                                           | 2      |

| 3. Terminal description  3.1. Terminal connections  3.2. Pin Functions                                                                                                                                                                     | 3      |

| 4. External Dimensions / Marking Layout                                                                                                                                                                                                    | 4      |

| 5. Absolute Maximum Ratings                                                                                                                                                                                                                | 5      |

| 6. Recommended Operating Conditions                                                                                                                                                                                                        | 5      |

| 7. Frequency Characteristics                                                                                                                                                                                                               | 5      |

| 8. Electrical Characteristics  8.1. DC characteristics  8.2. AC characteristics                                                                                                                                                            | 6      |

| 9. Matters that demand special attention on use  9.1. About data when communication is stopped.  9.2. Migrating to backup, and returning.  9.3. Restrictions on Access Operations During Power-on Initialization and Recovery from Backup. | 8<br>3 |

| 10.1. Reference information                                                                                                                                                                                                                |        |

| 10.1. Reference Data                                                                                                                                                                                                                       |        |

| 11. Application notes                                                                                                                                                                                                                      | 11     |

| 12. Overview of Functions and Description of Registers                                                                                                                                                                                     | 12     |

| 12.1. Overview of Functions                                                                                                                                                                                                                |        |

| 12.2. Register table                                                                                                                                                                                                                       |        |

| 13.1. How to use                                                                                                                                                                                                                           | 15     |

| 13.1. Description of Clock & Calendar function                                                                                                                                                                                             | 15     |

| 13.2. Fixed-cycle Timer Interrupt Function                                                                                                                                                                                                 | 16     |

| 13.3. Alarm Interrupt Function                                                                                                                                                                                                             | 18     |

| 13.5. /IRQ "L" Interrupt Output When Interrupt Function Operates                                                                                                                                                                           | 22     |

| 13.6. Voltage detection function (VLF)                                                                                                                                                                                                     |        |

| 13.7. FOUT function [clock output function]                                                                                                                                                                                                | 23     |

| 13.8. Flow-chart                                                                                                                                                                                                                           | 24     |

| 13.9 Reading/Writing Data via the I <sup>2</sup> C Bus Interface                                                                                                                                                                           |        |

### LOW BACKUP CURRENT I<sup>2</sup>C-BUS -INTERFACE REAL TIME CLOCK MODULE

# **RX – 8571 NB**

• Built-in 32.768-kHz crystal resonator (with controlled frequency precision).

Interface type

Interface voltage range

Voltage when during hold (timer hold)

Low current consumption during backup

I<sup>2</sup>C-BUS

1.6 V to 5.5 V

200 nA (Typ.) / 3 V

• 32.768-kHz output function with output control : C-MOS output With Control Pin

• User register : Built in 128 bit RAM

• Real-time clock function

Clock/calendar function, auto leap year correction function, alarm interrupt function, etc.

#### 1. Overview

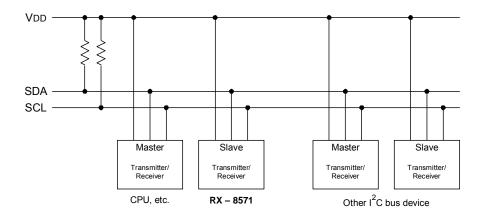

This is a real-time clock module of the I<sup>2</sup>C-BUS interface system that incorporates a 32.768 kHz crystal oscillator.

The real-time clock function incorporates not only a calendar and clock counter for the year, month, day, day of the week, hour, minute, and second, but also a time alarm, interval timer, and time update interruption, among other features.

All of these many functions are implemented in a thin, compact SOP package, which makes it suitable for various kinds of mobile telephones and other small electronic devices.

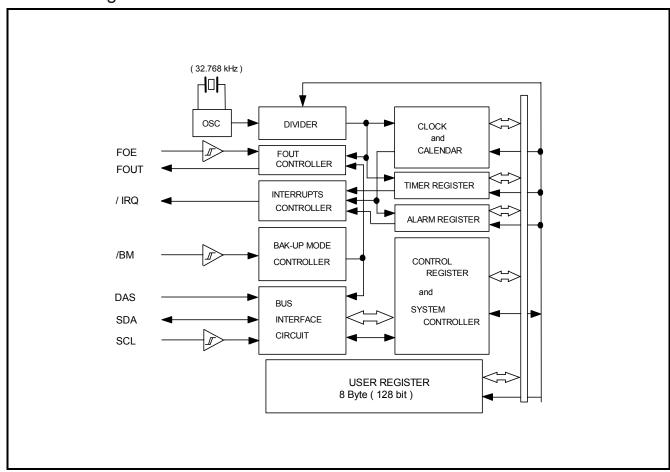

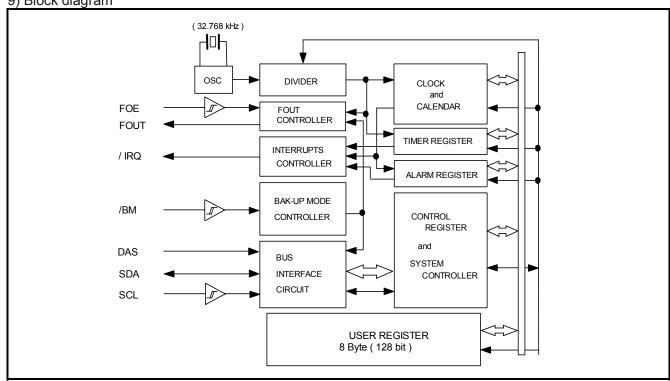

### 2. Block Diagram

# 3. Terminal description

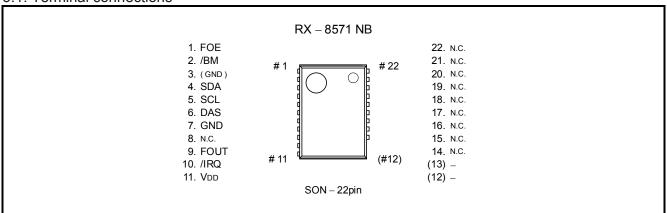

#### 3.1. Terminal connections

#### 3.2. Pin Functions

| Signal name | I/O                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                  | Fun              | ction                                                                                                             |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SDA         | Bi-<br>directional                                                                                                                                                                                                                                                    | I <sup>2</sup> C-BUS com<br>An appropria<br>be connected<br>It is able to ir                                                                                                                                                                                                                            | Addresses, data, acknowledge bits, etc. are input and output in synchronization with the I <sup>2</sup> C-BUS communication serial clock.  An appropriate pull-up resistance in accordance with the capacity of the signal cable must be connected to this terminal, which is an open drain at the time of output.  It is able to input up to 5.5V regardless of VDD applied voltage. |                  |                  |                                                                                                                   |  |  |  |  |

| SCL         | Input                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                         | The serial clock for I <sup>2</sup> C-BUS communication is input here. It is able to input up to 5.5V regardless of VDD applied voltage.                                                                                                                                                                                                                                              |                  |                  |                                                                                                                   |  |  |  |  |

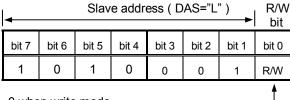

| DAS         | Input                                                                                                                                                                                                                                                                 | This pin sele                                                                                                                                                                                                                                                                                           | nput up to 5.5<br>Slave<br>01                                                                                                                                                                                                                                                                                                                                                         | dress with       |                  | hich is composed I <sup>2</sup> C-BUS.  applied voltage.                                                          |  |  |  |  |

| /BM         | /BM Input It is a backup mode change input pin. Shift to a backup mode (/BM="L"), can suppress a current consumption to a minimum. In that case, the FOUT output stops, and access becomes invalid. It is able to input up to 5.5V regardless of VDD applied voltage. |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                  |                  |                                                                                                                   |  |  |  |  |

| FOUT        | Output                                                                                                                                                                                                                                                                | The FOUT terminal is a 32.768-kHz clock output terminal provided with output control.  The FOE terminal is an input terminal for controlling the FOUT output.  The FOE terminal is able to input up to 5.5V regardless of VDD applied voltage.  FOUT terminal when stops output becomes high impedance. |                                                                                                                                                                                                                                                                                                                                                                                       |                  |                  |                                                                                                                   |  |  |  |  |

|             |                                                                                                                                                                                                                                                                       | /BM pin<br>input                                                                                                                                                                                                                                                                                        | FOE pin<br>input                                                                                                                                                                                                                                                                                                                                                                      | FSEL1<br>bit     | FSEL0<br>bit     | FOUT pin<br>output                                                                                                |  |  |  |  |

|             |                                                                                                                                                                                                                                                                       | "H"                                                                                                                                                                                                                                                                                                     | "H"                                                                                                                                                                                                                                                                                                                                                                                   | 0<br>0<br>1<br>X | 0<br>1<br>0<br>X | 32768 Hz Output (C-MOS output) *  1024 Hz Output (C-MOS output)  1 Hz Output (C-MOS output)  OFF (high impedance) |  |  |  |  |

| FOE         | Input                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                         | X                                                                                                                                                                                                                                                                                                                                                                                     | 1                | 1                | OFF (high impedance)                                                                                              |  |  |  |  |

|             |                                                                                                                                                                                                                                                                       | "L"                                                                                                                                                                                                                                                                                                     | X                                                                                                                                                                                                                                                                                                                                                                                     | Х                | X                | OFF (high impedance)                                                                                              |  |  |  |  |

|             |                                                                                                                                                                                                                                                                       | X : don't car                                                                                                                                                                                                                                                                                           | e                                                                                                                                                                                                                                                                                                                                                                                     |                  |                  |                                                                                                                   |  |  |  |  |

| / IRQ       | Output                                                                                                                                                                                                                                                                | Output This terminal outputs interrupt signals ("L" level) for alarm interval timers, time update interruptions, and the like. This is an N-ch open-drain output terminal. It is able to Pull-up to 5.5V regardless of VDD applied voltage.                                                             |                                                                                                                                                                                                                                                                                                                                                                                       |                  |                  |                                                                                                                   |  |  |  |  |

| VDD         |                                                                                                                                                                                                                                                                       | This is a power-supply terminal for the of the main power supply.                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                       |                  |                  |                                                                                                                   |  |  |  |  |

|             | _                                                                                                                                                                                                                                                                     | 11113 13 a pov                                                                                                                                                                                                                                                                                          | io. cappij io.                                                                                                                                                                                                                                                                                                                                                                        | minar ioi        |                  | main power suppry.                                                                                                |  |  |  |  |

| GND         | _                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                  |                  | le (Ground) of the power supply.                                                                                  |  |  |  |  |

Note : Be sure to connect a bypass capacitor rated at least 0.1  $\mu F$  between VDD and GND.

#### 4. External Dimensions / Marking Layout

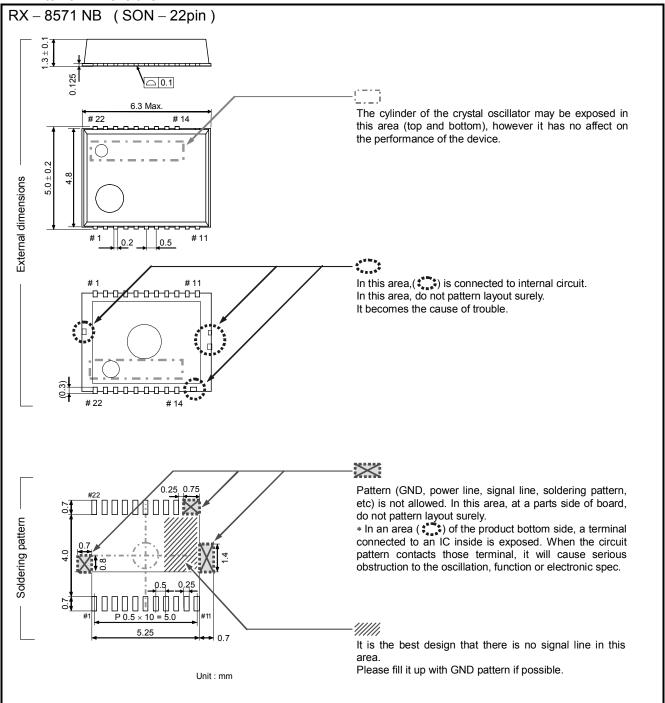

#### 4.1. External Dimensions

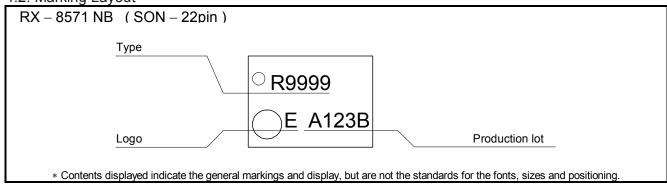

#### 4.2. Marking Layout

# 5. Absolute Maximum Ratings

GND = 0 V

| Item                | Symbol          | Condition                                 | Rating             | Unit |

|---------------------|-----------------|-------------------------------------------|--------------------|------|

| Supply voltage      | V <sub>DD</sub> | Between V <sub>DD</sub> and GND           | -0.3 to +6.5       | V    |

| Input voltage       | VIN             | DAS, SCLK, SDA, /BM,(FOE pins             | GND-0.3 to +6.5    | V    |

| Output voltage (1)  | VOUT1           | FOUT pins                                 | GND-0.3 to VDD+0.3 | V    |

| Output voltage (2)  | VOUT2           | SDA, /IRQ pin                             | GND-0.3 to +6.5    | V    |

| Storage temperature | Тѕтс            | When stored separately, without packaging | −55 to +125        | °C   |

# 6. Recommended Operating Conditions

GND = 0 V

| Item                     | Symbol | Condition                             | Min. | Тур. | Max. | Unit |

|--------------------------|--------|---------------------------------------|------|------|------|------|

| Operating supply voltage | VDD    | -                                     | 1.6  | 3.0  | 5.5  | V    |

| Clock supply voltage     | Vclk   | _                                     | VLOW | 3.0  | 5.5  | V    |

| Low voltage detection    | VLOW   | _                                     |      |      | 1.3  | V    |

| Applied voltage when OFF | VPUP   | DAS, SCLK, SDA, /BM,<br>FOE, /IRQ pin |      |      | 5.5  | V    |

| Operating temperature    | Topr   | No condensation                       | -40  | +25  | +85  | °C   |

# 7. Frequency Characteristics

GND = 0 V

| Item                                   | Symbol | Condition                                                                             |      | Rating |          | Unit                         |

|----------------------------------------|--------|---------------------------------------------------------------------------------------|------|--------|----------|------------------------------|

| Output frequency                       | fo     |                                                                                       |      | 32.768 | ( Typ. ) | kHz                          |

| Frequency/voltage characteristics      | Δf/f   | Ta = +25 °C<br>VDD = 3.0 V                                                            |      | 5 ± 23 | (*1)     | × 10 <sup>-6</sup>           |

| Frequency/voltage characteristics      | f/V    | Ta = +25 °C<br>VDD = 2.0 V ~ 5.0 V                                                    | -2   |        | +2       | imes 10 <sup>-6</sup> / V    |

| Frequency/temperatur e characteristics | Тор    | Ta = $-20$ °C to +70 °C,<br>VDD = $3.0$ V ; +25 °C reference                          | -120 |        | +10      | × 10 <sup>-6</sup>           |

| Oscillation start time                 | tsta   | Ta = +25 °C,<br>VDD = 1.6 V                                                           |      | 0.3    | 1.0      | s                            |

| Oscillation start time                 | I ISTA | Ta = $-40 ^{\circ}\text{C}$ to $+85 ^{\circ}\text{C}$<br>VDD = $1.6 ^{\circ}\text{V}$ |      |        | 3.0      | s                            |

| Aging                                  | fa     | Ta = $+25$ °C,<br>VDD = $3.0$ V; first year                                           | -5   |        | +5       | × 10 <sup>-6</sup><br>/ year |

$<sup>^{*1}</sup>$ ) This difference is 1 minute by 1 month. ( excluding offset )

# 8. Electrical Characteristics

#### 8.1. DC characteristics

8.1.1. DC characteristics (1)

\* Unless otherwise specified, GND = 0 V , VDD = 1.6 V to 5.5 V ,  $Ta = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$

|                           |                              |                                        |                                     |                       |                     |      | , ia to t | <del>5 10 105 C</del> |

|---------------------------|------------------------------|----------------------------------------|-------------------------------------|-----------------------|---------------------|------|-----------|-----------------------|

| Item                      | Symbol                       | С                                      | ondition                            |                       | Min.                | Тур. | Max.      | Unit                  |

| Current consumption (1)   | IDD1                         | /BM=FOE="L", /IR0<br>fSCL=0Hz, Ta = +2 |                                     | V <sub>DD</sub> = 3 V |                     | 200  | 400       | nA                    |

| Current consumption (2)   | IDD2                         | /BM=FOE="L"<br>/IRQ = OFF              |                                     | V <sub>DD</sub> = 5 V |                     | 220  | 450       | nA                    |

| Current consumption (3)   | IDD3                         | fSCL=0Hz<br>Ta = Ta = ±0 °C to         | +50 °C                              | V <sub>DD</sub> = 3 V |                     | 200  | 420       | i IIA                 |

| Current consumption (4)   | IDD4                         | /BM=FOE="L"                            |                                     | V <sub>DD</sub> = 5 V |                     |      | 600       | n                     |

| Current consumption (5)   | IDD5                         | fscL = 0 Hz, /IRC                      | ) = OFF                             | V <sub>DD</sub> = 3 V |                     |      | 550       | nA                    |

| Current consumption (6)   | IDD6                         | /BM=H, FOE="L"                         |                                     | V <sub>DD</sub> = 5 V |                     | 360  | 800       |                       |

| Current consumption (7)   | IDD7                         | fscL = 0 Hz, /IRC                      | ) = OFF                             | V <sub>DD</sub> = 3 V |                     | 340  | 700       | nA                    |

| Current consumption (8)   | IDD8                         | fscl = 0 Hz,<br>/IRQ = OFF, FOE =      | V <sub>DD</sub> = 5 V               |                       | 1.6                 | 3.3  |           |                       |

| Current consumption (9)   | IDD9                         | FOUT: 32.768 kHz<br>CL = 0 pF          | V <sub>DD</sub> = 3 V               |                       | 1.0                 | 2.1  | μΑ        |                       |

| Current consumption (10)  | IDD10                        | fscl = 0 Hz,<br>/IRQ = OFF, FOE =      | V <sub>DD</sub> = 5 V               |                       | 4.0                 | 7.0  |           |                       |

| Current consumption (11)  | IDD11                        | FOUT : 32.768 kHz<br>C∟ = 15 pF        | FOUT : 32.768 kHz ON,<br>CL = 15 pF |                       |                     | 2.5  | 4.0       | μΑ                    |

| High-level                | VIH1                         | FOE, DAS, /BM pir                      | 1                                   |                       | $0.8 \times V_{DD}$ |      | 6.5       | V                     |

| input voltage             | VIH2                         | SCL, SDA pin                           |                                     |                       | $0.8 \times V_{DD}$ |      | 6.5       | V                     |

| Low-level input voltage   | VIL                          | Input pin                              |                                     |                       | GND - 0.3           |      | 0.2 × VDD | V                     |

| -                         | Voн1                         |                                        | VDD=5 V, IO                         | H=−1 mA               | 4.5                 |      | 5.0       |                       |

| High-level output voltage | Voh2                         | FOUT pin                               | VDD=3 V, IO                         | н=–0.5 mA             | 2.7                 |      | 3.0       | V                     |

|                           | Vонз                         |                                        | VDD=3 V, IO                         | H=-100 μA             | 2.9                 |      | 3.0       |                       |

|                           | VOL1                         |                                        | VDD=5 V, IO                         | L=1 mA                | GND                 |      | GND+0.5   |                       |

|                           | VOL2                         | FOUT pin                               | VDD=3 V, IO                         | L=0.5 mA              | GND                 |      | GND+0.3   | V                     |

| Low-level                 | Vol3                         |                                        | VDD=3 V, IO                         | L=100 μA              | GND                 |      | GND+0.1   |                       |

| output voltage            | output voltage Vol4 /IRQ pin |                                        | VDD=5 V, IO                         | ∟=1 mA                | GND                 |      | GND+0.25  | V                     |

|                           | VOL5                         |                                        | VDD=3 V, IO                         | ∟=1 mA                | GND                 |      | GND+0.4   | V                     |

|                           | VOL6                         | SDA pin                                | VDD≥2 V, IO                         | L=3 mA                | GND                 |      | GND+0.4   | V                     |

| Input<br>leakage current  | ILK                          | Input pin, VIN = VDI                   | or GND                              |                       | -0.1                |      | 0.1       | μΑ                    |

| Output leakage current    | loz                          | Input pin, Vout = \                    | /DD or GND                          |                       | -0.1                |      | 0.1       | μΑ                    |

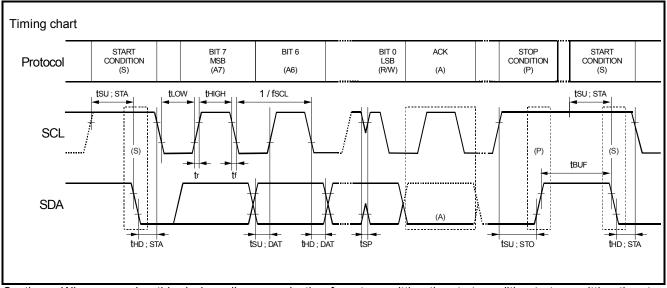

#### 8.2. AC characteristics

\* Unless otherwise specified, GND = 0 V , Ta = -40 °C to +85 °C

| Item                                                     | Symbol  |      | rd-Mode<br>100kHz) |      | Mode<br>100kHz) | Unit |  |

|----------------------------------------------------------|---------|------|--------------------|------|-----------------|------|--|

|                                                          |         | Min. | Max.               | Min. | Max.            |      |  |

| SCL clock frequency                                      | fscl    |      | 100                |      | 400             | kHz  |  |

| Start condition setup time                               | tsu;sta | 4.7  |                    | 0.6  |                 | μS   |  |

| Start condition hold time                                | thd;sta | 4.0  |                    | 0.6  |                 | μS   |  |

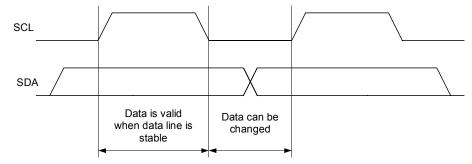

| Data setup time                                          | tsu;dat | 250  |                    | 100  |                 | ns   |  |

| Data hold time                                           | thd;dat | 0    |                    | 0    |                 | ns   |  |

| Stop condition setup time                                | tsu;sto | 4.0  |                    | 0.6  |                 | μS   |  |

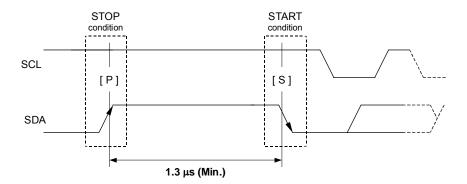

| Bus idle time between start condition and stop condition | tBUF    | 4.7  |                    | 1.3  |                 | μS   |  |

| Time when SCL = "L"                                      | tLOW    | 4.7  |                    | 1.3  |                 | μS   |  |

| Time when SCL = "H"                                      | thigh   | 4.0  |                    | 0.6  |                 | μS   |  |

| Rise time for SCL and SDA                                | tr      |      | 1.0                |      | 0.3             | μS   |  |

| Fall time for SCL and SDA                                | tf      |      | 0.3                |      | 0.3             | μS   |  |

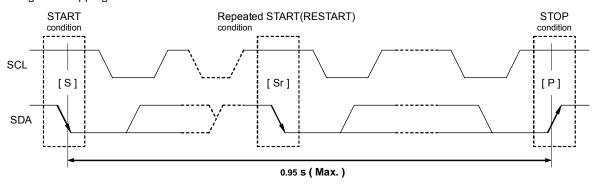

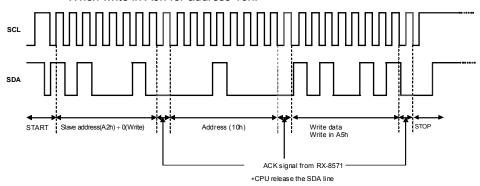

Caution: When accessing this device, all communication from transmitting the start condition to transmitting the stop condition after access **should be completed within 0.95 seconds**.

If such communication requires  ${\bf 0.95}$  seconds or longer, the  ${\rm I}^2{\rm C}$  bus interface is reset by the internal bus timeout function.

Data writing: It's necessary to input the data of 8-bit units.

During inputting the data of 8-bit units, a state of suspension occurs,

the data are not written appropriately.

# 9. Matters that demand special attention on use

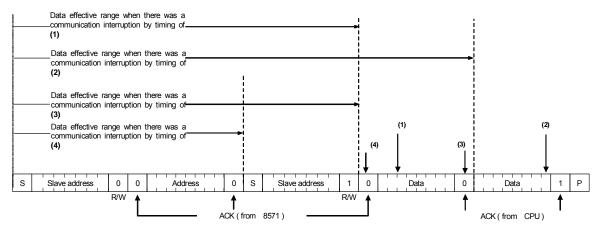

#### 9.1. About data when communication is stopped

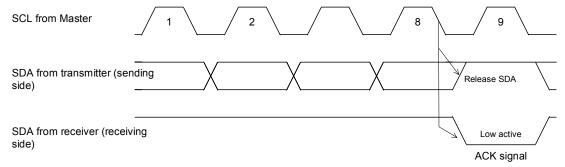

- (1) If access is interrupted with timing in transmission of acknowledge signal and timing except in checking (following drawing (1), (2)), up to data that passed and confirmed just before acknowledge signal is available.

- (2) If access is interrupted with timing in transmission of acknowledge signal and in checking (following drawing (3), (4)), up to data that passed and confirmed last acknowledge signal is available.

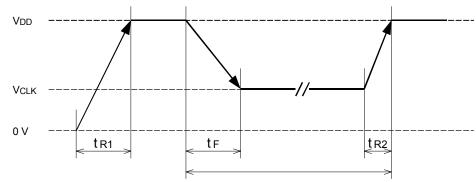

#### 9.2. Migrating to backup, and returning

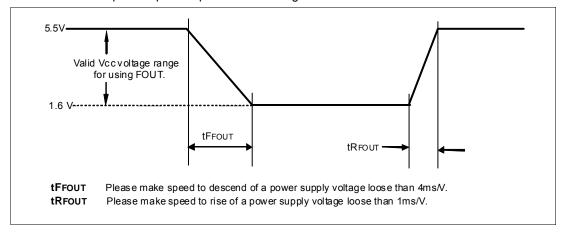

| Parameter                       | Symbol          | Min. | Тур. | Max. | Unit   |

|---------------------------------|-----------------|------|------|------|--------|

| Power drop time                 | tF              | 2    |      |      | μs / V |

| Power rise time                 | t <sub>R1</sub> | 5    |      |      | μs / V |

| Clock maintenance power-up time | tR2             | 0    |      |      | μs     |

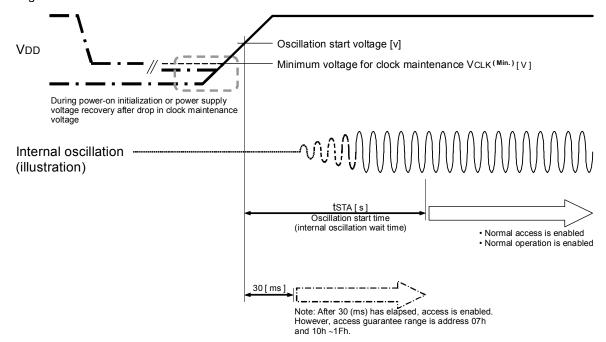

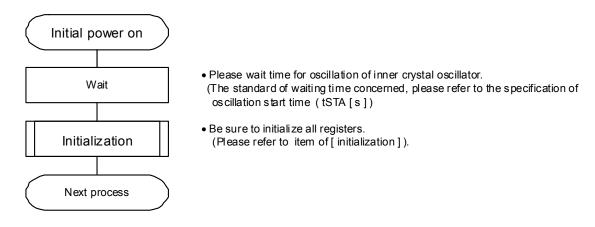

- 9.3. Restrictions on Access Operations During Power-on Initialization and Recovery from Backup

- RTC-register (Reg 00[h] ~ 0F[h]) operations are linked to the internal quartz oscillator's clock signal, so normal operation is not possible if there is no internal oscillation (= oscillation is stopped).

Therefore, we recommend that the initial setting to be set during power-on initialization or backup and restore operations (i.e., when the power supply voltage is recovered after oscillation has stopped due to a voltage drop.

- operations (i.e., when the power supply voltage is recovered after oscillation has stopped due to a voltage drop, etc.) should be "first start internal oscillation, then wait for the oscillation stabilization time (see tSTA standard) to elapse".

- Note the following caution points concerning access operations during power-on initialization or when restoring the power supply voltage from backup mode (hereafter referred to as "switching to the operating voltage").

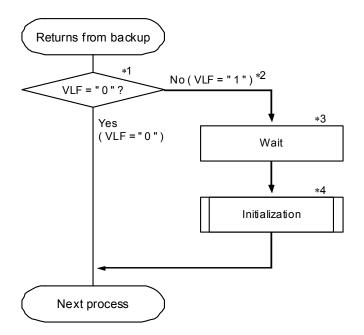

- 1) Before switching to the operating voltage, read the VLF-bit (which indicates the RTC error status).

- 2) Initialization is required when the value read from the VLF-bit is "VLF = 1 (error status)".

Before initializing in response to this VLF = "1" result, we recommend first waiting for the internal oscillation stabilization time (see the tSTA standard) to elapse.

Initialization is required when the status after reading a VLF-bit value of "1" is either of the following.

(Status 1) During power-on initialization

(Status 2) When the clock setting is invalid, such as due to a voltage drop during backup

\* Access timing during power-on initialization and when recovering the power supply voltage after a drop in the voltage used to maintain the clock

3) When the read VLF-bit value is "VLF = 0 (normal status)", access is enabled without waiting for stabilization of oscillation.

Normal operation is enabled under the following two statuses when "0" is read as the VLF-bit value.

(Status 1) When correct operation is enabled (except for settings errors while in use)

(Status 2) When data is retained normally while switching to the operating voltage from backup mode

#### 10.1. Reference information

#### 10.1. Reference Data

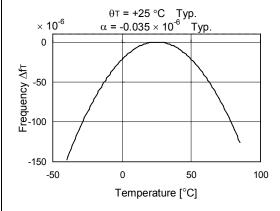

(1) Example of frequency and temperature characteristics

[ Finding the frequency stability ]

1. Frequency and temperature characteristics can be approximated using the following equations.

$$\Delta f_T = \alpha (\theta_T - \theta_X)^2$$

•  $\Delta f_T$  : Frequency deviation in any temperature •  $\alpha$  [ 1 / °C² ] : Coefficient of secondary temperature (  $-0.035 \pm 0.005$  )  $\times$  10<sup>-6</sup> / °C²

• θτ [ °C ] : Ultimate temperature ( +25 ± 5 °C )

• θx [°C] : Any temperature

2. To determine overall clock accuracy, add the frequency precision and voltage characteristics.

$$\Delta f/f = \Delta f/fo + \Delta fT + \Delta fV$$

•  $\Delta f/f$  : Clock accuracy (stable frequency)

in any temperature and voltage.

• Δf/fo : Frequency precision

ΔfT : Frequency deviation in any temperature.

Δfv : Frequency deviation in any voltage.

3. How to find the date difference

Date Difference =  $\Delta f/f \times 86400(Sec)$

\* For example:  $\Delta f/f = 11.574 \times 10^{-6}$  is an error of approximately 1 second/day.

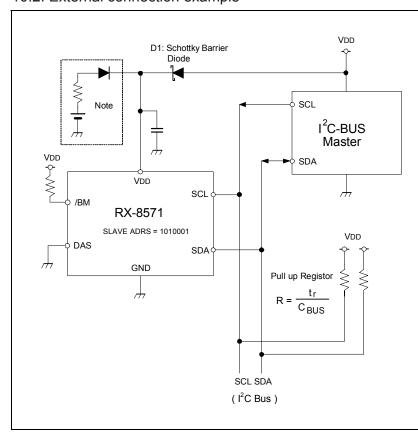

### 10.2. External connection example

#### Note:

It uses the secondary battery or a lithium battery. When using the seconding battery, the diode is not required. When using the lithium battery, the diode is required. For detailed value on the resistance, please consult a battery maker.

### 11. Application notes

#### 1) Notes on handling

This module uses a C-MOS IC to realize low power consumption. Carefully note the following cautions when handling.

#### (1) Static electricity

While this module has built-in circuitry designed to protect it against electrostatic discharge, the chip could still be damaged by a large discharge of static electricity. Containers used for packing and transport should be constructed of conductive materials. In addition, only soldering irons, measurement circuits, and other such devices which do not leak high voltage should be used with this module, which should also be grounded when such devices are being used.

#### (2) Noise

If a signal with excessive external noise is applied to the power supply or input pins, the device may malfunction or "latch up." In order to ensure stable operation, connect a filter capacitor (preferably ceramic) of greater that  $0.1~\mu F$  as close as possible to the power supply pins (between VDD and GNDs). Also, avoid placing any device that generates high level of electronic noise near this module.

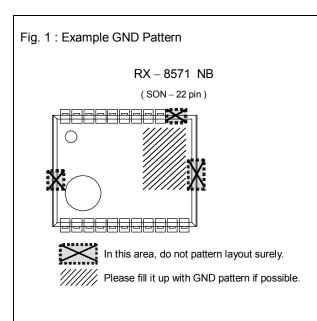

\* Do not connect signal lines to the shaded area in the figure shown in Fig. 1 and, if possible, embed this area in a GND land.

#### (3) Voltage levels of input pins

When the input pins are at the mid-level, this will cause increased current consumption and a reduced noise margin, and can impair the functioning of the device. Therefore, try as much as possible to apply the voltage level close to VDD or GND.

#### (4) Handling of unused pins

Since the input impedance of the input pins is extremely high, operating the device with these pins in the open circuit state can lead to unstable voltage level and malfunctions due to noise. Therefore, pull-up or pull-down resistors should be provided for all unused input pins.

#### 2) Notes on packaging

#### (1) Soldering heat resistance.

If the temperature within the package exceeds +260 °C, the characteristics of the crystal oscillator will be degraded and it may be damaged. The reflow conditions within our reflow profile is recommended. Therefore, always check the mounting temperature and time before mounting this device. Also, check again if the mounting conditions are later changed.

\* See Fig. 2 profile for our evaluation of Soldering heat resistance for reference.

#### (2) Mounting equipment

While this module can be used with general-purpose mounting equipment, the internal crystal oscillator may be damaged in some circumstances, depending on the equipment and conditions. Therefore, be sure to check this. In addition, if the mounting conditions are later changed, the same check should be performed again.

#### (3) Ultrasonic cleaning

Depending on the usage conditions, there is a possibility that the crystal oscillator will be damaged by resonance during ultrasonic cleaning. Since the conditions under which ultrasonic cleaning is carried out (the type of cleaner, power level, time, state of the inside of the cleaning vessel, etc.) vary widely, this device is not warranted against damage during ultrasonic cleaning.

#### (4) Mounting orientation

This device can be damaged if it is mounted in the wrong orientation. Always confirm the orientation of the device before mounting.

#### (5) Leakage between pins

Leakage between pins may occur if the power is turned on while the device has condensation or dirt on it. Make sure the device is dry and clean before supplying power to it.

Fig. 2: Reference profile for our evaluation of Soldering heat resistance. Temperature [ °C ] 300 +260 °C +255 °C tp:20 s to 40 s 250 Avg. Ramp-up +3°C/s Max · +217 °C -6 °C/s Max. 60 s to 150 s Ts max; +200 °C 200 ( +217 °C over ) Ts min ; +150 °C ts 150 60 s to 180 s (+150 °C to +200 °C) 100 50 Time +25 °C to Peak 300 360 420 480 540 600 780 720 Time [s]

### 12. Overview of Functions and Description of Registers

#### 12.1. Overview of Functions

#### 1) Clock functions

This function is used to set and read out month, day, hour, date, minute, second, and year (last two digits) data. Any (two-digit) year that is a multiple of 4 is treated as a leap year and calculated automatically as such until the year 2099.

At the time of a communication start, the Clock & Calendar data are fixed (hold the carry operation), and it is automatically revised at the time of the communication end.

#### 2) Fixed-cycle Timer Interrupt function

The fixed-cycle timer interrupt function generates an interrupt event periodically at any fixed cycle set between 244.14 µs and 65535 hours.

When an interrupt event is generated, the /TIRQ pin goes to low level ("L") and "1" is set to the TF bit to report that an event has occurred..

#### 3) Long-Timer function

It is able to use fixed cycle timer interrupt function as Long-Timer that deals with for approx. 7.5 years.

\* For details, see "13.2. Fixed-cycle Interrupt Function".

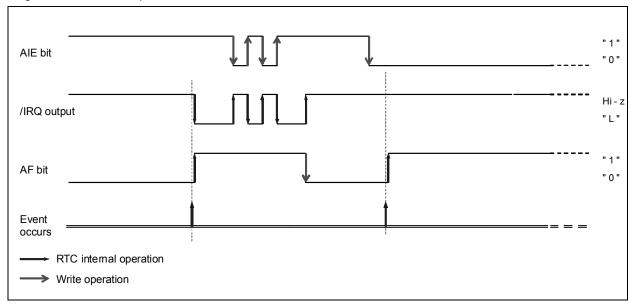

#### 4) Alarm interrupt function

The alarm interrupt function generates interrupt events for alarm settings such as date, day, hour, and minute settings. When an interrupt event occurs, the AF bit value is set to "1" and the /IRQ pin goes to low level to indicate that an event has occurred.

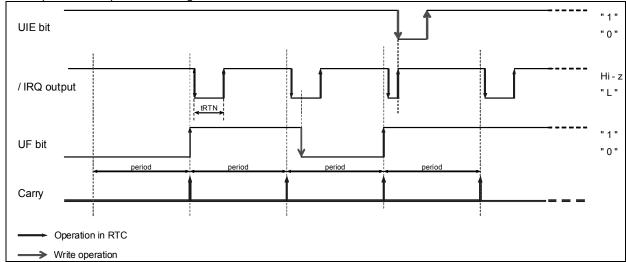

#### 5) Time update interrupt function

The time update interrupt function generates interrupt events at one-second or one-minute intervals, according to the timing of the internal clock. When an interrupt event occurs, the UF bit value becomes "1" and the /INT pin goes to low level to indicate that an event has occurred.

#### 6) Voltage detection function (VLF)

This function indicates the retained status of clock operations or internal data.

#### 7) Clock output function

A clock with the same frequency (32.768 kHz) as the built-in crystal resonator can be output from the FOUT pin (CMOS output).

#### 8) User RAM

RAM register is read/write accessible for any data.

Up to max. 176 bits can be expanded.

#### 9) Block diagram

#### 12.2. Register table

| Address [h]   | Function           | bit 7 | bit 6                                        | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | note           |

|---------------|--------------------|-------|----------------------------------------------|-------|-------|-------|-------|-------|-------|----------------|

| 00            | SEC                | 0     | 40                                           | 20    | 10    | 8     | 4     | 2     | 1     | *2             |

| 01            | MIN                | 0     | 40                                           | 20    | 10    | 8     | 4     | 2     | 1     | *2             |

| 02            | HOUR               | 0     | 0                                            | 20    | 10    | 8     | 4     | 2     | 1     | *2             |

| 03            | WEEK               | 0     | 6                                            | 5     | 4     | 3     | 2     | 1     | 0     | *2             |

| 04            | DAY                | 0     | 0                                            | 20    | 10    | 8     | 4     | 2     | 1     | *2             |

| 05            | MONTH              | 0     | 0                                            | 0     | 10    | 8     | 4     | 2     | 1     | *2             |

| 06            | YEAR               | 80    | 40                                           | 20    | 10    | 8     | 4     | 2     | 1     |                |

| 07            | RAM                | •     | •                                            | •     | •     | •     | •     | •     | •     | *3, *4         |

| 08            | MIN Alarm          | AE    | 40                                           | 20    | 10    | 8     | 4     | 2     | 1     |                |

| 09            | HOUR Alarm         | AE    | •                                            | 20    | 10    | 8     | 4     | 2     | 1     | *3             |

| 0A            | WEEK Alarm         | AE    | 6                                            | 5     | 4     | 3     | 2     | 1     | 0     | *3             |

| UA            | DAY Alarm          | AL    | •                                            | 20    | 10    | 8     | 4     | 2     | 1     | <sup>2</sup> 2 |

| 0B            | Timer Counter 0    | 128   | 64                                           | 32    | 16    | 8     | 4     | 2     | 1     |                |

| 0C            | Timer Counter 1    | 32768 | 16384                                        | 8192  | 4096  | 2048  | 1024  | 512   | 256   |                |

| 0D            | Extension Register | FSEL1 | FSEL0                                        | USEL  | TE    | WADA  | TSEL2 | TSEL1 | TSEL0 | *2             |

| 0E            | Flag Register      | TEST1 | TEST2                                        | UF    | TF    | AF    | TEST3 | VLF   | 0     | *1, *2         |

| 0F            | Control Register   | 0     | 0                                            | UIE   | TIE   | AIE   | TSTP  | STOP  | 0     | *2             |

| Address [h]   | Function           | bit 7 | bit 6                                        | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | note           |

| 10<br> <br>1F | RAM                |       | User Register<br>128 bit ( 16 word x 8 bit ) |       |       |       |       |       |       | *3, *4, *5     |

Note During the initial power-on (from 0 V) and if the value of the VLF bit is "1" when the VLF bit is read, be sure to initialize all registers before using them.

When doing this, be careful to avoid setting incorrect data as the date or time, as timed operations cannot be guaranteed if incorrect date or time data has been set.

- \*1. The <u>TEST1</u>, <u>TEST2</u>, <u>TEST3</u> bits are Epson Toyocom test bits.

- \* Be sure to write "0" by initializing before using the clock module. Afterward, be sure to set "0" when writing.

- \* The four *TEST*\* bits are undefined when read. Those bits should be masked after being read.

- \*2. The 'o' mark indicates a write-prohibited bit, which returns a "0" when read.

- \*3. The '•' mark indicates a read/write-accessible RAM bit for any data.

- \*4. As for Address 07[h] and User Register, R/W is enabled after 30ms after arrival the VDD voltage in a Operating voltage range at initial power-on (from 0 V).

- \*5 The User Register is read/write accessible for any data in the range from 00 h to FF h.

#### 12.3. Description of Functions

#### 12.3.1. Clock & Calendar Register ( Reg - 00[h] ~ 06[h] )

The clock and the calendar consists of seconds, minutes, hours, day of the week, day, month, and year.

\* For details, see "13.1. Clock functions".

#### 12.3.2. RAM Register (Reg - 07[h] and Reg - $10[h] \sim 1F[h]$ )

This RAM register is read/write accessible for any data in the range from 00 h to FF h.

R/W is enabled after 30ms after arrival the VDD voltage in an Operating voltage range at initial power-on.

#### 12.3.3. Alarm Register ( Reg - 08[h] ~ 0A[h] )

The alarm interrupt function is used, along with the AE, AF, and WADA bits, to set alarms for specified date, day, hour, and minute values. When the settings in the alarm registers and the WADA bit match the current time, the /IRQ pin goes to low level and "1" is set to the AF bit to report that and alarm interrupt event has occurred.

When this function is not used, this register is read/write accessible for any data by setting to AIE="0".

\* For details, see "13.2. Alarm Interrupt Function".

#### 12.3.4. Timer setting and Timer counter register ( Reg - 0B[h] $\sim$ 0C[h] )

To use the fixed-cycle timer interrupt function, the TE, TF, TIE, TSEL0, TSEL1 and TSEL2 bits are set and used. When this down counter's count value changes from 0001h to 0000h, when TF bit = "1", or when the /IRQ pin is at low level ("L"), it indicates that a fixed-cycle timer interrupt event has occurred. When this function is not used, This register is read/write accessible for any data by writing "0" to the TE and TIE bits.

\* For details, see "13.3. Fixed-cycle Timer Interrupt Function.

#### 12.3.5. Extension-related register (Reg - 0D[h] ~ 0F[h])

| Address [h] | Function           | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------------|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0D          | Extension Register | FSEL1 | FSEL0 | USEL  | TE    | WADA  | TSEL2 | TSEL1 | TSEL0 |

| 0E          | Flag Register      | TEST1 | TEST2 | UF    | TF    | AF    | TEST3 | VLF   | 0     |

| 0F          | Control Register   | 0     | 0     | UIE   | TIE   | AIE   | TSTP  | STOP  | 0     |

#### 1) FSEL1, FSEL0 bits (Frequency Select)

A combination of the FSEL1 and FSEL0 bits is used to select the frequency to be output.

The choice is possible by a combination of FSEL-bits and FOE-pin, select the frequency of clock output or inhibit the clock output. Setting example when a this function is not used. (The FOE terminal is connected to GND, FSEL0,1 = "0") \* For details, see "13.7. Fout Function.

#### 2) USEL, UF, UIE bits (Time update Interrupt)

These are bits to control an action of the Time update interrupt function.

Setting example when a time this function is not used. (USEL, UIE = "0", Ignore UF)

\* For details, see "13.4. Time update interrupt Function.

#### 3) TE, TF, TIE, TSEL2, TSEL1, TSEL0, TSTP bit (Fixed-cycle timer interrupt)

These are bits to control an action of the Fixed-cycle timer interrupt function.

Setting example when a time this function is not used.

(TE,TIE,TSTP, TSEL1,TSEL0="0", TSEL2="1", Ignore TF)

\* For details, see "13.3. Fixed-cycle Timer Interrupt Function ".

#### 4) WADA, AF, AIE bit ( Alarm interrupt)

These are bits to control an action of the Alarm interrupt function.

Setting example when a time this function is not used. (WADA, AIE = "0", Ignore AF)

\* For details, see "13.2. Alarm Interrupt Function".

#### 5) *TEST* bit

Those bits are the manufacturer's test bit. Always leave this bit value as "0" except when testing. Be careful to avoid writing to this bit when writing "1" to other bits in this register.

#### 6) VLF bit( Voltage Low Flag )

This flag bit indicates the retained status of clock operations or internal data. Its value changes from "0" to "1" when data loss occurs, such as due to a supply voltage drop. Once this flag bit's value is "1", its value is retained until a "0" is written to it.

\* For details, see "13.6. Voltage detection function".

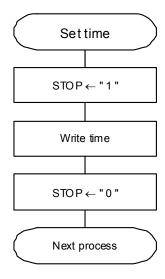

#### 7) STOP bit

This bit is used to stop functions related to the RTC's internal counter operations.

Writing a "1" to this bit stops the counter operations.

There is the following influence at the time of STOP bit "1".

\* 1) All the update of a clock and a calendar action stops.

With it, an alarm interrupt and time update interrupt events does not occur.

\* 2) One part of a fixed-cycle timer function stops.

A count stops at the time of 64Hz, 1Hz, 1min, 1h source clock setting of a fixed-cycle timer. (A fixed-cycle timer can work only in 4096Hz.)

\* 3) The effect of STOP bit to FOUT functions.

When STOP = "1", 32768Hz and 1024Hz output is possible. But 1Hz output is disabled.

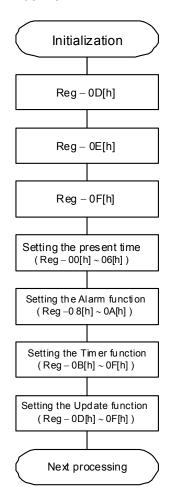

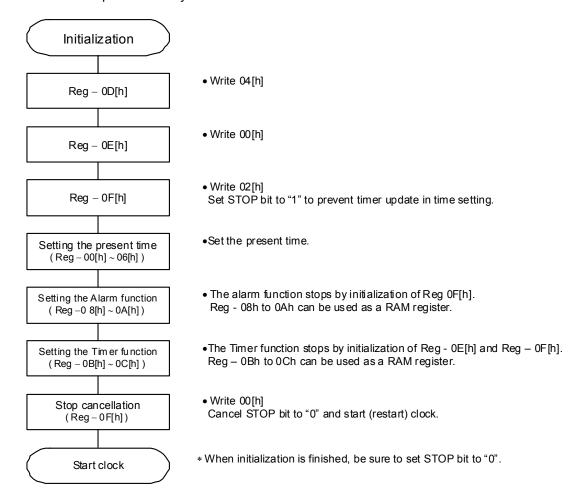

#### 13.1. How to use

#### 13.1. Description of Clock & Calendar function

At the time of a communication start, the Clock & Calendar data are fixed (hold the carry operation), and it is automatically revised at the time of the communication end. Therefore it recommends that the access to a clock calendar has continuous access by the auto increment function.

Setting example: Sun, 29-Feb-88 17:39:45 (leap year)

|             | <u> </u> |       |       |       |       |       |       |       |       |

|-------------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address [h] | Function | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| 00          | SEC      | 0     | 1     | 0     | 0     | 0     | 1     | 0     | 1     |

| 01          | MIN      | 0     | 0     | 1     | 1     | 1     | 0     | 0     | 1     |

| 02          | HOUR     | 0     | 0     | 0     | 1     | 0     | 1     | 1     | 1     |

| 03          | WEEK     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

| 04          | DAY      | 0     | 0     | 1     | 0     | 1     | 0     | 0     | 1     |

| 05          | MONTH    | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     |

| 06          | YEAR     | 1     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

|             |          |       |       |       |       |       |       |       |       |

<sup>\*</sup> Note with caution that writing non-existent time data may interfere with normal operation of the clock counter.

#### 13.1.1. Clock counter ( Reg - 00[h] ~ 02[h] )

1) [SEC] & [MIN] counter ( Reg - 00[h] ~ 01[h] )

These registers are 60-base BCD counters. These registers are incremented at the timing when carry is generated from a lower register. At the timing when the lower register changes from 59 to 00, carry is generated to the higher register and thus incremented.

When writing is performed to [SEC] register, Internal-count-down-chain less than one second (512Hz ~ 1 Hz) is cleared to 0.

#### 2) Hour counter (Reg - 02[h])

This register is a 24-base BCD counter (24 hour format). These registers are incremented at the timing when carry is generated from a lower register.

#### 13.1.2. . Week counter ( Reg - 03[h] )

The day (of the week) is indicated by 7 bits, bit 0 to bit 6.

The day data values are counted as: Day  $01h \rightarrow Day \ 02h \rightarrow Day \ 04h \rightarrow Day \ 08h \rightarrow Day \ 10h \rightarrow Day \ 20h \rightarrow Day \ 40h \rightarrow Day \ 01h \rightarrow Day \ 02h$ , etc.

It is incremented when carry is generated from the HOUR register. This register does not generate carry to a higher register. Since this register is not connected with the YEAR, MONTH and DAY registers, it needs to be set again with the matching day of the week if any of the YEAR, MONTH or DAY registers have been changed.

• The correspondence between days and count values is shown below.

| Day       | bit | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bi | bit 0 | Data [h] |

|-----------|-----|-------|-------|-------|-------|-------|----|-------|----------|

| Sunday    | 0   | 0     | 0     | 0     | 0     | 0     | 0  | 1     | 01 h     |

| Monday    | 0   | 0     | 0     | 0     | 0     | 0     | 1  | 0     | 02 h     |

| Tuesday   | 0   | 0     | 0     | 0     | 0     | 1     | 0  | 0     | 04 h     |

| Wednesday | 0   | 0     | 0     | 0     | 1     | 0     | 0  | 0     | 08 h     |

| Thursday  | 0   | 0     | 0     | 1     | 0     | 0     | 0  | 0     | 10 h     |

| Friday    | 0   | 0     | 1     | 0     | 0     | 0     | 0  | 0     | 20 h     |

| Saturday  | 0   | 1     | 0     | 0     | 0     | 0     | 0  | 0     | 40 h     |

<sup>\*</sup> Do not set "1" to more than one day at the same time.

#### 13.1.3. Calendar counter ( Reg - 04[h] ~ 06[h] )

1) [ DAY ] & [MONTH] register ( Reg - 04 [h] )

The DAY register is a variable (between 28-base and 31-base) BCD counter that is influenced by the month and the leap year. The MONTH register is 12-base BCD counter, when carry is generated from a lower register.

|                               | Jan. | Feb.     | Mar | Apr. | May | June | July | Aug. | Sep. | Oct. | Nov. | Dec. |

|-------------------------------|------|----------|-----|------|-----|------|------|------|------|------|------|------|

| Days Normal year<br>Leap year | 31   | 28<br>29 | 31  | 30   | 31  | 30   | 31   | 31   | 30   | 31   | 30   | 31   |

### 2) [ YEAR ] register ( Reg - 06 [h] )

This register is a BCD counter for years 00 to 99.

The leap year is automatically determined, which reflects in the DAY register.

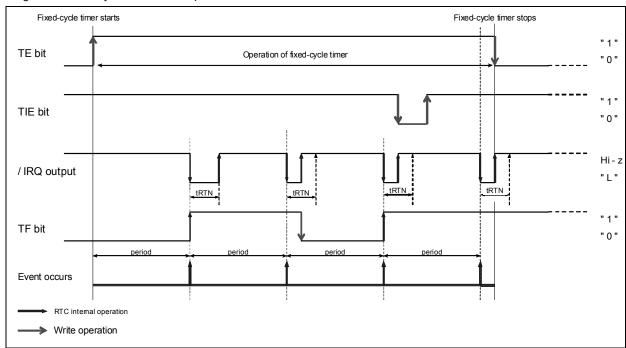

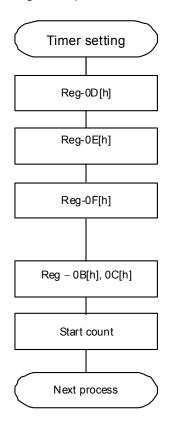

#### 13.2. Fixed-cycle Timer Interrupt Function

The fixed-cycle timer interrupt function generates an interrupt event periodically at any fixed cycle set between 244.14 µs and 65535 hours.

This function can stop at one time and is available as a accumulative timer.

After the interrupt occurs, the /IRQ status is automatically cleared (/IRQ status changes from low-level to Hi-z). At the time of source clock setting 1Hz or 1/60Hz or 1/3600Hz, IRQ outputs "L" after 7.813ms from event occurrence at the maximum.

#### 13.2.1. Related registers for function of fixed-cycle timer interrupt function

| Address [h] | Function           | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------------|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0B          | Timer Counter 0    | 128   | 64    | 32    | 16    | 8     | 4     | 2     | 1     |

| 0C          | Timer Counter 1    | 32768 | 16384 | 8192  | 4096  | 2048  | 1024  | 512   | 256   |

| 0D          | Extension Register | FSEL1 | FSEL0 | USEL  | TE    | WADA  | TSEL2 | TSEL1 | TSEL0 |

| 0E          | Flag Register      | TEST1 | TEST2 | UF    | TF    | AF    | TEST3 | VLF   | 0     |

| 0F          | Control Register   | 0     | 0     | UIE   | TIE   | AIE   | TSTP  | STOP  | 0     |

- \* Before entering operation settings, we recommend first clearing the TE bit to "0".

- \* When the fixed-cycle timer function is not being used, the fixed-cycle timer control register (Reg 0B to  $\,$  0C) can be used as a RAM register. In such cases, stop the fixed-cycle timer function by writing "0" to the TE and TIE bits.

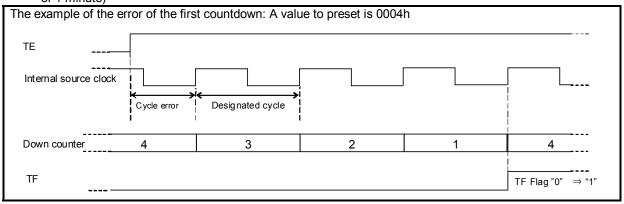

- 1) Down counter for fixed-cycle timer (Timer Counter 1, 0)

This register is used to set the default (preset) value for the counter. Any count value from 1 (0001 h) to 65535 (FFFFh) can be set.

Be sure to write "0" to the TE bit before writing the preset value. If a value is written while TE = "1" the first subsequent event will not be generated correctly.

\* When TE=0, read out data of timer counter is default(Preset) value.

And when TE=1, read out data of timer counter is just counting value.

But, when access to timer counter data, counting value is not held.

Therefore, for example, perform twice read access to obtain right data, and a way to adopt the case that two data accorded is necessary.

#### 2) TSEL2, TSEL1, TESL0 bits (Timer Select 2, 1, 0)

The combination of these three bits is used to set the countdown period (source clock) for this function. Be sure to write "0" to the TE bit before writing the source clock value.

| TSEL2, 1, 0 | TSEL1 TSEL1 TSEL0 (bit 1) (bit 0) |   |   | Source clock                | Auto reset time<br>tRTN | Effects of STOP<br>and RESET bits |

|-------------|-----------------------------------|---|---|-----------------------------|-------------------------|-----------------------------------|

|             | 0                                 | 0 | 0 | 4096 Hz /Once per 244.14 μs | 122 μs                  | _                                 |

|             | 0                                 | 0 | 1 | 64 Hz /Once per 15.625 ms   | 7.813 ms                |                                   |

| W/R         | 0                                 | 1 | 0 | 1 Hz /Once per second       | 7.813 ms                | * Does not operate when           |

|             | 0                                 | 1 | 1 | 1/60 Hz /Once per minute    | 7.813 ms                | the STOP bit value is "1".        |

|             | 1                                 | 0 | 0 | 1/3600 Hz /Once per hour    | 7.813 ms                |                                   |

- \*1) The /IRQ pin's auto reset time (tRTN) varies as shown above according to the source clock setting.

- \*2) The first countdown shortens than a source clock.

It is linked with carry update of inner timing, for example, if timer movement is started at 50 minute, the first countdown is performed after 10 minutes. (After the second time, countdown is performed with proper cycle of 1 minute)

#### 3) TE bit (Timer Enable)

When TE bit is "0", the default (preset) can be checked by reading this register.

| TE    | Data | Description                                                                                                                                  |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0    | Stops fixed-cycle timer interrupt function.  * Clearing this bit to zero does not enable the /IRQ low output status to be cleared (to Hi-z). |

| Write |      | Starts fixed-cycle timer interrupt function.                                                                                                 |

|       | 1    | * The countdown that starts when the TE bit value changes from "0" to "1" always begins from the preset value.                               |

#### 4) TF bit (Timer Flag)

This is a flag bit that retains the result when a fixed-cycle timer interrupt event is detected.

| TF         | Data | Description                                                                                                                                                             |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>Write |      | The TF bit is cleared to zero to prepare for the next status detection  * Clearing this bit to zero does not enable the /IRQ low output status to be cleared (to Hi-z). |

|            | 1    | This bit is invalid after a "1" has been written to it.                                                                                                                 |

| 0          |      | -                                                                                                                                                                       |

| Read       | 1    | Fixed-cycle timer interrupt events are detected. (Result is retained until this bit is cleared to zero.)                                                                |

#### 5) TIE bit (Timer Interrupt Enable)

This bit is used to control output of interrupt signals from the /IRQ pin when a fixed-cycle timer interrupt event has occurred.

| TIE   | Data | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write | 0    | 1) When a fixed-cycle timer interrupt event occurs, an interrupt signal is not generated or is canceled (/IRQ status remains Hi-z).  2) When a fixed-cycle timer interrupt event occurs, the interrupt signal is canceled (/IRQ status changes from low to Hi-z).  * Even when the TIE bit value is "0" another interrupt event may change the /IRQ status to low (or may hold /IRQ = "L"). |

|       | 1    | When a fixed-cycle timer interrupt event occurs, an interrupt signal is generated (/IRQ status changes from Hi-z to low).                                                                                                                                                                                                                                                                   |

#### 6) TSTOP bit (Timer stop)

This bit is used to stop fixed-cycle timer count down.

- \* It is linked with carry update of inner timing, therefore stop shorter period than source clock may not be reflected.

- \* For example, even if select source clock 1/3600 Hz and suspend countdown from 3 o'clock 5 minutes to 3 o'clock 55 minutes of time counter, countdown is performed 5 minutes later at 4 o'clock 0 minute similar to the case without suspend.

| TSTP                                   | Data | Description                                                                |

|----------------------------------------|------|----------------------------------------------------------------------------|

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 0    | Writing a "0" to this bit cancels stop status (restarts timer count down). |

| Write                                  | 4    | Writing a "1" to this bit stops the timer count down.                      |

|                                        | !    | * The /IRQ output does not change.                                         |

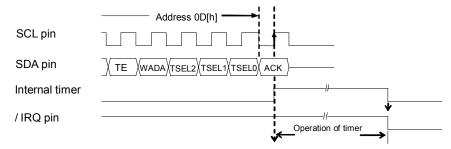

#### 13.2.3. Fixed-cycle timer start timing

Counting down of the fixed-cycle timer value starts at the rising edge of the SCL (ACK output) signal that occurs when the TE value is changed from "0" to "1".

#### 13.2.4. Fixed-cycle timer interrupt interval (example)

The combination of the source clock settings (settings in TSEL2, TSEL1 and TSEL0) and fixed-cycle timer countdown setting (Reg-0B to Reg-0C setting) sets the fixed-cycle timer interrupt interval, as shown in the following examples.

| Times Country                   |                                         |                                       | Source clock                         |                                           |                                             |

|---------------------------------|-----------------------------------------|---------------------------------------|--------------------------------------|-------------------------------------------|---------------------------------------------|

| Timer Counter setting 1 ~ 65535 | 4096 Hz<br>TSEL2 = 0<br>TSEL1, 0 = 0, 0 | 64 Hz<br>TSEL2 = 0<br>TSEL1, 0 = 0, 1 | 1 Hz<br>TSEL2 = 0<br>TSEL1, 0 = 1, 0 | 1 / 60 Hz<br>TSEL2 = 0<br>TSEL1, 0 = 1, 1 | 1 / 3600 Hz<br>TSEL2 = 1<br>TSEL1, 0 = 0, 0 |

| 0                               | _                                       | _                                     | _                                    | -                                         | _                                           |

| 1                               | 244.14 μs                               | 15.625 ms                             | 1 s                                  | 1 min                                     | 1 h                                         |

| 2                               | 488.28 μs                               | 31.250 ms                             | 2 s                                  | 2 min                                     | 2 h                                         |

| :                               | :                                       | :                                     | •                                    | :                                         | :                                           |

| 41                              | 10.010 ms                               | 640.63 ms                             | 41 s                                 | 41 min                                    | 41 h                                        |

| 128                             | 31.250 ms                               | 2.000 s                               | 128 s                                | 128 min                                   | 128 h                                       |

| 320                             | 78.125 ms                               | 5.000 s                               | 320 s                                | 320 min                                   | 320 h                                       |

| 410                             | 100.10 ms                               | 6.406 s                               | 410 s                                | 410 min                                   | 410 h                                       |

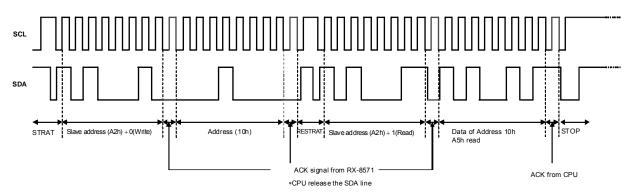

| :                               | :                                       | :                                     | :                                    | :                                         | :                                           |