# **QF1Da512**

Simple and versatile FIR engine (SavFIRe<sup>TM</sup>)

#### **APPLICATIONS**

- Audio Equalization, Crossovers, and 3D widening

- Televisions

- Docking Stations

- Stereo Headsets (both wired and wireless)

- Home Theatre Speakers

- Digital Volume Control

- Other powered speaker products

#### DESCRIPTION

A programmable digital filter designed for seamless insertion in a serial data path or used as a coprocessor. The device can be programmed using the Quickfilter Pro<sup>TM</sup> Design Software which supports a variety of FIR digital filter algorithms plus import and curve fitting (for equalization and other unique transfer functions). The FIR filter has 512 taps capable of easily generating audio equalization and crossover filters. The QF1Da512 supports a wide variety of data sources. It also has digital gain and programmable compression allowing the part to also serve as a distortion-less digital volume control. The QF1Da512 can be configured to filter one or both channels of an I2S data stream. The filter can operate over a broad range of data rates from 10sps up to 500ksps and can support data resolutions ranging from 12 to 24 bits.

#### ORDERING INFORMATION

| Device        | Package                                  |

|---------------|------------------------------------------|

| QF1Da512-QN-T | 16-Pin QFN - Tape & Reel (Reel qty 1000) |

| QF1Da512-QN-B | - Trays (tray qty 496)                   |

| QF1D512-DK    | Base 1D Development Kit                  |

| QF1Da512-DK   | 1Da Audio Dragon Platform                |

#### **FEATURES**

- 512-tap symmetric or 256-tap non-symmetric FIR filter

- Up to 24 bit data words

- 32 bit coefficients

- · Built in digital gain and compression

- Re-programmable in circuit

- Data Rate: Up to 500ksps (far exceeds audio needs)

- Data Interface: I<sup>2</sup>S, SPI & synchronous serial modes

- SPI Configuration

- Multiple devices can be daisy chained, with programmable bypass mode.

- Programmable Averaging and Down-sampler pre-FIR, including bypass mode

- Low Power: < 3mW @ 44.1Ksps, <6mW @ 96Ksps

- 3.3V Digital I/O, 5 Volt Tolerant with 3.3V & 1.8V Supplies

- Industrial Temp -40C to +85C

- Package: 16-pin QFN (3 X 3 mm)

#### QUICKFILTER DEVELOPMENT ENVIRONMENT

#### QF1Da512-DK Audio Evaluation Platform

- Daughter card with stereo RCA jacks for input and output

- Also support SPDIF inputs and outputs

#### QF1D512-DK; Motherboard

Host for configuring and programming QF1Da512-DK via USB

# **TABLE OF CONTENTS**

| 1           | SPECIFICATIONS                                 | 5  |

|-------------|------------------------------------------------|----|

| Ab          | osolute Maximum Ratings                        | 5  |

|             | nckage Assembly                                |    |

|             | ecommended Operating Conditions                |    |

|             | pical Performance Characteristics              |    |

|             | ectrical Characteristics                       | _  |

|             | ming Requirements                              |    |

|             | 1.1 CONFIGURATION TIMING REQUIREMENTS          |    |

| 1.1         | 1.2 Data Path Timing Requirements              |    |

| 2           | PINOUT AND PIN DESCRIPTIONS                    | 9  |

| 3           | GENERAL DESCRIPTION                            | 10 |

| Da          | ata Format and Control                         | 10 |

|             | eraging and Down-sampler                       |    |

|             | nite Impulse Response Filter (FIR)             |    |

|             | gital Gain and Compression (DGC)               |    |

| Со          | onfiguration Interface                         | 10 |

| 4           | SOFTWARE                                       | 11 |

| De          | evice Configuration                            | 11 |

|             | uickfilter Audio Development Kit (QF1Da512-DK) |    |

| Qu          | uickfilter Host Development Kit (QF1D512-DK)   | 11 |

| 5           | GENERAL OPERATION                              | 11 |

| 6           | CONFIGURATION INTERFACE                        | 12 |

|             | PI, Serial Peripheral Bus                      |    |

| <b>5.</b> 1 |                                                |    |

| 6.1         |                                                |    |

|             | ending Commands in Data Mode                   |    |

| 7           | DATA INTERFACE                                 | 13 |

|             |                                                |    |

| IVIC        | odes of Operationata Passthrough               | 13 |

| υa          | ata Passtnrougn                                | 10 |

| 8           | DIGITAL DOWN SAMPLING                          | 16 |

| Do          | ownconverter                                   | 16 |

|             | nannel Duplication                             |    |

| 9           | FIR FILTER                                     | 17 |

|             | odes of Operation                              |    |

| FIF         | R Latency                                      |    |

| . "         | · · · · · · · · · · · · · · · · · · ·          | 17 |

| 10          | DIGITAL GAIN AND COMPRESSION (DGC)             | 18 |

| Mode  | Mode of Operation                        |    |  |  |  |

|-------|------------------------------------------|----|--|--|--|

| 11 C  | CONTROL REGISTERS                        | 18 |  |  |  |

| Over  | rview                                    | 18 |  |  |  |

|       | figuration Registers                     |    |  |  |  |

|       | fficient Memory                          |    |  |  |  |

| 12 O  | DPERATING MODE CONFIGURATIONS            | 31 |  |  |  |

| 12.1  | I2S Mode                                 | 31 |  |  |  |

| 12.2  |                                          | 31 |  |  |  |

| 12.3  | Normal SPI Mode                          | 32 |  |  |  |

| 12.4  | Continuous SPI Mode (CS_N tied to GND)   | 32 |  |  |  |

| 12.5  | Synchronous Serial Mode (uP clock slave) | 33 |  |  |  |

| 12.6  |                                          |    |  |  |  |

| 12.7  | J                                        | 34 |  |  |  |

| 12.8  | QF1Da512 Configuration Mode              | 34 |  |  |  |

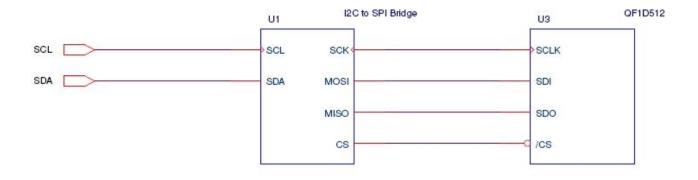

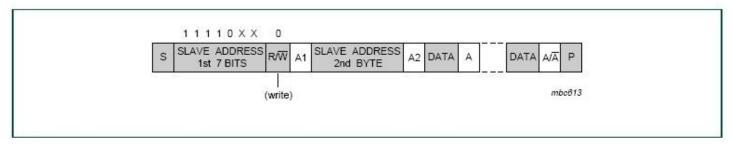

| 13 I2 | 2C OPTION                                | 35 |  |  |  |

| 13.1  | Mode of Operation                        | 35 |  |  |  |

|       |                                          |    |  |  |  |

| 14 D  | OGC USER GUIDANCE                        | 37 |  |  |  |

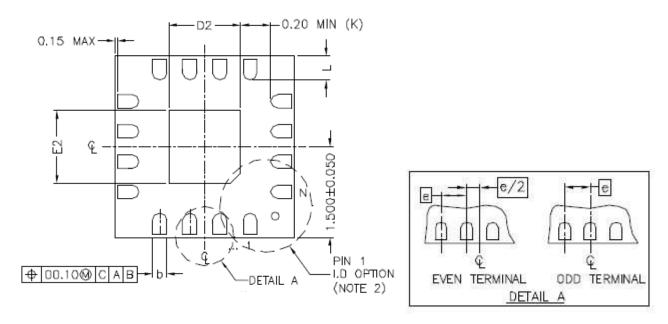

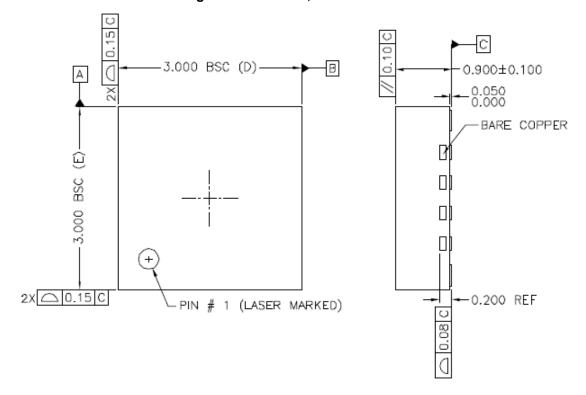

| 15 P. | PACKAGING INFORMATION                    | 38 |  |  |  |

| 16 R  | REGISTERS, TABLES, AND FIGURES           | 40 |  |  |  |

| Cont  | trol Register Listing                    | 40 |  |  |  |

|       | of Tables                                |    |  |  |  |

|       | of Figures                               |    |  |  |  |

|       |                                          |    |  |  |  |

#### 1 SPECIFICATIONS

#### **Absolute Maximum Ratings**

Stresses above those listed under Absolute Maximum Ratings can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Parameter                                             | Min   | Max   | Units |

|-------------------------------------------------------|-------|-------|-------|

| Storage Temperature                                   | -40   | 150   | °C    |

| Supply Voltage, V <sub>DD18</sub> to GND              | -0.3V | 2.16V | V     |

| Supply Voltage, V <sub>DD33</sub> with respect to GND | -0.3V | 4.0V  | V     |

| Digital Input Voltage with respect to GND             | -0.3  | 5.8   | V     |

| ESD Immunity (HBM, JESD22-A114-D Class 1C)            |       | 7.5   | KV    |

| ESD Immunity (HBM, AEC-Q100-002D)                     |       | 6.75  | KV    |

This integrated circuit can be damaged by ESD. Quickfilter Technologies recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

## **Package Assembly**

The QF1Da512 is offered in a "green" package (RoHS & no Sb/Br), assembled with enhanced environmentally compatible Pb-free and halide-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. The peak soldering temperature should not exceed 260°C during printed circuit board assembly.

# **Recommended Operating Conditions**

| Parameter             | Symbol            | Min  | Тур | Max  | Units |

|-----------------------|-------------------|------|-----|------|-------|

| Supply Voltage 1.8    | V <sub>DD18</sub> | 1.62 | 1.8 | 1.98 | V     |

| Supply Voltage 3.3    | V <sub>DD33</sub> | 3.0  | 3.3 | 3.6  | V     |

| Digital Input Voltage |                   | 0    |     | 5.5  | V     |

| Ambient Temperature   | T <sub>A</sub>    | -40  | 25  | 85   | °C    |

Note: Quickfilter guarantees the performance of this device over specified ranges by conducting electrical characterization over each range and by conducting a production test with single insertion coupled to periodic sampling.

# **Typical Performance Characteristics**

Default Conditions:  $T_A = 25 \text{ C}$ ,  $V_{DD18} = 1.8 \text{ V}$ ,  $V_{DD33} = 3.3 \text{ V}$ ,

## **Electrical Characteristics**

| Symbol                            | Parameter (                                    | Min                                           | Тур  | Max   | Units | Note |   |

|-----------------------------------|------------------------------------------------|-----------------------------------------------|------|-------|-------|------|---|

| Supply                            | Current & Power Dissipation                    | •                                             |      |       |       |      |   |

|                                   | 1.8V Supply Operating Current                  | - f <sub>S</sub> = 50 kHz, 512 taps           |      | 1.3   |       | mA   |   |

|                                   |                                                | - $f_S = 299 \text{ kHz}$ , 512 taps          |      | 6.6   |       | mA   |   |

| I <sub>DD18</sub>                 |                                                | - $f_S = 500 \text{ kHz}$ , 512 taps          |      | 11.6  |       | mA   |   |

|                                   |                                                | - Standby                                     |      | 50    |       | nA   |   |

|                                   | 3.3V Supply Operating Current                  | - f <sub>S</sub> = 50 kHz                     |      | 70    |       | uA   |   |

| I <sub>DD33</sub>                 |                                                | $- f_S = 299 \text{ kHz}$                     |      | 200   |       | uA   |   |

| IDD33                             |                                                | $- f_S = 500 \text{ kHz}$                     |      | 400   |       | uA   |   |

|                                   |                                                | - Standby                                     |      | 20    |       | uA   |   |

| Digital I                         | puts (cSDI, cCSn, cSCK, dSDI,                  | dCS, dSCK, RSTn)                              |      |       |       |      |   |

| $V_{IH}$                          | High-level Input Voltage, V <sub>DD33</sub> =  | 3.6V                                          | 2.0  |       | 5.5   | V    |   |

| $V_{IL}$                          | Low-level Input Voltage, V <sub>DD33</sub> = 3 | 3.0V                                          | -0.3 |       | 0.8   | V    |   |

| I <sub>IH</sub> , I <sub>IL</sub> | Input (leakage) current                        |                                               |      | +/- 1 |       | uA   |   |

| C <sub>IN</sub>                   | Input Capacitance                              |                                               |      | 10    |       | pF   |   |

| $R_{PU}$                          | Pull Up Resistance                             |                                               | 40   | 75    | 190   | KOhm |   |

| $R_{PD}$                          | Pull Down Resistance                           |                                               | 40   | 75    | 190   | KOhm |   |

| Digital C                         | Output (cSDO, dSDO)                            |                                               |      |       |       |      | Ш |

| $V_{OH}$                          | High-level Output Voltage, DVDD3               | <sub>3</sub> = 3.0V, I <sub>OH</sub> = -100uA | 2.4  |       |       | V    |   |

| $V_{OL}$                          | Low-level Output Voltage, DV <sub>DD3</sub>    |                                               |      | 0.4   | V     |      |   |

| Co                                | Output Capacitance                             |                                               |      | 10    | pF    |      |   |

| I <sub>load</sub>                 | Output Current                                 |                                               | 4    | mA    |       |      |   |

| $C_{load}$                        | Load Capacitance                               |                                               |      | 7     | pF    |      |   |

# **Timing Requirements**

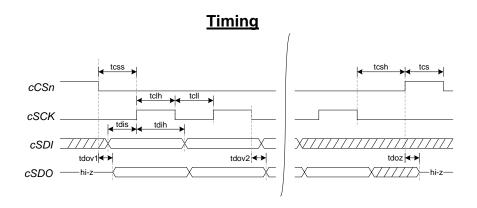

# 1.1.1 Configuration Timing Requirements

## **Parameters**

| Symbol | Parameter (SPI Input)             | Min | Max | Units | Note |

|--------|-----------------------------------|-----|-----|-------|------|

| fs     | Sample Frequency                  |     | 500 | KHz   |      |

| fsck   | Serial Port Clock Frequency       |     | 20  | MHz   |      |

| tcll   | cSCK low time                     | 12  |     | nS    |      |

| tclh   | cSCK high time                    | 12  |     | nS    |      |

| tcss   | cCSn falling to cSCK rising* time | 24  |     | nS    |      |

| tcsh   | cSCK falling to cCSn rising* time | 24  |     | nS    |      |

| tcs    | cCSn high time                    | 50  |     | nS    |      |

| tdis   | cSDI setup time                   | 12  |     | nS    |      |

| tdih   | cSDI hold time                    | 24  |     | nS    |      |

| tdov1  | cCSn falling to cSDO valid time   | 12  |     | nS    |      |

| tdov2  | cSCK falling* to cSDO valid time  | 12  |     | nS    |      |

| tdoz   | cCSn rising toc SDO high-Z time   | 12  |     | nS    |      |

<sup>\*</sup> Using default cSCK capture/drive polarity.

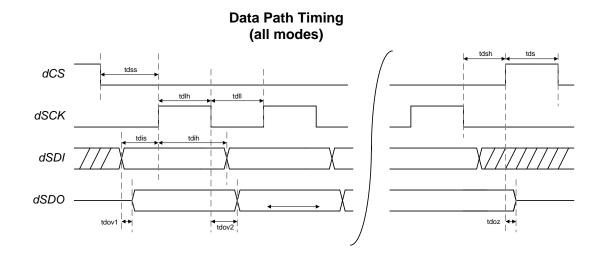

# 1.1.2 Data Path Timing Requirements

# **Parameters**

| Symbol | Parameter(SPI Output)                        | Min | Max | Units | Note |

|--------|----------------------------------------------|-----|-----|-------|------|

| fs     | Sample Frequency                             |     | 500 | KHz   |      |

| fdck   | Data Clock Frequency (dSCK)                  |     | 24  | MHz   |      |

| tdll   | dSCK low time                                | 12  |     | nS    |      |

| tdlh   | dSCK high time                               | 12  |     | nS    |      |

| tdss   | Setup time dCS low to dSCK rising edge       | 24  |     | nS    |      |

| tdsh   | dSCK falling to dCS rising* time             | 24  |     | nS    |      |

| tds    | Hold time dCS high                           | 50  |     | nS    |      |

| tdis   | dSDI setup time                              | 12  |     | nS    |      |

| tdih   | dSDI hold time                               | 24  |     | nS    |      |

| tdov1  | dSDI to dSDO valid (pass thru data)          | 8   |     | nS    |      |

| tdov2  | dSCK to dSDO valid (filtered data)           | 12  |     | nS    |      |

| tdoz   | dCS inactive to dSDO tri-state (Normal Mode) | 12  |     | nS    |      |

NOTE: For tdov1 and tdov2, the output pin is set with  $I_{\text{load}}$  at 4mA and  $C_{\text{load}}$  at 7pf.

## 2 PINOUT and PIN DESCRIPTIONS

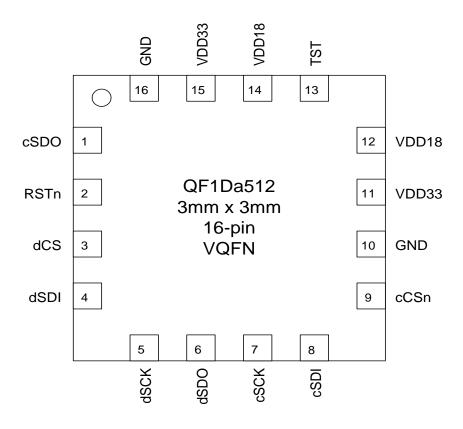

Figure 1: 16 Pin QFN Package Pin out

Table 1 Pin Descriptions

| Pin | Signal Name | I/O | Туре    | Description                                                                                      |  |

|-----|-------------|-----|---------|--------------------------------------------------------------------------------------------------|--|

| 1   | cSDO        | 0   | Digital | Configuration serial data output                                                                 |  |

| 2   | RSTn        | I   | Digital | Chip reset; active low; default internal pull-up                                                 |  |

| 3   | dCS         | I   | Digital | Data interface chip select; configurable as active low or high                                   |  |

| 4   | dSDI        | I   | Digital | Data serial data input                                                                           |  |

| 5   | dSCK        | I   | Digital | Data input clock used to capture dSDI; active capture edge either high, low or both              |  |

| 6   | dSDO        | 0   | Digital | Data serial data output                                                                          |  |

| 7   | cSCK        | I   | Digital | Serial input clock used for configuration data transfers; active capture edge either high or low |  |

| 8   | cSDI        | I   | Digital | Configuration serial data input                                                                  |  |

| 9   | cCSn        | I   | Digital | Configuration interface chip select; active low; default internal pull-up                        |  |

| 10  | GND         | N/A | Return  | Digital power supply return pin                                                                  |  |

| 11  | VDD33       | N/A | Power   | Digital I/O voltage; 3.3V                                                                        |  |

| 12  | VDD18       | N/A | Power   | Digital Core voltage; 1.8V                                                                       |  |

| 13  | TST         | I   | Digital | Production test                                                                                  |  |

| 14  | VDD18       | N/A | Power   | Digital I/O voltage; 3.3V                                                                        |  |

| 15  | VDD33       | N/A | Power   | Digital Core voltage; 1.8V                                                                       |  |

| 16  | GND         | N/A | Return  | Digital power supply return pin                                                                  |  |

#### 3 GENERAL DESCRIPTION

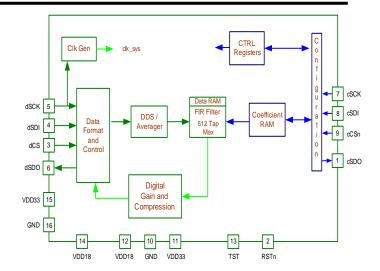

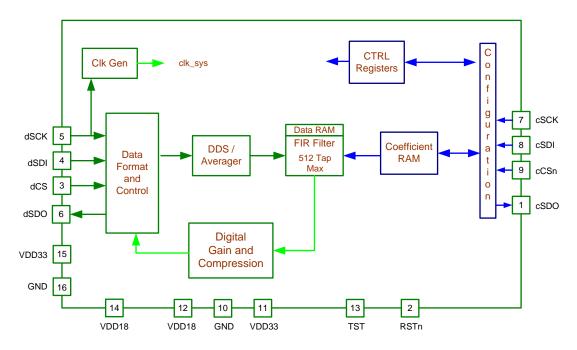

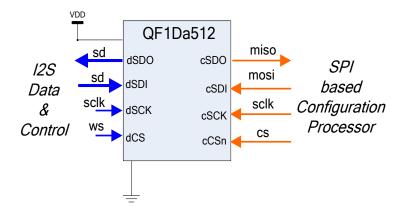

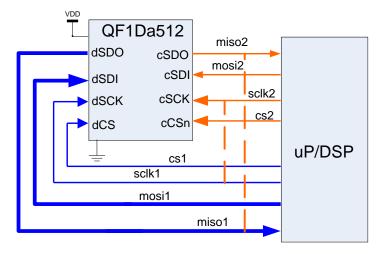

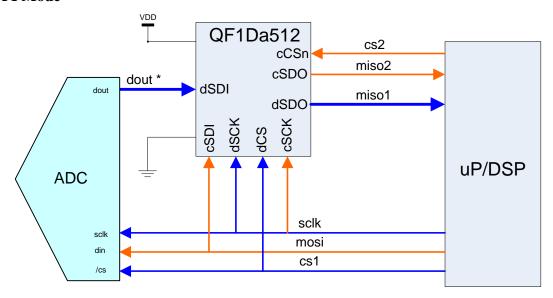

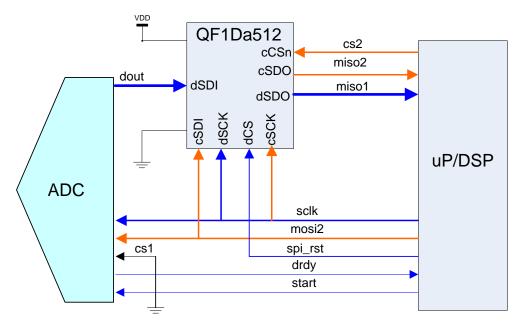

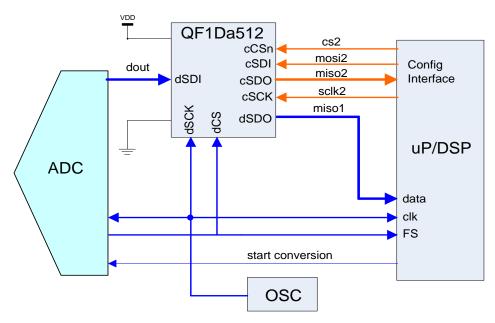

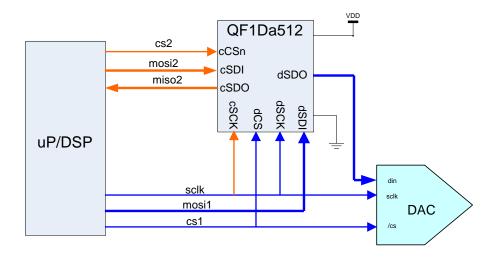

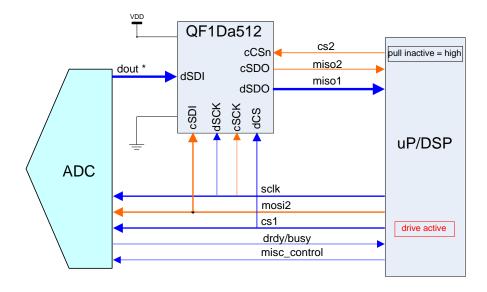

Figure 2: Functional Block Diagram

#### **Data Format and Control**

The Data Format and Control block accepts the digital serial data. It separates any header information and checks for data valid and then separates the data bits for processing. It also converts the data into the required format for the FIR filter. The data interface supports the standard I2S and SPI bus protocols. The data interface consists of the **dSCK**, **dCS**, **dSDI**, and **dSDO** pins and allows for digital data received on **dSDI** to be filtered or passed through to **dSDO**. If a header is used, it is passed unaltered along with the filtered data.

#### Averaging and Down-sampler

The Averaging / Down-sampler block down-samples the incoming data by a factor of 2 to 256. It also can be configured to average the down sampled data. Default is bypassed. This block also supports a special I2S feature of channel duplication which converts the standard left/right channel format to either all left or all right.

#### Finite Impulse Response Filter (FIR)

The FIR filter consists of up to 512 taps for a symmetric filter or 256 taps for an asymmetric filter.

#### Digital Gain and Compression (DGC)

DGC is used to maintain unity gain through the QF1Da512 for complex filters like those used in audio equalization. DGC is performed sample by sample with an instant attack and release. Both Gain and Compression (ratio) are comprised of 4 integer bits and 12 fractional bits. Quickfilter Pro™ can automatically determine Gain and Compression settings. Direct access and guidance is also available for advanced users.

#### Configuration Interface

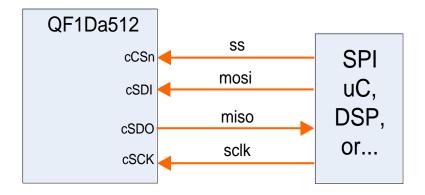

The configuration interface supports the standard SPI bus protocol and operates in SLAVE mode. **cSCK** is capable of operating up to 20 MHz, although it may be run at much lower speeds.

The configuration interface consists of the cSCK, cCSn, cSDI and cSDO pins and is used to read and write the control registers and program the coefficient memory space.

#### 4 SOFTWARE

#### **Device Configuration**

Before useful data can be output from the QF1Da512 it must first be correctly configured. Configuration parameters include the following:

- 1. Data mode of operation: I2S, SPI Normal, SPI Continuous, or Synchronous Serial mode

- 2. Data interface configuration: includes header information, use and size, and data size

- 3. Decimation and averaging configuration (if utilized)

- 4. FIR filter coefficients.

- 5. Gain and Compression (if utilized).

#### Quickfilter Audio Development Kit (QF1Da512-DK)

The Audio Development Kit is a development and evaluation platform for a stereo audio application utilizing two serial QF1Da512s. The QF1Da512-DK works in conjunction with the QF1D512-DK. The QF1D512-DK provides the interface to the Quickfilter Pro™ development software and hosts the QF1Da512 Audio Development Kit. Once programmed, the QF1Da512-DK can operate independent of the host.

The Quickfilter Pro™ Design Software allows all the necessary parameters to be generated in a quick and user-friendly manner. The user enters the desired characteristics (e.g. sampling rates, type of filter, cut-off frequencies etc.) for each channel and the software generates a configuration file for the devices. The configuration file can be immediately downloaded into the QF1Da512 on the evaluation platform, and the actual hardware **device** performance can be evaluated - in response to a user-applied signal source and sink. Device configuration parameters can be further adjusted, if necessary, until the optimum system performance is reached. Once the user is satisfied with the performance the Qf1Da512 configuration file can be saved for future use, for example to program devices in bulk prior to volume board manufacturing.

## **Quickfilter Host Development Kit (QF1D512-DK)**

The Development Kit is a complete hardware and software combination which allows for rapid development of the QF1Da512 configuration parameters for a specific application.

The Quickfilter Design Software tool allows all the necessary parameters to be generated in a quick and user-friendly manner. The user enters the desired characteristics (e.g. sampling rates, type of filter, cut-off frequencies etc.) for each channel and the software generates a configuration file for the device. The configuration file can be immediately downloaded into the QF1Da512 on the QF1Da512-DK development board, and the *actual filter performance* can be monitored - either in response to a PC-generated noise source or to a user-applied signal. Device configuration parameters can be further adjusted, if necessary, until the optimum filter performance is reached.

Once the user is satisfied with the performance the QF1Da512 configuration file can be saved for future use, for example to program the QF1Da512-DK. The QF1Da512-DK can support 2 stereo configurations for comparisons.

#### 5 GENERAL OPERATION

There are two modes of bus operation for the QF1Da512, "configure" mode, and "data" mode. The required mode is selected by writing the **FILT\_EN** bit in the **CONTROL** register (03h).

"Configure" mode is used to set up or change options in the QF1Da512. In this mode it is possible to read/write the control registers and the coefficient RAM. To *configure* the device, set both the **FILT EN** and **DIN PT** bits to 0 (see Section 6.3).

"Data" Mode is used to interface with a data source (i.e, ADC, uP, DSP, digital data stream...) and run the FIR filter. In this mode it is possible to write the control registers. To *process data* with the device, set the **FILT\_EN** bit high (see DATA INTERFACE). The format of the **dSDO** will match the format of the data coming into the **dSDI** pin.

Note: The Control registers can be written to and read from in either mode. However, to write the coefficients, the QF1Da512 must be in "configure" mode.

Rev A8 January 7, 2009 11 www.quickfiltertech.com

#### 6 CONFIGURATION INTERFACE

## SPI, Serial Peripheral Bus

#### **6.1.1** Mode of Operation

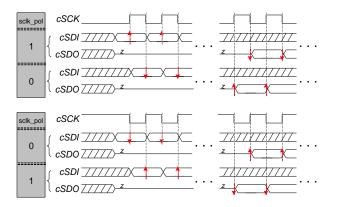

The QF1Da512 is designed to interface directly with the serial peripheral interface (SPI) of microcontrollers and Digital Signal Processors in native mode. The QF1Da512 always operates in SPI slave mode using the cSDI, cSDO, cSCK, and cCSn pins. cSDI is the input serial data, and cSDO is the output serial data (if FILT\_EN = DIN\_PT = 0). cSCK is the input serial clock. Default is to capture on rising edge, but this can be changed to capture on falling edge by writing the SCLK\_POL bit in the DCONFIG register (04h). The Control registers can be *written* while data is being processed.

#### **6.1.2 Data Format**

In order to address and read / write to the QF1Da512, **cCSn** is asserted low to select the device. When the device is in "configure" mode but is not selected, data will not be accepted via the serial input pin (**cSDI**) and the serial output pin (**cSDO**) will remain in a high impedance state.

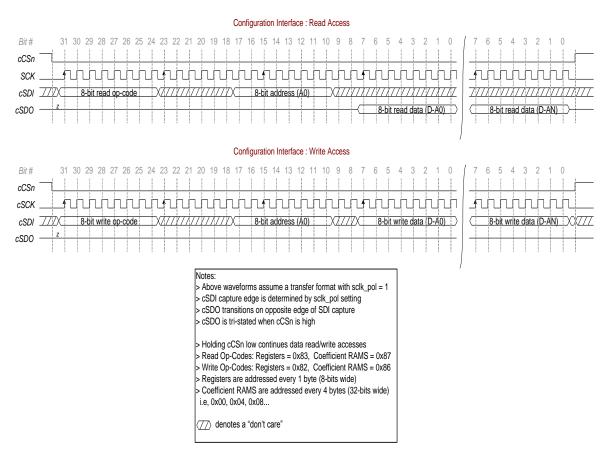

Figure 3: Configuration Data Timing

Note: There are 6 "don't care" clock cycles between the end of the op code and the 8-bit address. The value of cSDI during these clocks has no effect on the chip. There are also two "dead" clock cycles between the end of the address input and data output on the cSDO pin.

The Configuration SPI interface programs two different address spaces in the QF1Da512: a configuration register space and a coefficient memory space. The configuration register space is accessed when the Op-Codes 0x82/0x83 are used (refer to the notes above). The coefficient memory space is accessed when the Op-Codes 0x86/0x87 are used. Multiple successive registers or coefficient values may be programmed by simply appending 8-bit data values after the first data value is written. Thus the entire coefficient memory space may be written with a single Write access. Each 32-bit coefficient is written Most Significant Bit and Most Significant Byte first. Each 8-bit configuration register is written Most Significant Bit first.

The active edge of cSCK is programmable (SCLK\_POL bit in the DCONFIG register) to suit the application system timing:

Figure 4: Configuration Interface Transfer Format

#### **Sending Commands in Data Mode**

If the QF1Da512 is in Data mode and it is required to reconfigure the device, it is first necessary to switch to Configure mode. This is done by writing to the **FILT\_EN** bit using the configuration interface.

Note: While all of the configuration registers are accessible while the QF1Da512 is in Data mode, the only registers that should be written to are the CONFIG register FILT\_EN, DIN\_PT. Writes to other registers might result in corrupted filter data or other unpredictable behavior.

In configurations in which the **cSDI** and the **dSDI** pins have been tied together, allowing for single SPI port data filtering, it is necessary to ensure that the incoming data format does not match either the configuration register access format (see Table 4 Configuration Register Access Format) or the FIR coefficient memory access format (see Table 2 Register and Memory Format) as this may cause unintentional writes to configuration or coefficient memory. In other words, take care to ensure that the most significant byte of the data input does not match either of the WRITE opcodes.

#### 7 DATA INTERFACE

#### **Modes of Operation**

The QF1Da512 supports I2S or SPI and is designed to interface directly with a variety of ADC converters.

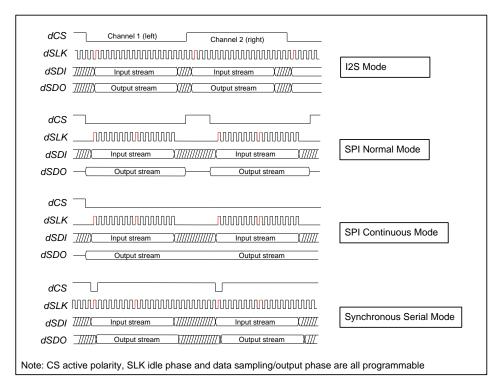

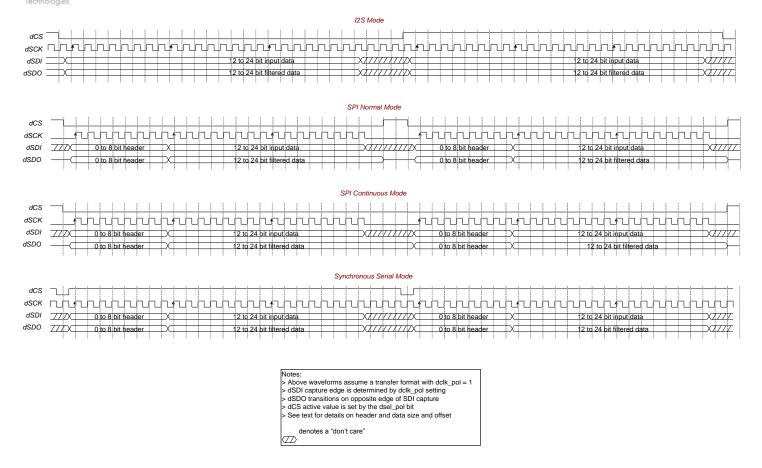

1. I2S Mode

A word select line (**WS** on the **dCS** input) indicates which of two time-division multiplexed data channels is being transmitted. The channels are transmitted alternately on the data line (**SD** on the **dSDI** input) and are synchronized by a clock line (**SCK** on the **dSCK** input).

- 2. SPI Mode

- a. Normal Mode

The data is framed by the dCS input signal

b. Continuous Mode

Once dCS is active, data is output corresponding to clock bursts on the dSCK input

c. Synchronous Serial Mode

**dCS** is used as a trigger to indicate the start of each new sample period. **dSCK** runs continuously, filtered data is output on the next *n* cycles of **dSCK** according to the programmed word length.

Figure 5: Interface Modes

The QF1Da512 supports both 2's complement and offset binary data formats. The data format is set by the **FORMAT** bit and the data mode is selected by the **MODE0** and **MODE1** bits in the **DCONFIG** register (04h).

| MODE1 | MODE0 | Bus Mode                |

|-------|-------|-------------------------|

| 1     | Х     | (Default) I2S Mode      |

| 0     | 0     | SPI Normal Mode         |

| 0     | 1     | SPI Continuous Mode     |

| 1     | Х     | Synchronous Serial Mode |

Figure 6: Data Format Selection

The data interface utilizes the **dSDI** (**SD** for I2S), **dSDO** (**SD** for I2S), **dCS** (**WS** for I2S) and **dSCK** (**SCK** for I2S) pins. **dSDI** is the input serial data, and **dSDO** is the output serial data (if **FILT\_EN** = 1). **dSCK** is the input data clock and **dCS** is the framing signal for the input data:

Figure 7: Data Interface Timing Diagram

Note: In "SPI Continuous Mode" the value of the dSDO output (Isb) at the end of the data sample will be held constant until the header is output for the next data sample.

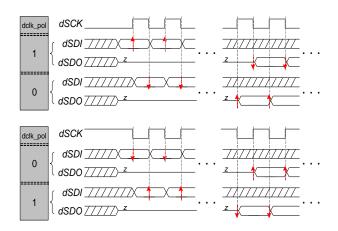

Default operation is to capture on the rising edge of dSCK (SCK for I2S), but this can be changed to capture on falling edge by writing the DCLK\_POL bit in the DCONFIG register (04h). The active polarity of dCS (WS for I2S) is also programmable via the DCONFIG register (DSEL\_POL bit), which is especially useful for applications where the input pins are paired; e.g., dSDI (SD for I2S) and cSDI, dSCK (SCK for I2S) and cSCK, cCSn and dCS (WS for I2S).

Figure 8: Data Interface Transfer Format

The QF1Da512 supports data widths in the range of 12 and 24 bits, and headers of up to 8 bits.

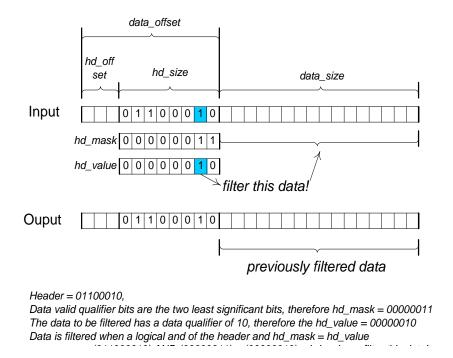

The format of the input data stream is specified in the HD\_OFFSET (address 09h), HD\_SIZE (address 0Ah), DATA\_OFFSET (address 000Dh), and the DATA\_SIZE (address 000Eh) registers. These registers set the header offset, header size, data offset, and data size respectively of the individual data sample. This allows for a large number of different data formats. Additionally, if the sample data contains a data valid qualifier, this field can be masked by configuring the HD\_MASK, address 0Bh and HD\_VALUE, address 0Ch registers. The filtering of the sample will occur only if a logical and of the header value and HD\_MASK matches HD\_VALUE, address 0Ch, otherwise the raw sample data is passed directly through to the dSDO pin unfiltered.

Figure 9: Data Header Masking Example

When configured for **FILTER** mode, **FILT\_EN** bit set to '1'in the **CONTROL** register (03h), the output stream on the **dSDO** pin will have the same format as the input stream coming in on the **dSDI** pin. The header data is passed directly through to the **dSDO** pin while the filtered data has a latency associated with it due to the properties of the FIR filter. If no filtering is being done (data valid qualifier in header does not match **HD\_VALUE**) coincident header and data will be passed through for possible use down-stream of the QF1Da512 device.

When averaging and / or down sampling is active, the data rate will be the same as the incoming data rate, but the number of valid samples will be reduced by the averaging / down sampling rate.

#### **Data Passthrough**

Sometimes it is required to pass-through the data present at **dSDI** directly to the **dSDO** output, for example when passing configuration data back from an ADC to the host controller. The data pass-through bit, **DIN\_PT**, in the **CONTROL** register (03h), will force this to occur when it is set to 1. In this mode dSDO follows dSDI immediately, there is no clocking required. This control bit overrides all other settings for **dSDO** functionality (see next section) and should be set to 0 for either configuration mode or data filtering.

#### 8 DIGITAL DOWN SAMPLING

#### **Downconverter**

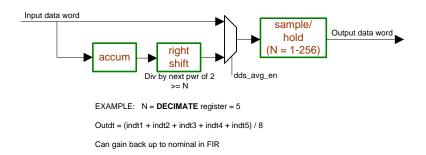

The QF1Da512 provides the capability to down-sample the incoming data samples. The divider ratio is any integer value and ranges from 1 (no down-sampling) to 256. The value is selected in the **DECIMATE** register (address 08h). In addition to down-sampling and "throwing away" the intermediate samples, and option is provided to average the samples and forward the averaged value to the downstream FIR filter. The averaging block effectively adds up N samples, where N is the down-sampling rate, then divides by a power of 2 by right shifting the result. Note that if averaging is enabled with a down-sampling rate that is not a power of 2, system gain will be affected. The averaging block always divides by the next highest power of 2 when a *non* power of 2 down-sampling rate is detected.

Refer to the diagram below. This feature can be useful for noise reduction and possibly increasing bit resolution of the input data stream. To select filtering of the down sampled data, **DEC\_AVG\_EN**, bit 0 of the **FCONFIG** register (address 05h) is enabled.

Figure 10: Averaging /Down-sampler Block Diagram

## **Channel Duplication**

Channel duplication is a special feature in I2S mode (DECIMATE must also be set to 00h). Duplication uses the standard left-right channel framing to create 2 channels of either right or left data. Using 2 QF1Da512s, the first device will both filter the specified channel and duplicate (unaltered) the same channel's input data to the opposite channel's frame on dSDO. The second device will be programmed to filter the unaltered data channel (and the previously filtered data will be passed to dSDO). For example, if the first device is in Duplication mode, left-channel active and functions as a low pass filter, then the output of the first device will be Left-lowpass/Left-raw-data (channel-1/channel-2). The second device is in Standard mode, right-channel active and functions as a high pass filter, then the output of the second device will be Left-lowpass/Left-highpass.

#### 9 FIR FILTER

#### **Modes of Operation**

The QF1Da512 filter can implement a symmetric 512-tap FIR filter or a 256-tap asymmetric FIR filter, which is used to define the precise filtering characteristics desired. The filter coefficients are 32 bits wide. The filtering provided by the software may be of the following types: low-pass, notched low-pass, high-pass, band-pass, dual band-pass, band-stop, and dual band-stop. Currently available filter algorithms include Parks-McClellan and Windowed Sync. User defined filters can also be implemented.

The QF1Da512 can be loaded with up to 256 filter coefficients. To implement a non-folded (asymmetric) filter the **FIR\_FOLD** bit in the **FCONFIG** register (05h) should be set to 0, allowing a filter of up to 256 taps. A folded (symmetric) filter of up to 512 taps can be implemented if **FIR\_FOLD** is set to 1.

Note: For a folded filter, if the number of coefficients (N) is even, a filter of 2N taps will be realized. If N is odd, a filter of 2N-1 taps will result.

The Quickfilter software allows the user to enter the filter characteristics required and see the predicted performance in terms of frequency and impulse response. Once the desired performance has been attained, the configuration can be downloaded to the QF1Da512, and the actual filter performance verified, by using the development kit. The development board can be fed with a white noise source (or other source as desired by the user) and the software can display an FFT of the QF1Da512's filter response.

#### FIR Latency

The delay introduced by the Qf1Da512 is dependent on the number of taps of the filter and the data rate of the samples coming into the FIR filter. The delay is calculated by the following equation:

#### Standard Mode

Filtered Channel: FIR Delay = (# taps - 1)/2 \* 1/fs + 8/fs

Bypassed Channel: Delay = 0

**Duplication Mode**

Filtered Channel: FIR Delay = (# taps - 1)/2 \* 1/fs + 12/fs

Replicated Channel: FIR Delay = 3/fs

In standard mode for data sampling at a 48 kHz rate, the latency will result in:

512 tap (maximum) filter: Latency = 5.49ms

100 tap filter: Latency = 1.20ms

In duplication mode for data sampling at a 48 kHz rate, the latency will result in:

Two 512 tap (maximum) filters in series: Latency = 5.57ms

Two 100 tap filters in series: Latency = 1.28ms

Note: If using the Quickfilter Pro development software the latency of a particular filter is calculated and displayed in the Information bar on the "Filter" tab.

Duplication mode is comprised of two serial QF1Da512s of which the first device is in duplication mode and the second device is in standard mode.

## 10 Digital Gain and Compression (DGC)

For standard FIR pass-band/stop-band filters, DGC is not necessary as the pass-band is designed for 0dB (unity). The Quickfilter Pro™ Freehand filter editor supports an audio mode where the gain and compression variables are automatically determined for the user. Optionally, Quickfilter Pro™ provides direct access to and guidance for all the DGC parameters.

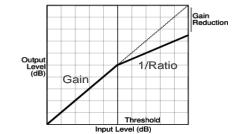

#### **Mode of Operation**

When Compression is enabled, Gain is applied to the FIR output signal when the input signal is below a Threshold value. Above the Threshold value, Gain and Compression are applied to the FIR output signal. When the Compressor is bypassed (**THRES** = FFh), only Gain is applied to the FIR output signal. The default value for Gain is 1.

Both Gain and Compression (ratio) are comprised of 4 integer bits and 12 factional bits.

The DGC parameters are,

- 1. Threshold signal levels above this value are compressed

- Gain the amount of gain to apply to the FIR output signal below the Threshold

- 3. Ratio the inverse slope of the compression curve above the Threshold

- 4. Maximum Maximum input amplitude value

Note – not all combinations of DGC parameters yield valid compression values settings. Therefore, it is best to use Quickfilter Pro™ to properly set these parameters. Also, care must be taken to avoid clipping when using the DGC function. Additional guidance can be found in section 14.

#### 11 CONTROL REGISTERS

#### Overview

The QF1Da512 internal data is separated into configuration registers and coefficient memory.

Table 2 Register and Memory Format

| Registers            | Address Range   | Data Size | Write OpCode | Read Opcode |

|----------------------|-----------------|-----------|--------------|-------------|

| Device Configuration | 0x0000 - 0x0021 | 8 bit     | 0x82         | 0x83        |

| FIR Coefficients     | 0x0000 – 0x00FF | 32 bit    | 0x86         | 0x87        |

Table 3 Control Registers

| Hex*  | Register Name | Description                              |  |

|-------|---------------|------------------------------------------|--|

| 0000h | TEST_RW       | Software Register, Test Reads and Writes |  |

| 0001h | CHIP_ID       | Chip ID Number                           |  |

| 0002h | VERSION       | Chip Version Number                      |  |

| 0003h | CONTROL       | Mode Control Register                    |  |

| 0004h | DCONFIG       | Data Format Control                      |  |

| 0005h | FCONFIG       | Filter Control and Status                |  |

| 0006h | NUM_TAPS      | Number of Taps, lower bits               |  |

| 0007h | NUM_TAPS      | Number of Taps, upper bits               |  |

| 0008h | DECIMATE      | Down-sampling Rate                       |  |

| 0009h | HD_OFFSET     | Header Offset                            |  |

| 000Ah | HD_SIZE       | Header Length                            |  |

| 000Bh | HD_MASK       | Header Valid Mask                        |  |

| 000Ch | HD_VALUE      | Header Valid Value                       |  |

| 000Dh | DATA_OFFSET   | Data Offset                              |  |

| 000Eh | DATA_SIZE     | Data length                              |  |

| 000Fh | GAIN          | Digital Gain Value, lower bits           |  |

| 0010h | GAIN          | Digital Gain Value, upper bits           |  |

| 0011h | THRESH        | Compression Threshold, lower bits        |  |

| 0012h | TREASH        | Compression Threshold, upper bits        |  |

| 0013h | MULTI         | Compression Multiplicor, lower bits      |  |

| 0014h | MULTI         | Compression Multiplicor, upper bits      |  |

| 0015h | ADDOR         | Compression Addor, lower bits            |  |

| 0016h | ADDOR         | Compression Addor, upper bits            |  |

| 0017h | IO_TST        | TST Pin Configuration                    |  |

| 0018h | IO_RST_N      | RSTn Pin Configuration                   |  |

| 0019h | IO_DCLK       | dSCK Pin Configuration                   |  |

| 001Ah | IO_DSEL       | dCS Pin Configuration                    |  |

| 001Bh | IO_DIN        | dSDI Pin Configuration                   |  |

| 001Ch | IO_CS_N       | CS_N cCSn Pin Configuration              |  |

| 001Dh | IO_SCLK       | cSCK Pin Configuration                   |  |

| 001Eh | IO_SDI        | IO_SDI cSDI Pin Configuration            |  |

| 001Fh | IO_SDO        | IO_SDO cSDO Pin Configuration            |  |

| 0020H | IO_DOUT       | dSDO Pin Configuration                   |  |

| 0021H | TEST          | Chip Test Register                       |  |

# **Configuration Registers**

Accessing the configuration registers uses an SPI access as shown below.

**Table 4 Configuration Register Access Format**

|                | OPCODE | ADDRESS       | UNUSED     | DATA                             |

|----------------|--------|---------------|------------|----------------------------------|

| Number of bits | 8 bits | 14 bits       | 2 bits     | 8 bits per register <sup>†</sup> |

| Write Access   | 82h    | 0000h – 0021h | Don't care | 00h – FFh                        |

| Read Access    | 83h    | 0000h – 0021h | Don't care | 00h – FFh                        |

Note: \* Multiple registers can be written/read by extending the SPI access cycle.

Listed below are the detailed configuration register definitions.

## → 1 00h TEST\_RW (User Register)

|       | Bit 7 | Bit 6                                                                                                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| POR   | 0     | 0                                                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

|       | W/R   | W/R                                                                                                                   | W/R   | W/R   | W/R   | W/R   | W/R   | W/R   |  |  |

| Bits  | D7    | D6                                                                                                                    | D5    | D4    | D3    | D2    | D1    | D0    |  |  |

| D7-D0 |       | Provided as a blank user byte for the programmer to read and write to as a test. This byte defaults to 0 at power up. |       |       |       |       |       |       |  |  |

## ightarrow 2 01h CHIP\_ID (Chip ID) - READ ONLY

|         | Bit 7 | Bit 6                                                                                                                                              | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| POR     | 1     | 1                                                                                                                                                  | 0     | 0     | 0     | 0     | 0     | 0     |  |

|         | R     | R                                                                                                                                                  | R     | R     | R     | R     | R     | R     |  |

| Bits    | ID7   | ID6                                                                                                                                                | ID5   | ID4   | ID3   | ID2   | ID1   | ID0   |  |

| ID7-ID0 |       | This read-only byte contains a number describing the identification of the QF1Da512 device.  Identification number of the QF1Da512, default = C0h. |       |       |       |       |       |       |  |

# $\rightarrow \textbf{3} \quad \textbf{02h VERSION} \; (\text{Version}) \; \text{-} \; \text{READ ONLY}$

|               | Bit 7                                                                                                                                | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| POR           | 0                                                                                                                                    | 0     | 0     | 0     | 0     | 0     | 0     | 1     |  |

|               | R                                                                                                                                    | R     | R     | R     | R     | R     | R     | R     |  |

| Bits          | VER7                                                                                                                                 | VER6  | VER5  | VER4  | VER3  | VER2  | VER1  | VER0  |  |

| VER7-<br>VER0 | This read-only byte contains a number describing the version of the QF1Da512 device.  Version number of the QF1Da512, default = 01h. |       |       |       |       |       |       |       |  |

# → 4 03h CONTROL (Filter/Pass Through Control)

|         | Bit 7        | Bit 6                                                                                                                                                                                                     | Bit 5        | Bit 4                                            | Bit 3     | Bit 2  | Bit 1 | Bit 0 |  |  |  |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------|-----------|--------|-------|-------|--|--|--|

| POR     | 0            | 0                                                                                                                                                                                                         | 0            | 0                                                | 0         | 0      | 0     | 0     |  |  |  |

|         | UNUSED       | UNUSED                                                                                                                                                                                                    | UNUSED       | UNUSED                                           | UNUSED    | UNUSED | RW    | RW    |  |  |  |

| Bits    | X            | X X X X X X DIN_PT FILT_EN                                                                                                                                                                                |              |                                                  |           |        |       |       |  |  |  |

| Bit7-2  | Unused       |                                                                                                                                                                                                           |              |                                                  |           |        |       |       |  |  |  |

| DIN_PT  | 0 = Normal   | operation, dS                                                                                                                                                                                             | DO pin outpu | the QF1Da51<br>ts the signal p<br>uts the data o | ath data. |        |       |       |  |  |  |

| FILT_EN | 0 = Configui | Filter Enable (FILT_EN): Enable the Signal processing blocks and data path  0 = Configuration mode, cSDO pin outputs the configuration register.  1 = Filter mode, dSDO pin outputs the signal path data. |              |                                                  |           |        |       |       |  |  |  |

# → 5 **04h DCONFIG** (Data Format Control)

|                       | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 5                    | Bit 4          | Bit 3         | Bit 2           | Bit 1          | Bit 0    |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------|---------------|-----------------|----------------|----------|--|--|

| POR                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                        | 0              | 1             | 0               | 1              | 1        |  |  |

|                       | RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RW                       | RW             | RW            | RW              | RW             | RW       |  |  |

| Bits                  | DUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MODE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MODE0                    | FORMAT         | dCS_POL1      | dCS_POL0        | dSCK_POL       | cSCK_POL |  |  |

| DUP                   | RW DUP MODE1 MODE0 FORMAT dCS_POL1 dCS_POL0 dSCK_POL cSCK_P  Duplicates (but does not alter) dSDI on channel selected by dCS_POL to output dSDO. Requires DECIMATE (08h) =00h and dCS as per above.  0 = Input data is not duplicated.  1 = Input data is duplicated.  Selects the data input mode.  00 = Input data mode is SPI Normal Mode.  01 = Input data mode is SPI Continuous Mode.  10 = Input data mode is Synchronous serial mode  10 = Input data mode is I2S Mode  Selects the data format of the incoming data.  0 = Incoming data format is 2's complement.  1 = Incoming data format is offset binary.  Selects polarity of the dCS pin for SPI and Synchronous serial modes. Also used in processing I2S data if the DUP bit is set.  00 = dCS is active low for SPI modes and Synchronous serial mode when only a single edge/level is being used as a trigger | equires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |                |               |                 |                |          |  |  |

| MODE1 –<br>MODE0      | 00 = Input 0<br>01 = Input 0<br>10 = Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | = Input data is not duplicated. = Input data is duplicated. elects the data input mode. 0 = Input data mode is SPI Normal Mode. 1 = Input data mode is SPI Continuous Mode. 0 = Input data mode is Synchronous serial mode 0 = Input data mode is I2S Mode elects the data format of the incoming data. = Incoming data format is 2's complement. = Incoming data format is offset binary. elects polarity of the dCS pin for SPI and Synchronous serial modes. Also used in processing I2S data if the DUP bit is set. 0 = dCS is active low for SPI modes and Synchronous serial mode when only a single edge/level is eing used as a trigger 1 = dCS is active high for SPI modes and Synchronous serial mode when only a single edge/level is eing used as a trigger 1 = dCS is active both high and low. This is the normal mode for I2S data. |                          |                |               |                 |                |          |  |  |

| FORMAT                | 0 = Incomir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | elects the data format of the incoming data.  = Incoming data format is 2's complement.  = Incoming data format is offset binary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |                |               |                 |                |          |  |  |

| dCS_POL1-<br>dCS_POL0 | data if 00 = dCS is being used 01 = dCS is being used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | data if the DUP bit is set.  00 = dCS is active low for SPI modes and Synchronous serial mode when only a single edge/level is being used as a trigger  01 = dCS is active high for SPI modes and Synchronous serial mode when only a single edge/level is being used as a trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |                |               |                 |                |          |  |  |

|                       | 10 = Filter t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | the incoming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | left channel o           | data (the data | where dCS is  |                 |                |          |  |  |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          | Copy (unalter  | ed) the incom | ing left chann  | el data to the | right    |  |  |

|                       | the d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SDO right cha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | annel output.            |                |               |                 |                |          |  |  |

| dSCK_POL              | Selects the the opposit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | clock edge o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | of dSCK on w<br>r mode). | hich the data  | on the dSDI p | oin is captured | d. dSDO is o   | utput on |  |  |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ) = dSDI is captured on the falling edge of dSCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |                |               |                 |                |          |  |  |

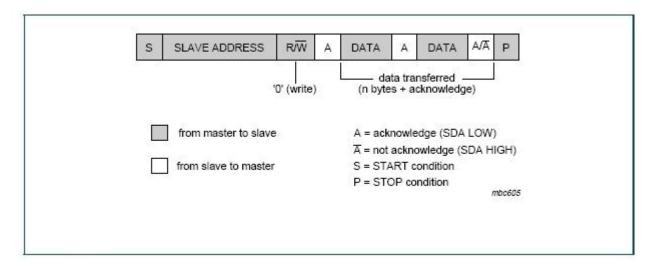

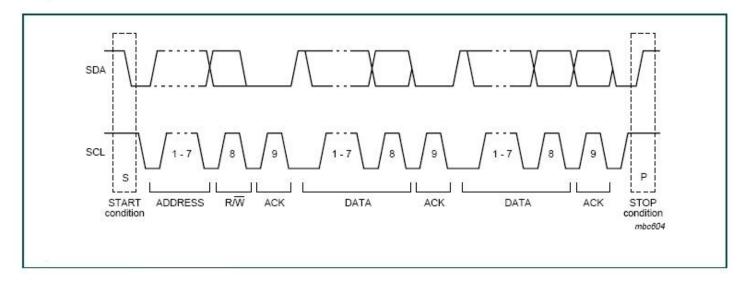

| cSCK_POL              | edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |                | •             | red. cSDO is    | output on the  | opposite |  |  |